Document Number:AN4587 Rev 0, 08/2013

# ADC FIFO Application on the S08P Family

by: Wang Peng

# **1** Introduction

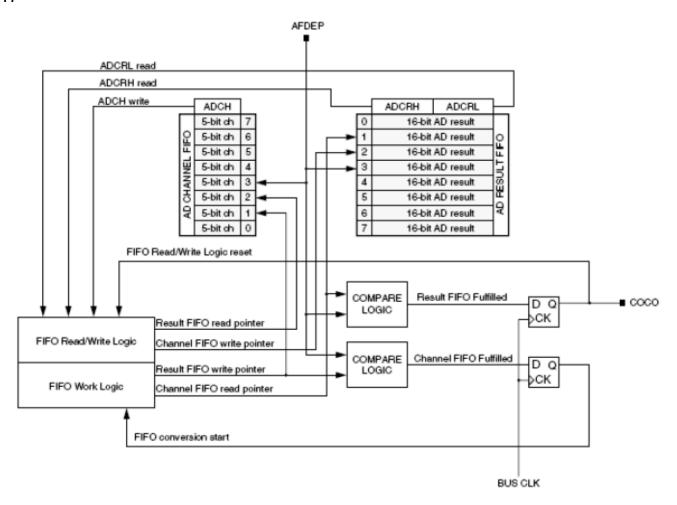

This application note serves as a guide for design engineer on how to use FIFO of ADC module on S08P family with demo code provided. There are many important features in S08P family, one of which supports ADC FIFO. This means that an analog input channel conversion result can be saved in the FIFO, and when all channel conversions in the input FIFO are done, it sets flag or generates interrupt. This is very useful for the applications which use many ADC channels and frequently process ADC conversion. The ADC module contains two FIFOs, analog input channel FIFO and conversion result FIFO:

- Analog input channel FIFO is used to buffer analog input channels. The analog input channel FIFO is accessed by ADCH bits in ADC\_SC1, when FIFO function is enabled. The analog channel must be written to this FIFO in order.

- Conversion result FIFO is used to store analog results. The result FIFO is accessed by ADC\_RH:ADC\_RL registers, when FIFO function is enabled. The result must be read via these two registers in the same order of analog input channel FIFO to get the proper results.

The following figure describes the structure of FIFO:

#### Contents

| 1 | Introduction |                  |   |  |

|---|--------------|------------------|---|--|

| 2 | Application  |                  | 2 |  |

|   | 2.1          | Initialization   | 2 |  |

|   | 2.2          | Software trigger | 3 |  |

|   | 2.3          | Hardware trigger | 6 |  |

|   | 2.4          | Scan mode        | 7 |  |

|   | 2.5          | Compare function | 8 |  |

| 3 | Cond         | clusion          | 9 |  |

| 4 | References   |                  |   |  |

| 5 | Glossary     |                  |   |  |

| 6 | Revi         | Revision history |   |  |

|   |              |                  |   |  |

Figure 1. ADC FIFO structure

# 2 Application

This module supports up to 8-deep result FIFO and channel FIFO with selectable FIFO depth. Through register AFDEP, user can flexibly set FIFO depth depending on different requirements, and also select software or hardware trigger to start conversion. In some cases, if required to determine if the input analog channel is greater or less than the value specified. To do so, enable compare function and FIFO to select 'AND' or 'OR' to check the analog input state specified by the channel FIFO. When condition is true, it will set COCO flag, and if interrupt is enabled, it will generate interrupt.

# 2.1 Initialization

An initialization procedure must be performed before the ADC module can be used to start conversions with FIFO. A typical sequence of initialization procedure is as follows:

- 1. Update the configuration register (ADC\_SC3) to select the input clock source and divide ratio used to generate the internal clock, ADCK. This register is also used for selecting sample time and low-power configuration.

- 2. Update the configuration register (ADC\_SC4) to select the FIFO scan mode, FIFO compare function selection (OR or AND function), and FIFO depth.

- 3. Update status and control register 2 (ADC\_SC2) to select the conversion trigger (hardware or software), compare function options if enabled.

### ADC FIFO Application on the S08P Family, Rev 0, 08/2013

4. Update status and control register 1 (ADC\_SC1) to select whether conversions will be continuous or completed only once, and to enable or disable conversion complete interrupts. The input channel on which conversion will be performed is also selected here. The initial value of the input channel field ADCH can be 0b11111 which disables ADC module.

Example 1, ADC FIFO initialization is as follows:

```

Void ADC_Init( void )

{

/* The following code segment demostrates how to initialize ADC by long

sample time, bus frequency, and 12 bit mode, software triggerd from ADO, AD1, AD2, and AD3

external pins with 4-level FIFO enabled, and enable interrupt */

ADC_APCTL1 = 0x0f;

ADC_APCTL2 = 0x00;

ADC_SC3_ADIV = ADC_ADIV_DIVIDE_4;

ADC_SC3_MODE = ADC_MODE_12BIT;

ADC_SC3_ADLSMP = 1; // enable long sample

ADC_SC3_ADICLK = CLOCK_SOURCE_BUS_CLOCK;

ADC_SC4_AFDEP = 0x03; // FIFO level 4

ADC_SC1_AIEN = 1; // enable interrupt

}

```

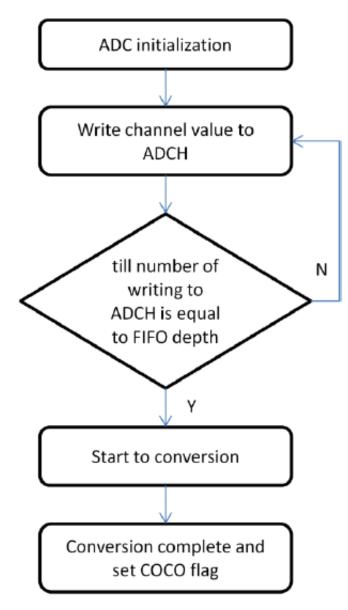

## 2.2 Software trigger

When ADC module is enabled as software trigger, write to ADCH will fill one ADC channel to channel FIFO. Once fulfilled the channel FIFO on the level specified by the AFDEP, ADC conversion will be started immediately. Conversion result will be stored in the result FIFO, it is accessed by reading ADC\_RH:ADC\_RL registers, after conversion is complete, it will set COCO flag, if enable interrupt, and also generate an interrupt request. The following flow chart explains the software trigger process:

Figure 2. Software trigger process

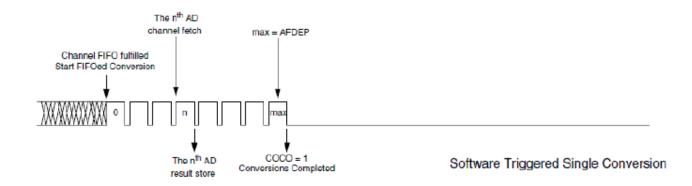

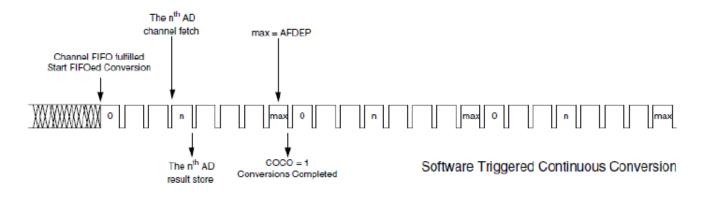

If the number of writing to register ADCH is less than depth specified by register AEFDEP, it does not start conversion until the channel FIFO is full. When writing channel value to ADCH is continued after ADC starts conversion and before COCO flag is set, it will abort the current conversion. Selecting the continues mode after conversion completes will initialize a new conversion. The following figure describes the difference between single and continuous conversion:

#### Application

## Figure 4. Software triggered continuous conversion

The sample code to initialize the ADC module with FIFO is as follows:

```

void ADC ConversionWithFifo( void )

{ /* initialize the ADC module to enable FIFO , and software trigger mode */

ADC APCTL1 = 0x0f;

ADC_APCTL2 = 0x00;

ADC_SC3_ADIV = ADC_ADIV_DIVIDE_4;

ADC_SC3_MODE = ADC_MODE_12BIT;

ADC SC3 ADLSMP = 1;

ADC SC3 ADICLK = CLOCK SOURCE ADACK; //select bus clock as clock source

ADC SC4 AFDEP = 0 \times 06; // FIFO level 7

ADC SC4 ASCANE = 0; // disable scan mode

/* write channel FIFO till fulfilled*/

ADC_SC1_ADCH = 0x1d; // write channel fifo 1

ADC_SC1_ADCH = 0 \times 02; // write channel fifo 2

ADC_SC1_ADCH = 0x03; // write channel fifo 3

ADC SC1 ADCH = 0x1d; // write channel fifo 4

ADC_SC1_ADCH = 0x16; // write channel fifo 5

ADC_SC1_ADCH = 0x1d; // write channel fifo 6

ADC SC1 ADCH = 0x1e; // write channel fifo 7

/* channel FIFO is ffulfilled, start to trigger conversion */

While( !ADC SC1 COCO);

// COCO flag is set, read result

while( !ADC SC2 FEMPTY )

{ // read data from ADC result register

uiADC Buff[ucADC Count++] = ADC R;

```

ADC FIFO Application on the S08P Family, Rev 0, 08/2013

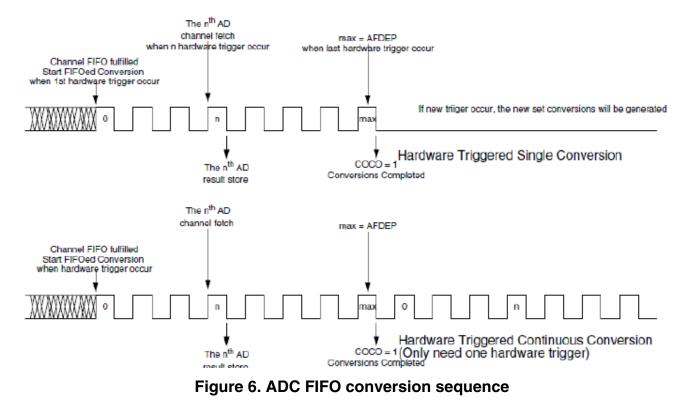

## 2.3 Hardware trigger

When a hardware trigger occurs, it only fetches one analog channel in order from input analog channel FIFO and then saves conversion value to result FIFO. Whereas in software trigger, after completing the conversion, it fetches from the next input channel in order till all of channels in channel FIFO are completed. Once the conversion completes, an automatic fetch for next analog value from channel FIFO will be done.

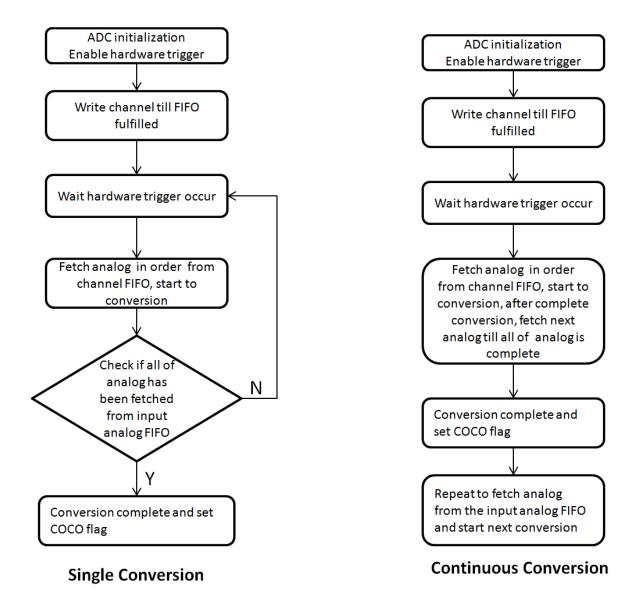

## Figure 5. Hardware trigger flowchart

The preceding flowchart describes the difference between single conversion and continuous conversion with hardware trigger.

The following figure describes the progress of ADC conversion with hardware trigger.

## 2.4 Scan mode

The FIFO also provides scan mode to simplify the dummy work of input channel FIFO. When the ASCANE bit in ADC\_SC4 is set in FIFO mode, the FIFO will always use the first dummied channel in spite of the value in the input channel FIFO. The ADC conversion starts to work in FIFO mode as soon as the first channel is dummied. The following write operation to the input channel FIFO will cover the first channel element in this FIFO. In scan FIFO mode, the COCO bit is set when the result FIFO is fulfilled according to the depth indicated by the AFDEP bits in ADC\_SC4 register.

```

The sample code of scan mode is as follows:

void ADC ScanModeWithFIFO( void )

uint8 t i;

uint16_t uiADC_Result[5];

uint8 \overline{t} ucCoun\overline{t};

ADC APCTL1 = 0x0f; // enable channel 0 - 3

ADC_APCTL2 = 0 \times 00;

ADC SC3 ADIV = ADC ADIV DIVIDE 4;

ADC SC3 MODE = ADC MODE 12BIT;

ADC SC3 ADLSMP = 0;

ADC SC3 ADICLK = CLOCK SOURCE ADACK;

ADC SC4 AFDEP = 0x03; // FIFO level 4

ADC SC4 ASCANE = 1; // enable FIFO scan mode

//start to conversion

ADC SC1 = 0x01; //write channel value

//wait conversion complete

ADC FIFO application on PT60

10 Freescale Semiconductor

while( !ADC SC1 COCO );

ucCount = 0;

while( !ADC_SC2_FEMPTY )

uiADC Result[ucCount] = ADC R;

printf("0x%x,",uiADC Result[ucCount]);

```

#### ADC FIFO Application on the S08P Family, Rev 0, 08/2013

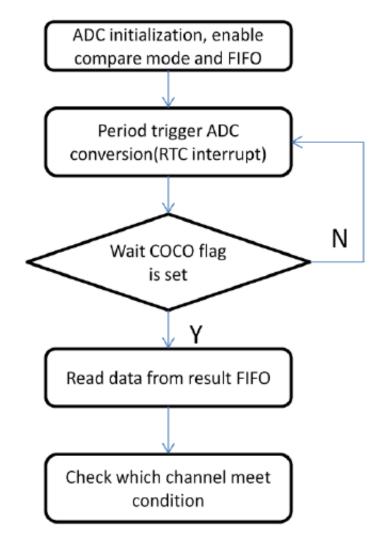

# 2.5 Compare function

COCO will not set if the following conditions are true:

- If none of the compare condition is true when ACFSEL is low.

- If not all the compare conditions are true when ACFSEL is high.

## Figure 7. FIFO comparison flow chart

It supports automatic comparison of the ADC conversion result with value specified by ADC\_CV, and sets only COCO flag when condition is true.

# 3 Conclusion

The ADC module supports FIFO operation to minimize the interrupts of CPU and improve the efficiency to access ADC module. It provides the software and hardware trigger as well as configurable FIFO depth, which makes it suitable for different applications. In addition, the compare function can work in low-power mode, and when condition is true, it can automatically wakes the MCU from low-power mode. This is very useful for low-power applications.

## **4** References

Following documents are available on freescale.com :

- MC9S08PT60RM: MC9S08PT60 Reference Manual

- AN1259: System Design and Layout Techniques for Noise Reduction in MCU-based Systems

## 5 Glossary

| BDM  | Background Debug Mode   |

|------|-------------------------|

| CRC  | Cyclic Redundancy Check |

| ECC  | Error Correction Codes  |

| RTC  | Real Time Counter       |

| ТРМ  | Timer/PWM Module        |

| FTM  | Flextimer Module        |

| МТІМ | Modulo Timer            |

| WDOG | Watchdog                |

| TSI  | Touch Sense Input       |

## 6 Revision history

| Revision number | Date    | Substantial changes |

|-----------------|---------|---------------------|

| 0               | 08/2013 | Initial release     |

#### How to Reach Us:

Home Page: freescale.com

Web Support: freescale.com/support Information in this document is provided solely to enable system and software implementers to use Freescale products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. Freescale reserves the right to make changes without further notice to any products herein.

Freescale makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. Freescale does not convey any license under its patent rights nor the rights of others. Freescale sells products pursuant to standard terms and conditions of sale, which can be found at the following address: freescale.com/SalesTermsandConditions.

Freescale, the Freescale logo, and CodeWarrior are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. All other product or service names are the property of their respective owners.

© 2013 Freescale Semiconductor, Inc.

Document Number AN4587 Revision 0, 08/2013