# Using the MPC5777M MCAN Module to Exchange CAN FD Messages

by: Graham Rice

# **1** Introduction

A CAN network (Controller Area Network) is an asynchronous serial bus network that connects devices, sensors and actuators for control applications. This multimaster communication protocol was first developed in 1986 for automotive application data rate of up to 1 Mbps with high integrity. CAN is now standardised in ISO 11898, ISO 16845 and SAE J1939 for automotive, industrial and general communications. Since embedded 1993. Freescale have included CAN controllers to power management chips and many 8-bit, 16-bit and 32-bit embedded architectures, including Qorivva automotive microcontrollers and QorIQ network processors.

The MPC57xx family of microcontrollers embed the Multimaster CAN (MCAN) module. This application note demonstrates how to use the MPC5777 MCAN module and more specifically the latest CAN FD (Flexible Data) features that are included in the MCAN module.

Using the Freescale MPC57xx motherboard and MPC5777M expansion card with the example code provided, previous CAN experience is not

## Contents

| 1         | Introduction1                              |

|-----------|--------------------------------------------|

| 2         | CAN FD overview2                           |

| 3         | Configuring and using the MCAN module 4    |

| 4         | Configuring the MCAN transmission          |

| sche      | eme4                                       |

| 5         | Assigning message memory space9            |

| 6<br>swit | Configuring CAN FD with bit rate<br>cching |

| 7         | Filtering messages by ID number12          |

| 8         | Transmitting, receiving and cancelling     |

| mes       | sages 16                                   |

| 9         | Conclusion                                 |

© 2014 Freescale Semiconductor, Inc.

necessary. If you do require basic CAN training before reading this application note, please go to <u>CAN</u> link. Examples used in this document are designed to demonstrate the latest MCAN module capabilities.

## 1.1 Objectives

After reading this document the reader will be able to:

- Understand the improvements available with CAN FD

- Perform basic transmit and receive operations with the MCAN module

- Configure memory space to transmit and receive messages

- Filter the received messages by the message ID number

- Send and receive CAN FD (Flexible Data) frames at higher speed.

# 2 CAN FD overview

This section provides an overview of CAN FD. It also describes FD message format and structure.

## 2.1 CAN FD

'FD' stands for flexible data. It means there is a change in bit rate at the end of the arbitration phase, for the data phase.

The CAN 2.0 specification limits a CAN frame to 8 data bytes at a maximum bit rate of 1 Mbps.

The CAN FD standard allows extended frames to be sent, up to 64 data bytes in a single frame at a higher bit rate for the data phase of a frame, up to 8 Mbps. The CAN FD standard introduces the ability to switch from one bit rate to another mid-frame. Extended Data Length (EDL), as shown in Figure 2, sets a data length of up to 8 or up to 64 data bytes. Bit Rate Switching (BRS) indicates whether two bit rates (the data phase is transmitted at a different bit rate to the arbitration phase) are enabled.

| (C1<br>(C2<br>(Z1C1 | 1.0        | )V/div<br>)V/div<br>)V | B     | W:1.0<br>W:1.0<br>38.1µ | OG |   | (   | t1<br>t2<br>Δt | 33    | 8.988 | Bµs |    |        |  |     |      |        |     | A' (<br>Nor | C1<br>Ie    | <b>5</b> 3. | .2V   | No          | rma         | Sto | 0µs/d<br>opped<br>i acqs |       | OOMS       | 5/s |     | .0ns/<br>:1001 |     |    |      |

|---------------------|------------|------------------------|-------|-------------------------|----|---|-----|----------------|-------|-------|-----|----|--------|--|-----|------|--------|-----|-------------|-------------|-------------|-------|-------------|-------------|-----|--------------------------|-------|------------|-----|-----|----------------|-----|----|------|

|                     | <u>r 1</u> |                        | <br>1 | 15 4                    | -  |   | P   | 1              | 1     |       | 1   | E  | 4      |  | 12  | 3    | 1      |     | 1           | 13 3        |             | -     | 12 - 2      |             | 1   | 123                      |       |            | 1   | 4   | 1              | -12 | 4  | 12.5 |

|                     |            |                        |       |                         |    |   |     |                |       |       |     |    |        |  |     |      | 127    |     |             |             |             |       |             |             |     |                          |       |            |     |     |                |     |    |      |

|                     |            |                        |       |                         |    |   |     |                |       |       |     |    |        |  |     |      | 12     |     |             |             |             |       |             |             |     |                          |       |            |     |     |                |     |    |      |

|                     |            | in m                   |       |                         |    |   |     |                |       |       |     |    |        |  | de, | i an | Actual |     |             | iteriter.   |             |       |             |             | -   |                          |       |            |     |     | 1              | V   | -  |      |

|                     |            |                        |       |                         |    |   |     |                |       |       |     |    |        |  |     |      | 37     |     |             |             |             | de ju |             |             |     |                          |       |            |     |     |                |     |    | ۲    |

|                     | <b>⊳</b>   |                        | <br>- |                         | 1  | - | 7   | -              | -     | i     | 1   | -  | 1      |  | -   | -    | -      |     |             |             |             | +     |             | ·           | 1   | -                        | <br>- |            | -   |     | 1              | 11  | f" | 11   |

|                     |            |                        |       |                         |    |   |     |                |       |       |     |    |        |  |     |      | 10     |     |             |             |             |       |             |             |     |                          |       |            |     |     |                |     |    |      |

| -                   |            |                        |       |                         |    |   |     |                |       |       |     |    |        |  |     |      | 87     |     |             |             |             |       |             |             |     |                          |       |            |     |     |                |     |    |      |

| - 3                 |            |                        |       |                         |    |   |     |                |       |       |     |    |        |  |     |      | 87     |     |             |             |             |       |             |             |     |                          |       |            |     |     |                |     |    |      |

| - 19                |            |                        |       |                         |    |   |     |                |       |       |     |    |        |  |     |      | 19     |     |             |             |             |       |             |             |     |                          |       | -<br>-<br> |     |     |                |     |    |      |

|                     | i i<br>1 1 | i.                     | 1     | 1 1                     |    | i | il. |                | 1     | Li    | 1   | 12 | î<br>T |  | 1   | i    | 1      |     |             |             |             | 1     | 1           | і_і.<br>— т |     | i<br>T                   | 1     | 1          | 1   | 1   |                | i   | 1  | 1    |

|                     | lind.      | - ļ.,                  | anta  |                         |    | - | 1   | -              | den s | ļ     | -   | -  | ġ-     |  | -   |      | H.     |     | -0          | <b>N</b> AM |             | UM    | <b>Varn</b> |             |     |                          |       |            |     | 0ÅI |                | 0÷  | -  |      |

|                     |            |                        |       |                         |    |   |     |                |       |       |     |    |        |  |     |      |        | - 4 | 10          |             |             |       |             |             |     |                          |       |            |     |     |                |     |    |      |

Figure 1 Bit rate change mid-message

## 2.2 FD message format and structure

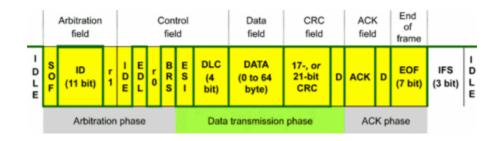

The data sent is packaged into a message as shown in Figure 2, consisting of:

- an arbitration phase

- a data transmission phase

- an ACK phase.

The arbitration phase is a message header consisting of an ID number and other bits to indicate the purpose of the message (supplying or requesting data), the speed and format configuration (CAN or CAN FD).

This is followed by the data transmission phase, consisting of the Data Length Code (DLC), to indicate how many data bytes the message contains. The data the user wishes to send the CRC and finally a dominant bit.

The ACK (acknowledgment) is transmitted by other nodes on the bus, if at least one has successfully received the message.

Figure 2 CAN FD frame

# **3** Configuring and using the MCAN module

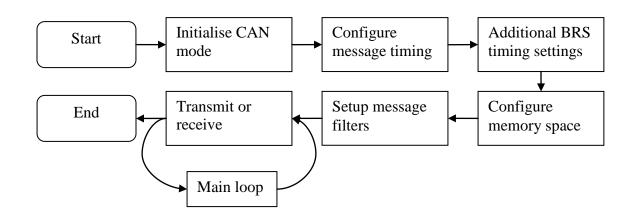

Figure 3 shows the steps required to initialise and configure an MPC5777M MCAN module, to create a low level MCAN driver. Each step within the flowchart is detailed in the following sections of this application note.

Figure 3 Steps to initialise and configure the MCAN module

## 4 Configuring the MCAN transmission scheme

## 4.1 Description

The backward compatible MCAN module on the MPC5777M can operate under the CAN 2.0 specification, and make use of the new CAN FD features. The module must be configured for CAN according to ISO11898-1, CAN FD or CAN FD with BRS. Timing parameters must be applied to the module, depending upon the scheme chosen. These timing constants define the time for a single bit and are used for the transmitter and receiver, so that they are configured identically.

The initialisation must also set the input and output pins to operate with the MCAN module(s).

All the MCAN modules share an auxiliary clock source which has a maximum frequency of 50 MHz on MPC5777M. Each module can be configured with its own operation scheme and timing parameters, which allows an MCU to operate on as many different buses as there are nodes at different bit rates.

## 4.2 Implementation

For the following examples, the auxiliary clock source will be configured as 40 MHz, taken directly from XOSC. This will allow the examples to run up to a maximum bit rate of 8 Mbps. The clock provided to the MCAN modules can be configured with the MPC5777M's Clock Generation Module (MC\_CGM) configuration registers (AC8).

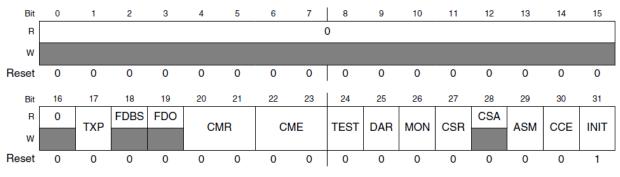

For transmitting and receiving a CAN FD message, the module must be configured for CAN FD with a single set of timing parameters provided. The scheme is selected by use of the CAN Control Register (CCCR) and the timing by the Bit Timing and Prescaler Register (BTP).

Note that the CCCR and BTP registers must be unlocked in order to change the configuration settings. The locking mechanism prevents changes being made while the module is operating. They can be unlocked by the CCE and INIT bits of the CCCR register.

Figure 4 shows that the INIT bit of the CCCR register operates in a different clock domain to the CPU and so care must be taken when attempting to change this bit. A suitable methodology is detailed in step 1 and step 2 of Table 1.

M\_CAN\_CCCR field descriptions

| 20–21<br>CMR | CAN Mode Request                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMA          | A change of the CAN operation mode is requested by writing to this bit field. After change to the requested operation mode the bit field is reset to '00' and the status flags FDBS and FDO are set accordingly. In case the requested CAN operation mode is not enabled, the value written to CMR is retained until it is overwritten by the next mode change request. In case CME = '01'/'10'/'11' a change to CAN operation according to ISO 11898-1 is always possible. Default is CAN operation according to ISO 11898-1.                                                      |

|              | 00 unchanged                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|              | 01 Request CAN FD operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|              | 10 Request CAN FD operation with bit rate switching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|              | 11 Request CAN operation according ISO11898-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 22–23<br>CME | CAN Mode Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|              | <ul> <li>NOTE: These are protected write (P) bits which means that write access by the bits is possible only when the bit 1 [CCE] and bit 0 [INIT] of CCCR are set to '1'.</li> <li>NOTE: When CME = '00', received frames are strictly interpreted according to ISO11898-1, which leads to the transmission of an error frame when receiving a CAN FD frame. In case CME = '01', transmission of long CAN FD frames and reception of long and fast CAN FD frames is enabled. With CME = '10'/'11', transmission and reception of long and fast CAN FD frames is enabled</li> </ul> |

|              | 00 CAN operation according to ISO11898-1 enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|              | 01 CAN FD operation enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|              | 10 CAN FD operation with bit rate switching enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|              | 11 CAN FD operation with bit rate switching enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 30           | Configuration Change Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CCE          | NOTE: Protected write (P) bit(s) which means that write access by the bit(s) is possible only when the bit 1 [CCE] CCCR[INIT] register fields are set to '1'.                                                                                                                                                                                                                                                                                                                                                                                                                       |

|              | 0 The CPU has no write access to the protected configuration registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|              | 1 The CPU has write access to the protected configuration registers (while CCCR.INIT = '1')                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 31<br>INIT   | Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|              | <b>NOTE:</b> Due to the synchronization mechanism between the two clock domains, there may be a delay until the value written to INIT can be read back. Therefore the programmer has to assure that the previous value written to INIT has been accepted by reading INIT before setting INIT to a new value.                                                                                                                                                                                                                                                                        |

|              | 0 Normal Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|              | 1 Initialization is started                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| L            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

#### Figure 4 MCAN\_CCCR register and bit definitions

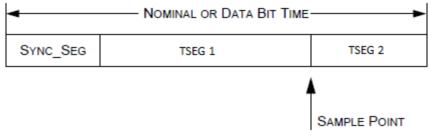

The bit time is defined by a multiple number of time quanta (tq), with 1 tq equal to the MCAN clock period. Each bit consists of a SYNC time, a Time Segment 1(TSEG1) and Time Segment 2(TSEG2). A 40 MHz MCAN clock will give a tq of 25 ns, with the programmed multipliers defining the length of these time segments. The SYNC value is always 1 and the remaining two segments can be user programmed. The receiver will sample and record the value of the transmitted bit between TSEG1 and TSEG2.

#### Address: 0h base + 1Ch offset = 1Ch

| Bit   | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19  | 20  | 21 | 22 | 23 | 24  | 25  | 26 | 27 | 28 | 29 | 30 | 31 |

|-------|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|-----|-----|----|----|----|-----|-----|----|----|----|----|----|----|

| R     |   |   | ( | ) |   |   |   |   |   |   | BE | 2P |    |    |    |    | 0  | )  |    |     | TSE | G1 |    |    |     | TSE | 62 |    |    | SJ | w  |    |

| w     |   |   |   |   |   |   |   |   |   |   |    | u  |    |    |    |    |    |    |    | 101 |     |    |    |    | 101 | -02 |    |    | 00 |    |    |    |

| Reset | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 1   | 0  | 1  | 0  | 0   | 0   | 1  | 1  | 0  | 0  | 1  | 1  |

#### M\_CAN\_BTP field descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0–5<br>Reserved   | This field is reserved.<br>This read-only field is reserved and always has the value 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6–15<br>BRP       | Baud Rate Prescaler<br>(0x000-0x3FF) The value by which the oscillator frequency is divided for generating the bit time quanta.<br>The bit time is built up from a multiple of this quanta. Valid values for the Baud Rate Prescaler are 0 to<br>1023. The actual interpretation by the hardware of this value is such that one more than the value prog<br>rammed here is used.<br>NOTE: Protected write (P) bit(s) which means that write access by the bit(s) is possible only when the bit<br>1 [CCE] CCCR[INIT] register fields are set to '1'. |

| 16–17<br>Reserved | This field is reserved.<br>This read-only field is reserved and always has the value 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 18–23<br>TSEG1    | (0x01-0x3F) Valid values are 1 to 63. The actual interpretation by the hardware of this value is such that<br>one more than the prog rammed value is used.<br>NOTE: Protected write (P) bit(s) which means that write access by the bit(s) is possible only when the bit<br>1 [CCE] CCCR[INIT] register fields are set to '1'.                                                                                                                                                                                                                       |

| 24–27<br>TSEG2    | (0x0-0xF) Valid values are 0 to 15. The actual interpretation by the hardware of this value is such that one more than the prog rammed value is used.                                                                                                                                                                                                                                                                                                                                                                                                |

|                   | NOTE: Protected write (P) bit(s) which means that write access by the bit(s) is possible only when the bit<br>1 [CCE] CCCR[INIT] register fields are set to '1'.                                                                                                                                                                                                                                                                                                                                                                                     |

| 28–31<br>SJW      | (0x0-0xF) Valid values are 0 to 15. The actual interpretation by the hardware of this value is such that one more than the value prog rammed here is used                                                                                                                                                                                                                                                                                                                                                                                            |

|                   | NOTE: Protected write (P) bit(s) which means that write access by the bit(s) is possible only when the bit<br>1 [CCE] CCCR[INIT] register fields are set to '1'.                                                                                                                                                                                                                                                                                                                                                                                     |

#### Figure 5 MCAN\_BTP register and bit definitions

Figure 6 Timing breakdown for a single bit

Timing can be optimised for data speed on the bus, or to maintain data integrity on a reactive bus. This can be achieved by varying the ratio between TSEG1 and TSEG2 thus the sample point for a bit.

Stage 5 in Table 1 shows how to configure the BTP timing parameters for a bit time of 2  $\mu$ s, and a sample point after 80% of the bit time, i.e. after 1.6  $\mu$ s. The calculation below demonstrates how this is achieved by setting TSEG1 to 31 tq, TSEG2 to 8 tq and dividing the clock speed by 2.

$$BTP: tq = \frac{2}{40 \text{ MHz}} = 50 \text{ ns, bit time} = (1 + 31 + 8) * 50 \text{ ns} = 2 \mu s \rightarrow 0.5 \text{ Mbit/s}$$

$$BTP \text{ sample point} = \frac{SYNC + TSEG1}{SYNC + TSEG1 + TSEG2} = \frac{1 + 31}{1 + 31 + 8} = 80\%$$

| Step | Operation                              | Description                                                       | Pseudo Code                                |

|------|----------------------------------------|-------------------------------------------------------------------|--------------------------------------------|

| 1    | Initialise MCAN_CCCR                   | Set INIT bit and check that it has been set                       | INIT = 1;<br>If INIT ≠ 1, wait until it is |

| 2    | Unlock protected registers             | Set CCCR.CCE bit                                                  | CCE = 1;                                   |

| 3    | Request CAN mode change                | Set CCCR.CMR to CAN FD                                            | CMR = 1;                                   |

| 4    | Change CAN mode                        | Set CCCR.CME to CAN FD                                            | CME = 1;                                   |

| 5    | Set BTP for 0.5 Mbps                   | Clk/2, T1 = 31, T2 = 8, SJW = 8                                   | M_CAN_1.BTP.R = 0x00011E77;                |

| 6    | Lock protected registers               | Clear CCCR.CCE bit                                                | CCE = 0;                                   |

| 7    | Return MCAN module to normal operation | Clear INIT bit and check it has been cleared                      | INIT = 0;<br>If INIT ≠ 0, wait until it is |

| 8    | Configure T <sub>x</sub> pin           | Enable output buffer with high drive strength and select pad mode | T <sub>x</sub> pin MSCR = 0x32000001;      |

| 9    | Configure R <sub>x</sub> pin           | Enable input buffer and select pad mode                           | R <sub>x</sub> pin MSCR = 0x00080002;      |

#### Table 1 Steps to configure the MCAN scheme

## 4.3 Code

The following code provides an initialisation function for MCAN 1. It unlocks the protected registers, then puts the modules into CAN FD mode and provides timing parameters. The protected registers are locked again and finally the module pins are configured for use by the MCAN 1 module.

```

void MCAN1 init() {

/* Init MCAN1 */

M CAN 1.CCCR.B.INIT = 0 \times 1;

//set to initialisation mode

while (M CAN 1.CCCR.B.INIT == 0);

M CAN 1.CCCR.B.CCE = 0x1;

// enable CCE bit to change configuration

//request CAN FD

M CAN 1.CCCR.B.CMR = 0x2;

M CAN 1.CCCR.B.CME = 0x2;

//enable CAN FD

//tq for 0.5Mbps SYNC=1, TSEG1=30+1, TSEG2=7+1, SJW=7+1

M CAN 1.BTP.R = 0 \times 00011E77;

M CAN 1.CCCR.B.CCE = 0x0; // disable CCE to prevent configuration changes

M CAN 1.CCCR.B.INIT = 0x0;//Return to normal operation

while (M CAN 1.CCCR.B.INIT == 0x1);

SIUL2.MSCR[10].R = 0x32000001;

//MCAN1T<sub>x</sub> Pin, PA[10]

SIUL2.MSCR[758].R = 0x00080002;

//MCAN1R<sub>x</sub> Pin, PA[11]

}

```

# 5 Assigning message memory space

## 5.1 Description

Memory must be assigned during initialisation to define where to store received messages and where to store messages prior to transmission.

The quantity of data bytes per message must be configured to determine how much memory space is required per message. This can be configured for messages that will not contain as many as 64 bytes maximum allowed by CAN FD, resulting in more efficient memory usage and allowing more messages to be stored in the allocated memory space.

## 5.2 Implementation

Each MCAN module can configure its transmit buffer and receive FIFO memory space. They are configured with a start address offset and the number of memory elements to store. The starting address is predefined as the start address shown in Figure 7, and it is the user's responsibility to ensure that the number of elements per memory space does not cause them to overlap.

| Start<br>address | End<br>address | Allocated<br>size | Used<br>size | PBRIDGE | PBRIDGE<br>Access<br>Control<br>Register | Description            |

|------------------|----------------|-------------------|--------------|---------|------------------------------------------|------------------------|

| 0xFFED4000       | 0xFFED7FFF     | 16 KB             | 20 KB        | Α       | OPACR74                                  | Shared CAN Message RAM |

Figure 7 Shared memory and address allocation for MCAN modules

Table 2 shows the configuration of all message memory space for an MCAN module. Steps 2-4 setup the receive FIFOs and transmit buffer, and the data length allowance for each of those memory spaces in steps 5 and 6.

| Step | Operation                           | Description                                                                                 | Pseudo Code                                        |

|------|-------------------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------|

| I    | Unlock protected registers          | Refer to section 4.2<br>'Implementation'                                                    |                                                    |

| 1    | Configure FIFO 0                    | Offset address = 0x400<br>Save 3 CAN messages<br>Overwrite old instead of<br>discarding new | Write M_CAN_1.RXF0C.R =<br>0x80030400;             |

| 2    | Configure FIFO 1                    | Offset address = 0x800<br>Save 5 CAN messages<br>Discard new messages when full             | Write M_CAN_1.RXF1C.R =<br>0x00050800;             |

| 4    | Configure T <sub>x</sub> Buffer     | Store 2 messages<br>Offset address = 0xD00                                                  | Write M_CAN_1.T <sub>x</sub> BC.R =<br>0x00020D00; |

| 5    | Set data limit for receive messages | 48 data bytes/message FIFO 1<br>32 data bytes/message FIFO 0                                | Write M_CAN_1.RXESC.R =<br>0x00000065;             |

#### Table 2 Steps to configure the MCAN memory space

| 6 | Set data limit for transmit messages | 64 data bytes/message $T_X$ buffer       | Write M_CAN_1.TXESC.R =<br>0x00000007; |

|---|--------------------------------------|------------------------------------------|----------------------------------------|

| F | Lock protected registers             | Refer to section 4.2<br>'Implementation' |                                        |

#### NOTE

The above registers are protected, and must be unlocked using the CCCR register, as demonstrated in section 4.2 'Implementation'.

# 6 Configuring CAN FD with bit rate switching

## 6.1 Description

To use Bit Rate Switching (BRS) the user is only required to configure an extra set of timing parameters and configure the module to use a different CAN scheme.

The original Bit Timing and Prescaler Register (BTP) timing parameters are used only for the arbitration phase of the message. The additional set is used for the data phase. The data phase bit timings are defined in exactly the same way as the arbitration message timing is configured using the Fast Bit Timing Prescaler register (FBTP).

Using the parameters demonstrated in Table 3, the calculation below shows how to achieve a bit time of 125 ns with a sample point after 80% of this bit time. Note that the clock divider is unused and default to  $\div 1$ .

*FBTP*:

$$tq = \frac{1}{40 \text{ MHz}} = 25 \text{ ns}$$

, bit time =  $(1 + 3 + 1) * 25 \text{ ns} = 125 \text{ ns} \rightarrow 8 \text{ Mbps}$

*FBTP* sample point =  $\frac{SYNC + TSEG1}{SYNC + TSEG1 + TSEG2} = \frac{1 + 3}{1 + 3 + 1} = 80\%$

## 6.2 Transceiver delay compensation (TDC)

The CAN transceiver always compares what is seen by the receiver and what it is trying to transmit in order to identify when a more dominant node has control of the bus. This can cause issues during the faster data phase, when, due to delays on the CAN bus, the transceiver sees a difference between what is transmitting and what is being received. This will cause the transmitter to believe it does not have control of the bus and it will abort the transmission.

To prevent this from occurring, delay compensation can be configured for the MCAN node, allowing a delay between the transmitter circuitry applying a bit to the bus and the receiver reading it back from the bus. This delay is specific to the CAN Physical Layer (PHY) and bus, so when the correct delay has been determined, it can be stored to always ensure correct operation.

If the correct delay for the bus is unknown, the message may not be transmitted because the transceiver believes it has been dominated, and it does not indicate an error, instead the Transmit Buffer Request Pending register (TXBRP) will never clear to zero.

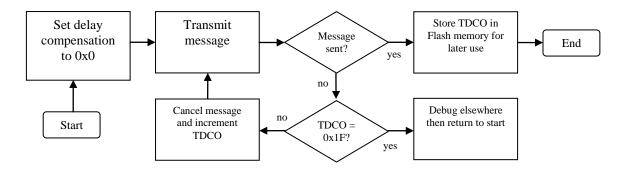

To find the correct delay for the bus, a trial and error method is the only way to realistically find the delay value. This process is only suitable for development and it would be unwise to use it in a real application; the result being part messages on the bus and time to tune the Transmit Delay Compensation Offset (TDCO) to allow the module to transmit and receive successfully. Instead the appropriate TDCO value should be found using this process during development, and that value programmed into the application device code. The process can be summarised as shown in Figure 8.

Figure 8 Finding the correct TDCO

The length of the delay can be found simply by increasing the number of time quanta from 0x0 to 0x1F until the messages can be sent and the correct delay has been found. If the TDCO value reaches 0x1F and no message has been sent successfully, it is more likely that the transmission fault lies elsewhere.

The delay value may not be a single value, rather a range of values that are suitable for successful transmission. It is a good practice to find the minimum and maximum delay values and then select a delay that is median of the range.

Table 3 shows the additional configuration steps for use of BRS, changing the mode of operation of the module and programming the fast bit timing parameters with a transceiver delay compensation value.

| Step | Operation                  | Description                                            | Pseudo Code                  |

|------|----------------------------|--------------------------------------------------------|------------------------------|

| I    | Unlock protected registers | Refer to section 4.2<br>'Implementation'               |                              |

| 1    | Request CAN mode change    | Set CCCR.CMR to CAN FD with BRS                        | CMR = 2;                     |

| 2    | Change CAN mode            | Set CCCR.CME to CAN FD with BRS                        | CME = 2;                     |

| 3    | Set FBTP for 0.5 Mbps      | Clk/1, T1 = 3, T2 = 1, SJW = 2<br>TDC = ON<br>TDCO = 5 | M_CAN_1.FBTP.R = 0x05800201; |

| F    | Lock protected registers   | Refer to section 4.2<br>'Implementation'               |                              |

Table 3 Program FBTP register for BRS and apply a TDCO value

# 7 Filtering messages by ID number

## 7.1 Introduction

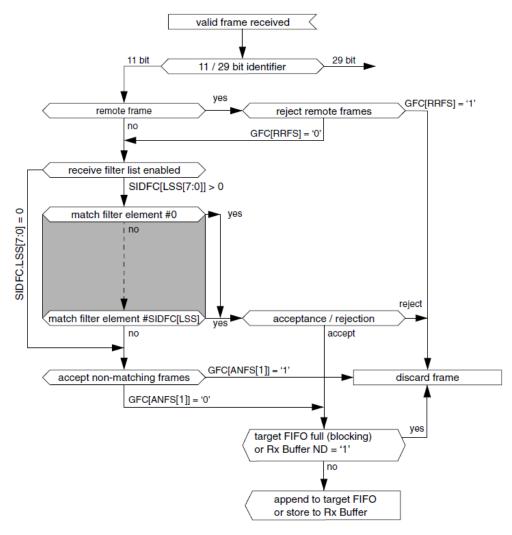

Received messages can be filtered by ID number into either of the receive FIFOs.

The destination of ID numbers that do not match with any filter is decided by the Global Filter Configuration register (GFC). This register will also determine the destination of remote frames which request data from a node without sending any data.

## 7.2 Implementation

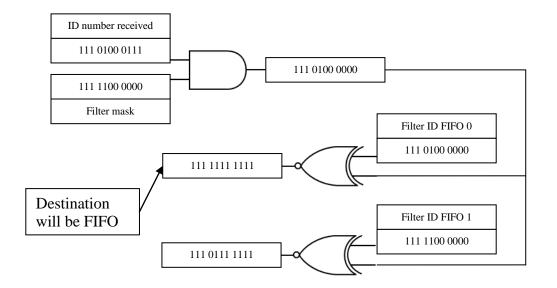

Up to 128 filter configurations can be implemented on each MCAN module in the device. To implement a classic filter for 11-bit ID numbers, a filter mask, ID comparison, and the destination FIFO for the message must be selected.

Figure 9 11-bit ID filter comparison path

Figure 9 demonstrates how messages are sorted. Focusing only on messages with 11-bit IDs and no remote frames, a received message is compared to each filter element in turn. The first element that matches with the message will decide the memory address where the message will be stored. No more comparisons will be made after the first positive result. If no positive result is obtained, the message can either be discarded or stored in a particular FIFO, depending on the MCAN\_GFC register.

Figure 10 shows the five most significant bits of the filter mask will be considered (bits 21-25). As the masks are identical, matching of the ID number (bits 5-15) will determine if the received message is placed into FIFO 0 (top filter) or FIFO 1 (bottom filter), selected with bits 2-4. Bits 0-1 set the configuration to classic filter.

| 0    | 1  | 2 |      | 4 | 5               |   |   |   |   |     |   |   |   |   | 1<br>5 | 1<br>6 |    |      |    | 2<br>0 | 2<br>1 |   |   |   | 2<br>5 |      |      |   |   |   | 3<br>1 |

|------|----|---|------|---|-----------------|---|---|---|---|-----|---|---|---|---|--------|--------|----|------|----|--------|--------|---|---|---|--------|------|------|---|---|---|--------|

| filt | er |   | FIFO | ) |                 |   |   |   |   | ID  |   |   |   |   |        |        | Re | serv | ed |        |        |   |   |   | Filte  | er M | lask |   |   |   |        |

|      | 8  | 3 |      |   | F               | F |   |   | 4 | 1   |   |   | 0 | ) |        |        | (  | )    |    |        | 7      | 7 |   |   | 0      | 0    |      |   | 0 |   |        |

| 1    | 0  | 0 | 0    | 1 | 1               | 1 | 1 | 0 | 1 | 0   | 0 | 0 | 0 | 0 | 0      | 0      | 0  | 0    | 0  | 0      | 1      | 1 | 1 | 1 | 1      | 0    | 0    | 0 | 0 | 0 | 0      |

| 0х   | (2 |   | 0x1  |   |                 |   |   |   | 0 | x74 | 0 |   |   |   |        |        |    |      |    |        |        |   |   |   | 0      | x7C  | :0   |   |   |   |        |

|      |    |   |      |   |                 |   |   |   |   |     |   |   |   |   |        |        |    |      |    |        |        |   |   |   | 1      |      |      |   |   |   |        |

| 0    | 1  | 2 |      | 4 | 5               |   |   |   |   |     |   |   |   |   | 1<br>5 | 1<br>6 |    |      |    | 2<br>0 | 2<br>1 |   |   |   | 2<br>5 |      |      |   |   |   | 3<br>1 |

| filt | er |   | FIFO | ) |                 |   |   |   |   | ID  |   |   |   |   |        |        | Re | serv | ed |        |        |   |   |   | Filte  | er M | lask |   |   |   |        |

|      | ç  | ) |      |   | 7               | 7 |   |   | C | 5   |   |   | ( | ) |        |        | (  | )    |    |        | 7      | 7 |   |   | (      | 0    |      |   | 0 |   |        |

| 1    | 0  | 0 | 1    | 0 | 0 1 1 1 1 1 0 0 |   |   |   |   |     |   |   | 0 | 0 | 0      | 0      | 0  | 0    | 0  | 0      | 1      | 1 | 1 | 1 | 1      | 0    | 0    | 0 | 0 | 0 | 0      |

| 0х   | (2 |   | 0x2  |   |                 |   |   |   | 0 | x7C | 0 |   |   |   |        |        |    |      |    |        |        |   |   |   | 0      | x7C  | :0   |   |   |   |        |

#### Figure 10 Example ID Filter configuration

Other filter settings are detailed in the section titled 'Standard message ID Filter element' of the MPC5777M reference manual.

Figure 11 shows how these two filters will select the destination of the received message. The masked ID number is compared to the filter ID. An exact match produces a positive result, selecting the message destination.

#### Figure 11 Application of a classic filter configuration to a received ID number

Location of the filter elements in RAM is programmed by the Standard ID Filter Configuration register (SIDFC). The base address (FLSSA) and number of elements (LSS) the module uses for comparisons must be provided.

| Add           | ress | s: Of | ı ba | se + | 84 | h of | fset | = 84 | 4h |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|---------------|------|-------|------|------|----|------|------|------|----|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| Bit           | 0    | 1     | 2    | 3    | 4  | 5    | 6    | 7    | 8  | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 |

| R 0 LSS FLSSA |      |       |      |      |    |      |      |      |    |   |    |    |    |    |    | C  | )  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| w             |      |       |      |      |    |      |      |      |    |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| Reset         | 0    | 0     | 0    | 0    | 0  | 0    | 0    | 0    | 0  | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

#### M\_CAN\_SIDFC field descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                        |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0–7<br>Reserved   | This field is reserved.<br>This read-only field is reserved and always has the value 0.                                                                                                                                                                                                                                                            |

| 8–15<br>LSS       | List Size Standard<br>0 No standard Message ID filter<br>1-128 Number of standard Message ID filter elements<br>>128 Values greater than 128 are interpreted as 128<br>NOTE: Protected write (P) bit(s) which means that write access by the bit(s) is possible only when the bit                                                                  |

| 16–29<br>FLSSA    | 1 [CCE] CCCR[INIT] register fields are set to '1'.  Filter List Standard Start Address Start address of standard Message ID filter list (32-bit word address, see Message RAM).  NOTE: Protected write (P) bit(s) which means that write access by the bit(s) is possible only when the bit     1 [CCE] CCCR[INIT] register fields are set to '1'. |

| 30–31<br>Reserved | This field is reserved.<br>This read-only field is reserved and always has the value 0.                                                                                                                                                                                                                                                            |

#### Figure 12 Programming the filter element memory locations

The FIFO start addresses are defined by the Receiver FIFO Configuration registers (RXFnC), see section 5 'Assigning message memory space'. For 29-bit ID lengths, the Extended ID Filter Configuration register (XIDFC) must be programmed in a similar way to the SIDFC register. Each 29-bit filter element configuration takes two words; for the filter and for the mask configuration, that is described in detail in 'Extended message ID filter element' of the MPC5777M reference manual.

Table 4 shows how to configure the module to use two filters, and then place those filters into memory. The code listing demonstrates placing some example filters into memory for two MCAN modules.

| Step | Operation                                    | Description                                                          | Pseudo code                            |  |  |

|------|----------------------------------------------|----------------------------------------------------------------------|----------------------------------------|--|--|

| I    | Unlock protected registers                   | Refer to section 4.2<br>'Implementation'                             |                                        |  |  |

| 1    | Configure MCAN2 filter location and quantity | Offset address = 0xF00<br>No. of filters = 2                         | Write M_CAN_2.SIDFC.R =<br>0x00020F00; |  |  |

| I    | Lock protected registers                     | Refer to section 4.2<br>'Implementation'                             |                                        |  |  |

| 2    | Program MCAN2 filter 1                       | Classic filter<br>Destination = FIFO 0<br>ID = 0x740<br>Mask = 0x7C0 | Write (0x0F00) = 0x8F0007C0;           |  |  |

| 3    | Program MCAN2 filter 2                       | Classic filter<br>Destination = FIFO 1<br>ID = 0x7C0<br>Mask = 0x7C0 | Write (0x0F04) = 0x978007C0;           |  |  |

#### Table 4 Program the filters and their location in memory

## 7.3 Code

The following function programs example filters for the receiver module, with the resulting filters detailed in Table 5.

```

#define FULL SRAM BASE ADDR MSG RAM 0xFFED4000

//MCAN shared SRAM base address

#define MCAN1 SIDFC FLSSA 0x0000

//MCAN 1 STANDARD MESSAGE ID FILTERS

#define MCAN2 SIDFC FLSSA 0x0F00

//MCAN 2 STANDARD MESSAGE ID FILTERS

void MCAN ID init() {

//MCAN1 ID values

* (vuint32 t*) (FULL SRAM BASE ADDR MSG RAM + MCAN1 SIDFC FLSSA) = 0x8F0007C0;

/*#1 Rx 11-bit Filter FIF00*/

*(vuint32 t*)(FULL SRAM BASE ADDR MSG RAM + MCAN1 SIDFC FLSSA + 0x04) = 0x978007C0;

/*#2 Rx 11-bit Filter FIF01*/

//MCAN2 ID values

* (vuint32 t*) (FULL SRAM BASE ADDR MSG RAM + MCAN2 SIDFC FLSSA) = 0x8F4007C0;

/*#3 Rx 11-bit Filter FIFO 0*/

* (vuint32 t*) (FULL SRAM BASE ADDR MSG RAM + MCAN2 SIDFC FLSSA + 0x04) = 0x97C007C0;

/*#4 Rx 11-bit Filter FIF01*/

```

}

| Filter element | Filter type | Destination  | ID comparison | Mask  |

|----------------|-------------|--------------|---------------|-------|

| MCAN1 #1       | Classic     | MCAN1 FIFO 0 | 0x700         | 0x7C0 |

| MCAN1 #2       | Classic     | MCAN1 FIFO 1 | 0x780         | 0x7C0 |

| MCAN2 #3       | Classic     | MCAN2 FIFO 0 | 0x740         | 0x7C0 |

| MCAN2 #4       | Classic     | MCAN2 FIFO 1 | 0x7C0         | 0x7C0 |

#### Table 5 Filters programmed by the code above

# 8 Transmitting, receiving and cancelling messages

## 8.1 Introduction

For a module to transmit a message, the message is formed within the defined memory space and the transmission is initiated. The message is sent by the node to a receiver, where it is formed in the receiver memory space.

## 8.2 Implementation

This example will configure MCAN modules 1 and 2. Section 4 'Configuring the MCAN transmission scheme' describes how to configure the memory space for the modules. As they share the same SRAM space, each module must be configured to use different address ranges. An example of this is shown in Table 6.

The message to be transmitted is formed in the transmit buffer following the format in Figure 13. The size and location of the MCAN transmit buffer is defined by a start address and number of buffer elements in the Transmit Buffer Configuration register (TXBC) and the maximum number of data bytes per message in the Transmit buffer Element Size Configuration register (TXESC) (see section 5 'Assigning message memory space').

T2 to T17 is the maximum allocated data space, DLC defines how many of these bytes will be taken, for example, if DLC is 0x7, but 64 bytes of data space has been allocated by the TXESC register, the module will take the first seven bytes, from DB0 to DB6.

| DL       | C code | No. of Bytes sent | DLC | Code | No. of Bytes sent |  |

|----------|--------|-------------------|-----|------|-------------------|--|

| 0x0 0000 |        | 0                 | 0x8 | 1000 | 8                 |  |

#### Table 6 DLC codes

| 0x1 | 0001 | 1 | 0x9 | 1001 | 12 |

|-----|------|---|-----|------|----|

| 0x2 | 0010 | 2 | 0xA | 1010 | 16 |

| 0x3 | 0011 | 3 | 0xB | 1011 | 20 |

| 0x4 | 0100 | 4 | 0xC | 1100 | 24 |

| 0x5 | 0101 | 5 | 0xD | 1101 | 32 |

| 0x6 | 0110 | 6 | OxE | 1110 | 48 |

| 0x7 | 0111 | 7 | 0xF | 1111 | 64 |

Only CAN FD messages are able to send messages with more than 8 data bytes, so to use DLC codes of 0x9 to 0xF the module must be configured for CAN FD in the CCCR register (see section 4 'Configuring the MCAN transmission scheme').

The receiver buffer follows the same format, but with additional bits to give further information about the message that has been received. The Accept Non-Matching Frames bit (ANMF) and Filter Index bits (FIDX), shown in Figure 14, combine to indicate which filter element the message ID matched with which could be used to give a particular message type. A time stamp can be attached to the message (refer to section 'Timestamp Counter Configuration Register' in MPC5777M Reference Manual).

| To         DB3(7:0)         DB4(7:0)         DB4(7:0)         DB4(7:0)         DB4(7:0)         DB4(7:0)         DB4(7:0)         DB107:0)         DB407:0)         DB407:0)         DB407:0)         DB407:0)         DB407:0)         DB407:0)         DB407:0)         DB407:0)         DB107:0)         DB407:0)         DB107:0)         DB407:0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                        | 0    |       |      |                  | 78     |          |                       | 15                                                                                                                           | 16                        | 23      | 24         | 31 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-------|------|------------------|--------|----------|-----------------------|------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------|------------|----|

| MM[7:0]         F         res           T2         DB3[7:0]         DB2[7:0]         DB1[7:0]         DB0[7:0]           T3         DB7[7:0]         DB6[7:0]         DB5[7:0]         DB4[7:0]           T3         DB7[7:0]         DBm-1[7:0]         DBm-1[7:0]         DBm-3[7:0]           T0         DBT70]         DBm-1[7:0]         DBm-3[7:0]         DBm-3[7:0]           T0         Bit XTD: Extended Identifier         0         11-bit standard Identifier         1           T0         Bit XTD: Extended Identifier         0         11-bit standard Identifier         1           T0         Bit XTD: Extended Identifier         0         Transmit data frame         1           T0         Bit 2 RTR: Remote Transmission Request         0         Transmit data frame         1           T0         Bit 3:31 ID[28:0]: Identifier         Standard or extended Identifier has to be written to ID[28:18].         1           T1         Bits 0:7 MM[7:0]: Message Marker         Written by CPU duing Tx Buffer configuration. Copied into Tx Event FIFO control         0 Don't store Tx events           T1         Bits 8:15         DLC[3:0]         Data Length Code         0-8 Transmit frame with 0-8 data bytes           9-15         CAN FD: transmit frame with 0-8 data bytes         9-15 Cranshit fr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | то                     | 8    | Т     | Т    | ID[28:0]         |        |          |                       |                                                                                                                              |                           |         |            |    |

| T3         DB7[7:0]         DB8[7:0]         DB5[7:0]         DB4[7:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | MM[7:0] F res DLC[3:0] |      |       |      |                  |        |          | DLC[3:0]              | res                                                                                                                          |                           |         |            |    |

| Tn       DBm(7:0]       DBm-1(7:0]       DBm-2(7:0]       DBm-3(7:0]         T0 Bit 1 XTD: Extended Identifier       0 11-bit standard identifier       1 29-bit extended identifier         1 29-bit extended identifier       0 Transmit data frame       1 Transmit remote frame         NOTE:       When RTR = 1, the M_CAN transmits a remote frame according to ISO 11998-1, even if CCCR.CME enables the transmission in CAN FD format.         T0 Bits 3:31 ID[28:0]: Identifier       Standard or extended identifier depending on bit XTD. A standard identifier thas to be written to ID[28:18].         T1 Bits 0:7 MM[7:0]: Message Marker       Written by CPU during Tx Buffer configuration. Copied into Tx Event FIFO element for identification of Tx message status.         T1 Bits 0:7 MM[7:0]: Message Marker       Event FIFO control         0 Don't store Tx events       1 Store Tx events         11 Bits 12:15 DLC[3:0]       Data Length Code         0-8 Transmit frame with 0-8 data bytes       9-15 CAN FD: transmit frame bas 2/16/20/24/32/48/64 data bytes         9-15 CAN FD: transmit frame bas 2/16/20/24/32/48/64 data bytes       9-15 CAN FD: transmit frame bas 2/16/20/24/32/48/64 data bytes         12 Bits 0:7       DB3(7:0): Data Byte 1       DB2(7:0): Data Byte 1         12 Bits 0:15       DB6(7:0): Data Byte 7         13 Bits 16:23       DB6(7:0): Data Byte 6 <td>T2</td> <td>D</td> <td>B3[7:</td> <td>:0]</td> <td></td> <td>DB</td> <td>2[7:0]</td> <td></td> <td></td> <td>DB1[7:0]</td> <td></td> <td>DB0[7:0]</td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | T2                     | D    | B3[7: | :0]  |                  | DB     | 2[7:0]   |                       |                                                                                                                              | DB1[7:0]                  |         | DB0[7:0]   |    |

| Tn         DBm(7:0]         DBm-1(7:0]         DBm-2(7:0]         DBm-3(7:0]           T0 Bit 1 XTD: Extended Identifier         0 11-bit standard identifier         1 29-bit extended identifier           T0 Bit 2 RTR: Remote Transmission Request         0 Transmit data frame         1 Transmit remote frame           T0 Bits 3:31 ID[28:0]: Identifier         0 Transmit of extended identifier depending on bit XTD. A standard or extended identifier depending on bit XTD. A standard or extended identifier depending on bit XTD. A standard identifier has to be written to ID[28:18].           T1 Bits 0:7 MM[7:0]: Message Marker         Written by CPU during Tx Buffer configuration. Copied into Tx Event FIFO element for identification of Tx message status.           T1 Bits 0:7 MM[7:0]: Message Marker         Event FIFO control         0 Don't store Tx events           T1 Bits 12:15 DLC[3:0]         Data Longth Code         0.4 Transmit frame with 0.4 data bytes           9-15 CAN FD: transmit frame with 8 data bytes         9-15 CAN FD: transmit frame has 2/16/20/24/32/48/64 data bytes           9-15 Its 0:7         DB3(7:0): Data Byte 3         DB3(7:0): Data Byte 1           T2 Bits 0:7         DB3(7:0): Data Byte 1         DB3(7:0): Data Byte 7           T3 Bits 6:15         DB6(7:0): Data Byte 6         T3 Bits 0:7           T3 Bits 0:17         DB3(7:0): Data Byte 6         T3 Bits 0:7           T3 Bits 0:15         DB6(7:0): Data Byte 4         T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | T3                     | D    | B7[7: | :0]  |                  | DB     | 6[7:0]   |                       |                                                                                                                              | DB5[7:0]                  |         | DB4[7:0]   |    |

| TO Bit 1 XTD: Extended Identifier       0 11-bit standard identifier         1 29-bit extended identifier       1 29-bit extended identifier         TO Bit 2 RTR: Remote Transmission Request       0 Transmit data frame         1 Transmit remote frame       NOTE: When RTR = 1, the M_CAN transmits a remote frame according to 15011998-1, even if CCCR.CME enables the transmission in CAN FD format.         TO Bits 3:31 ID[28:0]: Identifier       Standard or extended identifier depending on bit XTD. A standard or extended identifier has to be written to ID[28:18].         T1 Bits 0:7 MM[7:0]: Message Marker       Written by CPU during Tx Buffer configuration. Copied into Tx Event FIFO element for identification of Tx message status.         T1 Bits 0:7 MM[7:0]: Message Marker       Event FIFO clontol         0 Don't store Tx events       1 Store Tx events         1 Store Tx events       1 Store Tx events         1 Store Tx events       9-15 CAN FD: transmit frame has 2/16/20/24/32/48/64 data bytes         9-15 CAN FD: transmit frame has 2/16/20/24/32/48/64 data bytes       9-15 Transmit frame with 0-8 data bytes         12 Bits 0:7       DB3[7:0]: Data Byte 3         T2 Bits 2:15       DE2[7:0]: Data Byte 0         T3 Bits 0:7       DB7[7:0]: Data Byte 0         T3 Bits 0:7       DB7[7:0]: Data Byte 0         T3 Bits 0:7       DB7[7:0]: Data Byte 7         T3 Bits 0:7       DB7[7:0]: Data Byte 6 <td< td=""><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                        |      |       |      |                  |        |          |                       |                                                                                                                              |                           |         |            |    |

| 1 29-bit extended identifier         1 29-bit extended identifier         1 Transmit data frame         1 Transmit data frame         1 Transmit remote frame         NOTE: When RTR = 1, the M_CAN transmits a remote<br>frame according to ISO11898-1, even if CCCR.CME<br>enables the transmission in CAN FD format.         T0 Bits 3:31 ID[28:0]: Identifier       Standard or extended identifier depending on bit XTD. A<br>standard identifier has to be written to ID[28:18].         T1 Bits 0:7 MM[7:0]: Message Marker       Written by CPU during TX Buffer configuration. Copied into TX<br>Event FIFO element for identification of Tx message status.         T1 Bits 0:7 MM[7:0]: Message Marker       Event FIFO control<br>0 Don't store Tx events         1 Store Tx events       1 Store Tx events         1 Store Tx events       1 Store Tx events         1 Bits 12:15 DLC[3:0]       Data Length Code         0-8 Transmit frame with 0-8 data bytes       9-15 Transmit frame with 0-8 data bytes         9-15 Transmit frame with 8 data bytes       9-15 Transmit frame with 8 data bytes         9-15 Transmit frame with 9-8 data bytes       12 Bits 8:15         12 Bits 8:15       DB3[7:0]: Data Byte 1         12 Bits 0:7       DB3[7:0]: Data Byte 1         12 Bits 0:7       DB7[7:0]: Data Byte 6         13 Bits 0:7       DB4[7:0]: Data Byte 6         13 Bits 0:7       DB4[7:0]: Data Byte 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Tn                     | D    | Bm[7  | :0]  |                  | DB     | m-1[7:0] |                       |                                                                                                                              | DBm-2[7:0]                |         | DBm-3[7:0] |    |

| TO Bit 2 RTR: Remote Transmission Request       0 Transmit data frame         1 Transmit remote frame       1 Transmit remote frame         NOTE:       When RTR = 1, the M_CAN transmits a remote frame according to ISO1 1898-1, even if CCCR.CME enables the transmission in CAN PD format.         T0 Bits 3:31 ID[28:0]: Identifier       Standard or extended identifier depending on bit XTD. A standard identifier has to be written to ID[28:18].         T1 Bits 0:7 MM[7:0]: Message Marker       Written by CPU during Tx Buffer configuration. Copied into Tx Event FIFO Control         0 Don't store Tx events       1 Store Tx events         11 Bits 12:15 DLC[3:0]       Data Length Code         0-8 Transmit frame with 0-8 data bytes       9-15 CAN FD: transmit frame with 0-8 data bytes         9-15 CAN FD: transmit frame with 8 data bytes       9-15 CAN FD: transmit frame with 8 data bytes         9-15 CAN FD: transmit frame with 8 data bytes       9-15 CAN FD: transmit frame has 2/16/20/24/32/48/64 data bytes         9-15 EX       DB2[7:0]: Data Byte 3         T2 Bits 0:7       DB3[7:0]: Data Byte 2         T2 Bits 0:7       DB2[7:0]: Data Byte 3         T2 Bits 16:23       DB1[7:0]: Data Byte 0         T3 Bits 0:7       DB7[7:0]: Data Byte 6         T3 Bits 0:7       DB7[7:0]: Data Byte 6         T3 Bits 0:7       DB7[7:0]: Data Byte 6         T3 Bits 0:27       DB7[7:0]: Data Byte 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | T0 Bit                 | 1 X  | (TD:  | Ext  | ended Identifier |        |          |                       | 01                                                                                                                           | 1-bit standard identifier | r       |            |    |