# Powering the LS102xA with the MC34VR500 Power Management Interface Chip

# **1** Introduction

The MC34VR500 power management solution for network processor systems is a high-efficiency, quad buck regulator with up to 4.5 A output and five user-programmable LDOs. With four buck regulators and five LDO output channels, the MC34VR500 powers more than the network processor, significantly reducing design complexity and the overall bill of materials (BOM). The highly integrated MC34VR500 output voltage, frequency, and turn-on sequence are user programmable using  $I^2C$ .

The MC34VR500 is ideally suited to power system solutions based on QorIQ T1 and LS1 networking communications processors with unique programmable multiple buck regulators and LDOs. All regulators are internally compensated. Startup, slew rate control, and DVS are internally controlled, which means minimal external components are required.

This application note explains how to incorporate the MC34VR500 into an LS1 design. It uses the LS1021A-IOT as a design example.

#### Contents

| 1 | Introd | luction                                 | 1 |

|---|--------|-----------------------------------------|---|

| 2 |        | regulators and LDOs in the<br>IVR500    | 2 |

|   | 2.1    | Configuring buck regulators for LS102xA | 2 |

|   | 2.2    | Configuring LDO1-LDO5<br>regulators     | 4 |

| 3 | Power  | r sequence                              | 6 |

| 4 | Digita | ll control                              | 6 |

| 5 | Schen  | natic reference                         | 7 |

| 6 | Refere | ences                                   |   |

| 7 | Revis  | ion history                             | 8 |

# 2 Buck regulators and LDOs in the MC34VR500

This section describes how the MC34VR500 buck regulators and LDOs can be used in a LS102xA processor design.

The MC34VR500 has been designed to match the power rail requirements of the LS1021A processor. The single Power Management Interface Chip (PMIC) solution supplies all the LS1021A rails except for 3.3 V. As the MC34VR500 is supplied from a 3.3 V input supply, it can be used for the LS1 I/O, if necessary.

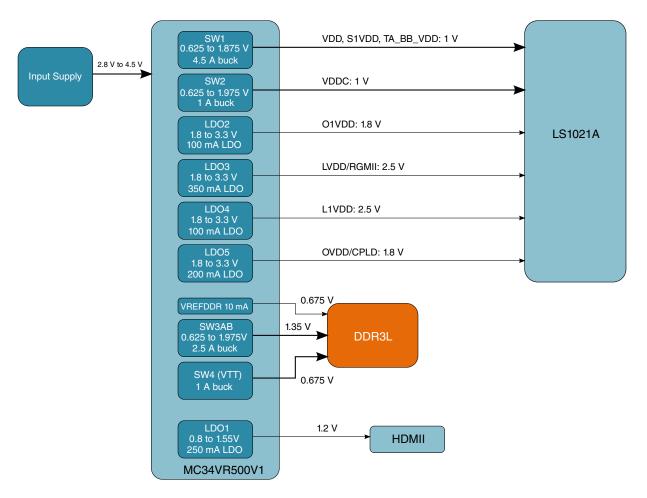

The LS1021A-IOT is a reference design that uses the MC34VR500V1ES. This figure shows how the MC34VR500 supplies the LS1021A rails and DDR3L memory, as well as peripheral devices in that design.

Figure 1. MC34VR500 powering the LS1021A-IOT gateway

# 2.1 Configuring buck regulators for LS102xA

The four buck regulators (SW1-4) on the MC34VR500 can produce high current outputs suitable for the LS102xA cores and DDR3 and DDR4 supplies:

- Use SW1 for the switchable core voltage and SW2 for the always on  $V_{DDC}$  supply.

- Use SW3 to generate the  $GV_{DD}$  for the LS1 and DDR devices.

- Use SW4 in its  $V_{TT}$  mode for DDR memory termination. In the  $V_{TT}$  mode:

- Its reference voltage internally tracks the output voltage of SW3, scaled by 0.5.

- Only the PWM switching mode is allowed to have sinking current capability.

There are three switching modes available for the buck's regulators:

- 1. Pulse Width Modulation (PWM): This mode allows continuous pulses generated by the internal MOSFETs, irrespective of the load current. This is the preferred mode of switching at load currents greater than 100 mA.

- 2. Pulse Frequency Modulation (PFM): In this mode, the switching frequency is proportional to the load current. Turn off the internal bottom MOSFET if the inductor current goes negative. This is the preferred mode at load currents less than 100 mA.

- 3. Auto Pulse Skip Mode (APS): This is the default mode in the MC34VR500. This offers a good compromise between PFM and PWM.

The switching frequency selections are: 1 MHz, 2 MHz, or 4 MHz (useful for certain applications with strict EMC requirement). By default, 2 MHz is used.

If we take a more detailed look at the LS1021A power requirements, we see that the MC34VR500 adequately meets the specification of the LS1021A core and DDR power requirements. We assume worst-case values that are taken from the data sheet.

The following tables summarize the voltage and current capabilities of the buck regulators with respect to the LS1021A requirements.

#### NOTE

The regulators max current is the normal operating maximum. Each regulator can handle instantaneous currents in excess of this. See the MC34VR500 data sheet for more information.

| LS1 rail               |               |             | Regulator      |               |             |

|------------------------|---------------|-------------|----------------|---------------|-------------|

| Rail name              | Voltage       | Max current | Regulator name | Voltage       | Max current |

| V <sub>DD</sub>        | 1.0 V ± 30 mV | 3.06 A      | SW1ABC         | 1.0 V ± 25 mV | 4.5 A       |

| TA_BB_V <sub>DD</sub>  |               | 0.02 A      |                |               |             |

| S1V <sub>DD</sub>      |               | 0.32 A      |                |               |             |

| USB1_SDV <sub>DD</sub> |               | 0.011 A     |                |               |             |

| USB1_SXV <sub>DD</sub> |               | 0.026 A     |                |               |             |

| USB1_SPV <sub>DD</sub> |               | 0.044 A     | _              |               |             |

|                        | Total         | 3.891 A     |                |               |             |

Table 1. SW1 (supplies V<sub>DD</sub>, TA\_BB\_V<sub>DD</sub>, S1V<sub>DD</sub>, and USB\_SxV<sub>DD</sub>)

| Table 2. | SW2 | (supplies | V <sub>DDC</sub> only) |  |

|----------|-----|-----------|------------------------|--|

|----------|-----|-----------|------------------------|--|

| LS1 rail         |               |             | Regulator      |               |             |

|------------------|---------------|-------------|----------------|---------------|-------------|

| Rail name        | Voltage       | Max current | Regulator name | Voltage       | Max current |

| V <sub>DDC</sub> | 1.0 V ± 30 mV | 0.41 A      | SW2            | 1.0 V ± 30 mV | 2.0 A       |

|                  | Total         | 0.41 A      |                |               |             |

### Table 3. SW3 (supplies GV<sub>DD</sub> to the LS1 and DDR memories, SerDes PLLs, and SerDes)

| LS1 rail                    |                |             | Regulator      |                |             |

|-----------------------------|----------------|-------------|----------------|----------------|-------------|

| Rail name                   | Voltage        | Max current | Regulator name | Voltage        | Max current |

| GV <sub>DD</sub> @ 1600 MHz | 1.35 V ± 67 mV | 0.883 A     | SW3AB          | 1.35 V ± 67 mV | 2.5 A       |

| GV <sub>DD</sub> DDR3L x3   |                | 0.973 A     |                |                |             |

| AV <sub>DD</sub> _SD1_PLL1  |                | 0.185 A     |                |                |             |

| AV <sub>DD</sub> _SD1_PLL2  |                |             |                |                |             |

| X1V <sub>DD</sub>           |                | 0.258 A     |                |                |             |

|                             | Total          | 2.3 A       |                |                |             |

### Table 4. SW4 (supplies V<sub>TT</sub>)

| LS1 rail        |         |             | Regulator      |                 |             |

|-----------------|---------|-------------|----------------|-----------------|-------------|

| Rail name       | Voltage | Max current | Regulator name | Voltage         | Max current |

| V <sub>TT</sub> | 0.675 V | ~500 mA     | SW4            | 0.675 V ± 40 mV | 1.0 A       |

# 2.2 Configuring LDO1-LDO5 regulators

The five general-purpose LDO regulators in the MC34VR500 are suitable for the I/O voltages required by the LS102xA processors. All LDOs have a short circuit and over-current protection.

The following tables provide the voltage and current ratings of each regulator, as well as example peripherals on the LS1021A-IOT, such as PHYs, that would use the voltage rail.

### Table 5. LDO1 (powers external HDMI peripheral)

| Rail       |                |             | Regulator      |                   |                       |

|------------|----------------|-------------|----------------|-------------------|-----------------------|

| 1.2 V rail | Voltage        | Max current | Regulator name | Regulator voltage | Regulator max current |

| HDMI       | 1.2 V ± 120 mV | 65 mA       | LDO1           | 1.2 V ± 36 mV     | 250 mA                |

### Table 6. LDO2

| Rail                    |               |             | Regulator      |                   |                          |

|-------------------------|---------------|-------------|----------------|-------------------|--------------------------|

| Always On 1.8 V<br>rail | Voltage       | Max current | Regulator name | Regulator voltage | Regulator max<br>current |

| O1V <sub>DD</sub>       | 1.8 V ± 90 mV | 12 mA       | LDO2           | 1.8 V ± 54 mV     | 100 mA                   |

#### Buck regulators and LDOs in the MC34VR500

| <b>Table</b> | 7. L | _DO3 |

|--------------|------|------|

|--------------|------|------|

| Rail                                      |                |             | Regulator      |                   |                          |

|-------------------------------------------|----------------|-------------|----------------|-------------------|--------------------------|

| 2.5 V rails                               | Voltage        | Max current | Regulator name | Regulator voltage | Regulator max<br>current |

| LV <sub>DD</sub> (assume 2x<br>RGMII I/F) | 2.5 V ± 125 mV | 137 mA      | LDO3           | 2.5 V ± 75 mV     | 350 mA                   |

| LV <sub>DD</sub> (assume 2x<br>RGMII I/F) |                | 30 mA       |                |                   |                          |

| LV <sub>DD</sub> (assume 2x<br>RGMII I/F) |                | 3 mA        |                |                   |                          |

|                                           | Total          | 170 mA      |                |                   |                          |

### Table 8. LDO4

| Rail                                       |                |             | Regulator      |                   |                       |

|--------------------------------------------|----------------|-------------|----------------|-------------------|-----------------------|

| Always On 2.5 V<br>rail                    | Voltage        | Max current | Regulator name | Regulator voltage | Regulator max current |

| L1V <sub>DD</sub> (assume 1x<br>RGMII I/F) | 2.5 V ± 125 mV | 69 mA       | LDO4           | 2.5 V ± 75 mV     | 100 mA                |

### Table 9. LDO5<sup>1</sup>

| Rail                         |               |             | Regulator      |                   |                          |  |

|------------------------------|---------------|-------------|----------------|-------------------|--------------------------|--|

| 1.8 V rails                  | Voltage       | Max current | Regulator name | Regulator voltage | Regulator max<br>current |  |

| OV <sub>DD</sub>             | 1.8 V ± 90 mV | 12 mA       | LDO5           | 1.8 V ± 54 mV     | 200 mA                   |  |

| AV <sub>DD</sub> _CGA1       |               | 69 mA       |                |                   |                          |  |

| AV <sub>DD</sub> _PLAT 1.8 V |               |             |                |                   |                          |  |

| AV <sub>DD</sub> _D1 1.8 V   |               | 69 mA       |                |                   |                          |  |

|                              | Total         | 170 mA      |                |                   |                          |  |

| Note:                        |               |             |                |                   |                          |  |

1. These regulators are straight forward to work with and require a single 4.7 uF output capacitor.

### Table 10. REFOUT (VREF DDR)<sup>1</sup>

| Rail                                                                                                                      |                   |             | Regulator      |                   |                       |

|---------------------------------------------------------------------------------------------------------------------------|-------------------|-------------|----------------|-------------------|-----------------------|

| VREF rail                                                                                                                 | Voltage           | Max current | Regulator name | Regulator voltage | Regulator max current |

| VREF                                                                                                                      | 0.675 V ± 13.5 mV | 500 uA      | REFOUT         | 0.675 V ± 6.75 mV | 10 mA                 |

| Note:                                                                                                                     | •                 |             |                |                   |                       |

| 1 REFOLIT is an internal PMOS half supply voltage follower canable of supplying up to 10 mA. The output voltage is at one |                   |             |                |                   |                       |

1. REFOUT is an internal PMOS half supply voltage follower capable of supplying up to 10 mA. The output voltage is at one half the input voltage. It is typically used as the reference voltage for DDR memories. A filtered resistor divider is used to create a low frequency pole. This divider then uses a voltage follower to drive the load.

# 3 Power sequence

The LS1021A requires that its power rails be applied in a specific sequence in order to ensure proper device operation. For details, refer to the Power sequencing section of LS1021A datasheet.

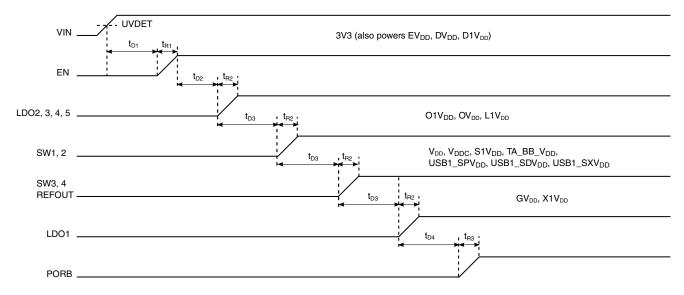

This figure shows the MC34VR500 pre-programmed power sequence. It has been implemented to match the previously discussed LS1 requirements.

| Parameter                                                                           | Description                          | Typical                                   | Unit |

|-------------------------------------------------------------------------------------|--------------------------------------|-------------------------------------------|------|

| t <sub>D1</sub>                                                                     | Turn-on delay                        | Depends on the external signal driving EN | ms   |

| t <sub>R1</sub>                                                                     | Rise time of EN                      | Depends on the external signal driving EN | ms   |

| t <sub>D2</sub>                                                                     | Turn-on delay of first regulator     | 2.5                                       | ms   |

| t <sub>R2</sub>                                                                     | Rise time of regulators <sup>1</sup> | 0.2                                       | ms   |

| t <sub>D3</sub>                                                                     | Delay between regulators             | 1.0                                       | ms   |

| t <sub>D4</sub>                                                                     | Turn-on delay of PORB                | 2.0                                       | ms   |

| t <sub>R3</sub>                                                                     | Rise time of PORB                    | 0.2                                       | ms   |

| Note:                                                                               |                                      |                                           |      |

| 1. Rise time is a function of slew rate of regulators and nominal voltage selected. |                                      |                                           |      |

# 4 Digital control

The MC34VR500 has an EN control pin to allow the system to control the startup of the device, for example, if it is part of a greater power tree. Typically, the device powers up with the One Time Programming (OTP) values stored in the device. You can also program and configure the MC34VR500 via the I<sup>2</sup>C bus.

Additional communication is provided by direct logic interfacing, including interrupt and reset. Startup voltage and sequence are internally programmed. After power up, you can change the regulator voltages via the I<sup>2</sup>C bus.

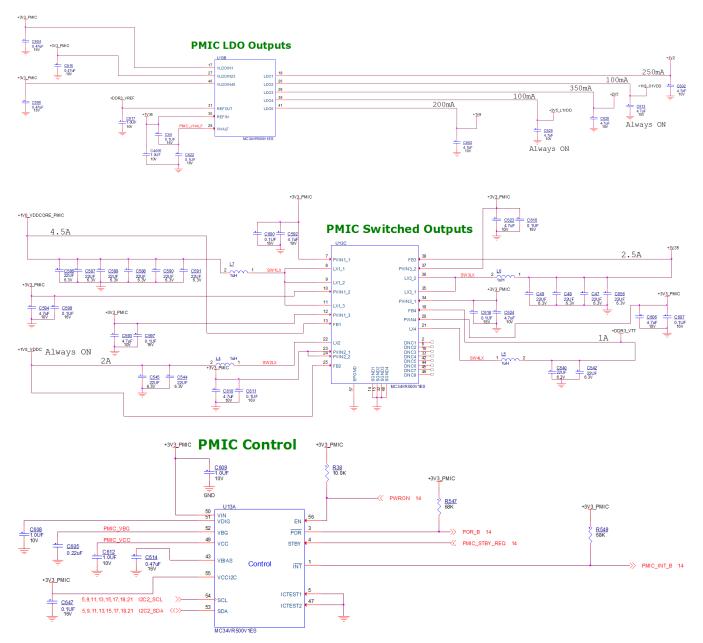

### 5 Schematic reference

The MC34VR500V1ES has been used successfully in the LS1021A-IOT design. The schematics are available for reference from http://www.nxp.com.

The following figures show the PMIC power schematics. See the MC34VR500 data sheet for recommended external component values for the PMIC.

# **6** References

This table provides URLs where you can obtain information on related NXP products and application solutions.

| Document number and description  |                                        | URL                                                                                                                                                                                                        |  |

|----------------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| LS1021A                          | Data sheet                             | https://www.nxp.com/webapp/Download?<br>colCode=LS1021A&location=null&fsrch=1&sr=1&pageNum=1<br>amp;&Parent_nodeId=&Parent_pageType=&Parent_nodeId=<br>&Parent_pageType=                                   |  |

| MC34VR500                        | Data sheet                             | http://cache.nxp.com/docs/en/data-sheet/MC34VR500.pdf?<br>pspll=1                                                                                                                                          |  |

| AN5064                           | Schematic Guidelines for the MC34VR500 | http://cache.nxp.com/docs/en/application-note/AN5064.pdf?<br>fsrch=1&sr=1&pageNum=1                                                                                                                        |  |

| AN5076                           | MC34VR500 Layout<br>Guidelines         | http://cache.nxp.com/docs/en/application-note/AN5076.pdf?<br>fsrch=1&sr=2&pageNum=1                                                                                                                        |  |

| AN4878                           | LS1021A Design Checklist               | https://www.nxp.com/webapp/Download?<br>colCode=AN4878&location=null&fsrch=1&sr=1&pageNum=1<br>&Parent_nodeId=&Parent_pageType=&Parent_nodeId=&Par<br>ent_pageType=&Parent_nodeId=&Parent_pageType=        |  |

| NXP sup                          | port pages                             | URL                                                                                                                                                                                                        |  |

| MC34VR500 Product Summary page   |                                        | http://www.nxp.com/products/automotive-products/energy-<br>power-management/pmics/pmic-for-networking-processors/<br>multi-output-dc-dc-regulator:MC34VR500                                                |  |

| LS1021A Product Summary page     |                                        | http://www.nxp.com/products/microcontrollers-and-<br>processors/arm-processors/qoriq-layerscape-arm-processor<br>qoriq-layerscape-1021a-dual-core-communications-<br>processor-with-lcd-controller:LS1021A |  |

| LS1021A-IOT Product Summary page |                                        | http://www.nxp.com/products/reference-designs/qoriq-<br>ls1021a-iot-gateway-reference-design:LS1021A-IoT?<br>lang_cd=en                                                                                    |  |

Table 12. References

# 7 Revision history

This table provides a revision history for this application note.

| Table 13. | Document | revision | history |

|-----------|----------|----------|---------|

|-----------|----------|----------|---------|

| Revision | Date    | Description            |

|----------|---------|------------------------|

| 0        | 07/2017 | Initial public release |

#### How to Reach Us:

Home Page: nxp.com

Web Support: nxp.com/support Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/SalesTermsandConditions.

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, Freescale, the Freescale logo, Layerscape, QUICC Engine, CoreNet, and QorIQ are trademarks of NXP B.V. All other product or service names are the property of their respective owners. ARM, ARM Powered, Cortex, and TrustZone are registered trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved.

© 2017 NXP B.V.

Document Number AN5085 Revision 0, 07/2017