**Application Note**

# Introduction to the Zipwire Interface

Inter-Processor Communication with SIPI/LFAST on the MPC57xx and S32Vxxx families

by: Randy Dees, Hugo Osornio, Steven Becerra, and Ray Marshall

### **1** Introduction

The <u>MPC57xx family</u> is the first family of devices that include a new bus for communicating between two devices over a high speed (320 Mb/s) serial interface called Zipwire. It is implemented using a Serial Inter-Processor Interface (SIPI) over an LVDS<sup>1</sup> Fast Asynchronous Serial Transmission Interface (LFAST). The SIPI module controls the higher level protocol of the interface, and the LFAST controls the physical interface.

#### NOTE

Some devices support two separate interfaces that are similarly based on the LFAST and SIPI modules. The first. discussed in this application note, is the Zipwire interface that consists of the SIPI and LFAST modules and is used for interprocessor communication. Some devices implement a second separate interface that can be used as a high-speed debug interface. This debug Zipwire interface consists of the LFAST, a reduced SIPI module that has a very limited functionality, and a JTAG Master interface module (JTAGM) that allows access of the JTAG debug interface through the LFAST interface.

1. LVDS is Low Voltage Differential Signalling

© 2015 Freescale Semiconductor, Inc.

#### Contents

| 1 | Introduction 1      |                                   |    |  |  |  |

|---|---------------------|-----------------------------------|----|--|--|--|

| 2 | Zipw                | rire Interface overview           | 2  |  |  |  |

|   | 2.1                 | Zipwire SIPI LFAST software model | 4  |  |  |  |

|   | 2.2                 | Typical Zipwire example overview  | 5  |  |  |  |

| 3 | Zipw                | Zipwire examples                  |    |  |  |  |

|   | 3.1                 | Function file locations           | 6  |  |  |  |

|   | 3.2                 | Zipwire demo overview             | 7  |  |  |  |

|   | 3.3                 | LFAST clock settings              | 12 |  |  |  |

|   | 3.4                 | Zipwire pins                      | 13 |  |  |  |

|   | 3.5                 | Example Configuration             | 14 |  |  |  |

| 4 | LFA                 | ST configuration                  | 15 |  |  |  |

| 5 | Zipw                | Zipwire hardware and layout24     |    |  |  |  |

| A | Zipwire driver2     |                                   |    |  |  |  |

|   | A.1                 | Overview                          |    |  |  |  |

|   | A.2                 | About this Appendix               | 26 |  |  |  |

|   | A.3                 | Zipwire Driver API                | 26 |  |  |  |

| В | B Zipwire connector |                                   | 35 |  |  |  |

| С | References          |                                   |    |  |  |  |

| D | Revis               | sion history                      |    |  |  |  |

|   |                     | — 🦻 freescale                     |    |  |  |  |

#### ∠ıpwire Interface overview

Zipwire uses a low-speed reference clock that is shared between the clients and uses a single pair of LVDS signals for data transmission and a second pair for reception. The normal communication mode for the Zipwire is 320 Mb/s, however, it starts up at a lower speed until a basic connection is established between the devices.

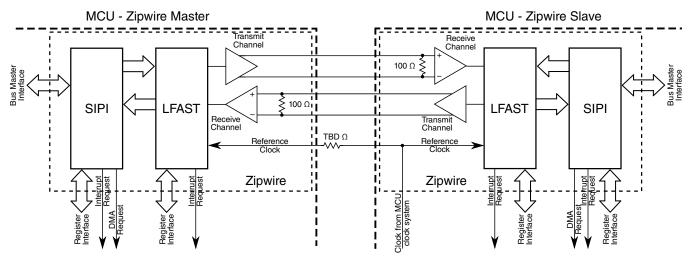

On the current Freescale microcontrollers (MCU) that support the Zipwire interface, if two MCUs are connected, either MCU can be defined as the master and the other defined as the slave device. This may also depend on the clock generation requirements for the devices.

- The master device is defined as the device that "owns" the link. It acts as the initiator for all link management commands, such as changing the interface speed, sending ping commands, and recovering from errors. The master device receives the reference clock from the slave device.

- The slave device generates the reference clock and provides it to the master. In addition, the slave device responds to all link management commands from the master device.

The following table shows the Freescale devices that implement the Zipwire interface for interprocessor communication. It includes both Power Architecture® based devices and devices based on ARM® cores.

#### Table 1. Devices that support the Zipwire interprocessor communication interface

| Device   | Core type          |

|----------|--------------------|

| MPC574xP | Power Architecture |

| MPC574xR | Power Architecture |

| MPC577xK | Power Architecture |

| MPC577xC | Power Architecture |

| MPC5777M | Power Architecture |

| S32V23x  | ARM                |

The Zipwire interface is compatible with devices available from ST Microelectronics and the High Speed Serial Interface (HSSI) from Infineon Technologies AG.

The Zipwire interface could also be used to connect an MCU with an external smart peripheral.

This application note provides an overview of the Zipwire Interprocessor communication interface, including the hardware interface, the recommended software API<sup>2</sup>, and an example of a typical use to transfer information between two devices.

### 2 Zipwire Interface overview

Some members of the MPC57xx family implement a Zipwire Interface as an Interprocessor Communication interface. Zipwire is a fully operational and layered protocol to exchange data between two devices. Features of the Zipwire interface include:

- Point to point communication

- Simple high speed, full duplex, flexible interface

- Low pin count (5)

- Timeout protection

- Fixed priority

- Cyclic redundancy check for data integrity

- Pipe-lined, multi-channel architecture for overlapping requests (up to two outstanding requests by the initiator)

- · Streaming mode

- Multiple loopback modes to check the physical interface

- · Automatic ping response generation when in slave mode

- Detects unsupported channel numbers and unsupported payload sizes

2. Application Programming Interface

#### Zipwire Interface overview

The actual physical layer is implemented with the LFAST physical communication interface. As implied in the name of the interface, the LFAST physical layer is an asynchronous fast serial interface. The protocol is based on a frame format that includes synchronization information at the beginning of the frame. Data within the frame is synchronous.

The application layer of Zipwire is implemented in the SIPI. The application layer runs on top of the LFAST physical communication interface and has its own protocol. The main purpose of the SIPI is to provide the framework to exchange information and provides the link between memory or processes on one MCU through the LFAST physical communication interface to another MCU or a smart peripheral device. SIPI also adds error detection features such as CRC, acknowledge, and timeout. (The LFAST protocol does not include any error detection/correction scheme by itself). The SIPI layer supports multiple channels and some transfers can be overlapped.

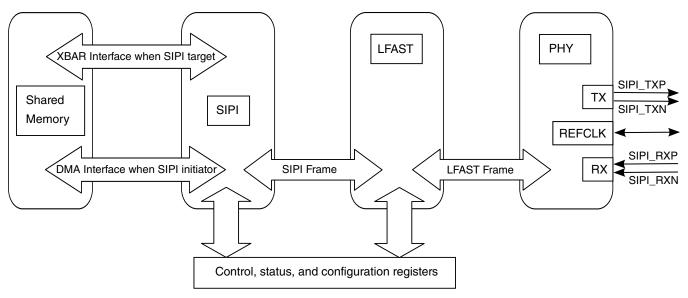

In summary, SIPI and LFAST offer the means to exchange information between processors at rates up to 320 Mb/s. The following figure shows an overview of a typical Zipwire implementation showing the memory interface through the SIPI and LFAST modules to the physical drivers and receivers.

Figure 1. Zipwire overview

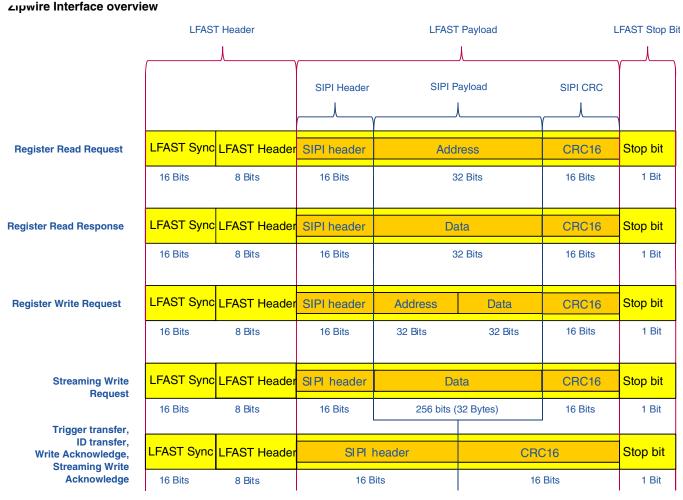

The figure below shows the frame format of the LFAST encapsulated SIPI frames/messages. A frame starts with 16 bits for synchronization (0b1010\_1000\_0100\_1011 [0xA84B]) followed by the LFAST header. The payload of the LFAST frame includes the SIPI header and the actual payload (the contents depend on the payload type), followed by a CRC of the SIPI information. The frame ends with a single '1' stop bit. The synchronization pattern allows the receiver to adjust when the bits will be sampled within the remaining bits in the frame for optimum performance. The receiver uses a multiphase clock to determine which phase of its internal clock to use based on decoding the LFAST sync pattern.

Figure 2. Zipwire message formats

See the Zipwire, SIPI, and LFAST chapters of the device reference manual for more information about the specific values of the LFAST Header, SIPI header, and explanation of the different types of messages.

### 2.1 Zipwire SIPI LFAST software model

Software should interact with the Zipwire hardware through the standard API. The Zipwire API conforms to the standard Open Systems Interconnection (OSI) model. The following table shows the mapping of the software and hardware to the OSI model. The Zipwire LFAST module handles the basic media layer (packet, frame, and bit formatting), with the SIPI module handling most of the Host layers, except for the network process to application layer (transport, session, and presentation layers). Using the Zipwire API allows the user software to interface in a standard manner to the lower levels of the model.

| OSI Model   |           |                 |                                                                                                                  | Protocol Name    |         |

|-------------|-----------|-----------------|------------------------------------------------------------------------------------------------------------------|------------------|---------|

| Layer       | Data Unit | Layer           | Function                                                                                                         | 1                |         |

| Host Layers | Data      | 7. Application  | Network process to application                                                                                   | SIPI<br>Software | Zipwire |

|             |           | 6. Presentation | Data representation, encryption and<br>decryption, convert machine dependent<br>data to machine independent data | SIPI<br>Hardware |         |

Table continues on the next page ...

| OSI Model    |                               |              |                                                                  |       | Protocol Name |  |

|--------------|-------------------------------|--------------|------------------------------------------------------------------|-------|---------------|--|

| Layer        | ayer Data Unit Layer Function |              |                                                                  |       |               |  |

|              |                               | 5. Session   | Inter-host communication, managing sessions between applications |       |               |  |

|              | Segment                       | 4. Transport | End-to-end connections, reliability and flow control             |       |               |  |

| Media Layers | Packet                        | 3. Network   | Path determination and logical addressing                        | LFAST |               |  |

|              | Frame                         | 2. Data Link | Physical addressing                                              |       |               |  |

|              | Bit                           | 1. Physical  | Media, signal and binary transmission                            |       |               |  |

#### Table 2. Zipwire SIPI LFAST software model (continued)

### 2.2 Typical Zipwire example overview

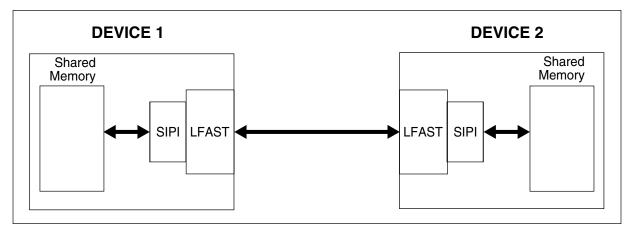

The simplest example of a Zipwire interface is two MPC5777M microcontrollers communicating to each other (See the figure below). Device 1 wants to write a memory location of Device 2.

- 1. The SIPI module, acting as the initiator, of the first MCU will use the DMA to acquire data to be sent from memory. This is done via software initialization.

- 2. Once the data registers are full, the initiator SIPI will automatically construct a frame indicating the operation to perform, the address to be written, the data to write, and a CRC. This is handled by the SIPI module in hardware.

- 3. This SIPI frame will then be sent by the hardware o the LFAST module and the module will embed the SIPI frame within a greater LFAST compliant frame that will be sent through the physical interface.

- 4. The LFAST frame will be received by the second MCU, acting as a target node. The LFAST will then decompose the frame back into a SIPI understandable frame and send it to the SIPI. This is handled in hardware.

- 5. The SIPI target will verify that the message is correct and use the XBAR master interface to modify the data at the requested address. Once completed, the SIPI target will send back a write acknowledge message to the initiator. This is all handled by the Zipwire hardware.

- 6. Once the acknowledge has been received by the initiator, the DMA on the first device can start another operation until the desired amount of data has been written to the target MCU.

Figure 3. Typical Zipwire application

### 3 Zipwire examples

This section describes some basic examples of using the Zipwire driver. Simple functions were written to show the basic operations of the Zipwire interface, including determining the remote device connected and performing simple operations to the remote device over the Zipwire link.

Each of the examples is set up as a separate example and each contains both the Master and the Slave software. Each includes calls to the Zipwire API routines. The Zipwire API is included in this document as an appendix.

### 3.1 Function file locations

This application note includes a zip file that contains all of the code discussed in this application note. The software was compiled with the Green Hills Software Multi compiler, version 2014.1.2, but later versions should also work.

The software project included in this application note is divided into two sections. There is the main example code and there is a separate subdirectory of the code required for the API interface. The following table lists all functions in this example application note and the file name in which they are implemented. There are three functions that must be modified with MCU specific information.

| File Name                            | Description                                         | Function                                                |

|--------------------------------------|-----------------------------------------------------|---------------------------------------------------------|

| crt0.s                               | Device low level 'C' code<br>initialization         | 1                                                       |

| LFAST.c                              | Device specific initialization                      | LFAST_Configure(unsigned char master) <sup>1</sup>      |

| main.c                               | Main example code                                   | user_testcase(void)                                     |

|                                      |                                                     | main(void)                                              |

| mcu_init_flash.c                     | MCU specific initialization (in 'C')                | MC_MODE_INIT(void) <sup>1</sup>                         |

| SIPI.c Example functions used in the |                                                     | unsigned char sipi_app_note_read(void)                  |

|                                      | example code that call the<br>Zipwire API functions | unsigned char sipi_app_note_write(void)                 |

|                                      |                                                     | unsigned char sipi_app_note_multiple_read_no_dma(void)  |

|                                      |                                                     | unsigned char sipi_app_note_multiple_write_no_dma(void) |

|                                      |                                                     | unsigned char sipi_app_note_multiple_write_dma(void)    |

|                                      |                                                     | unsigned char sipi_app_note_stream_write(void)          |

|                                      |                                                     | unsigned char sipi_app_note_ID(void)                    |

|                                      |                                                     | unsigned char sipi_app_note_event(void)                 |

Table 3. Example function file locations

#### 1. Values used in this function are device specific

In addition to the example code, there are additional header files that are included in this example project. These are shown in the following table.

#### Table 4. Zipwire example header files

| File Name | Description                                                                                                                                                             |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | This header file provides all of the prototype functions for the Zipwire driver. This file can be included in the target software to include the Zipwire API functions. |

|           | This header file contains all of the necessary definitions for the Zipwire driver internal use.                                                                         |

The files and functions for the Zipwire API itself, are included in the appendix of this application note. The file SIPI\_HSSL\_Header\_v4.h, along with the Zipwire API object files should be included in the project to include the Zipwire API routines.

### 3.2 Zipwire demo overview

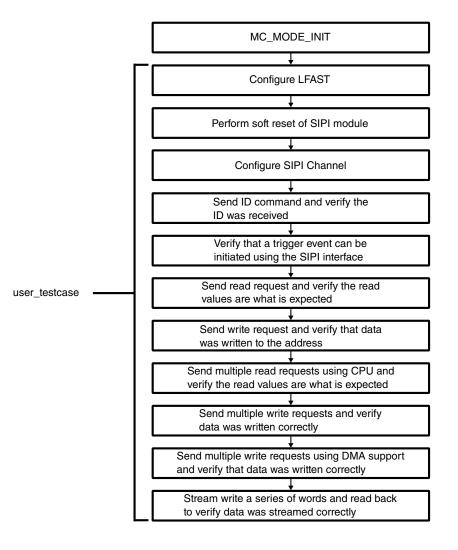

The Zipwire demo program is an example of using the Zipwire driver and is contained in the file main.c. This program initializes the MCU and then calls the example functions. The flow chart of the demo is shown in Figure 4.

### Figure 4. Zipwire Demo Code Flow Chart

The demo consists of several functions that are called from the demo. These functions are listed in Table 5.

|  | Table 5. | Demo fu | unction | overview |

|--|----------|---------|---------|----------|

|--|----------|---------|---------|----------|

| Function                           | Description                                                                                                                                                 |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| sipi_app_note_read                 | Exercises the SIPI_read() and SIPI_read_channel_data functions to send a read request and verifies that the read values are the expected values.            |

| sipi_app_note_write                | Exercises the SIPI_write(), SIPI_read() and SIPI_read_channel_data functions to send a write request and then verify that the address was actually written. |

| sipi_app_note_ID                   | Exercises the SIPI_ID() and SIPI_read_channel_data functions to send the ID command and read the CADR to verify that the ID was received.                   |

| sipi_app_note_event                | Exercises SIPI_Trigger() to verify that a trigger event can be initiated using the SIPI interface.                                                          |

| sipi_app_note_multiple_read_no_dma | Exercises SIPI_multiple_read() without using DMA support, each array will be read using CPU and the read contents will be verified.                         |

Table continues on the next page...

| Function                            | Description                                                                                                                                                                                             |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| sipi_app_note_multiple_write_no_dma | Exercises SIPI_multiple_write() and SIPI_multiple_read() to send multiple write requests, once completed will read the written content to verify that the data was written correctly.                   |

| sipi_app_note_multiple_write_dma    | Exercises SIPI_multiple_write() using DMA support and SIPI_multiple_read() to send multiple write requests, once completed will read the written content to verify that the data was written correctly. |

| sipi_app_note_stream_write          | Exercises SIPI_stream_transfer() and SIPI_multiple_read() to stream write a series of words and then read them back to verify the data.                                                                 |

#### Table 5. Demo function overview (continued)

### 3.2.1 Function index

The following table shows the functions used in the SIPI application note demo.

| Туре          | Name                                | Arguments            |

|---------------|-------------------------------------|----------------------|

| void          | LFAST_Configure                     | unsigned char master |

| void          | MC_MODE_INIT                        | void                 |

| unsigned char | sipi_app_note_ID                    | void                 |

| unsigned char | sipi_app_note_event                 | void                 |

| unsigned char | sipi_app_note_multiple_read_no_dma  | void                 |

| unsigned char | sipi_app_note_multiple_write_dma    | void                 |

| unsigned char | sipi_app_note_multiple_write_no_dma | void                 |

| unsigned char | sipi_app_note_read                  | void                 |

| unsigned char | sipi_app_note_stream_write          | void                 |

| unsigned char | sipi_app_note_write                 | void                 |

| void          | user_testcase                       | void                 |

### 3.2.2 Function MC\_MODE\_INIT

This function initializes the MPC5777M processor. It sets up the phase lock loop to set the device operating frequency, the peripheral clock frequencies, and enables all of the peripheral modules in the different "RUN" modes. It then performs a mode change to enable the clocks and enable all cores of the device.

The function must be tailored for the target system and environment, including the device crystal frequency.

NOTE

The Zipwire clock is set up in the file LFAST.c.

Prototype: void MC\_MODE\_INIT(void);

∠ıpwire examples

### 3.2.3 Function user\_testcase

The user testcase is the actual example code and calls most of the other functions of the Zipwire example code. The flow of this section is shown in Figure 4.

Prototype: void user\_testcase(void);

### 3.2.4 Function LFAST\_Configure

Configures the LFAST as either a Master or a Slave, sets the clocks and bus speeds, and configures the pins to set the LFAST link.

Prototype: void LFAST\_Configure(unsigned char master);

| Table 7. LFAST_Configure Arguments |

|------------------------------------|

|------------------------------------|

| Туре          | Name   | Direction | Description                                                     |

|---------------|--------|-----------|-----------------------------------------------------------------|

| unsigned char | master | input     | defines whether to configure the LFAST node as master or slave. |

### 3.2.5 Function sipi\_app\_note\_ID

Exercises the SIPI\_ID() and SIPI\_read\_channel\_data functions to send the ID command and read the CDR to verify that the ID was received.

Prototype: unsigned char sipi\_app\_note\_ID(void);

#### Return:

- 0 = Successfully Set Up

- 2 = Channel Busy

- 3 = Invalid Channel

- 4 = Timeout Error

- 10 = ID Not received properly

### 3.2.6 Function sipi\_app\_note\_read

Exercises the SIPI\_read() and SIPI\_read\_channel\_data() functions to send a read request and verifies that the read values are the expected values.

Prototype: unsigned char sipi\_app\_note\_read(void);

#### Return:

- 0 = Successful

- 1 = Invalid Width

- 2 = Channel Busy

- 3 = Invalid Channel

- 4 = Timeout Error

- 10 = Wrong read value

### 3.2.7 Function sipi\_app\_note\_write

Exercises the SIPI\_write(), SIPI\_read() and SIPI\_read\_channel\_data functions to send a write request and then verify that the address was actually written.

Prototype: unsigned char sipi\_app\_note\_write(void);

Return:

- 0 = Successfully Set Up

- 1 = Invalid Data Size

- 2 = Channel Busy

- 3 = Invalid Channel

- 4 = Timeout Error / Wrong Acknowledge

- 10 = Wrong Read Value

### 3.2.8 Function sipi\_app\_note\_multiple\_read\_no\_dma

Exercises SIPI\_multiple\_read() without using DMA support. Each array will be read using CPU and the read contents will be verified.

Prototype: unsigned char sipi\_app\_note\_multiple\_read\_no\_dma(void);

#### Return:

- 0 = Successfully Set Up

- 1 = Incorrect Channel

- 2 = Channel Busy

- 4 = Timeout Error

- 10 = Data not read properly

### 3.2.9 Function sipi\_app\_note\_multiple\_write\_no\_dma

Exercises SIPI\_multiple\_write() and SIPI\_multiple\_read() to send multiple write requests, once completed will read the written content to verify that the data was written correctly.

Prototype: unsigned char sipi\_app\_note\_multiple\_write\_no\_dma(void);

**Return:**

- 0 = Successfully Set Up

- 1 = Incorrect Channel

- 2 =Channel Busy

- 4 = Timeout Error

- 10 = Data not read properly

### 3.2.10 Function sipi\_app\_note\_multiple\_write\_dma

Exercises SIPI\_multiple\_write() using DMA support and SIPI\_multiple\_read() to send multiple write requests. Once completed, will read the written content to verify that the data was written correctly.

Prototype: unsigned char sipi\_app\_note\_multiple\_write\_dma(void);

#### **Return:**

- 0 = Successfully Set Up

- 1 = Incorrect Channel

#### ∠ıpwire examples

- 2 = Channel Busy

- 4 = Timeout Error

- 10 = Data not read properly

### 3.2.11 Function sipi\_app\_note\_stream\_write

Exercises SIPI\_stream\_transfer() and SIPI\_multiple\_read() to stream write a series of words and then read them back to verify the data.

Prototype: unsigned char sipi\_app\_note\_stream\_write(void);

#### Return:

- 0 = Successfully Set Up

- 1 = Incorrect Channel

- 2 = Channel Busy

- 4 = Timeout Error

- 10 = Data not read properly

### 3.2.12 Function sipi\_app\_note\_event

Exercises SIPI\_Trigger() to verify that a trigger event can be initiated using the SIPI interface. Target device waits until the trigger event is received.

Prototype: unsigned char sipi\_app\_note\_event(void);

#### Return:

- 0 = Successfully Set Up

- 1 = Incorrect Channel

- 2 = Channel Busy

### 3.3 LFAST clock settings

The LFAST interface requires a reference clock and uses an internal Phase Lock Loop (PLL) to derive the timing used for transmitting and receiving the LFAST signals. The clock is generated by the Zipwire slave device, and the Zipwire master device uses the external clock as the reference for its PLL. The possible frequencies are shown in the table below.

| Reference clock frequency | Low speed operating<br>frequency | High speed operating<br>frequency | LFAST PLL multiplier |

|---------------------------|----------------------------------|-----------------------------------|----------------------|

| 10 MHz                    | 5 MHz                            | 320 MHz                           | 32                   |

| 20 MHz                    | 5 MHz                            | 320 MHz                           | 16                   |

Software must enable the clock signal in low speed mode initially. Once a link is established at low speed, the Zipwire interface can be put into high speed mode.

In the current MCUs, there are three sources for the clock used by the Zipwire interface, the MCU oscillator, the output of the system phase-lock loop (PLL), or the external LFAST reference clock that is provided by the slave Zipewire device. The clock frequency is typically 20 MHz. The Zipwire interface contains a dedicated PLL<sup>3</sup> that uses the reference clock to generate the 320 MHz required for operation of the LFST and SIPI modules.

### 3.4 Zipwire pins

The Zipwire interface consists of five signals: a pair of LVDS transmit pins, a pair of receive LVDS pins, and a clock. The clock is unidirectional and is defined to be an output on the Slave and an input on the Master node. The following table shows the Zipwire pins.

#### NOTE

The signal names are named slightly different between the different devices. Both names indicate the Zipwire signal.

| Zipwire signal           | Full Name                            | Direction    | Description                                                    |

|--------------------------|--------------------------------------|--------------|----------------------------------------------------------------|

| SIPI_TXN/<br>LFAST_TXN   | SIPI Transmit LVDS Negative terminal | Output       | The negative signal of the Zipwire transmit interface.         |

| SIPI_TXP/<br>LFAST_TXP   | SIPI Transmit LVDS Positive terminal | Output       | The positive signal of the Zipwire transmit interface.         |

| SIPI_RXN/<br>LFAST_RXN   | SIPI Receive LVDS Negative terminal  | Input        | The negative signal of the Zipwire receive interface.          |

| SIPI_RXP/<br>LFAST_RXP   | SIPI Receive LVDS Positive terminal  | Input        | The positive signal of the Zipwire receive interface.          |

| LFAST_REFCL<br>K/REF_CLK | LFAST interface system clock         | Input/Output | The input or output reference clock for the Zipwire interface. |

#### Table 9. Zipwire Signals

Different devices instantiate the Zipwire signals on different pins of the device. The following table shows the pins used for the Zipwire interface.

| Zipwire pin      | MPC5     | 574xP <sup>1</sup> | MPC          | 577xC          | MPC5     | 77xK             | MPC               | 5777M         | S32                     | V23x   |

|------------------|----------|--------------------|--------------|----------------|----------|------------------|-------------------|---------------|-------------------------|--------|

|                  | Port Pin | MSCR               | Port<br>Pin  | MSCR           | Port Pin | MSCR             | Port Pin          | MSCR          | Port Pin                | MSCR   |

| SIPI_TXN         | PI[5]    | 133<br>(SSS=3)     | PLLCFG<br>0  | 208<br>(SSS=4) | 2        | —                | PD[6]             | 54<br>(SSS=1) | 3                       | _      |

| SIPI_TXP         | PC[12]   | 44<br>(SSS=3)      | PLLCFG<br>1  | 209<br>(SSS=4) | 2        | —                | PA[14]<br>(SSS=1) | 14<br>(SSS=1) | 3                       | —      |

| SIPI_RXN         | PI[6]    | 134<br>(SSS=3)     | WKPCF<br>G   | 213<br>(SSS=4) | 2        | _                | PF[13]            | 93            | 4                       | —      |

| SIPI_RXP         | PG[7]    | 103<br>(SSS=3)     | BOOTC<br>FG0 | 211<br>(SSS=4) | 2        | _                | PD[7]             | 55            | 4                       | —      |

| LFAST_REFCL<br>K | PI[7]    | 135<br>(SSS=1)     | PLLCFG<br>2  | 210<br>(SSS=4) | 135      | PI[7]<br>(SSS=1) | PF[14]            | 94<br>(SSS=1) | PC8<br>(MODE_<br>MUX=2) | 40/550 |

1. The Zipwire interface is only available in the 257 MAPBGA package.

2. The transmit and receive pins on this device are dedicated LVDS functions and require no configuration.

3. Function selected by SRC\_SOC\_GPR3[4]

4. This is a dedicated LVDS signal for the LFAST interface.

3. In devices that include both an Interprocessor communication Zipwire interface and a debug Zipwire interface, the PLL may be shared between both interfaces.

∠ıpwire examples

Table 11 describes the values to be programmed into the Multiplexed Signal Configuration register to setup up the Zipwire pins for the MPC5777M. Other devices in Table 10 may require a different initialization.

| value               | 5                                                                                                                                 |                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                   |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Register<br>Setting | Direction                                                                                                                         | Bit settings                                                                                                                                                                                                        | Description                                                                                                                                                                                                                                                                                       |

| 0x0500_0000         | Output                                                                                                                            | ODC = 0b101                                                                                                                                                                                                         | Output Drive Control is LFAST LVDS                                                                                                                                                                                                                                                                |

| 0x0500_0000         | Output                                                                                                                            | ODC = 0b101                                                                                                                                                                                                         | Output Drive Control is LFAST LVDS                                                                                                                                                                                                                                                                |

| 0x0020_0001         | Output                                                                                                                            | ILS = 0b10                                                                                                                                                                                                          | Input Level Selection is LVDS                                                                                                                                                                                                                                                                     |

|                     |                                                                                                                                   | SSS = 0x01                                                                                                                                                                                                          | Source Signal Source is SIPI_RXN                                                                                                                                                                                                                                                                  |

| 0x0020_0001         | Input                                                                                                                             | ILS = 0b10                                                                                                                                                                                                          | Input Level Selection is LVDS                                                                                                                                                                                                                                                                     |

|                     |                                                                                                                                   | SSS = 0x01                                                                                                                                                                                                          | Source Signal Source is SIPI_RXP                                                                                                                                                                                                                                                                  |

| 0x0008_0001         | Input                                                                                                                             | WPUE = 1                                                                                                                                                                                                            | Weak pull up is enabled                                                                                                                                                                                                                                                                           |

|                     |                                                                                                                                   | SSS = 0x1                                                                                                                                                                                                           | Source Signal Source is LFAST_REFCLK                                                                                                                                                                                                                                                              |

| 0x2280_0000         | Output                                                                                                                            | OERC = 0b010                                                                                                                                                                                                        | Output Edge Rate is Strong Drive (50 ohm/5 ns)                                                                                                                                                                                                                                                    |

|                     |                                                                                                                                   | ODC = 0b010                                                                                                                                                                                                         | Output drive control is push-pull                                                                                                                                                                                                                                                                 |

|                     |                                                                                                                                   | SMC = 0b1                                                                                                                                                                                                           | Pin is not disabled in Safe Mode Control                                                                                                                                                                                                                                                          |

|                     |                                                                                                                                   | SSS = 0x1                                                                                                                                                                                                           | Source Signal Source is LFAST_REFCLK                                                                                                                                                                                                                                                              |

|                     | Register<br>Setting           0x0500_0000           0x0500_0000           0x0020_0001           0x0020_0001           0x0008_0001 | Setting         Distribution           0x0500_0000         Output           0x0500_0000         Output           0x0020_0001         Output           0x0020_0001         Input           0x0008_0001         Input | Register<br>SettingDirectionBit settings $0x0500\_0000$ OutputODC = 0b101 $0x0500\_0000$ OutputODC = 0b101 $0x0020\_0001$ OutputILS = 0b10 $0x0020\_0001$ InputILS = 0b10 $0x0020\_0001$ InputILS = 0b10 $0x0008\_0001$ InputSSS = 0x01 $0x2280\_0000$ OutputOERC = 0b010 $0DC = 0b010$ SMC = 0b1 |

# Table 11. MPC5777M Multiplexed Signal Configuration register (MSCR) values

### 3.5 Example Configuration

The Zipwire.h file is used to define if the software should configure the Zipwire node as a master or slave interface. CONFIGURED\_AS\_MASTER must be set to select either master or slave mode depending on the compile requirements of the software. To use this example, the example software must be compiled both as a master and as a slave and programed into two separate MCUs. These MCUs should have the Zipwire interfaces connected to each other, connecting the master's transmit pins (N and P) to the Slave's receive pins (N and P). The Slave's transmit pins (N and P) must be connected to the master's receive pins (N and P). The clock pin of the master and slave must also be connected to each other.

#### NOTE

Depending on the board layout and requriements, a termination resistor may be needed on the REFCLK signal. See Zipwire hardware and layout.

This example is written to support different implementations of the Zipwire interface, although all current implementations have the same number of channels. In addition, all current MCU implementations support being set as a master or a slave.

### 3.5.1 Define CONFIGURED\_AS\_MASTER

Definition:#define CONFIGURED\_AS\_MASTER 0

#### Possible values:

- 0 =Slave

- 1 = Master

### 4 LFAST configuration

The LFAST module allows for many options to be programmed into its configuration registers. However, most of these options should not be used by customers. This section describes the recommended configuration that should be used for the LFAST Master interface that is implemented in this example, specifically, in the LFAST\_Configure (LFAST.c).

| Step | Description                                              | RM Operation                                                                                                                                   | Registers <sup>1</sup>                                 | Bits                                                                                                                           |

|------|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| 0    | Initialize<br>device pins<br>for the                     | Set up the Positive and Negative Transmit pins<br>in the System Integration unit Lite 2 (SIUL2)<br>Multiplexed Signal Control Registers (MSCR) | See Table 11                                           |                                                                                                                                |

|      | Zipwire<br>interface                                     | Set up the Positive and Negative Receive pins in the SIUL2 MSCR                                                                                |                                                        |                                                                                                                                |

| 1    | Set the<br>LFAST<br>wakeup                               | AST programmed according to the LVDS                                                                                                           | LFAST Rate Change<br>Delay Control Register<br>(RCDCR) | Data Rate Controller<br>Count Value (DRCNT) =<br>0xF                                                                           |

|      | delay and<br>rate change<br>delay for the<br>Line Driver |                                                                                                                                                | LFAST Wakeup Delay<br>Control register (SLCR)          | High Speed Sleep Mode<br>Exit Time (HSCNT) =<br>0x12 (18 cycles)                                                               |

|      | (LD).                                                    |                                                                                                                                                |                                                        | Low Speed Sleep Mode<br>Exit Time (LSCNT) = 0x1                                                                                |

|      |                                                          |                                                                                                                                                |                                                        | Wake Up time for the LD<br>(HWKCNT) = 0x54                                                                                     |

|      |                                                          |                                                                                                                                                |                                                        | Wake Up time for the LD (LWKCNT) = 0x2                                                                                         |

| 2    | 2 Set the<br>LFAST<br>operating                          | FAST parameters for the PLL                                                                                                                    | LFAST PLL Control<br>Register (PLLCR)                  | PLL Loop Optimization<br>(LPCFG) = 3 (2x IBASE<br>current                                                                      |

|      | speeds                                                   |                                                                                                                                                |                                                        | Division Factor for the<br>PLL Reference Clock<br>(PREDIV) = 0 (Direct<br>Clock)                                               |

|      |                                                          |                                                                                                                                                |                                                        | Feedback Division factor<br>for PLL Reference Clock<br>(FBDIV) = 15                                                            |

|      |                                                          |                                                                                                                                                |                                                        | Test mode<br>programmability<br>(IPTMODE) = 0b000<br>Normal functional mode.<br>Test modes should not<br>be used by customers. |

|      |                                                          |                                                                                                                                                |                                                        | SW signal to turn off the<br>PLL (SWPOFF) = 0b0.<br>The PLL should not be<br>disabled for normal<br>operation.                 |

|      |                                                          |                                                                                                                                                |                                                        | Software signal to turn<br>on the PLL (SWPON) =                                                                                |

#### Table 12. LFAST Master mode configuration

Table continues on the next page...

⊾гผง้T configuration

| Step | Description                                | RM Operation                                                                                          | Registers <sup>1</sup>                                              | Bits                                                                                                                                                                 |

|------|--------------------------------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |                                            |                                                                                                       |                                                                     | 0b0 = Do not turn on the PLL.                                                                                                                                        |

|      |                                            |                                                                                                       |                                                                     | Invert reference clock<br>edge to the PFD<br>(REVINV) = 0b0 = The<br>reference clock should<br>not be inverted.                                                      |

|      |                                            |                                                                                                       |                                                                     | PLL Lock Ready Count<br>Width (PLCLKCW) = 0b0<br>= 1040 cycles <sup>2</sup>                                                                                          |

|      |                                            |                                                                                                       |                                                                     | Enable Fraction mode in<br>feedback divider<br>(FDINEN) = 0b0 - do not<br>enable                                                                                     |

| 3    | Set up the<br>SIUL2 MSCR<br><sup>3</sup>   | Initialize the Zip wire clock pin as an input with<br>CMOS levels to receive the clock from the Slave | SIUL2 Multiplexed Signal<br>Control Register<br>(MSCR) <sup>4</sup> | Master: MSCR =<br>0x0038_0001                                                                                                                                        |

| 4    | Program the<br>LVDS<br>Control<br>Register | The LCR is programed with configuration parameters of the LVDS                                        | LCR = 0x0000_502C<br>(default value)                                | SWWKLD, SWSLPLD,<br>SWWKLR, SWSSLPLR,<br>SWOFFLD, SWONLD,<br>SWOFFLR, SWONLR =<br>0b0 - do not put the line<br>driver or line receiver to<br>sleep or disabled state |

|      |                                            |                                                                                                       |                                                                     | LVDS Line Receiver off<br>state (LVRXOFF) = 0b0 -<br>low when the LFAST<br>Receiver is in shutdown<br>mode                                                           |

|      |                                            |                                                                                                       |                                                                     | LVTXOE = 0b1 - output<br>buffer enabled                                                                                                                              |

|      |                                            |                                                                                                       |                                                                     | TXCMUX = 0b0 - do not<br>put phase clock on the<br>transmit pin                                                                                                      |

|      |                                            |                                                                                                       |                                                                     | LVRFEN = 0b1 - enable<br>the LVDS reference                                                                                                                          |

|      |                                            |                                                                                                       |                                                                     | LVLPEN = 0b0 - enable<br>normal mode (not<br>loopback mode)                                                                                                          |

|      |                                            |                                                                                                       |                                                                     | LVRXOP = 0b101 -<br>enable receive<br>termination and<br>configure for maximum<br>data rate                                                                          |

|      |                                            |                                                                                                       |                                                                     | LVTXOP = 0b1 - enable<br>LFAST mode                                                                                                                                  |

|      |                                            |                                                                                                       |                                                                     | LVCKSS = 0b0 - use<br>normal data mode                                                                                                                               |

|      |                                            |                                                                                                       |                                                                     | LVCKP=0b0 - use the<br>direct PLL clock                                                                                                                              |

### Table 12. LFAST Master mode configuration (continued)

Table continues on the next page ...

| Step | Description                                                           | RM Operation                                                                                                                                  | Registers <sup>1</sup>                       | Bits                                                                                 |

|------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------|

| 5    |                                                                       | Write MCR[MSEN] = 1. Then select LFAST<br>modes by configuring MCR[CTSEN],<br>MCR[TXSLPEN]and MCR[DATAEN]                                     | Mode Configuration<br>Register (MCR)         | Master: MCR[MSEN] =<br>0b1                                                           |

|      | or Slave<br>operation.                                                | Enable Data Frame Transmission.                                                                                                               |                                              | MCR[DATAEN] = 0b1 -<br>enable data frame<br>transmission and<br>reception            |

| 6    | Use 20 MHz<br>clock input<br>with divide<br>by 4 for PLL<br>clock     | Select the fraction of sysclk in Low Speed Select mode                                                                                        | Mode Configuration<br>Register (MCR)         | MCR[LSSEL] = 0b1 -<br>divide by 4                                                    |

| 7    | Enable<br>LFAST<br>Transmitter<br>Line Driver<br>and Line<br>Receiver | Write MCR[DRFEN] = 1 to enable the LFAST                                                                                                      | Mode Configuration<br>Register (MCR)         | LFAST Driver/Receiver<br>Enable (DRFEN) = 0b1 -<br>Enable                            |

| 8    | Enable the<br>Transmit and<br>Receive<br>circuits                     | Write MCR[RXEN] = 1 and MCR[TXEN] = 1 to<br>negate the Line Driver (LD) powerdown, Line<br>Receiver (LR) disable, and LR powerdown<br>signals | Mode Configuration<br>Register (MCR)         | LVDS Transmit Enable<br>(TXEN) = 0b1, LVDS<br>Receiver Enable (RXEN<br>= 0b1.        |

|      | the following store (failed)                                          | eps (9-16) until the slave acknowledges whether t                                                                                             | he Ping frame was succes                     | sfully received or not from                                                          |

| 9    |                                                                       | Write ICR[ICLCPLD] = 31h to enable the Slaves<br>Tx Interface                                                                                 | ICLC Control Register<br>(ICR)               | ICLC Payload<br>(ICLCPLD) = 0x31 -<br>Enable Slave transmitter                       |

| 10   | Initiate a<br>ICLC frame<br>request and<br>set to only                | Write ICR[SNDICLC] = 1 and ICR[ICLCSEQ] = 1                                                                                                   | ICLC Control Register<br>(ICR)               | ICLC Frame request<br>(SNDICLC) = 0b1 =<br>initiate the transfer of an<br>ICLC frame |

|      | allow ICLC<br>frames to be<br>sent                                    |                                                                                                                                               |                                              | ICLC Enabled<br>(ICLCSEQ) = 0b1=<br>Enable the sending of<br>only ICLC frames        |

| 11   | Enable<br>transmit<br>arbiter                                         | Write MCR[TXARBD] = 0                                                                                                                         | Mode Configuration<br>Register (MCR)         | Transmit Arbiter Disable<br>(TXARBD) = 0x0 =<br>Enable Tx arbiter and<br>framer      |

| 12   | Wait for ICLC<br>frame to be<br>transmitted                           | The ICLC transmission is confirmed by verifying one of the following:<br>• ICR[SNDICLC] = 0                                                   | ICLC Control Register<br>(ICR)               | ICLC Frame request<br>(SNDICLC) = 0b0 Frame<br>transmitted                           |

|      |                                                                       | <ul> <li>TISR[TXICLCF] = 1</li> </ul>                                                                                                         | Transmit Interrupt Status<br>Register (TISR) | Transmit ICLC Frame<br>transmitted Interrupt<br>(TXICLCF) = 0b1                      |

| 13   | Clear<br>TXICLCF                                                      | Write TISR[TXICLCF] = 1                                                                                                                       | Transmit Interrupt Status<br>Register (TISR) | Transmit ICLC Frame<br>transmitted Interrupt<br>(TXICLCF) = 0b1                      |

### Table 12. LFAST Master mode configuration (continued)

Table continues on the next page ...

டாகல்T configuration

| Step     | Description                                              | RM Operation                                                                                                                                                                                                                                                                    | Registers <sup>1</sup>                                                                    | Bits                                                                                                                                               |

|----------|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 14       | Request a<br>ping from the<br>Slave node                 | Write ICR[ICLCPLD] = 00h to check the LFAST slaves status                                                                                                                                                                                                                       | ICLC Control Register<br>(ICR)                                                            | ICLC Payload<br>(ICLCPLD) = 0x00 Ping<br>request from Master to<br>Slave                                                                           |

| 15       | Send the<br>ping from<br>slave request<br>frame          | Write ICR[SNDICLC] = 1                                                                                                                                                                                                                                                          | ICLC Control Register<br>(ICR)                                                            | ICLC Frame request<br>(SNDICLC) = 0b1 =<br>initiate the transfer of an<br>ICLC frame                                                               |

| 16       | Confirm<br>slave status                                  | <ul> <li>The LFAST slave status is confirmed by occurrence of one of the following:</li> <li>LFAST slave is enabled if RIISR[ICPSF] = 1. Proceed to step 14</li> <li>LFAST slave is disabled if RIISR[ICPFF] = 1. The LFAST master must wait and restart from Step 7</li> </ul> | Receive Interface<br>Control Logic Channel<br>(ICLC) Interrupt Status<br>Register (RIISR) | Ping Frame Response<br>successful (ICPSF) =0b1<br>(Continue initialization)<br>or Ping Response Failed<br>(ICPFF) = 0b1 (If fail,<br>restart loop) |

| End of \ | Wait for succes                                          | sful Slave communication loop                                                                                                                                                                                                                                                   |                                                                                           |                                                                                                                                                    |

| 17       | Clear the<br>Ping Frame<br>Request<br>Successful<br>flag | Clear ICPSF                                                                                                                                                                                                                                                                     | Receive Interface<br>Control Logic Channel<br>(ICLC) Interrupt Status<br>Register (RIISR) | Ping Frame Response<br>successful (ICPSF) = 1 =<br>clear the response status                                                                       |

| Speed I  | Node Change                                              |                                                                                                                                                                                                                                                                                 | •                                                                                         |                                                                                                                                                    |

| 18       | Begin<br>change to<br>high speed<br>mode                 | Write PLLCR[SWPON] = 1 to enable the LFAST masters PLL                                                                                                                                                                                                                          | LFAST PLL Control<br>Register (PLLCR)                                                     | Software signal to turn<br>on the PLL (SWPON) =<br>0b1                                                                                             |

| 19       | Wait for PLL<br>to relock                                | Wait for PLL disable signal to be negated and<br>wait for PLL lock by confirming:<br>• PLLLSR[PLLDIS] = 0<br>• then PLLLSR[PLDCR] = 1                                                                                                                                           | LFAST PLL and LVDS<br>Status Register<br>(LFAST_PLLLSR)                                   | PLL disable Status<br>(PLLDIS) = 0 = PLL<br>disable signal is<br>negated.                                                                          |

|          |                                                          |                                                                                                                                                                                                                                                                                 |                                                                                           | PLL Lock Delay Counter<br>Ready (PLDCR) = 1 =<br>PLL Lock delay counter<br>is decremented to 0                                                     |

| 20       | Start PLL<br>frame                                       | Write ICLC start PLL frame, ICR[ICLCPLD] = 02h                                                                                                                                                                                                                                  | ICLC Control Register<br>(ICR)                                                            | ICLC Payload<br>(ICLCPLD) = 0x02 =<br>Start PLL in preparation<br>for High Speed mode                                                              |

| 21       | Initiate<br>transfer of<br>ICLC frame                    | Write ICR[SNDICLC] = 1                                                                                                                                                                                                                                                          | ICLC Control Register<br>(ICR)                                                            | ICLC Frame request<br>(SNDICLC) = 0b1 =<br>initiate the transfer of an<br>ICLC frame                                                               |

| 22       | ICLC occurrence of one of the following                  | The ICLC transmission is confirmed by occurrence of one of the following: <ul> <li>ICR[SNDICLC] = 0</li> </ul>                                                                                                                                                                  | ICLC Control Register<br>(ICR)                                                            | ICLC Frame request<br>(SNDICLC) = 0b0 Frame<br>transmitted                                                                                         |

|          |                                                          | <ul> <li>TISR[TXICLCF] = 1</li> </ul>                                                                                                                                                                                                                                           | Transmit Interrupt Status<br>Register (TISR)                                              | Transmit ICLC Frame<br>transmitted Interrupt<br>(TXICLCF) = 0b1                                                                                    |

Table 12.

LFAST Master mode configuration (continued)

Table continues on the next page...

| Step | Description                                        | RM Operation                                                                                                                                                  | Registers <sup>1</sup>                       | Bits                                                                                 |

|------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------|

| 23   | Clear<br>TXICLCF                                   | Write TISR[TXICLCF] = 1                                                                                                                                       | Transmit Interrupt Status<br>Register (TISR) | Transmit ICLC Frame<br>transmitted Interrupt<br>(TXICLCF) = 0b1                      |

| 24   | <b>0</b>                                           |                                                                                                                                                               | ICLC Control Register<br>(ICR)               | ICLC Payload<br>(ICLCPLD) = 0x10 =<br>Select Receive Data<br>Fast frame              |

|      |                                                    |                                                                                                                                                               |                                              | ICLC Frame request<br>(SNDICLC) = 0b1 =<br>initiate the transfer of an<br>ICLC frame |

| 25   | Confirm<br>ICLC<br>transmission                    | The ICLC transmission is confirmed by the occurrence of one of the following:<br>• ICR[SNDICLC] = 0                                                           | ICLC Control Register<br>(ICR)               | ICLC Frame request<br>(SNDICLC) = 0b0 Frame<br>transmitted                           |

|      |                                                    | <ul> <li>TISR[TXICLCF] = 1</li> </ul>                                                                                                                         | Transmit Interrupt Status<br>Register (TISR) | Transmit ICLC Frame<br>transmitted Interrupt<br>(TXICLCF) = 0b1                      |

| 26   | Clear<br>TXICLCF                                   | Write TISR[TXICLCF] = 1                                                                                                                                       | Transmit Interrupt Status<br>Register (TISR) | Transmit ICLC Frame<br>transmitted Interrupt<br>(TXICLCF) = 0b1                      |

| 27   | Enable<br>transmit fast<br>frames                  | To change LFAST master's Transmit interface<br>speed both of the following operations are<br>performed:<br><b>Note:</b> (The slaves Rx interface speed should | ICLC Control Register<br>(ICR)               | ICLC Payload<br>(ICLCPLD) = 0x10 =<br>Select Transmit Data<br>Fast frame             |

|      |                                                    | <ul> <li>Write ICR[ICLCPLD] = 10h for Tx data fast frame</li> <li>Write ICR[SNDICLC] = 1</li> </ul>                                                           |                                              | ICLC Frame request<br>(SNDICLC) = 0b1 =<br>initiate the transfer of an<br>ICLC frame |

| 28   | Confirm<br>ICLC<br>transmission                    | The ICLC transmission is confirmed by the occurrence of one of the following:<br>• ICR[SNDICLC] = 0                                                           | ICLC Control Register<br>(ICR)               | ICLC Frame request<br>(SNDICLC) = 0b0 Frame<br>transmitted                           |

|      |                                                    | <ul> <li>TISR[TXICLCF] = 1</li> </ul>                                                                                                                         | Transmit Interrupt Status<br>Register (TISR) | Transmit ICLC Frame<br>transmitted Interrupt<br>(TXICLCF) = 0b1                      |

| 29   | Clear<br>TXICLCF                                   | Write TISR[TXICLCF] = 1                                                                                                                                       | Transmit Interrupt Status<br>Register (TISR) | Transmit ICLC Frame<br>transmitted Interrupt<br>(TXICLCF) = 0b1                      |

| 30   | Clear<br>ICLCSEQ                                   | Write ICR[ICLCSEQ] = 0 to be able to set the TDR bit                                                                                                          | ICLC Control Register<br>(ICR)               | ICLC enabled<br>(ICLCSEQ) = 0                                                        |

| 31   | Change<br>LFAST<br>master Rx<br>interface<br>speed | Write SCR[TDR] = 1 to change the LFAST<br>masters Tx interface speed.                                                                                         | Speed Control Register<br>(SCR)              | Transmit Data Rate<br>(TDR) = 0b1 = High<br>speed (320 Mb/s)                         |

| 32   | Change<br>LFAST<br>master Rx                       | Write SCR[RDR] = 1 to change the LFAST<br>masters Rx interface speed                                                                                          | Speed Control Register<br>(SCR)              | Receive Data Rate<br>(TDR) = 0b1= High<br>speed (320 Mb/s)                           |

### Table 12. LFAST Master mode configuration (continued)

Table continues on the next page...

டாகல்T configuration