## **Freescale Semiconductor**

APR23/D

# Using the DSP56300 Direct Memory Access Controller

by

Eliezer Sand

Freescale Semiconductor Israel Ltd.

#### How to Reach Us:

#### Home Page:

www.freescale.com

#### E-mail:

support@freescale.com

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd.

Technical Information Center

2 Dai King Street

Tai Po Industrial Estate

Tai Po, N.T., Hong Kong

+800 2666 8080

support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405

Denver, Colorado 80217 1-800-441-2447 or 303-675-2140

Fax: 303-675-2150

$LDCF or Free scale Semiconductor@\,hibbert group.com$

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document. Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

## **TABLE OF CONTENTS**

| 1.1<br>1.2                                                                   | OVERVI                                                                                                                                                                                                                      | INTRODUCTION                                                                                                                                                                                                  | 1-3                                                                |

|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| SECTIO<br>2.1                                                                |                                                                                                                                                                                                                             | <b>DMA USAGE BASIC EXAMPLES</b> ERRING FROM X MEMORY TO Y MEMORY                                                                                                                                              |                                                                    |

| 2.2<br>2.3                                                                   |                                                                                                                                                                                                                             | OADING FROM EXTERNAL MEMORY                                                                                                                                                                                   |                                                                    |

|                                                                              |                                                                                                                                                                                                                             | MULTI-DIMENSIONAL DMA TRANSFERS                                                                                                                                                                               |                                                                    |

| 3.1                                                                          |                                                                                                                                                                                                                             | MENSIONAL (2D) TRANSFER                                                                                                                                                                                       |                                                                    |

| 3.2                                                                          |                                                                                                                                                                                                                             | DIMENSIONAL (3D) TRANSFER                                                                                                                                                                                     |                                                                    |

| 3.3                                                                          | EXAMPL                                                                                                                                                                                                                      | LES FOR OTHER ADDRESS TYPES                                                                                                                                                                                   | 3-5                                                                |

| 3.3.1                                                                        |                                                                                                                                                                                                                             | ar Buffer Using 2D Addressing                                                                                                                                                                                 |                                                                    |

| 3.3.2                                                                        |                                                                                                                                                                                                                             | fers with Equidistant Offset                                                                                                                                                                                  |                                                                    |

| 3.3.3                                                                        | Transf                                                                                                                                                                                                                      | ferring Data for 3D ESSI Transmitters                                                                                                                                                                         | 3-6                                                                |

|                                                                              |                                                                                                                                                                                                                             |                                                                                                                                                                                                               |                                                                    |

| SECTIO                                                                       |                                                                                                                                                                                                                             | OPERATION OF MULTIPLE DMA CHANNELS                                                                                                                                                                            |                                                                    |

| SECTIO<br>4.1                                                                | INTROD                                                                                                                                                                                                                      | UCTION                                                                                                                                                                                                        | 4-3                                                                |

|                                                                              | INTRODI<br>COLOR                                                                                                                                                                                                            | UCTION                                                                                                                                                                                                        | 4-3<br>4-3                                                         |

| 4.1                                                                          | INTRODI<br>COLOR                                                                                                                                                                                                            | UCTION                                                                                                                                                                                                        | 4-3<br>4-3                                                         |

| 4.1<br>4.2                                                                   | INTRODI<br>COLOR (<br>PRIORIT<br>COLOR (                                                                                                                                                                                    | UCTION                                                                                                                                                                                                        | 4-3<br>4-3<br>4-5<br>4-6                                           |

| 4.1<br>4.2<br>4.3                                                            | INTRODI<br>COLOR (<br>PRIORIT<br>COLOR (                                                                                                                                                                                    | UCTION                                                                                                                                                                                                        | 4-3<br>4-3<br>4-5<br>4-6                                           |

| 4.1<br>4.2<br>4.3<br>4.4                                                     | INTRODI<br>COLOR (<br>PRIORIT<br>COLOR (<br>CONTINI                                                                                                                                                                         | UCTION                                                                                                                                                                                                        | 4-3<br>4-5<br>4-6<br>4-8                                           |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5                                              | INTRODIC<br>COLOR (<br>PRIORIT<br>COLOR (<br>CONTINI                                                                                                                                                                        | UCTION                                                                                                                                                                                                        | 4-3<br>4-5<br>4-6<br>4-8<br><b>5-1</b>                             |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5                                              | INTRODIC COLOR (CONTINUE)  N 5 CONTEN                                                                                                                                                                                       | UCTION  COMPRESSION EXAMPLE 1  TES BETWEEN CHANNELS  COMPRESSION EXAMPLE 2  UOUS MODE  DMA AND CORE CONTENTION                                                                                                | 4-3<br>4-5<br>4-6<br>4-8<br><b>5-1</b><br>5-3                      |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br><b>SECTIO</b><br>5.1                      | INTRODIC COLOR (CONTINUE)  N 5 CONTEN                                                                                                                                                                                       | UCTION COMPRESSION EXAMPLE 1 TIES BETWEEN CHANNELS COMPRESSION EXAMPLE 2 UOUS MODE  DMA AND CORE CONTENTION NTION FOR INTERNAL MEMORY                                                                         | 4-3<br>4-5<br>4-6<br>4-8<br><b>5-1</b><br>5-3<br>5-3               |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br><b>SECTIO</b><br>5.1<br>5.2               | INTRODIC COLOR (CONTINUE)  N 5 CONTENT CONTENT CONTENT CONTENT CONTENT PRIORIT                                                                                                                                              | UCTION                                                                                                                                                                                                        | 4-3<br>4-5<br>4-6<br>4-8<br><b>5-1</b><br>5-3<br>5-3               |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br><b>SECTIO</b><br>5.1<br>5.2<br>5.3        | INTRODIC COLOR (CONTINUE)  N 5 CONTENT CONTENT CONTENT PRIORIT PACKING                                                                                                                                                      | UCTION COMPRESSION EXAMPLE 1 TES BETWEEN CHANNELS COMPRESSION EXAMPLE 2 UOUS MODE  DMA AND CORE CONTENTION NTION FOR INTERNAL MEMORY NTION FOR PERIPHERAL REGISTERS TIES ON EXTERNAL ACCESS                   | 4-3<br>4-5<br>4-6<br>4-8<br><b>5-1</b><br>5-3<br>5-3<br>5-5        |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br><b>SECTIO</b><br>5.1<br>5.2<br>5.3<br>5.4 | INTRODIC COLOR (CONTINUE)  N 5 CONTENCONTENCONTENCONTENCONTENCONTENCONTENCONTENCONTENCONTENCONTENCONTENCONTENCONTENCONTENCONTENCONTENCONTENCONTENCONTENCONTENCONTENCONTENCONTENCONTENCONTENCONTENCONTENCONTENCONTENCONTENCO | UCTION COMPRESSION EXAMPLE 1 TIES BETWEEN CHANNELS COMPRESSION EXAMPLE 2 UOUS MODE  DMA AND CORE CONTENTION NTION FOR INTERNAL MEMORY NTION FOR PERIPHERAL REGISTERS TIES ON EXTERNAL ACCESS G/UNPACKING MODE | 4-3<br>4-5<br>4-6<br>4-8<br><b>5-1</b><br>5-3<br>5-3<br>5-5<br>5-6 |

| 5.8   | STOP    | INSTRUCTION                                | 5-8  |

|-------|---------|--------------------------------------------|------|

| 5.9   | DEBU    | G MODE                                     | 5-8  |

| SECTI | ON 6    | HI32 DMA OPERATION                         | 6-1  |

| 6.1   | INTRO   | DUCTION                                    | 6-3  |

| 6.2   | HI32 II | N UNIVERSAL BUS MODE                       | 6-3  |

| 6.2.1 | HI3     | 2 DSP Side Registers in Universal Bus Mode | 6-3  |

| 6.2.2 | HI3     | 2 DMA Operation in Universal Bus Mode      | 6-4  |

| 6.2.3 | DM.     | A Code Example—HI32 in UB Mode             | 6-5  |

| 6.3   | HI32 II | N PCI BUS MODE                             | 6-9  |

| 6.3.1 | HI3     | 2 DSP Side Registers in PCI Bus Mode       | 6-9  |

| 6.3.2 | HI3     | 2 DMA Operation in PCI Mode                | 6-10 |

| 633   | DM.     | A Code Example—HI32 in PCI Bus Mode        | 6-11 |

## **LIST OF FIGURES**

| Figure 3-1 | Linear to 2D Transfer                                            |

|------------|------------------------------------------------------------------|

| Figure 3-2 | 3D to 2D Transfer                                                |

| Figure 4-1 | Screen Memory Representation                                     |

| Figure 4-2 | Transfer from System Memory to Screen Memory 4-4                 |

| Figure 4-3 | Example of Multi-channel Operation                               |

| Figure 4-4 | QCIF Block Transfer Example4-7                                   |

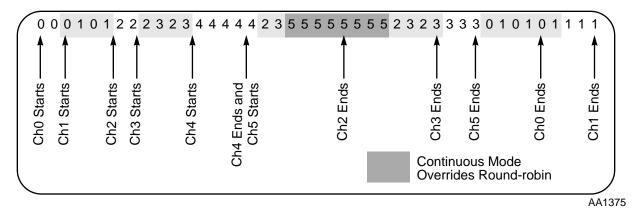

| Figure 4-5 | Example of Multi-channel Operation with Continuous Mode 4-8      |

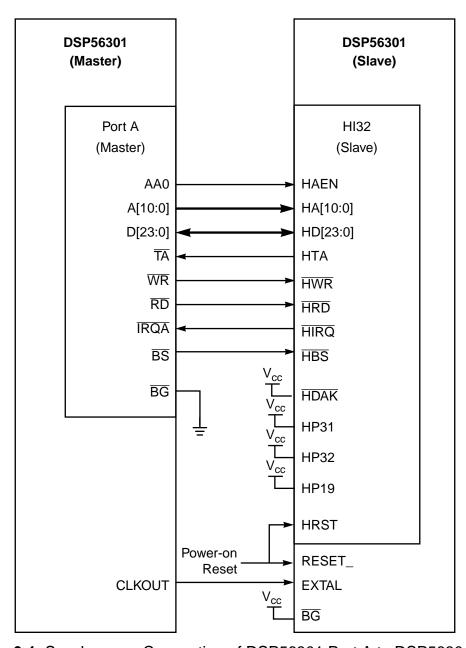

| Figure 6-1 | Synchronous Connection of DSP56301 Port A to DSP56301 HI32 . 6-7 |

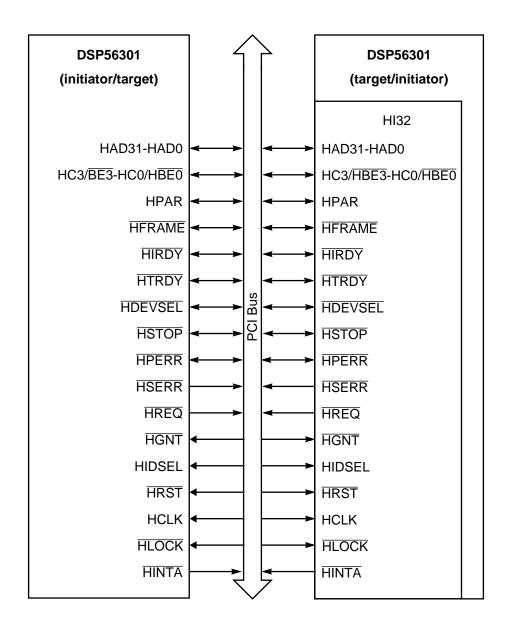

| Figure 6-2 | Connection of DSP56301 to PCI Bus 6-12                           |

## **LIST OF TABLES**

| Table 1-1 | DMA Controller Data Transfers    | 3 |

|-----------|----------------------------------|---|

| Table 1-2 | DMA Control Register Structure1- | 4 |

| Table 1-3 | DMA Counter Structure            | 8 |

| Table 1-4 | DMA Status Register Structure    | 9 |

# SECTION 1 INTRODUCTION

The Direct Memory Access (DMA) controller is the part of the DSP56300 core that permits data transfers between internal or external memory and/or internal or external I/O in any combination, without intervention of the core. Due to dedicated DMA address and data buses, as well as internal memory partitioning, a high level of isolation is achieved so that the DMA operation does not interfere with or slow down the core operation.

| 1.1 | OVERVIEW      | .1-3 |

|-----|---------------|------|

| 1.2 | DMA REGISTERS | .1-3 |

Overview

## 1.1 OVERVIEW

Because the DMA controller is part of the DSP56300 core, the Bus Interface Unit (BIU) receives all the needed controls from the DMA controller and can manage external activity with maximum flexibility and performance, depending on the profile of the tasks to be handled. The DMA controller has six channels, each with its own register set. All the registers are memory-mapped in the internal I/O memory space. **Table 1-1** shows the various types of data transfers the DMA controller can perform.

**Table 1-1** DMA Controller Data Transfers

| Location (      | Minimum Clock<br>Cycles per Single<br>Word Transfer |                 |                 |

|-----------------|-----------------------------------------------------|-----------------|-----------------|

| Internal Memory | $\rightarrow$                                       | Internal Memory | 2               |

| External Memory | $\leftrightarrow$                                   | Internal Memory | 2 + wait states |

| External Memory | $\rightarrow$                                       | External Memory | 2 + wait states |

| Internal Memory | $\leftrightarrow$                                   | Internal I/O    | 2               |

| External Memory | $\leftrightarrow$                                   | Internal I/O    | 2 + wait states |

| Internal I/O    | $\rightarrow$                                       | Internal I/O    | 2               |

Data transfer for one channel takes a minimum of 2 clock cycles per single word. The number of clocks per transfer can be larger if there is a contention between the core and the DMA activity (i.e., if they both access the same 1/4 K of internal RAM in the same cycle (or three cycles in Packing mode—see **Section 5.4** on page 5-5), or, if they both want to access external memory).

## 1.2 DMA REGISTERS

The DMA has six identical channels. Each channel has four dedicated registers:

- **DSR***i* —DMA Source Register for channel *i* which holds the source base address for the next DMA transfer

- **DDR***i* —DMA Destination Register for channel *i* which holds the destination base address for the next DMA transfer

- **DCO***i* —DMA Counter for channel *i* which contains the number of DMA transfers left to perform

- **DCR***i* —DMA Control Register for channel *i* which contains all the bits needed to control the operation of the channel

## **DMA Registers**

In addition to these channel-dedicated registers, there are also five common registers. The common registers include four DMA Offset Registers (DOR0, DOR1, DOR2, and DOR3) and one read-only DMA Status Register (DSTR). The DORs hold offset addresses to be used by any of the channels, as required, in specific addressing modes.

- **Table 1-2** describes the function of DMA Control Register (DCR) bits.

- **Table 1-3** on page 1-8 describes the different modes of the DMA Counter (DCO) which are selected by the addressing mode defined in the DCR.

- Table 1-4 on page 1-9 describes the structure of the read only DSTR.

**Table 1-2** DMA Control Register Structure

| Bit<br>No. | Bit<br>Names | Value    | Function                                                                                                                                                                                |                                                                   |                                                                       |          |                                                                      |          |          |     |                                                                   |

|------------|--------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------|----------|----------------------------------------------------------------------|----------|----------|-----|-------------------------------------------------------------------|

|            |              |          | Clearing the bit disables DMA transfers on this channel.                                                                                                                                |                                                                   |                                                                       |          |                                                                      |          |          |     |                                                                   |

| 23         | DE           | 1        | Setting the bit initiates a transfer, or enables the initiation of a transfer by another source (e.g., by external interrupt).                                                          |                                                                   |                                                                       |          |                                                                      |          |          |     |                                                                   |

| 22         | DIE          | 0        | Clearing this bit disables the interrupt-at-end-of-transfer function for this channel.                                                                                                  |                                                                   |                                                                       |          |                                                                      |          |          |     |                                                                   |

| 22         | DIE          | 1        | Setting the bit enables the interrupt-at-end-of-transfer function for this channel.                                                                                                     |                                                                   |                                                                       |          |                                                                      |          |          |     |                                                                   |

|            |              | _        | <ul> <li>These bits define:</li> <li>Transfer mode: Block, line or word per request</li> <li>Trigger source: DMA request or DE with/without DE auto clear at end-of-transfer</li> </ul> |                                                                   |                                                                       |          |                                                                      |          |          |     |                                                                   |

|            |              | 000      | This value selects a block transfer by request with DE auto clear.                                                                                                                      |                                                                   |                                                                       |          |                                                                      |          |          |     |                                                                   |

|            | DTM[2:0]     | DTM[2:0] | 001                                                                                                                                                                                     | This value selects a word transfer by request with DE auto clear. |                                                                       |          |                                                                      |          |          |     |                                                                   |

| 21–19      |              |          | DTM[2:0]                                                                                                                                                                                | DTM[2:0]                                                          | DTM[2:0]                                                              | DTM[2:0] | DTM[2:0]                                                             | DTM[2:0] | DTM[2:0] | 010 | This value selects a line transfer by request with DE auto clear. |

|            |              |          |                                                                                                                                                                                         | 011                                                               | This value selects a block transfer by DE with DE auto clear.         |          |                                                                      |          |          |     |                                                                   |

|            |              |          |                                                                                                                                                                                         | 100                                                               | This value selects a block transfer by request without DE auto clear. |          |                                                                      |          |          |     |                                                                   |

|            |              |          |                                                                                                                                                                                         |                                                                   |                                                                       | 101      | This value selects a word transfer by request without DE auto clear. |          |          |     |                                                                   |

|            |              | 110      | This value is not defined and is reserved.                                                                                                                                              |                                                                   |                                                                       |          |                                                                      |          |          |     |                                                                   |

|            |              | 111      | This value is not defined and is reserved.                                                                                                                                              |                                                                   |                                                                       |          |                                                                      |          |          |     |                                                                   |

|            |              | _        | These bits select the channel priority.                                                                                                                                                 |                                                                   |                                                                       |          |                                                                      |          |          |     |                                                                   |

|            |              | 00       | This value selects Priority Level 0 (lowest).                                                                                                                                           |                                                                   |                                                                       |          |                                                                      |          |          |     |                                                                   |

| 18–17      | DPR[1:0]     | 01       | This value selects Priority Level 1.                                                                                                                                                    |                                                                   |                                                                       |          |                                                                      |          |          |     |                                                                   |

|            |              | 10       | This value selects Priority Level 2.                                                                                                                                                    |                                                                   |                                                                       |          |                                                                      |          |          |     |                                                                   |

|            |              | 11       | This value selects Priority Level 3 (highest).                                                                                                                                          |                                                                   |                                                                       |          |                                                                      |          |          |     |                                                                   |

Introduction

**DMA Registers**

Table 1-2

DMA Control Register Structure (Continued)

| Bit<br>No. | Bit<br>Names | Value | Function                                                   |  |  |  |  |  |       |                              |

|------------|--------------|-------|------------------------------------------------------------|--|--|--|--|--|-------|------------------------------|

| 16         | DCON         | 0     | Clearing this bit disables Continuous mode.                |  |  |  |  |  |       |                              |

| 10         | DCON         | 1     | Setting this bit enables Continuous mode for this channel. |  |  |  |  |  |       |                              |

|            |              | _     | These bits identify the DMA request source.                |  |  |  |  |  |       |                              |

|            |              | 00000 | External (IRQA pin)                                        |  |  |  |  |  |       |                              |

|            |              | 00001 | External (IRQB pin)                                        |  |  |  |  |  |       |                              |

|            |              | 00010 | External (IRQC pin)                                        |  |  |  |  |  |       |                              |

|            |              | 00011 | External (IRQD pin)                                        |  |  |  |  |  |       |                              |

|            |              | 00100 | Transfer Done from channel 0                               |  |  |  |  |  |       |                              |

| 15–11      | DRS[4:0]     | 00101 | Transfer Done from channel 1                               |  |  |  |  |  |       |                              |

|            |              | 00110 | Transfer Done from channel 2                               |  |  |  |  |  |       |                              |

|            |              | 00111 | Transfer Done from channel 3                               |  |  |  |  |  |       |                              |

|            |              | 01000 | Transfer Done from channel 4                               |  |  |  |  |  |       |                              |

|            |              |       |                                                            |  |  |  |  |  | 01001 | Transfer Done from channel 5 |

|            |              |       | Peripheral Request MDRQ0–Peripheral Request MDRQ21         |  |  |  |  |  |       |                              |

|            |              | 11111 |                                                            |  |  |  |  |  |       |                              |

| 10         | D3D          | 0     | Clearing this bit disables 3D mode.                        |  |  |  |  |  |       |                              |

| 10         | 1            |       | Setting this bit enables 3D mode.                          |  |  |  |  |  |       |                              |

## nu oduction

**DMA Registers**

## Freescale Semiconductor, Inc.

**Table 1-2** DMA Control Register Structure (Continued)

| Bit<br>No. | Bit<br>Names | Value                                | Function                                                  |              |                 |    |     |

|------------|--------------|--------------------------------------|-----------------------------------------------------------|--------------|-----------------|----|-----|

|            |              | $\mathbf{If}\mathbf{D}3\mathbf{D}=0$ |                                                           |              |                 |    |     |

|            |              | _                                    | Destination<br>Addressing Mode                            | Counter Mode | Offset Select   |    |     |

|            |              | 000                                  | Two-dimensional                                           | В            | DOR0            |    |     |

|            |              | 001                                  | Two-dimensional                                           | В            | DOR1            |    |     |

|            |              | 010                                  | Two-dimensional                                           | В            | DOR2            |    |     |

|            |              | 011                                  | Two-dimensional                                           | В            | DOR3            |    |     |

|            |              | 100                                  | No Update                                                 | A            | None            |    |     |

|            |              | 101                                  | Postincrement-by-1                                        | A            | None            |    |     |

|            |              | 110                                  | Reserved                                                  |              |                 |    |     |

|            |              | 111                                  | 111 Reserved                                              |              |                 |    |     |

| 9–7        | DAM[5:3]     |                                      | f the destination address ยุ<br>han the source address ge |              |                 |    |     |

|            |              |                                      | If D3D = 1                                                |              |                 |    |     |

|            |              | _                                    | Destination<br>Addressing Mode                            | Offset       | Select          |    |     |

|            |              | 000                                  | Two-dimensional                                           | DC           | ORO             |    |     |

|            |              | 001                                  | Two-dimensional                                           | DC           | PR1             |    |     |

|            |              |                                      |                                                           | 010          | Two-dimensional | DC | DR2 |

|            |              | 011                                  | Two-dimensional                                           | DOR3         |                 |    |     |

|            |              | 100                                  | No Update                                                 | No           | one             |    |     |

|            |              | 101                                  | Postincrement-by-1                                        | No           | one             |    |     |

|            |              | 110                                  | Three-dimensional                                         | DOR0:        | DOR1            |    |     |

|            |              | 111                                  | Three-dimensional                                         | DOR2: DOR3   |                 |    |     |

**DMA Registers**

Table 1-2

DMA Control Register Structure (Continued)

| Bit<br>No. | Bit<br>Names | Value                       | re Function                                                                                                                                        |              |                      |  |  |

|------------|--------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------------|--|--|

|            |              | $\mathbf{If}\mathbf{D3D}=0$ |                                                                                                                                                    |              |                      |  |  |

|            |              | _                           | Source Addressing<br>Mode                                                                                                                          | Counter Mode | Offset Select        |  |  |

|            |              | 000                         | Two-dimensional                                                                                                                                    | В            | DOR0                 |  |  |

|            |              | 001                         | Two-dimensional                                                                                                                                    | В            | DOR1                 |  |  |

|            |              | 010                         | Two-dimensional                                                                                                                                    | В            | DOR2                 |  |  |

|            |              | 011                         | Two-dimensional                                                                                                                                    | В            | DOR3                 |  |  |

|            |              | 100                         | No Update                                                                                                                                          | A            | None                 |  |  |

|            |              | 101                         | Postincrement-by-1                                                                                                                                 | A            | None                 |  |  |

|            |              | 110                         |                                                                                                                                                    | Reserved     |                      |  |  |

|            |              | 111                         |                                                                                                                                                    | Reserved     |                      |  |  |

|            |              |                             | If the source address generation mode specifies a different counter mode that the destination address generation mode, then the counter mode is B. |              |                      |  |  |

|            |              | If D3D = 1                  |                                                                                                                                                    |              |                      |  |  |

|            |              | _                           | Addressing Mode                                                                                                                                    | Counter Mode | Offset Select        |  |  |

| 6-4        | DAM[2:0]     | M[2:0] 000                  | Source: 3D                                                                                                                                         | C            | Source: DOR0:DOR1    |  |  |

|            |              |                             | Dest: See DAM[5:3]                                                                                                                                 | С            | Dest: See DAM[5:3]   |  |  |

|            |              | 001                         | Source: 3D                                                                                                                                         | D            | Source: DOR0:DOR1    |  |  |

|            |              | 001                         | Dest: See DAM[5:3]                                                                                                                                 | D            | Dest: See DAM[5:3]   |  |  |

|            |              | 010                         | Source: 3D                                                                                                                                         | E            | Source: DOR0:DOR1    |  |  |

|            |              | 010                         | Dest: See DAM[5:3]                                                                                                                                 | £            | Dest: See DAM[5:3]   |  |  |

|            |              | 011                         | Source: 3D                                                                                                                                         | Dogowyod     | Source: DOR0:DOR1    |  |  |

|            |              | 011                         | Dest: See DAM[5:3]                                                                                                                                 | Reserved     | Dest: See DAM[5:3]   |  |  |

|            |              | 100                         | Source: See DAM[5:3]                                                                                                                               | С            | Source: See DAM[5:3] |  |  |

|            |              | 100                         | Destination: 3D                                                                                                                                    | C            | Dest: DOR2:DOR3      |  |  |

|            |              | 101                         | Source: See DAM[5:3]                                                                                                                               | D            | Source: See DAM[5:3] |  |  |

|            |              | 101                         | Destination: 3D                                                                                                                                    | <u>.</u>     | Dest: DOR2:DOR3      |  |  |

|            |              | 110                         | Source: See DAM[5:3]                                                                                                                               | E            | Source: See DAM[5:3] |  |  |

|            |              | 110                         | Destination: 3D                                                                                                                                    | <u> </u>     | Dest: DOR2:DOR3      |  |  |

|            |              | 111                         | Source: See DAM[5:3]                                                                                                                               | Reserved     | Source: See DAM[5:3] |  |  |

|            |              |                             | Destination: 3D                                                                                                                                    | weser veu    | Dest: DOR2:DOR3      |  |  |

## **DMA Registers**

Table 1-2 DMA Control Register Structure (Continued)

| Bit<br>No. | Bit<br>Names | Value | Function                                                                                                                  |  |

|------------|--------------|-------|---------------------------------------------------------------------------------------------------------------------------|--|

|            |              | _     | These bits select the destination memory (X data, Y data, or program).                                                    |  |

|            |              | 00    | X Memory Space                                                                                                            |  |

|            |              | 01    | Y Memory Space                                                                                                            |  |

| 3–2        | DDS[1:0]     | 10    | P Memory Space                                                                                                            |  |

|            |              | 11    | Reserved                                                                                                                  |  |

|            |              |       | In Cache mode, a DMA-to-program memory space has some limitations (as described in the <i>DSP56300 Family Manual</i> ).   |  |

|            |              | _     | These bits select the source memory (X data, Y data, or program).                                                         |  |

|            |              | 00    | X Memory Space                                                                                                            |  |

|            |              | 01    | Y Memory Space                                                                                                            |  |

| 1–0        | DSS{1:0]     | 10    | P Memory Space                                                                                                            |  |

|            |              | 11    | Reserved                                                                                                                  |  |

|            |              |       | In Cache mode, a DMA-from-program memory space has some limitations (as described in the <i>DSP56300 Family Manual</i> ). |  |

Table 1-3

DMA Counter Structure

| Addressing | Bit Structure Description |           |      |      |  |  |  |

|------------|---------------------------|-----------|------|------|--|--|--|

| Mode       | 23 18                     | 3 17 12   | 11 6 | 5 0  |  |  |  |

| No update  |                           | Not used  |      |      |  |  |  |

| Linear     |                           | DCO       |      |      |  |  |  |

| 2D         | De                        | СОН       | DCOL |      |  |  |  |

| 3D mode C  | DCOH DCOM DCC             |           |      |      |  |  |  |

| 3D mode D  | DCOH                      | DC        | COM  | DCOL |  |  |  |

| 3D mode E  | DCOH                      | DCOM DCOL |      |      |  |  |  |

Note: In No Update mode, the counter is not used. In Linear mode, the counter is used as a single register. In 2D mode, the counter is used as two registers DCOH and DCOL. In 3D mode, the counter is used as three registers DCOH, DCOM, and DCOL which can be different lengths, depending on the selected mode (i.e., C, D, or E).

**DMA Registers**

Table 1-4

DMA Status Register Structure

| Bit No. | Bit<br>Names             | Value | Function                                                     |  |

|---------|--------------------------|-------|--------------------------------------------------------------|--|

| 23-12   | These bits are reserved. |       |                                                              |  |

|         |                          | _     | These bits identify the active channel number                |  |

|         |                          | 000   | DMA Channel 0                                                |  |

|         |                          | 001   | DMA Channel 1                                                |  |

|         |                          | 010   | DMA Channel 2                                                |  |

| 11-9    | DCH[2:0]                 | 011   | DMA Channel 3                                                |  |

|         |                          | 100   | DMA Channel 4                                                |  |

|         |                          | 101   | DMA Channel 5                                                |  |

|         |                          | 110   | reserved                                                     |  |

|         |                          | 111   | reserved                                                     |  |

| 8       | DACT                     | 0     | The active DMA channel is disabled or awaiting DMA requests. |  |

|         |                          | 1     | The active DMA channel is performing a transfer.             |  |

| 7–6     | These bits are reserved. |       |                                                              |  |

| ۲       | DTD5                     | 0     | DMA channel 5 has not completed a transfer.                  |  |

| 5       |                          | 1     | DMA channel 5 has completed all requested transfers.         |  |

| 4       | DTD4                     | 0     | DMA channel 4 has not completed a transfer.                  |  |

| 4       |                          | 1     | DMA channel 4 has completed all requested transfers.         |  |

| 9       | DTD9                     | 0     | DMA channel 3 has not completed a transfer.                  |  |

| 3       | DTD3                     | 1     | DMA channel 3 has completed all requested transfers.         |  |

| 9       | DTD0                     | 0     | DMA channel 2 has not completed a transfer.                  |  |

| 2       | DTD2                     | 1     | DMA channel 2 has completed all requested transfers.         |  |

| 1       | DTD1                     | 0     | DMA channel 1 has not completed a transfer.                  |  |

|         | DTD1                     | 1     | DMA channel 1 has completed all requested transfers.         |  |

| 0       | DTD0                     | 0     | DMA channel 0 has not completed a transfer.                  |  |

| 0       |                          | 1     | DMA channel 0 has completed all requested transfers.         |  |

**DMA Registers**

<del>dsp</del>

# SECTION 2 DMA USAGE BASIC EXAMPLES

These examples show the simplest use of one DMA channel. They assume no interference from other sources, such as other DMA channels, contentions with the core, etc.

אויוע Usage Basic Examples

|   | )  |   |  |

|---|----|---|--|

|   | ı  |   |  |

|   | ı  |   |  |

|   | ı  |   |  |

|   |    |   |  |

|   | -  | P |  |

|   | ŀ  |   |  |

|   | )  |   |  |

| i | į  |   |  |

| ì | h  |   |  |

| Ì | Į  |   |  |

|   |    |   |  |

|   |    |   |  |

|   | 5  |   |  |

|   | ı  |   |  |

|   | ı  |   |  |

|   | )  |   |  |

| ĺ | h  |   |  |

| j | J  |   |  |

|   |    |   |  |

|   |    |   |  |

|   | i  |   |  |

| Ì | ı. |   |  |

| ĺ | 7  |   |  |

|   | )  |   |  |

| 9 |    |   |  |

| ļ | h  |   |  |

| ĺ | ,  |   |  |

|   |    |   |  |

|   | ١. |   |  |

| ĺ | h  |   |  |

| 2.1 | TRANSFERRING FROM X MEMORY TO Y MEMORY | .2-3 |

|-----|----------------------------------------|------|

| 2.2 | DOWNLOADING FROM EXTERNAL MEMORY       | .2-4 |

| 2.3 | GETTING DATA FROM THE ESSI RECEIVER    | .2-5 |

**DMA Usage Basic Examples**

Transferring from X Memory to Y Memory

#### 2.1 TRANSFERRING FROM X MEMORY TO Y MEMORY

The following code causes DMA channel 0 to transfer a block of N words linearly from X internal memory to Y internal memory.

```

#$source_addr,x:M_DSR0

movep

#$dest_addr,x:M_DDR0

movep

#$(N-1),x:M_DCO0

; # of words to be transferred

movep

#$9802d4,x:M_DCR0

; software-triggered,

movep

; x linear -> y linear

; due to core pipeline

nop

nop

; polling of DTD0

jclr

#0,x:M DSTR,*

```

In this code, the value written to DSR0 is the address of the first data item to be transferred. The value written to DDR0 is the target address of the first data item to be transferred.

It is not necessary to specify that the address is internal. **Note:**

The DMA hardware evaluates this information automatically according to the specific DSP56300 family member memory map. The number of transfers to perform (N) is (DCO + 1); therefore, the value written to DCO0 is (N - 1).

The content of DCR0 is as follows:

- 1. DE = 1 (i.e., start a transfer)

- 2. **DIE** = **0** (i.e., disable an interrupt to the core at end of block)

- 3. **DTM = 011** (i.e., block transfer triggered by DE—Software-triggered mode)

- 4. **DPR** = **00** (i.e., the priority level is zero—the lowest one)

- 5. **DCON** = **0** (i.e., the continuous mode is not activated)

- 6. **DRS** = **00000** (In Software-triggered mode, this field is ignored.)

- 7.  $\mathbf{D3D} = \mathbf{0}$  (i.e., non-three-dimensional mode)

- 8. **DAM = 101101** (i.e., source address is post-incremented by 1—Linear mode—and destination address is also Linear mode)

- 9. DDS = 01 (i.e., the destination space is Y memory)

- 10. **DSS** = 00 (i.e., the source space is X memory)

In this example, the core does not do anything while the DMA is transferring the block of data. The core polls the DTD bit of this channel and continues to execute the program after the DMA finishes transferring the data. Due to the chip pipeline, because the core

אויט Usage Basic Examples

### **Downloading from External Memory**

polls this bit until it equals 0, the chip must wait 2 clock cycles from the cycle in which DE is written until DTD is reset at the start of block transfer to indicate that the channel is busy. Another option is to poll the DACT bit (Bit 8) in the same DSTR until it is set. This bit indicates whether any DMA channel is actually transferring a data item. Because of the core and DMA pipelines, the core must wait 3 clock cycles (3 NOP instructions) until this bit is set and can be polled.

### 2.2 DOWNLOADING FROM EXTERNAL MEMORY

The example code presented in this section causes DMA channel 2 to transfer a block of N words linearly from external P memory to internal P memory. In this example, the trigger of the transfer is a request from Timer 0. This is an example of a program overlay in which the core works on a part of the program, while, in parallel, a DMA channel downloads another part of the program. It is common for an operating system to use a timer for scheduling such a DMA activity. In this example, the timer is programmed to use its most basic mode, and the DMA controller is programmed to generate a core interrupt at the end of transfer without clearing the DE bit. When the interrupt occurs, this code loads new parameters to the address registers to prepare them for the next download task that occurs when the next timer interrupt request occurs (i.e.,  $2 \times (\text{num\_comp})$  from the previous trigger). It doesn't matter whether the timer or the DMA is programmed first.

**Note:** The user must make sure that the program size N is smaller than the number of the timer cycles programmed in TCPR0. Otherwise, the DMA gets a new trigger before it finishes the previous task and ignores the new trigger.

| M_TCSR0 | EQU                   | \$ffff8f | ;DSP56301 Timer0 control/status reg.     |

|---------|-----------------------|----------|------------------------------------------|

| M_TLRO  | EQU                   | \$ffff8e | ;DSP56301 Timer0 load register           |

| M_TCPR0 | EQU                   | \$ffff8d | ;DSP56301 Timer0 compare register        |

|         |                       |          | ;                                        |

| bclr    | #9,SR                 |          | ; enable interrupt priority levels 3,2,1 |

| bset    | #17,x:M_I             | PRC      | enable DMA2 interrupt at priority        |

|         |                       |          | ;level 1                                 |

| movep   | #\$9,x:M_A            | ARO      | ;AARO indicates to all external P space  |

|         |                       |          | as static RAM                            |

| movep   | #\$1fffe2,x:M_BCR     |          | ;2 wait states in area 0 access          |

| movep   | #\$0,x:M <u>T</u> T   | LRO      | ; initial value of the timer counter     |

| movep   | #\$num_comp,x:M_TCPR0 |          | number of CLK/2 cycles until a trigger;  |

|         |                       |          | is generated;                            |

| movep   | #\$201,x:M            | _TCSR0   | ;TimerO enable at mode O + reload        |

| movep   | #\$ext_addr,x:M_DSR2  |          | external address;                        |

| movep   | #\$int_addr,x:M_DDR2  |          | ;internal address                        |

| movep   | #\$(N-1),x:M_DCO2     |          | ;N is number of words to ne downloaded   |

| movep   | #\$e082da,            | k:M_DCR2 | ;block transfer triggered by timer0      |

| • • •   |                       |          | ;p linear -> p linear                    |

### Getting Data from the ESSI Receiver

|        |           |                       | ;DE is not cleared at end of block ;interrupt is generated at the |

|--------|-----------|-----------------------|-------------------------------------------------------------------|

|        | •••       |                       | end of block                                                      |

|        |           |                       | ; channel priority 0 (doesn't matter in                           |

|        |           |                       | ;the example)                                                     |

|        | org p:I_1 | DMA2                  |                                                                   |

| I_DMA2 | movep     | (pointer1),x:M_DSR2   | ;interrupt routine: prepare parameters                            |

|        | movep     | $(pointer2),x:M_DDR2$ | ;for next download                                                |

Note:

Basically, the core can transfer a block of data from one memory space to another one. If the transfer is in data memory, then the DMA transfer saves core MIPS, but uses the same time (for transfer to/from peripheral the core does the transfer even faster using one cycle instead of two). For transfers to/from program space, however, the advantage of using the DMA is doubled, not only because it frees the core for other tasks, but also because it operates much faster. The DMA transfers a data item in 2 cycles, whereas the core must use a MOVEM instruction that takes 6 cycles.

#### **GETTING DATA FROM THE ESSI RECEIVER** 2.3

In the sample code provided in this section, DMA channel 5 is programmed to get data from the receiver of an ESSI peripheral. In this mode, the source address type must be No Update mode because the DMA reads the data register of the receiver and its address is constant. The data is transferred to a circular buffer in the internal X memory. In this example, the circular buffer is implemented using linear addressing; at the end of the buffer, an interrupt is issued and the DDR is re-programmed. The example in **Section 3.3.1** on page 3-5 shows an alternate way to implement a circular buffer with almost no intervention from the core.

Note:

In this example, the DMA works indefinitely regardless of the content of the counter DCO5, but the counter is used to generate an interrupt to the core in order to jump to the top of the buffer after it is filled. The ESSI can be initialized before or after the programming of the DMA channel.

| M_PCRD | EQU                | \$ffffaf | ;56301 Port D control register           |

|--------|--------------------|----------|------------------------------------------|

| M_RX1  | EQU                | \$ffffa8 | ;56301 ESSI1 receive data register       |

| M_CRB1 | EQU                | \$ffffa6 | ;56301 ESSI1 control register B          |

| M_CRA1 | EQU                | \$ffffa5 | ;56301 ESSI1 control register A          |

|        |                    |          |                                          |

| bclr   | #9,SR              |          | ; enable interrupt priority levels 3,2,1 |

| bset   | #23,x:M_II         | PRC      | enable DMA5 interrupt at priority        |

|        |                    |          | ;level 1                                 |

| movep  | #\$13,x:M_I        | PCRD     | enable ESSI1 SCO, SC1, SRD pins          |

| movep  | #\$180000,x:M_CRA1 |          | ;24 bits per word, maximal frequency     |

| movep  | #\$02010c,x:M_CRB1 |          | receiver enable, one bit clock;          |

#### A Usage Basic Examples

### **Getting Data from the ESSI Receiver**

| movep | #M RX1,x:M DSR5      |

|-------|----------------------|

| movep | #\$int_addr,x:M_DDR5 |

| movep | #\$(N-1),x:M_DCO5    |

| movep | #\$ee62c0,x:M_DCR5   |

;SCO(RXC) and SC1(FSR) are outputs ;address of the ESSI1 receive register ;buffer top address in internal memory ;N is the size of the circular buffer ;word transfer triggered by ESSI1 Rx

x no update -> x linear

;DE is not cleared at end of block ;interrupt is generated at the

;end of block

; channel priority 3 (doesn't matter

; in the example)

I DMA5

movep #\$int\_addr,x:M\_DDR5

;interrupt routine: point again to the ;circular buffer top address

Note:

When the receiver of the ESSI is full, a trigger to the DMA is generated. This trigger is asserted until the receiver is read (by the DMA or the core). Basically, the user can program a DMA channel to transfer a block from memory to memory when a trigger from peripheral is asserted. Although the DMA operates correctly, there is a problem, because the peripheral does not deassert the Receiver Full (or Transmitter Empty) condition and can, therefore, potentially have an undetected overrun or underrun error.

# SECTION 3 MULTI-DIMENSIONAL DMA TRANSFERS

The DMA is capable of transferring data in complex structures. The address mode of the source or the destination or both can be Two-Dimensional (2D) or Three-Dimensional (3D).

| 3.1 | TWO-DIMENSIONAL (2D) TRANSFER    | 3-3 |

|-----|----------------------------------|-----|

| 3.2 | THREE-DIMENSIONAL (3D) TRANSFER  | 3-4 |

| 2 2 | EVAMBLES FOR OTHER ADDRESS TYPES | 2.5 |

Two-Dimensional (2D) Transfer

## 3.1 TWO-DIMENSIONAL (2D) TRANSFER

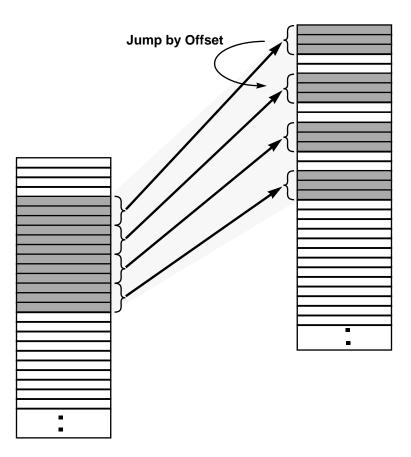

For a Two-Dimensional (2D) transfer, the DCO counter is divided into two counters DCOL and DCOH. An offset register is used to calculate the address jump. The total number of transfers is  $(DCOH + 1) \times (DCOL + 1)$ . The address for the DMA transfer is the current content of the address register (DSRi or DDRi). After the transfer is performed, if DCOL > 0, the address register is incremented by 1 and DCOL is decremented by 1. If DCOL = 0, the address register is loaded with the sum of its previous value and the content of the offset register. DCOH is decremented by 1 and DCOL is reloaded with the initial value that was written by the last core instruction. If DCOL = DCOH = 0 (i.e., the last transfer of the block), the address register is loaded with the sum of its previous value and the content of the offset register, and both DCOL and DCOH are reloaded with the initial values written by the last core instruction. With this last transfer of the block, the DMA either ceases operation or waits for a new trigger.

AA1369

Figure 3-1 Linear to 2D Transfer

#### 3.2 THREE-DIMENSIONAL (3D) TRANSFER

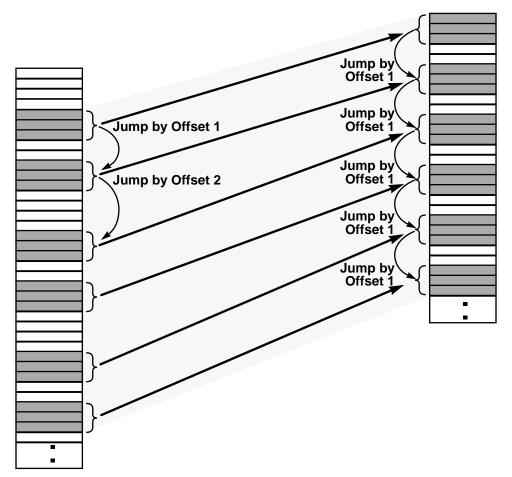

For a Three-Dimensional (3D) transfer, the DCO divides into three counters: DCOL, DCOM and DCOH. This transfer mode uses two offset registers to calculate the address jump. The total number of transfers is  $(DCOH + 1) \times (DCOM + 1) \times (DCOL + 1)$ . The DMA transfer address is the current content of the address register (DSRi or DDRi). After performing the transfer, if DCOL > 0, the address register is incremented by 1 and DCOL is decremented by 1. If DCOL = 0 and DCOM > 0, the address register is loaded with the sum of its previous value and the content of the first offset register, DCOM is decremented by 1 and DCOL is reloaded with the initial value written by the last core instruction. If DCOL = DCOM = 0 and DCOH > 0, the address register is loaded with the sum of its previous value and the content of the second offset register, DCOH is decremented by 1, and both DCOL and DCOM are reloaded with the initial values written to the DCO by the last core instruction. If DCOL = DCOM = DCOH = 0 (i.e., the last transfer of the block), the address register is loaded with the sum of its previous value and the content of the second offset register, and DCOL, DCOM and DCOH are reloaded with the initial values written to the DCO by the last core instruction. After this last transfer of the block, the DMA either ceases operation or waits for a new trigger.

Figure 3-2 3D to 2D Transfer

**Examples for Other Address Types**

## 3.3 EXAMPLES FOR OTHER ADDRESS TYPES

The following examples show how to use 2D and 3D Addressing modes to transfer data between other address types.

## 3.3.1 Circular Buffer Using 2D Addressing

The example code presented in this section transfers one data word per request until the end of the circular buffer, and then jumps back by a negative value offset register to the head of the buffer. Unlike the alternate code presented in **Section 2.3** on page 2-5, the following code does not require the core to handle any interrupts.

```

$ffffaf

M PCRD

EQU

; DSP56301 port D control register

EOU

$ffffa8

; DSP56301 ESSI1 receive data register

M_RX1

$ffffa6

$ffffa5

M CRB1

EOU

; DSP56301 ESSI1 control register B

M CRA1

EOU

; DSP56301 ESSI1 control register A

#$13,x:M_PCRD

; enable ESSI1 SCO, SC1, SRD pins

movep

#$180000,x:M_CRA1

; 24 bits per word, maximal frequency

movep

#$02010c,x:M CRB1

; receiver enable, one bit clock

movep

#$-(N-1),x:M_DOR0

; this is the offset to get back

movep

#M RX1,x:M DSR5

; address of the ESSI1 receive register

movep

#$int addr,x:M DDR5

; buffer top address in internal memory

movep

#$(fff000+(N-1)),x:M_DCO5

movep

#$ae6040,x:M DCR5

movep

; word transfer triggered by ESSI1 Rx

; x no update -> x 2D with DORO

; DE is not cleared at end of block

; interrupt is not generated at the

; end of block

; channel priority 3 (doesn't matter

; in the example)

```

## 3.3.2 Transfers with Equidistant Offset

The DSP56300 core Address Generation Unit (AGU) has an address mode called Post-increment By Offset Nn that uses the syntax (Rn) + Nn. This mode can be used, for example, to perform a decimation of samples stored in a large array. Using the DMA to perform the same task can free the pointer Rn. If the user programs a DMA channel to be 2D with DCOL = 0, then for every transfer, the address register is updated by offset N stored in the offset register DORi. Programming the same channel as 3D with DCOH = 0 and DCOL = 0, but with DCOM > 0 and DORi = N (offset) and DORj =  $-(N \times DCOM)$  implements a circular buffer that performs an equivalent decimation algorithm (i.e., the resulting address mode is similar to using the modulo modifier  $mod_{Mn}((Rn) + Nn))$ .

wudi-Dimensional DMA Transfers

**Examples for Other Address Types**

#### 3.3.3 Transferring Data for 3D ESSI Transmitters

In the example code presented in this section, three ESSI transmitters send data simultaneously from a DMA channel by using the Line Transfer mode and a 2D addressing mode to wrap around back to the first transmitter. In this example, the 3D mode is used to allow the source to generate a circular buffer. The 3D mode is needed because when DCOL = 0, the destination (ESSI registers) uses an offset and the buffer must also use an offset. Therefore, this offset is 1. The second offset is used for wrapping back to top of buffer. An interrupt is needed only after the buffer is scanned the number of times indicated by the contents of DCOH (i.e., DCOH + 1). In this code, the first write operation to the transmitters is done by the core because after reset, the TDE bit (Transmitter Data Empty) in the ESSI Status Register (Bit 6 in SSISR) is cleared, and therefore a DMA request can not be issued for the first word. In order not to change the code between the first buffer pass and all other passes, the first write is taken by the core in all passes.

```

$ffffbf

; DSP56301 port C control register

M PCRC

EQU

M_TX00

EQU

$ffffbc

; DSP56301 ESSI0 trans.0 data register

M TX01

EQU

$ffffbb

; DSP56301 ESSI0 trans.1 data register

M_TX02

$ffffba

; DSP56301 ESSI0 trans.2 data register

EQU

M_CRB0

EQU

$ffffb6

; DSP56301 ESSIO control register B

M CRAO

$ffffb5

; DSP56301 ESSI0 control register A

EQU

bclr

#8,SR

; enable interrupt priority levels 3,2,1

bset

#13,x:M IPRC

; enable DMAO interrupt at priority

; level 1

movep

#$2f,x:M PCRC

; enable five pins for ESSIO

#$180000,x:M CRA0

; 24 bits per word, maximal frequency

movep

#$01d12c,x:M_CRB0

; synchronous normal mode, one bit clock

movep

; three transmitters

#$fffffd,x:M_DOR2

; DOR2 = -2

movep

#$1,x:M_DOR0

; regular increment

movep

#$-buf_size,x:M_DOR1

; for jumping back to the top of buffer

movep

#$int buf,x:M DSR0

; buffer top address in internal memory

movep

#M TX02,x:M DDR0

; transmitter 2 data register

movep

\#$(2^{12}*B1+fc0003),x:M_DC00; the counter is divided to three

movep

; B1 = (buf size / 3) -1 -> DCOM

; DCOL = 2, DCOH = $3f

movep

#$d65d20,x:M DCR0

; line transfer triggered by ESSIO Tx

; x 3D with DORO, DOR1 -> X 2D with DOR2

; DE is cleared at end of block

; interrupt is generated at the

; end of block

; channel priority 3 (doesn't matter

; in the example)

I DMAO

bset

#23,x:M DCR0

; interrupt routine: start again

```

# SECTION 4 OPERATION OF MULTIPLE DMA CHANNELS

Because a DMA channel can be triggered by one of thirty-two sources, multiple DMA tasks can be performed orthogonally or concurrently. This section discusses use of multiple DMA channels in applications.

## NO

## Freescale Semiconductor, Inc.

**Operation of Multiple DMA Channels**

| 4.1 | INTRODUCTION                | 4-3 |

|-----|-----------------------------|-----|

| 4.2 | COLOR COMPRESSION EXAMPLE 1 | 4-3 |

| 4.3 | PRIORITIES BETWEEN CHANNELS | 4-5 |

| 4.4 | COLOR COMPRESSION EXAMPLE 2 | 4-6 |

| 4.5 | CONTINUOUS MODE             | 4-8 |

Introduction

Operation of Multiple DMA Chainles

## 4.1 INTRODUCTION

This section provides several examples that employ multiple DMA channels.

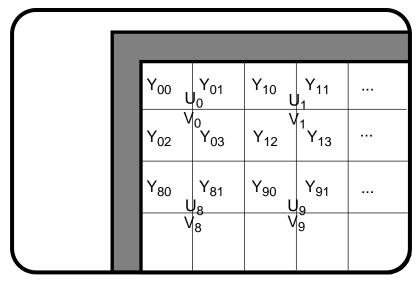

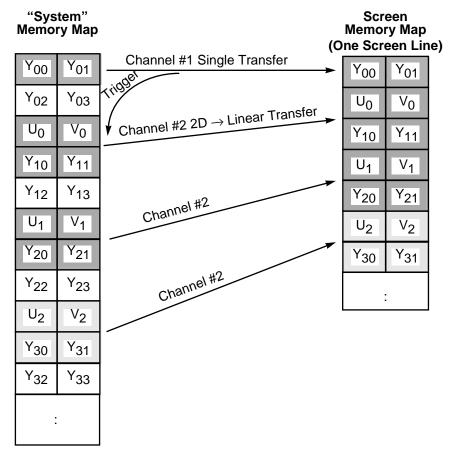

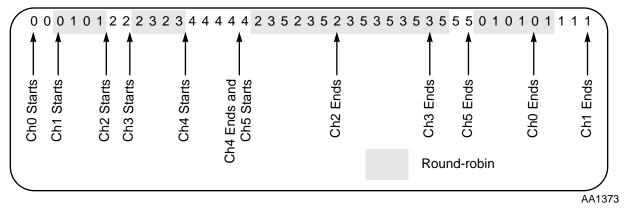

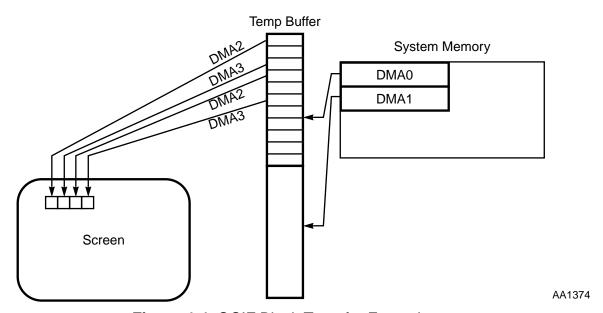

### 4.2 COLOR COMPRESSION EXAMPLE 1