Freescale Semiconductor

# Digital Subscriber Line Access Multiplexer Line Card Application Note

Preliminary Version 1.2

HCLDSLAM-AN/D

© Freescale Semiconductor, Inc., 2004. All rights reserved.

For More Information On This Frounce, Go to: www.freescale.com

### **DSLAM Application Note**

#### **Table of Contents**

| 1           | Modification History                             | 3   |

|-------------|--------------------------------------------------|-----|

| 2           | Overview                                         | 3   |

| 2 3 4 5 6 7 | Definitions, Acronyms and Abbreviations          | 6   |

| 4           | Related Documents                                | 7   |

| 5           | Application Mapping                              | 8   |

| 6           | Assumptions                                      | 9   |

| 7           | Network processor architecture                   | .10 |

| 7           | .1 Data Paths                                    |     |

| 8           | Network processor components                     | .13 |

|             | .1 XP                                            |     |

| 8           | .2 OAM Processing                                | .14 |

|             | .3 Statistics Management                         |     |

|             | .4 DSL Rx-Tx (CP0-CP3)                           |     |

|             | .5 OC-3c ATM/FR CP (CP4-CP7)                     |     |

|             | .6 IPv4 (CP12 & CP14)                            |     |

| 8           | .7 Segmentation (CP8 & CP10)                     | .38 |

|             | .8 Reassembly (CP9 & CP11)                       |     |

| 8           | .9 FR processing – switching (CP13 & CP15)       | 48  |

| 8           | .10 Fabric Port                                  | 51  |

| 8           | .11 Table Lookup Unit                            | 53  |

|             | .12 Buffer Management Unit                       |     |

|             | .13 Queue Management Unit                        |     |

|             | .14 Q-3 configurations for CPs, XP and FP        |     |

| <u>9</u>    | HOST PROCESSOR ARCHITECTURE                      |     |

| 10          | HOST PACKET I/O                                  | 61  |

|             | 0.1 Resources                                    |     |

|             | 0.2 Packet Reception                             |     |

|             | 0.3 Packet Transmission                          |     |

|             | CONSOLE COMMAND SHELL COMMANDS                   |     |

| <u></u> 1   | 1.1 Application Control.                         | 62  |

|             | 1.2 Table Maintenance and Display                |     |

|             | 1.3 DSL Link Configuration and Status            |     |

|             | 1.4 OC-3c interface Configuration and Status     |     |

|             | 1.5 ATM Configuration and Status                 |     |

|             | 1.6 FR Configuration and Status                  |     |

|             | 1.7 Statistics                                   |     |

|             | HOST PROCESSOR TO NETWORK PROCESSOR INTERFACE    |     |

|             | 2.1 FR                                           |     |

| 13          | HOST API REFERENCE                               |     |

|             | 3.1 Table API                                    |     |

|             | 3.2 Link and Channel API                         |     |

|             | 3.3 ATM API                                      |     |

|             | 3.4 FR API                                       |     |

|             | 3.5 Control API                                  |     |

|             | <u>3.6 I/O API</u>                               |     |

| 14          | Appendix – Optimizations done in the application |     |

|             |                                                  |     |

### **1** Modification History

| Rev | Date      | Author           | Department       | Changes                 |

|-----|-----------|------------------|------------------|-------------------------|

| 1.0 | 24-Feb-03 | HCL Technologies | Networking       | Initial version.        |

| 1.1 | 12-Mar-03 | J.Bednarek       | Freescale/C-Port | First Comments.         |

| 1.2 | 13-Mar-03 | HCL Technologies | Networking       | Incorporated review     |

|     |           |                  | -                | comments from Freescale |

## 2 Overview

This document aims at discussing the design of a Digital Subscriber Line Access Multiplexer (DSLAM) line card. The intended audiences of this document are the software designers, testers and programmers of the line card based on the C-Port network processor family.

The reader of this document is expected to have a fair understanding of the C-3e NP architecture and the associated co-processor such as Q-3 (Traffic Management Co-processor) with the basic understanding of M-2 Utopia/POS-PHY Adapter Reference Design used in the design of the DSLAM line card.

#### Feature Overview and Standards Support

This application supports the following features:

- A maximum of 192 ports of ADSL ports

- Support for upto 9 Mbps downstream traffic and 1 Mbps upstream traffic per DSL port/channel.

- OC-3c interfaces running ATM / FR over SONET

- FR header processing and reassembly

- AAL5 segmentation and reassembly

- ATM Cell switching

- FR switching

- IPv4 Unicast Routing on all interfaces (ATM/FR)

- Support for ATM traffic management

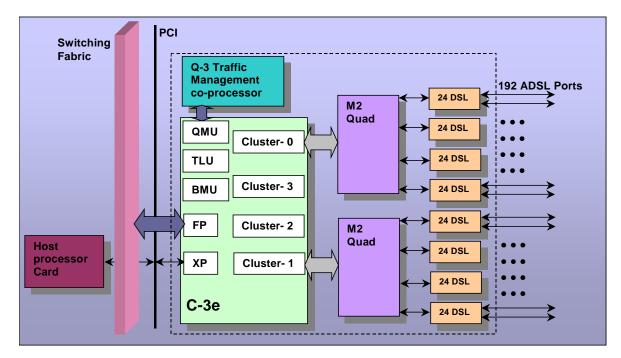

DSLAM line card is intended to work in a stack of cards connected on the switching fabric for communication with the other DSLAM cards as well as the line cards that terminate ATMs. The host module manages and maintains the statistics for the entire system. The communication of the host with the line cards is through the PCI interface. Figure 1 helps in understanding this configuration of the DSLAM line card.

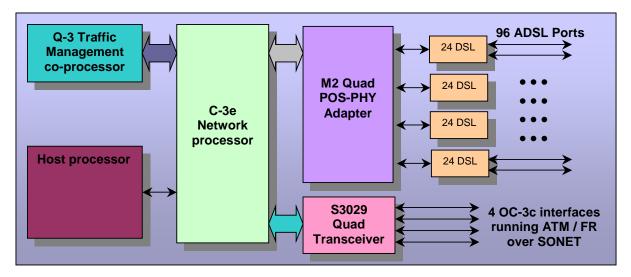

Figure 2 and Figure 3 show two configurations of DSLAM application for which the design has been implemented.

### Freescale Semiconductor, Inc.

HCL TECHNOLOGIES HCL

#### **DSLAM Application Note**

Figure 1: Stackable DSLAM line cards within a system

#### **DSLAM Application Note**

Configuration I (Figure 2) comprises of eight 24 port xDSL chipset supporting 192 ADSL ports in total. This configuration implements a switch fabric interface. The chunks received on DSL interfaces are sent across the fabric interface via FP.

Figure 2: Configuration- I DSLAM line card with 192 ADSL ports

Configuration II (figure 3) is comprised of 96 DSL ports. This configuration implements an uplink of four OC-3c interfaces. It does not have a switch fabric interface.

Figure 3: Configuration- II Independent DSLAM unit

## **3** Definitions, Acronyms and Abbreviations

| Abbreviation | Description                                |

|--------------|--------------------------------------------|

| AAL          | ATM Adaptation Layer                       |

| АТМ          | Asynchronous Transfer Mode                 |

| ATM TM       | ATM Traffic Management                     |

| BE           | Best effort                                |

| BOM          | Beginning of Message.                      |

| СА           | Channel Adapter                            |

| CBR          | Constant Bit Rate                          |

| CID          | Channel ID                                 |

| CIDR         | Classless Inter Domain Routing             |

| CPI          | Common Part Indicator.                     |

| CPRC         | Channel Processor RISC core.               |

| CRC          | Cyclic Redundancy Check.                   |

| DLCI         | Data Link Connection Identifier            |

| DWRR         | Dynamic Weighted Round Robin               |

| FR           | Frame Relay                                |

| HEC          | Header Error Control.                      |

| НТК          | Hash Trie Key.                             |

| ICMP         | Internet Control Message Protocol          |

| IP           | Internet Protocol                          |

| LCP          | Link Control Protocol                      |

| LLC          | Logical Link Control                       |

| LMI          | Local Management Interface                 |

| LPM          | Longest Prefix Match.                      |

| LSP          | Label switched path                        |

| MIB          | Management Information Block               |

| MPHY         | Multi PHY                                  |

| MTU          | Maximum transmission Unit                  |

| NCP          | Network Control Protocol                   |

| NLPID        | Network Layer Protocol ID                  |

| OAM          | Operation, Administration and Maintenance. |

| PDU          | Protocol Data Unit.                        |

| PPP          | Point to Point Protocol                    |

| QoS          | Quality Of Service                         |

| RED          | Random Early Discard                       |

| RM           | Resource Management.                       |

| RR           | Round Robin                                |

| SDU          | Service Data Unit.                         |

| SNAP         | Subnetwork Access Protocol.                |

| SPHY         | Single PHY                                 |

| ТСР          | Transport Control Protocol                 |

| Abbreviation | Description                                        |

|--------------|----------------------------------------------------|

| TLU          | Table Lookup Unit.                                 |

| TMC          | Traffic Management Co-Processor                    |

| TOS          | Type of Service                                    |

| TTL          | Time To Live                                       |

| UUI          | User-to-User Interface.                            |

| VC           | ATM Virtual Connection                             |

| VOP          | Virtual Output Port                                |

| VP           | ATM Virtual Path                                   |

| VPCI         | Virtual Path Identifier/Virtual Channel Identifier |

| WFQ          | Weighted Fair queueing                             |

## 4 Related Documents

This section lists down the various documents used as reference while developing this application notes.

- C-5e/C-3e Network Processor Silicon Revision A0

- Multi-PHY Switch Application Guide, CST2.2

- POS to Gigabit Ethernet Switch application guide CST 2.2

- ATM Cell Switch Application Guide, CST 2.1.1

- RFC 791, Internet Protocol

- RFC 1812, Requirements for IP Version 4 Routers

- RFC 2427, Multiprotocol Interconnect over Frame Relay

- RFC 2684, Multi Protocol Encapsulation over ATM Adaptation Layer 5

- ITU I.361, B-ISDN ATM Layer Specification

- ITU I.363.5, B-ISDN ATM Adaptation Layer Specification: Type 5 AAL

- ITU I.610 B-ISDN Operation and Maintenance Principles and Functions

- Frame Relay to ATM to 10/100 Ethernet Switch Router Application Guide, CST2.1

- C-ware Q-5 TMC API User guide Rev 00

## 5 Application Mapping

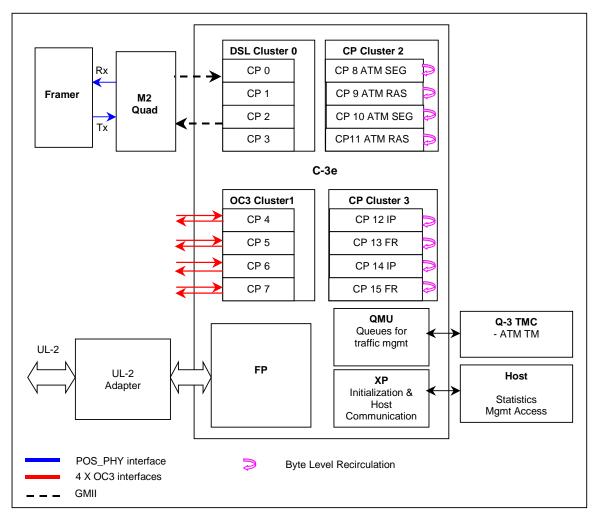

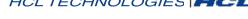

This application is comprised of many software components, each of which is divided into smaller components. The functional partitioning of the software is depicted in figure 4 with the clustering and re-circulation information. C-3e NP is chosen for implementing the DSLAM line card as the processing power of the NP and the M-2 Quad match and Q-3 is used for managing the traffic management for IP and ATM.

Figure 4 shows the DSLAM card functioning in a C-3e for configuration II (shown in figure 3).

In this configuration, the CP allocation is as follows:

- Cluster 0 (CP0-3) connected to M-2 Quad which in turn connected to four G-24 chip. It implements the MPHY interface.

- Cluster 1 (CP4-7) is connected to four OC-3c links

- CP8 and CP10 for AAL-5 segmentation

- CP9 and CP11 for AAL-5 reassembly

- CP12 and CP14 for IP processing

- CP13 and CP15 for FR switching and processing

CP8 and CP9 perform segmentation and reassembly, respectively, for the M-2 MPHY chunks received at DSL cluster (cluster 0). While CP10 and CP11 are for packets received at OC-3c cluster. Similarly, CP12 and CP13 do IP and FR processing, respectively, for M-2 MPHY chunks received at DSL cluster. Packets received at OC-3c interfaces will be queued to CP14 and CP15 for IP and FR processing. Appendix states the reason for this distribution of traffic.

The functional mapping of DSLAM card for configuration I will be same as figure 4 except for the OC-3c cluster. Cluster1 will be connected to another M-2 Quad for processing frames coming from another set of 96 ADSL ports. Other CP allocation is same in configuration I (Figure 2).

The following sections in the document explain the functionality specific to configuration II. For configuration I, DSL-cluster functionality will override the OC-3c cluster functionality.

#### **DSLAM Application Note**

#### Assumptions 6

Following assumptions are made in the DSLAM line card application design:

- The DSL ports (channels) are configured to receive either FR frames or ATM cells. • Thus, the ChanType field in the M-2 chunk header will indicate whether it is an ATM cell or FR frame.

- For configuration II (Figure 4), the administrator is responsible for distributing the • traffic across DSL channels and OC-3c ports. The bandwidth of the input pipe and that of the output pipe should be matched to avoid buffer overflow in the C-3e NP.

- M-2 CA takes care of CRC-10 (ATM HEC calculation). •

#### **DSLAM Application Note**

### 7 Network processor architecture

The DSLAM application consists of many software components. One component executes on the host and the other components execute on the various CPs within the C-3e. Each of the NP software components provides a subset of the features of the application. Figure 4 shows the mapping between software components and CPs. The data paths between these components can be conceptualized as a group of busses. In this context, a bus is the combined use of queues and buffer memory to forward data between two components. The queue number is analogous to the address on the bus. Each of the buses implies a different buffer and descriptor format (for ATM, FR, IP and so on). The traffic originating from DSL ports/channels will be either ATM or FR based on the channel configration.

A buffer and a buffer descriptor can specify the interface to a component. Table below lists each of the components and describes their interface. A component may have multiple interfaces and therefore multiple entries in the table. Unless specified otherwise in the table, the port field indicates the output port and the length field indicates the number of bytes in the buffer. The various buffer formats are described in <u>section Buffer</u> <u>Management Unit</u> and the buffer descriptor formats are described in appropriate sections.

| Component    | Buffer Format | Descriptor<br>format | Comments                                                            |

|--------------|---------------|----------------------|---------------------------------------------------------------------|

| IP           | BT_IPV4       | N/A                  | Port indicates input port; IP forwarding will be performed          |

| FR           | BT_FR         | FR                   |                                                                     |

| Segmentation | BT_IPV4       | Seg                  | EgressQueue field is required.                                      |

| Reassembly   | BT_ATM        | ATM                  | Port indicates input port;<br>AAL-5 reassembly will be<br>performed |

| UL-2         | BT_ATM        | ATM                  |                                                                     |

| Host         | BT_ATM        | ATM                  | Port indicates the input port;<br>only header field required        |

|              | All others    | N/A                  | Port indicates the input port                                       |

### 7.1 Data Paths

This section explains about various data paths originating from DSL port interfaces and flowing through other components in the NP. M-2 is the channel adapter for the DSLAM application. Figure 5 shows the diagrammatic representation of the data flows.

#### **DSLAM Application Note**

Figure 5: Data Flows in the DSLAM Application

### 7.1.1 Data Path for FR Frames

This section conceptualizes the data flows for FR frames. FR Frames are received in DSL Rx. The FR chunks will be reassembled as FR frame in the Rx, recirculated in other component CPs and finally transmitted as FR or AAL5 chunks via DSL Tx or OC-3c interfaces.

- FR frame is received as M-2 MPHY chunks in DSL Rx, are reassembled and identified as FR frame based on the DSL channel configuration. Then it will be enqueued to FR queue for further FR processing.

- FR component CP performs the DLCI lookup. Based on lookup response, it will enqueue the frame to IP queue or does FR switching (modify the FR header with new DLCI value) and enqueue into appropriate DSL Tx queue.

- IP component dequeues the FR frame from its queue, removes the FR header and enqueues the IP packet into destination queue (FR queue or ATM Segmentation queue) determined by IP lookup and port lookup result.

- ATM segmentation component will segment the IP packet into AAL5 cells, inserts the ATM header and enqueues these cells to appropriate Tx queue or to Q-3 traffic queue.

- DSL Tx dequeues the FR frame or ATM cells from its queue. It transmits MPHY chunks over DSL links. For ATM, each cell will fit into one MPHY chunk. For FR, it segments the frame into multiple MPHY chunks.

- If QoS treatment is needed, packets will be enqueued to Q-3 traffic queue from ATM Segmentation for applying various QoS parameters. Q-3 TMC provides marking/dropping, policing and traffic shaping for the packet based on configured traffic parameters. Q-3 TMC will enqueue the conformant packets into QMU queue. Non-conformant packets will either be discarded or marked.

### 7.1.2 Data Path for ATM cells

This section describes the data flow for ATM cells. The ATM cells are received in DSL Rx or OC-3c interfaces. The ATM cells will be recirculated in other component CPs and finally transmitted as FR / AAL5 chunks via DSL Tx or ATM cells in OC-3c interfaces.

- ATM cells will be enqueued to DSL Tx queue or OC-3c Tx queue (ATM switching) or FP queue.

- AAL5 cells are enqueued into reassembly queue by DSL Rx that performs the VC table lookup to send the new VPI/VCI values into the reassembly queue.

- ATM reassembly component will de-queue and reassembles the cells into AAL5 PDU. It will then be enqueued into IP queue.

- IP component dequeues the reassembled AAL5 PDU from its queue, enqueues it into destination queue (DSL Tx queue or OC-3c Tx queue or ATM Segmentation queue) determined by IP lookup and port lookup result.

- ATM segmentation component will segment the IP packet into AAL5 cells, modifies the AAL5 header (with new VPI/VCI) and enqueues these cells to DSL Tx queue or to OC-3c queue or to Q-3 traffic queue (if QoS is needed).

- DSL Tx dequeues the FR frame or AAL5 cells from its queue. It transmits MPHY chunks. For ATM, each cell will fit into one MPHY chunk. For FR, it segments the frame into MPHY chunks.

- OC-3c Tx dequeues the ATM cells and transmits them over the line.

- If QoS is needed, packets will be enqueued to Q-3 traffic queue from ATM Segmentation for applying various QoS parameters. Q-3 TMC provides marking/dropping, policing and traffic shaping for the packet based on configured traffic parameters. Q-3 TMC will en-queue the conformant packets into QMU queue. Non-conformant packets will be discarded.

### 8 Network processor components

This section describes each of the features of the applications in detail and explains how each component or resource within the NP is used to provide the applications' features.

The Executive Processor RISC Core (XPRC) is a general-purpose processor that provides management, control, and exception processing functions. The XP controls NP boot up, configuration, and initialization of all system components.

The Channel Processors (CPs) are the components most closely associated with processing data from a physical interface. There are 16 CPs organized as four clusters, each of which contains four CPs. Each cluster performs several functions that aid in the processing of data packets.

### 8.1 XP

The XP program is partitioned into distinct 'initialization' and 'main' executables. After loading and running the initialization executable, the main executable is loaded and overlayed on the initialization executable, reducing the IMEM used at run-time. This partitioning scheme uses the available IMEM resource to its fullest.

#### 8.1.1 Initialization Program

The initialization executable performs service initialization, configures system resources, and loads the CPs. In particular, the initialization executable does the following:

- Allocates buffer pools.

- Allocates and configures queues.

- Configures the fabric port

- Configures the PHY interfaces

- Loads the CPs

- Defers to the main XP executable program

#### 8.1.2 Main Program

The main executable completes any necessary initialization and starts the CPs before entering the main loop. In particular, the main executable does the following:

- Initializes the CRC correction table

- Starts the CPs and enables the fabric port.

- Starts some of the SDPs

- Initializes the OAM processing component

- Initializes the host communication component

- Enters the main loop

The main loop within the XP performs processing for OAM handling described in section "OAM processing" and host communication for updating statistics.

### 8.2 OAM Processing

OAM cells received by the DSL CPs or OC-3c CPs are forwarded to the XP for processing. OAM support in the application includes the following:

- Forward Performance Monitoring Receive Monitoring

- Blocks of user cells on a limited number of VCCs (128) are monitored for errors per flow. A BIP-16 is generated for all the cell payloads for each block where the block size is configurable. The block size is defaulted to 128 cells.

- The receiver checks the parity on the received block data and compares its results with the received BIP-16. The number of errors is determined and written to a statistics counter for the indicated VC.

OAM processing uses the <u>ATM VC table</u>.

#### 8.2.1 SDP

The DSL and OC-3c CPs support OAM performance monitoring. The SDP processors on the CPs do the following:

#### 8.2.1.1 RxSync

The RxSync processor performs the following OAM functions:

• Determines the CRC-10 for each cell received (regardless of whether the cell is OAM or not) and forwards a pass-fail notification to the RxByte processor.

RxSync is not configurable through its control space.

#### 8.2.1.2 RxByte

The RxByte processor performs the following OAM functions:

- Determines whether an F4/F5 OAM cell has been received and indicates this in extract space

- Writes cell payload overhead to extract space.

- Forwards CRC-10 pass/fail indication to the RC through extract space

- Determines the BIP-16 value on each cell received and writes this value to extract space.

- Determines whether a user cell has been received and writes this information to extract space

#### 8.2.2 RC

The RC performs higher level processing of data packets to support OAM – FPM.

#### 8.2.2.1 Initialization

During initialization, the 128 entry OAM PM table is initialized.

#### 8.2.2.2 Receive

The receive thread handles incoming data packets and performs OAM specific operations. Specifically, it does the following:

- Checks whether a received cell is on a VC where OAM FPM is being performed. This information is stored in the ATM VC table (the oamPm field). If this cell is a user cell, it does the following:

- XORs the current value of the BIP-16 into OAM FPM table running total for all user cells.

- Increments and masks the CurrentBlockValue (ranges from 0 to BlockSize-1).

- If the received cell is not a user cell, then the code checks whether an OAM cell has been received. If OAM but not of the type OAM FPM cell, the cell is forwarded to the XP. Otherwise, it does the following:

- Compares the CurrentBip16 value with the value received in the OAM FPM Cell. If these values are XOR-ed, the number of bits set indicates the number of errors. The number of bits set is determined through a lookup into a 16-byte table (where each byte in the table indicates the number of bits set for the index) for each nibble (oamPmErrTab). The information is used to update TotalBip16Errs counter.

#### 8.2.3 Data Structures

#### 8.2.3.1 OamPmTable

This OAM processor maintains OAM performance monitoring state information in the following data structure:

| Bytes | 0            | 1              | 2 | 3                     |  |

|-------|--------------|----------------|---|-----------------------|--|

| 0     | TotalBip1    | TotalBip16Errs |   | CurrentBlockValue     |  |

| 4     | CurrentB     | CurrentBip16   |   | <size< th=""></size<> |  |

| 8     | SeqnumExpect | Pad            |   |                       |  |

- totalBip16Errs count of BIP-16 errors calculated so far

- currentBlockValue the number of the cell in the current block

- currentBip16 the value of the BIP-16 calculated so far

- blockSize the block size (in cells)

- seqNumExpect the expected sequence number to be received

- pad unused

#### 8.3 Statistics Management

XPRC maintains all the statistics for the DSLAM applications. It passes the statistics storage pointer to the CP's at initialization. CPs update the statistics maintained in XPs

at run time. Host reads the statistics from XPs DMEM, needed by statistics console command.

For each DSL link, either ATM or FR statistics are maintained. IP statistics are also maintained for each DSL links. Given below are list of statistic fields for ATM, FR and IP.

List of ATM statistics:

- rxGoodCells Number of received ATM Cells

- rxOamCells Number of received ATM OAM Cells

- enqueueFail Number of times enqueue failed

- txCells Number of transmitted ATM Cells

- txOamCells; Number of transmitted ATM OAM Cells

- rxCongestDrops Number of ATM Cells dropped due to congestion

- rxHecErrored Number of ATM Cells having HEC errors

- rxInvalidVc Number of ATM Cells having invalid VCs

List of FR statistics:

- RxGoodFrames Number of received FR frames.

- EnqueueFail Number of times enqueue failed

- TxFrames Number of transmitted FR frames.

- CongestDrops Number of FR frames dropped due to congestion

- InvalidDlci Number of FR frames having invalid DLCI

- FcsError Number of FR frames having FCS errors

- EncapCntrlErr Number of FR frames having invalid control field

- EncapNlpidErr Number of FR frames having invalid NLPID

- FrReservedDlci- Number of FR frames having reserved DLCI value.

List of IP statistics:

- IpInReceives Total number packets received in IP module

- IpInHdrErrors The number of input datagrams discarded due to errors in their IP headers.

- IpForwDatagrams Number of input datagrams forwarded

- IpOutPayloadErrors Number of packets discarded due to payload errors

- IpOutInvalidPortErrors Number of packets discarded because its route entry mapped to an invalid egress port.

- IpOutNoRoutes Number of IP datagrams discarded because no route could be found to transmit them to their destination

XP needs 11.25 KB DMEM to support ATM/FR and IP statistics for a maximum of 192 DSL links.

### 8.4 DSL Rx-Tx (CP0-CP3)

CP0 to CP3 implement the MPHY interface receive processing and ATM processing for ADSL ports. CPs in this cluster receive and transmit MPHY chunks through M-2 Quad. The processing is divided into various components of the CPs. It is explained as follows:

### 8.4.1 SDP

#### 8.4.1.1 RxBit

RxBit waits for a transition of the *PhyStatus0* signal to indicate valid data and the start of a chunk. RxBit is responsible for coordinating ingress processing within the cluster. For doing this, it utilizes a token to determine which bit processor should forward its data stream. The processors without the token simply sink the data stream until the *PhyStatus0* signal indicates that data is no longer valid. They then return to waiting for it to indicate valid data again.

The processor owning the token, streams the first byte of data, passes the token, and then streams the data-stream to the RxSync processor until the *PhyStatus0* signal indicates that data is no longer valid. The processor then sends an EOF marker with *Merge9* set and a frame status value. Currently there are no errors detected by the RxBit processor and it always sends a frame status value indicating success. The processing then returns to waiting for *PhyStatus0* to indicate valid data again.

The RxBit processor does not currently use any control space information from the CPRC.

#### 8.4.1.2 RxSync

#### FR RxSync:

RxSync processor is not used for FR frames, it simply streams all data received to the RxByte processor.

#### ATM RxSync:

RxSync accumulates CRC-10 and forwards all the cells to RxByte along with CRC-10 flag. This flag eventually makes its way to CP, which will discard all errored cells.

#### 8.4.1.3 RxByte

#### ATM RxByte:

For ATM cells, RxByte performs the following functions:

- Processes M-2 CA Header. It strips off the sequence number and frame length from the M-2 header and write them to extract space.

- Pushes the VPI, VCI, and DSL channel ID through a shift and mask function that produces a Virtual Channel (VC) Index.

- Issues a ATM VPI/VCI lookup request to the TLU.

- It then writes the following fields into Extract Space:

- Payload Type Indicator (PTI) and Cell Loss Priority (CLP)

- Generic Flow Control (GFC)

- o VPI

- o VCI

- Encoded PTI (an internal representation of the "type" of cell such as User or OAM)

- Maintains congestion drop count (that is, how many intermediate cells were dropped)

- The remainder of the frame is streamed using a 4-byte deep pipeline. The pipeline is used to avoid streaming the 3 bytes of M-2 CA trailer and the 1byte frame status from RxBit.

- Verifies CRC-10 and places result into extract space

#### FR RxByte:

#### For FR frames, RxByte performs following activities:

- At the beginning of processing, the RxByte reports a count of any frames dropped by RxByte due to CPRC unavailability (i.e., CPRC hadn't released a scope yet)

- Waits for valid data. Simply monitors the FIFO from RxSync for valid data bytes.

- Processes M-2 CA Header. Strips off the sequence number and frame length from the M-2 header and writes them to extract space.

- Reads the chunk type and channel type into extract space

- For SOP FR chunk, first five bytes of FR header will be fetched into extract space. These bytes contain address, control, DLCI field and NLPID value of the header. It then sets L1 done for RxCPRC and sends the remaining bytes of payload of the chunk to DMEM.

- The protocol field is checked for IP protocol. If it is not IP, a frame status of Unknown Protocol is written to extract space and the rest of the frame is simply streamed to the buffer and not parsed.

- For non-SOP M-2 chunk, it sets L1 done for RxCPRC and sends the remaining bytes of payload of the chunk to DMEM.

- When data9 is received, it writes the chunk status code to extract space and switches scope.

- Streams the payload. The remainder of the frame is streamed using a 4byte deep pipeline. The pipeline is used to avoid streaming the 3bytes of M-2 CA trailer and the 1byte frame status from RxBit.

- Checks Status Bytes. The status bytes from RxBit and the M-2 CA are processed and the frame status in extract space is updated with any errors indicated. If there are any errors indicated, the CRC check will not be performed.

- Checks CRC. RxByte feeds the incoming stream through a CRC accumulator as it is processing the frame. After it has fed the CRC field from the M-2 CA trailer through the accumulator, the value of the accumulator is checked to determine if there has been any data corruption. Note, the status byte from RxBit should not be fed through the CRC accumulator. If any CRC errors are detected, the frame status in extract space will be updated to reflect the error.

- In order to ensure that the final byte streamed to the buffer has been written, RxByte must delay 10 clocks after the last byte was streamed before switching scope to give the DMA time to complete the action.

- RxByte now switches to the other scope and checks whether the CPRC has released it yet. If the CPRC has already released the new scope RxByte starts

over with the Report Dropped Frames step. Otherwise, it continues with the next step.

• Waits for scope ownership. While RxByte is waiting for the CPRC to release a scope, it continues to read any incoming data on the FIFO and discards the bytes read. It keeps track of how many frames are received in the discarded data and reported the count to the CPRC when scope is available.

#### 8.4.1.4 TxByte

The major activities of the TxByte processor are to transmit the M-2 CA header and the trailer bytes. Each activity is described below:

- M-2 CA Header: TxByte generates and outputs the sequence number and frame length fields of the M-2 header based on data from merge space.

- M-2 CA Trailer: TxByte generates and outputs a status field indicating a good frame and outputs the CRC-16 field based on the value read from the CRC accumulator.

The TxByte processing can be broken down into the following sequential steps:

#### FR TxByte:

- TxByte waits for valid data to appear in the FIFO from the CPRC.

- Once valid data is present, it initializes the CRC accumulator and begins processing the data. All data bytes output by the processing will also run through the CRC accumulator.

- It generates and outputs the sequence number and frame length fields of the M-2 header based on data from merge space.

- Stream bytes from the FIFO until it receives an indication that there is no more valid data in the FIFO (that is, Data9).

- Generates and outputs a status field indicating a good frame and outputs the CRC field based on the value read from the CRC accumulator.

- Now switches to the other scope of merge space.

#### ATM TxByte:

After receiving a cell, TxByte process formats the cell and sends it away to large FIFO. Following are the functions preformed by TxByte.

- Merge in ATM header, the information from the merge space. In DSLAM application, it does not generate HEC (Header Error Check) because the framer takes care of HEC calculation.

- Passes token by asserting data9

- It now streams bytes from the FIFO until it receives an indication that there is no more valid data in the FIFO (that is, Data9)

- CRC10 is appended to the end of the payload that totals 48 bytes.

#### 8.4.1.5 TxBit

• TxBit waits for an indication of valid data in its FIFO. While there is no valid data, it will transmit idle characters to the M-2 CA. It does not matter what character is

used for idle as long as the transmit enable signal (Data9) is not asserted when the character is transmitted.

- Once valid data is present in the FIFO, TxBit asserts the transmit enable signal and begins streaming the data from the FIFO to the M-2 CA.

- Once the FIFO is emptied of valid data, the TxBit processor de-asserts the transmit enable signal.

### 8.4.2 RC

The RC component uses two threads to perform its task, namely, an input thread and an output thread. The initialization code starts the two threads. Each of these is described next.

#### 8.4.2.1 Initialization

The RC component of DSL CP does the following things during its initialization:

- Creates the input and output threads.

- Initializes the ATM and IP route lookups launched by the SDP, for ATM cells and FR frames, respectively.

- Initializes both scopes by giving the SDP ownership

- Starts the SDP.

- Jumps to the first thread

#### 8.4.2.2 Input Thread

#### ATM Rx:

This component in DSL Rx CP handles ATM cells. Specifically, it does the following:

- Waits for ATM VPI/VCI lookup to complete

- Lookup failure causes the cell to be dropped and a statistics counter is incremented.

- Allocates new buffer and initiates payload transfer from DMEM to SDRAM.

- Builds descriptor with forwarding information from lookup response

- Waits for payload transfer to complete.

- Determines whether OAM FPM is being performed on this VC. If so:

- For user cells, read the current BIP16 value from extract space and XOR with current value. Update OAM fields.

- For OAM FPM cells, check BIP16 and maintain count of total BIP16 errors.

- For cells other than AAL-5, it launches port table lookup.

- Waits for port lookup to complete

- En-queues descriptor to egress queue or QoS queue indicated by port lookup result

- For AAL-5 cells, the cells are queued to reassembly module

#### FR Rx:

This component in DSL Rx CP handles FR frames. Specifically, it does the following:

• Waits for L1 done so that SDP has completed the header processing and put the necessary information into extract space.

- Makes the pointer (chRxCBPtr) point to DSL Rx Control block in DMEM. ChRxCBPtr will depict the M-2 chunk reassembly information in DMEM.

- Processes chunk based on chunk type (flow control or user) in extract space after checking for errors.

- For SOM chunk,

- Allocate new buffer for reassembling the FR chunks

- Destination queue will be the FR queue.

- Get the FR header information by properly interpreting the extract space.

- Write the FR header into DSL Rx channel control block (chRxCBPtr).

- Initiate the payload transfer from DMEM to SDRAM if no error is indicated in chunk. Update the buffer offset in DSL Rx channel control block (chRxCBPtr) by incrementing it with chunk length.

- For non-SOM chunks, retrieve reassembly state information (buffer handle and buffer offset) from Rx channel control block (chRxCBPtr) and initiate the payload transfer from DMEM to SDRAM if no error is indicated in chunk. Also, update the buffer offset in the control block (chRxCBPtr).

- For EOM chunk, build the descriptor with buffer handle, buffer length and FR header (DLCI value). En-queue it to the FR queue.

#### 8.4.2.3 Output Thread

The output thread handles outgoing cells or datagrams. Specifically, it does the following:

- Check channels in a round robin manner for credits available (chFlowChunksAvail).

- Get state information for current channel i.e. get the pointer chTxCBPtr which points to DSL Tx channel control block in DMEM. This control block will contain the segmentation state information.

- If chFlowChunksAvail is true, check whether this channel is in the process of segmenting the PDU into M-2 chunks i.e. transmitting the chunks of a PDU. If it is so, the next chunk of PDU will be transmitted.

- If no segmentation is in progress, the incoming descriptor will be de-queued from its queue. Note that the descriptor would have been en-queued by

- FR module (CP13 and CP15- for FR switching)

- ATM segmentation (CP8 and CP10)

- After de-queuing, the segmentation state will be updated with the values fetched from descriptor. Segmentation state values to be updated are: Buffer Handle, Buffer offset, length and port buffer type taken from incoming descriptor. Offset will be filled as zero

- PortBufferType will be checked to determine the incoming module i.e. from which module it has come (BT\_ATM or others) so that it will segment the PDU accordingly.

- If portBufferType is BT\_ATM, it is an ATM cell and hence will be switched. If portBufferType is other than BT\_ATM, the frame needs to be segmented into number of chunks based on the channel length in chTxCBPtr.

- For segmenting into chunks, chunk length (1 64 bytes) will be calculated based on offset in ChTxCBPtr (for first chunk, the offset will be 0). Also if chunk

length is less than 64 bytes, it will set the EOM flag stating that it is the last chunk.

- The offset in chTxCBPtr will be incremented by chunk length for the next chunk.

- It waits for the scope to be available from SDP.

- It fills the merge space with chanId\_chanType, chunkLength and userInd.

- For ATM, fills cell header also into the merge space.

- It then waits for payload transfer of previous chunk to complete.

- It initiates the payload transfer from SDRAM to DMEM for that chunk.

- For EOM chunk, it frees the buffer associated with previous chunk and resets the state information (in chTxCBPtr) for the new PDU.

#### 8.4.3 Data Structures

#### 8.4.3.1 Extract Space

RxByte writes information about data-grams into extract space for the RC. typedef struct {

| int8u | channelld;       |

|-------|------------------|

| int8u | chanType;        |

| int8u | sequenceNumber;  |

| int8u | chunkStatus;     |

| int8u | chunkHeader;     |

| int8u | chunkLength;     |

| int8u | frameStatus;     |

| int8u | congestionDrops; |

|       |                  |

union {

```

struct {

typedef struct {

int32u VpiVci : 28;

int32u PtiClp : 4;

} CellHdr;

int16u

bip16;

int16u

vccIndex;

pduHdrStatus;

int8u

int8u

encodedPti;

int8u

camValue:

flags:

int8u

int8

crc10Indicator;

int8u

pad1;

} atm;

struct {

typedef struct

{

int16u dlci;

int8u fecn; // congestion control bit

int8u becn; // congestion control bit

```

#### **DSLAM Application Note**

// congestion control bit (discard eligibility) int8u de: // control and response field bit int8u cr: int8u ea0; // extended address bit0 int8u ea1: // extended address bit1 } FrHeader; int8u userInd: int8u chunkLength; crcInd: int8u bufferType; int8u

} chunkType; int8u pad2[42];

} fr;

#### } DSLExtract;

The explanations for the above-mentioned fields will be as follows:

- Channel Id: -M-2 Channel Id. 8-bit field is used to store an identifier representing DSL channels

- chunkStatus: This field indicates that M-2 has encountered error coming from the framer.

- chunkHeader: Header field values of the M-2 chunk.

- ChunkLength: length of the M-2 chunk

- ChanType: M-2 Chunk type. It can be ATM cell or FR frame based on the DSL channel configuration

- Sequence Number: This field is used as chunk sequence number, which is checked to assure that there are no lost packets

- FrameStatus: Indicator of framing error, CRC error, and so on

- CongestionDrops: -16bit count of the number of PDUs dropped since last extract ownership (i.e. the number dropped by the RxSDP due to congestion on the part of the CPRC

- VpiVci and PtiClp: Outgoing ATM header to apply to cells

- VccIndex: 16bit entity containing the VccIndex used for the TLE request launched by the SDP

- pduHdrStatus: GOOD\_HEC\_CELL (0x00) or IDLE\_UA\_CELL (0x01) or BAD\_HEC\_CELL 0x80

- encodedPti: field to identify the ATM payload type

- camValue: Value used to cam are

- o 0xF4 OAM cells

- o 0xF5 OAM/RM cells

- Flags: Flag indication that current connection is valid.

- crc10Indicator: Non-zero Indicates CRC10 error. Only valid for OAM/RM cells, don't care for all other.

- FrHeader: FR header values containg DLCI (data link connection identifier), congestion control bits (Fecn, Becn, discard eligibility, control and response field bit) and extended address bits (ea0, ea1)

- UserInd: user indicator (BOM/COM/EOM)

• crcInd: - CRC indicator (for CRC16 or CRC32 calculation)

#### 8.4.3.2 DSL Rx Control Block

The state maintained (in DMEM) for each M-2 chunk has the following data structure. Note that this structure is used only in the case of FR and not in the case of ATM because ATM can be fit in single M-2 chunk:

| Byte Offset | 0           | 1                   | 2 | 3   |

|-------------|-------------|---------------------|---|-----|

| 0           | chBufHandle |                     |   |     |

| 4           | chBufOffse  | chBufOffset chDestQ |   | stQ |

| 16          | chHeader    |                     |   |     |

typedef struct {

| BsBufHandle | chBufHandle; |

|-------------|--------------|

| int16u      | chBufOffset; |

| int16u      | chDestQ;     |

| int32u      | chHeader;    |

| } DSLRxCB;  |              |

The explanations for the above-mentioned fields will be as follows:

- chBufHandle: specifies the handle of the reassembled buffer.

- chBufOffset: specifies the offset in the reassembled buffer.

- chDestQ: destination queue where the EOM chunk will be en-queued.

- chHeader: Chunk header. This field corresponds to ATM 'cellHeader' in the case of ATM chunks and FR header in case of FR frames.

#### 8.4.3.3 Descriptor Structure

The following is the data structure of the descriptor to be en-queued.

| Byte Offset | 0         | 1                   | 2 | 3 |

|-------------|-----------|---------------------|---|---|

| 0           | bufHandle |                     |   |   |

| 4           | Ler       | Length Port_bufType |   |   |

| 8           | AppData   |                     |   |   |

| 12          | AppData   |                     |   |   |

typedef struct {

BsBufHandle bufHandle; int16u length; int16u port\_bufType; union { int8u byte[8]; int16u hword[4]; int32u word[2]; AtmDescData atm;

FrDescData frameRe: SegDescData seg; } appData; } DescriptorMsg;

The explanations for the above-mentioned fields will be as follows:

- bufHandle specifies the handle of the reassembled buffer. •

- length specifies the chunk length. •

- port\_bufType specifies the input port and buffer type of the next module.

- appData Application specific data (FR/ATM). The structures are defined in the relevant sections.

#### 8.4.3.4 Merge space

The RC writes information about datagrams into merge space. The data structure of merge header looks like following.

```

typedef struct {

int8u chanType;

int8u chanId;

int8u userChunkLength;

int8u userInd;

union {

struct {

int32u

Frheader;

} Fr;

struct {

typedef struct {

int32u VpiVci: 28;

int32u PtiClp: 4;

} CellHdr;

int8u payloadType;

} atm;

} frAtm:

struct {

int8u

cpChen;

int8u

numChunks;

chunkSeq;

int8u

int8u

pad;

} m2MPHYHeader;

```

} DSLMergeSpc;

The explanations for the above-mentioned fields will be as follows:

- Chanld: Channel ID representing the egress DSL channel. •

- chanType specifies the channel Type (ATM/FR)

- userChunkLength chunk length (1-64 bytes for FR frames and 53 for ATM cells)

- userInd specifies the user chunk indicator (SOM/COM/EOM)

HCL TECHNOLOGIES HCL

- CellHdr ATM Cell header for outgoing cells

- payloadType Raw, Discard Header

- Frheader header field values for FR frames

- CpChen: MPHY cluster/channel information

- o cp\_id[7:6]

- o reserved[5:4]

- o chunk\_type[3:2]

- channel\_id[1:0]

- numChunks: MPHY number of chunks that current packet devides into.

- chunkSeq: MPHY initial chunk sequence number.

#### 8.4.3.5 DSL Tx Control Block

The state maintained (in DMEM) for segmentation on each outgoing DSL channel is stored in the following data structure:

| Byte Offset | 0                 | 1          | 2 | 3 |

|-------------|-------------------|------------|---|---|

| 0           | chBufHandle       |            |   |   |

| 4           | chBufOffse        | t chLength |   |   |

| 8           | ChFlowChunksAvail | Pad        |   |   |

typedef struct {

BsBufHandle chBufHandle; int16u chBufOffset; int16u chLength; int8u chFlowChunksAvail;

} DSLTxCB;

The explanations for the above-mentioned fields will be as follows:

- ChBufHandle: specifies the Buffer handle that has to be transmitted.

- ChBufOffset : specifies the offset of the chunk in the buffer.

- chLength: specifies the chunk length.

- ChFlowChunksAvail: specifies the counts of credits available to each DSL channel.

- Pad: unused

#### 8.4.3.6 Ring Bus Slots

DSL Rx CP needs to launch lookups in following tables for various packet processing:

• ATM VC Table and Port Table.

ATM VC table lookup uses these slots:

- ATM VC request slot

0

- ATM VC response slot

0

Port table lookup uses these slots:

- Port table request slot 1

- Port table response slot 4

### 8.5 OC-3c ATM/FR CP (CP4-CP7)

CP4 to CP7 implement the OC-3c ports for the DSLAM application. These ports are used to receive and transmit ATM cells / FR frames, based on the configuration.

There are different code images running on following components of these CPs: RxBit, RxSync and TxBit.

Based on the configuration updated by Host, XP loads the appropriate images on these processors. However, RxByte, TxByte and CPRC run the same image but execute different flows of code for ATM cells and FR frames.

The CPRC module consists of two functions, namely Oc3Rx and Oc3Tx running in two separate contexts. The Rx context receives cells/frames from the SDP and forwards them. The Tx context feeds cells/frames into the SDP for transmission. This CP also performs <u>OAM processing</u>.

#### 8.5.1 SDP

#### 8.5.1.1 ATM RxBit

The ATM RxBit processor extracts a bit stream from the PHY and passes it to SONET processor which strips off all the SONET overhead data. The RxBit is also responsible for detecting a SONET frame and notifying the SONET framer that it has found the correct A1/A2 sequence.

#### 8.5.1.2 FR RxBit

The FR RxBit does the following:

- Flag (0x7E) detection and packet extraction.

- Frame discard on detection of 7 or more consecutive 1's; notify this error to CPRC through extract space. Search for next Flag.

- Bit destuffing (removing 0 that occures after 5 consecutive 1's)

- Checking the packet alignment (packet remain byte boundary aligned after destuffing)

#### 8.5.1.3 ATM RxSync

ATM RxSync sends a payload type indication byte to RxByte stating that it has received an ATM cell. After the SONET framer strip SONET overhead, RxSync then extracts cells through Header Error Control (HEC) recognition. Immediately after successful cell header recognition, RxSync starts de-scrambling cells and checks to see if the cell is unassigned/idle (VPI=0 and VCI=0). If so, then the cell is discarded, and no further processing is necessary. All the other cells are forwarded to RxByte along with CRC10 flag. This flag eventually makes its way to CP that will discard all errored cells. The RxSync process gets its configuration parameters from control space as defined in section <u>ATM RxSync Control Space</u>.

Semiconductor, Inc

0

eescal

#### **DSLAM Application Note**

#### 8.5.1.4 FR RxSync

FR RxSync sends a payload-type indication byte to RxByte indicating that it is a FR frame. It then streams the bytes of the frame to RxByte. RxSync control space is not configurable from RC.

#### 8.5.1.5 RxByte

The RxByte processor receives a byte, which indicates that the incoming packet is an ATM cell or FR frame. Accordingly, RxByte performs the Byte-stream processing as follows:

#### ATM RxByte:

It parses the cell header to determine the cell type. When a cell arrives at the RxByte processor, it performs the following sequence of operations:

- Creates an ATM VC table lookup key using the cell header and the port number

- Examines the PTI field of the ATM header to determine the cell type, which may be user data, OAM, RM. This is done using a CAM match on the PTI bits.

- For all user data cells, a VC table lookup is launched

- Writes the cell header and cell status to the extract space

The XP configures each ATM port with a unique port number. RxByte is configured through control space as defined in section <u>RxByte Control space</u>. The RxByte processor writes information about incoming cells into extract space for the RC to use in its processing. The data structure is described in section <u>Extract Space</u>

#### FR RxByte:

For FR frames, RxByte processor fills the extract space with FR header field values and streams the payload into the buffer. The RxByte processor performs the following functions as part of the FR frame processing:

- Waits for a receive scope for extract space to be available.

- Receives bytes

- Launches a lookup based on the DLCI value in the FR header

- Streams the bytes into buffer

- When data9 (i.e., ninth bit is set in the incoming payload) is received, switches scope for extract space.

#### 8.5.1.6 TxByte

TxByte waits for valid data to appear in the FIFO from the CPRC. Once valid data is present and RC releases the merge space scope, it reads from merge space whether the packet, which has to be output, is an ATM cell or FR frame. Accordingly, it performs following activities:

#### ATM TxByte:

After receiving a cell, TxByte formats the cell and sends it to the large FIFO. It performs the following sequence of operations on every cell given to it for transmit:

- Read the cell header from the merge space and transmit it.

- Read the txType indicator. If it indicates an OAM cell, CRC-10 should be accumulated on each byte of the payload data.

- Read payloadLength field from the merge space and transmit that many bytes of payload data.

- If it is an OAM cell, append the accumulated CRC to the end of the payload.

#### FR TxByte:

- It initializes the CRC accumulator and begins processing the data. All data bytes output by the processing will also run through the CRC accumulator.

- Stream bytes from the FIFO until it receives an indication that there is no more valid data in the FIFO (that is, Data9).

- Now switches to the other scope of merge space.

#### 8.5.1.7 ATM TxBit

ATM TxBit monitors the data stream for out of frame signal and transmits the data to the output FIFO as a bit stream. TxBit is not configurable through control space.

#### 8.5.1.8 FR TxBit

FR TxBit performs following activities:

- Flag Generation (0x7E): Flag is sent as frame boundaries for every frame that is sent and during the idle time when there are no packets to send on the wire.

- Ensure that the Flag (0x7E) and the abort bytes (7 or more consecutive 1's) are not generated within the FR packet.

- Bit stuffing: To insert 0 after every five consecutive 1's that are read within byte of a packet. Five 1's needs not be byte aligned. This sequence can appear anywhere in the bit streams.

- Continuous transmission of flag (0x7E) bytes when there is no data to send

### 8.5.2 RC

The RC performs higher level processing of ATM cells or FR frames to determine where the packet descriptor that contains information about the packet and the buffer id to the actual packet in memory, needs to be sent next. The threads that run on the Oc3RC are described below.

#### 8.5.2.1 Oc3Receive

Based on the information from the extract space, Oc3Receive starts processing the packet. It checks whether the incoming packet is an ATM cell or a FR frame. Accordingly, it processes the packet as follows.

#### ATM Rx:

The ATM Rx function waits for results of the ATM VC table lookup launched by the RxByte. Depending on the results of this lookup the cell is forwarded to AAL5 RAS CP or ATM switched. It performs the following sequence of operations on each cell:

- Wait for an Rx scope, read the cell header, and cell status when the scope becomes available. If the cell status is set to an error, then the current cell is discarded.

- A message descriptor is created with bufType set to BT\_ATM and the buffer handle referring to the buffer handle of the newly arrived cell.

- If the cell status field indicates that this is an OAM or RM cell, it is forwarded to the XP.

- Wait for the ATM VC table lookup to return. This lookup contains information on how the cell should be treated. If the AAL5 flag bit is set in the flag field of the TLU lookup result, the cell is forwarded to the RAS CP.

- If no flag bits are set, this cell needs to be switched out to another ATM port. The

egress cell header from the VC table is written into the ATM cell header field of the

message descriptor. The CPRC then launches a port table lookup on the egress port

returned in the VC table lookup. The destination queue is determined from the port

table lookup and the cell is forwarded on to that queue.

#### FR Rx:

#### The FR Rx function does the following activities:

- It waits for the DLCI lookup response. If the lookup fails, silently drop the packet.

- Based on the FR table lookup response, the next level processing is identified (IP forwarding or FR switching).

- For IP packet, builds the descriptor with the appropriate fields and enqueue it to IP module.

- For the packet to be FR switched, it then queues the packet to FR queue for further processing.

#### 8.5.2.2 Oc3Transmit

Based on the information from the descriptor, Oc3Transmit starts processing the packet. It checks whether the outgoing packet is an ATM cell or a FR frame. Accordingly, it processes the packet as follows.

#### ATM Tx:

The ATM transmit function runs the following sequence of steps:

- Wait for a cell to arrive on the input queue. Dequeue it, read the cell header, and cell type.

- Allocate a Tx scope and copy the cell header, cell type and payload length in the merge space.

- Release the Tx scope thus starting the TxByte operations on the cell.

#### FR Tx:

The FR transmit function runs the following sequence of steps:

- Wait for a frame to arrive on the input queue. Dequeue it, read the FR header fields.

- The FR header has already been encapsulated by the FR CP

- Allocate a Tx scope and fills the merge space with header fields.

- Release the Tx scope thus starting the TxByte operations.

### 8.5.3 Data Structures

#### 8.5.3.1 ATM RxSync Control Space

The RxSync processor is configured through a structure in control space. The data structure has the following format:

| Byte Offset | 0        | 1        | 2     | 3   |

|-------------|----------|----------|-------|-----|

| 0           | DeltaCnt | alphaCnt | state | pad |

- deltaCnt specifies the number of cell header errors that the RxSync will tolerate before declaring a synchronization loss on the OC-3c link

- alphaCnt specifies the number of good cells that should be seen before RxSync goes in the ATM sync state

- state tells the current state of the link.

- pad unused

#### 8.5.3.2 RxByte Control Space

The RxByte processor is configured through a structure in control space. The data structure has the following format:

| Byte Offset | 0        | 1        | 2   | 3 |

|-------------|----------|----------|-----|---|

| 0           | portNumL | portNumU | pad |   |

| 4           | pad      |          |     |   |

- portNumL lower half of the port number corresponding to this CP

- portNumU upper half of the port number corresponding to this CP

- pad unused

#### 8.5.3.3 Extract Space

RxByte writes information about received cells/frames into extract space for the RC to use in its processing. The data structure has the following format:

```

typedef struct

int8u

packetType;

union {

typedef struct

{

int16u dlci;

int8u fecn; // congestion control bit

becn; // congestion control bit

int8u

int8u de; // congestion control bit (discard eligibility)

int8u cr;

// control and response field bit

int8u ea0: // extended address bit0

int8u ea1; // extended address bit1

} FrHeader;

typedef struct

CellHeader cellHeader:

int16u

vccIndex:

int8u

pduHdrStatus;

int8u

congestDrops;

int8

crc10Indicator;

int8u

encodedPti:

int8u

camValue;

int8u

pad1;

```

} AtmHeader; } packetInfo;

} extractSpc;

- packetType: To determine RC that incoming packet is an ATM cell or a FR frame

- FR header: FR header values, containing DLCI (data link connection identifier), congestion control bits (Fecn, Becn, discard eligibility, control and response field bit) and extended address bits (ea0, ea1)

- ATM header:

- o cellHeader the received cell header

- o vccIndex unused

- pduHdrStatus indicates success or error code following header processing

- congestDrops count of cells dropped due to congestion (RxByte could not get scope)

- o crc10Indicator indicates whether or not the CRC-10 value was corrent

- o encodedPti the PTI field from the cell header

- camValue used for OAM debug

- o pad unused

#### 8.5.3.4 Merge Space

The RC writes information about outgoing cells/frames into merge space for TxByte to use in its processing. The merge space is very specific to ATM cells as the FR frames do not need any processing at the TxByte level. They are streamed out to FR TxBit, which performs HDLC framing and Bit stuffing for FR frames.

The data structure has the following format:

| Byte Offset | 0 1 2 3                         |  |  |            |

|-------------|---------------------------------|--|--|------------|

| 0           | cellHeader                      |  |  |            |

| 4           | payloadLength txType packetType |  |  | packetType |

- PacketType: To determine TxByte whether the outgoing packet is an ATM cell or FR frame. If it is an ATM cell, then the merge space fields hold following meanings:

- cellHeader the outgoing header for ATM cells

- payloadLength negated payload length of the ATM cell, should always be –48

- txType non-zero for OAM cells, in which case CRC-10 is applied

- pad unused

### 8.6 IPv4 (CP12 & CP14)

CP12 and CP14 implement the IPv4 (Layer 3 forwarding) component for the DSLAM application. IP routing is the process of forwarding IP frames at layer 3 based upon the IP Destination Address (IP DA). An advantage of IP routing is that it can be used between dissimilar network media types. This application covers IP routing over ATM or Frame Relay.

Assumptions and notes for use:

- IP header options will not be recognized.

- IP Fragmentation and reassembly not supported

- Lookup is launched on the IP DA.

- Application generates two types of ICMP messages, which are based on the events that happen in the data path:

- o ICMP Time exceeded

- ICMP destination unreachable

The IP address is provided to the XP via the appData parameters in the shared HCA (Host Communication Area) structure. The XP passes this address to the CP in the initialization descriptor. The CP uses this as the IP source address for all NP generated ICMP messages.

#### 8.6.1 SDP

The SDP is configured for byte level re-circulation. The SDP re-circulates the IP packet to remove HDLC/FR encapsulation (if present) and validates the IP header. It also launches the IP destination address lookup to retrieve forwarding parameters for the datagram.

#### 8.6.1.1 TxByte

The TxByte processor performs the following functions:

- Receives IP datagram from BMU through DMEM

- Based on the Buffer Type, the following operations are done:

- o BT\_HDLC/BT\_FR: strips the respective headers and does IP parsing

- BT\_IP: Parses the IP header

- Sends control information about the datagram to RxByte processor, including the buffer handle, buffer type, and input port.

- Sends the IP datagram to RxByte processor

- Sends an end of packet byte which indicates errors if non-zero

- Switches scope and waits for more data to be available in DMEM.

The RC writes information about datagrams needing re-circulation into merge space for TxByte processor to use in its processing. The data structure is defined in section <u>Merge</u> <u>Space</u>. TxByte processor is not configurable through control space.

#### 8.6.1.2 RxByte

The RxByte processor performs the following functions:

- Waits for a receive scope to become available.

- Receives control information from TxByte processor and places it in extract space.

- Validates the IP header including version and header length and IP checksum and TTL field

- If the header is valid, launches a lookup of the IP destination address

- If the header is not valid, places an error code in the header status field of extract space and does not launch a lookup.

- If no error, TTL verification and TTL decrement operations are done and checksum modification is done and updated accordingly

- Streams the remaining payload to DMEM and writes the payload status field of extract space.

- Switches scope and waits for another to become available.

HCL TECHNOLOGIES HCL

The RxByte processor writes information about recirculated datagrams into extract space for the RC to use in its processing. The data structure is defined in <u>section Extract</u> <u>Space</u>. RxByte is not configurable through control space.

#### 8.6.2 RC

The IP forwarding component uses two threads to perform its task, namely, an input thread and an output thread. The initialization code starts the two threads. Each of these is described next.

#### 8.6.2.1 Initialization

The IP component does the following things during its initialization:

- Creates the input and output threads.

- Initializes the IP route lookup launched by the SDP

- Initializes both scopes by giving the SDP ownership

- Starts the SDP in byte loop back mode.

- Jumps to the first thread

#### 8.6.2.2 Input Thread

The input thread handles incoming datagrams. Specifically, it does the following:

- Monitors its queue.

- De-queues an IP descriptor.

- Increments a statistics counter

- Waits for a transmit scope to be available from the SDP.

- Fills in merge space with data from the descriptor including buffer handle and input port.

- Waits for the previous DMA transfer to complete.

- Begins the DMA transfer for the current buffer being processed

- Switch context to the next thread.

- Loops to the beginning to wait for another descriptor

#### 8.6.2.3 Output Thread

The output thread handles outgoing datagrams. Specifically, it does the following:

- Waits for a scope to become available from the SDP

- Begins the DMA transfer from DMEM to the SDRAM buffer indicated in extract space

- Checks for header errors, and if one has occurred, drops the packet and increments ipInHdrErrors counter. If the error is because of TTL expiry, ICMP time expired message is sent to the source.

- Waits for the IP route lookup to complete and if the lookup fails, drops the packet and increments ipOutNoRoutes counter. Send ICMP destination unreachable message to the source.

- Launches a lookup of the port indicated in the IP route lookup response.

- Waits for the port lookup to complete, and if the port is invalid, drops the packets and increments ipOutInvalidPortError counter.

- Fills in a descriptor using information from the IP route and port lookups

- Waits for the payload transfer to complete.

- Check for any payload error, if so drops the packet and increments ipOutPayloadError counter.

- Sends the descriptor to the appropriate destination determined by the lookups.

- Increments ipForwDatagrams counter

- Switches context to the next thread.

- Loops to the beginning to wait for another scope to be available

#### 8.6.3 Data Structures

#### 8.6.3.1 Merge space

The RC writes information about datagrams needing recirculation into merge space for TxByte processor to use in its processing. The data structure has the following format:

| Byte Offset | 0            | 1 | 2   | 3 |

|-------------|--------------|---|-----|---|

| 0           | bufHandle    |   |     |   |

| 4           | port_bufType |   | pad |   |

- bufHandle handle of the buffer being recirculated

- port\_bufType a bitmask defined as follows:

- o b12-5: port the input port on which this datagram was received

- b4-0: bufType the type of buffer being recirculated (could be one of BT\_IPv4, BT\_FR)

- pad unused

#### 8.6.3.2 Extract Space

RxByte writes information about re-circulated datagrams into extract space for the RC to use in its processing. Entire IP header is moved into the extract space. The first 8 bytes of the data structure has the following format:

| Byte Offset | 0            | 1 | 2           | 3            |

|-------------|--------------|---|-------------|--------------|

| 0           | bufHandle    |   |             |              |

| 4           | port_bufType |   | headerError | payloadError |

- bufHandle handle of the buffer being recirculated

- port\_bufType a bitmask defined as follows:

- o b12-5: port the input port on which this datagram was received

- b4-0: bufType the type of buffer being recirculated (could be BT\_IPv4)

The format of the next part of extract space

| Byte Offset | 0         | 1        | 2                | 3 |

|-------------|-----------|----------|------------------|---|

| 8           | vers_hlen | tos      | len              |   |

| 12          | id        |          | flags_fragOffset |   |

| 16          | ttl       | protocol | cks              |   |

| 20          | srcaddr   |          |                  |   |

| 24          | destaddr  |          |                  |   |

| 28-44       | pad       |          |                  |   |

- vers hlen header version and length •

- tos type of service •

- len IP total length

- id identification field •

- frags\_fragOffset fragmentation flags and offset •

- ttl time to live •

- protocol IP protocol

- cks IP header checksum •

- srcaddr IP source address •

- destaddr IP destination address

- Pad unused •

#### 8.6.3.3 **Queue Descriptor information**

One queue is allocated for IP module to communicate with other CPs and XPRC. The Queue descriptor structure is as follows:

| Byte Offset | 0         | 1     | 2            | 3 |  |

|-------------|-----------|-------|--------------|---|--|

| 0           | BufHandle |       |              |   |  |

| 4           | Le        | ength | Port_bufType |   |  |

| 8           | appData   |       |              |   |  |

| 12          | appData   |       |              |   |  |

The explanation of each field is as follows:

- bufHandle - handle to the buffer this descriptor describes

- length length of data in the buffer •

- port\_bufType a bit field structure as follows: •

- b12-5: port ingress port or egress port depending on descriptor type •

- b4-0: bufType the type of buffer

- appData application specific data as defined below:

Application specific data, it is a union of

- o int8u byte[8];

- o int16u hword[4];

- word[2]; o int32u

- o AtmDescData atm:

- o FrDescData frameRe;

- SegDescData seg; 0

#### **DSLAM Application Note**

The appData field can have different interpretations depending on the outgoing interface type.

The ATM appData field has the following format:

| Byte Offset | 0                   | 1 | 2 | 3 |

|-------------|---------------------|---|---|---|

| 0           | cellHeader          |   |   |   |

| 4           | VcIndex egressQueue |   |   |   |

The explanation of each field is as follows:

- cellHeader the cell header (VPI/VCI) to apply at the egress

- vcIndex the index associated with egress VPI/VCI

- egressQueue the egress queue, necessary as the cell passes through several processing blocks

The FrameRelay appData field has the following format:

| Byte Offset | 0               | 1 | 2 | 3 |

|-------------|-----------------|---|---|---|

| 0           | FrHeader        |   |   |   |

| 4           | EgressQueue pad |   |   |   |

The explanation of each field is as follows:

- FrHeader DLCI value

- EgressQueue Final Queue

- Pad unused

#### 8.6.3.4 Counters

IP module has these counters for statistics purpose; it's stored in XPRC's shared DMEM.

| S.No | Counter               | Purpose                                                                                                                               |

|------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 1.   | ipInReceives          | Total number packets received in IP module                                                                                            |

| 2.   | lpInHdrErrors         | The number of input datagrams discarded due to errors in their IP headers.                                                            |

| 3.   | IpForwDatagrams       | Number of input datagrams forwarded                                                                                                   |

| 4.   | IpOutPayloadError     | Number packets discarded due to payload errors                                                                                        |

| 5.   | IpOutInvalidPortError | Number of packets discarded because it route entry<br>mapped to egress port which is invalid (or temporarily<br>made as inaccessible) |

| 6.   | IpOutNoRoutes         | Number of IP datagrams discarded because no route could be found to transmit them to their destination                                |

#### 8.6.3.5 Ring Bus Slots

IPv4 uses these slots:

- IPv4 route request slot 0

- IPv4 route response 0

- Port request slot

- Port response slot 2

2

# 8.7 Segmentation (CP8 & CP10)

CP8 and CP10 implement AAL5 segmentation module. This CP gets message descriptors with bufType set to IPv4.

# 8.7.1 SDP

The SDP is configured for byte level re-circulation. It streams the IP packet and accumulates CRC. For AAL5 cells, it adds the necessary pad bytes to make the SDU length a multiple of 48 and creates the trailer. It then delivers fixed size chunks of the SDU to the CPRC. On the first chunk for an SDU, the SDP launches a port table lookup, whose results are used by the CPRC to determine the destination queue. The SDP does not interleave segmentations – it completely segments one SDU and delivers it to the CPRC before proceeding to the next SDU. The SDP accumulates payload CRC for all IP packets.

# 8.7.1.1 TxByte

The TxByte processor performs the following operations on every packet:

- Reads the segType, pduSize and UUI from the merge space. Sends them to RxByte processor

- Read all the merge space fields following it. Send them to RxByte processor.

- Initialize a counter with the negative of payload size.

- Start sending the payload bytes, incrementing the counter for each byte sent out. Accumulate CRC for each transmitted byte. Stop when the counter hits 0xff.

- Initialize a counter with the number of pad bytes.

- Start transmitting zeroes, incrementing this counter for every zero byte transmitted. Accumulate the CRC on each zero byte. Stop when the counter hits 0xff.

- The trailer should be sent for AAL-5 SDU. Send the UUI, CPI and payload length, accumulating the CRC on all of them. Now send the four bytes of the CRC. This completes the AAL5 trailer.

- Release the transmit scope and wait for data available from the RC.

TxByte gets the payload information from merge space as defined in <u>section Merge</u> <u>Space</u>. TxByte is not configurable through control space.

# 8.7.1.2 RxByte

The RxByte processor performs the following sequence of operations:

- Receive the segType, pduSize and uui from the TxByte and copy them to the extract space.

- Clear the lastCell flag.

- Receive the atmEgressQueue and destQueue from the TxByte and write them to the extract space.

- Receive the egress port from the TxByte and launch a port table lookup.

- Initialize a counter Counter1 with the negative of pduSize(0xc1).