# **STEPPER MOTOR (SM) TPU Function**

#### By Alphonso Gonzalez

## **1** Functional Overview

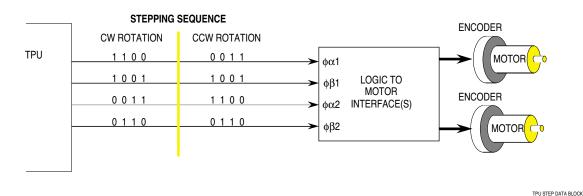

The stepper motor control function (SM) accelerates and decelerates a stepper motor linearly. Up to 14 step rates can be used. SM allows a stepper motor to rotate continuously or be used for discrete positioning. The CPU provides the desired step position in a 16-bit parameter, and the TPU steps the motor to the desired position using an acceleration/deceleration profile. The parameter indicating the desired position can be changed by the CPU while the TPU is stepping the motor. The algorithm can change control strategy each time a new step command is received.

A 16-bit parameter initialized by the CPU for each channel defines the output state of the pin. The bit pattern written by the CPU defines the method of stepping, such as full stepping or half stepping. With each transition, the 16-bit parameter rotates one bit. The period of each transition is defined by the programmed step rate.

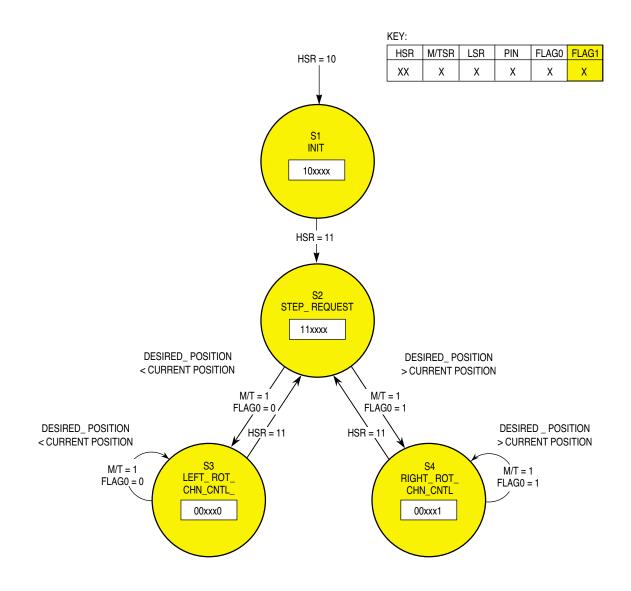

## **2 Detailed Description**

Any sequential group of up to eight channels can generate the control logic necessary to drive a stepper motor. A group of two or four TPU channels is used. There are two types of stepper motor channels: primary and secondary. The lowest numbered channel is the primary channel, or master, and the higher numbered channels are the secondary channels, or slaves. The secondary channels are serviced by the primary channel except during channel initialization.

To issue a step command, the CPU writes the desired step position to DESIRED\_POSITION and generates an HSR on the primary channel. CURRENT\_POSITION, containing the current step position, is updated continuously by the TPU as the motor is stepped. If DESIRED\_POSITION is greater than STEP\_RATE\_CNT steps from the CURRENT\_POSITION, the TPU accelerates the stepper motor by the programmed acceleration rate, steps at the run rate (maximum programmed rate), and then decelerates the stepper motor by the programmed acceleration rate, stopping at the desired position. If DESIRED\_POSITION is within STEP\_RATE\_CNT or fewer steps from the CURRENT\_POSITION, the TPU steps the motor to the position at the start/stop rate (minimum programmed rate).

The SM algorithm allows a change of the control strategy every time a new step command is received, i.e., every time DESIRED\_POSITION is changed. The advantages of this scheme become obvious when, for example, DESIRED\_POSITION is changed from step 50 to step 10, while stepping has proceeded from step 10 to step 30. Upon the change of DESIRED\_POSITION, the TPU decelerates the stepper motor, changes the direction of step, accelerates to the run rate, and decelerates to position 10.

The time period between steps (P) is defined by the following:

P(r) = K1- K2 \* r

where r is the current step rate (1–14), and K1 and K2 are programmable constants.

STEP\_CNTL0 and STEP\_CNTL1 define the linear acceleration rate. These parameters relate to K1 and K2 as shown in the following equation.

© Freescale Semiconductor, Inc., 2004. All rights reserved.

K1 = STEP\_CNTL1 – STEP\_CNTL0

K2 = STEP\_CNTL0

Thus,

## $P(r) = STEP_CNTL1 - STEP_CNTL0 * (1 + r)$

Timer TCR1 is used for matching; therefore, the weighting of the least significant bits (LSB) of STEP\_CNTL0 and STEP\_CNTL1 is defined to be equal to that of TCR1.

From one to fourteen step rates can be implemented. Two cases exist: STEP\_RATE\_CNT equals one, or STEP\_RATE\_CNT is more than one but less than 15. In both cases, when the host provides a new desired position and issues a step request, a delay of P(1) expires before the first step is taken. This delay ensures that the final step of the motor, due to a previous step request, is not disturbed before a time of P(1) has expired. P(1) is also the last programmed step rate used when decelerating to the final step position and the step rate at which a change of direction occurs. When STEP\_RATE\_CNT is one, P(1) represents the start/stop rate as well as the run rate.

When STEP\_RATE\_CNT is greater than one, P(1) is the step rate at which a change of direction in stepping will occur, P(2) is the start rate, and  $P_{(STEP_RATE_CNT)}$  is the run rate. When the condition for changing step direction arises, the stepper motor decelerates to step rate P(1), and the next step is taken in the opposite direction at step rate P(2). How these parameters are used is an important consideration when determining K1 and K2 constants.

PIN\_CONTROL associated with each SM channel determines the direction of stepping and whether full or half stepping is to be used. Whenever DESIRED\_POSITION is greater than CURRENT\_POSITION, the bit pattern of PIN\_CONTROL from least significant bit (LSB) to most significant bit (MSB) defines the output levels at the programmed step rates. Whenever DESIRED\_POSITION is less than CURRENT\_POSITION, the bit pattern of PIN\_CONTROL from MSB to LSB defines the output levels at the programmed step rates.

During initialization, SM employs CHANNEL\_CONTROL to configure the channel, using the data supplied by the host CPU. The TPU then fills CHANNEL\_CONTROL with a copy of PIN\_CONTROL for configuring the pin level. With each step taken, another bit of the copy of PIN\_CONTROL in CHANNEL\_CONTROL is used to configure the pin level, then CHANNEL\_CONTROL is rotated in the appropriate direction and written back. After rotating 16 bits to the left or right, CHANNEL\_CONTROL is again updated with PIN\_CONTROL.

### 2.1 Stepper Motor Initialization

In the following example, the stepper motor is assumed to be controlled by channels 4–7. Channel 4 is considered the master channel and channels 5, 6, and 7 are the secondary channels. The user should do the following:

- 1. Set each channel's function select register to the SM algorithm (write the SM function select value to address \$FFFE10).

- 2. Write the pin control bit pattern to each channel's pin control parameter (addresses \$YFFF42, \$YFFF52, \$YFFF62, and \$YFFF72). For full stepping, the parameters may be \$CCCC, \$3333, \$9999, and \$6666 for channels 4, 5, 6, and 7, respectively.

- 3. Set each channel control parameter (addresses \$YFFF40, \$YFFF50, \$YFFF60, and \$YFFF70) to operate with the appropriate TCR (typically TCR1) and configure pins as outputs. Force each initial pin state to be the same as bit 15 of the respective pin control parameter.

- 4. In the master channel, set the current position parameter to the presumed midpoint location (address \$YFFF44).

- 5. Set the next step rate to one and the modulo count to zero in the master channel (\$0001 to address \$YFFF48).

- 6. Set the last secondary channel number to seven (for channel number 7) and the step count to the number of different step rates (1 to 14) in the master channel (\$0x07 to address \$YFFF4A).

- 7. Set the step control parameters in the first secondary channel (channel number 5, addresses \$YFFF54, \$YFFF56).

STEP\_CNTL0 is the difference between the time interval of two adjacent steps during acceleration or deceleration (assuming the step rate count is > 1). With ten step rates, the period of the longest time interval is 4 ms, followed by intervals of 3.8, 3.6, 3.4, 3.2, 3.0, 2.8, 2.6, 2.4 ms and the rest of the intervals (until deceleration begins) are 2.2 ms between each step. The change in step rate is therefore 0.2 ms, and assuming that TCR1 increments every 10  $\mu$ s, STEP\_CNTL0 is set to (0.2 ms/ 10  $\mu$ s) = 20 TCR counts.

STEP\_CNTL1 is calculated from equation P(r), as follows:

$P(r) = STEP_CNTL1 - STEP_CNTL0 * (1 + r)$  $P(r) = STEP_CNTL1 - 20 * (1 + r)$

at r = 1; P(1) = 4.0 ms = 400 TCR counts

$400 = STEP_CNTL1 - (20 * 2)$

STEP\_CNTL1 = 400 + (20 \* 2)

- 8. If interrupts are desired, then set the interrupt enable bit for channel 4 by performing an OR between the contents of address \$YFFE0A and the value \$0010.

- 9. Execute an HSR for initialization of each channel by writing \$AA00 to address \$YFFE1A.

- 10. Turn on each channel by writing to the channel priority register (For mid priority, write \$AA00 to address \$YFFE1E).

The channels are now configured for operation. The initialization state sets the outputs to their initial levels. A step request is made by writing the new step destination into the desired position parameter of the master channel (address \$YFFF46) and by requesting a step from the HSR register (\$0300 to address \$YFFE1A).

Since stepper motor position is always relative to a start point, the motor is usually positioned or restored to a zero reference location. One technique is to initialize the desired position to zero, and the present position to beyond the maximum position, thereby causing the motor to step against a fixed stop from whatever location it is in when initialization takes place. Another method requires a zero-point switch or sensor. This positional reset is accomplished by interrupts. The master channel for the stepper motor algorithm is set to generate interrupts, and software flags keep track of the current operation. The algorithm generates an interrupt after initialization and after every step request.

#### 2.2 Stepper Motor Interrupts

Following is a sequence of pseudocode that uses a separate zero-point sensor to cause interrupts, saves the position of the stepper corresponding to the zero point, and sets the flag indicating that the motor has been zeroed (and clears the interrupt enable for the master stepper channel). Normal operation does not cause interrupts, but an attempt to return to the zero point causes an interrupt.

```

Clear interrupt flag

IF the stepper channel has been initialized THEN continue

ELSE

Set initialized flag

IF at point zero

THEN Set zeroed flag

Save zero location

```

```

Quit

ELSE Step request down

Set seek flag down

Quit

END IF

END IF

IF the stepper motor has been zeroed THEN continue

ELSE

(Note 1)

IF the seek flag is up

THEN Step request down

Set seek flag down

Ouit

ELSE Step request up

Set seek flag up

Quit

END IF

END IF

IF the stepper motor is still not zeroed

THEN

(Note 2)

Clear zeroed flag

IF the seek flag is up

THEN Step request down

Set seek flag down

Quit

ELSE Step request up

Set seek flag up

Ouit

END IF

ELSE

**No reason for interrupt**

Quit

```

```

END IF

```

```

NOTES:

```

- 1. Initialized but not zeroed. The interrupt must indicate that the first step request down is complete without encountering the zero switch (or possibly has already sought both directions and not encountered the zero sensor). The motor may be too far below the switch, and should, therefore, seek upwards (or down again).

- 2. This is an error case. Either the interrupt has no reason, or the zero point is not yet found (the motor is lost). In that case, begin seeking for the zero point.

## **3 Function Code Size**

Total TPU function code size determines what combination of functions can fit into a given ROM or emulation memory microcode space. SM function code size is:

$63 \mu$  instructions + 6 entries = 69 long words

## **4 Function Parameters**

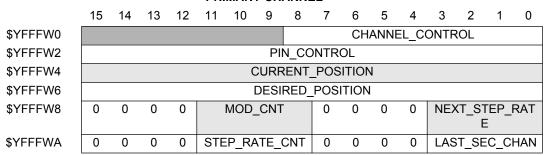

This section provides detailed descriptions of discrete input/output function parameters stored in channel parameter RAM. **Figure 1** shows TPU parameter RAM address mapping. **Figure 2** shows the parameter RAM assignment used by the SM function. In the diagrams, Y = M111, where M is the value of the module mapping bit (MM) in the system integration module configuration register (Y = \$7 or \$F).

| Channel | Base     |    |    | Par | amete | r Addr | ess |    |    |

|---------|----------|----|----|-----|-------|--------|-----|----|----|

| Number  | Address  | 0  | 1  | 2   | 3     | 4      | 5   | 6  | 7  |

| 0       | \$YFFF## | 00 | 02 | 04  | 06    | 08     | 0A  |    | _  |

| 1       | \$YFFF## | 10 | 12 | 14  | 16    | 18     | 1A  |    | _  |

| 2       | \$YFFF## | 20 | 22 | 24  | 26    | 28     | 2A  | _  | —  |

| 3       | \$YFFF## | 30 | 32 | 34  | 36    | 38     | 3A  |    | _  |

| 4       | \$YFFF## | 40 | 42 | 44  | 46    | 48     | 4A  | _  | _  |

| 5       | \$YFFF## | 50 | 52 | 54  | 56    | 58     | 5A  | _  | —  |

| 6       | \$YFFF## | 60 | 62 | 64  | 66    | 68     | 6A  |    | _  |

| 7       | \$YFFF## | 70 | 72 | 74  | 76    | 78     | 7A  | _  | —  |

| 8       | \$YFFF## | 80 | 82 | 84  | 86    | 88     | 8A  | _  | —  |

| 9       | \$YFFF## | 90 | 92 | 94  | 96    | 98     | 9A  |    | _  |

| 10      | \$YFFF## | A0 | A2 | A4  | A6    | A8     | AA  | _  | _  |

| 11      | \$YFFF## | B0 | B2 | B4  | B6    | B8     | BA  | _  | —  |

| 12      | \$YFFF## | C0 | C2 | C4  | C6    | C8     | CA  |    | _  |

| 13      | \$YFFF## | D0 | D2 | D4  | D6    | D8     | DA  | _  | —  |

| 14      | \$YFFF## | E0 | E2 | E4  | E6    | E8     | EA  | EC | EE |

| 15      | \$YFFF## | F0 | F2 | F4  | F6    | F8     | FA  | FC |    |

--- = Not Implemented (reads as \$00)

### Figure 1 TPU Channel Parameter RAM CPU Address Map

**Figure 2** shows all of the host interface areas for the SM function, described in **5 Host Interface to Function**, as well as the parameters, addresses, reference times, and reference sources. This segment lists and defines the parameters for all modes of the SM time function.

#### PRIMARY CHANNEL

#### **SECONDARY CHANNEL 1**

|          | 15 | 14         | 13 | 12 | 11 | 10 | 9   | 8    | 7    | 6  | 5    | 4     | 3    | 2   | 1 | 0 |

|----------|----|------------|----|----|----|----|-----|------|------|----|------|-------|------|-----|---|---|

| \$YFFFW0 |    |            |    |    |    |    |     |      |      | CH | ANNE | EL_CO | ONTR | ROL |   |   |

| \$YFFFW2 |    |            |    |    |    |    | PII | N_CC | NTR  | OL |      |       |      |     |   |   |

| \$YFFFW4 |    | STEP_CNTL0 |    |    |    |    |     |      |      |    |      |       |      |     |   |   |

| \$YFFFW6 |    |            |    |    |    |    | S   | TEP_ | CNTI | _1 |      |       |      |     |   |   |

| \$YFFFW8 |    |            |    |    |    |    |     |      |      |    |      |       |      |     |   |   |

| \$YFFFWA |    |            |    |    |    |    |     |      |      |    |      |       |      |     |   |   |

#### SECONDARY CHANNELS 2 — 7

|          | 15 | 14 | 13 | 12 | 11 | 10 | 9   | 8    | 7   | 6  | 5    | 4     | 3    | 2   | 1 | 0 |

|----------|----|----|----|----|----|----|-----|------|-----|----|------|-------|------|-----|---|---|

| \$YFFFW0 |    |    |    |    |    |    |     |      |     | CH | ANNE | EL_CO | ONTF | ROL |   |   |

| \$YFFFW2 |    |    |    |    |    |    | PII | N_CC | NTR | OL |      |       |      |     |   |   |

| \$YFFFW4 |    |    |    |    |    |    |     |      |     |    |      |       |      |     |   |   |

| \$YFFFW6 |    |    |    |    |    |    |     |      |     |    |      |       |      |     |   |   |

| \$YFFFW8 |    |    |    |    |    |    |     |      |     |    |      |       |      |     |   |   |

| \$YFFFWA |    |    |    |    |    |    |     |      |     |    |      |       |      |     |   |   |

Y= Channel number

Parameter Write Access:

| Written by CPU         |

|------------------------|

| Written by TPU         |

| Written by CPU and TPU |

| Unused parameters      |

#### **Figure 2 Function Parameter RAM Assignment**

### 4.1 CHANNEL\_CONTROL

The CPU must write CHANNEL\_CONTROL for the primary and for all secondary channels prior to initialization in order to establish initial PSC, PAC, and TBS fields. The PSC field forces the output level of the pin directly without affecting the pin action control latches and should be configured to force the same level as bit 15 of PIN\_CONTROL. The PAC field is not used. The following table defines the allowable data for this parameter. CHANNEL\_CONTROL PSC field should be initialized to the same level as the MSB of PIN\_CONTROL.

| 15 | 14 | 13 | 12      | 11 | 10 | 9 | 8 | 7  | 6 | 5 | 4 | 3   | 2 | 1  | 0  |  |

|----|----|----|---------|----|----|---|---|----|---|---|---|-----|---|----|----|--|

|    |    | N  | OT USED |    |    |   |   | TE |   |   |   | PAC |   | PS | SC |  |

| TBS     | PAC | PSC | Action            |                          |  |  |

|---------|-----|-----|-------------------|--------------------------|--|--|

| 8765    | 432 | 10  | Input             | Output                   |  |  |

|         |     | 0 1 | _                 | Force Pin High           |  |  |

|         |     | 10  | _                 | Force Pin Low            |  |  |

|         |     | 11  | —                 | Do Not Force Any State   |  |  |

| 01 x x  |     |     |                   | Output Channel           |  |  |

| 0100    |     |     | _                 | Capture TCR1, Match TCR1 |  |  |

| 0101    |     |     |                   | Capture TCR1, Match TCR2 |  |  |

| 0110    |     |     | _                 | Capture TCR2, Match TCR1 |  |  |

| 0111    |     |     | _                 | Capture TCR2, Match TCR2 |  |  |

| 1 x x x |     |     | Do Not Change TBS | Do Not Change TBS        |  |  |

SM CHANNEL\_CONTROL Options

After configuring the channel latches in initialization, the TPU fills CHANNEL\_CONTROL with a copy of PIN\_CONTROL, which later is used to configure the pin level. Each time the TPU services an SM channel, it rotates the content of CHANNEL\_CONTROL in the appropriate direction and then uses bit 15 of CHANNEL\_CONTROL to configure the pin level. After CHANNEL\_CONTROL is rotated 16 bits to the left or right, SM again copies PIN\_CONTROL into CHANNEL\_CONTROL.

## 4.2 PIN\_CONTROL

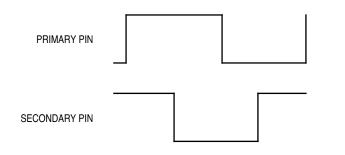

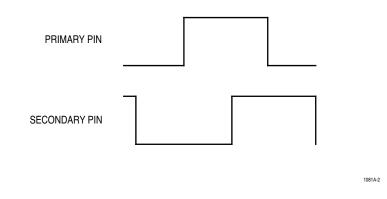

PIN\_CONTROL contains data representing the sequence of pin transitions. This 16-bit parameter must be initialized by the CPU for all channels used for stepper motor control. The bit pattern of the parameter indicates the sequence of output states of the pin. As an example for full-stepping sequence, typical parameters for two channels are \$3333 and \$9999. For half-stepping sequence, typical parameters are \$E0E0, \$0E0E, \$8383, and \$3838 for four successive channels, respectively. An illustrated example of PIN\_CONTROL data follows for full stepping a two-phase motor.

### 4.2.1 Primary Channel

| 15       | 14     | 13     | 12    | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 |  |

|----------|--------|--------|-------|----|----|---|---|---|---|---|---|---|---|--|

| 0        | 0      | 1      | 1     | 0  | 0  | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 |  |

| 4.2.2 Se | econda | ary Ch | annel |    |    |   |   |   |   |   |   |   |   |  |

| 15       | 14     | 13     | 12    | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 |  |

| 1        | 0      | 0      | 1     | 1  | 0  | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 |  |

When DESIRED\_POSITION is greater than CURRENT\_POSITION, the bit pattern from LSB to MSB defines the output levels at the programmed step rates, i.e., bit 0 is moved into bit 15, to define the output. The output pins are sequenced as shown.

When DESIRED\_POSITION is less than CURRENT\_POSITION, the bit pattern from MSB to LSB defines the output levels at the programmed step rates, i.e., bit 14 is moved into bit 15 to define the output. The output pins are sequenced as shown.

1081A-1

## 4.3 CURRENT\_POSITION

CURRENT\_POSITION contains the current step position of the stepper motor. This unsigned parameter is incremented or decremented each time CHANNEL\_CONTROL is rotated. In other words, in a fullstep configuration, each count represents a full step; in a half-step configuration, each count represents a half step.

## 4.4 DESIRED\_POSITION

DESIRED\_POSITION contains the desired position of the stepper motor and is updated by the CPU. The range for DESIRED\_POSITION is \$0 to (\$FFFF–STEP\_RATE\_CNT), unsigned.

## 4.5 LAST\_SEC\_CHAN

LAST\_SEC\_CHAN contains the channel number of the last secondary channel among the channels to be sequentially grouped, beginning with the primary channel, to synthesize the SM algorithm. The CPU updates this parameter. The upper four bits of this parameter must be set to zero.

## 4.6 STEP\_RATE\_CNT

STEP\_RATE\_CNT contains the number of step rates used in the acceleration/deceleration profile. The CPU updates this parameter to a value between 1 and 14 (\$1–\$E).

## 4.7 NEXT\_STEP\_RATE

NEXT\_STEP\_RATE contains the step rate to be programmed after the current step is complete. This parameter must be initialized to one by the CPU and is updated subsequently by the TPU.

### 4.8 MOD\_CNT

MOD\_CNT indicates the four-bit modulo count for the number of rotations that have occurred. MOD\_CNT must be initialized to \$0 by the CPU and subsequently is updated by the TPU. This parameter is incremented and decremented concurrently with CURRENT\_POSITION. When MOD\_CNT equals zero, PIN\_CONTROL is copied to CHANNEL\_CONTROL.

### 4.9 STEP\_CNTL0 and STEP\_CNTL1

STEP\_CNTL0 and STEP\_CNTL1, located in the first secondary channel, are updated by the CPU, and specify the acceleration/deceleration rate described earlier.

All 16 bits of STEP\_CNTL0 and STEP\_CNTL1 may be used in defining constants K1 and K2; however, the time period between steps P(r) must be less than \$8000 for all programmed step rates.

## **5 Host Interface to Function**

This section provides information concerning the TPU host interface to the function. **Figure 3** is a TPU address map. Detailed TPU register diagrams follow the figure. In the diagrams, Y = M111, where M is the value of the module mapping bit (MM) in the system integration module configuration register (Y =\$7 or \$F).

| Address  | 15 8 7 0                                      |

|----------|-----------------------------------------------|

| \$YFFE00 | TPU MODULE CONFIGURATION REGISTER (TPUMCR)    |

| \$YFFE02 | TEST CONFIGURATION REGISTER (TCR)             |

| \$YFFE04 | DEVELOPMENT SUPPORT CONTROL REGISTER (DSCR)   |

| \$YFFE06 | DEVELOPMENT SUPPORT STATUS REGISTER (DSSR)    |

| \$YFFE08 | TPU INTERRUPT CONFIGURATION REGISTER (TICR)   |

| \$YFFE0A | CHANNEL INTERRUPT ENABLE REGISTER (CIER)      |

| \$YFFE0C | CHANNEL FUNCTION SELECTION REGISTER 0 (CFSR0) |

| \$YFFE0E | CHANNEL FUNCTION SELECTION REGISTER 1 (CFSR1) |

| \$YFFE10 | CHANNEL FUNCTION SELECTION REGISTER 2 (CFSR2) |

| \$YFFE12 | CHANNEL FUNCTION SELECTION REGISTER 3 (CFSR3) |

| \$YFFE14 | HOST SEQUENCE REGISTER 0 (HSQR0)              |

| \$YFFE16 | HOST SEQUENCE REGISTER 1 (HSQR1)              |

| \$YFFE18 | HOST SERVICE REQUEST REGISTER 0 (HSRR0)       |

| \$YFFE1A | HOST SERVICE REQUEST REGISTER 1 (HSRR1)       |

| \$YFFE1C | CHANNEL PRIORITY REGISTER 0 (CPR0)            |

| \$YFFE1E | CHANNEL PRIORITY REGISTER 1 (CPR1)            |

| \$YFFE20 | CHANNEL INTERRUPT STATUS REGISTER (CISR)      |

| \$YFFE22 | LINK REGISTER (LR)                            |

| \$YFFE24 | SERVICE GRANT LATCH REGISTER (SGLR)           |

| \$YFFE26 | DECODED CHANNEL NUMBER REGISTER (DCNR)        |

Figure 3 TPU Address Map

| CH         Interrupt Enable           0         Channel interrupts disabled           1         Channel interrupts enabled           CFSR[0:3]         Channel Function Select Registers         SYFFEOC - \$YFF           15         14         13         12         11         10         9         8         7         6         5         4         3         2         1           CFS(CH 15, 11, 7, 3)         CFS(CH 14, 10, 6, 2)         CFS(CH 13, 9, 5, 1)         OFS(CH 12, 8, 4, 0)         CFS(CH 13, 9, 5, 1)         OFS(CH 12, 8, 4, 0)           CFS(I)         SM Function Number (Assigned during microcode assembly)         HSQR[0:1]         Host Sequence Registers         SYFFE14 - \$YFF           15         14         13         12         11         0         9         8         7         6         5         4         3         2         1           0H 15, 7         CH 14, 6         CH 13, 5         CH 12, 4         CH 11, 3         CH 10, 2         CH 9, 1         CH 8, 1           14         13         12         11         0         9         8         7         6         5         4         3         2         1           CH         Initialization         11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4       CH 12       CH 11       CH 10       CH 9       CH 8       CH 7       CH 6       CH 4       CH 3       CH 2       CH 1       CH 0         0       Channel interrupts disabled       0       Channel interrupts disabled       0       Channel interrupts disabled         -       Channel Function Select Registers       \$YFFE0C - \$YFFE1       \$YFFE0C - \$YFFE1         13       12       11       10       9       8       7       6       5       4       3       2       1       0         -       Channel Function Select Registers       SYFFE14 - \$YFFE1       0       0       CFS (CH 13, 9, 5, 1)       0       0       0       0       0       15, 11, 7, 3)       0       0       0       0       0       0       0       0       0       15, 11, 7, 3)       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CIER –  | - Chan        | nel Inte    | errupt E | nable    | Regis     | ter          |        |         |           |             |       |      |         | \$YF        | FE0  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------|-------------|----------|----------|-----------|--------------|--------|---------|-----------|-------------|-------|------|---------|-------------|------|

| CH         Interrupt Enable           0         Channel interrupt Sisabled           1         Channel interrupt senabled           SFSR[0:3]         Channel Function Select Registers         SYFFEOC - \$YFF           15         14         13         12         11         0         9         8         7         6         5         4         3         2         1           CFS (CH 15, 11, 7, 3)         CFS (CH 14, 10, 6, 2)         CFS (CH 13, 9, 5, 1)         CFS (CH 12, 8, 4, 0)         SYFFE14 - \$YFF           ISFS[4:0]         — Mot Sequence Registers         SYFFE14 - \$YFF         SYFFE14 - \$YFF         SYFFE14 - \$YFF           15         14         13         12         11         0         9         8         7         6         5         4         2         1           CH 15, 7         CH 14, 6         CH 13, 5         CH 12, 4         CH 11, 3         CH 10, 2         CH 9, 1         CH 8, 1           Isrn(1:0)         — Host Service Request         SYFFE18 - \$YFF         16         14         13         12         11         10         9         8         7         6         5         4         3         2         1           CH 15, 7         CH 14, 6<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | CH         Interrupt Enable           0         Channel interrupts disabled           1         Channel interrupts disabled           1         Channel interrupts enable           -         Channel interrupts enabled           -         Channel interrupt enabled           -         Host Sequence Registers           -         Host Service Request           13         12           14         10           0         No Host Service Request           10         Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 15      | 14            | 13          | 12       | 11       | 10        | 9            | 8      | 7       | 6         | 5           | 4     | 3    | 2       | 1           | 0    |

| 0         Channel interrupts disabled<br>1           2;FSR[0:3] — Channel Function Select Registers         \$YFFEOC - \$YFF           15         14         13         12         11         10         9         8         7         6         5         4         3         2         1           15         14         13         12         11         10         9         8         7         6         5         4         3         2         1           15         14         13         12         11         10         9         8         7         6         5         4         3         2         1           16         14         13         12         11         10         9         8         7         6         5         4         3         2         1           16         14         13         12         11         10         9         8         7         6         5         4         3         2         1           16         14         13         12         11         10         9         8         7         6         5         4         3         2         1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0         Channel interrupts disabled           1         Channel interrupts enabled           - Channel Function Select Registers         \$YFFE0C - \$YFFE1           13         12         11         0         9         8         7         6         5         4         3         2         1         0           115, 11, 7, 3)         CFS (CH 14, 16, 2)         CFS (CH 13, 9, 5, 1)         CFS (CH 12, 8, 4, 0)         SM           SM Function Number (Assigned during microcode assembly)         -         Host Sequence Registers         \$YFFE14 - \$YFFE1           13         12         11         10         9         8         7         6         5         4         3         2         1         0           - Host Sequence Registers         \$YFFE14 - \$YFFE1         CH 13, 5         CH 12, 4         CH 11, 3         CH 10, 2         CH 9, 1         CH 8, 0           - Host Service Request Registers         \$YFFE18 - \$YFFE1         3         2         1         0           - CH         Initialization         0         CH 10, 2         CH 9, 1         CH 8, 0           - 11         No Host Service Request         01         No Host Service Request         0         0           - Channel Priority                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CH 15   | CH 14         | CH 13       | CH 12    | CH 11    | CH 10     | CH 9         | CH 8   | CH 7    | CH 6      | CH 5        | CH 4  | CH 3 | CH 2    | CH 1        | CH   |

| 0         Channel interrupts disabled           1         Channel interrupts disabled           1         Channel interrupts enabled           2F\$R[0:3] — Channel Function Select Registers         \$YFFE0C - \$YFF           15         14         13         12         11         10         9         8         7         6         5         4         3         2         1           CFS (CH 15, 11, 7, 3)         CFS (CH 14, 10, 6, 2)         CFS (CH 13, 9, 5, 1)         CFS (CH 12, 4, 40)           JSFS[1:1] — Host Sequence Registers         SYFFE14 - \$YFF           15         14         13         12         11         10         9         8         7         6         5         4         3         2         1           16         14         13         12         11         10         9         8         7         6         5         4         3         2         1           16         14         13         12         11         10         9         8         7         6         5         4         3         2         1           CH         Initialization         0         No Host Service Request         01         No Host Servic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0         Channel interrupts disabled           1         Channel interrupts enabled           - Channel Function Select Registers         \$YFFE0C - \$YFFE1           13         12         11         0         9         7         6         5         4         3         2         1         0           115, 11, 7, 3)         CFS (CH 14, 16, 2)         CFS (CH 13, 9, 5, 1)         CFS (CH 12, 8, 4, 0)         SM           SM Function Number (Assigned during microcode assembly)         -         Host Sequence Registers         \$YFFE14 - \$YFFE1           13         12         11         10         9         8         7         6         5         4         3         2         1         0           - Host Sequence Registers         \$YFFE14 - \$YFFE1         CH 13, 5         CH 12, 4         CH 11, 3         CH 10, 2         CH 9, 1         CH 8, 0           uence encodings are implemented for the SM function.         -         Host Service Request         \$YFFE18 - \$YFFE1           13         12         11         10         9         8         7         6         5         4         3         2         1         0           CH         Initialization         0         Initialization         10<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |               |             |          |          | 011       |              |        | l 1     |           |             |       |      |         |             |      |

| 1       Channel interrupts enabled         SYFFEOC - \$YFF         15       14       13       12       11       10       9       8       7       6       5       4       3       2       1         CFS (CH 15, 11, 7, 3)       CFS (CH 14, 10, 6, 2)       CFS (CH 13, 9, 5, 1)       CFS (CH 13, 9, 5, 1)       CFS (CH 12, 8, 4, 0)         CFS (CH 15, 11, 7, 3)       CFS (CH 14, 10, 6, 2)       CFS (CH 13, 9, 5, 1)       CFS (CH 12, 8, 4, 0)         CFS (CH 15, 11, 7, 3)       CFS (CH 13, 9, 5, 1)       CFS (CH 12, 8, 4, 0)         CFS (CH 15, 11, 7, 3)       CFS (CH 12, 8, 4, 0)         CFS (CH 13, 9, 5, 1)       CFS (CH 12, 8, 4, 0)         CFS (CH 14, 16, 6, 2)       CFS (CH 12, 4, 0)         CH 11, 3       CH 10, 2       CH 9, 1       CH 8, 0         CH 11, 3       CH 10, 2       CH 9, 1       CH 6         CH       Initialization         00       No Host Service Request         10 <t< td=""><td>1       Channel interrupts enabled         - Channel Function Select Registers       \$YFFE0C - \$YFFE1         13       12       11       10       9       8       7       6       5       4       3       2       1       0         115,11,7,3)       CF5 (CH 14, 10, 6, 2)       CF5 (CH 13, 9, 5, 1)       CF5 (CH 12, 8, 4, 0)       SM Function Number (Assigned during microcode assembly)         Host Sequence Registers       \$YFFE14 - \$YFFE1         13       12       11       10       9       8       7       6       5       4       3       2       1       0         Host Sequence Registers       \$YFFE14 - \$YFFE1       SYFFE14 - \$YFFE1       1       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0</td></t<> <td></td> <td>blod</td> <td>_</td> <td></td> <td></td> <td></td>                                                                                                                                                                                              | 1       Channel interrupts enabled         - Channel Function Select Registers       \$YFFE0C - \$YFFE1         13       12       11       10       9       8       7       6       5       4       3       2       1       0         115,11,7,3)       CF5 (CH 14, 10, 6, 2)       CF5 (CH 13, 9, 5, 1)       CF5 (CH 12, 8, 4, 0)       SM Function Number (Assigned during microcode assembly)         Host Sequence Registers       \$YFFE14 - \$YFFE1         13       12       11       10       9       8       7       6       5       4       3       2       1       0         Host Sequence Registers       \$YFFE14 - \$YFFE1       SYFFE14 - \$YFFE1       1       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |               |             |          |          |           |              |        |         |           |             | blod  | _    |         |             |      |

| CFSR[0:3] Channel Function Select Registers       \$YFFE0C - \$YFF         15       14       13       12       11       10       9       8       7       6       5       4       3       2       1         CFS (CH 15, 11, 7, 3)       CFS (CH 14, 10, 6, 2)       CFS (CH 13, 9, 5, 1)       CFS (CH 12, 8, 4, 0)         CFS (CH 15, 11, 7, 3)       CFS (CH 13, 9, 5, 1)       CFS (CH 12, 8, 4, 0)         CFS (CH 15, 17, 7)       M Function Number (Assigned during microcode assembly)         HSQR[0:1] Host Sequence Registers       \$YFFE14 - \$YFF         15       14       13       12       11       10       9       8       7       6       5       4       3       2       1         CH 15, 7       CH 14, 6       CH 13, 5       CH 12, 4       CH 11, 3       CH 10, 2       CH 9, 1       CH 8,         Vo host sequence encodings are implemented for the SM function.       HSR[1:0] Host Service Request Registers       \$YFFE16 - \$YFF       15       14       13       12       11       10       9       8       7       6       5       4       3       2       1         CH       Initialization       11       Step Request       SYFFE1C - \$YFF       15       14       13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | - Channel Function Select Registers       \$YFFE0C - \$YFFE1         13       12       11       10       9       8       7       6       5       4       3       2       1       0         115, 11, 7, 3)       0FS (CH 14, 10, 6, 2)       0FS (CH 13, 9, 5, 1)       0FS (CH 12, 8, 4, 0)         SM Function Number (Assigned during microcode assembly)         Host Sequence Registers       \$YFFE14 - \$YFFE1         13       12       11       10       9       8       7       6       5       4       3       2       1       0         Host Sequence Registers       \$YFFE14 - \$YFFE1       13       12       11       0       9       8       7       6       5       4       3       2       1       0         uence encodings are implemented for the SM function.       -       -       Hot 11, 3       CH 10, 2       CH 9, 1       CH 8, 0         0       CH 13, 5       CH 12, 4       CH 11, 3       CH 10, 2       CH 9, 1       CH 8, 0         13       12       11       10       9       8       7       6       5       4       3       2       1       0         Channel Priority Registers       SYFFE1C - \$YFFE1 </td <td></td> <td>_</td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |               |             |          |          |           |              |        |         |           |             |       | _    |         |             |      |

| 15       14       13       12       11       10       9       8       7       6       5       4       3       2       1         CFS (CH 15, 11, 7, 3)       CFS (CH 14, 10, 6, 2)       CFS (CH 13, 9, 5, 1)       CFS (CH 12, 8, 4, 0)         CFS (CH 15, 11, 7, 3)       CFS (CH 14, 10, 6, 2)       CFS (CH 13, 9, 5, 1)       CFS (CH 12, 8, 4, 0)         CFS (CH 15, 11, 7, 3)       CFS (CH 14, 10, 6, 2)       CFS (CH 13, 9, 5, 1)       CFS (CH 12, 8, 4, 0)         CFS (CH 15, 11, 7, 3)       HSCR[0:1]       HOS Sequence Registers       \$YFFE14 - \$YFF         15       14       13       12       11       10       9       8       7       6       5       4       3       2       1         0H 15, 7       CH 14, 6       CH 13, 5       CH 12, 4       CH 11, 3       CH 10, 2       CH 9, 1       CH 8,         Vo host sequence encodings are implemented for the SM function.       #       SYFFE18 - \$YFF       15       14       13       12       11       10       9       8       7       6       5       4       3       2       1         CH       Initialization       11       Step Request       10       Initialization       1       1       1       1 <td>13       12       11       10       9       8       7       6       5       4       3       2       1       0         115, 11, 7, 3)       CFS (CH 14, 10, 6, 2)       CFS (CH 13, 9, 5, 1)       CFS (CH 12, 8, 4, 0)         SYFFE14 - \$YFFE1         13       12       11       10       9       8       7       6       5       4       3       2       1       0         - Host Sequence Registers       SYFFE14 - \$YFFE1         13       12       11       10       9       8       7       6       5       4       3       2       1       0         UP (CH 13, 5       CH 12, 4       CH 11, 3       CH 10, 2       CH 9, 1       CH 8, 0         UP (CH 13, 5       CH 12, 4       CH 11, 3       CH 10, 2       CH 9, 1       CH 8, 0         CH       Initialization         00       No Host Service Request       01       No Host Service Request         13       12       11       10       9       8       7       6       5       4       3       2       1       0         CH       Initialization         1</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>1</td> <td></td> <td></td> <td>Channe</td> <td>rinterru</td> <td></td> <td>ableu</td> <td></td> <td></td> <td></td> <td></td> | 13       12       11       10       9       8       7       6       5       4       3       2       1       0         115, 11, 7, 3)       CFS (CH 14, 10, 6, 2)       CFS (CH 13, 9, 5, 1)       CFS (CH 12, 8, 4, 0)         SYFFE14 - \$YFFE1         13       12       11       10       9       8       7       6       5       4       3       2       1       0         - Host Sequence Registers       SYFFE14 - \$YFFE1         13       12       11       10       9       8       7       6       5       4       3       2       1       0         UP (CH 13, 5       CH 12, 4       CH 11, 3       CH 10, 2       CH 9, 1       CH 8, 0         UP (CH 13, 5       CH 12, 4       CH 11, 3       CH 10, 2       CH 9, 1       CH 8, 0         CH       Initialization         00       No Host Service Request       01       No Host Service Request         13       12       11       10       9       8       7       6       5       4       3       2       1       0         CH       Initialization         1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |               |             |          |          | 1         |              |        | Channe  | rinterru  |             | ableu |      |         |             |      |

| CFS (CH 15, 11, 7, 3)         CFS (CH 14, 10, 6, 2)         CFS (CH 13, 9, 5, 1)         CFS (CH 12, 8, 4, 0)           CFS (21) — SM Function Number (Assigned during microcode assembly)         HSQR[0:1] — Host Sequence Registers         \$YFFE14 - \$YFF           15         14         13         12         11         10         9         8         7         6         5         4         3         2         1           15         14         13         12         11         10         9         8         7         6         5         4         3         2         1           CH 15, 7         CH 14, 6         CH 13, 5         CH 12, 4         CH 11, 3         CH 10, 2         CH 9, 1         CH 8,           No host sequence encodings are implemented for the SM function.         HSRR[1:0] — Host Service Request Registers         \$YFFE18 - \$YFF           15         14         13         12         11         10         9         8         7         6         5         4         3         2         1           CH         Initialization         00         No Host Service Request         01         No Host Service Request         01         11         S         1           CPR[1:0] — Channel Priority Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | I15, I1, 7, 3)       CFS (CH 14, 10, 6, 2)       CFS (CH 13, 9, 5, 1)       CFS (CH 12, 8, 4, 0)         SM Function Number (Assigned during microcode assembly)       -       Host Sequence Registers       \$YFFE14 - \$YFFE1         13       12       11       10       9       8       7       6       5       4       3       2       1       0         CH 14, 6       CH 13, 5       CH 12, 4       CH 11, 3       CH 10, 2       CH 9, 1       CH 8, 0         uence encodings are implemented for the SM function.       -       Host Service Request Registers       \$YFFE18 - \$YFFE1         13       12       11       10       9       8       7       6       5       4       3       2       1       0         Uence encodings are implemented for the SM function.       -       Host Service Request       \$YFFE18 - \$YFFE1       13       12       1       0       9       7       6       5       4       3       2       1       0         CH       Initialization       0       Initialization       11       10       10       11       10       10       10       10       10       10       10       10       10       10       10       10       10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CFSR[(  | D:3] —        | Chann       | el Fun   | ction S  | elect F   | Registe      | rs     |         |           |             |       | \$Y  | FFE00   | C – \$YI    | FFE1 |

| CFS[4:0] — SM Function Number (Assigned during microcode assembly)         SYFFE14 – \$YFF         15       14       13       12       11       10       9       8       7       6       5       4       3       2       1         15       14       13       12       11       10       9       8       7       6       5       4       3       2       1         CH 15, 7       CH 14, 6       CH 13, 5       CH 12, 4       CH 11, 3       CH 10, 2       CH 9, 1       CH 8,         No host sequence encodings are implemented for the SM function.       HSRE[1:0]       Host Service Request Registers       SYFFE18 - \$YFF         15       14       13       12       11       10       9       8       7       6       5       4       3       2       1         CH       Initialization       Initial                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | M Function Number (Assigned during microcode assembly)         - Host Sequence Registers       \$YFFE14 - \$YFFE1         13       12       11       10       9       8       7       6       5       4       3       2       1       0         CH 14, 6       CH 13, 5       CH 12, 4       CH 11, 3       CH 10, 2       CH 9, 1       CH 8, 0         uence encodings are implemented for the SM function.       -       Host Service Request Registers       \$YFFE18 - \$YFFE1         13       12       11       10       9       8       7       6       5       4       3       2       1       0         - Host Service Request Registers       \$YFFE18 - \$YFFE1       13       12       11       10       9       8       7       6       5       4       3       2       1       0         00       CH 11, 5       CH 12, 4       CH 11, 3       CH 0, 1       CH 9, 1       CH 8, 0         01       No Host Service Request       10       Initialization       11       1       0         13       12       11       10       9       8       7       6       5       4       3       2       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 15      | 14            | 13          | 12       | 11       | 10        | 9            | 8      | 7       | 6         | 5           | 4     | 3    | 2       | 1           | 0    |

| HSQR[0:1] Host Sequence Registers       \$YFFE14 \$YFF         15       14       13       12       11       10       9       8       7       6       5       4       3       2       1         15       14       13       12       11       10       9       8       7       6       5       4       3       2       1         15       14       13       12       11       10       9       8       7       6       5       4       3       2       1         CH 15, 7       CH 14, 6       CH 13, 5       CH 12, 4       CH 11, 3       CH 10, 2       CH 9, 1       CH 8, 1         To 6       5       4       3       2       1         CH iso CH 13, 5       CH 12, 4       CH 11, 3       CH 10, 2       CH 9, 1       CH 8, 1         CH       Initialization         00       Initialization       10       Initialization       11       11       Step Request       10       11       11       11       11       14       3       2       1       14       13       12       11       10       9       8       7       <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Host Sequence Registers       \$YFFE14 - \$YFFE1         13       12       11       10       9       8       7       6       5       4       3       2       1       0         CH 14, 6       CH 13, 5       CH 12, 4       CH 11, 3       CH 10, 2       CH 9, 1       CH 8, 0         uence encodings are implemented for the SM function.       -       Host Service Request Registers       \$YFFE18 - \$YFFE1         13       12       11       10       9       8       7       6       5       4       3       2       1       0         - Host Service Request Registers       \$YFFE18 - \$YFFE1       13       12       11       0       9       8       7       6       5       4       3       2       1       0         CH       Initialization       00       No Host Service Request       10       11       CH 8, 0         Channel Priority Registers       \$YFFE1C - \$YFFE1       13       12       11       10       9       8       7       6       5       4       3       2       1       0         Channel Priority       00       Disabled       01       Low       10       11       Ha, 0 </td <td>C</td> <td>CFS (CH 15</td> <td>, 11, 7, 3)</td> <td></td> <td>(</td> <td>CFS (CH 1</td> <td>4, 10, 6, 2)</td> <td></td> <td></td> <td>CFS (CH ·</td> <td>13, 9, 5, 1</td> <td>)</td> <td></td> <td>CFS (CH</td> <td>12, 8, 4, 0</td> <td>)</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | C       | CFS (CH 15    | , 11, 7, 3) |          | (        | CFS (CH 1 | 4, 10, 6, 2) |        |         | CFS (CH · | 13, 9, 5, 1 | )     |      | CFS (CH | 12, 8, 4, 0 | )    |

| 15       14       13       12       11       10       9       8       7       6       5       4       3       2       1         CH 15, 7       CH 14, 6       CH 13, 5       CH 12, 4       CH 11, 3       CH 10, 2       CH 9, 1       CH 8, 0         No host sequence encodings are implemented for the SM function.       HSRR[1:0] — Host Service Request Registers       \$YFFE18 - \$YFF         15       14       13       12       11       10       9       8       7       6       5       4       3       2       1         CH 15, 7       CH 14, 6       CH 13, 5       CH 12, 4       CH 11, 3       CH 10, 2       CH 9, 1       CH 8, 1         CH       Initialization       00       No Host Service Request       01       No Host Service Request         10       Initialization       11       Step Request       SYFFE1C - \$YFF         15       14       13       12       11       10       9       8       7       6       5       4       3       2       1         CPR[1:0]       — Channel Priority Registers       SYFFE1C - \$YFF       15       14       13       12       11       10       9       8       7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 13       12       11       10       9       8       7       6       5       4       3       2       1       0         CH 14, 6       CH 13, 5       CH 12, 4       CH 11, 3       CH 10, 2       CH 9, 1       CH 8, 0         uence encodings are implemented for the SM function.       -       Hot Service Request Registers       \$YFFE18 - \$YFFE1         13       12       11       10       9       8       7       6       5       4       3       2       1       0         CH 14, 6       CH 13, 5       CH 12, 4       CH 11, 3       CH 10, 2       CH 9, 1       CH 8, 0         CH       Initialization         00       No Host Service Request       01       Initialization         10       Initialization       11       Step Request       0         Channel Priority Registers         Channel Priority         00       Disabled       01       CH 10, 2       CH 9, 1       CH 8, 0         CH       Channel Priority         00       Disabled       01       Low       01       CH 8, 0         10       Middle       11       High       2       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CFS[4:0 | 0] — SM       | / Fund      | ction N  | umber    | (Assig    | ned du       | ring m | nicroco | de ass    | embly)      | )     |      |         |             |      |