Next-Generation Digital Signal Processors

November 2010

Beyond DSPS Giving Customers Another Choice

INCLUDING

StarCore MSC8xxx and DSP56K Families (Including Symphony Audio DSPs)

| History of Freescale/Motorola DSPs 2                                                                                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Technical Highlights:</b> A closer look at the StarCore DSP families 3                                                                                                                                                                    |

| MSC815x and MSC825x Family Overview4StarCore DSP Roadmap6SC3850 Core7DSP Core Subsystem9MAPLE-B11CLASS Fabric12RISC-Based QUICC Engine Subystem13Serial RapidIO® Architecture14PCI Express® Controller15DDR2/316Time-Division Multiplexing17 |

| Application Solutions 18                                                                                                                                                                                                                     |

| Wireless Base Stations19Video20Voice22Medical Imaging24Aerospace and Defense26Advanced Test and Measurement28                                                                                                                                |

| Development Software, Tools and Reference Designs30                                                                                                                                                                                          |

| CodeWarrior Development Studio for StarCore 10.0 DSPs.31Voice Software32Video Software32Base Station Software33MSC8156 Evaluation Module35MSC8156ADS37MSC8156AMC39P2020-MSC8156 AdvancedMC™ Reference Design41                               |

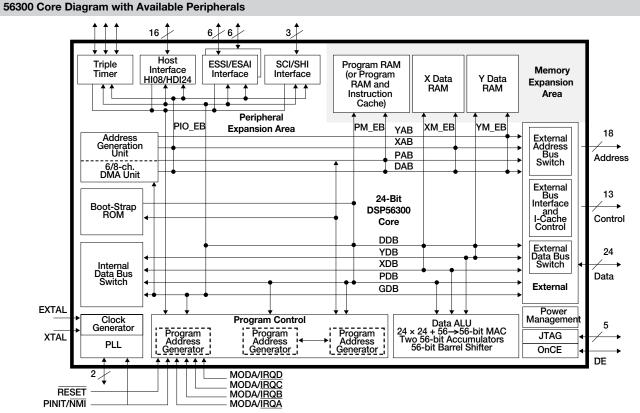

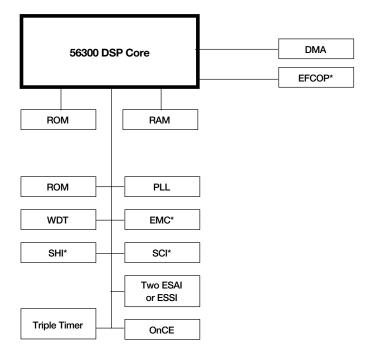

| Technical Highlights: A closer look at the DSP56K families43                                                                                                                                                                                 |

| DSP56K Family Overview44DSP56K Core45Application Solutions48                                                                                                                                                                                 |

| DSP56K Family Development Software,<br>Tools and Reference Designs 49                                                                                                                                                                        |

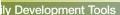

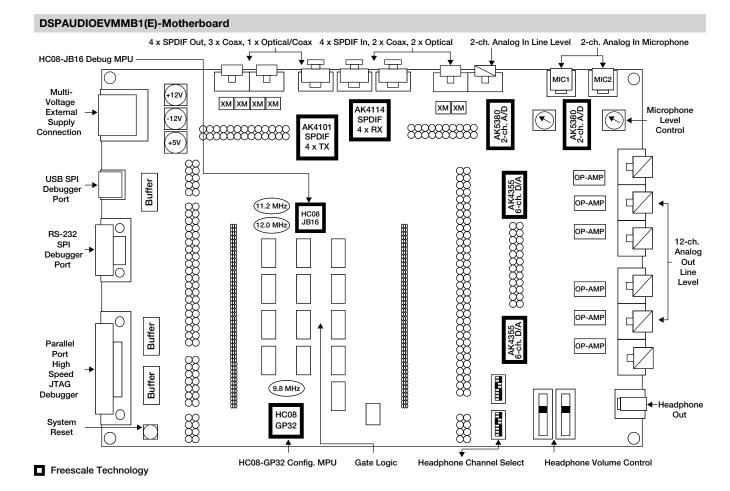

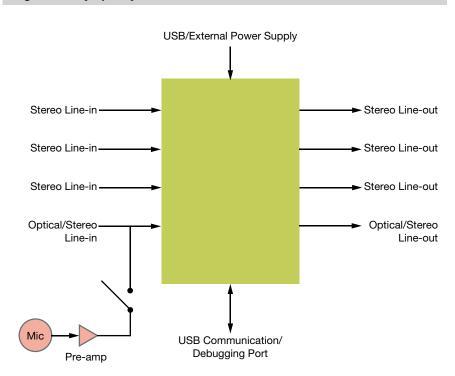

| Development Software50DSPAUDIOEVM Evaluation Module51Symphony SoundBite Development Kit52DSP563xx Evaluation Module (DSP563xxEVME)54Additional Resources56Ecosystem Partners56                                                               |

This document contains information on a new product. Specifications and information herein are subject to change without notice.

#### Freescale DSP Evolution

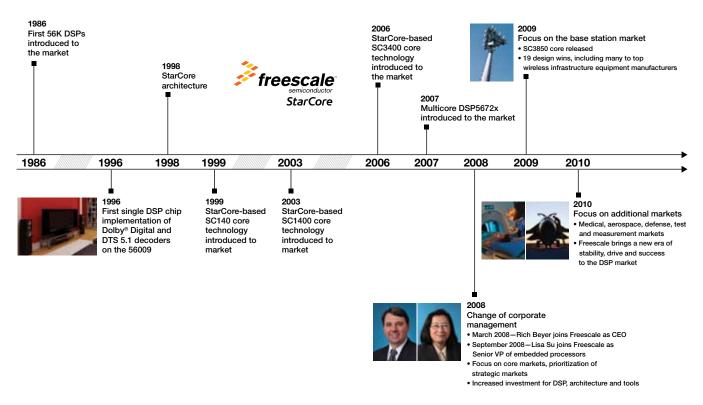

### **History of Freescale/Motorola DSPs**

Freescale Semiconductor (under the Motorola brand) introduced our first DSP to the market in 1986 with the introduction of the general purpose digital signal processors (DSPs) based on the 56K architecture. The 56K general purpose DSPs evolved into an extensive family of embedded DSPs, including 56K DSPs with integrated audio software called the Symphony DSP line. These DSPs remain popular across a wide range of applications, including audio and industrial control. Due to the very large customer base and continued popularity of these products, we will be releasing new 56K products in 2011.

In 1998, Freescale introduced the highperformance StarCore architecture to the broad market. In 2008, Rich Beyer ioined Frescale as CEO and Lisa Su was appointed Senior Vice President for embedded processors. They recognized the growth potential in DSP markets and substantially increased investments in the StarCore DSP architecture and tools. This increased investment in StarCore has resulted in the highest performance DSPs on the market today. Initially, the base station market was the primary focus for high-performance StarCore DSPs. In 2009, the SC3850 core was released as the building block core of the MSC8156 six-core high-performance DSP. The MSC8156 has been an overwhelming success in the base station market with 17 major design wins, including eight of the top 10 wireless infrastructure equipment companies.

In 2010, the focus for the StarCore DSPs expanded with the introduction of the MSC825x family and the MSC8152/ MSC8251 broad market DSPs. These new products are targeted for process intensive applications in the video, voice, medical, aerospace, defense and test and measurement markets and provide the optimal blend of cost effectiveness and high performance throughput.

**Technical Highlights** A closer look at the StarCore DSP families

00

0

ъ

C

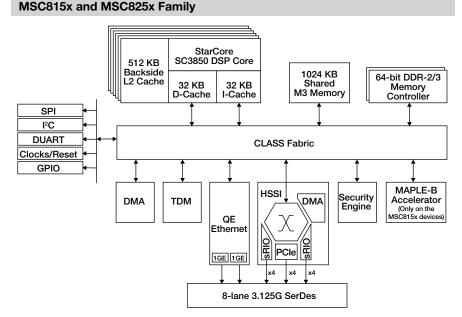

### MSC815x and MSC825x Family Overview

The MSC815x and MSC825x families of DSPs are based on the industry's highest performance DSP core, built on StarCore technology, and designed for the advanced processing requirements and capabilities of today's high-performance, high-end industrial applications for the video, voice, medical imaging, aerospace, defense and advanced test and measurement markets.

By leveraging the 45 nm process technology in a highly integrated SoC, the MSC815x and MSC825x families of DSPs deliver industry-leading performance and power savings. These DSPs are based on SC3850 StarCore technology. The SC3850 DSP core has earned leading benchmark results from independent signal-processing technology analysis firm Berkeley Design Technology, Inc. (BDTI). Specifically, Freescale's SC3850 1.2 GHz core registered a fixed-point BDTIsimMark2000<sup>™</sup> score of 18,500the highest score of any DSP architecture tested by BDTI to date. The combination of the award-winning SC3850 core and the richest and highest performance DSP peripherals available serve to accelerate system performance and result in a family of DSPs that offer up to twice the performance of competitors' parts.

Despite being the highest performing DSP available in the broad market today, these DSPs are also extremely price competitive. Starting at \$75 USD MSRP, the MSC815x and MSC825x DSP families offer the industry's best value and integration and may save customers up to one million USD over the product's lifetime in processor cost. In addition to silicon savings, pin and peripheral compatibility across the MSC815x and MSC825x families helps to enable software and tool reuse, allowing scalability from a single-core device to multicore devices, or to create multiple products from the same hardware.

| Pin for Pin Compatibility          |                     |                |                |            |                  |                  |                |            |

|------------------------------------|---------------------|----------------|----------------|------------|------------------|------------------|----------------|------------|

| Device                             | MSC8156             | MSC8154        | MSC8152        | MSC8151    | MSC8256          | MSC8254          | MSC8252        | MSC8251    |

| SC8350 DSP Cores                   | 6                   | 4              | 2              | 1          | 6                | 4                | 2              | 1          |

| Core Speed (MHz)                   | 1 GHz               | 1 GHz          | 1 GHz          | 1 GHz      | 1 GHz<br>800 MHz | 1 GHz<br>800 MHz | 1 GHz          | 1 GHz      |

| Core Performance<br>(16-bit MMACs) | Up to<br>48000      | Up to<br>32000 | Up to<br>16000 | Up to 8000 | Up to<br>48000   | Up to 32000      | Up to<br>16000 | Up to 8000 |

| Shared M3 Memory                   |                     | 11             | ИB             |            |                  | 11               | MB             |            |

| I-Cache (per core)                 |                     | 32             | KB             |            | 32 KB            |                  |                |            |

| D-Cache (per core)                 |                     | 32             | KB             |            | 32 KB            |                  |                |            |

| L2 I-Cache (per core)              |                     | 512            | KB             |            | 512 KB           |                  |                |            |

| DDR2/3                             | 2 (800 MHz)         |                | 2 (800 MHz)    |            |                  |                  |                |            |

| PCI Express®                       |                     | 1              |                | 1          |                  |                  |                |            |

| GEMAC (RGMII, SGMII)               | 2                   |                | 2              |            |                  |                  |                |            |

| Serial RapidIO®                    | 2                   |                | 2              |            |                  |                  |                |            |

| TDM                                | 4                   |                | 4              |            |                  |                  |                |            |

| SPI                                |                     | 1              |                |            | •                | 1                |                |            |

| UART                               |                     |                | 1              |            | 1                |                  |                |            |

| l <sup>2</sup> C                   |                     | 1              |                |            |                  | 1                |                |            |

| Turbo/Virterbi Accelerators        | 1                   |                |                |            |                  |                  |                |            |

| FFT/DFT/CRC Accelerators           |                     |                | 1              |            |                  |                  |                |            |

| Processor Technology               | 45 nm               |                | 45 nm          |            |                  |                  |                |            |

| Package                            | 783 Ball<br>FC-PBGA |                |                |            | Ball<br>PBGA     |                  |                |            |

### Key Features and Benefits

- The MSC815x and MSC825x DSPs deliver a high level of performance and integration, combining one, two, four or six new and enhanced, fully programmable SC3850 cores, each running at up to 1 GHz.

- The MSC815x family has added performance from a multi-accelerator platform engine (MAPLE-B) for fast Fourier transforms (FFT), inverse fast Fourier transforms (iFFT), discrete Fourier transforms (DFT), inverse discrete Fourier transforms (iDFT) and Turbo and Viterbi decoding.

- A high-performance internal RISCbased QUICC Engine subsystem supports multiple networking protocols to help provide reliable data transport over packet networks while significantly offloading processing from the DSP cores. TCP/IP stack control via the integrated QUICC Engine coprocessor allows fast communication between FPGA and DSP to DSP.

- Comprehensive memory support includes two 64-bit DDR3 running at 800 MHz to enable fast system throughput for multicore DSPs, GPP capability with an integrated MMU and full ECC protection on all memories.

- A rich peripheral set includes two Serial RapidIO<sup>®</sup> (four lane) interfaces, two Gigabit Ethernet interfaces for network communications, a PCI Express<sup>®</sup> x4 interface and four multi-channel TDM interfaces.

- The system is tied together with high-speed, high-bandwidth chiplevel arbitration and switching fabric (CLASS). The CLASS is a non-blocking, fully pipelined, low latency fabric interconnect based on a single module and therefore has uniformity in data transfer.

- Supports industrial temperature grade: -40°C to +105°C junction.

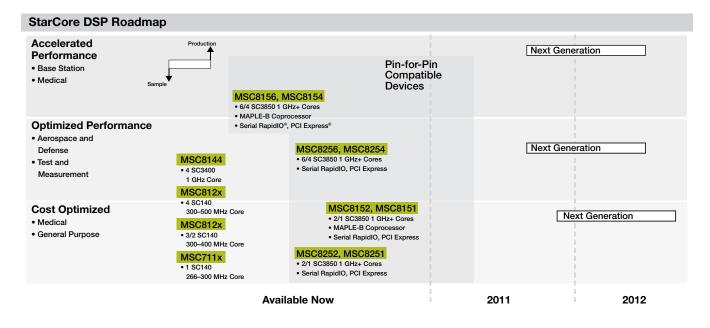

### StarCore DSP Roadmap

Freescale is no stranger to multicore DSP design. From the StarCore inception in 1998, we are on our fourth generation of StarCore cores and our third generation of multicore DSPs with additions to the StarCore family already in development. We offer cost-effective, high-performance DSPS to meet the performance requirements of process-intensive applications such as medical imaging or voice communications. The new MSC825x and MSC815x DSPs are the world's first DSPs available in the 45 nm process technology.

### Freescale Product Longevity

Freescale has a longstanding track record of providing long-term production support for our products. Freescale is pleased to provide a formal Product Longevity Program for the market segments we serve. For market segments in which Freescale participates, Freescale will make a broad range of devices available for a minimum of 10 years. Life cycles begin at the time of launch. The MSC815x, MSC825x and 5672x families of DSPs are included in the Product Longevity Program. For terms and conditions and to obtain a list of available products, visit **freescale.com/ productlongevity**.

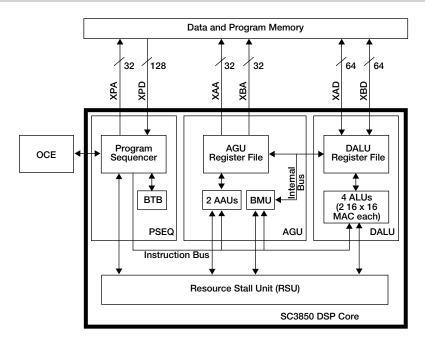

### SC3850 Core

The SC3850 DSP core features an innovative architecture that addresses the performance requirements of today's processing intensive DSP applications. This flexible DSP core supports computeintensive applications by providing high performance, low power, efficient compilation and high code density. Each high-performance core is binary compatible with previous generations of StarCore technology.

Performing eight MACs per cycle, the SC3850 core delivers up to 8000 16-bit MMACS using an internal 1 GHz clock at 1V. Operation includes a multiplyaccumulate command with associated data movements and pointer updates.

The StarCore SC3850 DSP core and subsystem is an evolution of the StarCore SC3400 DSP core and subsystem that enhances many of the original core and subsystem components and optimizes overall performance and memory hierarchy to target future application needs.

### SC3850 Benefits

- Improved control/compiled code

performance

- Better operation of DSP intensive kernels

- Minimizing memory system stalls to increase core use

### **Key Features**

- Main core resources

- Four data ALU execution units

- Two integer and address generation units

- 16 40-bit data registers with eight guard bits, freely accessible by data ALU instructions

#### SC3850 DSP Core Block Diagram

- 16 32-bit address registers, freely accessible by address generation instructions

- Instruction set

- 16-bit instruction set, expandable to 32 and 48 instructions

- High orthogonality of operands

- Rich instruction set for DSP and control features

- Good compiler target

- Very high execution parallelism

- Up to six instructions executed in a single clock cycle, statically scheduled

- Variable length execution set (VLES) execution model

- Up to four data ALU instructions and two memory access/integer instructions per cycle

- Data type support

- Byte (8-bit), word (16-bit) and long (32-bit) data widths, supported by instructions and memory moves

- Both integer (signed and unsigned) and fractional data types

- Packed fractional complex data type

- Several packed data types (two to four objects on the same register) for SIMD operations

- Very high numerical throughput for DSP operations

- Each data ALU can perform two 16 x 16 multiplications per cycle (total of eight multiplications for all ALUs), which can be used for:

- Dot product acceleration (40 + (16 x 16) + (16 x 16))

- SIMD2 multiplication and accumulation into two 20-bit register portions

- Acceleration of complex multiplication

- Acceleration of extended precision multiplication

- Application specific instructions for acceleration of the following algorithms:

- FFT

- Video processing

- Viterbi

- Baseband operations

- High throughput memory interface

- Unified, 32-bit byte addressable memory space

- Dual Harvard architecture that permits one 128-bit program access and two 64-bit data accesses per cycle

- Core to data memory throughput of up to 16 GB per second, at 1 GHz core frequency

- Support of Big Endian, Little Endian and Mixed Endian memory policies

- Zero overhead modulo arithmetic support for address pointers

- Advanced pipeline

- 12-stage, fully interlocked pipeline

- No stalls for memory load to register MAC operation and result storage

- Speculation of conditionally executed instructions and change of flow execution paths

- Control features

- Zero-overhead hardware loops with up to four levels of nesting

- A branch target buffer (BTB) for accelerating execution of change of flow instructions

- OS support

- Precise memory exception support for advanced OS

- User and supervisor privilege levels, supporting a protected, taskoriented execution model

- Full support for memory protection and address translation in the offcore memory management unity

- Exception and normal stack pointer for software stack support

- Low task switch overhead using wide stack save and restore instructions

- Rich set of real-time debug capabilities through an on-chip emulator (OCE)

- Real-time PC, data address and data breakpoint capabilities

- Up to six hardware breakpoint channels and unlimited debuggerenabled software breakpoints

- Single stepping

- Externally forced instructions in debug mode by the host processor

- Precise detection of PC breakpoints

- PC tracing with filtering and compression options

- Support for Nexus IEEE-ISTO 5001-2003<sup>™</sup> standard with off-core ready modules

- Low-power design

- Low-power wait and stop instructions

- Fully static logic

TheSC3850 DSP core technology achieved a BDTIsimMark2000 score of 18,500—the highest score of any DSP architecture tested by BDTI to date. This score exceeds the BDTImark2000 score of 16,690 previously set by Texas Instrument's 1.2 GHz C66X DSP.

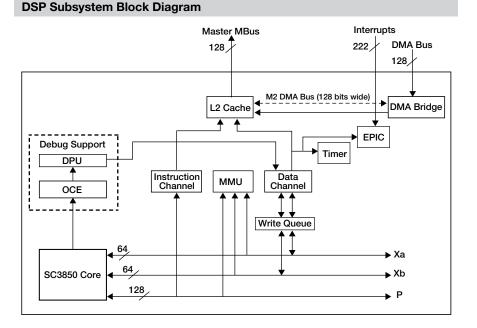

### **DSP Core Subsystem**

Each SC3850 core is embedded in a DSP subsystem that enhances the power of the SC3850 core and provides a simple interface to each SC3850 core.

The DSP core subsystem includes:

- An SC3850 core

- Instruction channel with a 32 KB instruction cache that supports advanced prefetching

- Data channel built around a 32 KB data cache, which supports advanced prefetching

- Memory management unit (MMU) for task protection and address translation

- Unified 512 KB L2 cache with partitioning support for multitasking reconfigurable in 64 KB partitions as M2 memory

- Write queue that interfaces between the core and the data channel

- Dual timer for internal use (such as RTOS)

- Extended programmable interrupt controller (EPIC) supporting 256 interrupts

- Real-time debug support with the OCE and a debug and profiling unit (DPU)

The subsystem has the following units and distinctive features:

- Instruction cache

- 32 KB

- Eight ways with 16 lines per way

- Multi-task support

- Real-time support through locking flexible boundaries

- Prefetch capability

- Software coherency support (sweep)

- PFETCH touch loading instruction support

- Data cache

- 32 KB

- · Eight ways with 16 lines per way

- Can serve two data accesses in parallel (XA, XB)

- Multi-task support

- Real-time support through locking flexible boundaries

- Software coherency support (Cache ISA or sweep)

- Write-back writing policy

- Write-through writing policy

- Hardware line prefetch capability

- Cache performance ISA support (DFETCH touch loading and DMALLOC)

- MMU

- Virtual to physical address translation

- Task protection

- Defines the memory and access attributes of memory regions

- Unified L2 cache

- 512 KB

- · Eight ways with 1024 indices

- 64-byte line size

- Physically addressed

- Maximum user flexibility for real-time support through address partitioning of the cache

- Rich cache policy support

- Multi-channel, two-dimensional software prefetch support

- Software coherency support with seamless transition from L1 cache coherency operation

- External memory interface

- MBus unified address separate data bus, with 32-bit address and 128-bit data

- Supports asynchronous clock ratio

- Debug and profiling

- On-chip emulator (OCE) for corerelated debug and profiling support

- Debug and profiling unit (DPU) for subsystem level debug and profiling support

- Debug state, single stepping and command insertion from the host debugger

- Breakpoints on PC, data address and data bus values

- More than 40 event counting options in six parallel counters

- Cache debug mode enabling observation of the cache state (cache array, tags, valid and dirty bits, etc.) and to change the contents of the data cache array

- Real-time tracing of PC, task ID and profiling information to the main memory

- Interrupt handling

- Extended programmable interrupt controller (EPIC) to handle 256 interrupts, including from internal sources

- Supports 222 interrupts external to the MSC8156 SC3850 DSP subsystem, independently configured as maskable or non-maskable

- 32 priority levels for interrupts

- Asynchronous and synchronous interrupts

- Two general-purpose 32-bit timers for RTOS support

- Low-power design modes of operation

- Wait processing state, where the clocks of the core and caches are gated but peripherals operate

- Stop processing state for full clock gating

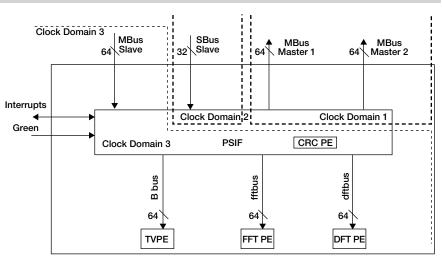

### **MAPLE-B**

The MAPLE-B is an algorithm accelerator for Turbo, Viterbi, FFT/iFFT, DFT/iDFT and CRC algorithms. It consists of a programmable system interface (PSIF), controller with CRC accelerator, DMA capabilities and three accelerators attached using an IP interface.

- Turbo/Viterbi processing element: Performs up to 200 Mbps of Turbo decoding (six iterations) or up to 115 Mbps of K=9 (zero tail) Viterbi decoding

- FFT processing element: FFT and iFFT for sizes 128, 256, 512, 1024 or 2048 points at up to 350 million samples per second

- DFT processing element: DFT and iDFT for sizes up to 1536 points at up to 175 million samples per second

The PSIF has two 64-bit wide MBus master ports used to transfer input and output data to and from system memory and a 64-bit MBus slave port that allows any host to access its internal memories. Hosts access internal memories to perform the following functions:

- Place buffer descriptors in the PSIF internal memory

- Access the MAPLE-B parameter RAM

- Access the processing element registers

The PSIF internal registers are accessed using the SBus.

The four accelerator processing elements include the following:

- Turbo/Viterbi Processing Element (TVPE)

- FFT processing element (FFTPE)

- DFT processing element (DFTPE)

- CRC processing element (CRCPE)

#### MAPLE-B

Highlights of the MAPLE-B include:

- Software-friendly buffer descriptorbased handshake and task assignment with minimal overhead on DSP cores for control

- Runs at 450 MHz

- Highly flexible and programmable Turbo and Viterbi decoder supporting various configurable decoding parameters (polynomials, rate, binary/duo, tail bit, zero tail)

- Up to 200 Mbps of Turbo decoding for low latency and advanced antenna systems or up to 100 Mbps of K=7 tail bit multi-iteration Viterbi decoding for low latency data/control channels decoding

- Support for WCDMA, CDMA2K, WiMAX and 3G-LTE standards

- CB CRC (LTE) or APQ (all standards) Turbo decoding stopping criteria for low power/low latency and higher statistical system capacity

- Rate de-matching, HARQ support accelerated

- Flexible and advanced FFT/DFT acceleration:

- FFT/iFFT for sizes 128, 256, 512, 1024, 2048 points at up to 280 Msps

- DFT/iDFT for LTE sizes at up to 175 Msps

- In 10 MHz WiMAX case up to 350 Msps of 1024 points FFT

- High-speed CRC calculation/check

accelerator for:

- LTE code and transport block in UL and DL

- · WiMAX PHY burst CRC in UL and DL

### **CLASS** Fabric

The chip-level arbitration and switching system (CLASS) is the central internal interconnect system for the MSC815x and MSC825x DSP families. The CLASS is a non-blocking, full-fabric interconnect that allows any initiator to access any target in parallel with another initiator-target couple. The CLASS uses a fully pipelined low latency design and demonstrates per-target prioritized round-robin arbitration, highly optimized to the target characteristics.

The CLASS operates at 500 MHz (half the SC3850 core speed). The CLASS clock is separate from the SC3850 core clock to provide an optimized trade off between power dissipation, memory technology and miss latency. Controlling the intradevice data flow, the CLASS reduces bottlenecks and permits high bandwidth fully pipelined traffic.

The CLASS is ready for use and does not require any special configuration to perform non-blocking pipelined transactions from any initiator to any memory.

The CLASS modules implement the following features:

- Non-blocking, full-fabric interconnect

- Full bandwidth utilization toward each target

- Allows full pipeline when a specific initiator accesses a specific target

- Allows full pipeline when accesses are generated by one or more initiators to specific targets

- Read transactions can have a maximum pipeline of 16 acknowledged requests before completing the transaction toward the initiator

- Write transactions can have a maximum pipeline of three acknowledged requests before completing the transaction toward the initiator

- Programmable priority mapping

- Programmable auto priority upgrade

- Address decoding for target selection and multi target demultiplexing

- Programmable address space start/ end registers per target for flexible address decoding (resolution of 4 KB). Not supported in the reduced configuration option

- Fixed priority between address decoding results, allowing overlapping and deduction of address windows

- Per-target arbitration algorithm

- Four-level prioritization

- Each level implements pseudo round-robin arbitration algorithm

- Weighted arbitration

- Optimized data bus utilization mode

- Programmable masking priority for starvation elimination

- Multiplexing the initiator buses according to the arbitration winner

- Normalizing mode that splits nonaligned transactions according to the target capabilities (maximal burst size, power-of-2 burst, burst alignment, full size burst, data-beat alignment, wrap size)

- Error detection and handling

- The CLASS identifies illegal addresses addresses that do not belong to any of the address windows or fall inside the negative windows

- The CLASS stores the illegal address, reports the error and generates an interrupt

- Debug and profiling unit (CDPU)

support

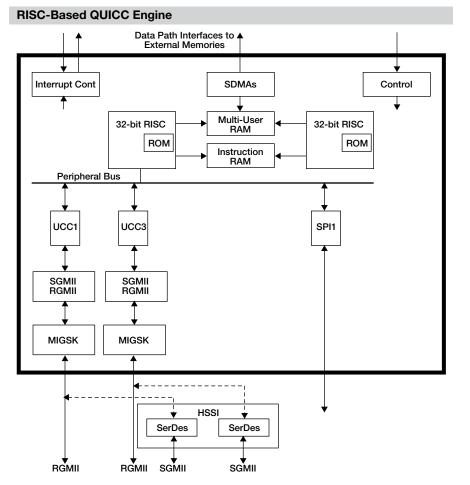

### **RISC-Based QUICC Engine Subsystem**

The QUICC Engine subsystem is a versatile RISC-based communication processor that supports multiple external interfaces and protocols independently from the core processor(s) in an integrated processing device.

In the MSC815x and MSC825x, the QUICC Engine includes two Gigabit Ethernet controllers (supporting both RGMII and SGMII interfacing) and one SPI interface. With the QUICC Engine block, packet processing up to and beyond layer 4 (TCP/UDP) can be offloaded from the SC3850 cores. This allows the cores to be relieved of the data transfer and handling overhead commonly associated with Ethernet tasks.

QUICC Engine packet processing allows the programmer to create multiple independent data and control flows between each core and each QUICC Engine Ethernet controller enabling the flexibility of both symmetric and asymmetric multicore processing models.

The QUICC Engine can be clocked at up to 500 MHz, and is comprised of:

- Dual RISC engines

- Internal interfaces to the core and peripherals

- Parameter RAM

- Buffer descriptors

- Multi-threading operation

- Serial numbers

- Instruction RAM (IRAM)

- Serial DMA controller

- Clocking

- · Signal multiplexing

- Baud-rate generation

- Dedicated interrupt controller with interrupt signals for each MSC815x core

- Two programmable unified communication controllers (UCCs), each of which provides dedicated support for an Ethernet controller for RGMII/SGMII interfaces

- Supports lossless flow control and PAUSE flow control for full duplex operation

- Transmit flow control via a host command

- Automatic transmit flow control according to programmable receive FIFO thresholds

- Programmable MAC parameter in flow control frame

- Full collision support

- Framing support for single and multibuffered Ethernet frames

- Serial management interface MDC/ MDIO

- Transmitter network management and diagnostics

- Receiver network management and diagnostics

- Enhanced MIB statistics

- Frame filtering and address recognition

- VLAN support

- IEEE<sup>®</sup> Std. 802.1p/Q QoS support

- Serial peripheral interface (SPI)

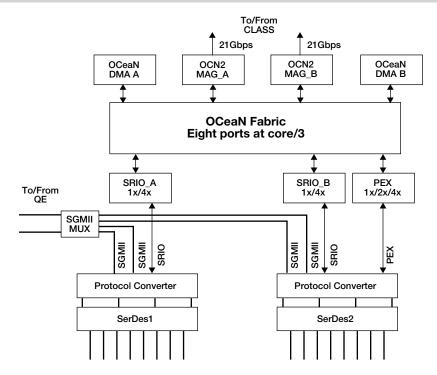

### Serial RapidIO<sup>®</sup> Architecture

The RapidIO architecture provides high data bandwidth, low-latency capability, and support for high-performance I/O devices. The MSC815x and MSC825x parts include a Serial RapidIO architecture that supports two ports, a RapidIO message unit (RMU) and two RapidIO DMA units. The Serial RapidIO ports comply with the RapidIO Interconnect Specification, Revision 1.2, which supports 1x/4x operation up to 3.125 Gbaud.

The MSC815x and MSC825x devices can either connect directly to a host or a Serial RapidIO switch. Packets ready for processing are sent from the host to the MSC815x/825x device and the processed packets are sent back to the host. Each Serial RapidIO port supports read, write, messages, doorbells and maintenance accesses. The RapidIO DMA units are used for NWRITE, NWRITE\_R, NREAD and SWRTE operations, while the RMU controls message and doorbell operations. The buffers in the Serial RapidIO endpoints support packets up to 256 bytes.

The two Serial RapidIO ports can be configured to perform pass-through operations between them. This connectivity allows packets to be forwarded to the next device connected to the second RapidIO port.

### Features

Two Serial RapidIO ports supporting 1x/4x operation up to 3.125 Gbaud with a RapidIO messaging unit and two RapidIO DMA units

#### Serial RapidIO®

- Each Serial RapidIO port supports read, write, messages, doorbells and maintenance accesses

- Small and large transport information field only

- Priority flow

- Pass-through between the two ports that allows cascading devices using the Serial RapidIO and enabling message/data path between the two Serial RapidIO ports without core intervention. A message/data not designated for the specific device passes through to the next device

- RapidIO messaging unit supports:

- Two outbound message queues

- Two inbound message queues

- One outbound doorbell queue

- One inbound doorbell queue

- One inbound port-write queue

- Each RapidIO DMA unit supports:

- Four high-speed/high-bandwidth channels accessible by local and remote masters

- Basic DMA operation modes (direct, simple chaining)

- Extended DMA operation modes (advanced chaining and stride capability)

- Programmable bandwidth control between channels

- Up to 256 bytes for DMA sub-block transfers to maximize performance over the RapidIO interface

- Three priority levels supported for source and destination transactions

The PCI Express<sup>®</sup> controller supports communication with PCI Express devices connected to the MSC815x or MSC825x devices for high-bandwidth data transfers. It complies with the PCI Express Base Specification, Revision 1.0a and connects to a 2.5 GHz serial interface configurable for up to a x4 interface.

The PCI Express controller can be configured to operate as either a root complex (RC) or an endpoint (EP) device. As an RC device, the PCI Express controller connects the core and memory subsystem to I/O devices and configures the EP devices during device discovery and enumeration. It can also act as an initiator and a target device. As an initiator, the PCI Express controller supports memory read and write operations with a maximum transaction size of 256 bytes. As a target interface, the PCI Express controller accepts read and write operations to local memory space. When configured as an EP device, the PCI Express controller accepts configuration transactions to the internal PCI Express configuration registers. Message generation and acceptance are supported in both RC and EP modes.

The address translation mapping unit (ATMU) maps transactions from the MSC815x or MSC825x devices to the PCI Express controller as a memory, I/O, message or configuration transaction via translation windows. Transactions from the PCI Express controller are mapped to the MSC815x/MSC825x internal platform via inbound translation windows. For outbound translation windows. For outbound transactions, the MSC815x/ MSC825x supports four translation windows and one default window. For inbound transactions, the MSC815x/ MSC825x supports three inbound windows and one configuration window.

#### Features

- Complies with the PCI Express Base Specification, Revision 1.0a

- Supports root complex (RC) and endpoint (EP) configurations

- 32- and 64-bit address support

- x4, x2 and x1 link support

- PCI Express configuration registers (type 0 in EP mode, type 1 in RC mode)

- 256 byte maximum payload size

- ATMU

- Three inbound general purpose translation windows and one configuration window

- Four outbound translation windows and one default window

- Supports eight non-posted and four posted PCI Express transactions

- Credit-based flow control management

- Supports PCI Express messages and interrupts

## DDR2/3

The MSC815x and MSC825x DSP families support two DDR controllers for external memory expansion. The DDR SDRAM interface is useful when an application requires additional code or data storage to supplement the internal M2 or M3 memory.

The DDR controllers can interface with JEDEC-compliant 8- or 16-bit DDR2 or DDR3. The data bus interface is 64/72 or 32/40 bits wide. Each controller supports two physical bands or chip selects to provide up to a maximum 1 GB of DDR space for each controller. Discrete, unbuffered and registered dual rank memory modules (DIMMs) are supported.

Built-in error checking and correcting (ECC) protection ensures reliable operation. When ECC is enabled, the DDR memory controller corrects all single-bit errors and detects all double-bit errors within the 64-bit or 32-bit data bus. The memory interface supports voltages of 1.5V (SSTL\_15) for DDR3 and 1.8V (SSTL\_18) for DDR2. Accesses to memory are burst oriented, with support for burst length of eight for DDR3 and burst length of four for DDR2. For DDR3, on-chip ZQ calibration is supported to adjust output driver and on-die termination impedance. DDR3 also supports write leveling to compensate for the flight time skew delay with respect to the strobe and clock signals.

| Features/Category        | DDR2                                                                                | DDR3                                                                                                            |

|--------------------------|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| Package                  | BGA                                                                                 | BGA                                                                                                             |

| Densities                | 256 MB to 8 GB                                                                      | 512 MB to 8 GB                                                                                                  |

| Voltage                  | 1.8V core and I/O                                                                   | 1.8V core and I/O                                                                                               |

| I/O Signalling           | SSTL_18                                                                             | SSTL_15                                                                                                         |

| Internal Memory Banks    | 4 to 8                                                                              | 8                                                                                                               |

| Data Rate                | Up to 800 Mbps                                                                      | Up to 800 Mbps                                                                                                  |

| Termination              | On-die termination for data group, VTT termination for address, command and control | On-die termination for data group, VTT termination<br>for address, command and control. Supports<br>dynamic ODT |

| Data Strobes             | Differential (recommended) or single-ended                                          | Differential                                                                                                    |

| Burst Length             | BL-4, 8 (4-bit prefetch)                                                            | BL-8 (Burst chop4) 8-bit prefetch                                                                               |

| CL/tRCD/tRP              | 15 ns each                                                                          | 12 ns each                                                                                                      |

| Master Reset             | No                                                                                  | Yes                                                                                                             |

| ODT (On-Die Termination) | Yes                                                                                 | Yes                                                                                                             |

| Driver Calibration       | Off-chip (OCD)                                                                      | On-chip with ZQ pin (ZQ calibration)                                                                            |

| Leveling                 | No                                                                                  | Yes                                                                                                             |

| Interface Data Bus Width | 32/40-bit and 64/72-bit                                                             | 32/40-bit and 64/72-bit                                                                                         |

| DIMM Support             | Discrete, unbuffered and registered 64 MB through 8 GB                              | Discrete, unbuffered and registered 64 MB through 8 GB and mirrored DIMMS                                       |

| Full ECC Support         | Single error correction/detection, double error detection                           | Single error correction/detection, double error detection                                                       |

| Self Refresh Support     | Yes                                                                                 | Yes                                                                                                             |

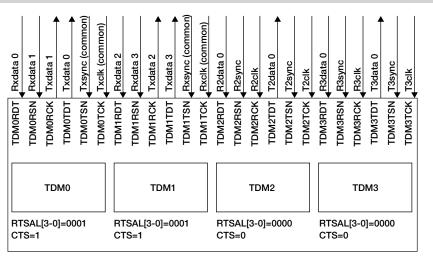

The time-division multiplexing (TDM) interface provides a glueless connection to most E1/T1 framers as well as to common buses such as the ST-Bus. The TDM interface is composed of four identical TDM modules, each supporting 256 bidirectional channels running at up to 62.5 Mbps. Time slot sizes can be configured to 2, 4, 8 or 16 bits. A hardware A-law/ $\mu$ -law conversion is supported for 8-bit channels.

Each TDM module can operate in independent or shared mode. In independent mode, the transmit and receive have separate clock, frame sync and data links with up to 256 transmit channels and up to 256 receive channels. In shared clock and sync mode, the clock and frame sync signals are shared between the two receive data links and two transmit data links. Each of the two transmit and data links support up to 128 channels. In shared data link mode, up to four full-duplex data links share the same clock and frame sync. Each link supports up to 128 channels.

### Features

Four independent TDM modules. Together, the four TDM modules support up to 1K time slots for receive and 1K time slots for transmit

#### **TDM Modules Diagram**

- Independent receive and transmit mode

- Shared sync and clock mode

- Shared data link

- 2-, 4-, 8- or 16-bit word size. All channels share the same size

- Hardware A-law/µ-law conversion

- Up to 62.5 Mbps data rate per TDM module

- Up to 16 MB per channel buffer where A/µ law buffer size has double size

- Separate or shared interrupts for receive and transmit

- Each channel can be programmed as active or inactive

- Support for either 0.5 ms (4 frames) or 1 ms (8 frames) latency

- Glueless interface to E1/T1 framers

# **Application Solutions**

### **Wireless Base Stations**

The MSC8156 and MSC8154 highperformance StarCore DSPs are the perfect solution for the industry's need for the very highest performance in multicore baseband DSPs. With up to 6 GHz DSP core performance, this fully programmable advanced DSP subsystem offers up to 48 GMACs (8- or 16-bit) of processing performance. This performance is proven by successful deployments of the MSC8156 at several of the top wireless infrastructure OEMs.

Code compatibility with the previous generation MSC8144 DSP ensures seamless software migration to the new MSC8156 DSPs.

Additional value drivers for the base station market include:

- Control code efficiency at GPP level

- Low latency memory hierarch

- High-throughput, low-latency baseband accelerators

- Advanced high-speed interfaces pertinent to different systems topologies

- High speed/wide external DDR interfaces

- Drives a low BOM channel card

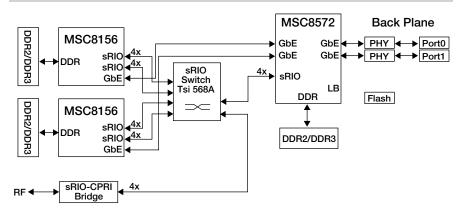

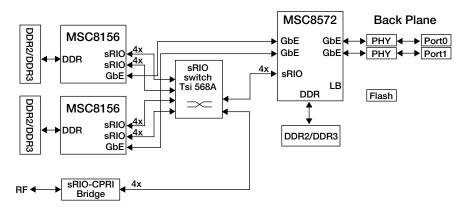

### 3G-LTE, Single Sector 20 MHz Channel Card

- 20 MHz use case, 4 x 4 DL and 2 x 2 UL MIMO

- Suitable for UL SIMO and basic UL MIMO schemes

- Peak data rates per sector are assumed to be 300 Mbps DL/150 Mbps UL as supported by category 5 type user equipment with multi-user UL MIMO

- One MSC8156 device allocated to UL processing

- One MSC8156 device allocated to DL processing

- sRIO switch for full connectivity between devices, with option to remove sRIO switch using pass through feature (TBV)

- Small front-end bridge needed in case of CPRI/OBSAI backplane

### WiMAX Three Sector 10 MHz Channel Card

- Three sectors 10 MHz

- Downlink: Four Tx antenna, beamforming, 100 Mbps max per sector

- Uplink: Eight Rx antenna, 14 Mbps max per sector

- Serial RapidIO switch for full connectivity between devices, with option to remove Serial RapidIO switch using pass-through feature (TBV)

- Small front-end bridge needed in case of CPRI/OBSAI backplane

### Video

High-definition video applications requiring superb video quality and support for scalable solutions are best served by the MSC825x DSP family coupled with Freescale's extensive off-the-shelf codec libraries.

Freescale was first to introduce a fully featured 1080P30 HD H.264/SVC embedded solution supporting temporal, spatial and quality scalability, available for free download and evaluation. SVC, together with over 30 video, audio and voice codecs, running on the highperformance MSC825x devices, enables a variety of high-end video applications.

Key advantages of Freescale's hardware and software solutions for video applications:

- Highest performing multicore DSP platform available with the ability to support HD H.264/SVC and other advanced codecs

- Programmable DSP and software codecs allow customers to add proprietary code and tweak solution to best suit the target market

- Rich device peripherals: Dual 4x Serial RapidIO, 4x PCI Express and dual Gigabit Ethernet allow flexible multidevice system solutions and seamless connectivity to FPGAs or other system components

- 2x DDR3 at 800 MHz for high data rate video applications

- 2-, 4- and 6-core, pin-compatible devices for scalable system solutions

- All codecs scale to support multiple streams of lower resolution with no performance degradation

- H.264/SVC, H.264BP, MPEG-4, MPEG-2, G.729, AAC and many other video, voice and audio components available from Freescale or ecosystem partners

- Freescale video and audio production codecs are shipping in today's leading media products

### Videoconferencing

MSC825x devices, together with the rich media codec libraries, are well suited for videoconferencing applications and their H.264/SVC, high video quality and system flexibility requirements.

Freescale's software codecs support low delay encoding and decoding required in videoconferencing applications and maintain high quality at low bitrates. The support of fully featured SVC further assists when combating unreliable networks or network bottlenecks by use of the scalability options for maintaining a high quality video transmission.

Rich device peripherals allow seamless connectivity to other system components, such as FPGA or a host processor, and also allow for multi-device solutions required in videoconferencing MCUs.

Freescale offers a rich portfolio of video software technologies, including H.264 baseline profile running at 1080p30 and legacy support for H.263/MPEG-4. Please contact your Freescale representative for more information.

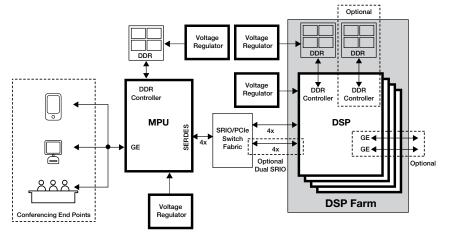

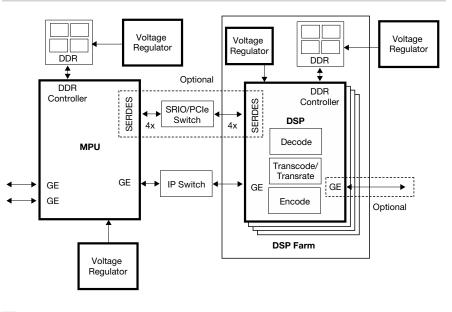

### **Multipoint Control Unit**

The videoconferencing multi-point control unit is a key element in modern videoconferencing systems, enabling interoperability and communication between participants using a wide variety of end point terminals. The multi-point control unit, often referred to as a bridge, establishes conference calls between three or more people for converged video, voice and data conferences.

MSC825x is used for performing encode, decode and other image processing functions required in the multi-point control unit.

Serial RapidIO and PCI Express high bandwidth interfaces enable transfer of raw video data between devices in multidevice solutions that are prevalent in videoconferencing infrastructure systems.

Rich software codec libraries allow interoperability of participants connecting with advanced and legacy end-points and enable maximum flexibility in MCU design with no performance degradation for support of lower resolution streams.

### Videoconferencing End Point (EP)

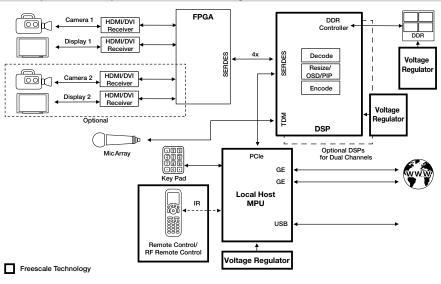

Videoconferencing end point (EP) systems are used to make video-enabled calls between two participants (point to point) or multiple participants (multi point). A typical EP will feature at least one HD camera and one screen while high-end (telepresence) systems will include three HD cameras and three large screens to better emulate a face to face meeting and an additional data channel. Processing elements in the EP must perform at least a single encode and decode of HD video and additional image processing functions, such as image resize and on-screen display. High-end room systems require multiple simultaneous encodes and decodes at frame rates up to 60 frames per second.

MSC825x is used for performing the encode, decode and other image processing functions connected on the one end via PCle interface to an FPGA for image capture and display and on the other end to a host processor for network connectivity. Based on specific system requirements, one or more DSP devices can be used to perform the multiple encode and decode functions while utilizing the high bandwidth Serial RapidIO ports for inter-device connectivity.

### Media Gateway

Please refer to media gateway application section on page 23.

#### Room System and Telepresence Videoconferencing End Point

#### Enterprise IP-PBX Block Diagram

Freescale Technology

### Voice

VoIP (Voice over IP) is becoming a more frequently utilized technology as customers discover its cost and quality benefits. As the communications industry completes the migration from circuit-switched to packet-switched infrastructure, equipment manufacturers require system solutions that include:

- Comprehensive design tools and system-level solutions

- DSP devices that offer increasing levels of signal processing and integration

- Peripherals that provide the ability to interface with both packet- and circuit-switched networks and software support

The challenges in today's packet-based networks are to reduce overall cost (increased integration), reduce power consumption and create a unified approach to transporting voice, video and additional media. The Freescale MSC825x family of DSPs is a fully software-programmable series of DSP solutions suitable not only for voice, video and data applications. Customers can use the MSC825x family to architect very flexible and scalable solutions for media-over-IP equipment. Due to the programmability and flexibility of the DSP family, customers can adjust the mix of media traffic being processed in real time.

The DSP subsystem is designed to run essential signal processing functions for voice, fax and modem data applications. At the heart of a typical media processing subsystem are multiple MSC825x DSPs.

Typical functions include voice encoding and decoding (wide band and narrow band), tone detection, voice activity detection/comfort noise generation/ packet loss concealment (VAD/CNG/ PLC), echo cancellation (EC), as well as modem and fax data modulation and demodulation.

The DSP subsystem interfaces to a host processor (typically a Freescale processor built on Power Architecture<sup>®</sup> technology, such as a QorlQ processor) via the PCI

Express and/or the Gigabit Ethernet interfaces. The MSc825x family offers up to four TDM interfaces, each supporting a maximum of 256 channels of narrow-band voice. These can then connect to T1/E1 TDM ports.

Freescale offers a rich portfolio of voice (narrow and wide-band) software technologies, along with voice enhancement, tone detection and generation, video and modem/fax-related functions.

Please contact your Freescale representative for more information.

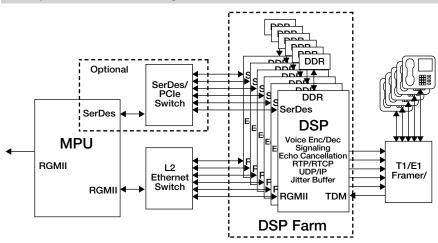

#### Media Gateway (Unified Communications)/ Session Border Controllers

Application highlights and requirements:

- Packet based (IP to IP)

- Programmability and flexibility for converged voice and video communications

- High-bandwidth/low-latency DSP layer 2 interconnect

- Low power consumption

- High channel density, 100s to 1000s of channels

- Hardware support for redundancy

### **Enterprise Application**

Application highlights and requirements:

- TDM support for conventional POTs or T1/E1 interfaces (TDM to IP)

- Medium to low channel density, scalability from 10s to 100s of channels

- Requires specialized functions for telephone interface such as line echo cancellation

#### Media Gateway Block Diagram

Freescale Technology

#### **Enterprise IP-PBX Block Diagram**

### **Medical Imaging**

The complexities of medical imaging require extraordinary processing power. Modalities such as ultrasound, X-ray, magnetic resonance imaging (MRI) and computed tomography (CT) scans all push performance limits for advanced integrated I/O, rigorous data processing and high levels of connectivity. These needs are addressed by the MSC815x and MSC825x families of highperformance DSPs which are capable of performing the compute intensive image reconstruction and image processing at the heart of medical imaging systems.

MSC815x and MSC825x devices offer unprecedented I/O and memory bandwidth with the ability to combine PCI Express, Serial RapidIO and/or Gigabit Ethernet and one or two 64-bit DDR2/3 interfaces for data intensive applications such as medical image reconstruction.

The MSC815x device family also features a dedicated DFT/FFT hardware accelerator capable of running up to 350 Mega samples/sec. Off-loading these functions from the cores leaves ample processing headroom for additional system requirements or enables the use of single- or dual-core devices.

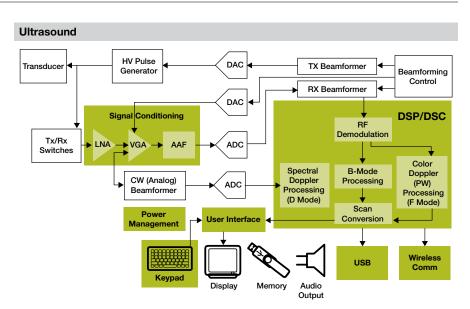

### Ultrasound

Ultrasound is a non-invasive medical imaging technique used to visualize muscles, tendons, pathological lesions and many internal organs and other structures. It plays an important role during prenatal care and is commonly used as a diagnostic tool. Ultrasound

#### Freescale Technology

sends ultrasonic waves through the patient and detects the echoes of the bounced back waves, applies digital processing to these signals and builds an image to be shown on a screen.

Image reconstruction and processing can be best realized on MSC815x or MSC825x high-performance single- or multicore DSP devices which are capable of performing the data intensive B mode image reconstruction and the different modes of doppler processing that are integral parts of any ultrasound system. Doppler processing can be accelerated by use of the dedicated FFT/DFT units in the Maple hardware coprocessor to achieve greater throughput and better utilization of the device's resources. MSC815x and MSC825x DSP families are also ideal for additional signal processing functions, such as filtering, demodulation and scan conversion required for achieving the desired output image.

Freescale plans to offer B-mode processing libs in order to accelerate development time for our end customers. Please contact your Freescale representative for more information.

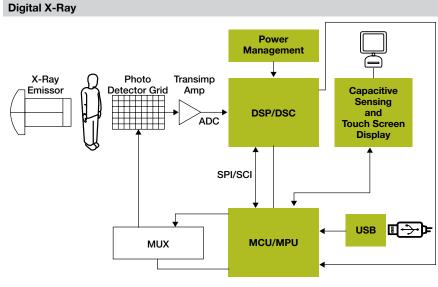

### Digital X-Ray Scanner

Digital X-ray imaging uses digital sensors instead of traditional photographic film. A common X-ray system is composed of an analog front end where the actual X-ray is performed and transmitted to a digital image processing unit for image reconstruction, processing and display generation.

The signal processing and conditioning used to generate radiography involves the transformation of signals from the spatial domain to frequency domain by use of Fourier Transform, performing convolutions on the transformed data and inverse transform back to spatial domain. The MSC815x family of devices with the MAPLE coprocessor containing the dedicated DFT/FFT hardware accelerators is ideal for implementing these functions and other image processing techniques used in X-ray applications.

| MAPLE Coprocessor DFT/FFT Performance                                      |                                       |                               |  |  |

|----------------------------------------------------------------------------|---------------------------------------|-------------------------------|--|--|

| Standard Compliance                                                        | Data Rates                            | Comments                      |  |  |

| FFT sizes: 128, 256, 512, 1024, 2048 points                                | FFFT 2048: Up to 280 Mega samples/sec | Advanced scaling options      |  |  |

| DFT sizes: Variable-length DFT/IDFT                                        | FFT 1024: Up to 350 Mega samples/sec  | Guard bands insertion in iFFT |  |  |

| processing of $2^{k} \cdot 3^{m} \cdot 5^{n} \cdot 12$ , up to 1536 points | DFT: Up to 175 Mega samples/sec       |                               |  |  |

### **Aerospace and Defense**

### **Mission-Critical Applications**

MSC815x and MSC825x DSPs provide a number of features critical to the aerospace and defense industries, including high processing performance, high throughput I/Os, flexible programmable architecture, extended temperatures and 10+ years of product longevity\*.

A key need for aerospace and defense customers is test time and costs. With the scalability allowed by the MSC815x and MSC825x families, customers can use the single-core MSC8251 for one program and the MSC8256 six-core DSP for different projects using the same hardware enabled by the pin-forpin compatibility of our MSC825x and MSC815x families, reducing the need for full retest or verification.

### Software Defined Radio

Software defined radio (SDR) systems have become prevalent in the last decade in order to overcome wireless communication interoperability issues. SDR is now necessary for emergency/ public safety and military communications with a strong pull from consumer segments. The common requirements of this application space include pure programmable processing performance and multitasking. The MSC815x math capability allows it to handle various modem processing functions, including filtering, modulation, demodulation, error correction encoding and decoding as well as a minimum product lifetime of 10 years\*. The MSC815x is complimented by the MPC8572 communications

\*Products may be supported by Freescale's Product Longevity Program. For Terms and Conditions and to obtain a list of available products, visit freescale.com/productlongevity.

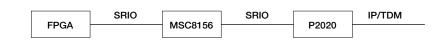

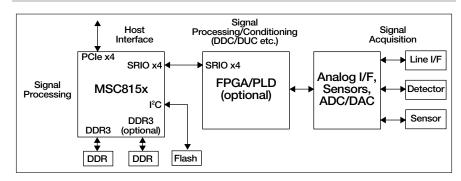

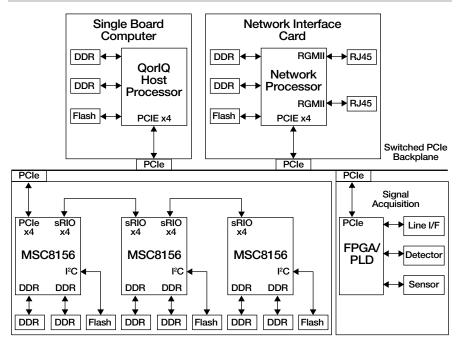

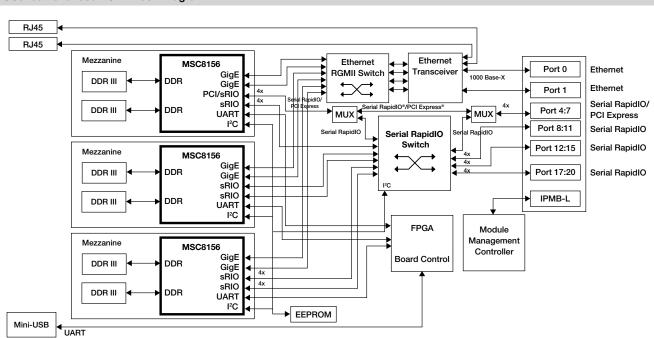

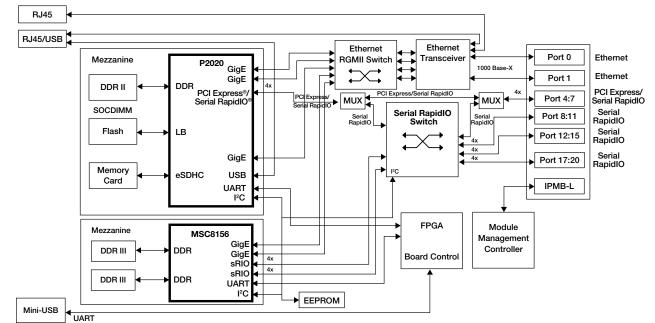

#### MSC8156 and P2020 Hardware Block Diagram

Many mission critical devices have an inherent need for fast capture of data and processors with high processing performance as well as high throughput. Mission critical applications also use a large number of FFT/DFT calculations. The high performance of the MSC815x and MSC825x families of DSPs, ranging from 1 GHz single-core DSPs up to 6 GHz multicore DSPs with FFT/DFT/Virterbi and Turbo coprocessor blocks, combined with a 500 MHz switching fabric, make them a perfect solution for a number of mission critical needs. In a large portion of mission critical applications, highperformance DSPs connect to FPGAs or to QorIQ devices. All MSC815x and

MSC825x family members have both PCI Express 1.0 and multiple four lane Serial RapidIO interfaces in order to create the fastest possible throughput between FPGA, QorIQ communications processors or other DSPs. Freescale provides multiple development platforms with MSC8156 to FPGA (MSC8156ADS) or MSC8156 to QorIQ (MSC8156 and P2020 AdvancedMC<sup>TM</sup> reference design) with freely available schematics, gerber and orchard files to accelerate board development. A small front-end bridge is required in case of a CPRI/OBSAI backplane.

#### Software Defined Radio

processor, built on Power Architecture technology, which is an optimized networking processor that allows high communications throughput and reliability in a wireless radio communication product.

### **Key Features**

- Downlink: Four Tx antennas, beamforming, 100 Mbps max per sector

- Uplink: Eight Rx antennas, 14 Mbps max per sector

- Serial RapidIO switch for full connectivity between devices, with option to remove Serial RapidIO switch using pass-through feature (TBV)

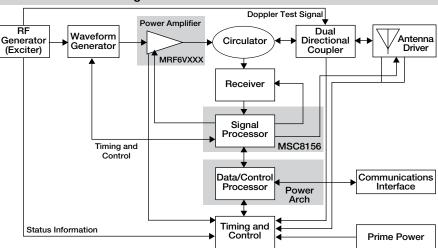

### Radar/Sonar

The MSC8156 DSP is ideally suited for radar, sonar or infrared as a standalone system or as an integrated part of a military or aerospace end product. With 6 GHz of processing power, full ECC memory protection and a 10+ year product life cycle\*, the MSC8156 DSP is an ideal choice for high-performance radar, sonar or infrared solutions. With many application processing requirements relying heavily on FFT/DFT/FIR algorithms, the MAPLE-B coprocessor with a hardware accelerated FFT/ DFT and Turbo/Virterbi coprocessing allow customers to call the required functions via predefined APIs.

#### Radar/Sonar Block Diagram

\*Products may be supported by Freescale's Product Longevity Program. For Terms and Conditions and to obtain a list of available products, visit freescale.com/productlongevity.

### **Advanced Test and Measurement**

Testing is a necessary requirement for manufacturers of consumer and industrial electronic equipment. Irrespective of the market segment, products must be tested before being shipped to the end customer. There are certain sub segments within the overall test and measurement market where the use of advanced digital signal processing is prevalent. The three sub segments and applications are as follows:

- · Communications test equipment

- Wireless testers (WiMAX, Wi-Fi, WCDMA, 4G-LTE)

- Wireline testers (packet switched and circuit switched)

- Automated/semiconductor test

equipment

- Digital/analog testers

- · General purpose test

- · Signal generators and analyzers

Freescale's MSC815x and MSc825x families of devices are particularly well suited to many of these sub-segments. Boasting not only the highest performing fixed-point DSP core on the market, but also a rich array of high-speed interconnect and memory interfaces. Furthermore, the MSC815x family of DSPs is backed by MAPLE-B technology, which accelerates common algorithms found on DSPs targeted at many of the applications listed at left. One of the common challenges of DSPs, generally in test and measurement, and wireless test and measurement in particular, is the availability and use of high-speed peripheral interfaces that allow high amounts of data to be stored and processed in real time.

Freescale's latest generation of DSP processors helps to solve these challenges by offering a total of eight lanes of SerDes high-speed interconnect designed to support un-paralleled bandwidth and low latency data exchange with the following interface combinations:

- Two 1x/4x Serial RapidIO ports

- One 1x/4x Serial RapidIO ports, one 1x Serial RapidIO port and two SGMII ports

- One 1x/4x Serial RapidIO port and a PCI Express port

- One 1x/4x Serial RapidIO port, two SGMII ports and a PCI Express port

Freescale complements this interconnect with two 64-bit, 800 MHz data rate, DDR-III interfaces.

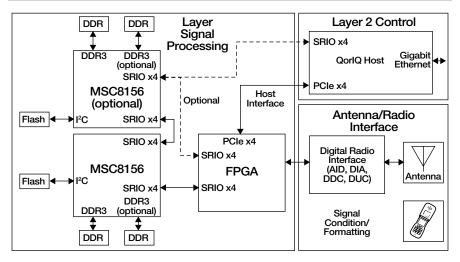

### Wireless Handset Test Equipment

The following system diagrams show examples of a DSP-based wireless handset test and measurement system. The system demonstrates a standard baseband system where modulated radio data is sent and received from the radio and antenna interfaces. Oversampled data is down converted (decimated) or upsampled (interpolated) from and to the radio card. An FPGA may be used to perform physical layer formatting between the layer 1 processing functions performed on the MSC8156, or multiple MSC8156s, and the radio card. Processing is subsequently split into layer 1 (MIMO support, downlink and uplink physical and transport channel processing) and layer 2 processing (media access, radio link control and packet data convergence) typically performed on a host processor such as Freescale's QorIQ P4040 or P4080 communications processors.

#### Wireless Handset Test Equipment

#### PCI-Based Single DSP Test System

#### **Modular Test Platform**

Development Software, Tools and Reference Designs

O

### CodeWarrior Development Studio for StarCore 10.0 DSPs

CodeWarrior Development Studio is an Eclipse-based, completely integrated development environment (IDE) that provides a highly visual and automated framework to accelerate the development of the most complex embedded applications.

### **Debugging Tools**

Debugging multicore architectures can be a challenging task. CodeWarrior IDE includes a wide range of debugging tools simplifying the task of multicore embedded programming. CodeWarrior's multicore debugging features such as core grouping and multicore run control make this task much easier. The MMU configurator provides a way to debug RTOS virtual memory management problems by allowing the developer to see and experiment with and even generate code for different MMU settings. The on-chip emulation (OCE) configurator provides an easy way for developers to monitor for different types of accesses to critical areas of memory.

### Software Analysis, Profiling and Trace

With an extensive array of tools, developers save time by quickly identifying and resolving functional and performance issues. CodeWarrior IDE for StarCore DSPs has a sophisticated profiler that helps the developer pinpoint cache performance or stall problems as well as show how ALUs and AGUs are being utilized. The trace analyzer provides a view of the sequence of instruction execution that led the processor to be in a problem state. Through trace points, the developer can pinpoint the precise segments of code that are of interest. Sometimes user applications corrupt system register values. The register analyzer can quickly identify unexpected hardware states and alert the programmer to a problem.

### Compiler

CodeWarrior's optimizing compiler provides developers with choices in developing high-performance code. For developers who do not want to spend time hand-tuning their applications for the maximum possible performance, CodeWarrior's compiler has aggressive optimization options that do the job. Developers who want to obtain the maximum performance possible can choose from a wide selection of intrinsic functions that implement common tasks in a way that most efficiently utilizes the architecture. The documentation provided with the tools includes descriptions of how and when to use different intrinsic functions, and examples that illustrate their use.

### SmartDSP OS RTOS (SDOS)

SDOS is Freescale's optimized multicore StarCore OS. It offers highly efficient program execution with extensive functionality, including an integrated network stack, a compact and lightweight kernel with real-time, priority-based, preemptable execution. It is offered royalty free to Freescale customers and offers packaged drivers along with kernel and driver source code.

### Voice Software

Freescale and certain key partners offer an extensive range of voice-related software technologies for license in source code or binary code format. Our voice software portfolio covers many standardized ITU-T, IETF and 3GPP voice and voice-related technologies. In addition, Freescale has a number of patented technologies for advanced voice applications like wide band conferencing, sample rate conversion, automatic level control and narrow band line echo cancellation.

Whatever your voice application, whether circuit-switched, packet-switched, TDM or IP-based, narrow band, wide band or extended wide band, Freescale and our third-party network are likely to have the technology you need.

All software is covered by complete documentation explaining the memory, performance requirements and integration of the respective technologies.

| Voice Codecs                     |                                                  |                    |

|----------------------------------|--------------------------------------------------|--------------------|

| Low Complexity: Narrow/Wic       | le Band                                          |                    |

| G711                             | G.729 B                                          | GSM-FR             |

| PLC                              | G722.1 (C)                                       | VADCNG             |

| G.726 ( A )                      |                                                  |                    |

| Mid Complexity: Narrow/Wid       | e Band                                           |                    |

| G.723.1A                         | GSM-HR (raw bitstream output)                    | AMR-NB             |

| G.729 (1)                        | GSM-EFR                                          | G722 with Annex IV |

| iLBC                             |                                                  |                    |

| High Complexity: Narrow/Wig      | de Band                                          |                    |

| G.728                            | EVRC-A                                           | EVRC-B             |

| G722.2 (AMR-WB)                  |                                                  |                    |

| High Complexity: Wide Band       |                                                  |                    |

| AAC-LC/LD                        | AAC-HE                                           | EVRC-WB            |

| Voice Enhancement De             | vices                                            |                    |

| Low Complexity                   | Sample Rate Convertor                            | Mid Complexity     |

| ALC-WB                           | N-Way Conferencing                               | G.168              |

| NR                               | Voice Activity Det (VAD)<br>Stand Alone          |                    |

| FAX/Modem                        |                                                  |                    |

| Caller ID (depends on v.23 pump) | V.21/V.27/V.29/V.17<br>(as part of T.38 package) | V.32/V.32bis       |

| T.38                             | V.23                                             |                    |

Please contact your Freescale sales representative or our third-party providers for further information on licensing and commercial terms and conditions.

### Video Software

Freescale offers a wide variety of video codecs necessary for implementing today's leading media communication systems, such as videoconferencing and media gateways. All codecs are optimized for high quality and maximum efficiency running on the StarCore-based MSC815x and MSC825x high-performance DSPs. Codecs are available in binary form for quick download and evaluation or can be licensed in source form open to customer edits. Freescale's flexible software codecs running on high-performance single- and multicore DSP devices enable scalable,

cost-effective programmable system solutions required for winning in today's competitive market place.

Freescale's video codec offering includes the first fully featured implementation of HD H.264/scalable video coding (SVC) standard, allowing single encode to multiple targets and overcoming network reliability issues.

Detailed codec information and quick downloads can be found at freescale.com/DSP.

#### Video Codecs

| Codec      |  |

|------------|--|

| H.264/SVC  |  |

| H.264BP    |  |

| Н.263р3    |  |

| MPEG-4SP   |  |

| H.261      |  |

| MPEG-2     |  |

| MJPEG      |  |

| JPEG2000   |  |

| H.264MP/HP |  |

### **Base Station Software**

### LTE Layer 1 Software

The LTE Layer 1 software includes physical baseband channel processing and radio transport channel functions as defined in the 3GPP standards. Freescale provides a comprehensive set of kernel modules covering the Layer 1 processing for physical downlink shared channel and physical uplink shared channels. The kernels are further combined into uplink and downlink chains, which run in real time using the SmartDSP realtime operating system as a reference. All software is developed as ANSI-C callable and fully documented.

In brief, the physical layer processing functions include:

- Modulation

- Channel coding

- Transmission schemes

- Multiplexing

- MIMO/diversity

- Channel estimation

- Equalization (outside 3GPP scope)

### WCDMA Layer 1 Software

The WCDMA Layer 1 software covers uplink and downlink symbol rate processing as defined in the 3GPP standards. Freescale provides a comprehensive, fully documented set of kernels developed in C and ASM.

#### Real-Time Software Subsystem Features

| neal-Till                       | ne Software Subsystem reatures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Category                        | Specifications/Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Design<br>approach              | <ul> <li>Layered API software approach enables multi-level reuse and ease of integration</li> <li>Modular C software modules for all subsystems. Includes C wrapper for optimized real-<br/>time assembly modules</li> <li>Algorithm verification with floating- and fixed-point simulation system</li> <li>Multicore framework allows for efficient inter-core communication and task partitioning</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                               |

| Features                        | <ul> <li>Focus on high-speed shared user physical channels</li> <li>Physical Downlink Shared Channel (PDSCH) (36.211 chapter 5.3)</li> <li>Physical Uplink Shared Channel (PUSCH) (36.211 chapter 6.3)</li> <li>Random Access Channel (RACH)</li> <li>Modular design with well-defined interfaces and module interactions</li> <li>Downlink         <ul> <li>IF1Tx: L1/L2 logical interface. Memory mapped over Serial RapidIO</li> <li>IF2Tx: Transport to physical channel interface per 3GPP 36.211 and 36.212</li> <li>IF3Tx: Transport to OFDMA processing interface. Re-maps IFFT signal generation onto FPGA</li> <li>IF4Tx: Baseband I/Q sample interface towards the antenna FPGA</li> <li>Message-based configuration and runtime control</li> <li>Includes MIMO processing</li> </ul> </li> </ul> |

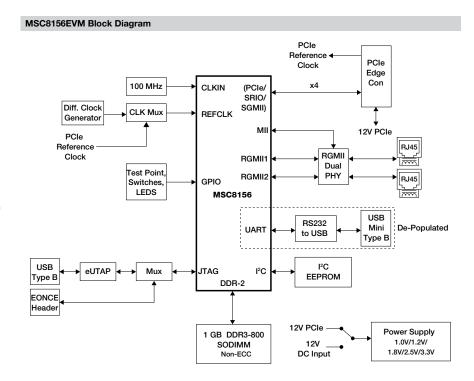

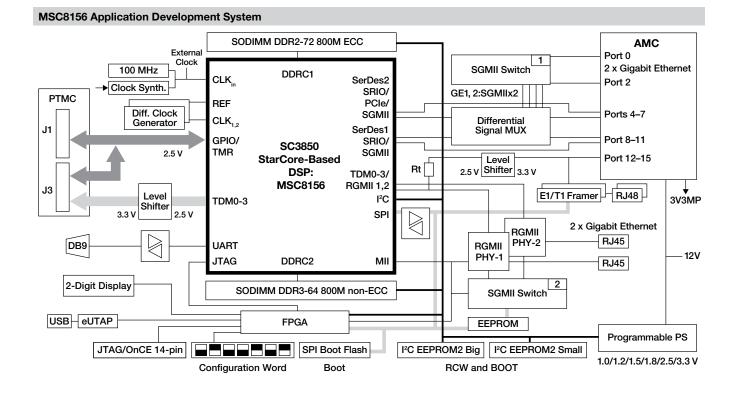

| RTOS<br>support                 | SmartDSP OS: Integrates real-time kernels and drivers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |