### **Freescale Semiconductor**

Data Sheet: Product Preview

Document Number: MC33493A Rev. 2, 07/2007

**VROHS**

### PLL Tuned UHF Transmitter for Data Transfer Applications

- Selectable frequency bands: 315—434 MHz and 868—928 MHz

- On Off Keying (OOK) and Frequency Shift Keying (FSK) modulation

- Adjustable output power range

- Fully integrated voltage control regulator (VCO)

- Supply voltage range: 1.9—3.6 V

- Very low standby current: 0.1 nA @  $T_A = 25 \text{ °C}$

- Low-supply voltage shutdown

- Data clock output for microcontroller

- Extended temperature range: -20 to 85 °C

- Low external component count

- Typical application compliant with European Telecommunications Standards Institute (ETSI) standard

|                                           | IVIC33493A |       |        |  |  |

|-------------------------------------------|------------|-------|--------|--|--|

| 14<br>TSSOP-14<br>DTB SUFFIX<br>CASE 948G |            |       |        |  |  |

| PIN                                       | CONNE      | CTION | S      |  |  |

| DATACLK                                   | <b>1</b>   | 14 🗖  | MODE   |  |  |

| DATA                                      | 2          | 13 🗖  | ENABLE |  |  |

| BAND                                      | 3          | 12 🗖  | vcc    |  |  |

| GND 🔳                                     | 4          | 11 🗰  | GNDRF  |  |  |

| XTAL1                                     | <b>5</b>   | 10 🗰  | RFOUT  |  |  |

| XTALO                                     | 6          | 9 🗖   | vcc    |  |  |

| REXT                                      | 7          | 8     | CFSK   |  |  |

MC33103V

### **Ordering Information**

| Device      | Ambient<br>Temperature<br>Range | Package           |

|-------------|---------------------------------|-------------------|

| MC33493ADTB | –20°C to 85°C                   | TSSOP14           |

| MC3493ADTBE | –20°C to 85°C                   | TSSOP14<br>(ROHS) |

This document contains information on a product under development. Freescale reserves the right to change or discontinue this product without notice.

© Freescale Semiconductor, Inc., 2007. All rights reserved.

### **Table of Contents**

| 1<br>2 | Transmitter Functional Description   |

|--------|--------------------------------------|

| 2      | RF Output Stage                      |

| 4      | Modulation                           |

| 5      | Microcontroller Interface            |

| 6      | State Machine                        |

| 7      | Power Management                     |

| 8      | Data Clock                           |

| 9      | Electrical Characteristics           |

| 10     | Radio Frequency (RF) Output Spectrum |

| 11     | Output Power Measurement             |

| 12     | Complete Application Schematic and   |

|        | PCB for OOK Modulation               |

| 13     | Complete Application Schematic and   |

|        | PCB for FSK Modulation               |

| 14     | Recommendations for FSK Modulation   |

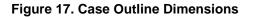

| 15     | Case Outline Dimensions              |

### List of Figures

NP

\_\_\_\_\_

| Figure 9. Output Power Measurement Configurations 13         |

|--------------------------------------------------------------|

| Figure 10.Output Model and Matching Network                  |

| for 434 MHz Band                                             |

| Figure 11.Output Power at 434 MHz Band vs Rext Value 14      |

| Figure 12. Application Schematic for OOK Modulation,         |

| 434 MHz Frequency Band 15                                    |

| Figure 13.Two-Button Keyfob Board Layout                     |

| Figure 14.Application Schematic for FSK Modulation,          |

| Serial Configuration, 434 MHz Frequency Band 17              |

| Figure 15.Application PCB Layout for FSK Modulation,         |

| Serial Configuration, 434 MHz Frequency Band 18              |

| Figure 16.Crystal Load Capacitance Contributors Schematic 19 |

| Figure 17.Case Outline Dimensions 20                         |

| List of Tables                                               |

| Table 1. Pin Function Desc   | ription                              |

|------------------------------|--------------------------------------|

| Table 2. Absolute Maximum    | n Ratings                            |

| Table 3. Band Selection an   | d Associated Divider Ratios 4        |

| Table 4. DATACLK Frequen     | cy vs Crystal Oscillator Frequency 5 |

| Table 5. Electrical Characte | eristics                             |

| Table 6. External Compone    | ents Description for OOK 15          |

| Table 7. Typical Crystal Cha | aracteristics (SMD Package) 16       |

| Table 8. External Compone    | ents Description for FSK 17          |

| Table 9. Crystal Pulling Cap | pacitor Values vs                    |

| Carrier Frequency            | Total Deviation -1 18                |

| Table 10.Crystal Pulling Cap | pacitor Values vs                    |

| Carrier Frequency            | Total Deviation -2 18                |

| Table 11.Pads and Tracks P   | arasitic Values                      |

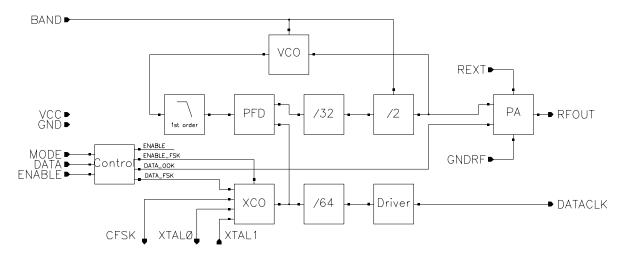

### Figure 1. Simplified Block Diagram

| Pin | Name    | Description                                  |  |

|-----|---------|----------------------------------------------|--|

| 1   | DATACLK | Clock output to the microcontroller          |  |

| 2   | DATA    | Data input                                   |  |

| 3   | BAND    | Frequency band selection                     |  |

| 4   | GND     | Ground                                       |  |

| 5   | XTAL1   | Reference oscillator input                   |  |

| 6   | XTAL0   | Reference oscillator output                  |  |

| 7   | REXT    | Power amplifier output current setting input |  |

| 8   | CFSK    | FSK switch output                            |  |

| 9   | VCC     | Power supply                                 |  |

| 10  | RFOUT   | Power amplifier output                       |  |

| 11  | GNDRF   | Power amplifier ground                       |  |

| 12  | VCC     | Power supply                                 |  |

| 13  | ENABLE  | Enable input                                 |  |

| 14  | MODE    | Modulation type selection input              |  |

#### **Table 1. Pin Function Description**

#### **Table 2. Absolute Maximum Ratings**

| Parameter                                                    | Symbol          | Value                                              | Unit |

|--------------------------------------------------------------|-----------------|----------------------------------------------------|------|

| Supply voltage                                               | V <sub>CC</sub> | $V_{GND}$ – 0.3 to 3.7                             | V    |

| Voltage allowed on each pin                                  |                 | V <sub>GND</sub> – 0.3<br>to V <sub>CC</sub> + 0.3 | V    |

| ESD HBM voltage capability on each pin <sup>1</sup> (note 1) |                 | ±2000                                              | V    |

| ESD MM voltage capability on each pin <sup>2</sup> (note 2)  |                 | ±150                                               | V    |

| Storage temperature                                          | Ts              | -65 to +150                                        | °C   |

| Junction temperature                                         | Tj              | +150                                               | °C   |

<sup>1</sup> Human Body model, AEC-Q100-002 Rev. C.

<sup>2</sup> Machine Model, AEC-Q100-003 Rev. E.

**Transmitter Functional Description**

# **1** Transmitter Functional Description

MC33493A is a PLL-tuned low-power UHF transmitter. The different modes of operation are controlled by the microcontroller through several digital input pins. The power supply voltage ranges from 1.9 V to 3.6 V, allowing operation with a single lithium cell.

# 2 Phase Locked Loop and Local Oscillator

The VCO is a completely integrated relaxation oscillator. The phase frequency detector (PFD) and the loop filter are fully integrated. The exact output frequency is equal to:  $f_{RFOUT} = f_{XTAL} \times [PLL \text{ divider ratio}]$ . The frequency band of operation is selected through the BAND pin.

Table 3 shows details for each frequency band selection.

Table 3. Band Selection and Associated Divider Ratios

| BAND Input Level | Frequency Band<br>(MHz) | PLL Divider Ratio | Crystal Oscillator<br>Frequency (MHz) |

|------------------|-------------------------|-------------------|---------------------------------------|

| High             | 315                     | 32                | 9.84                                  |

|                  | 434                     | 52                | 13.56                                 |

| Low              | 868                     | 64                | 10.00                                 |

An out-of-lock function is performed by monitoring the PFD output voltage. When it exceeds defined limits, the RF output stage is disabled.

# 3 Radio Frequency (RF) Output Stage

The radio frequentcy (RF) output stage source is a single-ended square-wave switched current. Harmonics are present in the output current drive. Their radiated absolute level depends on the antenna characteristics and output power. Typical application demonstrates compliance to ETSI standard.

A resistor,  $R_{ext}$ , connected to the REXT pin controls the output power allowing a trade-off between radiated power and current consumption.

The output voltage is internally clamped to  $V_{cc} \pm 2 V_{be}$  (typ.  $V_{cc} \pm 1.5 V @ T_A=25 °C$ ).

## 4 Modulation

To select the On Off Keying (OOK) modulation, a low-logic level must be applied on the MODE pin. This modulation is performed by switching the RF output stage on or off. The logic level applied on the DATA pin controls the output stage state:

$DATA = 0 \rightarrow output stage off,$

DATA =  $1 \rightarrow$  output stage on.

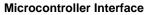

Applying a high-logic level on the MODE pin selects Frequency Shift Keying (FSK) modulation. This modulation is achieved by crystal pulling. An internal switch connected to the CFSK pin enables switching the external crystal load capacitors. Figure 2 shows the possible configurations: serial and parallel.

The logic level applied on pin DATA controls the state of this internal switch:

DATA=0  $\rightarrow$  switch off, DATA=1  $\rightarrow$  switch on.

DATA input is internally re-synchronized by the crystal reference signal. The corresponding jitter on the data duty cycle cannot exceed  $\pm 1$  reference period ( $\pm 75$  ns for a 13.56 MHz crystal).

This crystal pulling solution implies that the RF output frequency deviation equals the crystal frequency deviation multiplied by the PLL Divider ratio (see Table 3).

## 5 Microcontroller Interface

Four digital input pins (ENABLE, DATA, BAND, and MODE) enable the circuit to be controlled by a microcontroller. The band frequency and the modulation type should be configured before enabling the circuit.

One digital output pin, DATACLK, provides the microcontroller with a reference frequency for data clocking. This frequency is equal to the crystal oscillator frequency divided by 64 (see Table 4).

### Table 4. DATACLK Frequency vs Crystal Oscillator Frequency

| Crystal Oscillator Frequency (MHz) | DATACLK Frequency (kHz) |

|------------------------------------|-------------------------|

| 9.84                               | 154                     |

| 13.56                              | 212                     |

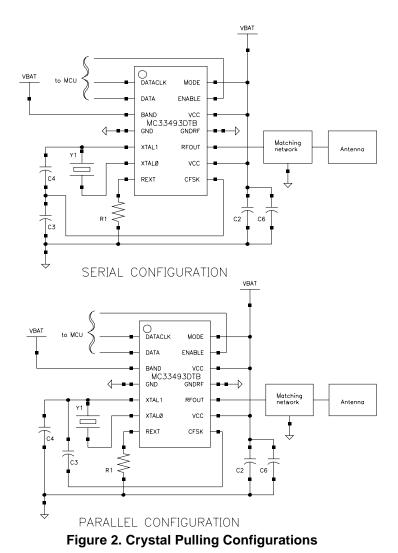

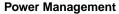

State Machine

## 6 State Machine

Figure 3 details the state machine.

Figure 3. State machine

State 1: The circuit is in standby mode and draws only a leakage current from the power supply.

State 2: In this state, the PLL is out of the lock-in range; therefore, the RF output stage is switched off, preventing RF transmission. Data clock is available on the DATACLK pin. Each time the device is enabled, the state machine passes through this state.

State 3: In this state, the PLL is within the lock-in range. If  $t < t_{PLL\_lock\_in}$ , the PLL may be in acquisition mode. If  $t \ge t_{PLL\_lock\_in}$ , then the PLL is locked. Data entered on the DATA pin are output on the RFOUT pin according to the modulation selected by the level applied on the MODE pin.

State 4: When the supply voltage falls below the shutdown voltage threshold ( $V_{SDWN}$ ,) the entire circuit switches off. After this shutdown, applying a low level on the ENABLE pin unlatches the circuit.

Figure 4 shows the waveforms of the main signals for a typical application cycle.

Figure 4. Signals Waveform and Timing Definition

## 7 Power Management

When the battery voltage falls below the shutdown voltage threshold ( $V_{SDWN}$ ) the entire circuit switches off. After this shutdown, the circuit is latched until a low level is applied on pin ENABLE (see State 4 of the state machine).

## 8 Data Clock

At start-up, data clock timing is valid after the data clock settling time. Because the clock is switched off asynchronously, the last period duration cannot be guaranteed.

## 9 Electrical Characteristics

Unless otherwise specified, voltage range  $V_{cc}=[V_{shutdown}; 3.6 V]$ , temperature range TA=[-20 °C;+ 85 °C],  $R_{ext}=12 \text{ k}\Omega \pm 5\%$ , RF output frequency  $f_{carrier} = 433.92$  MHz, reference frequency  $f_{reference} = 13.560$  MHz, output load RL = 50  $\Omega \pm 1\%$  (Figure 9). Values refer to the circuit shown in the recommended application schematics: Figure 12 shows OOK modulation and Figure 14 shows FSK modulation. Typical values reflect average measurement at VCC = 3 V, TA = 25 °C.

**Electrical Characteristics**

|      |                                                               |                                                                                                  |      | Limits         |      | 11             |  |

|------|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------|----------------|------|----------------|--|

|      | Parameter                                                     | Test Conditions, Comments                                                                        | Min. | Тур.           | Max. | Unit           |  |

| 1    | General Parameters                                            |                                                                                                  |      |                |      |                |  |

| 1.1  |                                                               | $T_A \le 25 \ ^\circ C$                                                                          | -    | 0.1            | 5    | nA             |  |

| 1.2  | Supply current in<br>standby mode                             | T <sub>A</sub> = 60 °C                                                                           | _    | 7              | 30   | nA             |  |

| 1.3  |                                                               | T <sub>A</sub> = 85 °C                                                                           |      | 40             | 150  | nA             |  |

| 1.7  |                                                               | 315 and 434 bands,<br>OOK and FSK modulation,<br>continuous wave, T <sub>A</sub> = 25 °C         | -    | 11.6           | 13.5 | mA             |  |

| 1.5  |                                                               | 315 and 434 bands, DATA=0, –20 °C $\leq$ T_A $\leq$ 85 °C                                        | —    | 4.4            | 5.5  | mA             |  |

| 1.6  | Supply current in transmission mode                           | 868 MHz band, DATA=0, –20 °C $\leq$ T_A $\leq$ 85 °C                                             | —    | 4.6            | 5.7  | mA             |  |

| 1.8  |                                                               | 315 and 434 bands,<br>OOK and FSK modulation,<br>continuous wave, −20 °C ≤ T <sub>A</sub> ≤85 °C | _    | 11.6           | 14.4 | mA             |  |

| 1.9  |                                                               | 868 MHz band,<br>OOK and FSK modulation,<br>continuous wave, –20 °C ≤T <sub>A</sub> ≤ 85 °C      | -    | 11.8           | 14.6 | mA             |  |

| 1.10 | Supply voltage                                                |                                                                                                  | —    | 3              | 3.6  | V              |  |

| 1.12 |                                                               | $T_A = -20 \ ^\circ C$                                                                           | —    | 1.99           | 2.06 | V              |  |

| 1.13 | Shutdown voltage threshold                                    | T <sub>A</sub> = 25 °C                                                                           |      | 1.86           | 1.95 | V              |  |

| 1.14 | 5                                                             | T <sub>A</sub> = 60 °C                                                                           |      | 1.76           | 1.84 | V              |  |

| 1.15 |                                                               | T <sub>A</sub> = 85 °C                                                                           |      | 1.68           | 1.78 | V              |  |

| 2    |                                                               | RF Parameters                                                                                    |      |                |      |                |  |

| 2.1  | R <sub>ext</sub> value                                        |                                                                                                  | 12   | —              | 21   | kΩ             |  |

| 2.2  |                                                               | 315 and 434 MHz bands, with 50 $\Omega$ matching network                                         | —    | 5              | _    | dBm            |  |

| 2.3  | Output power                                                  | 868 MHz band, with 50 $\Omega$ matching network                                                  | —    | 1              | _    | dBm            |  |

| 2.4  | Output power                                                  | 315 and 434 MHz bands, $-20~^{\circ}\text{C} \leq \text{T}_{\text{A}} \leq 85~^{\circ}\text{C}$  | -2.5 | 0              | 2.5  | dBm            |  |

| 2.8  |                                                               | 868 MHz band,<br>–20 °C ≤T <sub>A</sub> ≤ 85 °C                                                  | -6   | -3             | 0    | dBm            |  |

| 2.12 | Current and output power variation vs. R <sub>ext</sub> value | 315 and 434 MHz bands, with 50 $\Omega$ matching network                                         | _    | -0.35<br>-0.25 | —    | dB/kΩ<br>mA/kΩ |  |

| 2.13 |                                                               | 315 and 434 MHz bands, with 50 $\Omega$ matching network                                         |      | -34            | —    | dBc            |  |

| 2.14 | Harmonic 2 level                                              | 868 MHz band, with 50 $\Omega$ matching network                                                  | —    | -49            | —    | dBc            |  |

| 2.15 |                                                               | 315 and 434 MHz bands                                                                            | —    | -23            | -17  | dBc            |  |

| 2.16 |                                                               | 868 MHz band                                                                                     |      | -38            | -27  | dBc            |  |

### **Table 5. Electrical Characteristics**

#### **Electrical Characteristics**

|      | Devenuetor                                                 | Test Canditions, Commonts                                                                |      | Limits |      | l lucit |

|------|------------------------------------------------------------|------------------------------------------------------------------------------------------|------|--------|------|---------|

|      | Parameter                                                  | Test Conditions, Comments                                                                | Min. | Тур.   | Max. | Unit    |

| 2.17 |                                                            | 315 and 434 MHz bands, with 50 $\Omega$ matching network                                 | -    | -32    | —    | dBc     |

| 2.18 | Harmonic 3 level                                           | 868 MHz band, with 50 $\Omega$ matching network                                          | -    | -57    | —    | dBc     |

| 2.19 |                                                            | 315 and 434 MHz bands                                                                    | —    | -21    | -15  | dBc     |

| 2.20 |                                                            | 868 MHz band                                                                             | —    | -48    | -39  | dBc     |

| 2.21 | Spurious level                                             | 315 and 434 MHz bands                                                                    | —    | -36    | -24  | dBc     |

| 2.22 | @ f <sub>carrier</sub> ± f <sub>DATACLK</sub>              | 868 MHz band                                                                             | —    | -29    | -17  | dBc     |

| 2.23 | Spurious level                                             | 315 MHz band                                                                             |      | -37    | -30  | dBc     |

| 2.24 | @ $f_{carrier} \pm f_{reference}$                          | 434 MHz band                                                                             | —    | -44    | -34  | dBc     |

| 2.25 |                                                            | 868 MHz band                                                                             | —    | -37    | -27  | dBc     |

| 2.41 | Spurious level                                             | 315 MHz band                                                                             | —    | -62    | -53  | dBc     |

| 2.26 | @ f <sub>carrier</sub> /2                                  | 434 MHz band                                                                             | _    | -80    | -60  | dBc     |

| 2.27 |                                                            | 868 MHz band                                                                             | —    | -45    | -39  | dBc     |

| 2.30 | Phase noise                                                | 315 and 434 MHz bands,<br>±175 kHz from f <sub>carrier</sub>                             | —    | -75    | -68  | dBc/Hz  |

| 2.31 |                                                            | 868 MHz band,<br>±175 kHz from f <sub>carrier</sub>                                      | _    | -73    | -66  | dBc/Hz  |

| 2.32 | PLL lock-in time,<br><sup>t</sup> PLL_lock_in              | $f_{carrier}$ within 30 kHz from the final value, crystal series resistor = 150 $\Omega$ | _    | 400    | 1600 | μs      |

| 2.33 | XTAL1 input capacitance                                    |                                                                                          |      | 1      | —    | pF      |

| 2.34 | Crystal resistance                                         | OOK modulation                                                                           | —    | 20     | 200  | Ω       |

| 2.44 |                                                            | FSK modulation                                                                           |      | 20     | 50   |         |

| 2.35 | OOK modulation depth                                       |                                                                                          | 75   | 90     | —    | dBc     |

| 2.36 | FSK modulation                                             | 315 and 434 MHz bands, see note                                                          | —    | —      | 100  | kHz     |

| 2.37 | carrier frequency<br>total deviation                       | 868 MHz band, see note                                                                   | _    | _      | 200  | kHz     |

| 2.38 | CFSK output resistance                                     | MODE = 0, DATA = x $MODE = 1, DATA = 0$                                                  | 50   | 70     | —    | kΩ      |

| 2.39 |                                                            | MODE = 1, DATA = 1                                                                       | _    | 90     | 300  | Ω       |

| 2.43 | CFSK output capacitance                                    |                                                                                          | _    | 1      | —    | pF      |

| 2.40 | Data rate                                                  | Manchester coding                                                                        | _    | —      | 10   | kbit/s  |

| 2.41 | Data to RF delay difference between                        | MODE = 0, see note                                                                       | 3.5  | 5.25   | 7.5  | μs      |

| 2.42 | falling and rising edges,<br>t <sub>delay_difference</sub> | MODE = 1, see note                                                                       | -200 | —      | 200  | ns      |

### Table 5. Electrical Characteristics (continued)

#### **RF Output Spectrum**

|      | Deremeter                                                           | Test Conditions, Comments                                                  | Limits                    |           |                           |      |  |

|------|---------------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------|-----------|---------------------------|------|--|

|      | Parameter Test Conditions, Comments                                 |                                                                            |                           | Тур.      | Max.                      | Unit |  |

|      | This parameter depends on crystal ch<br>Delay difference definition | haracteristics, load capacitor values (see Table 4                         | ) and PC                  | B track o | capacitan                 | ce.  |  |

|      | ut data                                                             | From 50% of data<br>demodulated sign<br>t <sub>delay_difference</sub> = t  | nal envel                 | ope edg   | e:                        |      |  |

|      | <sup>t</sup> delay_rise                                             | <sup>t</sup> delay_fall                                                    |                           |           |                           |      |  |

| 3    |                                                                     | Microcontroller Interfaces                                                 |                           |           |                           |      |  |

| 3.1  | Input low voltage                                                   |                                                                            | 0                         | _         | 0.3 x<br>V <sub>CC</sub>  | V    |  |

| 3.2  | Input high voltage                                                  | Pins: BAND, MODE, ENABLE, and DATA                                         |                           | _         | V <sub>CC</sub>           | V    |  |

| 3.3  | Input hysteresis voltage                                            |                                                                            |                           | —         | 120                       | mV   |  |

| 3.4  | Input current                                                       | Pins: BAND, MODE, DATA = 1                                                 |                           | _         | 100                       | nA   |  |

| 3.5  | ENABLE pulldown resistor                                            |                                                                            | —                         | 180       | —                         | kΩ   |  |

| 3.6  | DATACLK output low voltage                                          |                                                                            | 0                         | —         | 0.25 x<br>V <sub>CC</sub> | V    |  |

| 3.7  | DATACLK output high voltage                                         | $C_{load} = 2  pF$                                                         | 0.75 x<br>V <sub>CC</sub> | —         | V <sub>CC</sub>           | V    |  |

| 3.8  | DATACLK rising time                                                 | C <sub>load</sub> = 2 pF, measured from 20% to 80% of the<br>voltage swing |                           | 250       | 500                       | ns   |  |

| 3.9  | DATACLK falling time                                                |                                                                            |                           | 150       | 400                       | ns   |  |

| 3.10 | DATACLK settling time,<br><sup>t</sup> DATACLK_settling             | 45% < duty cycle f <sub>DATACLK</sub> < 55%                                |                           | 800       | 2000                      | μs   |  |

### Table 5. Electrical Characteristics (continued)

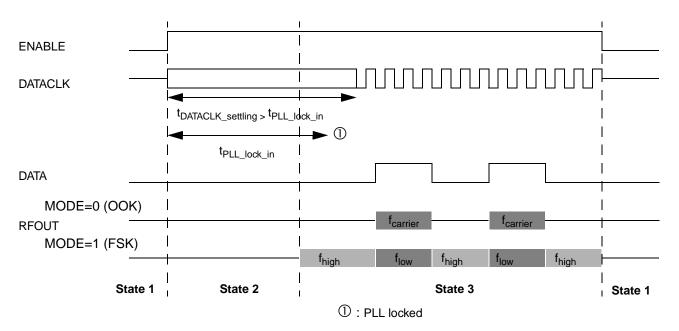

## 10 RF Output Spectrum

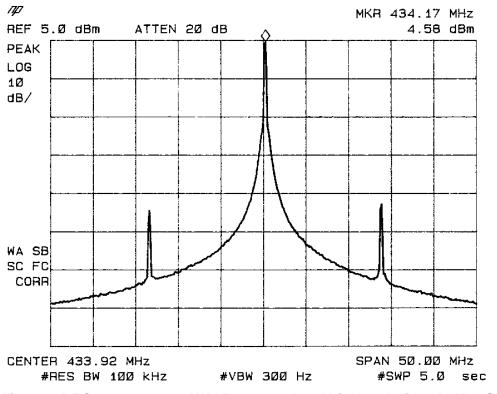

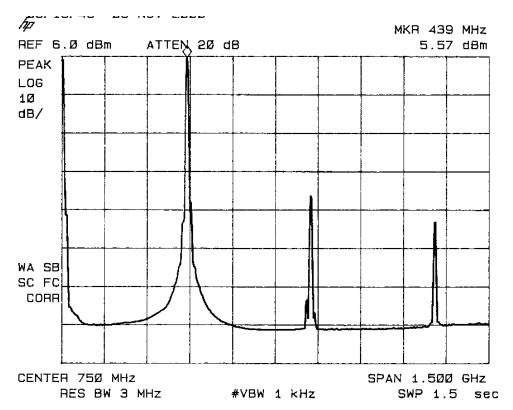

The following figures represent spectrums of the transmitter carrier, measured in conduction mode. Three different spans have been used. The 5 MHz span spectrum (Figure 5) shows phase noise response close to the RF carrier and the noise suppression within the PLL-loop bandwidth. The 50 MHz span spectrum (Figure 6) shows phase noise and reference spurious. Finally, the 1.5 GHz span spectrum (Figure 7) shows the second and third harmonics of carrier. All spectrums are measured in OOK modulation at DATA=1.

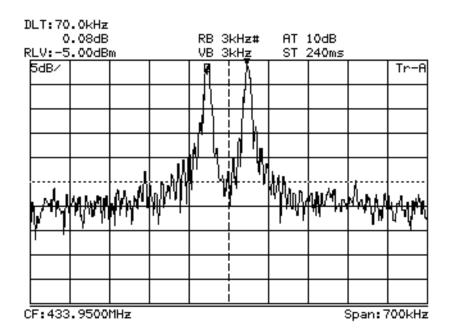

Figure 8 shows the spectrum in case of FSK modulation with 45 kHz deviation at 4 kbit/s data rate.

Figure 5. RF Spectrum at 434 MHz Frequency Band Displayed with a 5 MHz Span

Figure 6. RF Spectrum at 434 MHz Frequency Band Displayed with a 50 MHz Span

**RF Output Spectrum**

Figure 7. RF Spectrum at 434 MHz Frequency Band Displayed with a 1.5 GHz Span

Figure 8. RF Spectrum at 434 MHz Band for a 70 kHz FSK Deviation at 4.8 kbit/s

**Output Power Measurement**

### 11 Output Power Measurement

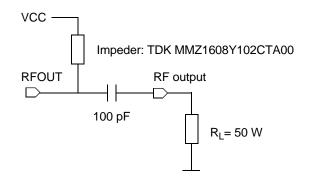

The RF output levels given in Section 9, "Electrical Characteristics," are measured with a 50  $\Omega$  load directly connected to the RFOUT pin, as shown below in Figure 9. This wideband coupling method gives results independent of the application.

#### **Figure 9. Output Power Measurement Configurations**

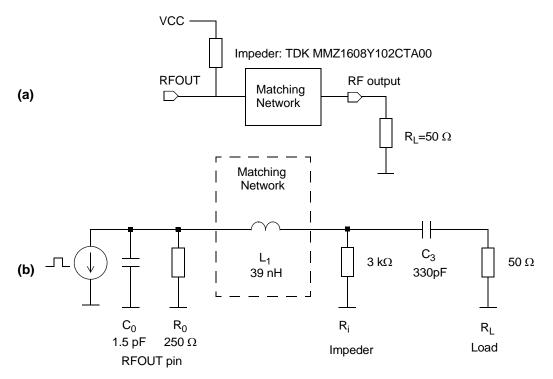

The configuration shown in Figure 10(a) provides better efficiency in terms of output power and harmonics rejection. The schematic on Figure 10(b) gives the equivalent circuit of the RFOUT pin and the DC bias impeder as well as matching network components for 434 MHz frequency band.

Figure 10. Output Model and Matching Network for 434 MHz Band

#### **Complete Application Schematic and PCB for OOK Modulation**

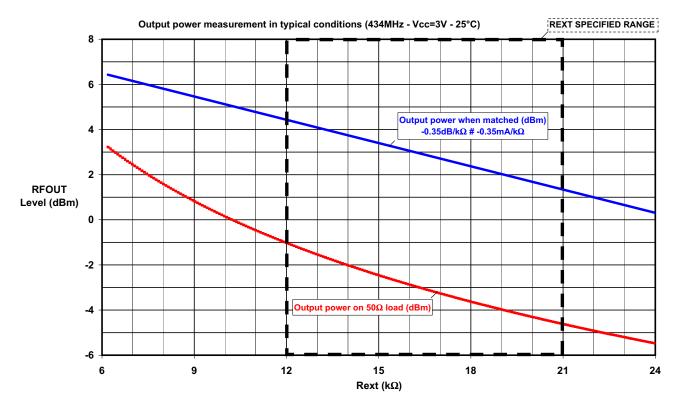

Figure 11 shows the output power versus the  $R_{ext}$  resistor value with 50  $\Omega$  load and with matching network.

Figure 11. Output Power at 434 MHz Band vs Rext Value

The 50  $\Omega$  matching network used for the 868 MHz band is similar to the 434 MHz, excepting components values: L1 is changed to 8.2 nH and C3 to 470 pF in Figure 11. The typical gain of this 868 MHz matching network is 4 dB compared to unmatched configuration.

### 12 Complete Application Schematic and PCB for OOK Modulation

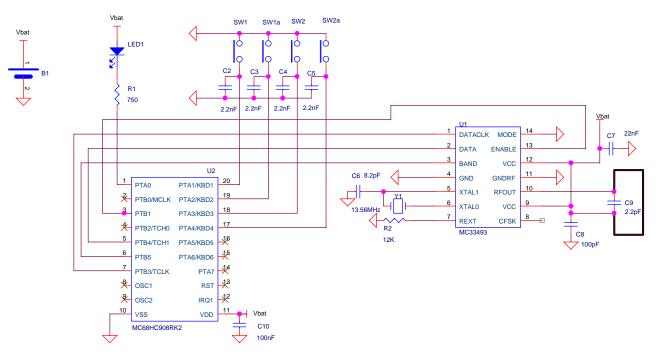

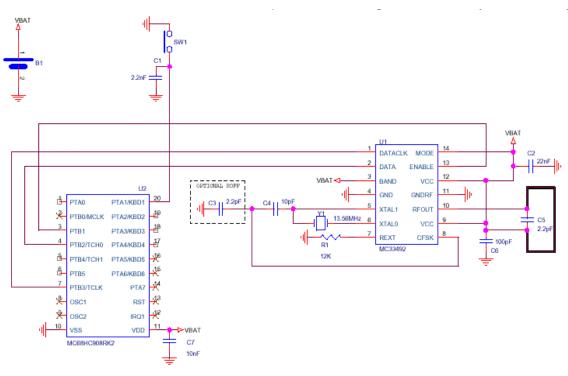

Figure 12 shows a complete application schematic using a MC68HC908RK2 microcontroller. OOK modulation is selected,  $f_{carrier} = 433.92$  MHz. The C<sub>2</sub> to C<sub>5</sub> capacitors can be removed if switch debounce is done by software.

**Complete Application Schematic and PCB for OOK Modulation**

For 868 MHz band application, the input pin BAND must be wired to ground. See component description on Table 6 and Table 7.

| Component                                                  | Function               | Value               | Unit |

|------------------------------------------------------------|------------------------|---------------------|------|

| Y1                                                         | Crystal,               | 315 MHz band: 9.84  | MHz  |

|                                                            | see Table 7            | 434 MHz band: 13.56 | MHz  |

|                                                            |                        | 868 MHz band: 13.56 | MHz  |

| R2 RF output level setting<br>resistor (R <sub>ext</sub> ) |                        | 12                  | kΩ   |

| C6                                                         | Crystal load capacitor | 8.2 <sup>1</sup>    | pF   |

| C7 Power supply decoupling<br>C8 capacitors                |                        | 22                  | nF   |

|                                                            |                        | 100                 | pF   |

Table 6. External Components Description for OOK

<sup>1</sup> C6 value equals recommended crystal load capacitance reduced by the PCB stray capacitances.

Examples of crystal reference are given below (see characteristics in Table 7) for different application bands:

- at 315 MHz band (f<sub>reference</sub> = 9.84375 MHz, -40  $^\circ$ C < T<sub>A</sub> < 85  $^\circ$ C): NDK LN-G102-950,

- at 434/868 MHz bands (f<sub>reference</sub> = 13.56 MHz, -40 °C < T<sub>A</sub> < 125 °C): NDK NX8045GB/CSJ S1-40125-8050-12 and NDK NX1255GA.

#### Complete Application Schematic and PCB for FSK Modulation

| Parameter            | NDK LN-G102-950<br>(for 315 MHz) | NDK NX8045GB/CSJ<br>S1-40125-8050-12<br>(for 434 MHz and 868 MHz) | NDK NX1255GA<br>(for 434 MHz and 868 MHz) | Unit |

|----------------------|----------------------------------|-------------------------------------------------------------------|-------------------------------------------|------|

| Load capacitance     | 12                               | 12                                                                | 12                                        | pF   |

| Motional capacitance | 3.33                             | 4.4                                                               | 10.5                                      | fF   |

| Static capacitance   | 1.05                             | 1.5                                                               | 2.46                                      | pF   |

| Loss resistance      | 28                               | 18.5                                                              | 10                                        | Ω    |

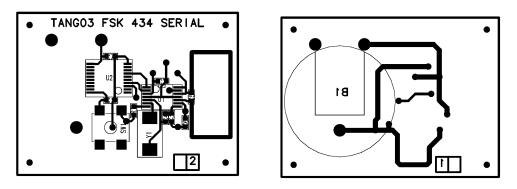

Figure 13 shows a two-button keyfob board. Size is  $30 \times 45$  millimeters.

Figure 13. Two-Button Keyfob Board Layout

### 13 Complete Application Schematic and PCB for FSK Modulation

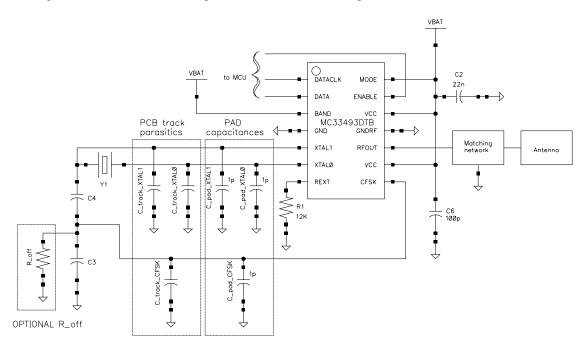

Figure 14 shows a complete application schematic using a MC68HC908RK2 microcontroller. FSK modulation is selected,  $f_{carrier}$  = 433.92 MHz. C<sub>1</sub> capacitor can be removed if switch debounce is done by software.

NP

**Complete Application Schematic and PCB for FSK Modulation**

### Figure 14. Application Schematic for FSK Modulation, Serial Configuration, 434 MHz Frequency Band

For 868 MHz band application, the input pin BAND must be wired to ground. See component description in Table 8.

| Table 8. External Components | Description for FSK |

|------------------------------|---------------------|

|------------------------------|---------------------|

| Component | Function                                                | Value                               | Unit |

|-----------|---------------------------------------------------------|-------------------------------------|------|

| Y1        | Crystal                                                 | 315 MHz band: 9.84,<br>See Table 7  | MHz  |

|           |                                                         | 434 MHz band: 13.56,<br>see Table 7 | MHz  |

|           |                                                         | 868 MHz band: 13.56,<br>see Table 7 | MHz  |

| R1        | RF output level setting<br>resistor (R <sub>ext</sub> ) | 12                                  | kΩ   |

| C3        | Crystal load capacitor                                  | See Table 9                         | pF   |

| C4        |                                                         |                                     | pF   |

| C2        | Power supply decoupling capacitor                       | 22                                  | nF   |

| C6        |                                                         | 100                                 | pF   |

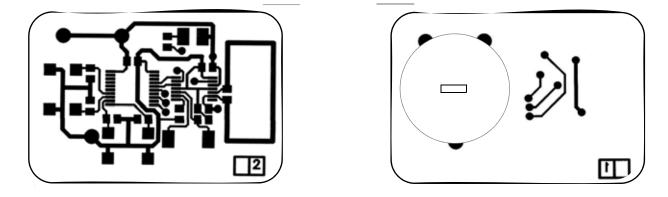

Figure 15 shows the corresponding PCB layout.

#### Figure 15. Application PCB Layout for FSK Modulation, Serial Configuration, 434 MHz Frequency Band

Table 9 gives the measured FSK deviations respective to C3 and C4 capacitor values for three deviations. Crystal reference is NDK NX8045GB/CSJ S1-40125-8050-12.

| Carrier frequency<br>(MHz) | Carrier frequency total deviation (kHz) | C3 capacitor (pF) | C4 capacitor (pF) | Recommended R_off value (k $\Omega$ ) |

|----------------------------|-----------------------------------------|-------------------|-------------------|---------------------------------------|

| 434                        | 45                                      | 4.7               | 6.8               | 10                                    |

|                            | 70                                      | 2.2               | 10                | —                                     |

|                            | 100                                     | 1                 | 15                | 22                                    |

| 868                        | 90                                      | 4.7               | 6.8               | 10                                    |

|                            | 140                                     | 2.2               | 10                | —                                     |

|                            | 200                                     | 1                 | 15                | 22                                    |

Table 9. Crystal Pulling Capacitor Values vs Carrier Frequency Total Deviation -1-

Another crystal reference, NDK NX1255GA (see Table 7), is enabled to reach higher deviation as mentioned on Table 10. These results are due to the higher crystal motional capacitor.

Table 10. Crystal Pulling Capacitor Values vs Carrier Frequency Total Deviation -2-

| Carrier frequency<br>(MHz) | Carrier frequency total deviation (kHz) | C3 capacitor value<br>(pF) | C4 capacitor value<br>(pF) | Recommended R_off value (k $\Omega$ ) |

|----------------------------|-----------------------------------------|----------------------------|----------------------------|---------------------------------------|

| 434                        | 150                                     | 1                          | 27                         | —                                     |

| 868                        | 300                                     | 1                          | 27                         | —                                     |

### 14 **Recommendations for FSK Modulation**

FSK deviation is function of total load capacitance presented to the crystal. This load capacitance is constituted by various contributors:

- the crystal characteristic, especially its static capacitance

- the external load capacitors (C3, C4 as defined in Figure 14 and Table 9)

- the device internal capacitance of pins XTAL0, XTAL1, CFSK

- the PCB track capacitance

The schematic given in Figure 16 shows a typical FSK application using serial capacitor configuration, where device pads and PCB track capacitances are mentioned.

Device pad capacitance is defined by the package capacitance and by the internal circuitry. Typical capacitance values for these pads are given in Table 11.

Some realistic assumptions and measurements have been made concerning track parasitic capacitances for a 0.8 mm FR4 double side application PCB. They are given in Table 11 and the corresponding PCB layout is shown in figure Figure 17.

To achieve large deviations, this total load capacitance must be lowered. For a given crystal, the PCB must be carefully laid out to reduce the capacitance of the tracks wired to XTAL0, XTAL1, and CFSK pins.

**Recommendation**: a R\_off resistor can be added in parallel with the FSK switch to optimize the transient response of demodulated signal. Table 11 gives the optimized R\_off values for two deviations. There is no footprint for R\_off resistor on the layout in Figure 16. When used, this component can be soldered on top of C3.

Figure 16. Crystal Load Capacitance Contributors Schematic

| Capacitance   | Value | Unit |

|---------------|-------|------|

| C_pad_XTAL0   | 1     | pF   |

| C_pad_XTAL1   | 1     | pF   |

| C_pad_CFSK    | 1     | pF   |

| C_track_XTAL0 | 1.5   | pF   |

| C_track_XTAL1 | 1.5   | pF   |

| C_track_CFSK  | 1.5   | pF   |

**Table 11. Pads and Tracks Parasitic Values**

PLL Tuned UHF Transmitter for Data Transfer Applications, Rev. 2

**Case Outline Dimensions**

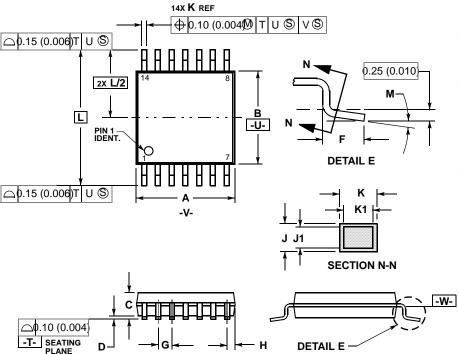

## 15 Case Outline Dimensions

NOTES:

- DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

CONTROLLING DIMENSION: MILLIMETER.

- CONTROLLING DIMENSION: MILLIMETER.

DIMENSION A DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH OR GATE BURRS SHALL NOT

- MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE.

DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.

INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED

- 0.25 (0.010) PER SIDE. DIMENSION K DOES NOT INCLUDE DAMBAR

- DIMENSION K DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08 (0.003) TOTAL IN EXCESS OF THE K DIMENSION AT MAXIMUM MATERIAL CONDITION.

- MAXIMUM MATERIAL CONDITION.

TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY.

- 7. DIMENSION A AND B ARE TO BE

|     | MILLIN                  | IETERS | INCHES     |       |  |  |

|-----|-------------------------|--------|------------|-------|--|--|

| DIM | MIN                     | MAX    | MIN        | MAX   |  |  |

| Α   | 4.90                    | 5.10   | 0.193      | 0.200 |  |  |

| В   | 4.30                    | 4.50   | 0.169      | 0.177 |  |  |

| С   | _                       | 1.20   | _          | 0.047 |  |  |

| D   | 0.50 0.75 0<br>0.65 BSC |        | 0.002      | 0.006 |  |  |

| F   |                         |        | 0.020 0.03 | 0.030 |  |  |

| G   |                         |        | 0.026 BSC  |       |  |  |

| н   |                         |        | 0.020      | 0.024 |  |  |

| J   | 0.09                    | 0.20   | 0.004      | 0.008 |  |  |

| J1  | 0.09                    | 0.16   | 0.004      | 0.006 |  |  |

| Κ   | 0.19                    | 0.30   | 0.007      | 0.012 |  |  |

| K1  | 0.19                    | 0.25   | 0.007      | 0.010 |  |  |

| L   | 6.40 BSC                |        | 0.252 BSC  |       |  |  |

| М   | 0°                      | 8°     | 0°         | 8°    |  |  |

CASE 948G-01 ISSUE O

\_\_\_\_\_

THIS PAGE INTENTIONALLY BLANK

#### How to Reach Us:

Home Page: www.freescale.com

#### Web Support:

http://www.freescale.com/support

#### USA/Europe or Locations Not Listed:

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 +1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

For Literature Requests Only: Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com

Document Number: MC33493A Rev. 2 03/2007 Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics as their non-RoHS-compliant and/or non-Pb-free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org © Freescale Semiconductor, Inc. 2007. All rights reserved.