Archived by Freescale Semiconductor, Inc., 2008

## **escale Semiconductor**

Advance Information

## **1.0 A Negative Voltage Hot Swap Controller**

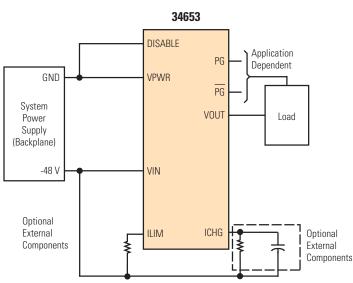

The 34653 is a highly integrated -48 V hot swap controller with an internal Power MOSFET. It provides the means to safely install and remove boards from live -48 V backplanes without having to power down the entire system. It regulates the inrush current, from the supply to the load's filter capacitor, to a user-programmable limit, allowing the system to safely stabilize. A disable function allows the user to disable the 34653 manually or through a microprocessor and safely disconnect the load from the main power line.

The 34653 has active high and active low power good output signals that can be used to directly enable a power module load. Undervoltage and overvoltage detection circuitry monitors the input voltage to check that it is within its operating range. A start-up delay timer ensures that it is safe to turn on the Power MOSFET and charge the load capacitor.

A two-level current limit approach to controlling the inrush current and switching on the load limits the peak power dissipation in the Power MOSFET. Both current limits are user programmable.

#### Features

iive Informatior

- Integrated Power MOSFET and Control IC in a Small Outline Package

- Input Voltage Operation Range from -39 V to -74 V

- Programmable Overcurrent Limit with Auto Retry

- Programmable Charging Current Limit Independent of Load Capacitor

- Start-Up and Retry Delay Timer

- Overvoltage and Undervoltage Detection

- Active High and Low Power Good Output Signals

- Thermal Shutdown

- Pb-Free Packaging Designated by Suffix Code EF

| ORD           | ERING INFORMA                          | TION    |

|---------------|----------------------------------------|---------|

| Device        | Temperature<br>Range (T <sub>A</sub> ) | Package |

| MCZ34653EF/R2 | -40°C to 85°C                          | 8 SOICN |

| MC34653EF/R2  | -40 C 10 65 C                          | 0 301CN |

98ASB42564B

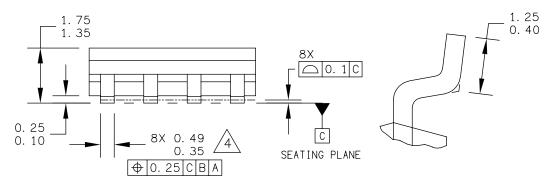

**8-PIN SOICN**

Document Number: MC34653 Rev. 8.0, 2/2007

34653

HOT SWAP

## **√**RoHS

Archive Information

Figure 1. 34653 Simplified Application Diagram

\* This document contains certain information on a new product. Specifications and information herein are subject to change without notice. © Freescale Semiconductor, Inc., 2007. All rights reserved.

Archive Information

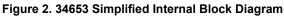

RNAL BLOCK DIAGRAM

## INTERNAL BLOCK DIAGRAM

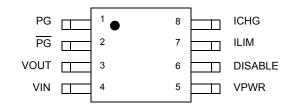

**PIN CONNECTIONS**

## **PIN CONNECTIONS**

Figure 3. 8-SOICN Pin Connections

#### Table 1. 8-SOICN Pin Definitions

A functional description of each pin can be found in the FUNCTIONAL PIN DESCRIPTION section beginning on page 8.

| Pin | Pin Name | Formal Name                        | Definition                                                                                                                                                                                                                                    |

|-----|----------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | PG       | Power Good Output<br>(Active High) | This is an active high power good output signal. This pin is referenced to VIN.                                                                                                                                                               |

| 2   | PG       | Power Good Output<br>(Active Low)  | This is an active low power good output signal. This pin is referenced to VIN.                                                                                                                                                                |

| 3   | VOUT     | Voltage Output                     | This pin is the drain of the internal Power MOSFET and supplies a current limited voltage to the load.                                                                                                                                        |

| 4   | VIN      | Negative Supply<br>Voltage Input   | This is the most negative power supply input. All pins except DISABLE are referenced to this input.                                                                                                                                           |

| 5   | VPWR     | Positive Supply<br>Voltage Input   | This is the most-positive power supply input. The load connects between this pin and the VOUT pin.                                                                                                                                            |

| 6   | DISABLE  | Disable Input Control              | This pin is used to easily disconnect or connect the load from the main power line by disabling or enabling the 34653. It can also be used to reset the fault conditions that cause a "Power No Good" signal. This pin is referenced to VPWR. |

| 7   | ILIM     | Current Limit Control              | This pin is used to set the overcurrent limit during normal operation.                                                                                                                                                                        |

| 8   | ICHG     | Charging Current<br>Limit Control  | This pin is used to set the load's input capacitor charging current limit, hence limiting the inrush current to a known constant value.                                                                                                       |

## **MAXIMUM RATINGS**

### Table 2. Maximum Ratings

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Ratings                                                                       | Symbol               | Value                                           | Unit |

|-------------------------------------------------------------------------------|----------------------|-------------------------------------------------|------|

| ELECTRICAL RATINGS                                                            |                      |                                                 |      |

| Power Supply Voltage                                                          | V <sub>PWR</sub>     | 85                                              | V    |

| Power MOSFET Energy Capability                                                | E <sub>MOSFET</sub>  | Varies <sup>(1)</sup>                           | mJ   |

| Continuous Output Current <sup>(2)</sup>                                      | I <sub>O(CONT)</sub> | 1.0                                             | А    |

| Maximum Voltage                                                               |                      |                                                 | V    |

| DISABLE Pin                                                                   | _                    | V <sub>IN</sub> - 0.3 to V <sub>PWR</sub> + 5.5 |      |

| ILIM and ICHG Pins                                                            | —                    | 5.0                                             |      |

| PG Pin (V <sub>PG</sub> - V <sub>IN</sub> )                                   | —                    | 85                                              |      |

| PG Pin (V <sub>PG</sub> - V <sub>IN</sub> )                                   | —                    | 85                                              |      |

| All Pins Minimum Voltage                                                      | —                    | -0.3                                            | V    |

| PG, PG Maximum Current                                                        | _                    | Internally Limited                              | А    |

| ESD Voltage, All Pins <sup>(3)</sup>                                          |                      |                                                 | V    |

| Human Body Model                                                              | V <sub>ESD3</sub>    | ±2000                                           |      |

| Machine Model                                                                 | V <sub>ESD4</sub>    | ±200                                            |      |

| THERMAL RATINGS                                                               | ·                    | · ·                                             |      |

| Storage Temperature                                                           | T <sub>STG</sub>     | -65 to 150                                      | °C   |

| Operating Temperature                                                         |                      |                                                 | °C   |

| Ambient <sup>(4)</sup>                                                        | T <sub>A</sub>       | -40 to 85                                       |      |

| Junction                                                                      | Т <sub>Ј</sub>       | -40 to 160                                      |      |

| Peak Package Reflow Temperature During Reflow <sup>(5)</sup> , <sup>(6)</sup> | T <sub>PPRT</sub>    | Note 6                                          | °C   |

| Thermal Resistance <sup>(7), (8)</sup>                                        | _                    |                                                 | °C/W |

| Junction-to-Ambient, Single-Layer Board <sup>(9)</sup>                        | R <sub>θJA</sub>     | 167                                             |      |

| Junction-to-Ambient, Four-Layer Board <sup>(10)</sup>                         | R <sub>θJMA</sub>    | 115                                             |      |

- 1. Refer to the section titled Power MOSFET Energy Capability on page 21 for a detailed explanation on this parameter.

- 2. Continuous output current capability so long as  $T_J$  is  $\leq 160^\circ C.$

- 3. ESD1 testing is performed in accordance with the Human Body Model ( $C_{ZAP}$ =100 pF,  $R_{ZAP}$ =1500  $\Omega$ ), ESD2 testing is performed in accordance with the Machine Model ( $C_{ZAP}$ =200 pF,  $R_{ZAP}$ =0  $\Omega$ ).

- 4. The limiting factor is junction temperature, taking into account power dissipation, thermal resistance, and heatsinking.

- 5. Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

- Freescale's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL), Go to www.freescale.com, search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts. (i.e. MC33xxxD enter 33xxx), and review parametrics.

- 7. Refer to the section titled Thermal Shutdown on page 15 for more thermal resistance values under various conditions.

- 8. The VOUT and VIN pins comprise the main heat conduction paths.

- 9. Per SEMI G38-87 and JEDEC JESD51-2 with the single-layer board (JESD51-3) horizontal.

- 10. Per JEDEC JESD51-6 with the board (JESD51-7) horizontal. There are no thermal vias connecting the package to the two planes in the board.

34653

### STATIC ELECTRICAL CHARACTERISTICS

#### Table 3. Static Electrical Characteristics

Characteristics noted under conditions 36 V  $\leq$  V<sub>PWR</sub>  $\leq$  80 V and -40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C. All voltages are referenced to VIN unless otherwise noted.

| Characteristic                                                      | Symbol               | Min                   | Тур  | Max                   | Unit |

|---------------------------------------------------------------------|----------------------|-----------------------|------|-----------------------|------|

| POWER SUPPLY PIN (VPWR)                                             |                      |                       |      |                       |      |

| Supply Voltage                                                      | V <sub>PWR</sub>     | 36                    | —    | 80                    | V    |

| Operating Voltage Range                                             | V <sub>PWR</sub>     | V <sub>UV(ON)</sub>   |      | V <sub>OV(ON)</sub>   | V    |

| Supply Current, Device Enabled, Default Mode, Normal Operation (11) | I <sub>IN</sub>      | —                     | 900  | 1400                  | μA   |

| Undervoltage Lockout Threshold (UVLO)                               |                      |                       |      |                       | V    |

| Rising                                                              | V <sub>UVLOR</sub>   | 7.0                   | 8.0  | 9.0                   |      |

| Falling                                                             | V <sub>UVLOF</sub>   | 6.0                   | 7.0  | 8.0                   |      |

| Hysteresis                                                          | V <sub>UVLOHY</sub>  | —                     | 1.0  | —                     |      |

| JNDERVOLTAGE CONTROL                                                |                      |                       |      | 1 1                   |      |

| UV Threshold (Default)                                              |                      |                       |      |                       | V    |

| Rising                                                              | V <sub>UV(ON)</sub>  | —                     | 38   | —                     |      |

| Falling                                                             | V <sub>UV(OFF)</sub> | —                     | 37   | —                     |      |

| Hysteresis                                                          | V <sub>UVHY</sub>    | —                     | 1.0  | —                     |      |

| DVERVOLTAGE CONTROL                                                 |                      | 1                     |      |                       |      |

| OV Threshold (Default)                                              |                      |                       |      |                       | V    |

| Rising                                                              | V <sub>OV(OFF)</sub> | —                     | 78   | —                     |      |

| Falling                                                             | V <sub>OV(ON)</sub>  | —                     | 76   | —                     |      |

| Hysteresis                                                          | V <sub>OVHY</sub>    | —                     | 2.0  | —                     |      |

| DISABLE INPUT CONTROL PIN (DISABLE) (12)                            |                      | -                     |      |                       |      |

| DISABLE Input Voltage                                               |                      |                       |      |                       | V    |

| Inactive State                                                      | V <sub>DISL</sub>    | V <sub>PWR</sub> -1.2 | —    | V <sub>PWR</sub> +1.2 |      |

| Active State, Positive Signal                                       | V <sub>DISHP</sub>   | V <sub>PWR</sub> +2.0 | —    | —                     |      |

| Active State, Negative Signal                                       | V <sub>DISHN</sub>   | —                     | —    | V <sub>PWR</sub> -2.0 |      |

| DISABLE Input Current                                               | I <sub>DIS</sub>     |                       |      |                       | μA   |

| $V_{\text{DIS}} = V_{\text{PWR}} + 3.3 \text{ V}$                   |                      | 20                    | 60   | 140                   |      |

| $V_{\text{DIS}} = V_{\text{PWR}} - 3.3 \text{ V}$                   |                      | -20                   | -60  | -140                  |      |

| V <sub>DIS</sub> = V <sub>IN</sub>                                  |                      | -50                   | -150 | -250                  |      |

Notes

11. The supply current depends on operation mode and can be calculated as follows: •Start-Up Mode:  $I_{IN} = 539 \ \mu A + 548 \ \mu * I_{CHG}(A) + 216 \ \mu * I_{LIM}(A) + V_{PWR}(V) / 460(k\Omega)$ •Normal Mode:  $I_{IN} = 539 \ \mu A + 240 \ \mu * I_{LIM}(A) + 288 \ \mu * I_{LOAD}(A) + V_{PWR}(V) / 460(k\Omega)$ •Overcurrent Mode:  $I_{IN} = 539 \ \mu A + 612 \ \mu * I_{LIM}(A) + V_{PWR}(V) / 460(k\Omega)$ •Disable Mode:  $I_{IN} = 539 \ \mu A + 240 \ \mu * I_{LIM}(A) + I_{DIS}(\mu A) + V_{PWR}(V) / 460(k\Omega)$

12. Referenced to VPWR.

# TRICAL CHARACTERISTICS

#### Table 3. Static Electrical Characteristics (continued)

Characteristics noted under conditions 36 V  $\leq$  V<sub>PWR</sub>  $\leq$  80 V and -40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C. All voltages are referenced to VIN unless otherwise noted.

| Characteristic                                         | Symbol              | Min | Тур  | Max | Un |

|--------------------------------------------------------|---------------------|-----|------|-----|----|

| CURRENT LIMIT PINS (ILIM, ICHG)                        |                     |     |      |     |    |

| Overcurrent Limit Steady State                         | I <sub>LIM</sub>    |     |      |     | A  |

| Default                                                |                     | _   | 1.0  | —   |    |

| Maximum with External Resistor                         |                     | _   | 1.25 | —   |    |

| Minimum with External Resistor                         |                     | _   | 0.15 | —   |    |

| Current Limit During Start-Up                          | I <sub>СНG</sub>    |     |      |     | A  |

| Default                                                |                     | —   | 0.1  | —   |    |

| Maximum with External Resistor                         |                     | —   | 0.5  | —   |    |

| Minimum with External Resistor                         |                     | —   | 0.05 | —   |    |

| Short Circuit Current Limit                            | I <sub>SHORT</sub>  | —   | 5.0  | —   | A  |

| I <sub>LIM</sub> Current Limit Hysteresis              | ILIMHY              | _   | 12   | _   | %  |

| I <sub>LIM</sub> Current Limit Accuracy                | ILIMCLA             | -20 | —    | 20  | %  |

| I <sub>CHG</sub> Current Limit Accuracy                | ICHGCLA             | -35 | —    | 35  | %  |

| ILIM Pin Voltage                                       | V <sub>ILIM</sub>   | —   | 3.1  | —   | V  |

| I <sub>LIM</sub> to R <sub>ILIM</sub> Setting Constant | ILIMCNS             | —   | 129  | —   | A* |

| I <sub>CHG</sub> Reference Current                     | ICHGOUT             | —   | -8.0 | —   | μ  |

| I <sub>CHG</sub> to R <sub>ICHG</sub> Setting Constant | ICHGCNS             | _   | 335  | _   | kΩ |

| POWER GOOD PINS (PG, PG) (13)                          |                     | 1   |      |     |    |

| Power Good Output Low Voltage                          | V <sub>PGL</sub>    |     |      |     | V  |

| I <sub>PG</sub> = 1.6 mA                               |                     | _   | _    | 0.5 |    |

| Power Good Leakage Current                             | I <sub>PGLG</sub>   | _   | _    | 10  | μ  |

| Power Good Current Limit                               | I <sub>PGCL</sub>   |     |      |     | m  |

| $V_{PG}$ or $V_{\overline{PG}}$ = 3.0 V                |                     | _   | —    | 7.0 |    |

| OUTPUT VOLTAGE PIN (VOUT)                              |                     |     |      | 1   |    |

| VOUT Leakage Current                                   | I <sub>OUTLG</sub>  | _   | —    | 50  | μ  |

| POWER MOSFET                                           |                     | 1   | 1    |     |    |

| ON Resistance @ 25°C                                   | R <sub>DS(ON)</sub> | _   | 144  | —   | m  |

| THERMAL SHUTDOWN                                       | 1                   |     |      |     | •  |

| Thermal Shutdown Temperature                           | T <sub>SD</sub>     | _   | 160  | —   | °( |

| Thermal Shutdown Temperature Hysteresis                | T <sub>SDHY</sub>   | _   | 25   | _   | °( |

13. Referenced to VIN.

### **DYNAMIC ELECTRICAL CHARACTERISTICS**

#### **Table 4. Dynamic Electrical Characteristics**

Characteristics noted under conditions 36 V  $\leq$  V<sub>PWR</sub>  $\leq$  80 V and -40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C. All voltages are referenced to VIN unless otherwise noted.

| Characteristic                                                                                              | Symbol             | Min      | Тур | Мах | Ur |

|-------------------------------------------------------------------------------------------------------------|--------------------|----------|-----|-----|----|

| UNDERVOLTAGE CONTROL                                                                                        |                    |          |     |     |    |

| Undervoltage Active to Gate Low Filter Time                                                                 | t <sub>UVAL</sub>  | —        | 1.0 | —   | m  |

| OVERVOLTAGE CONTROL                                                                                         |                    |          | •   |     |    |

| Overvoltage Active to Gate Low Filter Time                                                                  | t <sub>OVAL</sub>  | —        | 1.0 | —   | m  |

| DISABLE INPUT CONTROL PIN (DISABLE) (14)                                                                    |                    |          |     | 1   |    |

| DISABLE Active to Gate Low Filter Time                                                                      | t <sub>DISAL</sub> | —        | 1.0 | —   | m  |

| CURRENT LIMIT CONTROL PINS (ILIM, ICHG)                                                                     |                    | <u> </u> | ł   | ł   |    |

| Short Circuit Protection Delay                                                                              | t <sub>SCPD</sub>  | —        | —   | 10  | μ  |

| Overcurrent Limit Filter Time                                                                               | t <sub>OCFT</sub>  |          | 100 | —   | μ  |

| Overcurrent Limit Regulation Time                                                                           | t <sub>OC</sub>    |          | 3.0 | —   | m  |

| I <sub>CHG</sub> Rise Time                                                                                  | t <sub>ICHGR</sub> |          |     |     | m  |

| Default                                                                                                     |                    | —        | 1.0 | _   |    |

| Adjustable with an External Capacitor                                                                       |                    | 1.0      | —   | —   |    |

| POWER GOOD OUTPUT PINS (PG, $\overline{PG}$ ) <sup>(15)</sup>                                               |                    |          | •   |     |    |

| Power Good Output Delay Time, from Power MOSFET Enhancement to PG and $\overrightarrow{\text{PG}}$ Asserted | t <sub>PG</sub>    | 10       | 28  | 46  | m  |

| FAULT TIMER                                                                                                 |                    |          |     |     |    |

| Start-Up and Retry Delay Timer                                                                              | t <sub>TIMER</sub> |          |     |     | m  |

| Default                                                                                                     |                    | 130      | 200 | 270 |    |

Referenced to VPWR. 14.

15. Referenced to VIN.

## FUNCTIONAL DESCRIPTION

## INTRODUCTION

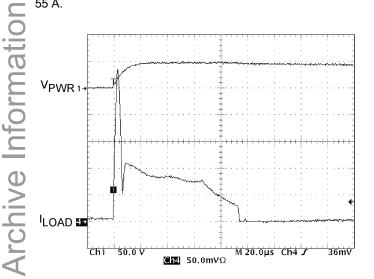

Most telecom and data transfer networks require that circuit boards be inserted and removed from the system without powering down the entire system. When a circuit board is inserted into or removed from a live backplane, the filter or bypass capacitors at the input of the board's power module or switching power supply can cause large transient currents when being charged or discharged. These currents can cause severe and permanent damage to the boards, thus making the system unstable. Figure 4 displays the inrush current to the filter capacitor if a hot swap device is absent. The inrush current reached an unsafe value of more than 55 A.

# Figure 4. Circuit Board Insertion Without a Hot Swap Device, Inrush Current Not Limited

The 34653 is an integrated negative voltage hot swap controller with an internal Power MOSFET. The 34653 resides on the plug-in boards and allows the boards to be safely inserted or removed by powering up the supply

#### **NEGATIVE SUPPLY INPUT VOLTAGE (VIN)**

This is the most negative power supply input. All pins except DISABLE, PG, and  $\overline{PG}$  are referenced to this input.

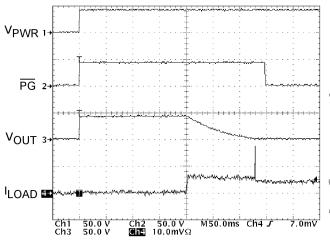

## POWER GOOD OUTPUT (ACTIVE HIGH) (PG)

The PG pin is the active high power good output signal that is used to enable or disable a load. This signal goes active after a successful power-up sequence and stays active as long as the device is in normal operation and is not experiencing any faults. voltages in a controlled manner and regulating the inrush current to a user-programmable limit, thus allowing the system to safely stabilize (see Figure 5). The 34653 provides protection against overcurrent, undervoltage, overvoltage, and overtemperature. Furthermore, it protects the system from short circuits.

#### Figure 5. Circuit Board Insertion With the Hot Swap Device, Inrush Current Limited

By integrating the control circuitry and the Power MOSFET switch into a space-efficient package, the 34653 offers a complete, cost-effective, and simple solution that takes much less board space than a similar part with an external Power MOSFET requires.

The 34653 can be used in -48 V telecom and networking systems, servers, electronic circuit breakers, -48 V distributed power systems, negative power supply control, and central office switching.

## FUNCTIONAL PIN DESCRIPTION

The signal is deactivated under the following conditions:

- Power is turned off.

- The device is disabled for more than 1.0 ms.

- The device exceeded its thermal shutdown threshold for more than 12 μs.

- The device is in overvoltage or undervoltage mode for more than 1.0 ms.

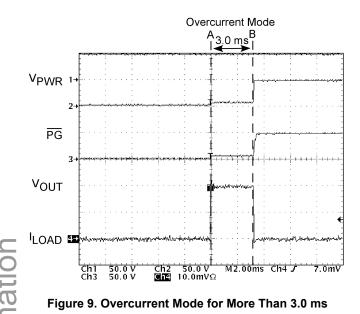

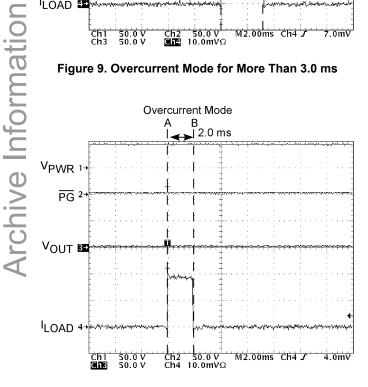

- Load current exceeded the overcurrent limit for more than 3.0 ms.

This pin is referenced to VIN.

Archive Information

8

Archive Informa

## POWER GOOD OUTPUT (ACTIVE LOW) PG

The  $\overline{PG}$  pin is the active low power good output signal that is used to enable or disable a load. This signal goes active after a successful power-up sequence and stays active as long as the device is in normal operation and is not experiencing any faults.

The signal is deactivated under the following conditions:

- Power is turned off.

- The device is disabled for more than 1.0 ms.

- The device exceeded its thermal shutdown threshold for more than 12 μs.

- The device is in overvoltage or undervoltage mode for more than 1.0 ms.

- Load current exceeded the overcurrent limit for more than 3.0 ms.

This pin is referenced to VIN.

### **OUTPUT VOLTAGE (VOUT)**

The VOUT pin is the drain of the internal Power MOSFET and supplies a current-limited voltage to the load. The load connects between the VOUT and VPWR pins.

### POSITIVE SUPPLY VOLTAGE INPUT (VPWR)

The VPWR pin is the most-positive power supply input. The load connects between the VPWR and VOUT pins.

#### **DISABLE INPUT CONTROL (DISABLE)**

The DISABLE pin is used to easily disconnect or connect the load from the main power line by disabling or enabling the 34653. It can also be used to reset the fault conditions that cause a "Power No Good" signal.

If left open or connected to VPWR, the DISABLE pin is inactive and the device is enabled. If a positive voltage (above  $V_{PWR}$ ) or a negative voltage (below  $V_{PWR}$ ) is applied to DISABLE, it is active and the device is disabled. The disable function has a 1.0 ms filter timer.

This pin is referenced to VPWR.

#### **CURRENT LIMIT CONTROL (ILIM)**

The ILIM pin is used to set the overcurrent limit during normal operation. This pin can be left unconnected for a default overcurrent limit value of 1.0 A or the user can connect an external resistor between the ILIM and VIN pins to set the overcurrent limit value. This value can vary between 0.15 A and 1.25 A. The overcurrent detection circuit has a 100  $\mu$ s filter timer.

#### CHARGING CURRENT LIMIT CONTROL (ICHG)

The ICHG pin is used to set the current limit that is used to charge the load's input capacitor, hence limiting the inrush current to a known constant value. This pin can be left unconnected for a default charging current limit value of 0.1 A and a default I<sub>CHG</sub> rise time of 1.0 ms. Or the user can connect an external resistor between the ICHG and VIN pins to set the current limit value between 0.05 A and 0.5 A and an external capacitor to increase the I<sub>CHG</sub> rise time. The recommended maximum rise time is 10 ms.

## FUNCTIONAL DEVICE OPERATION

#### **OPERATIONAL MODES**

#### START-UP SEQUENCE

When power is first applied to the 34653 by connecting the VIN pin to the negative voltage rail and the VPWR pin to the positive voltage rail, the 34653 keeps the Power MOSFET turned off, deactivates the power good output signals, and resets the retry counter. If the device is disabled, no further activities will occur and power-up would not start. If the device is enabled, it starts to establish an internally regulated supply voltage required for the internal circuitry. The Power MOSFET will stay off until the start of the charging process.

After the Power-ON Reset (POR) and once the Undervoltage Lockout (UVLO) threshold is cleared, the 34653 checks for external components on two pins-ILIM and ICHG-to set the levels of the Overcurrent Limit and the Charging Current Limit, respectively. The device then initiates the start-up timer (Point A in Figure 6) and checks for the start-up conditions (see next paragraph). The duration of the timer is a default value. For undervoltage and overvoltage faults during power up the 34652 retries infinitely until normal input voltage is attained. If the die temperature ever increased beyond the thermal shutdown threshold or the device is disabled, then the start-up timer resets and the retry counter increments. If after 10 retries the die temperature is still high and the device is still disabled, the 34652 will not retry again and the power in the device must be recycled or the device must be disabled to reset the retry counter.

Figure 6. Start-Up Sequence

#### Start-Up Conditions

The start-up conditions are as follows:

- Input voltage is below the overvoltage turn-off threshold. This threshold is a default.

- Input voltage is above the undervoltage turn-off threshold. This threshold is a default.

- Die temperature is less than the thermal shutdown temperature.

- Device is enabled.

If the start-up conditions are satisfied for a time equal to the length of the start-up timer and the retry counter is less than or equal to 10, the device starts to turn on the Power MOSFET gradually to control the inrush current that charges up the load capacitor to eventually switch on the load (Point B in Figure 6).

#### **Charging Process**

When charging a capacitor from a fixed voltage source, a definite amount of energy will be dissipated in the control circuit, no matter what the control algorithm is. This energy is equal to the energy transferred to the capacitor— $\frac{1}{2}$ CV<sup>2</sup>. With this in mind, the Power MOSFET in the 34653 cannot absorb this pulse of energy instantaneously, so the pulse must be dissipated over time. To limit the peak power dissipation in the Power MOSFET and to spread out the duration of the energy dissipation in the Power MOSFET, the circuit uses a two-level current approach to controlling the inrush current and switching on the load as explained in the following paragraphs.

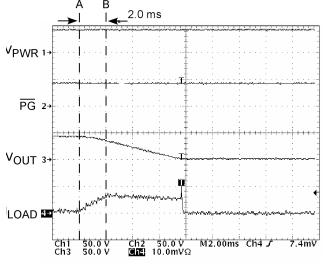

When the Power MOSFET is turned on, the current limit is set gradually from 0 A to  $I_{CHG}$  (between Points A and B in Figure 7). The low charging current value and the gradual rise time of  $I_{CHG}$  are either defaults or they can be user programmable (2.0 ms rise time in the example in Figure 7). The low charging current value of  $I_{CHG}$  is intended to limit the temperature increase during the load capacitor charging process, and the gradual rise to  $I_{CHG}$  is to prevent transient dips in the input voltage due to sharp increases in the current. This prevents the input voltage from drooping due to current steps acting on the input line inductance, and that in turn prevents a premature activation of the UV detection circuit.

U L L

Û

#### Figure 7. Power MOSFET Turn-On and the Gradual Increase in the Charging Current from 0 A to I<sub>CHG</sub> (2.0 ms in Example)

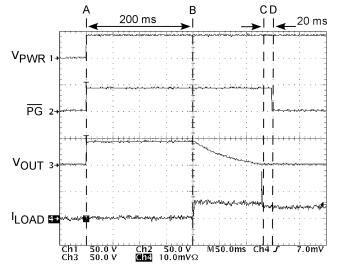

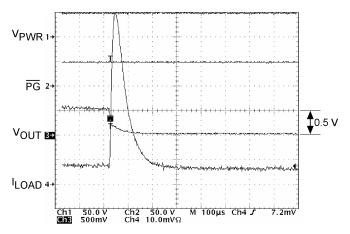

The I<sub>CHG</sub> current charges up the load capacitor relatively slowly. When the load capacitor is fully charged, the Power MOSFET reaches its full enhancement, which triggers the current limit detection to change from I<sub>CHG</sub> to I<sub>LIM</sub> and the load current to decrease (Point C in Figure 6, page 10). The current spike at Point C in Figure 6 is better displayed in Figure 8. We can see that when the  $|V_{OUT} - V_{IN}| < 0.5 V$ , the Power MOSFET fully turns on to reach its full enhancement, charging the capacitor an additional 0.5 V with a higher current value that quickly ramps down. This eliminates the need for a current slew rate control because the hazard for a voltage change is less than 0.5 V. The power good output signals activate after a 20 ms delay (Point D in Figure 6), which in turn enables the load. The 34653 is now in normal operation mode and the retry counter resets.

#### NORMAL MODE

If one of the start-up conditions (list on page 10) is violated any time from the start of the Power MOSFET enhancement process and thereafter during normal operation, the Power MOSFET turns off and the power good output signals deactivate, disabling the load, and a new timer cycle starts as explained previously. The 34653 also monitors the load current to prevent any overload or short circuit conditions from happening to protect the load from damage.

#### LOAD CURRENT CONTROL

When in normal operation mode, the 34653 monitors the load and provides two modes of current control as explained in the paragraphs below.

#### **Overcurrent Mode**

The 34653 monitors the load for overcurrent conditions. If the current going through the load becomes larger than the overcurrent limit for longer than the overcurrent limit filter timer of 100 µs, the overcurrent signal is asserted and the gate of the Power MOSFET is discharged to try to regulate the current at the I<sub>LIM</sub> value (Point A in Figure 9). The 34653 is in overcurrent mode for 3.0 ms. If after a 3.0 ms filter timer the device is still in overcurrent mode, the device turns off the Power MOSFET and deactivates the power good output signals (Point B in Figure 9). The 34653 then initiates another start-up timer and goes back through the enhancement process. If during the 3.0 ms timer the fault was cleared, then the 34653 goes back to the normal operation mode and the power good output signals stay activated as shown in Figure 10. This way the device overcomes temporary overcurrent situations and at the same time protects the load from a more severe overcurrent situation.

#### **Short Circuit Mode**

If the current going through the load becomes >5.0 A, the Power MOSFET is discharged very fast (in less than 10  $\mu$ s) to try to regulate the current at the I<sub>LIM</sub> value, and the 34653 is in the overcurrent mode for 3.0 ms. Then it follows the pattern outlined in the Overcurrent Mode paragraph above.

0

Archive

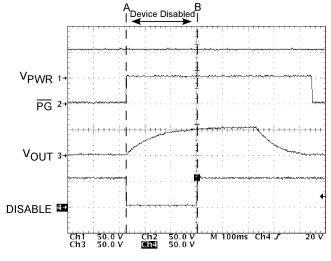

#### **DISABLING AND ENABLING THE 34653**

When a negative voltage (< 1.8 V below V<sub>PWR</sub>) is applied to the DISABLE pin for more than 1.0 ms (Point A in Figure 11), the 34653 is disabled, the Power MOSFET turns off, and the power good output signals deactivate. The 34653 stays in this state until the voltage on the DISABLE pin is brought to within ±1.2 V of V<sub>PWR</sub> for more than 1.0 ms to enable the device (Point B in Figure 11). Then a new start-up sequence initiates as described on page 10. Applying a positive voltage (> 1.8 V above V<sub>PWR</sub>) would also disable the 34653 in the same manner.

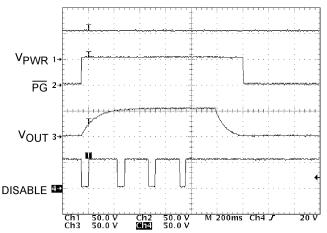

Figure 12 demonstrates that the 34653 must be enabled for the length of the start-up timer to start turning on the Power MOSFET. After the fourth disable signal, the 34653 was enabled for the length of the start-up timer. And because the retry counter is less than 10, the 34653 turns on the Power MOSFET and starts the charging process (refer to <u>Charging Process</u>, pages 10–11).

#### **BOARD REMOVAL**

When the board is removed, its power ramps down. As soon as the 34653's input voltage reaches the undervoltage turn-off threshold, the undervoltage detection circuit activates and the Power MOSFET turns off for having violated one of the start-up conditions (list on page 10).

FUNCTIONAL DEVICE OPERATION OPERATIONAL MODES

#### STATE MACHINE

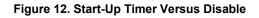

Figure 13 is a representation of the 34653 behavior in different modes of operation.

Figure 13. State Diagram

Archive Information

CTIONAL DEVICE OPERATION

### **PROTECTION AND DIAGNOSIS FEATURES**

#### UNDERVOLTAGE

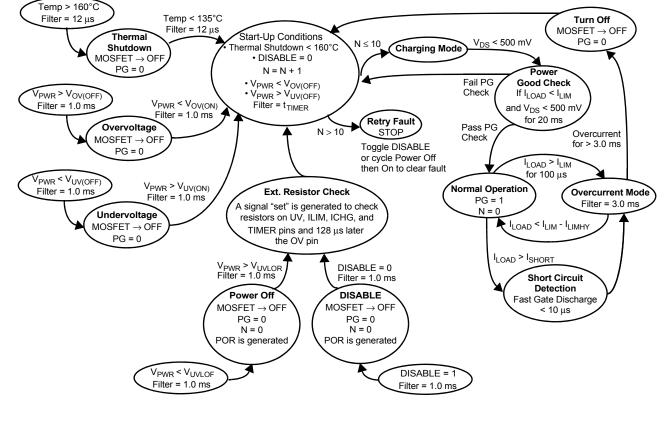

When the input voltage drops below the undervoltage falling threshold for more than 1.0 ms, an undervoltage fault is detected and one of the start-up conditions (list on page 10) is violated. The 34653 turns off the Power MOSFET and deactivates the power good output signals, disabling the load (Point A in Figure 14). The 34653 stays in this state until the input voltage rises above the undervoltage rising threshold for more than 1.0 ms, signaling that the supply voltage is in the normal operation range (Point B in Figure 14). The na new start-up sequence initiates as described on page 10. The undervoltage detection circuit is also equipped with a 1.0 V hysteresis.

#### Figure 14. Undervoltage Fault Followed by a New Start-Up Sequence

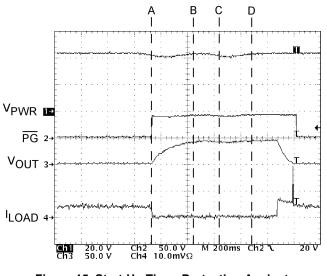

Figure 15 shows how the 34653 uses the start-up timer to make sure that the input voltage is above the undervoltage falling threshold. The 34653 was in normal operation before Point A. At Point A an undervoltage fault occurs. Then the fault is cleared at Point B, and the 34653 initiates a start-up sequence. Before the end of the start-up timer another undervoltage fault occurs at Point C, so the 34653 does not turn on the Power MOSFET. At Point D the fault is cleared again for the length of the start-up timer and the 34653 turns on the Power MOSFET and starts the charging process (refer to <u>Charging Process</u>, pages 10–11).

#### OVERVOLTAGE

When the input voltage exceeds the overvoltage rising threshold for more than 1.0 ms, an overvoltage fault is detected and one of the start-up conditions (list on page 10) is violated. The 34653 turns off the Power MOSFET and deactivates the power good output signals, disabling the load. The 34653 stays in this state until the input voltage falls below the overvoltage falling threshold for more than 1.0 ms, signaling that the supply voltage is in the normal operation range. Then a new start-up sequence initiates as described on page 10. The overvoltage detection circuit is also equipped with a 2.0 V hysteresis.

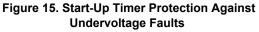

The waveforms for an overvoltage fault are shown in Figure 16.

Figure 16. Overvoltage Fault

nive Informati

#### THERMAL SHUTDOWN

The thermal shutdown feature helps protect the internal Power MOSFET and circuitry from excessive temperatures. During start-up and thereafter during normal operation, the 34653 monitors the temperature of the internal circuitry for excessive heat. If the temperature of the device exceeds the thermal shutdown temperature of 160°C, one of the start-up conditions (list on page 10) is violated, and the device turns off the Power MOSFET and deactivates the power good output signals. Until the temperature of the device goes below 135°C, a new start-up sequence will not be initiated. This feature is an advantage over solutions with an external Power MOSFET to sense the temperature quickly and accurately. The thermal shutdown circuit is equipped with a 12  $\mu$ s filter.

Thermal design is critical to proper operation of the 34653. The typical R<sub>DS(ON)</sub> of the internal Power MOSFET is 0.144  $\Omega$  at room ambient temperature and can reach up to 0.251  $\Omega$  at high temperatures. The thermal performance of the 34653 can vary depending on many factors, among them:

- The ambient operating temperature (T<sub>A</sub>).

- The type of PC board—whether it is single layer or multilayer, has heat sinks or not, etc.—all of which affects the value of the junction-to-ambient thermal resistance (R<sub>P,IA</sub>).

- The value of the desired load current (I<sub>LOAD</sub>).

When choosing an overcurrent limit, certain guidelines need to be followed to make sure that if the load current is running close to the overcurrent limit the 34653 does not go into thermal shutdown. It is good practice to set the parameters so that the resulting maximum junction temperature is below the thermal shutdown temperature by a safe margin.

Equation 1 can be used to calculate the maximum allowable overcurrent limit based on the maximum desired junction temperature or vice versa.

The power dissipation in the device can be calculated as follows:

$\mathsf{P} = \mathsf{I}^2_{(\mathsf{LOAD})} * \mathsf{R}_{\mathsf{DS}(\mathsf{ON})}$

#### OR

$$P = [T_J(max) - T_A(max)] / R_{\theta JA}$$

Combining the two equations:

$I_{(LOAD)}^2 = [T_J(max) - T_A(max)] / [R_{\theta JA} * R_{DS(ON)}]$  Eq 1 For example:

$T_A(max) = 55^{\circ}C$

$R_{\theta JA}$  = 111 °C/W for a four-layer board  $R_{DS(ON)}$  = 0.251  $\Omega$  at high temperatures

Then:

$$\begin{split} I^2{}_{(\text{LOAD})} &= [\text{T}_{\text{J}}(\text{max}) - 55 \text{ }^\circ\text{C}] / [111 \text{ }^\circ\text{C/W} * 0.251 \Omega] \\ I^2{}_{(\text{LOAD})} &= [\text{T}_{\text{J}}(\text{max}) - 55 \text{ }^\circ\text{C}] / 27.86 \text{ }^\circ\text{C}/\text{A}^2 \end{split}$$

So if the overcurrent limit is 1.0 A, then the maximum junction temperature is 82.86 °C, which is well below the thermal shutdown temperature that is allowed.

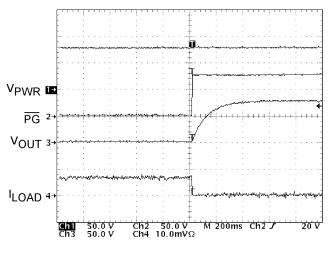

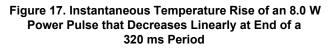

The previous explanation applies to steady state power when the device is in normal operation. During the charging process, the power is dominated by the I \* V across the Power MOSFET. When charging starts, the power in the Power MOSFET rises up and reaches a maximum value of I \* V, then quickly ramps back down to the steady state level in a period governed by the size of the load's input capacitor that is being charged and by the value of the charging current limit I<sub>CHG</sub>. In this case the instantaneous power dissipation is much higher than the steady state case, but it is on for a very short time.

For example:

I<sub>CHG</sub> = 100 mA, the default value

C<sub>LOAD</sub> = 400 µF, a very large capacitor

$V_{PWR}$  = 80 V, worst case

Then:

The power pulse magnitude =  $I_{CHG} * V_{PWR}$  = 8.0 W

The power pulse duration =  $C_{LOAD} * V_{PWR} / I_{CHG}$  = 320 ms

<u>Figure 17</u> displays the temperature profile of the device under the instantaneous power pulse during the charging process. <u>Table 5</u> depicts thermal resistance values for different board configurations.

## Table 5. Thermal Resistance Data

| Туре                       | Condition                                                                                                                                                     | Symbol                | Value | Unit |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------|------|

| Junction to Ambient        | o Ambient Single-layer board (1s), per JEDEC jesd51-2 with board (JESD51-3) horizontal                                                                        |                       |       |      |

| Junction to Ambient        | Four-layer board (2s2p), per JEDEC JESD51-2 with board (JESD51-3) horizontal                                                                                  | $R_{\thetaJMA}$       | 115   | °C/W |

| Junction to Ambient        | Single-layer board with a 300 mm <sup>2</sup> radiator pad on its top surface, not standard JEDEC                                                             | -                     | 145   | °C/W |

| Junction to Ambient        | Single-layer board with a 600 mm <sup>2</sup> radiator pad on its top surface, not standard JEDEC                                                             | -                     | 143   | °C/W |

| Junction to Ambient        | Four-layer board with a via for each thermal lead, not standard JEDEC                                                                                         | -                     | 111   | °C/W |

| Junction to Ambient        | Four-layer board with a 300 mm <sup>2</sup> radiator pad on its top surface and a full array of vias between radiator pad and top surface, not standard JEDEC | -                     | 107   | °C/W |

| Junction to Ambient        | Four-layer board with a 600 mm <sup>2</sup> radiator pad on its top surface and a full array of vias between radiator pad and top surface, not standard JEDEC | -                     | 107   | °C/W |

| Junction to Board          | Thermal resistance between die and board per JEDEC JESD51-8                                                                                                   | $R_{	extsf{	heta}JB}$ | 62    | °C/W |

| Junction to Case           | Thermal resistance between die and case top                                                                                                                   | $R_{	extsf{	heta}JC}$ | 57    | °C/W |

| Junction to Package<br>Top | Temperature difference between package top and junction per JEDEC JESD51-2                                                                                    | $\Psi_{\text{JT}}$    | 18    | °C/W |

Archive Informa

TYPICAL APPLICATIONS

## **TYPICAL APPLICATIONS**

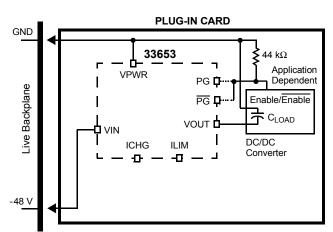

The 34653 resides on the plug-in board (see Figures 18 and 19), allowing the board to be safely inserted or removed without damaging electrical equipment. The 34653 can be operated with no external components other than the power good output signal pull-up resistor if the default mode was selected for all the programmable features. This is one of the great advantages of the 34653: it operates with minimal user interface and minimal external component count and still offers complete hot swapping functionality with all the necessary protection features, from undervoltage/ overvoltage detection, to current limiting, to short circuit protection and power good output signaling. The default values were chosen to be sufficient for many standard applications.

Figure 18 is a typical application diagram depicting the default mode and using the power good output signal pullup resistor. Refer to the static and dynamic electrical characteristics tables on pages 5 through  $\frac{7}{2}$  for the various default values.

#### Figure 18. Typical Application Diagram with Default Settings and Minimal External Components

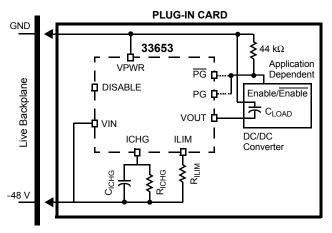

The 34653 can be also programmed for different values of the Overcurrent Limit and the Charging Current Limit using external components connected to the device. Figure 19 shows the 34653 with the required external components that allow access to all programmable features in the device.

Figure 19. Typical Application Diagram with External Components Necessary to Program the Device

# UNDERVOLTAGE AND OVERVOLTAGE DETECTION

The 34653 monitors the input voltage to ensure that it is within the operating range and that there are no overvoltage or undervoltage conditions, and to quickly turn off the Power MOSFET if there are. Internal comparators connected to an internal resistor divider between the VPWR and VIN input pins compare the supply voltages with a reference voltage. The typical default values of 37 V for the UV turn-off threshold (falling threshold) and 78 V for the OV turn-off threshold (rising threshold) will give a typical operating range of 38 V to 76 V. This range is suitable for telecom industry standards.

When the device passes the UVLO threshold, it uses the UV/OV detection circuits to check the input supply levels before turning on the Power MOSFET during the start-up Timer delay and thereafter. As long as the voltage is above the undervoltage falling threshold and below the overvoltage rising threshold, the supply is within operating range and the Power MOSFET is allowed to turn on and stay on. If the input voltage falls below its undervoltage falling threshold or rises above its overvoltage rising threshold, then one of the start-up conditions (list on page 10) is violated and the Power MOSFET turns off, the power good signal deactivates, and a new start-up timer initiates. The undervoltage and overvoltage detection circuits are equipped with a 1.0 ms filter to filter out momentary input supply dips.

#### TIMER

The Timer function on the 34653 provides the time base used to generate the timing sequences at start-up. The same timer controls the retry delay when the device experiences any fault. The Timer function has a default timer value of

34653

CAL APPLICATIONS

200 ms. During start-up and if any fault occurred, this timer value is used when initiating a start-up sequence.

### POWER GOOD OUTPUT SIGNALS

The power good pins PG and  $\overline{\text{PG}}$  are output pins that are used to directly enable a power module load. The device has active high and active low power good output signals. Choosing which power good active signal depends on the Enable signal requirement of the load. This feature allows the 34653 to adapt to different applications and a wide variety of loads.

The power good output signal is active if the Power MOSFET is fully enhanced and the device is in normal operation. The signal goes active after a typical 20 ms delay. The signal deactivates if one of the following occurs:

• Power is turned off.

hive Informatior

- The device is disabled for more than 1.0 ms.

- The device exceeded its thermal shutdown threshold for more than 12  $\mu s.$

- The device is in overvoltage or undervoltage mode for more than 1.0 ms.

- Load current exceeded the overcurrent limit for more than 3.0 ms.

When the power good output signal becomes inactive, it disables the load, protecting it from any faults or damage. These loads are usually DC/DC converters, depicted in Figure 19, page <u>17</u>. An LED can also be connected to PG to indicate that the power is good.

The PG and  $\overline{PG}$  pins are referenced to VIN and require a pullup resistor connected to VPWR (Figures 18 and 19, page 17).

#### **DISABLING AND ENABLING THE 34653**

The Disable control input (DISABLE) provides two functions:

- External enable/disable control.

- Manual resetting of the device and the retry counter after a fault has occurred.

Using the DISABLE pin, a user can enable/disable the 34653 device, which facilitates easy access to connect the load to or disconnect it from the main power rail.

When power is first applied, the DISABLE pin must be inactive in order for the 34653 to initiate a start-up sequence. If the DISABLE pin is active, the device makes no further steps until the pin is inactive. At any point during the start-up and thereafter during normal operation, if the DISABLE pin is activated, then the retry counter resets, the Power MOSFET turns off and the power good output signals deactivate. The DISABLE circuit is equipped with a 1.0 ms filter to filter out any glitches or transients on the DISABLE input and prevent the Power MOSFET from turning off prematurely. The DISABLE pin is referenced to VPWR. If left open or connected to VPWR, meaning the voltage at the DISABLE pin is between V<sub>PWR</sub> + 1.2 V and V<sub>PWR</sub> - 1.2 V, it is inactive and the device is enabled. If a positive voltage (1.8 V above V<sub>PWR</sub>) or a negative voltage (1.8 V below V<sub>PWR</sub>) is applied to DISABLE, it is active and the device is disabled.

#### **CHARGING CURRENT LIMIT**

When the device passes the UVLO threshold, it checks if there is any external resistor or external capacitor connected to the ICHG pin. If there is, then it determines the value of the charging current limit value and the charging current limit rise time accordingly. If there is not, it uses the default charging current limit value of 100 mA and rise time of 1.0 ms.

**Note** Users are allowed to connect an external capacitor to ICHG pin only if an external resistor is also connected. During the external components' check, a capacitor produces an impulse of current and an external resistor will be detected, even it the external resistor is absent.

When the Power MOSFET is turned on, the current limit is set gradually from 0 A to I<sub>CHG</sub>. This current charges up the load capacitor relatively slowly. When the load capacitor is fully charged, the Power MOSFET reaches its full enhancement, which triggers the current limit to change from I<sub>CHG</sub> to I<sub>LIM</sub> and the load current to decrease. The power good output signals activate after a 20 ms delay, which in turn enables the load. The 34653 is now in normal operation mode and the retry counter resets.

The low charging current value of  $I_{CHG}$  is intended to limit the temperature increase during the load capacitor charging process, and the gradual rise to  $I_{CHG}$  is to prevent transient dips in the input voltage due to sharp increases in the limit current. This prevents the input voltage from drooping due to current steps acting on the input line inductance, and that in turn prevents a premature activation of the UV detection circuit.

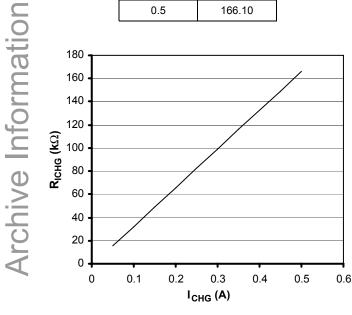

#### Choosing the External Resistor RICHG Value

The user can change the value of the charging current limit by adding a resistor (R<sub>ICHG</sub>) between the ICHG and VIN pins, as shown in Figure 19, page 17. The charging current value ranges between 50 mA and 500 mA, with a default value of 100 mA. Table 6 lists examples of R<sub>ICHG</sub> for different values of I<sub>CHG</sub> and Figure 20 shows a plot of R<sub>ICHG</sub> versus I<sub>CHG</sub>. It is recommended that the closest 1% standard resistor value to the actual value be chosen.

Note Accuracy requirements are application dependent.

To calculate the value of the  $R_{ICHG}$  resistor we use the following equations:

$$\begin{split} &\mathsf{I}_{\mathsf{CHG}}(\mathsf{A}) = [\mathsf{R}_{\mathsf{ICHG}}(\mathsf{k}\Omega) + 1.4 \; \mathsf{k}\Omega] \; / \; 335 \\ &\mathsf{R}_{\mathsf{ICHG}}(\mathsf{k}\Omega) = 335 \, * \; \mathsf{I}_{\mathsf{CHG}}(\mathsf{A}) - 1.4 \; \mathsf{k}\Omega \end{split}$$

TYPICAL APPLICATIONS

#### Table 6. $\rm R_{ICHG}$ Values for Some Desired $\rm I_{CHG}$ Values

| I <sub>CHG</sub> (A) | R <sub>ICHG</sub> (kΩ) |

|----------------------|------------------------|

| 0.05                 | 15.35                  |

| 0.1                  | 32.10                  |

| 0.15                 | 48.85                  |

| 0.2                  | 65.60                  |

| 0.25                 | 82.35                  |

| 0.3                  | 99.10                  |

| 0.35                 | 115.85                 |

| 0.4                  | 135.60                 |

| 0.45                 | 149.35                 |

| 0.5                  | 166.10                 |

Figure 20. External Resistor (R<sub>ICHG</sub>) Value Versus Charging Current Limit Value (I<sub>CHG</sub>)

#### Choosing the External Capacitor CICHG Value

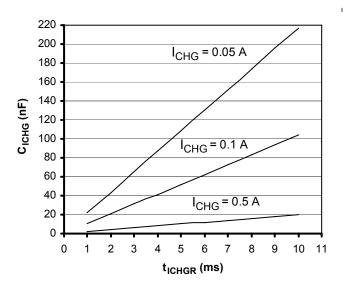

The user can also change the charging current rise time by adding a capacitor (C<sub>ICHG</sub>) between the ICHG and VIN pins, as shown in Figure 19, page 17. The charging current rise time ranges between 1.0 ms (default value) and a recommended maximum of 10 ms. Table 7 lists examples of C<sub>ICHG</sub> for different values of t<sub>ICHGR</sub> and Figure 21 shows a plot of C<sub>ICHG</sub> versus t<sub>ICHGR</sub>.

To calculate the value of the  $C_{\rm ICHG}$  capacitor we use the following equation:

$C_{ICHG}(nF) = 1000 * t_{ICHGR}(ms) / [3 * R_{ICHG}(k\Omega)]$

# Table 7. C $_{\rm ICHG}$ Values for Some Desired $t_{\rm ICHGR}$ Values at a Specific I $_{\rm CHG}$ Value

| t <sub>ICHGR</sub> (ms) | C <sub>ICHG</sub> (nF)<br>I <sub>CHG</sub> = 0.05 A | C <sub>ICHG</sub> (nF)<br>I <sub>CHG</sub> = 0.1 A | C <sub>ICHG</sub> (nF)<br>I <sub>CHG</sub> = 0.5 A |

|-------------------------|-----------------------------------------------------|----------------------------------------------------|----------------------------------------------------|

| 1.0                     | 21.72                                               | 10.38                                              | 2.01                                               |

| 2.0                     | 43.43                                               | 20.77                                              | 4.01                                               |

| 3.0                     | 65.15                                               | 31.15                                              | 6.02                                               |

| 4.0                     | 86.86                                               | 41.54                                              | 8.03                                               |

| 5.0                     | 108.58                                              | 51.92                                              | 10.03                                              |

| 6.0                     | 130.29                                              | 62.31                                              | 12.04                                              |

| 7.0                     | 152.01                                              | 72.69                                              | 14.05                                              |

| 8.0                     | 173.72                                              | 83.07                                              | 16.05                                              |

| 9.0                     | 195.44                                              | 93.46                                              | 18.06                                              |

| 10                      | 217.16                                              | 103.84                                             | 20.07                                              |

Figure 21. Charging Current External Capacitor (C<sub>ICHG</sub>) Versus Charging Current Rise Time t<sub>ICHGR</sub>

34653

ormati

rchive Inf

CAL APPLICATIONS

#### **OVERCURRENT LIMIT**

When in normal operation mode, the 34653 monitors the load and compares (with a hysteresis) the current going through a Sensor MOSFET with a reference current value generated in reference to the current limit value ILIM. If the current going through the Sensor MOSFET becomes larger than the reference current for more than 100  $\mu$ s, the overcurrent signal is asserted, the gate of the Power MOSFET is discharged fast (in less than 10 µs) to try to regulate the current, and the 34653 is in overcurrent mode for 3.0 ms. If after a 3.0 ms filter time the device is still in overcurrent mode, the device turns off the Power MOSFET and deactivates the power good output signals. The 34653 then initiates another start-up timer and goes back through the enhancement process. If during the 3.0 ms timer the fault was cleared where the load current was less than I<sub>LIM</sub> minus the hysteresis value, which is 12% of  $\mathrm{I}_{\mathrm{LIM}}$  value, then the 34653 goes back to the normal operation mode and the power good output signals stay activated. This way the device overcomes temporary overcurrent situations and at the same time protects the load from more severe overcurrent situations.

When the device passes the UVLO threshold, it checks if there is any external resistor connected to the ILIM pin. If there is, it determines the value of the overcurrent limit. If there is not, it uses the default overcurrent limit value of 1.0 A. It then uses the Sensor MOSFET to monitor the load for any overcurrent conditions during operation as explained in the previous paragraph.

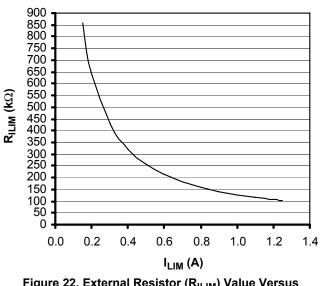

#### Choosing the External Resistor RILIM Value

The user can change the current limit by adding a resistor (R<sub>ILIM</sub>) between the ILIM and VIN pins, as shown in Figure 19, page 17. This way the 34653 device is adaptable to different requirements and operating environments. The overcurrent value ranges between 0.15 A and 1.25 A, with a default value of 1.0 A. Table 8 lists examples of R<sub>ILIM</sub> for different values of I<sub>LIM</sub> and Figure 22 shows a plot of R<sub>ILIM</sub> versus I<sub>LIM</sub>. It is recommended that the closest 1% standard resistor value to the actual value be chosen.

Note Accuracy requirements are application dependent.

To calculate the value of the  $\mathsf{R}_{\mathsf{ILIM}}$  resistor we use the following equations:

$$\begin{split} I_{\text{LIM}}(\text{A}) &= 129 \ / \ [\text{R}_{\text{ILIM}}(\text{k}\Omega) + 1.4 \ \text{k}\Omega] \\ \text{R}_{\text{ILIM}}(\text{k}\Omega) &= [129 \ / \ \text{I}_{\text{LIM}}(\text{A})] - 1.4 \ \text{k}\Omega \end{split}$$

#### Table 8. RILIM Values for Some Desired ILIM Values

| I <sub>LIM</sub> (A) | R <sub>ILIM</sub> (kΩ) |

|----------------------|------------------------|

| 0.15                 | 859.71                 |

| 0.2                  | 644.43                 |

| 0.3                  | 429.15                 |

| 0.4                  | 321.52                 |

| 0.5                  | 256.93                 |

| 0.6                  | 213.88                 |

| 0.7                  | 183.12                 |

| 0.8                  | 160.06                 |

| 0.9                  | 142.12                 |

| 1.0                  | 127.77                 |

| 1.1                  | 116.02                 |

| 1.2                  | 106.24                 |

| 1.25                 | 101.93                 |

#### SHORT CIRCUIT DETECTION

If the current going through the load becomes >5.0 A, the Power MOSFET is discharged very fast (in less than 10  $\mu$ s) to try to regulate the current, and the 34653 is in the overcurrent mode for 3.0 ms. Then it follows the pattern outlined in the <u>Overcurrent Limit</u> paragraph above.

Archive Information

#### POWER MOSFET ENERGY CAPABILITY

Figure 23 shows a projected energy capability of the device's internal Power MOSFET under a drain-to-source voltage of 82 V and an ambient temperature of 90°C. It is compared to the energy levels required for the capacitive loads of 100  $\mu$ F, 200  $\mu$ F, and 400  $\mu$ F at 80 V for the discharge periods of 16 ms, 32 ms, and 64 ms, respectively. It is clear that the Power MOSFET well exceeds the required energy capability for all three cases with a sufficient margin. For example, the 400  $\mu$ F capacitor load with a 64 ms discharge time requires an energy capability of about 1540 mJ, which is well below the Power MOSFET capability of about 3500 mJ. As a result to this analysis the 33652 is expected to exceedingly meet all the energy capability requirements for the possible capacitive loads.

Figure 23. Projected Energy Capability of the Power MOSFET Compared to the Required Energy Levels of Some Capacitive Loads

Archive Information

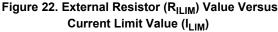

#### **PACKAGE DIMENSIONS**

**Important** For the most current revision of the package, visit www.freescale.com and perform a keyword search on the "98A" drawing number below.

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. |      |      | MECHANICA | L OUTLINE | PRINT VERSION NO | DT TO SCALE    |             |

|---------------------------------------------------------|------|------|-----------|-----------|------------------|----------------|-------------|

| TIT                                                     | TLE: |      |           |           | DOCUMENT NO      | ): 98ASB42564B | REV: U      |

|                                                         | 8LD  | SOIC | NARROW    | BODY      | CASE NUMBER      | 2: 751–07      | 07 APR 2005 |

|                                                         |      |      |           |           | STANDARD: JE     | DEC MS-012AA   |             |

EF SUFFIX (Pb-Free) 8-PIN SOIC NARROW BODY PLASTIC PACKAGE 98ASB42564B ISSUE U

**REVISION HISTORY**

## **REVISION HISTORY**

| REVISION | DATE   | DESCRIPTION OF CHANGES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.0      | 2/2006 | Changed Document Order No.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 7.0      | 8/2006 | <ul> <li>Corrected PIN CONNECTIONS on page 3</li> <li>Updated document to the prevailing Freescale form and style</li> <li>Updated PACKAGE DIMENSIONS on page 22</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 8.0      | 2/2007 | <ul> <li>Added Part Number MCZ34653EF/R2 to Ordering Information</li> <li>Added RoHS logo</li> <li>Removed Peak Package Reflow Temperature During Reflow (solder reflow) parameter from MAXIMUM RATINGS on page 4.</li> <li>Added note Freescale's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL), Go to www.freescale.com, search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts. (i.e. MC33xxxD enter 33xxx), and review parametrics. on page 4.</li> </ul> |

Archive Information

#### How to Reach Us:

Home Page: www.freescale.com

E-mail:

support@freescale.com

#### **USA/Europe or Locations Not Listed:** Freescale Semiconductor

Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

## Europe, Middle East, and Africa: Freescale Halbleiter Deutschland GmbH

**Technical Information Center** Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc., 2007. All rights reserved.