### **Freescale Semiconductor**

Order Number: MC92315AI/D Rev. 1.1, 17 Feb 2000

### Advance Information MC92315 2K/8K Integrated DVB-T Demodulator

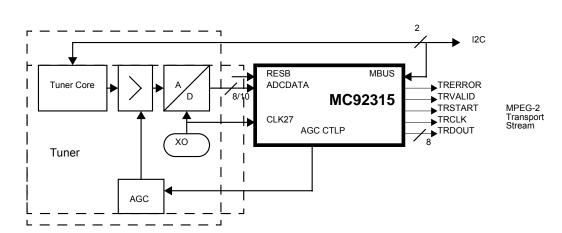

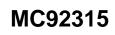

The MC92315 is a DVB-T compliant demodulator for 2K/8K transmission mode according to the ETSI specification for digital terrestrial broadcasting (ETS 300744). The MC92315 contains all the functionality required to demodulate and decode DVB-T compliant broadcast signals.

#### **Feature Summary**

- Automatic detection of 2K/8K mode

- Usable for 8MHz/7MHz/6MHz channels

- Digital I/Q separation on-chip

- Digital AFC on chip

- No VCXO required, free running XO at 27MHz sufficient

- Supports QPSK, 16-QAM and 64-QAM (non-hierarchical and hierarchical)

- Supports all guard interval lengths (1/32, 1/16, 1/8, 1/4)

- Automatic locking to any DVB-T guard interval

- 10-bit CMOS input for 2's-complement or offset-binary ADC data

- Provides control signals for AGC clock frequency control

- Viterbi Decoder for DVB convolutional code rates 1/2, 2/3, 3/4, 5/6 and 7/8

- Reed/Solomon Decoder for DVB Reed-Solomon code (204,188,8)

- I<sup>2</sup>C serial bus compatible interface (M-Bus) for external programming and control

- Operating voltage 1.8V for the core and 3.3V for the I/O

- Power requirement 0.8W

- Package 160PQFP and 100TQFP

- Pin-compatible to MC92314 2K DVB-T demodulator

© Freescale Semiconductor, Inc., 2004. All rights reserved.

| Ordering Information |         |  |  |  |  |  |  |

|----------------------|---------|--|--|--|--|--|--|

| Device               | Package |  |  |  |  |  |  |

| MC92315DH            | 160PQFP |  |  |  |  |  |  |

| MC92315NY            | 100TQFP |  |  |  |  |  |  |

ights reserved.

#### MC92315 Pinout (160PQFP)

The pinout for this package is given in the figure below:

MC92315 Advance Information

| SIGNAL         | PIN-NR.                                     | FUNCTIONALITY                                                 | TYPE              | ACTIVE |  |

|----------------|---------------------------------------------|---------------------------------------------------------------|-------------------|--------|--|

| RESB           | 135                                         | Reset (asynchronous)                                          | TTL - IN          | low    |  |

| CLK27          | 33                                          | 27 MHz Clock input                                            | TTL - IN          | high   |  |

| ADCDATA[7:0]   | 21, 16, 11,<br>6, 1, 160,<br>155, 150       | ADC input for 8-Bit ADCs                                      | TTL - IN          | high   |  |

| ADCDATA[-1:-2] | 147, 145                                    | 10-Bit extension for 10-Bit ADCs                              | reserved<br>(VSS) | N/A    |  |

| AGCCTLP        | 36                                          | Analogue AGC control (+)                                      | TTL - OUT         | high   |  |

| SDA            | 56                                          | I <sup>2</sup> C compatible control bus, data pin             | TTL - OD          | N/A    |  |

| SCL            | 51                                          | I <sup>2</sup> C compatible control bus, clock pin            | TTL - IN          | high   |  |

| MBUSID[3:0]]   | 80, 76, 71,<br>66                           | I <sup>2</sup> C compatible control bus, variable ID selector | TTL - IN          | high   |  |

| VO             | 92                                          | Output of Viterbi Decoder                                     | TTL - OUT         | high   |  |

| VCLK           | 89                                          | Clock for Viterbi Output                                      | TTL - OUT         | high   |  |

| GP[3:0]        | 104, 102,<br>99, 97                         | General Purpose output pins, accessible via I <sup>2</sup> C  | TTL - OUT         | high   |  |

| TRERROR        | 130                                         | MPEG-2 Frame Error Indicator                                  | TTL - OUT         | high   |  |

| TRVALID        | 121                                         | MPEG-2 Byte Valid Indicator                                   | TTL - OUT         | high   |  |

| TRSTART        | 125                                         | MPEG-2 Sync Byte Indicator                                    | TTL - OUT         | high   |  |

| TRCLK          | 120                                         | MPEG-2 Byte Clock                                             | TTL - OUT         | high   |  |

| TRDOUT[7:0]    | 115, 110,<br>105, 100,<br>95, 90, 85,<br>81 | MPEG-2 Transport Stream Byte Output                           | TTL - OUT         | high   |  |

| INSYNC         | 143                                         | FEC Frame Synchronization Status                              | TTL - OUT         | high   |  |

| VLOCK          | 142                                         | Viterbi Decoder Synchronization Status                        | TTL - OUT         | high   |  |

| TPSLOCKB       | 141                                         | TPS demodulator in lock (active L)                            | TTL - OUT         | low    |  |

| TPSVALID       | 140                                         | TPS data detected                                             | TTL - OUT         | high   |  |

| AFCLCK         | 139                                         | AFC status indicator                                          | TTL - OUT         | high   |  |

| CLKLCK         | 138                                         | Time Synchronization state indicator TTL - OUT                |                   |        |  |

| VDD33          | 5, 86, 101,<br>116, 134                     | 3.3 V Supply Voltage for I/O                                  |                   | N/A    |  |

#### Table 1: MC92315 Pin List (160PQFP)

| SIGNAL | PIN-NR.                                                                                                                                                      | FUNCTIONALITY                       | ТҮРЕ | ACTIVE |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|------|--------|

| VDD18  | 10, 15, 20,<br>25, 35, 43,<br>48, 53, 58,<br>63, 68, 73,<br>78, 91, 96,<br>106, 111,<br>123, 129,<br>144, 148,<br>152, 157                                   | 1.8 V Supply Voltage for core       |      | N/A    |

| VSS    | 3, 8, 13,<br>18, 23, 28,<br>38, 45, 50,<br>55, 60, 65,<br>70, 75, 83,<br>88, 93, 98,<br>103, 108,<br>113, 118,<br>127, 132,<br>137, 146,<br>149, 154,<br>159 | Ground pins                         |      | N/A    |

| AVDD18 | 30                                                                                                                                                           | 1.8 V analogue VDD (Integrated PLL) |      |        |

| AVSS   | 32                                                                                                                                                           | Analogue VSS (Integrated PLL)       |      |        |

- VDD18 denotes the V<sub>DD</sub> pins for the core in 1.8 V technology.

- VDD33 denotes the V<sub>DD</sub> pins for the I/O in 3.3 V technology.

- AVDD18 denotes the supply voltage for the integrated PLL. It must be LC-filtered according to the 2K/8K Compatibility Schematic distributed in August 1998.

- AVSS denotes the ground pin of the integrated PLL. It must be connected with a low-impedance connection to the system ground plane.

- VDD18 denotes the V<sub>DD</sub> pins for the core in 1.8 V technology.

- VDD33 denotes the V<sub>DD</sub> pins for the I/O in 3.3 V technology.

- AVSS denotes the ground pin of the integrated PLL. It must be connected with a low-impedance connection to the system ground plane.

- NOTE: Signal functions (e.g. MBUSID[3:0]) in the MC92315 Pin List are grouped in sequential order from the highest bit to the lowest bit.

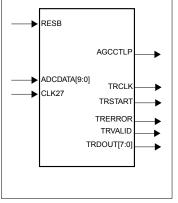

#### MC92315 Pinout (100TQFP)

The pinout for the smaller package is given in the figure below:

#### -

#### Table 2: MC92315 Pin List (100TQFP) List

| SIGNAL | PIN-NR. | FUNCTIONALITY        | FUNCTIONALITY TYPE |      |  |  |  |

|--------|---------|----------------------|--------------------|------|--|--|--|

| RESB   | 86      | Reset (asynchronous) | IN                 | low  |  |  |  |

| CLK27  | 23      | 27 MHz Clock input   | IN                 | high |  |  |  |

| SIGNAL                                                                                                                          | PIN-NR.                                                                                          | FUNCTIONALITY                                                 | TYPE              | ACTIVE |

|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-------------------|--------|

| ADCDATA[7:0]                                                                                                                    | 15, 12, 9,<br>6, 3, 2, 99,<br>96                                                                 | ADC input for 8-Bit ADCs                                      | IN                | high   |

| ADCDATA[-1:-2]                                                                                                                  | 93, 91                                                                                           | 10-Bit extension for 10-Bit ADCs                              | reserved<br>(VSS) | N/A    |

| AGCCTLP                                                                                                                         | 25                                                                                               | Analogue AGC control (+)                                      | OUT               | high   |

| SDA                                                                                                                             | 37                                                                                               | I <sup>2</sup> C compatible control bus, data pin             | OD                | N/A    |

| SCL                                                                                                                             | 34                                                                                               | I <sup>2</sup> C compatible control bus, clock pin            | IN                | high   |

| MBUSID[3:0]]                                                                                                                    | 52, 48, 45,<br>43                                                                                | I <sup>2</sup> C compatible control bus, variable ID selector | IN                | high   |

| VO                                                                                                                              | 61                                                                                               | Output of Viterbi Decoder                                     | OUT               | high   |

| VCLK                                                                                                                            | 58                                                                                               | Clock for Viterbi Output                                      | OUT               | high   |

| GP[3:0]                                                                                                                         | 51, 49, 66,<br>64                                                                                | General Purpose output pins, accessible via I <sup>2</sup> C  | OUT               | high   |

| TRERROR                                                                                                                         | 83                                                                                               | MPEG-2 Frame Error Indicator                                  | OUT               | high   |

| TRVALID                                                                                                                         | 78                                                                                               | MPEG-2 Byte Valid Indicator                                   | OUT               | high   |

| TRSTART                                                                                                                         | 80                                                                                               | MPEG-2 Sync Byte Indicator                                    | OUT               | high   |

| TRCLK                                                                                                                           | 77                                                                                               | MPEG-2 Byte Clock                                             | OUT               | high   |

| TRDOUT[7:0]                                                                                                                     | 74, 71, 70,<br>67, 62, 59,<br>55, 53                                                             | MPEG-2 Transport Stream Byte Output                           | OUT               | high   |

| VLOCK                                                                                                                           | 89                                                                                               | Viterbi Decoder Synchronization Status                        | OUT               | high   |

| TPSLOCK                                                                                                                         | 88                                                                                               | TPS demodulator in lock (active H)                            | OUT               | high   |

| VDD33                                                                                                                           | 5, 56, 68,<br>75, 85                                                                             | 3.3 V Supply Voltage for I/O                                  |                   | N/A    |

| VDD18                                                                                                                           | 8, 11, 14,   19, 24, 29,   32, 35, 38,   41, 46, 50,   60, 63, 72,   79, 82, 90,   94, 97,   100 |                                                               | N/A               |        |

| VSS 1, 4, 7, 10,<br>17, 20, 26,<br>30, 33, 36,<br>39, 42, 44,<br>47, 54, 57,<br>65, 69, 73,<br>76, 81, 84,<br>87, 92, 95,<br>98 |                                                                                                  | Ground pins                                                   |                   | N/A    |

| SIGNAL | PIN-NR. | FUNCTIONALITY                                               | ТҮРЕ | ACTIVE |

|--------|---------|-------------------------------------------------------------|------|--------|

| AVDD18 | 21      | 1.8 V analogue VDD for the analog part of the ntegrated PLL |      |        |

| AVSS   | 22      | Analogue VSS for the analog part of the integrated PLL      |      |        |

**NOTE:** For the description of the supply voltages see Table 1 on page 3.

#### DC ELECTRICAL CHARACTERITICS

The MC92315 DC Electrical Characteristics are given in the following tables:

#### Table 3: Electrical Considerations

|                   | ABSOLUTE MAXIMUM RATINGS                                |             |      |  |  |  |  |  |  |

|-------------------|---------------------------------------------------------|-------------|------|--|--|--|--|--|--|

| Symbol            | Parameter                                               |             | Unit |  |  |  |  |  |  |

| V <sub>DD33</sub> | DC Supply Voltage, I/O                                  | -0.3 to 4   | V    |  |  |  |  |  |  |

| V <sub>DD18</sub> | DC Supply Voltage, Core                                 | -0.3 to 2   | V    |  |  |  |  |  |  |

| V <sub>DDAP</sub> | DC Supply Voltage, Analog PLL                           | -0.3 to 2   | V    |  |  |  |  |  |  |

| V <sub>DDDP</sub> | DC Supply Voltage, Digital PLL                          | -0.3 to 2   | V    |  |  |  |  |  |  |

| V <sub>in</sub>   | DC Input Voltage                                        | -0.3 to 4   | V    |  |  |  |  |  |  |

| I                 | DC Current Drain per Pin, Any Single Input or<br>Output | 25          | mA   |  |  |  |  |  |  |

| I                 | DC Current Drain VDD and VSS Pins                       | TBD         | mA   |  |  |  |  |  |  |

| T <sub>stg</sub>  | Storage Temperature                                     | -55 to +150 | °C   |  |  |  |  |  |  |

| TL                | Lead Temperature (10 second soldering)                  | 300         | °C   |  |  |  |  |  |  |

Note: Maximum ratings are those values beyond which damage to the device may occur.

|                     | RECOMMENDED OPERATING CONDITIONS (to guarantee functionality) |      |      |      |  |  |  |  |  |

|---------------------|---------------------------------------------------------------|------|------|------|--|--|--|--|--|

| Symbol              | Parameter                                                     | Min  | Max  | Unit |  |  |  |  |  |

| V <sub>DD33</sub> * | DC Supply Voltage, V <sub>DD33</sub> = 3.3V (Nominal)         | 3.0  | 3.6  | V    |  |  |  |  |  |

| V <sub>DD18</sub> * | DC Supply Voltage, V <sub>DD18</sub> = 1.8V (Nominal)         | 1.65 | 1.95 | V    |  |  |  |  |  |

| V <sub>DDAP</sub>   | DC Supply Voltage, Analog PLL                                 | 1.65 | 1.95 | V    |  |  |  |  |  |

| V <sub>DDDP</sub>   | DC Supply Voltage, Digital PLL                                | 1.65 | 1.95 | V    |  |  |  |  |  |

| T <sub>A</sub>      | Commercial Operating Temperature                              | 0    | 70   | °C   |  |  |  |  |  |

| TJ                  | Junction Temperature                                          | 0    | 105  | °C   |  |  |  |  |  |

\* For testing, only. V<sub>DD</sub> range is wider for simulation purposes.

#### NOTES:

- 1. All parameters are characterized for DC conditions after thermal equilibrium has been established.

- Unused inputs must always be tied to an appropriate logic voltage level (e.g., either V<sub>SS</sub> or V<sub>DD</sub>). Pins marked N/C 2. are to be left unconnected. V<sub>DDAP</sub> requires external ltering of the supply. See details in the users manual.

- 3. Power sequencing precautions:

- It is recommended that V<sub>DD18</sub>,V<sub>DDAP</sub> and V<sub>DDDP</sub> be applied before V<sub>DD33</sub>. Vin must not exceed V<sub>DD33</sub> by more than 0.3 V at any time including during power-on reset. V<sub>DD33</sub> must not exceed V<sub>DD18</sub>, V<sub>DDAP</sub> or V<sub>DDDP</sub> by more than 1.9V at any time including during power-on reset.

- 4. This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit. For proper operation it is recommended that V<sub>in</sub> and V<sub>out</sub> be constrained to the range V<sub>SS</sub>≤ (V<sub>in</sub> or V<sub>out</sub>)≤V<sub>DD33</sub>.

| Table 4: DC Electrical Characteristics ( $T_a = 0 C$ to 70 C) |  |

|---------------------------------------------------------------|--|

| V <sub>DD33</sub> = 3.3V±0.3V                                 |  |

| Sym.              | Parameter                                                                                 | Condition                                                    | Min.                  | Max.                  | Unit |

|-------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------|-----------------------|-----------------------|------|

| V <sub>IH</sub>   | LVTTL Inputs (3.3 V)                                                                      |                                                              | 0.7*V <sub>DD33</sub> | V <sub>DD33</sub>     | V    |

| V <sub>IL</sub>   | LVTTL Inputs (3.3 V)                                                                      |                                                              | 0                     | 0.3*V <sub>DD33</sub> | V    |

|                   | Input Leakage Current, No Pull Resistor                                                   | $V_{in} = V_{DD33}$ or $V_{SS}$                              |                       | 1                     |      |

| l <sub>in</sub>   | with 100K Pullup Resistor                                                                 |                                                              | -18                   | -72                   | μA   |

|                   | with 100K Pulldown Resistor                                                               |                                                              | 18                    | 72                    |      |

|                   | Output High Current, 5 mA LVTTL Output<br>Type                                            | V <sub>DD33</sub> =Min, V <sub>OH</sub> = 2.5 V              | 5                     |                       |      |

| I <sub>ОН</sub>   | Output High Current, 10 mA LVTTL Output<br>Type                                           | -                                                            | 10                    |                       | mA   |

| I <sub>OL</sub>   | Output Low Current, 5 mA LVTTL Output V <sub>DD33</sub> =Min, V <sub>OL</sub> = 0.4 Volts |                                                              | 5                     |                       | mA   |

| 'OL               | Output Low Current, 10 mA LVTTL Output<br>Type                                            | 10                                                           |                       |                       |      |

| V <sub>OH</sub>   | Output High Voltage, LVTTL                                                                | V <sub>DD33</sub> = Min, I <sub>OH</sub> = -100 mA           | 2.5                   |                       | V    |

| V <sub>OL</sub>   | Output Low Voltage, LVTTL                                                                 | V <sub>DD33</sub> = Min, I <sub>OH</sub> = -100 mA           |                       | 0.4                   | V    |

|                   | Output Leakage Current,<br>3-State Output                                                 | Output = Hi Impedance, $V_{out}$<br>= $V_{DD33}$ or $V_{SS}$ |                       | 5                     |      |

| I <sub>OZ</sub>   | Output Leakage Current,                                                                   | Output = Hi Impedance, Vout                                  |                       |                       | μA   |

|                   | Open Drain Output (Device Off)                                                            | = V <sub>DD33</sub>                                          |                       | 5                     |      |

| I <sub>DD33</sub> | Max Quiescent Supply Current                                                              |                                                              |                       |                       | mA   |

#### **Switching Characteristics**

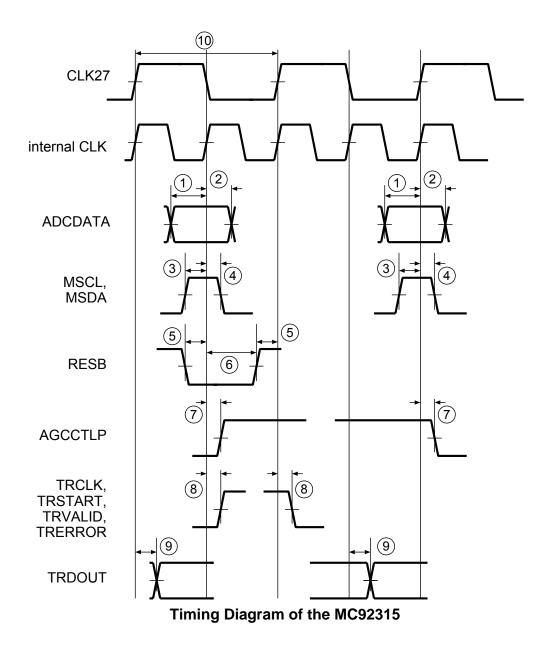

The timing diagram of the MC92315 is shown below and additional timing information can be found in Table 5. The external clock CLK27 is multiplied by two to generate an 'internal clock' that is used for all registers of the MC92315. It should be noted that all timing relationships pertain to both edges of the clock CLK27 as both, rising and falling edges of CLK27 correspond to a rising edge of the internal clock. If CLK27 is used to clock the external ADC it will not matter which edge is used to trigger the ADC operation as longs as setup/hold requirements given in Table 5 are met.

| No. | Characteristic                                       | min  | max  | unit |

|-----|------------------------------------------------------|------|------|------|

| 1   | ADCDATA to CLK setup time                            |      | 2.2  | ns   |

| 2   | ADCDATA to CLK hold time                             |      | 0.6  | ns   |

| 3   | MSCL, MSDA to CLK setup time                         |      | 0.7  | ns   |

| 4   | MSCL, MSDA to CLK hold time                          |      | 0    | ns   |

| 5   | RESB to CLK setup time                               |      | 7.0  | ns   |

| 6   | RESB to CLK hold time                                |      | 2.0  | ns   |

| 7   | CLK to AGCCTRLP out delay                            | 3.2  | 6.6  | ns   |

| 8   | CLK to TRCLK, TRSTART, TRVALID,<br>TRERROR out delay | 3.2  | 7.6  | ns   |

| 9   | CLK to TRDOUT out delay                              | 3.0  | 6.6  | ns   |

| 10  | CLK period                                           | 36.0 | 37.6 | ns   |

#### Table 5: MC92315 Timing

# Improvements included in the MC92315 device compared to the MC92314

In the following paragraphs the major improvements included in the 2K/8K OFDM demodulator MC92315 with respect to its predecessor MC92314 (2K only) are summarised:

#### Improvements concerning status information

#### Lock indicator register added

To improve the visibility of the internal functional blocks an additional I<sup>2</sup>C register was added, showing all the lock indicator bits of the OFDM demodulator.

#### AGC lock indicator added

The visibility of the AGC functional block was improved by adding a status bit to the above mentioned register.

#### **CSE** information readable

To support reception quality measurement apart from BER measurement the appropriate value provided by the CSE block was made available. A new introduced 8 bit I<sup>2</sup>C register provides this information intended especially for choosing the best antenna orientation by minimising the value reported in this register.

# Improvements concerning the clock synchronisation

#### Full digital clock synchronisation

Instead of using an external VCXO all the clock synchronisation is done in the digital domain internally in the MC92315. The VCXO (running at 36.57 MHz) used in the MC92314 is simply replaced by a free running crystal oscillator running at 27 MHz (+/-1 MHz). The external ADC runs at this rate, too.

This concept avoids one of the external control loops employed in the MC92314.

The exact clock frequency of the crystal can be programmed into the MC92315, allowing faster clock synchronisation. The correction value can be read via  $I^2C$ , stored externally and used to speed up clock synchronisation after the next channel change of power up.

## High efficiency clock synchronisation for the 8K mode

As the clock synchronisation in the 8K mode is much more difficult than in the 2K mode this block has been significantly reworked:

- Separate configuration of the clock synchronisation parameters for 2K and 8K reception.

- Programmable threshold to switch from acquisition to tracking mode.

• I In the 8K mode the tracking mode is separated additionally into two stages with different loop bandwidths (wide and narrow) with automatic changeover to ensure the best performance during acquisition **and** afterwards.

## Improvements concerning other demodulator parameters

#### AFC range increased

The available correction range of the internal AFC was doubled. The user is able to select via  $I^2C$  the same range as before or double it by changing the internal coefficients.

#### Increased wordlength

The precision of the signal processing was increased, starting at the 10 bit ADC input. This provides a better overall SNR figure at the output of the MC92315.

### No change of external clocking for different channel bandwidths

To make use of the different channel bandwidths specified by the DVB-T standard it is not necessary to use different clock frequencies like in the MC92314. The different channel bandwidths are programmable by  $I^2C$ , leaving the only difference between receivers for different channel bandwidths in the analog part.

### Viterbi decoder takes code rate setting from OFDM demodulator

To avoid unneccesary long synchronisation times of the Viterbi decoder the most time consuming step (i.e. the selection of the coderate of the convolutional code) is replaced by using the TPS information from the OFDM demodulator. As a side effect the code rate for the whole device can be set (e.g. in applications with fixed code rate) by writing only into the OFDM part.

#### I<sup>2</sup>C Register Map of the MC92315

As the single chip DVB-T demodulator MC92315 is the further development of Freescale's single chip 2K device, the register structure of its ancestor was preserved to allow as much reuse of the control software as possible. Therefore the registers are still grouped into the OFDM part and the FEC part, corresponding to Free-Iscale's first generation DVB-T devices MC92308 and MC92309.

#### **Register Map for the OFDM Part**

The register map of the OFDM block is given in the table below with the registers changed or added w.r.t. its predecessor MC92314 marked.

The I<sup>2</sup>C device address for the OFDM part is 010XXXX with XXXX beeing the logic levels at the external MBUSID pins.

| Addr | Name    | Туре | Def/<br>Fmt | b7       | b6       | b5   | b4   | b3 | b2   | b1    | b0 |

|------|---------|------|-------------|----------|----------|------|------|----|------|-------|----|

| \$0  | TPS R0  | R    | n/a         | S[7:0]   |          |      |      |    |      |       |    |

| \$1  | TPS R1  | R    | n/a         | S[15:8]  |          |      |      |    |      |       |    |

| \$2  | TPS R2  | R    | n/a         | S[23:16] |          |      |      |    |      |       |    |

| \$3  | TPS R3  | R    | n/a         |          | S[31:24] |      |      |    |      |       |    |

| \$4  | TPS R4  | R    | n/a         | S[39:32] |          |      |      |    |      |       |    |

| \$5  | TPS R5  | R    | n/a         |          | S[47:40] |      |      |    |      |       |    |

| \$6  | TPS R 6 | R    | n/a         | S[55:48] |          |      |      |    |      |       |    |

| \$7  | TPS R7  | R    | n/a         | S[63:56] |          |      |      |    |      |       |    |

| \$8  | TPS R 8 | R    | n/a         | AFCL     | CLKL     | TPSV | TPSL |    | S[67 | 7:64] |    |

#### Table 6: OFDM Block Register Map

| Addr | Name      | Туре | Def/<br>Fmt  | b7                            | b6              | b5  | b4   | b3   | b2          | b1   | b0    |  |

|------|-----------|------|--------------|-------------------------------|-----------------|-----|------|------|-------------|------|-------|--|

| \$9  | TPS ldx   | W    | n/a          |                               | 1               | 000 |      | 1    |             |      |       |  |

| \$A  | Reset     | w    | \$00         | AFC<br>AGC                    | TSYNC           | FE  | FFT  | CHAN | DEC         | x    | TOTAL |  |

| \$B  | OFDM R0   | R/W  | \$12         | Х                             | X CODERATE      |     |      | GUA  | GUARD CONST |      |       |  |

| \$C  | OFDM R1   | w    | \$1F         | CHANBW XX                     |                 |     | AFSY | ATPS | AFCM        | TSM  |       |  |

| \$D  | OFDM R2   | w    | \$D3         | FTSE                          | TSE AFCS AGCS X |     |      | X    | UHFI        | ADCM | MS2K  |  |

| \$E  | CKFILT2K  | w    | \$00<br>2's  | CLKFILT2K_PROP CLKFILT2K_INT  |                 |     |      |      |             |      |       |  |

| \$F  | GAIN OFFS | w    | \$20<br>2's  | AGC_GAIN AFC_GAIN             |                 |     |      |      |             |      |       |  |

| \$10 | AFCSWP0   | W    | \$00         | I                             |                 |     |      |      |             |      |       |  |

| \$11 | AFCSWP1   | w    | \$E8<br>2's  | AFCSWPSTRT                    |                 |     |      |      |             |      |       |  |

| \$12 | AFCTHRA   | w    | \$15<br>Uns. | AFCTHRESH_A                   |                 |     |      |      |             |      |       |  |

| \$13 | AFCTHRB   | w    | \$10<br>Uns. | AFCTHRESH_B                   |                 |     |      |      |             |      |       |  |

| \$14 | AGCTHR0   | W    | \$96         |                               |                 |     |      |      |             |      |       |  |

| \$15 | AGCTHR1   | w    | \$2A<br>Uns. | AGCTHRESH                     |                 |     |      |      |             |      |       |  |

| \$16 | AFCSWS0   | W    | \$80         |                               |                 |     |      |      |             |      |       |  |

| \$17 | AFCSWS1   | w    | \$00<br>2's  | AFCSWPSPEED                   |                 |     |      |      |             |      |       |  |

| \$18 | CSE R0    | w    | \$40<br>Uns. | CSE_0                         |                 |     |      |      |             |      |       |  |

| \$19 | CSE R1    | w    | \$20<br>Uns. | CSE_1                         |                 |     |      |      |             |      |       |  |

| \$1A | CSE R2    | w    | \$10<br>Uns. | CSE_2                         |                 |     |      |      |             |      |       |  |

| \$1B | CSE R3    | w    | \$00<br>2's  | CSE_3                         |                 |     |      |      |             |      |       |  |

| \$1C | CSE R4    | w    | \$C6<br>Uns. | CSE_4                         |                 |     |      |      |             |      |       |  |

| \$1D | CLKF8KWD  | w    | \$1F<br>2's  | CLKF8KWIDE_PROP CLKF8KWIDE_IN |                 |     |      |      | Г           |      |       |  |

| §1E  | CLKF8KNA  | W    | \$1F<br>2's  | CLKF8KNRW_PROP CLKF8KNRW_INT  |                 |     |      |      |             | -    |       |  |

- I

- I

I

I

I

I

I

| Addr | Name    | Туре | Def/<br>Fmt | b7                        | b6                    | b5   | b4   | b3                | b2    | b1    | b0     |  |

|------|---------|------|-------------|---------------------------|-----------------------|------|------|-------------------|-------|-------|--------|--|

| \$1F | CLKOFS0 | W    | \$00        |                           |                       |      |      |                   |       |       |        |  |

| \$20 | CLKOFS1 | W    | \$00<br>2's | CLKOFFSET                 |                       |      |      |                   |       |       |        |  |

| \$22 | LOCKIN  | R    | n/a         | STRV                      | AFCL                  | CLKL | TPSV | TPSL              | AGCL  | DEINT | INSYNC |  |

| \$23 | OFDMR3  | R/W  | \$20        | GI                        | GIDET AGI<br>SE AFCRG |      |      |                   | ALPHA |       | 8K     |  |

| \$35 | AGCFIX0 | W    | \$00        |                           |                       |      |      |                   |       |       |        |  |

| \$36 | AGCFIX1 | W    | \$00<br>2's | AGCFIX                    |                       |      |      |                   |       |       |        |  |

| \$3B | TSFB0   | R    | n/a         | TS_FEEDBACK[7:0]          |                       |      |      |                   |       |       |        |  |

| \$3C | TSFB1   | R    | n/a<br>2's  | KDET                      | KDET XXX              |      |      | TS_FEEDBACK[11:8] |       |       |        |  |

| \$3F | AFCFB0  | R    | n/a         | AFC_FEEDBACK              |                       |      |      |                   |       |       |        |  |

| \$40 | AFCFB1  | R    | n/a<br>2's  |                           |                       |      |      |                   |       |       |        |  |

| \$43 | AGCFB0  | R    | n/a         |                           |                       |      |      |                   |       |       |        |  |

| \$44 | AGCFB1  | R    | n/a<br>2's  | AGC_FEEDBACK              |                       |      |      |                   |       |       |        |  |

| \$48 | FTFIX0  | W    | \$00        | FT_FIX[7:0]               |                       |      |      |                   |       |       |        |  |

| \$49 | FTFIX1  | W    | \$E0<br>2's | ATSY KENA XX FT_FIX[11:8] |                       |      |      |                   |       |       |        |  |

### I

1

#### Note:

The bits marked 'X' are reserved bits.

Registers wider than 8 bits must be written LSB first, which is done in the most efficient way using the address auto-increment of the I<sup>2</sup>C controller. **The value is stored internally not earlier than the MSB is written**.

Similar the reading of 2-byte read-only registers must start with the LSB. **The values provided by the internal blocks are latched only if the LSB is read**. If the user does an access to the MSB only no meaningful data are returned.

For more information see the MC92315 User Manual.

#### **Register Map for the FEC Part**

See the Table 7 on page 15 for the registers of the FEC block.

The I<sup>2</sup>C device address for the FEC part is 001XXXX with XXXX beeing the logic levels at the external MBUSID pins

| Addr | Name         | Туре | Def  | b7                  | b6         | b5    | b4   | b3          | b2         | b1    | b0         |  |

|------|--------------|------|------|---------------------|------------|-------|------|-------------|------------|-------|------------|--|

| \$00 | CONFIG_VIT   | W    | \$FF | DAP                 | DLT        | DDEC  | DTHR | IFS         | VSYNC[2:0] |       |            |  |

| \$01 | THRESHOLD    | W    | \$00 |                     | THRES[4:0] |       |      |             |            |       |            |  |

| \$02 | DECREMENT    | W    | \$00 | DEC[4:0]            |            |       |      |             |            |       |            |  |

| \$03 | TIMEOUT      | W    | \$00 | TIME[3:0]           |            |       |      |             |            |       |            |  |

| \$04 | AVG_PERIOD   | W    | \$00 | PERIOD[3:0]         |            |       |      |             |            |       |            |  |

| \$08 | QVALLSB      | R    |      | QVAL[7:0]           |            |       |      |             |            |       |            |  |

| \$09 | QVALMSB      | R    |      | QVAL[14:8]          |            |       |      |             |            |       |            |  |

| \$0A | SYNC_VIT     | R    |      |                     |            |       |      | VLCK        |            |       | R<br>PHASE |  |

| \$0B | SELECTEDRATE | R    |      |                     |            |       |      | 1           | SR[2:0]    |       |            |  |

| \$0C | FIFO_STATE   | R    |      |                     |            |       |      |             | I          | VFF   | VEF        |  |

| \$11 | AQ_THRESH    | W    | \$68 | AQ_SYNC[2:0] AQ_REF |            |       |      |             | Q_REF[4:   | :0]   |            |  |

| \$12 | TR_THRESH    | W    | \$7F | TF                  | R_SYNC[2   | 2:0]  |      | TR_REF[4:0] |            |       |            |  |

| \$13 | TIME_COUNT   | W    | \$FF | TC[7:0]             |            |       |      |             |            |       |            |  |

| \$18 | BER_COUNT    | R    |      | BER_COUNT[7:0]      |            |       |      |             |            |       |            |  |

| \$19 | BAD_COUNT    | R    |      | BAD_COUNT[3:0]      |            |       |      |             |            |       |            |  |

| \$1A | SYNC_RS      | R    |      | 00000               |            |       |      |             | STRV       | DEINT | IN<br>SYNC |  |

| \$1F | SOFT_RESET   | W    | \$00 |                     | GP         | [3:0] |      |             |            | SRRS  | SRVIT      |  |

**NOTE:** The pecularities concerning the 2-byte registers of the OFMD part don't apply to the FEC block.

Home Page: www.freescale.com email: support@freescale.com USA/Europe or Locations Not Listed: Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 (800) 521-6274 480-768-2130 support@freescale.com Europe, Middle East, and Africa: Freescale Halbleiter Deutschland GmbH **Technical Information Center** Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com Japan: Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064, Japan 0120 191014 +81 2666 8080 support.japan@freescale.com Asia/Pacific: Freescale Semiconductor Hong Kong Ltd. **Technical Information Center** 2 Dai King Street Tai Po Industrial Estate, Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com For Literature Requests Only: Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 (800) 441-2447 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor @hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document. Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.