# MCF5307 ColdFire® Integrated Microprocessor User's Manual

MCF5307UM/D Rev. 2.0, 08/2000

ColdFire is a registered trademark and DigitalDNA is a trademark of Motorola, Inc.  $I^2C$  is a registered trademark of Phillips Semiconductors

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and (M) are registered trademarks of Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### How to reach us:

USA/EUROPE/Locations Not Listed: Motorola Literature Distribution; P.O. Box 5405, Denver, Colorado 80217. 1–303–675–2140

or 1-800-441-2447

JAPAN: Motorola Japan Ltd.; SPS, Technical Information Center, 3–20–1, Minami–Azabu. Minato–ku, Tokyo 106–8573 Japan.

81-3-3440-3569

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Centre, 2 Dai King Street, Tai Po Industrial Estate, Tai Po, N.T.,

Hong Kong. 852-26668334

Technical Information Center: 1-800-521-6274

HOME PAGE: http://www.motorola.com/semiconductors

Document Comments: FAX (512) 895-2638, Attn: RISC Applications Engineering

World Wide Web Addresses: http://www.motorola.com/PowerPC

http://www.motorola.com/NetComm http://www.motorola.com/ColdFire

| Overview                                        | 1        |

|-------------------------------------------------|----------|

| Part I: MCF5307 Processor Core                  | Part I   |

| ColdFire Core                                   | 2        |

| Hardware Multiply/Accumulate (MAC) Unit         | 3        |

| Local Memory                                    | 4        |

| Debug Support                                   | 5        |

| Part II: System Integration Module (SIM)        | Part II  |

| SIM Overview                                    | 6        |

| Phase-Locked Loop (PLL)                         | 7        |

| I <sup>2</sup> C Module                         | 8        |

| Interrupt Controller                            | 9        |

| Chip-Select Module                              | 10       |

| Synchronous/Asynchronous DRAM Controller Module | 11       |

| Part III: Peripheral Module                     | Part III |

| DMA Controller Module                           | 12       |

| Timer Module                                    | 13       |

| UART Modules                                    | 14       |

| Parallel Port (General-Purpose I/O)             | 15       |

| Part IV: Hardware Interface                     | Part IV  |

| Mechanical Data                                 | 16       |

| Signal Descriptions                             | 17       |

| Bus Operation                                   | 18       |

| IEEE 1149.1 Test Access Port (JTAG)             | 19       |

| Electrical Specifications                       | 20       |

| Appendix: Memory Map                            | Α        |

| Glossary of Terms and Abbreviations             | GLO      |

| Index                                           | IND      |

| 1        | Overview                                        |

|----------|-------------------------------------------------|

| Part I   | Part I: MCF5307 Processor Core                  |

| 2        | ColdFire Core                                   |

| 3        | Hardware Multiply/Accumulate (MAC) Unit         |

| 4        | Local Memory                                    |

| 5        | Debug Support                                   |

| Part II  | Part II: System Integration Module (SIM)        |

| 6        | SIM Overview                                    |

| 7        | Phase-Locked Loop (PLL)                         |

| 8        | I <sup>2</sup> C Module                         |

| 9        | Interrupt Controller                            |

| 10       | Chip-Select Module                              |

| 11       | Synchronous/Asynchronous DRAM Controller Module |

| Part III | Part III: Peripheral Module                     |

| 12       | DMA Controller Module                           |

| 13       | Timer Module                                    |

| 14       | UART Modules                                    |

| 15       | Parallel Port (General-Purpose I/O)             |

| Part IV  | Part IV: Hardware Interface                     |

| 16       | Mechanical Data                                 |

| 17       | Signal Descriptions                             |

| 18       | Bus Operation                                   |

| 19       | IEEE 1149.1 Test Access Port (JTAG)             |

| 20       | Electrical Specifications                       |

| А        | Appendix B: Memory Map                          |

| GLO      | Glossary of Terms and Abbreviations             |

| IND      | Index                                           |

## **CONTENTS**

| Paragraph | Title | Page   |

|-----------|-------|--------|

| Number    | riue  | Number |

#### **About This Book**

#### Chapter 1 Overview

| 1.1     | Features                                                      |

|---------|---------------------------------------------------------------|

| 1.2     | MCF5307 Features                                              |

| 1.2.1   | Process                                                       |

| 1.3     | ColdFire Module Description 1-7                               |

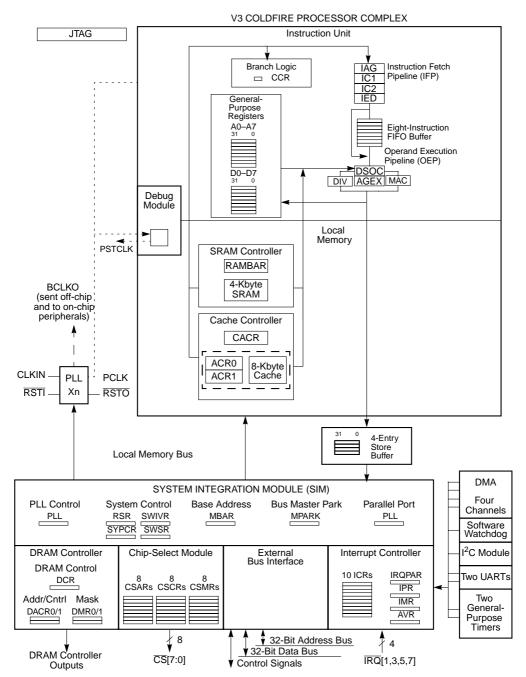

| 1.3.1   | ColdFire Core                                                 |

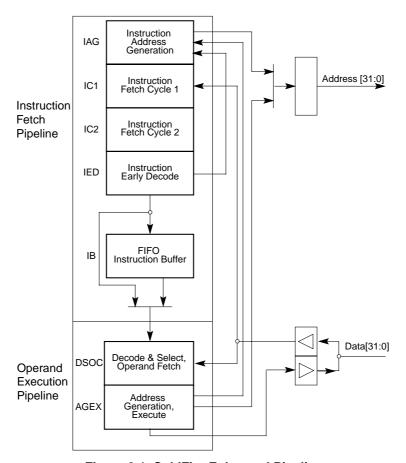

| 1.3.1.1 | Instruction Fetch Pipeline (IFP)                              |

| 1.3.1.2 | Operand Execution Pipeline (OEP)1-7                           |

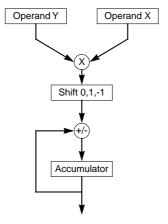

| 1.3.1.3 | MAC Module 1-7                                                |

| 1.3.1.4 | Integer Divide Module                                         |

| 1.3.1.5 | 8-Kbyte Unified Cache 1-8                                     |

| 1.3.1.6 | Internal 4-Kbyte SRAM 1-8                                     |

| 1.3.2   | DRAM Controller                                               |

| 1.3.3   | DMA Controller                                                |

| 1.3.4   | UART Modules1-8                                               |

| 1.3.5   | Timer Module 1-9                                              |

| 1.3.6   | I2C Module                                                    |

| 1.3.7   | System Interface                                              |

| 1.3.7.1 | External Bus Interface                                        |

| 1.3.7.2 | Chip Selects 1-10                                             |

| 1.3.7.3 | 16-Bit Parallel Port Interface 1-10                           |

| 1.3.7.4 | Interrupt Controller                                          |

| 1.3.7.5 | JTAG 1-11                                                     |

| 1.3.8   | System Debug Interface                                        |

| 1.3.9   | PLL Module 1-11                                               |

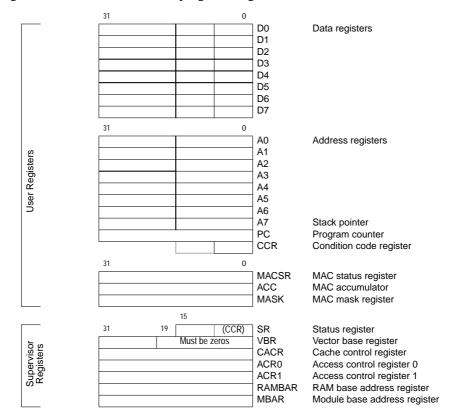

| 1.4     | Programming Model, Addressing Modes, and Instruction Set 1-12 |

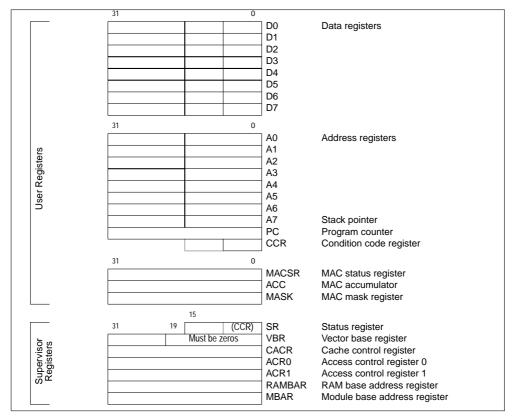

| 1.4.1   | Programming Model 1-13                                        |

| 1.4.2   | User Registers 1-14                                           |

| 1.4.3   | Supervisor Registers 1-14                                     |

| 1.4.4   | Instruction Set1-15                                           |

| 1. r.T  | mon action bet                                                |

#### **CONTENTS**

| Paragraph |  |

|-----------|--|

| Number    |  |

#### **Title**

#### **Page** Number

#### Part I **MCF5407 Processor Core**

# Chapter 2 ColdFire Core

| 2.1       | Features and Enhancements                         | 2 21 |

|-----------|---------------------------------------------------|------|

| 2.1.1     | Clock-Multiplied Microprocessor Core              |      |

| 2.1.2     | Enhanced Pipelines                                |      |

| 2.1.2.1   | Instruction Fetch Pipeline (IFP)                  |      |

| 2.1.2.1.1 | Branch Acceleration                               |      |

| 2.1.2.1.1 | Operand Execution Pipeline (OEP)                  |      |

| 2.1.2.2.1 | Illegal Opcode Handling                           |      |

| 2.1.2.2.1 | Hardware Multiply/Accumulate (MAC) Unit           |      |

| 2.1.2.2.3 | Hardware Divide Unit                              |      |

| 2.1.2.2.3 | Debug Module Enhancements                         |      |

| 2.1.3     | Programming Model                                 |      |

| 2.2.1     | User Programming Model                            |      |

| 2.2.1.1   | Data Registers (D0–D7)                            |      |

| 2.2.1.1   | Address Registers (A0–A6)                         |      |

| 2.2.1.3   | Stack Pointer (A7, SP)                            |      |

| 2.2.1.3   | Program Counter (PC)                              |      |

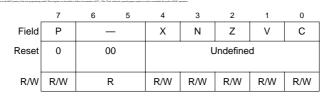

| 2.2.1.5   | Condition Code Register (CCR)                     |      |

| 2.2.2     | Supervisor Programming Model                      |      |

| 2.2.2.1   | Status Register (SR)                              |      |

| 2.2.2.2   | Vector Base Register (VBR)                        |      |

| 2.2.2.3   | Cache Control Register (CACR)                     |      |

| 2.2.2.4   | Access Control Registers (ACR0–ACR1)              |      |

| 2.2.2.5   | RAM Base Address Register (RAMBAR)                |      |

| 2.2.2.6   | Module Base Address Register (MBAR)               |      |

| 2.3       | Integer Data Formats.                             |      |

| 2.4       | Organization of Data in Registers                 |      |

| 2.4.1     | Organization of Integer Data Formats in Registers |      |

| 2.4.2     | Organization of Integer Data Formats in Memory    |      |

| 2.5       | Addressing Mode Summary                           |      |

| 2.6       | Instruction Set Summary                           |      |

| 2.6.1     | Instruction Set Summary                           |      |

| 2.7       | Instruction Timing                                | 2-40 |

| 2.7.1     | MOVE Instruction Execution Times                  |      |

| 2.7.2     | Execution Timings—One-Operand Instructions        |      |

| 2.7.3     | Execution Timings—Two-Operand Instructions        |      |

| 2.7.4     | Miscellaneous Instruction Execution Times         |      |

|           |                                                   |      |

| Paragraph<br>Number       | Title                                                            | Page<br>Number   |

|---------------------------|------------------------------------------------------------------|------------------|

| 2.7.5                     | Branch Instruction Execution Times                               | 2-46             |

| 2.8                       | Exception Processing Overview                                    | 2-47             |

| 2.8.1                     | Exception Stack Frame Definition                                 |                  |

| 2.8.2                     | Processor Exceptions                                             | 2-50             |

|                           | Chapter 3 Hardware Multiply/Accumulate (MAC) Unit                |                  |

| 3.1                       | Overview                                                         | 3-1              |

| 3.1.1                     | MAC Programming Model                                            |                  |

| 3.1.2                     | General Operation                                                |                  |

| 3.1.3                     | MAC Instruction Set Summary                                      |                  |

| 3.1.4                     | Data Representation                                              |                  |

| 3.2                       | MAC Instruction Execution Timings                                | 3-5              |

|                           | Chapter 4 Local Memory                                           |                  |

| 4.1                       | Interactions between Local Memory Modules                        | 4-1              |

| 4.2                       | SRAM Overview                                                    | 4-1              |

| 4.3                       | SRAM Operation                                                   | 4-2              |

| 4.4                       | SRAM Programming Model                                           | 4-3              |

| 4.4.1                     | SRAM Base Address Register (RAMBAR)                              | 4-3              |

| 4.5                       | SRAM Initialization                                              |                  |

| 4.5.1                     | SRAM Initialization Code                                         | -                |

| 4.6                       | Power Management                                                 |                  |

| 4.7                       | Cache Overview                                                   |                  |

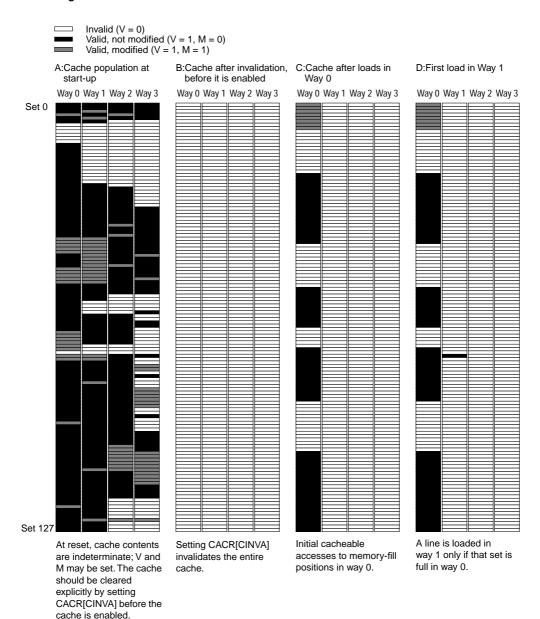

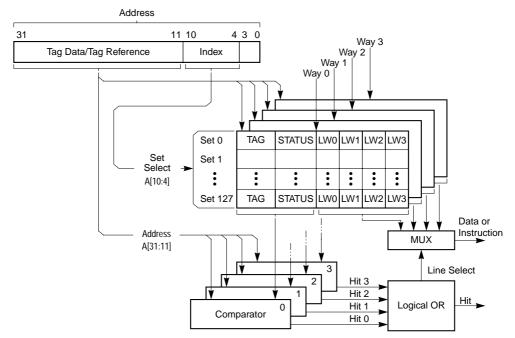

| 4.8                       | Cache Organization                                               |                  |

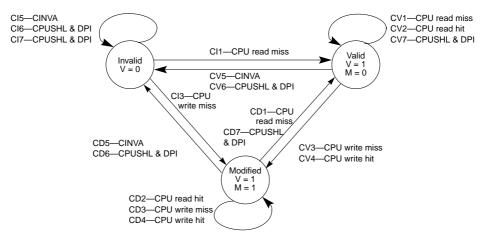

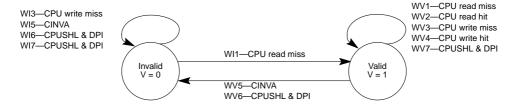

| 4.8.1                     | Cache Line States: Invalid, Valid-Unmodified, and Valid-Modified |                  |

| 4.8.2                     | The Cache at Start-Up                                            |                  |

| 4.9                       | Cache Operation                                                  |                  |

| 4.9.1                     | Caching Modes                                                    |                  |

| 4.9.1.1                   | Cacheable Accesses                                               |                  |

| 4.9.1.2                   | Write-Through Mode                                               |                  |

| 4.9.1.3                   | Copyback Mode                                                    |                  |

| 4.9.2                     | Cache Protocol                                                   |                  |

| 4.9.3<br>4.9.3.1          | Cache Protocol                                                   | -                |

| 4.9.3.1                   | Write Miss                                                       | -                |

| 4.9.3.2<br>4.9.3.3        | Read Hit                                                         |                  |

| 4.9.3.4                   | Write Hit                                                        |                  |

| 4.9.4                     | Cache Coherency                                                  |                  |

| <b>→.</b> フ. <del>↑</del> | Cache Coherency                                                  | <del>4</del> -1/ |

| Paragraph<br>Number | Title                                                 | Page<br>Number |

|---------------------|-------------------------------------------------------|----------------|

| 4.9.5               | Memory Accesses for Cache Maintenance                 |                |

| 4.9.5.1             | Cache Filling                                         | 4-17           |

| 4.9.5.2             | Cache Pushes                                          | 4-18           |

| 4.9.5.2.1           | Push and Store Buffers                                | 4-18           |

| 4.9.5.2.2           | Push and Store Buffer Bus Operation                   | 4-18           |

| 4.9.6               | Cache Locking                                         | 4-19           |

| 4.10                | Cache Registers                                       | 4-21           |

| 4.10.1              | Cache Control Register (CACR)                         | 4-21           |

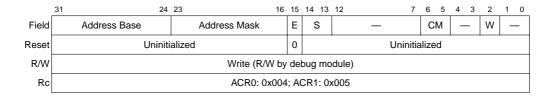

| 4.10.2              | Access Control Registers (ACR0–ACR1)                  | 4-22           |

| 4.11                | Cache Management                                      | 4-24           |

| 4.12                | Cache Operation Summary                               | 4-25           |

| 4.12.1              | Cache State Transitions                               | 4-25           |

| 4.13                | Cache Initialization Code                             | 4-29           |

|                     | Chapter 5 Debug Support                               |                |

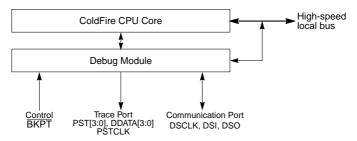

| 5.1                 | Overview                                              | 5-1            |

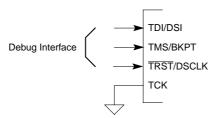

| 5.2                 | Signal Description                                    | 5-2            |

| 5.3                 | Real-Time Trace Support                               | 5-3            |

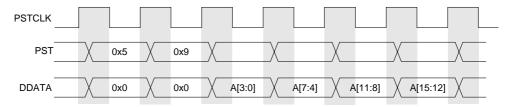

| 5.3.1               | Begin Execution of Taken Branch (PST = 0x5)           |                |

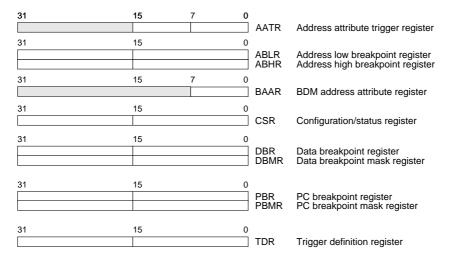

| 5.4                 | Programming Model                                     |                |

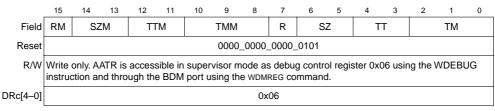

| 5.4.1               | Address Attribute Trigger Register (AATR)             |                |

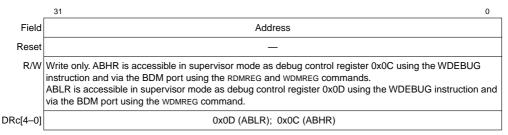

| 5.4.2               | Address Breakpoint Registers (ABLR, ABHR)             |                |

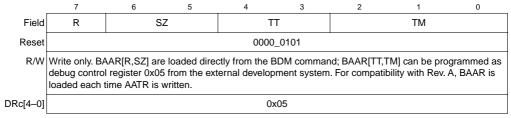

| 5.4.3               | BDM Address Attribute Register (BAAR)                 | 5-9            |

| 5.4.4               | Configuration/Status Register (CSR)                   | 5-10           |

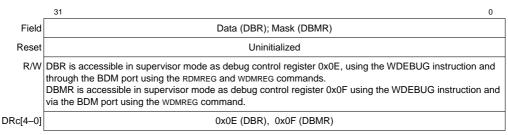

| 5.4.5               | Data Breakpoint/Mask Registers (DBR, DBMR)            |                |

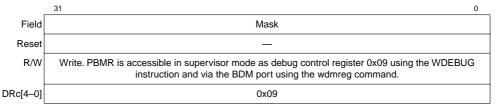

| 5.4.6               | Program Counter Breakpoint/Mask Registers (PBR, PBMR) |                |

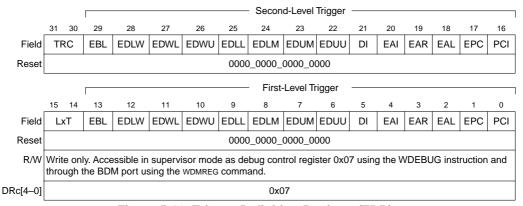

| 5.4.7               | Trigger Definition Register (TDR)                     |                |

| 5.5                 | Background Debug Mode (BDM)                           | 5-16           |

| 5.5.1               | CPU Halt                                              |                |

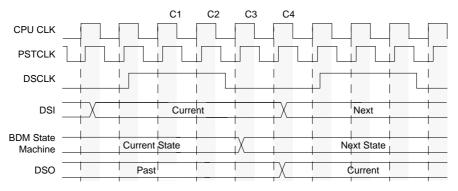

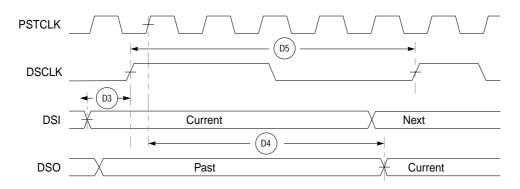

| 5.5.2               | BDM Serial Interface                                  | 5-17           |

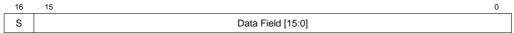

| 5.5.2.1             | Receive Packet Format                                 |                |

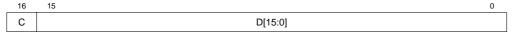

| 5.5.2.2             | Transmit Packet Format                                | 5-19           |

| 5.5.3               | BDM Command Set                                       |                |

| 5.5.3.1             | ColdFire BDM Command Format                           |                |

| 5.5.3.1.1           | Extension Words as Required                           |                |

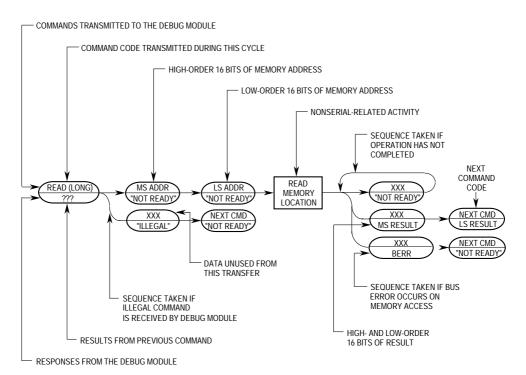

| 5.5.3.2             | Command Sequence Diagrams                             |                |

| 5.5.3.3             | Command Set Descriptions                              |                |

| 5.5.3.3.1           | Read A/D Register (RAREG/RDREG)                       |                |

| 5.5.3.3.2           | Write A/D Register (WAREG/WDREG)                      |                |

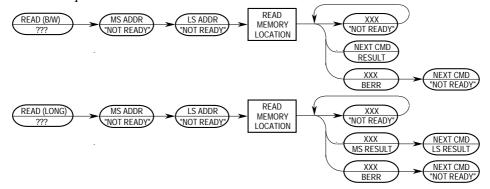

| 5.5.3.3.3           | Read Memory Location (READ)                           | 5-26           |

| Paragraph<br>Number | Title                                                     | Page<br>Number |

|---------------------|-----------------------------------------------------------|----------------|

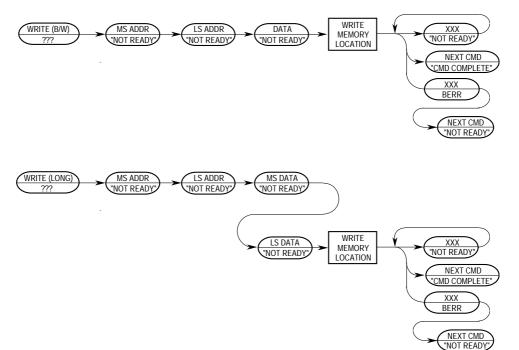

| 5.5.3.3.4           | Write Memory Location (WRITE)                             | 5-27           |

| 5.5.3.3.5           | Dump Memory Block (DUMP)                                  |                |

| 5.5.3.3.6           | Fill Memory Block (FILL)                                  |                |

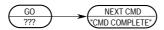

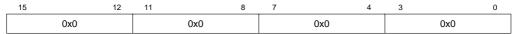

| 5.5.3.3.7           | Resume Execution (GO)                                     |                |

| 5.5.3.3.8           | No Operation (NOP)                                        | 5-34           |

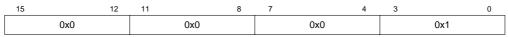

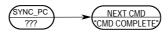

| 5.5.3.3.9           | Synchronize PC to the PST/DDATA Lines (SYNC_PC)           | 5-35           |

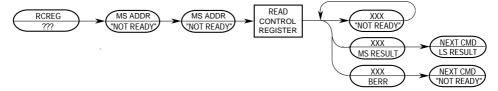

| 5.5.3.3.10          | Read Control Register (RCREG)                             |                |

| 5.5.3.3.11          | Write Control Register (WCREG)                            |                |

| 5.5.3.3.12          | Read Debug Module Register (RDMREG)                       | 5-38           |

| 5.5.3.3.13          | Write Debug Module Register (WDMREG)                      | 5-39           |

| 5.6                 | Real-Time Debug Support                                   | 5-39           |

| 5.6.1               | Theory of Operation                                       | 5-40           |

| 5.6.1.1             | Emulator Mode                                             | 5-41           |

| 5.6.2               | Concurrent BDM and Processor Operation                    | 5-41           |

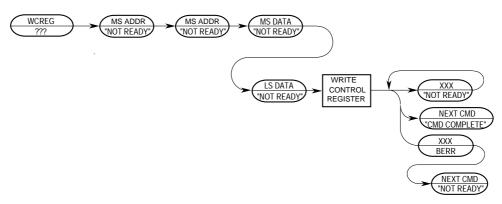

| 5.7                 | Motorola-Recommended BDM Pinout                           | 5-42           |

| 5.8                 | Processor Status, DDATA Definition                        | 5-42           |

| 5.8.1               | User Instruction Set                                      | 5-43           |

| 5.8.2               | Supervisor Instruction Set                                | 5-46           |

|                     | System Integration Module (SIM)  Chapter 6  SIM Overview  |                |

| 6.1                 | Features                                                  | 6-1            |

| 6.2                 | Programming Model                                         |                |

| 6.2.1               | SIM Register Memory Map                                   |                |

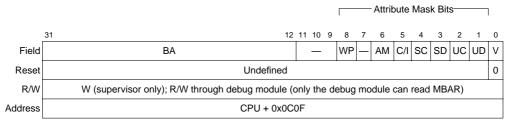

| 6.2.2               | Module Base Address Register (MBAR)                       |                |

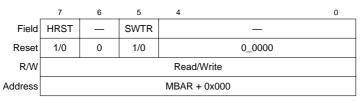

| 6.2.3               | Reset Status Register (RSR)                               |                |

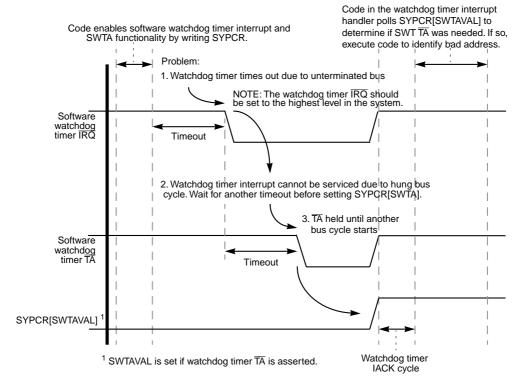

| 6.2.4               | Software Watchdog Timer                                   |                |

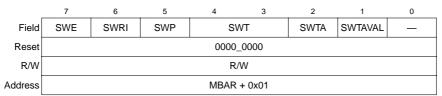

| 6.2.5               | System Protection Control Register (SYPCR)                |                |

| 6.2.6               | Software Watchdog Interrupt Vector Register (SWIVR)       |                |

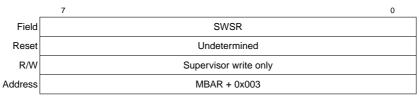

| 6.2.7               | Software Watchdog Service Register (SWSR)                 |                |

| 6.2.8               | PLL Clock Control for CPU STOP Instruction                |                |

| 6.2.9               | Pin Assignment Register (PAR)                             | 6-10           |

| 6.2.10              | Bus Arbitration Control                                   |                |

| 6.2.10.1            | Default Bus Master Park Register (MPARK)                  |                |

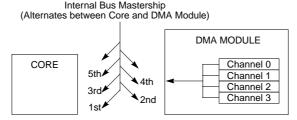

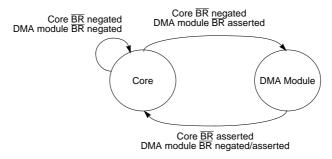

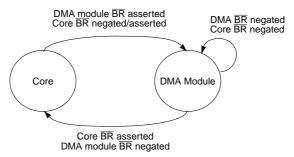

| 6.2.10.1.1          | Arbitration for Internally Generated Transfers (MPARK[PAR |                |

| 6.2.10.1.2          | Arbitration between Internal and External Masters         |                |

|                     | for Accessing Internal Resources                          | 6-14           |

| Paragraph<br>Number                                            | Title                                                                                                                                           | Page<br>Number       |  |

|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|

|                                                                | Chapter 7 Phase-Locked Loop (PLL)                                                                                                               |                      |  |

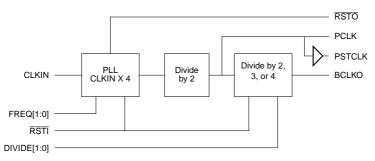

| 7.1<br>7.1.1<br>7.2<br>7.2.1<br>7.2.2<br>7.2.3<br>7.2.4<br>7.3 | Overview                                                                                                                                        |                      |  |

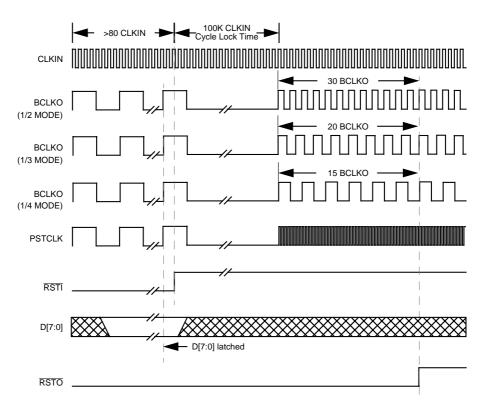

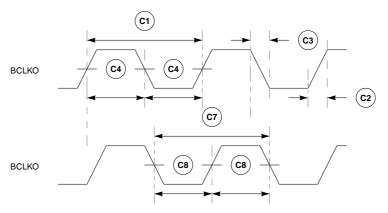

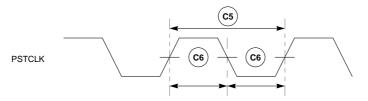

| 7.4<br>7.4.1<br>7.4.2<br>7.5                                   | Timing Relationships PCLK, PSTCLK, and BCLKO RSTI Timing PLL Power Supply Filter Circuit                                                        | 7-4<br>7-4<br>7-5    |  |

|                                                                | Chapter 8<br>I <sup>2</sup> C Module                                                                                                            |                      |  |

| 8.1<br>8.2                                                     | Overview Interface Features                                                                                                                     |                      |  |

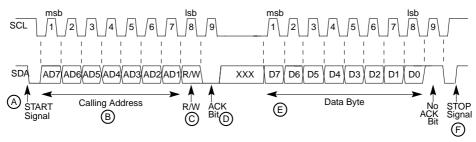

| 8.3<br>8.4<br>8.4.1                                            | I <sup>2</sup> C System Configuration I <sup>2</sup> C Protocol Arbitration Procedure                                                           | 8-3<br>8-3<br>8-4    |  |

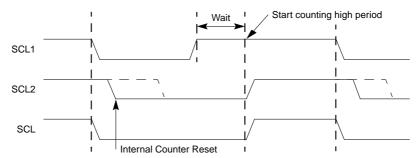

| 8.4.2<br>8.4.3<br>8.4.4<br>8.5                                 | Clock Synchronization  Handshaking  Clock Stretching  Programming Model                                                                         | 8-5<br>8-5           |  |

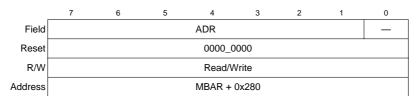

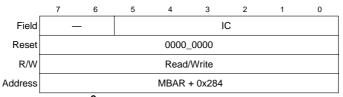

| 8.5.1<br>8.5.2<br>8.5.3                                        | I <sup>2</sup> C Address Register (IADR)                                                                                                        | 8-6<br>8-7<br>8-8    |  |

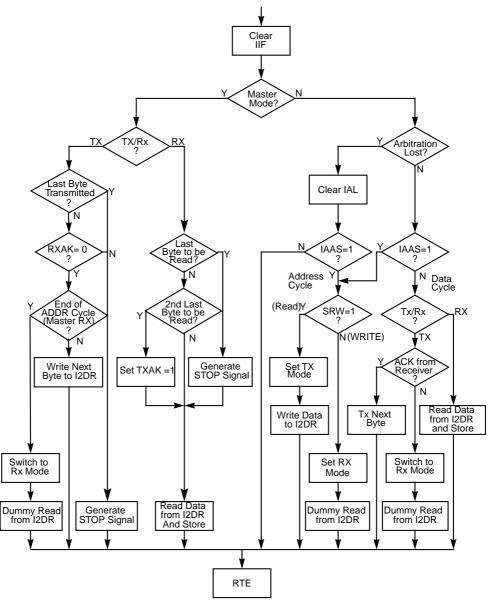

| 8.5.4<br>8.5.5<br>8.6<br>8.6.1                                 | I <sup>2</sup> C Status Register (I2SR) I <sup>2</sup> C Data I/O Register (I2DR) I <sup>2</sup> C Programming Examples Initialization Sequence | 8-10<br>8-10         |  |

| 8.6.2<br>8.6.3<br>8.6.4                                        | Generation of START  Post-Transfer Software Response  Generation of STOP                                                                        | 8-10<br>8-11<br>8-12 |  |

| 8.6.5<br>8.6.6<br>8.6.7                                        | Generation of Repeated START                                                                                                                    | 8-13                 |  |

| Paragraph<br>Number | Title                                              | Page<br>Number |

|---------------------|----------------------------------------------------|----------------|

|                     | Chapter 9<br>Interrupt Controller                  |                |

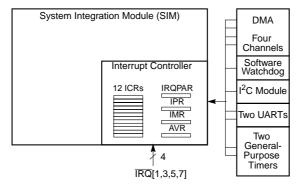

| 9.1                 | Overview                                           | 9-1            |

| 9.2                 | Interrupt Controller Registers                     |                |

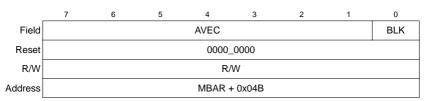

| 9.2.1               | Interrupt Control Registers (ICR0–ICR9)            | 9-3            |

| 9.2.2               | Autovector Register (AVR)                          | 9-5            |

| 9.2.3               | Interrupt Pending and Mask Registers (IPR and IMR) | 9-6            |

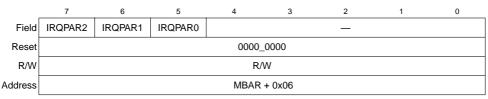

| 9.2.4               | Interrupt Port Assignment Register (IRQPAR)        | 9-7            |

|                     | Chapter 10                                         |                |

|                     | Chip-Select Module                                 |                |

| 10.1                | Overview                                           | 10-1           |

| 10.2                | Chip-Select Module Signals                         | 10-1           |

| 10.3                | Chip-Select Operation                              | 10-2           |

| 10.3.1              | General Chip-Select Operation                      | 10-3           |

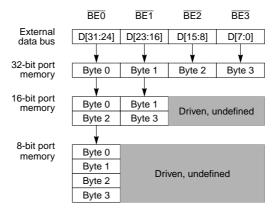

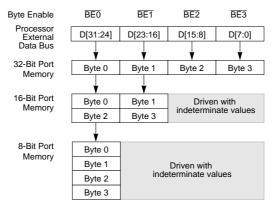

| 10.3.1.1            | 8-, 16-, and 32-Bit Port Sizing                    |                |

| 10.3.1.2            | Global Chip-Select Operation                       |                |

| 10.4                | Chip-Select Registers                              |                |

| 10.4.1              | Chip-Select Module Registers                       |                |

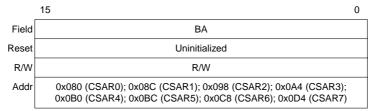

| 10.4.1.1            | Chip-Select Address Registers (CSAR0–CSAR7)        |                |

| 10.4.1.2            | Chip-Select Mask Registers (CSMR0–CSMR7)           |                |

| 10.4.1.3            | Chip-Select Control Registers (CSCR0–CSCR7)        |                |

| 10.4.1.4            | Code Example                                       | 10-9           |

|                     | Chapter 11                                         |                |

|                     | Synchronous/Asynchronous DRAM Controller Module    | )              |

| 11.1                | Overview                                           | 11-1           |

| 11.1.1              | Definitions                                        | 11-2           |

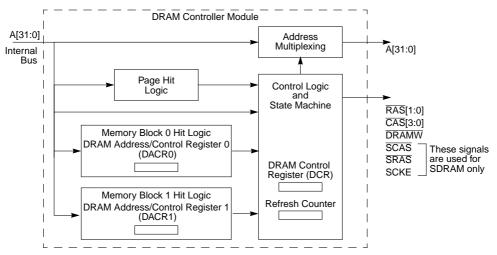

| 11.1.2              | Block Diagram and Major Components                 | 11-2           |

| 11.2                | DRAM Controller Operation                          | 11-3           |

| 11.2.1              | DRAM Controller Registers                          | 11-3           |

| 11.3                | Asynchronous Operation                             |                |

| 11.3.1              | DRAM Controller Signals in Asynchronous Mode       |                |

| 11.3.2              | Asynchronous Register Set                          |                |

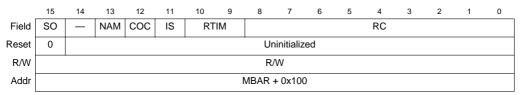

| 11.3.2.1            | DRAM Control Register (DCR) in Asynchronous Mode   |                |

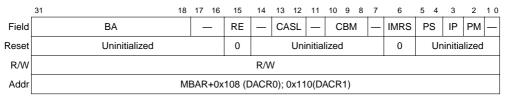

| 11.3.2.2            | DRAM Address and Control Registers (DACR0/DACR1)   |                |

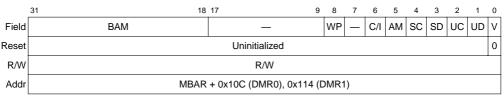

| 11.3.2.3            | DRAM Controller Mask Registers (DMR0/DMR1)         |                |

| 11.3.3              | General Asynchronous Operation Guidelines          |                |

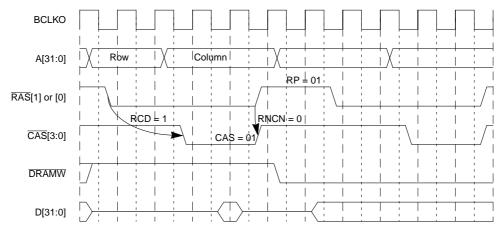

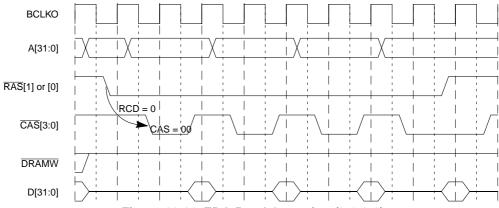

| 11.3.3.1            | Non-Page-Mode Operation                            | 11-11          |

| Paragraph<br>Number | Title                                            | Page<br>Number |

|---------------------|--------------------------------------------------|----------------|

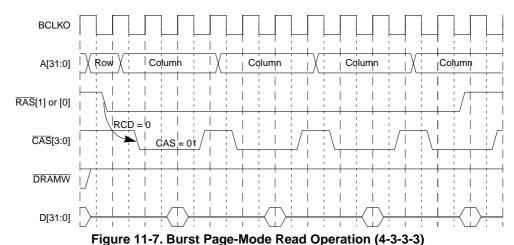

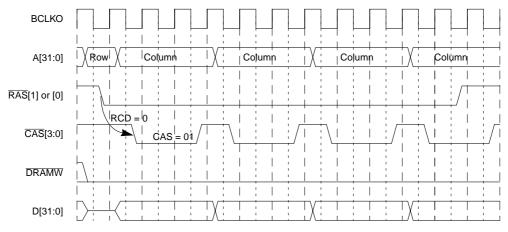

| 11.3.3.2            | Burst Page-Mode Operation                        | 11-12          |

| 11.3.3.3            | Continuous Page Mode                             | 11-13          |

| 11.3.3.4            | Extended Data Out (EDO) Operation                | 11-15          |

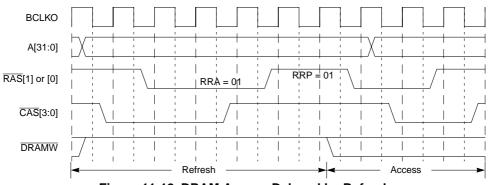

| 11.3.3.5            | Refresh Operation                                | 11-16          |

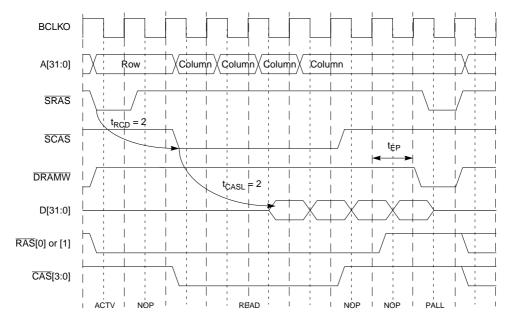

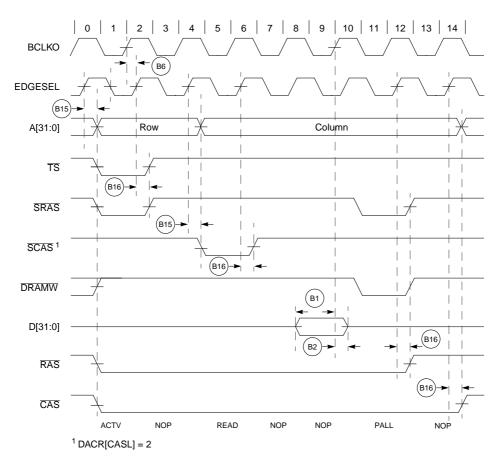

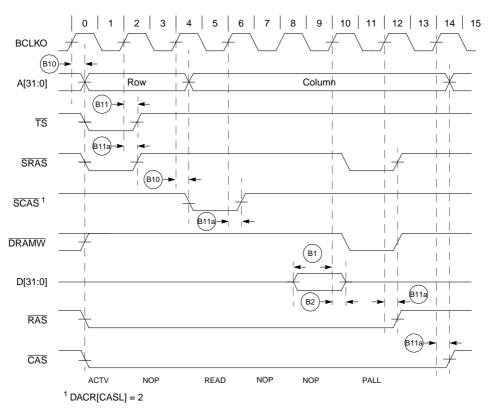

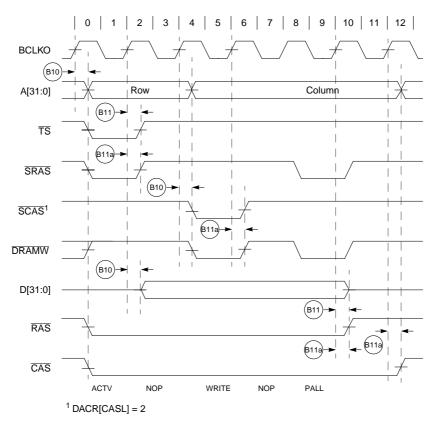

| 11.4                | Synchronous Operation                            | 11-16          |

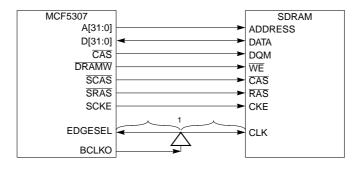

| 11.4.1              | DRAM Controller Signals in Synchronous Mode      | 11-17          |

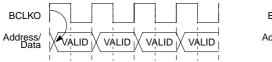

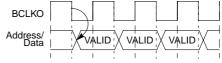

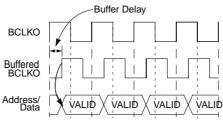

| 11.4.2              | Using Edge Select (EDGESEL)                      | 11-18          |

| 11.4.3              | Synchronous Register Set                         |                |

| 11.4.3.1            | DRAM Control Register (DCR) in Synchronous Mode  | 11-19          |

| 11.4.3.2            | DRAM Address and Control Registers (DACR0/DACR1) | 11.20          |

| 11 122              | in Synchronous Mode                              |                |

| 11.4.3.3            | DRAM Controller Mask Registers (DMR0/DMR1)       |                |

| 11.4.4              | General Synchronous Operation Guidelines         |                |

| 11.4.4.1            | Address Multiplexing                             |                |

| 11.4.4.2            | Interfacing Example                              |                |

| 11.4.4.3            | Burst Page Mode                                  |                |

| 11.4.4.4            | Continuous Page Mode                             |                |

| 11.4.4.5            | Auto-Refresh Operation                           |                |

| 11.4.4.6            | Self-Refresh Operation                           |                |

| 11.4.5              | Initialization Sequence                          |                |

| 11.4.5.1            | Mode Register Settings                           |                |

| 11.5                | SDRAM Example                                    |                |

| 11.5.1              | SDRAM Interface Configuration                    |                |

| 11.5.2              | DCR Initialization                               |                |

| 11.5.3              | DACR Initialization                              |                |

| 11.5.4              | DMR Initialization  Mode Register Initialization |                |

| 11.5.5              | •                                                |                |

| 11.5.6              | Initialization Code                              | 11-39          |

|                     | Part III                                         |                |

|                     | Peripheral Module                                |                |

|                     | Chapter 12                                       |                |

|                     | DMA Controller Module                            |                |

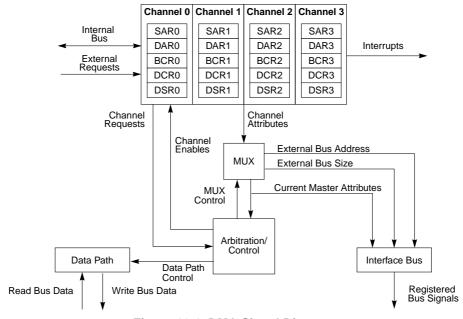

| 12.1                | Overview                                         | 12-1           |

| 12.1.1              | DMA Module Features                              | 12-2           |

| 12.2                | DMA Signal Description                           | 12-2           |

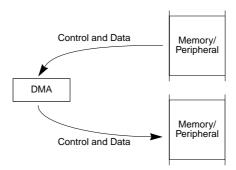

| 12.3                | DMA Transfer Overview                            | 12-3           |

| 12.4                | DMA Controller Module Programming Model          | 12-4           |

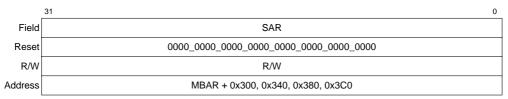

| 12.4.1              | Source Address Registers (SAR0–SAR3)             |                |

| 12.4.2              | Destination Address Registers (DAR0–DAR3)        | 12-7           |

| Paragraph<br>Number | Title                                                | Page<br>Number |

|---------------------|------------------------------------------------------|----------------|

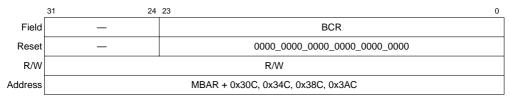

| 12.4.3              | Byte Count Registers (BCR0–BCR3)                     |                |

| 12.4.4              | DMA Control Registers (DCR0–DCR3)                    | 12-8           |

| 12.4.5              | DMA Status Registers (DSR0-DSR3)                     | 12-10          |

| 12.4.6              | DMA Interrupt Vector Registers (DIVR0-DIVR3)         | 12-11          |

| 12.5                | DMA Controller Module Functional Description         | 12-11          |

| 12.5.1              | Transfer Requests (Cycle-Steal and Continuous Modes) | 12-12          |

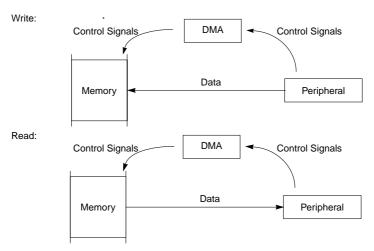

| 12.5.2              | Data Transfer Modes                                  | 12-12          |

| 12.5.2.1            | Dual-Address Transfers                               |                |

| 12.5.2.2            | Single-Address Transfers                             |                |

| 12.5.3              | Channel Initialization and Startup                   | 12-13          |

| 12.5.3.1            | Channel Prioritization                               |                |

| 12.5.3.2            | Programming the DMA Controller Module                |                |

| 12.5.4              | Data Transfer                                        |                |

| 12.5.4.1            | External Request and Acknowledge Operation           |                |

| 12.5.4.2            | Auto-Alignment                                       |                |

| 12.5.4.3            | Bandwidth Control                                    | 12-18          |

| 12.5.5              | Termination                                          | 12-18          |

| 12.1                | Timer Module                                         | 12 1           |

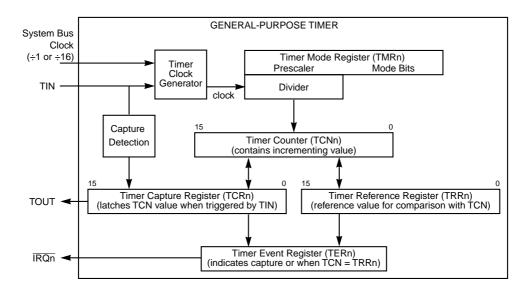

| 13.1<br>13.1.1      | Overview  Key Features                               |                |

| 13.1.1              | General-Purpose Timer Units                          |                |

| 13.3                | General-Purpose Timer Units                          |                |

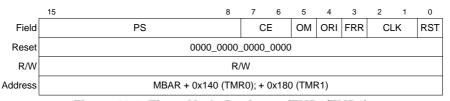

| 13.3.1              | Timer Mode Registers (TMR0/TMR1)                     |                |

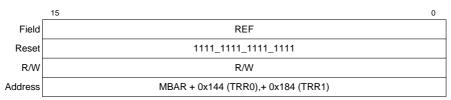

| 13.3.1              | Timer Reference Registers (TRR0/TRR1)                |                |

| 13.3.3              | Timer Capture Registers (TCR0/TCR1)                  |                |

| 13.3.4              | Timer Counters (TCN0/TCN1)                           |                |

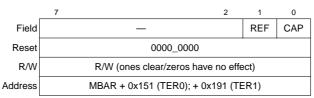

| 13.3.5              | Timer Event Registers (TER0/TER1)                    |                |

| 13.4                | Code Example                                         |                |

| 13.5                | Calculating Time-Out Values                          |                |

| 13.3                | Calculating Time Out Values                          |                |

|                     | Chapter 14<br>UART Modules                           |                |

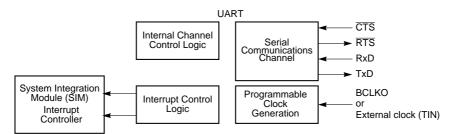

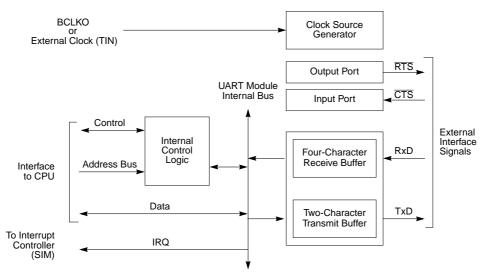

| 14.1                | Overview                                             | 14-1           |

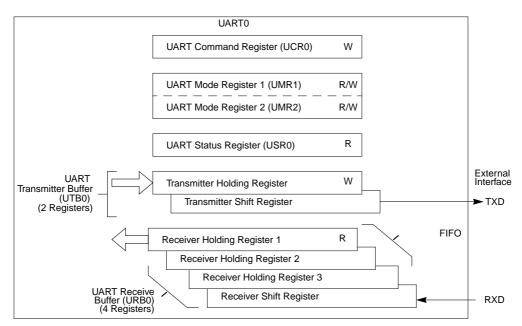

| 14.2                | Serial Module Overview                               | 14-2           |

| 14.3                | Register Descriptions                                |                |

| 14.3.1              | UART Mode Registers 1 (UMR1n)                        |                |

| 14.3.2              | UART Mode Register 2 (UMR2n)                         |                |

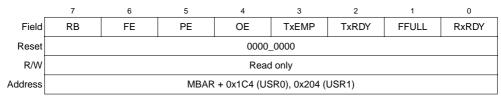

| 14.3.3              | UART Status Registers (USRn)                         | 14-7           |

|                     |                                                      |                |

| Paragraph<br>Number | Title                                              | Page<br>Number |

|---------------------|----------------------------------------------------|----------------|

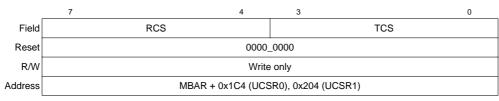

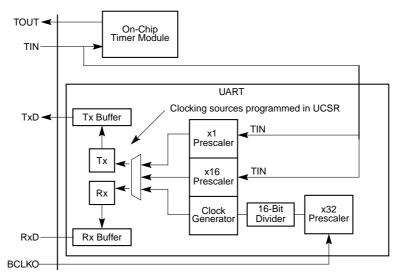

| 14.3.4              | UART Clock-Select Registers (UCSRn)                | 14-8           |

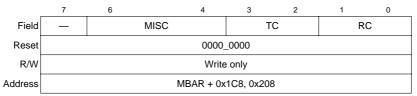

| 14.3.5              | UART Command Registers (UCRn)                      | 14-9           |

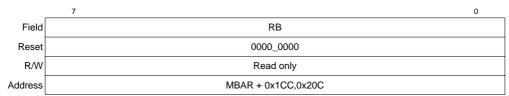

| 14.3.6              | UART Receiver Buffers (URBn)                       | 14-11          |

| 14.3.7              | UART Transmitter Buffers (UTBn)                    | 14-11          |

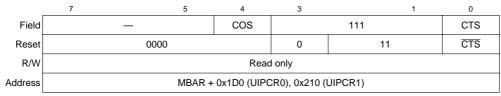

| 14.3.8              | UART Input Port Change Registers (UIPCRn)          | 14-12          |

| 14.3.9              | UART Auxiliary Control Register (UACRn)            | 14-12          |

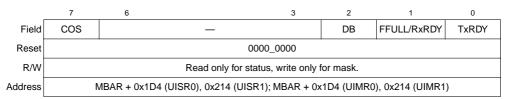

| 14.3.10             | UART Interrupt Status/Mask Registers (UISRn/UIMRn) | 14-13          |

| 14.3.11             | UART Divider Upper/Lower Registers (UDUn/UDLn)     | 14-14          |

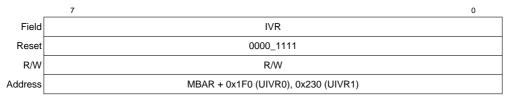

| 14.3.12             | UART Interrupt Vector Register (UIVRn)             | 14-15          |

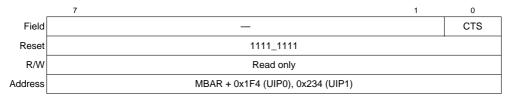

| 14.3.13             | UART Input Port Register (UIPn)                    | 14-15          |

| 14.3.14             | UART Output Port Command Registers (UOP1n/UOP0n)   | 14-15          |

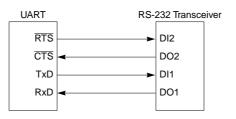

| 14.4                | UART Module Signal Definitions                     | 14-16          |

| 14.5                | Operation                                          | 14-18          |

| 14.5.1              | Transmitter/Receiver Clock Source                  |                |

| 14.5.1.1            | Programmable Divider                               | 14-18          |

| 14.5.1.2            | Calculating Baud Rates                             |                |

| 14.5.1.2.1          | BCLKO Baud Rates                                   | 14-19          |

| 14.5.1.2.2          | External Clock                                     | 14-19          |

| 14.5.2              | Transmitter and Receiver Operating Modes           |                |

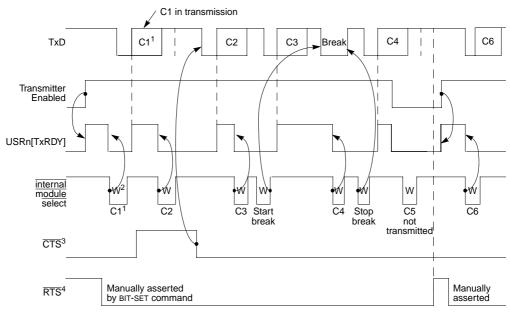

| 14.5.2.1            | Transmitting                                       | 14-21          |

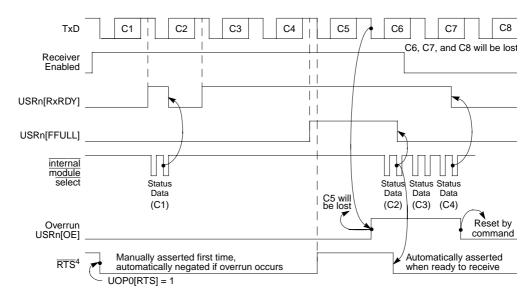

| 14.5.2.2            | Receiver                                           |                |

| 14.5.2.3            | FIFO Stack                                         | 14-24          |

| 14.5.3              | Looping Modes                                      | 14-25          |

| 14.5.3.1            | Automatic Echo Mode                                |                |

| 14.5.3.2            | Local Loop-Back Mode                               |                |

| 14.5.3.3            | Remote Loop-Back Mode                              | 14-26          |

| 14.5.4              | Multidrop Mode                                     |                |

| 14.5.5              | Bus Operation                                      |                |

| 14.5.5.1            | Read Cycles                                        |                |

| 14.5.5.2            | Write Cycles                                       |                |

| 14.5.5.3            | Interrupt Acknowledge Cycles                       |                |

| 14.5.6              | Programming                                        |                |

| 14.5.6.1            | UART Module Initialization Sequence                |                |

|                     | Chapter 15                                         |                |

|                     | Parallel Port (General-Purpose I/O)                |                |

| 15.1                | Parallel Port Operation                            | 15-1           |

| 15.1.1              | Pin Assignment Register (PAR)                      | 15-1           |

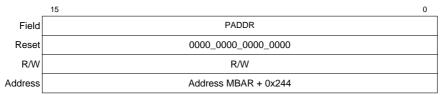

| 15.1.2              | Port A Data Direction Register (PADDR)             | 15-2           |

| 15.1.3              | Port A Data Register (PADAT)                       | 15-2           |

| 15.1.4              | Code Example                                       | 15-3           |

| Paragraph<br>Number | Title                                                           | Page<br>Number |

|---------------------|-----------------------------------------------------------------|----------------|

|                     | Part IV<br>Hardware Interface                                   |                |

|                     | Chapter 16<br>Mechanical Data                                   |                |

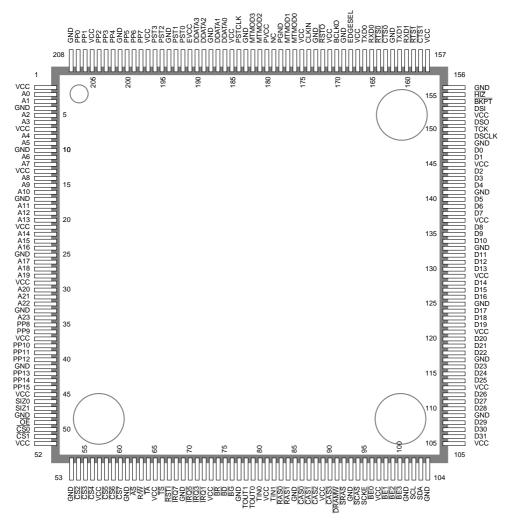

| 16.1                | Package                                                         | 16-1           |

| 16.2                | Pinout                                                          |                |

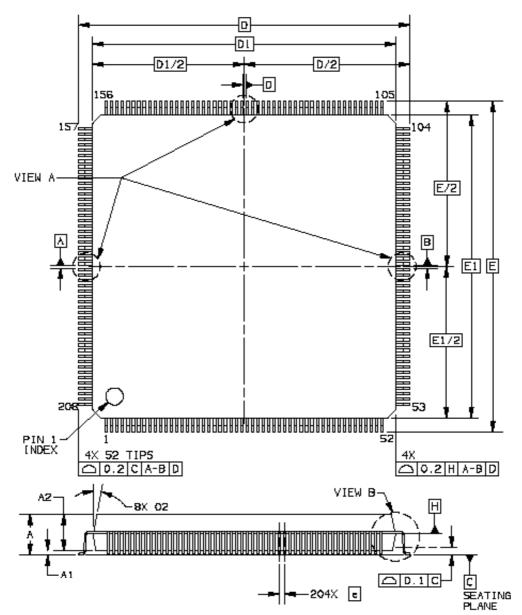

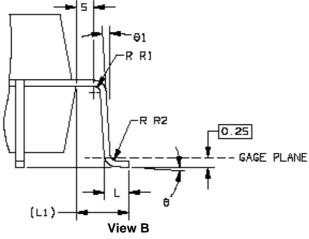

| 16.3                | Mechanical Diagram                                              | 16-8           |

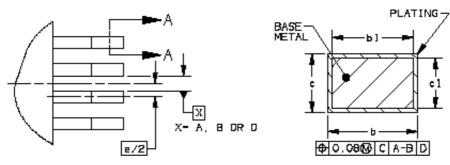

| 16.4                | Case Drawing                                                    | 16-9           |

|                     | Chapter 17                                                      |                |

|                     | Signal Descriptions                                             |                |

| 17.1                | Overview                                                        | 17-1           |

| 17.2                | MCF5307 Bus Signals                                             | 17-7           |

| 17.2.1              | Address Bus                                                     | 17-7           |

| 17.2.1.1            | Address Bus (A[23:0])                                           |                |

| 17.2.1.2            | Address Bus (A[31:24]/PP[15:8])                                 | 17-7           |

| 17.2.2              | Data Bus (D[31:0])                                              |                |

| 17.2.3              | Read/Write $(R/\overline{W})$                                   |                |

| 17.2.4              | Size (SIZ[1:0])                                                 |                |

| 17.2.5              | Transfer Start (TS)                                             |                |

| 17.2.6              | Address Strobe (AS)                                             |                |

| 17.2.7              | Transfer Acknowledge (TA)                                       |                |

| 17.2.8              | Transfer In Progress (TIP/PP7)                                  |                |

| 17.2.9              | Transfer Type (TT[1:0]/PP[1:0])                                 |                |

| 17.2.10             | Transfer Modifier (TM[2:0]/PP[4:2])                             |                |

| 17.3                | Interrupt Control Signals                                       | 17-12          |

| 17.3.1              | Interrupt Request (IRQ1/IRQ2, IRQ3/IRQ6, IRQ5/IRQ4, and IRQ7    |                |

| 17.4<br>17.4.1      | Bus Arbitration Signals                                         |                |

| 17.4.1              | Bus Request (BR)                                                |                |

| 17.4.2              | Bus Driven (BD)                                                 |                |

| 17.4.5              | Clock and Reset Signals.                                        |                |

| 17.5.1              | Reset In (RSTI)                                                 |                |

| 17.5.2              | Clock Input (CLKIN).                                            |                |

| 17.5.3              | Bus Clock Output (BCLKO)                                        |                |

| 17.5.4              | Reset Out (RSTO)                                                |                |

| 17.5.5              | Data/Configuration Pins (D[7:0])                                |                |

| 17.5.5.1            | D[7:5Boot Chip-Select ( $\overline{\text{CS0}}$ ) Configuration |                |

| 17.5.5.2            | D7—Auto Acknowledge Configuration (AA_CONFIG)                   |                |

| Paragraph<br>Number | Title                                                | Page<br>Number |

|---------------------|------------------------------------------------------|----------------|

| 17.5.5.3            | D[6:5]—Port Size Configuration (PS_CONFIG[1:0])      |                |

| 17.5.6              | D4—Address Configuration (ADDR_CONFIG)               | 17-14          |

| 17.5.7              | D[3:2]—Frequency Control PLL (FREQ[1:0]              |                |

| 17.5.8              | D[1:0]—Divide Control PCLK to BCLKO (DIVIDE[1:0])    | 17-15          |

| 17.6                | Chip-Select Module Signals                           | 17-15          |

| 17.6.1              | Chip-Select (CS[7:0])                                | 17-16          |

| 17.6.2              | Byte Enables/Byte Write Enables (BE[3:0]/BWE[3:0])   |                |

| 17.6.3              | Output Enable (OE)                                   | 17-16          |

| 17.7                | DRAM Controller Signals                              |                |

| 17.7.1              | Row Address Strobes (RAS[1:0])                       |                |

| 17.7.2              | Column Address Strobes (CAS[3:0])                    | 17-16          |

| 17.7.3              | DRAM Write (DRAMW)                                   |                |

| 17.7.4              | Synchronous DRAM Column Address Strobe (SCAS)        | 17-17          |

| 17.7.5              | Synchronous DRAM Row Address Strobe (SRAS)           | 17-17          |

| 17.7.6              | Synchronous DRAM Clock Enable (SCKE)                 | 17-17          |

| 17.7.7              | Synchronous Edge Select (EDGESEL)                    | 17-17          |

| 17.8                | DMA Controller Module Signals                        | 17-17          |

| 17.8.1              | DMA Request (DREQ[1:0]/PP[6:5])                      | 17-18          |

| 17.9                | Serial Module Signals                                | 17-18          |

| 17.9.1              | Transmitter Serial Data Output (TxD)                 | 17-18          |

| 17.9.2              | Receiver Serial Data Input (RxD)                     | 17-18          |

| 17.9.3              | Clear to Send (CTS)                                  |                |

| 17.9.4              | Request to Send (RTS)                                | 17-18          |

| 17.10               | Timer Module Signals                                 | 17-18          |

| 17.10.1             | Timer Inputs (TIN[1:0])                              |                |

| 17.10.2             | Timer Outputs (TOUT1, TOUT0)                         | 17-19          |

| 17.11               | Parallel I/O Port (PP[15:0])                         | 17-19          |

| 17.12               | I2C Module Signals                                   | 17-19          |

| 17.12.1             | I2C Serial Clock (SCL)                               |                |

| 17.12.2             | I2C Serial Data (SDA)                                | 17-19          |

| 17.13               | Debug and Test Signals                               |                |

| 17.13.1             | Test Mode (MTMOD[3:0])                               |                |

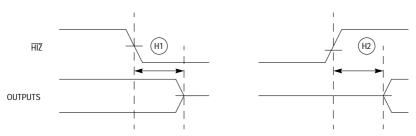

| 17.13.2             | High Impedance (HIZ)                                 |                |

| 17.13.3             | Processor Clock Output (PSTCLK)                      |                |

| 17.13.4             | Debug Data (DDATA[3:0])                              |                |

| 17.13.5             | Processor Status (PST[3:0])                          |                |

| 17.14               | Debug Module/JTAG Signals                            |                |

| 17.14.1             | Test Reset/Development Serial Clock (TRST/DSCLK)     |                |

| 17.14.2             | Test Mode Select/Breakpoint (TMS/BKPT)               |                |

| 17.14.3             | Test Data Input/Development Serial Input (TDI/DSI)   |                |

| 17.14.4             | Test Data Output/Development Serial Output (TDO/DSO) |                |

| 17.14.5             | Test Clock (TCK)                                     | 17-23          |

| Paragraph<br>Number | Title                                                            | Page<br>Number |

|---------------------|------------------------------------------------------------------|----------------|

|                     | Chapter 18                                                       |                |

|                     | Bus Operation                                                    |                |

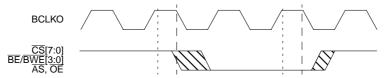

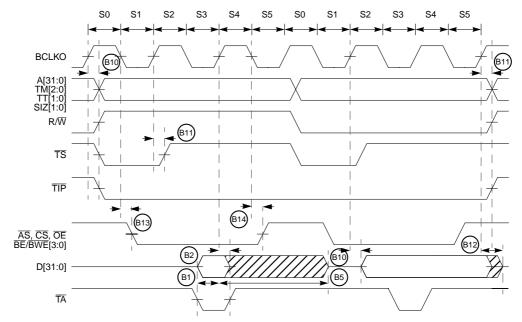

| 18.1                | Features                                                         | 18-1           |

| 18.2                | Bus and Control Signals                                          |                |

| 18.3                | Bus Characteristics                                              |                |

| 18.4                | Data Transfer Operation                                          |                |

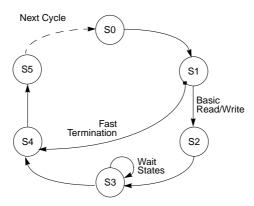

| 18.4.1              | Bus Cycle Execution                                              | 18-4           |

| 18.4.2              | Data Transfer Cycle States                                       | 18-5           |

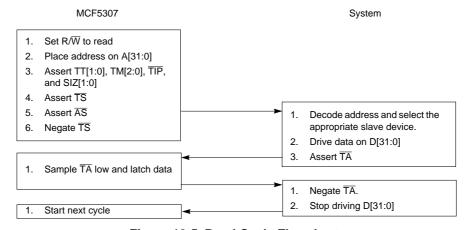

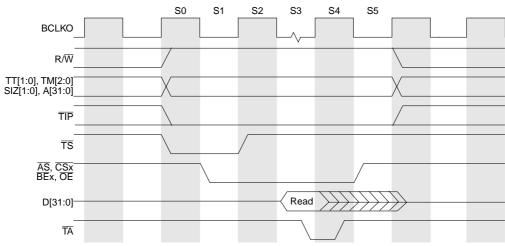

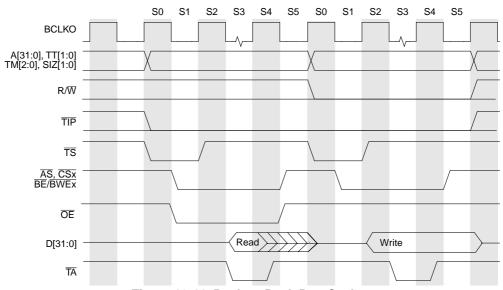

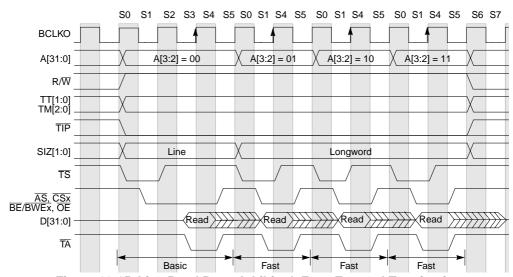

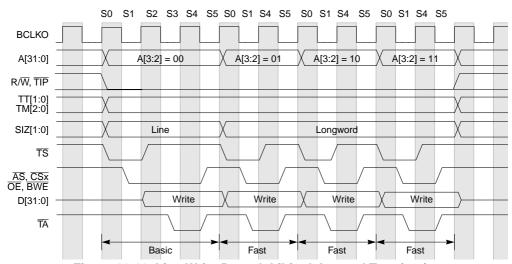

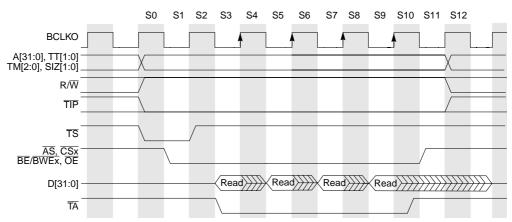

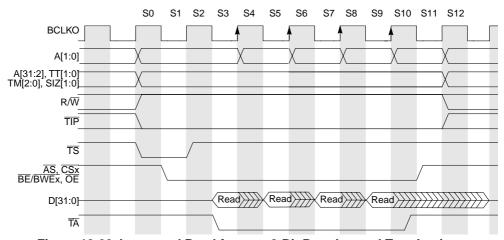

| 18.4.3              | Read Cycle                                                       | 18-7           |

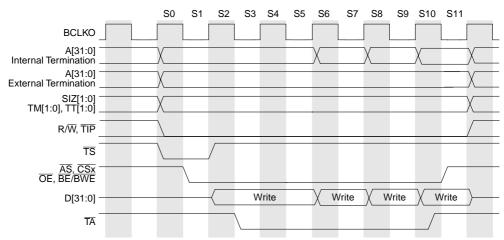

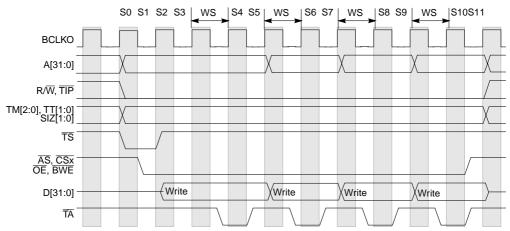

| 18.4.4              | Write Cycle                                                      | 18-8           |

| 18.4.5              | Fast-Termination Cycles                                          | 18-9           |

| 18.4.6              | Back-to-Back Bus Cycles                                          | 18-10          |

| 18.4.7              | Burst Cycles                                                     | 18-11          |

| 18.4.7.1            | Line Transfers                                                   |                |

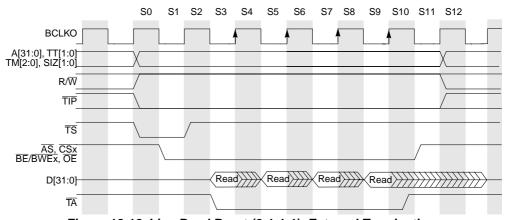

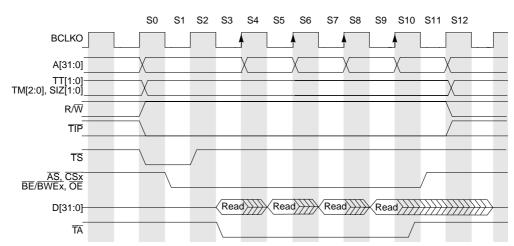

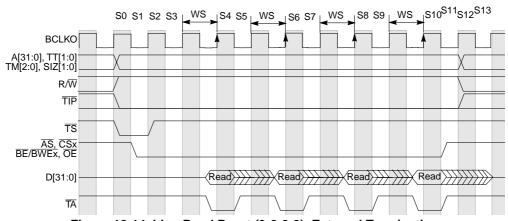

| 18.4.7.2            | Line Read Bus Cycles                                             |                |

| 18.4.7.3            | Line Write Bus Cycles                                            |                |

| 18.4.7.4            | Transfers Using Mixed Port Sizes                                 |                |

| 18.5                | Misaligned Operands                                              |                |

| 18.6                | Bus Errors                                                       |                |

| 18.7                | Interrupt Exceptions                                             |                |

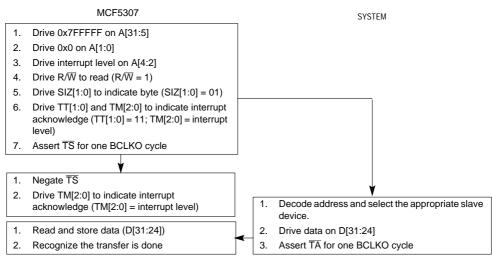

| 18.7.1              | Level 7 Interrupts                                               |                |

| 18.7.2              | Interrupt-Acknowledge Cycle                                      |                |

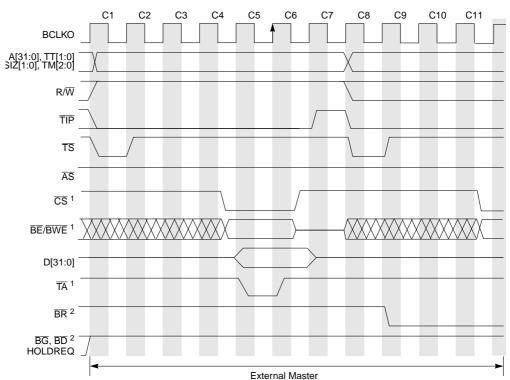

| 18.8                | Bus Arbitration                                                  |                |

| 18.8.1              | Bus Arbitration Signals                                          |                |

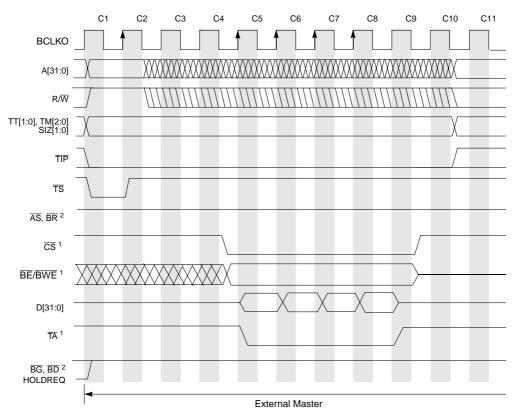

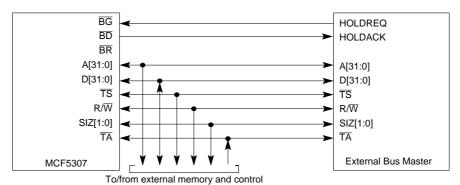

| 18.9                | General Operation of External Master Transfers                   |                |

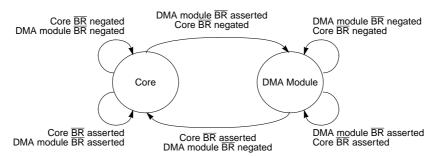

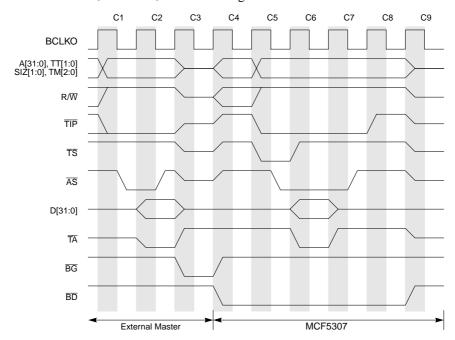

| 18.9.1              | Two-Device Bus Arbitration Protocol (Two-Wire Mode)              |                |

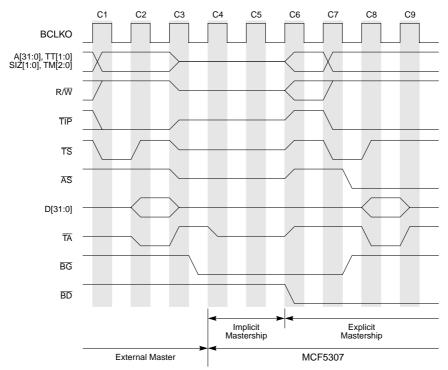

| 18.9.2              | Multiple External Bus Device Arbitration Protocol (Three-Wire Mo |                |

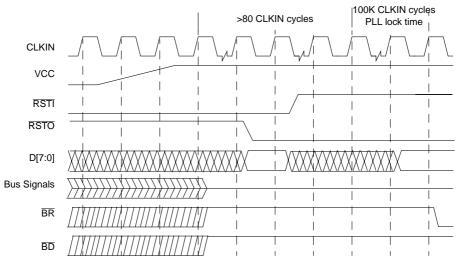

| 18.10               | Reset Operation                                                  |                |

| 18.10.1             | Master Reset                                                     |                |

| 18.10.2             | Software Watchdog Reset                                          | 18-35          |

|                     | Chapter 19                                                       |                |

|                     | IEEE 1149.1 Test Access Port (JTAG)                              |                |

| 10.1                | Overminu                                                         | 10.1           |

| 19.1                | Overview                                                         |                |

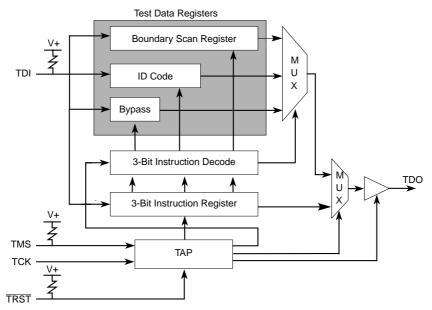

| 19.2<br>19.3        | JTAG Signal Descriptions                                         |                |

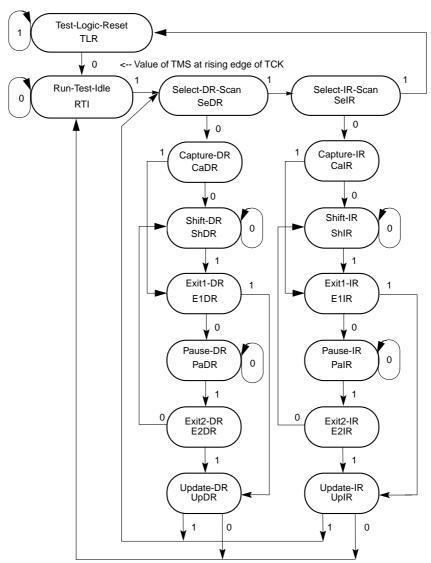

|                     | TAP Controller                                                   |                |

| 19.4                | JTAG Register Descriptions                                       |                |

| 19.4.1<br>19.4.2    | IDCODE Register                                                  |                |

| 19.4.2              | JTAG Boundary-Scan Register                                      |                |

| 17.4.3              | JIAO Doundary-Scan Register                                      | 17-/           |

| Paragraph<br>Number | Title                                                     | Page<br>Number |

|---------------------|-----------------------------------------------------------|----------------|

| 19.4.4              | JTAG Bypass Register                                      | 19-10          |

| 19.5                | Restrictions                                              |                |

| 19.6                | Disabling IEEE Standard 1149.1 Operation                  | 19-11          |

| 19.7                | Obtaining the IEEE Standard 1149.1                        |                |

|                     | Chapter 20 Electrical Specifications                      |                |

| 20.1                | General Parameters                                        | 20-1           |

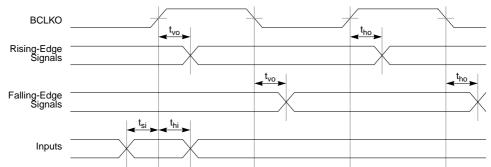

| 20.2                | Clock Timing Specifications                               | 20-2           |

| 20.3                | Input/Output AC Timing Specifications                     |                |

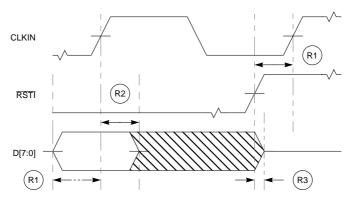

| 20.4                | Reset Timing Specifications                               |                |

| 20.5                | Debug AC Timing Specifications                            |                |

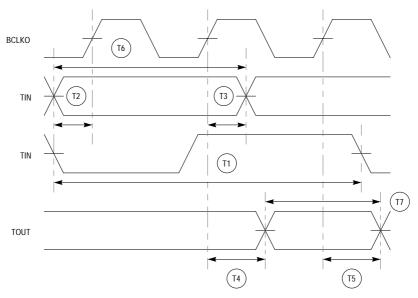

| 20.6                | Timer Module AC Timing Specifications                     |                |

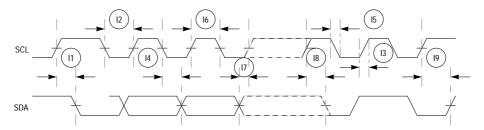

| 20.7                | I <sup>2</sup> C Input/Output Timing Specifications       | 20-15          |

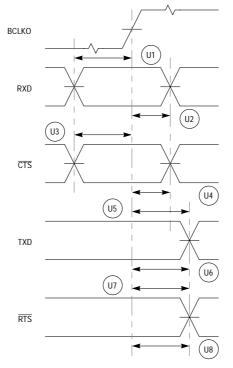

| 20.8                | UART Module AC Timing Specifications                      |                |

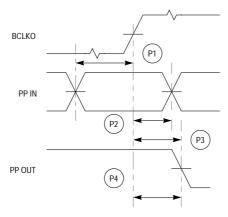

| 20.9                | Parallel Port (General-Purpose I/O) Timing Specifications | 20-18          |

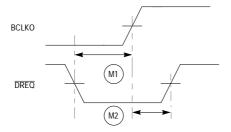

| 20.10               | DMA Timing Specifications                                 | 20-19          |

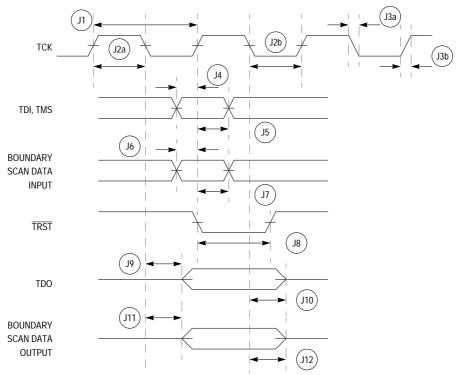

| 20.11               | IEEE 1149.1 (JTAG) AC Timing Specifications               | 20-20          |

| Figure<br>Numbe | I ITIO                                                             | Page<br>Number |

|-----------------|--------------------------------------------------------------------|----------------|

|                 |                                                                    |                |

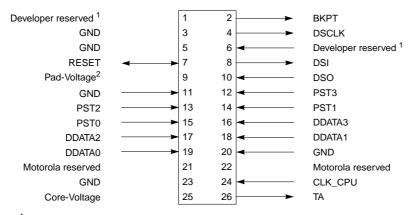

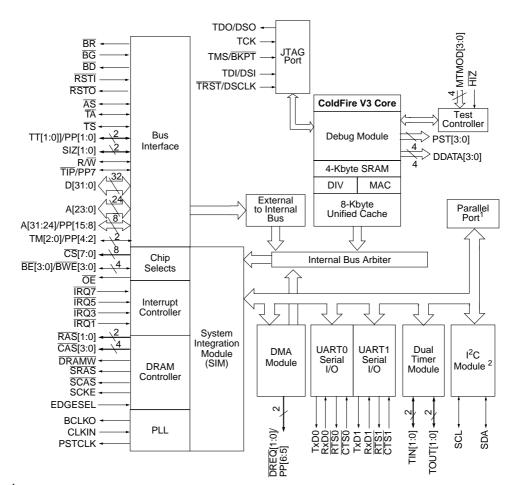

| 1-1             | MCF5307 Block Diagram                                              |                |

| 1-2             | UART Module Block Diagram                                          | 1-9            |

| 1-3             | PLL Module                                                         |                |

| 1-4             | ColdFire MCF5307 Programming Model                                 | 1-13           |

| 2-1             | ColdFire Enhanced Pipeline                                         |                |

| 2-2             | ColdFire Multiply-Accumulate Functionality Diagram                 | 2-25           |

| 2-3             | ColdFire Programming Model                                         | 2-27           |

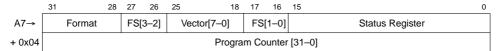

| 2-5             | Status Register (SR)                                               | 2-30           |

| 2-6             | Vector Base Register (VBR)                                         | 2-30           |

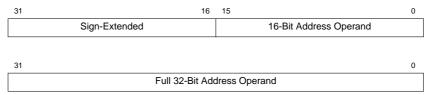

| 2-7             | Organization of Integer Data Formats in Data Registers             | 2-32           |

| 2-8             | Organization of Integer Data Formats in Address Registers          | 2-32           |

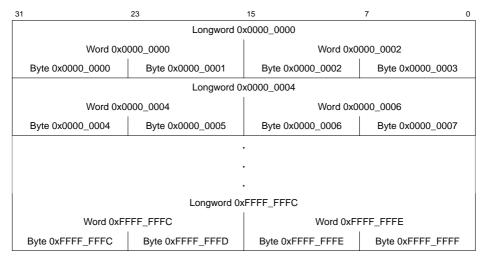

| 2-9             | Memory Operand Addressing                                          | 2-33           |

| 2-10            | Exception Stack Frame Form                                         | 2-49           |

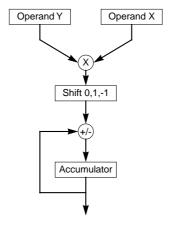

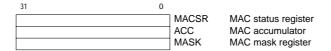

| 3-1             | ColdFire MAC Multiplication and Accumulation                       | 3-2            |

| 3-2             | MAC Programming Model                                              | 3-2            |

| 4-1             | SRAM Base Address Register (RAMBAR)                                | 4-3            |

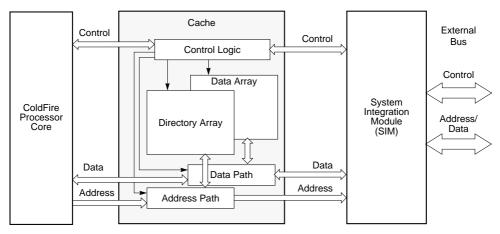

| 4-2             | Unified Cache Organization                                         |                |

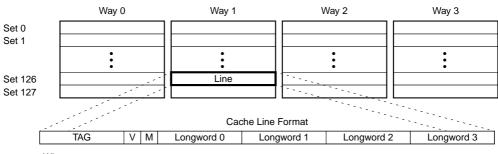

| 4-3             | Cache Organization and Line Format                                 |                |

| 4-4             | Cache—A: at Reset, B: after Invalidation, C and D: Loading Pattern |                |

| 4-5             | Caching Operation                                                  | 4-11           |

| 4-6             | Write-Miss in Copyback Mode                                        |                |

| 4-7             | Cache Locking                                                      |                |

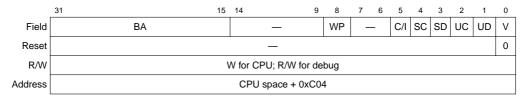

| 4-8             | Cache Control Register (CACR)                                      |                |

| 4-9             | Access Control Register Format (ACRn)                              |                |

| 4-10            | An Format                                                          |                |

| 4-11            | Cache Line State Diagram—Copyback Mode                             |                |

| 4-12            | Cache Line State Diagram—Write-Through Mode                        |                |

| 5-1             | Processor/Debug Module Interface                                   |                |

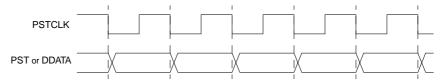

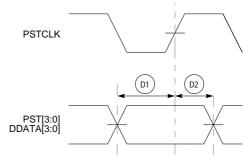

| 5-2             | PSTCLK Timing                                                      |                |

| 5-3             | Example JMP Instruction Output on PST/DDATA                        |                |

| 5-4             | Debug Programming Model                                            |                |

| 5-5             | Address Attribute Trigger Register (AATR)                          |                |

| 5-6             | Address Breakpoint Registers (ABLR, ABHR)                          |                |

| 5-7             | BDM Address Attribute Register (BAAR)                              |                |

| 5-8             | Configuration/Status Register (CSR)                                |                |

| 5-9             | Data Breakpoint/Mask Registers (DBR and DBMR)                      |                |

| 5 /             | Zam Zamponia rausi registera (Zbri una Dbritt)                     |                |

| Figure<br>Number | Title                                                     | Page<br>Number |

|------------------|-----------------------------------------------------------|----------------|

| 5-10             | Program Counter Breakpoint Register (PBR)                 | 5-14           |

| 5-11             | Program Counter Breakpoint Mask Register (PBMR)           |                |

| 5-12             | Trigger Definition Register (TDR)                         | 5-15           |

| 5-13             | BDM Serial Interface Timing                               |                |

| 5-14             | Receive BDM Packet                                        | 5-19           |

| 5-15             | Transmit BDM Packet                                       | 5-19           |

| 5-16             | BDM Command Format                                        | 5-21           |

| 5-17             | Command Sequence Diagram                                  | 5-22           |

| 5-19             | RAREG/RDREG Command Sequence                              |                |

| 5-18             | RAREG/RDREG Command Format                                | 5-24           |

| 5-21             | WAREG/WDREG Command Sequence                              | 5-25           |

| 5-20             | WAREG/WDREG Command Format                                | 5-25           |

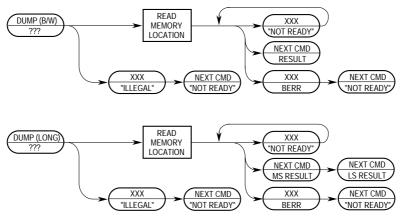

| 5-23             | READ Command Sequence                                     | 5-26           |

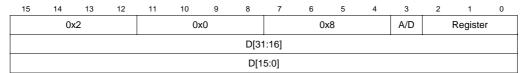

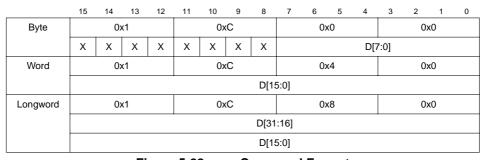

| 5-22             | READ Command/Result Formats                               | 5-26           |

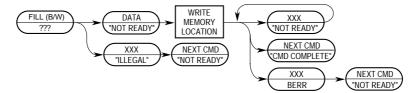

| 5-24             | WRITE Command Format                                      | 5-27           |

| 5-25             | WRITE Command Sequence                                    | 5-28           |

| 5-26             | DUMP Command/Result Formats                               | 5-29           |

| 5-27             | DUMP Command Sequence                                     | 5-30           |

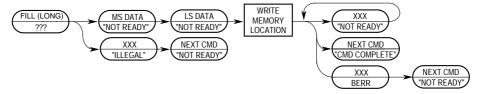

| 5-28             | FILL Command Format                                       | 5-31           |

| 5-29             | FILL Command Sequence                                     | 5-32           |

| 5-31             | GO Command Sequence                                       | 5-33           |

| 5-30             | GO Command Format                                         | 5-33           |

| 5-33             | NOP Command Sequence                                      |                |

| 5-32             | NOP Command Format                                        | 5-34           |

| 5-35             | SYNC_PC Command Sequence                                  | 5-35           |

| 5-34             | SYNC_PC Command Format                                    |                |

| 5-37             | RCREG Command Sequence                                    | 5-36           |

| 5-36             | RCREG Command/Result Formats                              |                |

| 5-39             | WCREG Command Sequence                                    | 5-37           |

| 5-38             | WCREG Command/Result Formats                              | 5-37           |

| 5-41             | RDMREG Command Sequence                                   | 5-38           |

| 5-40             | RDMREG bdm Command/Result Formats                         | 5-38           |

| 5-43             | WDMREG Command Sequence                                   | 5-39           |

| 5-42             | WDMREG BDM Command Format                                 | 5-39           |

| 5-44             | Recommended BDM Connector                                 | 5-42           |

| 6-1              | SIM Block Diagram                                         | 6-1            |

| 6-2              | Module Base Address Register (MBAR)                       | 6-4            |

| 6-3              | Reset Status Register (RSR)                               | 6-5            |

| 6-4              | MCF5307 Embedded System Recovery from Unterminated Access | 6-7            |

| 6-5              | System Protection Control Register (SYPCR)                |                |

| 6-6              | Software Watchdog Interrupt Vector Register (SWIVR)       | 6-9            |

| 6-7              | Software Watchdog Service Register (SWSR)                 |                |

| 6-8              | Pin Assignment Register (PAR)                             | 6-10           |

| Figure<br>Number | Title                                                              | Page<br>Number |

|------------------|--------------------------------------------------------------------|----------------|

| 6-9              | Default Bus Master Register (MPARK)                                |                |

| 6-10             | Round Robin Arbitration (PARK = 00)                                |                |

| 6-11             | Park on Master Core Priority (PARK = 01)                           |                |

| 6-12             | Park on DMA Module Priority (PARK = 10)                            |                |

| 6-13             | Park on Current Master Priority (PARK = 01)                        |                |

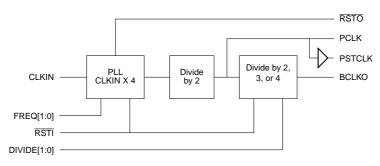

| 7-1              | PLL Module Block Diagram                                           |                |

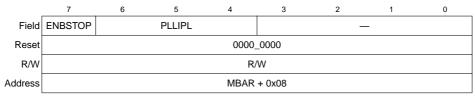

| 7-2              | PLL Control Register (PLLCR)                                       |                |

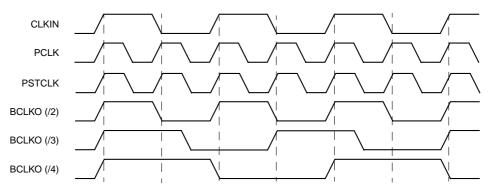

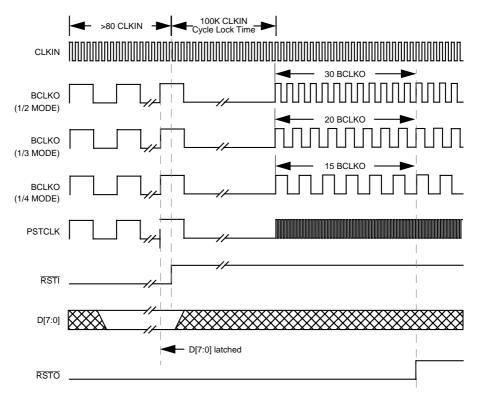

| 7-3              | CLKIN, PCLK, PSTCLK, and BCLKO Timing                              | 7-5            |

| 7-4              | Reset and Initialization Timing.                                   |                |

| 7-5              | PLL Power Supply Filter Circuit                                    |                |

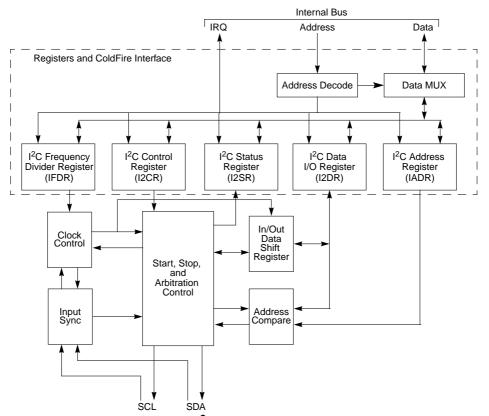

| 8-1              | I <sup>2</sup> C Module Block Diagram                              |                |

| 8-2              | I <sup>2</sup> C Standard Communication Protocol                   |                |

| 8-3              | Repeated START                                                     |                |

| 8-4              | Synchronized Clock SCL                                             |                |

| 8-5              | I <sup>2</sup> C Address Register (IADR)                           | 8-6            |

| 8-6              | I <sup>2</sup> C Frequency Divider Register (IFDR)                 |                |

| 8-7              | I <sup>2</sup> C Control Register (I2CR)                           | 8-8            |

| 8-8              | I <sup>2</sup> CR Status Register (I2SR)                           |                |

| 8-9              | I <sup>2</sup> C Data I/O Register (I2DR)                          | 8-10           |

| 8-10             | Flow-Chart of Typical I <sup>2</sup> C Interrupt Routine           |                |

| 9-1              | Interrupt Controller Block Diagram                                 |                |

| 9-2              | Interrupt Control Registers (ICR0–ICR9)                            |                |

| 9-3              | Autovector Register (AVR)                                          |                |

| 9-4              | Interrupt Pending Register (IPR) and Interrupt Mask Register (IMR) |                |

| 9-5              | Interrupt Port Assignment Register (IRQPAR)                        |                |

| 10-1             | Connections for External Memory Port Sizes                         |                |

| 10-2             | Chip Select Address Registers (CSAR0–CSAR7)                        |                |

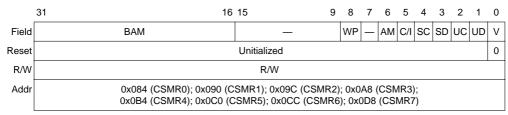

| 10-3             | Chip Select Mask Registers (CSMRn)                                 |                |

| 10-4             | Chip-Select Control Registers (CSCR0–CSCR7)                        |                |

| 11-1             | Asynchronous/Synchronous DRAM Controller Block Diagram             |                |

| 11-2             | DRAM Control Register (DCR) (Asynchronous Mode)                    |                |

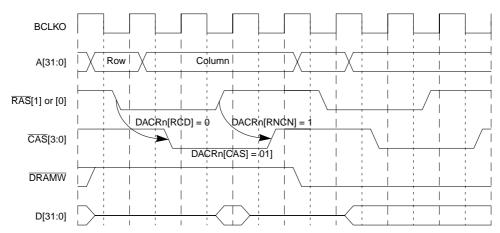

| 11-3             | DRAM Address and Control Registers (DACR0/DACR1)                   |                |

| 11-4             | DRAM Controller Mask Registers (DMR0 and DMR1)                     |                |

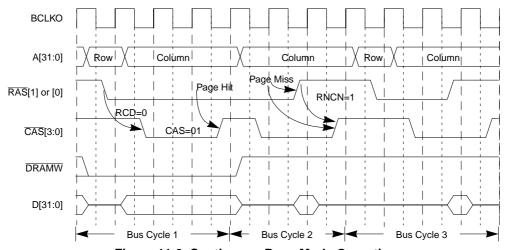

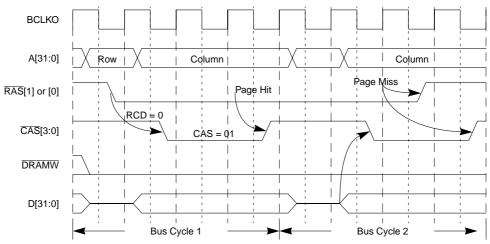

| 11-5             | Basic Non-Page-Mode Operation RCD = 0, RNCN = 1 (4-4-4-4)          |                |

| 11-6             | Basic Non-Page-Mode Operation RCD = 1, RNCN = 0 (5-5-5-5)          |                |

| 11-7             | Burst Page-Mode Read Operation (4-3-3-3)                           |                |

| 11-8             | Burst Page-Mode Write Operation (4-3-3-3)                          |                |

| 11-9             | Continuous Page-Mode Operation                                     |                |

| 11-10            | Write Hit in Continuous Page Mode                                  |                |

| 11-11            | EDO Read Operation (3-2-2-2)                                       |                |

| 11-12            | DRAM Access Delayed by Refresh                                     |                |

| 11-13            | MCF5307 SDRAM Interface                                            |                |

| 11-14            | Using EDGESEL to Change Signal Timing                              | 11-19          |

| Figure<br>Number | Title                                                          | Page<br>Number |

|------------------|----------------------------------------------------------------|----------------|

| 11-15            | DRAM Control Register (DCR) (Synchronous Mode)                 | 11-19          |

| 11-16            | DACR0 and DACR1 Registers (Synchronous Mode)                   |                |

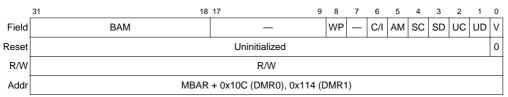

| 11-17            | DRAM Controller Mask Registers (DMR0 and DMR1)                 | 11-22          |

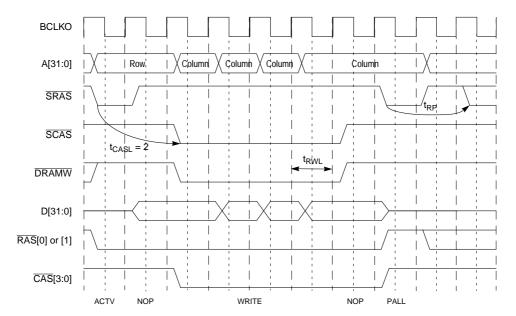

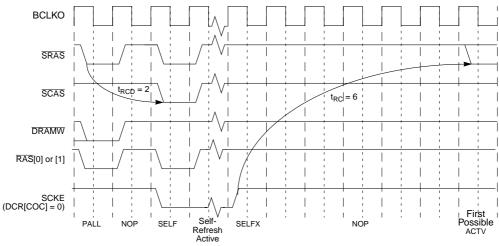

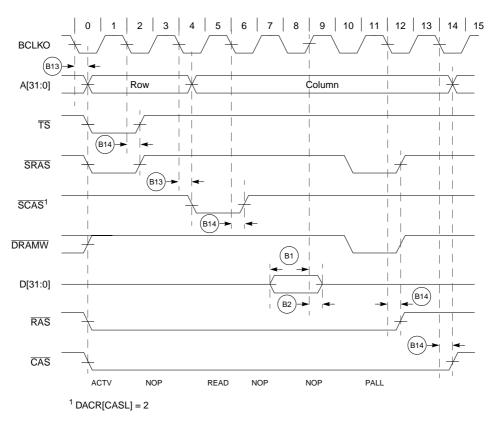

| 11-18            | Burst Read SDRAM Access                                        |                |

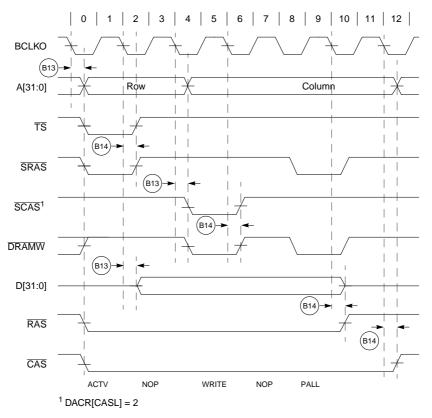

| 11-19            | Burst Write SDRAM Access                                       |                |

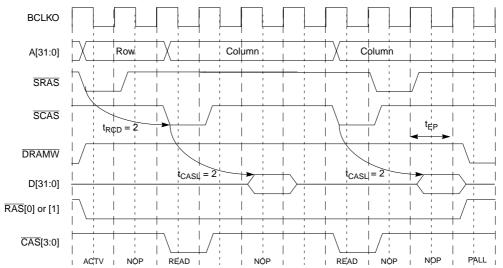

| 11-20            | Synchronous, Continuous Page-Mode Access—Consecutive Reads     | 11-30          |

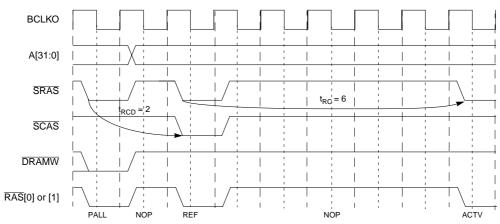

| 11-21            | Synchronous, Continuous Page-Mode Access—Read after Write      | 11-31          |

| 11-22            | Auto-Refresh Operation                                         | 11-32          |

| 11-23            | Self-Refresh Operation                                         |                |

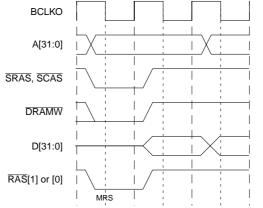

| 11-24            | Mode Register Set (mrs) Command                                | 11-34          |

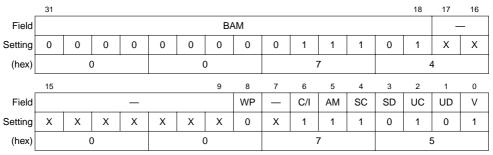

| 11-25            | Initialization Values for DCR                                  | 11-35          |

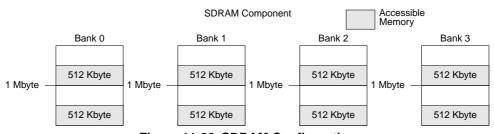

| 11-26            | SDRAM Configuration                                            |                |

| 11-27            | DACR Register Configuration                                    | 11-36          |

| 11-28            | DMR0 Register                                                  |                |

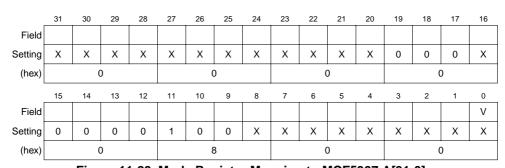

| 11-29            | Mode Register Mapping to MCF5307 A[31:0]                       |                |

| 12-1             | DMA Signal Diagram                                             | 12-1           |

| 12-2             | Dual-Address Transfer                                          | 12-3           |

| 12-3             | Single-Address Transfers                                       |                |

| 12-4             | Source Address Registers (SARn)                                | 12-6           |

| 12-5             | Destination Address Registers (DARn)                           |                |

| 12-6             | Byte Count Registers (BCRn)—BCR24BIT = 1                       |                |

| 12-7             | BCRn—BCR24BIT = 0                                              | 12-8           |

| 12-8             | DMA Control Registers (DCRn)                                   | 12-8           |

| 12-9             | DMA Status Registers (DSRn)                                    |                |

| 12-10            | DMA Interrupt Vector Registers (DIVRn)                         |                |

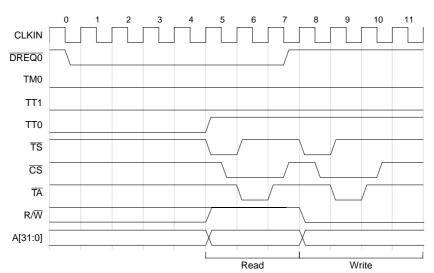

| 12-11            | DREQ Timing Constraints, Dual-Address DMA Transfer             |                |

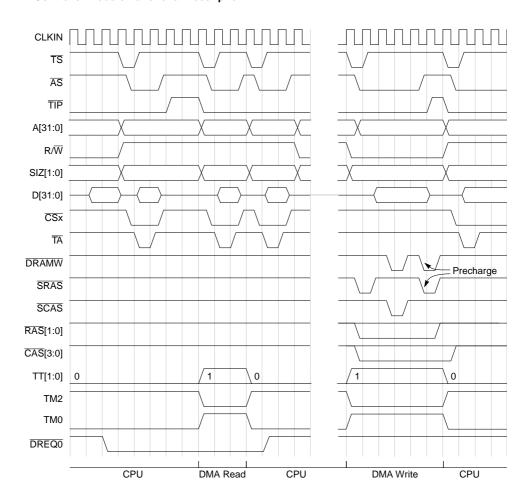

| 12-12            | Dual-Address, Peripheral-to-SDRAM, Lower-Priority DMA Transfer |                |

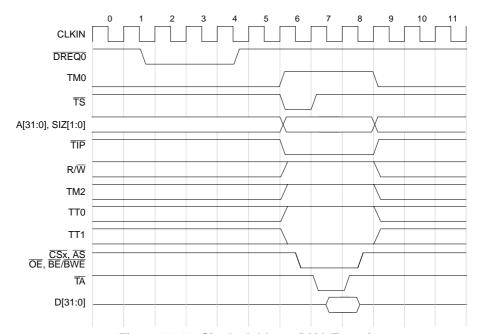

| 12-13            | Single-Address DMA Transfer                                    | 12-17          |

| 13-1             | Timer Block Diagram                                            |                |

| 13-2             | Timer Mode Registers (TMR0/TMR1)                               |                |

| 13-3             | Timer Reference Registers (TRR0/TRR1)                          |                |

| 13-4             | Timer Capture Register (TCR0/TCR1)                             |                |

| 13-5             | Timer Counters (TCN0/TCN1)                                     |                |

| 13-6             | Timer Event Registers (TER0/TER1)                              |                |

| 14-1             | Simplified Block Diagram                                       |                |

| 14-2             | UART Mode Registers 1 (UMR1n)                                  | 14-5           |

| 14-3             | UART Mode Register 2 (UMR2n)                                   | 14-6           |

| 14-4             | UART Status Register (USRn)                                    |                |

| 14-5             | UART Clock-Select Register (UCSRn)                             | 14-8           |

| 14-6             | UART Command Register (UCRn)                                   |                |

| 14-7             | UART Receiver Buffer (URB0)                                    |                |

| 14-8             | UART Transmitter Buffer (UTB0)                                 |                |

| 14-9             | UART Input Port Change Register (UIPCRn)                       | 14-12          |

| Figure<br>Number | Title                                                                | Page<br>Number |

|------------------|----------------------------------------------------------------------|----------------|

| 14-10            | UART Auxiliary Control Register (UACRn)                              | 14-13          |

| 14-11            | UART Interrupt Status/Mask Registers (UISRn/UIMRn)                   |                |

| 14-12            | UART Divider Upper Register (UDUn)                                   | 14-14          |

| 14-13            | UART Divider Lower Register (UDLn)                                   |                |

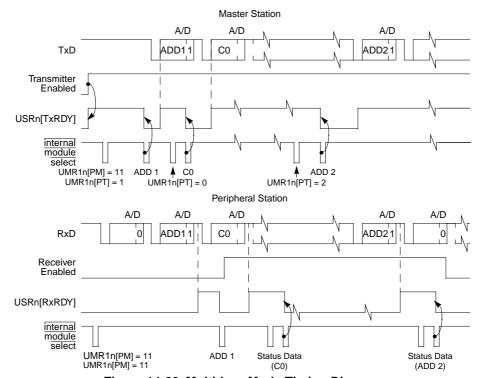

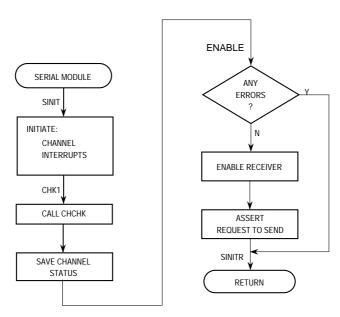

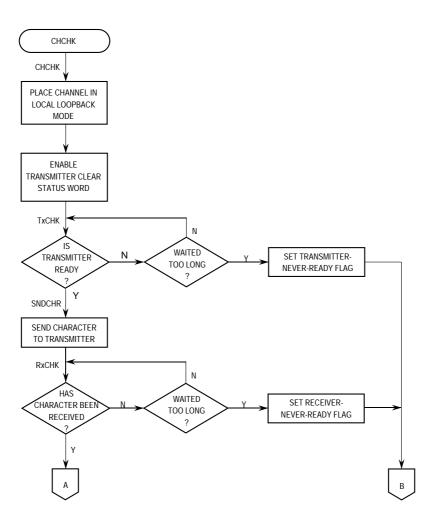

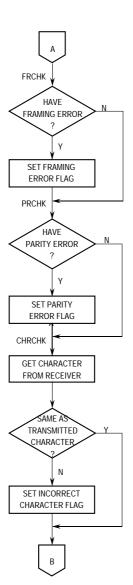

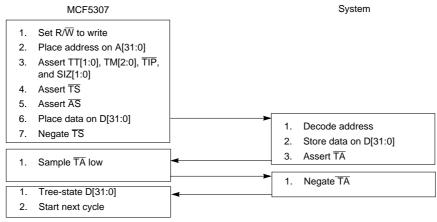

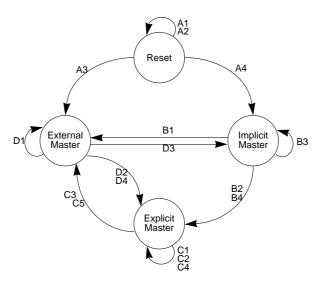

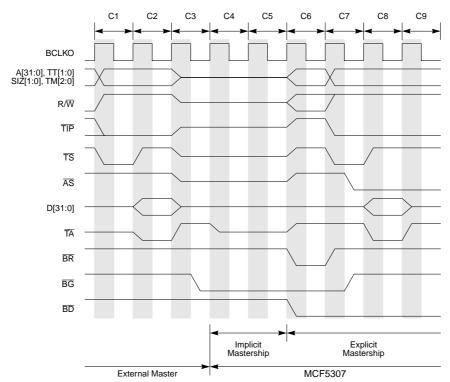

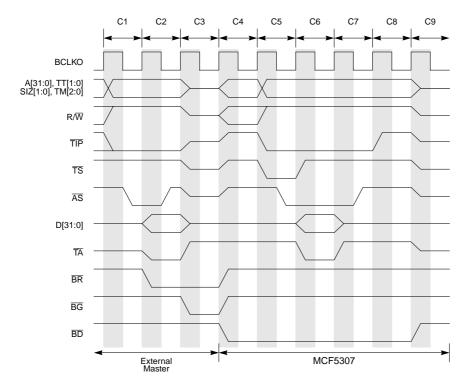

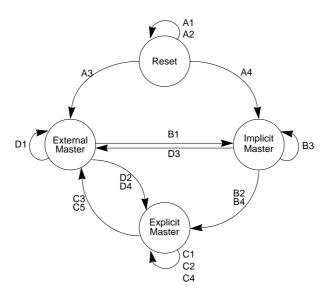

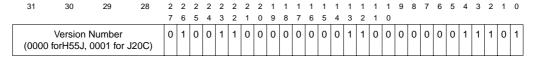

| 14-14            | UART Interrupt Vector Register (UIVRn)                               | 14-15          |