# MF4SAM3X SDS

### MIFARE SAM AV3 secure access module

Rev. 3.2 — 5 March 2024

Product short data sheet

## 1 General description

The NXP MIFARE SAM AV3 secure hardware solution is the ideal add-on for reader devices offering additional security services. Supporting DES, TDEA, AES and RSA capabilities, it offers secure storage and secure communication in various infrastructures.

Unlike other products in the field, MIFARE SAM AV3 has proven interoperability with all broad card and RFID product portfolio of NXP, (MIFARE, NTAG DNA, ICODE DNA, UCODE DNA and SmartMX product families), making it the most versatile and secure SAM solution on the market today.

The MIFARE SAM AV3 is built on the SmartMX2 P60 secure smart card controller with CC EAL6+ certification of NXP. Its software implementation is evaluated and composite certified by the MIFARE Security Evaluation Scheme. Similar to the hardware CC evaluation, the MIFARE Scheme also evaluates against high attack potential. Hence, systems using MIFARE SAM AV3 are reassured with the state-of-the-art security measures adopted by the industry.

### **Programmable Logic**

The MIFARE SAM AV3 is equipped with a new Programmable Logic functionality which allows customers to flexibly create their business logic on the SAM. This new functionality opens up many new possibilities with the creation of project-specific customization such as a new key diversification algorithm, a new secure messaging, or a new secure storage.

#### X-mode communication

When used in combination with a reader IC supporting innovative "X" features, MIFARE SAM AV3 provides a significant boost in performance to the reader along with faster communication between reader and module. The "X" feature is a new way to use the SAM in a system, with SAM connected to the microcontroller and the reader IC simultaneously.

#### Secured communication

The connection between the SAM and the reader is performed using security protocols based on either AES symmetric cryptography or PKI RSA asymmetric cryptography. The protocols comply with the state-of-art standards and thereby ensure data confidentiality and integrity.

### 2 Features and benefits

#### 2.1 Cryptography

- Supports MIFARE Crypto1, DES, TDEA (112 bits and 168 bits), AES (128 bits, 192 bits and 256 bits), RSA (up to 2048 bits) and ECC (up to 256 bits) cryptography

- · Supported NXP products:

- MIFARE DESFire EV3, EV2, EV1, and Light

- MIFARE Plus EV2, EV1, X, S, and SE

- MIFARE Classic EV1

- MIFARE Ultralight AES, C and EV1

- NTAG, ICODE, and UCODE DNA

- · Secure storage and updating of keys

- 128 key entries for symmetric cryptography

- 3 RSA key entries for asymmetric cryptography

- 8 ECC public key entries for signature verification

- 4 ECC curves entries

- 48 EMV CA public key entries (supports 8 RID minimum)

- SHA-1, SHA-224 and SHA-256 hashing computation

- TDEA and AES-based key diversification

- · Generic cryptography commands for user-defined schemes

- · Supports EMVCo terminal functionality

- True random number generator (TRNG) compliant to AIS-31

#### 2.2 Communication

- ISO/IEC 7816 (part 2 and 3) contact interface

- Support Class A, B and C operating condition

- Support ISO/IEC 7816 baud rates

- Support high-speed baud rates up to 1.5 Mbit/s

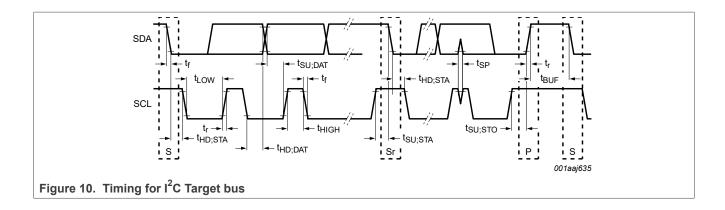

- Optional I<sup>2</sup>C Target mode host interface (only available on HVQFN package)

- Communication protocol compliant with ISO/IEC 7816-3 T=1 protocol

- Up to four logical channels; simultaneous multiple card support

- Support for MIFARE DESFire and MIFARE Plus authentication (with related secure messaging and session key generation)

- Secure Host to SAM and back end to SAM communication with symmetric cryptography including 3-pass authentication for confidentiality and integrity

- Secure Host to SAM and back end to SAM communication with RSA-based cryptography for key updating

- X-mode direct interface with NXP's contactless reader ICs (RC663, RC52x, PN512)

# 2.3 Programmable logic (restricted feature) <sup>2</sup>

- Up to 32 kB of code and data in EEPROM for user customized functionality

- 1 kB of RAM for user's dynamic data

- · Internal Host access to all MIFARE SAM AV3 commands

## 2.4 Security evaluation and certification

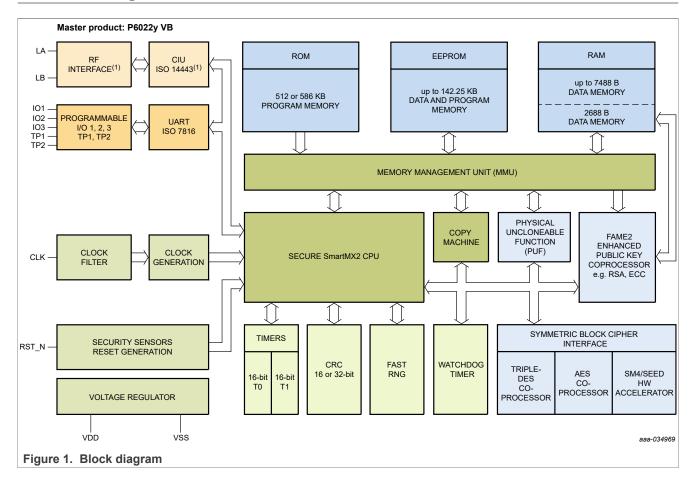

- CC EAL6+ certified hardware platform (based on NXP's SmartMX2 P6022y VB)

- Composite certified with MIFARE Security Evaluation Scheme (Equivalent to EMVCo Security Evaluation) (Evaluation lab: TÜViT, Certification lab: UL)

- FIPS 140-2 CAVP certified

#### 2.5 New features

This section gives an overview of the new features compared to MIFARE SAM AV2. Please see [1] for details.

- All new features from MIFARE DESFire EV2 requiring cryptographic operations. This includes EV2 secure messaging and Transaction MAC support (incl CommitReaderID).

- All new features from MIFARE Plus EV1 requiring cryptographic operations. This includes EV1 secure messaging, Transaction MAC support (incl CommitReaderID) and Sector Security Level Switching.

- New Virtual Card Selection and Proximity Check protocols.

- · Post-Delivery Configuration support.

- MIFARE Ultralight EV1 password authentication.

- AES authentication according to ISO/IEC 29167-10 for UCODE and ICODE support.

- LRP support for DESFire secure messaging, as supported by DESFire Light and NTAG42x(TT) and for Offline Crypto operations.

- ECC originality signature verification as supported by all recent MIFARE products.

- Generic CMAC-based key derivation for a.o. Transaction MAC session key generation and (e.g. UCODE) key diversification.

- · Fine-grained key access control.

- EMV terminal support for certificate verification, offline authentication and pin code verification.

- Programmable Logic feature to allow customized business logic and a.o. key diversifications to be run within the SAM.

- Personalization SAM feature to generate cryptogram to export keys for injection in another SAM for AES variant and for RSA variant.

- AES-256 support for Offline Crypto and SAM-Host protection.

- · RSA OAEP encryption and decryption.

- ATR configuration.

- I<sup>2</sup>C target interface in addition to ISO/IEC 7816 interface (for HVQFN only).

<sup>2</sup> Note: The PL code uploading functionality is only available to a limited set of customers.

# 3 Ordering information

Table 1. Ordering information

| Type number       | Package               |                                                                                                                                              |          |  |  |  |

|-------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------|--|--|--|

|                   | Name                  | Description                                                                                                                                  | Version  |  |  |  |

| MF4SAM3U15/9BA659 | wafer<br>unbumped     | 150 μm thickness sawn wafer on film frame carrier (FFC)                                                                                      | NAU000   |  |  |  |

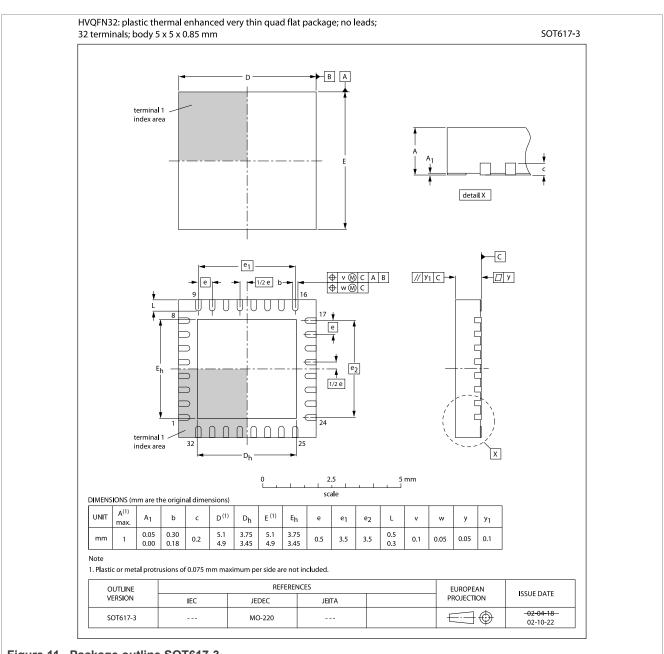

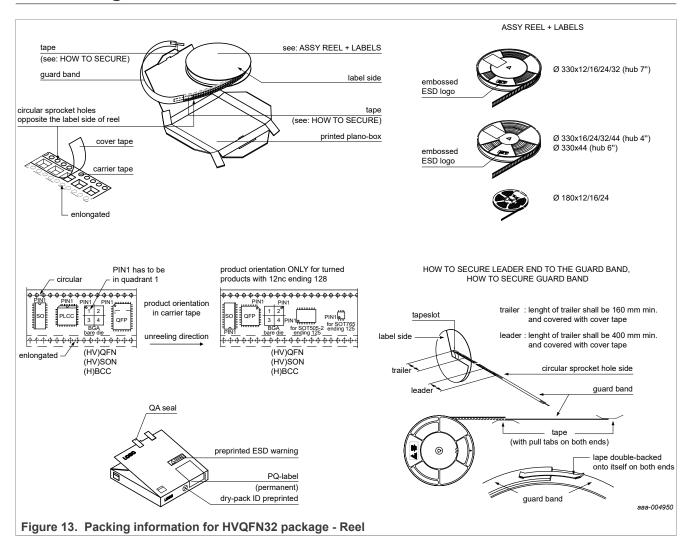

| MF4SAM3HN/9BA659  | HVQFN32               | plastic thermal enhanced very thin quad flat package; no leads; 32 terminals; body 5 x 5 x 0.85 mm; reel pack; minimum order quantity: 6.000 | SOT617-3 |  |  |  |

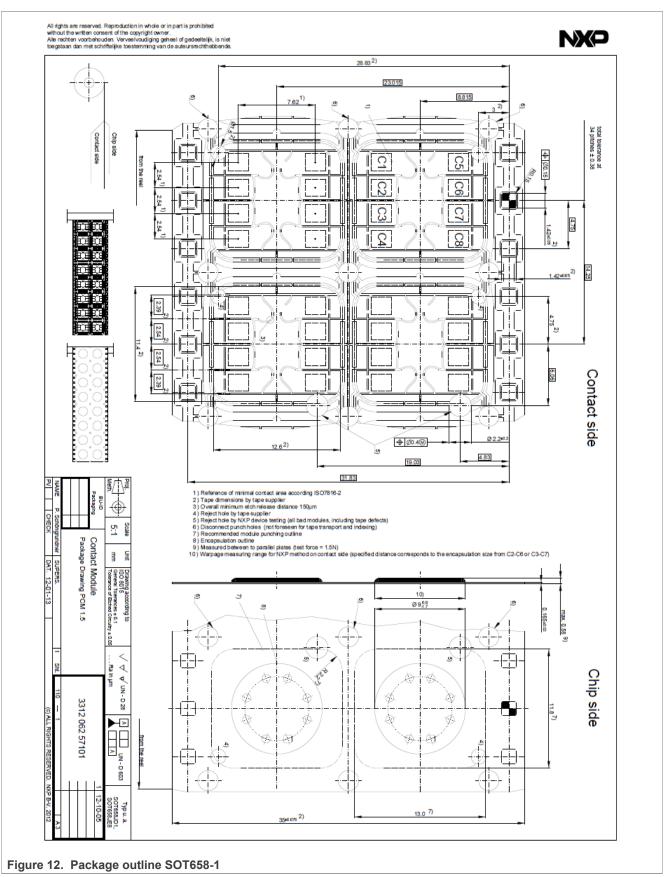

| MF4SAM3X84/9BA659 | PCM1.5 <sup>[1]</sup> | contact chip card module (super 35 mm tape format, 8 contact), minimum order quantity: 11.900                                                | SOT658-1 |  |  |  |

<sup>[1]</sup> NXP Semiconductors is ending the internal PCM1.5 manufacturing of 8-pin contact modules. For more information please contact your sales representative.

# 4 Block diagram

# 5 Pinning information

## 5.1 Pin description

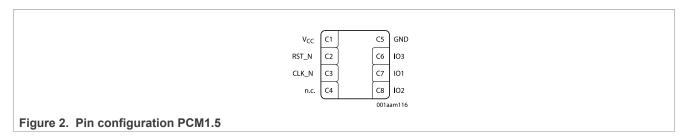

## 5.1.1 PCM1.5 pin configuration

Table 2. Pin description PCM 1.5 MIFARE SAM AV3

|          |                                         |                                                                                                                                                                                                                         | 70 21 1 111 000011 2011 1 0 111 110 1111 7 112 0 7 111 7 110                                                                                                                                                                                                                                                       |  |  |  |  |  |

|----------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 16       | MIFARE SAM A                            | V3                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| Symbol   | Symbol                                  | Pad                                                                                                                                                                                                                     | Description                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| VCC      | V <sub>CC</sub>                         | C1                                                                                                                                                                                                                      | power supply voltage input                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| RST      | RST_N                                   | C2                                                                                                                                                                                                                      | reset input, active LOW                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| CLK      | CLK_N                                   | C3                                                                                                                                                                                                                      | clock input                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| reserved | n.c.                                    | C4                                                                                                                                                                                                                      | n.c.                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| GND      | GND                                     | C5                                                                                                                                                                                                                      | ground (reference voltage) input                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| VPP      | IO3                                     | C6                                                                                                                                                                                                                      | used for I <sup>2</sup> C communication to RC (SCL)                                                                                                                                                                                                                                                                |  |  |  |  |  |

| IO1      | IO1                                     | C7                                                                                                                                                                                                                      | input/output for serial data (host communication)                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| reserved | IO2                                     | C8                                                                                                                                                                                                                      | used for I <sup>2</sup> C communication to RC (SDA)                                                                                                                                                                                                                                                                |  |  |  |  |  |

|          | Symbol VCC RST CLK reserved GND VPP IO1 | Symbol         Symbol           VCC         V <sub>CC</sub> RST         RST_N           CLK         CLK_N           reserved         n.c.           GND         GND           VPP         IO3           IO1         IO1 | Symbol         Symbol         Pad           VCC         V <sub>CC</sub> C1           RST         RST_N         C2           CLK         CLK_N         C3           reserved         n.c.         C4           GND         GND         C5           VPP         IO3         C6           IO1         IO1         C7 |  |  |  |  |  |

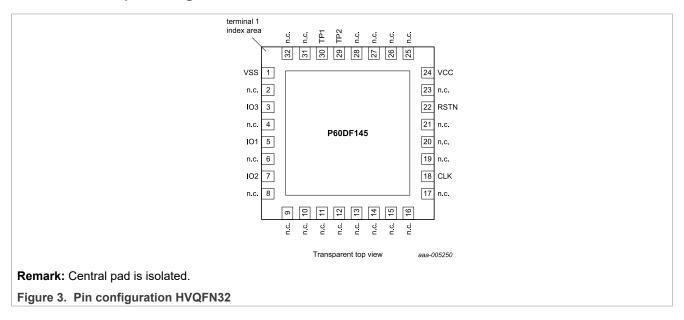

## 5.1.2 HVQFN32 pin configuration

MF4SAM3X\_SDS

Table 3. Pin description HVQFN32 MIFARE SAM AV3

| Pad | Symbol          | Description                                                                                                     |

|-----|-----------------|-----------------------------------------------------------------------------------------------------------------|

| 1   | GND             | ground (reference voltage) input                                                                                |

| 3   | IO3             | used for I <sup>2</sup> C communication to RC (SCL)                                                             |

| 5   | IO1             | input/output for serial data (ISO7816 or SDA_Target for I <sup>2</sup> C host communication)                    |

| 7   | IO2             | used for I <sup>2</sup> C communication to RC (SDA)                                                             |

| 24  | V <sub>CC</sub> | power supply voltage input                                                                                      |

| 22  | RST_N           | reset input, active LOW                                                                                         |

| 18  | CLK_N           | clock input                                                                                                     |

| 29  | TP2             | SCL_Target: used for I <sup>2</sup> C communication to Host when I <sup>2</sup> C host communication is enabled |

| 30  | TP1             | I2C_Enable: enable I <sup>2</sup> C host communication when high                                                |

## 6 Limiting values

Table 4. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to VSS (ground = 0 V).

| Symbol               | Parameter                             | Conditions                                   | Min  | Max                     | Unit       |

|----------------------|---------------------------------------|----------------------------------------------|------|-------------------------|------------|

| V <sub>DD(AMR)</sub> | supply voltage                        |                                              | -0.5 | 6                       | V          |

| V <sub>I(AMR)</sub>  | input voltage                         | any signal pad                               | -0.5 | V <sub>DD</sub> + 0.5 V | V          |

| I <sub>I(AMR)</sub>  | input current                         | pads IO1, IO2, IO3 and TP1, TP2              | -    | ± 15                    | mA         |

| Io                   | output current                        | pads IO1, IO2, IO3 and TP1, TP2              | -    | ± 15                    | mA         |

| I <sub>Iu</sub>      | latch-up current                      | $V_1 < 0 \text{ V or } V_1 > V_{DD}$         | -    | ± 100                   | mA         |

| V <sub>esd</sub>     | electrostatic discharge               | pads VDD, VSS, CLK, RST_N, IO1, IO2, IO3 [2] | -    | ± 4                     | kV         |

|                      | voltage (HBM)                         | TP1, TP2 [3]                                 | -    | ± 2                     | kV         |

|                      | electrostatic discharge voltage (CDM) | all pads [4]                                 | -    | ± 500                   | V          |

| P <sub>tot</sub>     | total power dissipation               | [5]                                          | -    | 1                       | W          |

| T <sub>stg</sub>     | storage temperature                   | [6]                                          | -55  | 125                     | $^{\circ}$ |

- [1] If IO2 and IO3 are available.

- [2] In accordance with ANSI/ESDA/JEDEC JS-001-2011, ESDA/JEDEC Joint Standard for Electrostatic Discharge Sensitivity Testing Human Body Model (HBM) Component Level.

- [3] Only available if enabled via OEF setting.

- [4] In accordance with JEDEC JESD22-C101 for Charged-Device Model (CDM).

- [5] Depending on appropriate thermal resistance of the package.

- [6] Depending on delivery type, refer to NXP Semiconductors General Specification for 12" Wafers (15) and to NXP Semiconductors Contact & Dual Interface Chip Card Module Specification (16).

#### **CAUTION**

This device is sensitive to ElectroStatic Discharge (ESD). Observe precautions for handling electrostatic sensitive devices.

Such precautions are described in the ANSI/ESD S20.20, IEC/ST 61340-5, JESD625-A or equivalent standards.

MF4SAM3X\_SDS

All information provided in this document is subject to legal disclaimers.

© 2024 NXP B.V. All rights reserved.

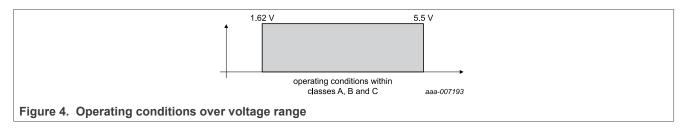

# 7 Recommended operating conditions

Table 5. Operating conditions

| Symbol                | Parameter                                               | Conditions                                                      | Min  | Тур | Max      | Unit |

|-----------------------|---------------------------------------------------------|-----------------------------------------------------------------|------|-----|----------|------|

| V <sub>DD</sub> (5)   | supply voltage <sup>[1]</sup>                           | Class A/5 V nominal supply voltage contact interface operation  | 4.5  | 5   | 5.5      | V    |

| V <sub>DD</sub> (3)   |                                                         | Class B/3 V nominal supply voltage contact interface operation  | 2.7  | 3   | 3.3      | V    |

| V <sub>DD</sub> (1.8) |                                                         | Class C/1.8V nominal supply voltage contact interface operation | 1.62 | 1.8 | 1.98     | V    |

| Vı                    | DC input voltage on digital inputs and digital I/O pads | -                                                               | 0    | -   | $V_{DD}$ | V    |

| T <sub>amb</sub>      | operating ambient<br>temperature <sup>[2]</sup>         |                                                                 | -25  | -   | 85       | °C   |

<sup>[1]</sup> All described supply voltages according to ISO/IEC 7816-3.

The supported operating supply voltage ranges limited by exception sensors covers the whole range of classes A, B and C. The Product Name devices operate within the full voltage range described in <u>Figure 4</u>.

<sup>[2]</sup> All product properties and values specified within this data sheet are only valid within the operating ambient temperature range.

## 8 Static characteristics

#### 8.1 Measurement conventions

Testing measurements are performed at the contact pads of the device under test. All voltages are defined with respect to the ground contact pad VSS. All currents flowing into the Smart Card IC are considered positive.

#### 8.2 Levels and currents

Table 6. Electrical DC characteristics of Input/Output: IO1, IO2 and IO3 Conditions:  $V_{DD}$  = 1.62 V to 5.5 V;  $V_{SS}$  = 0 V;  $T_{amb}$  = -25 °C to 85 °C, unless otherwise specified

| Symbol            | Parameter                                                                                  | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Min                   | Тур         | Max                    | Unit             |

|-------------------|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------------|------------------------|------------------|

| V <sub>IH</sub>   | HIGH-level input voltage                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0.7 × V <sub>DD</sub> | -           | V <sub>DD</sub> + 0.3  | V                |

| V <sub>IL</sub>   | LOW-level input voltage                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -0.3                  | -           | 0.25 × V <sub>DD</sub> | V                |

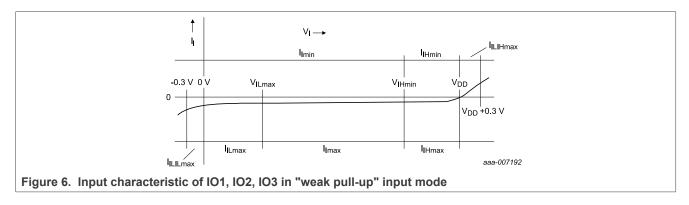

| Ін                | HIGH-level input current in<br>"weak pull-up" input mode                                   | $0.7 \ V_{DD} \le V_I \le V_{DD}$ ;<br>Test conditions for the maximum absolute value:<br>$I_{IH(max)}$ : $V_I = 0.7 \ V_{DD}$ ,<br>$V_{DD} = V_{DD(max)}$ of the respective supply voltage class A, B or C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0                     | -           | -20                    | μА               |

| I <sub>IL</sub>   | LOW-level input current                                                                    | $0 \text{ V} \le \text{V}_{\text{I}} \le 0.3 \text{ V}_{\text{DD}};$ Test conditions for the maximum absolute value: $I_{\text{IL}(\text{max})}$ : $V_{\text{I}} = 0 \text{ V}$ , $V_{\text{DD}} = V_{\text{DD}(\text{max})}$ of the respective supply voltage class A, B or C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -                     | -           | -50                    | μА               |

| I <sub>TL</sub>   | HIGH-to-LOW transition input current (only in "quasi-bidirectional" mode)                  | $0.3 \text{ V}_{DD} < \text{V}_{\text{I}} \le \text{V}_{DD};$<br>Test conditions for the maximum absorving $0.5 \text{ V}_{DD}$ , $0.5 \text{ V}_{DD}$ |                       | y voltage o | class A, B or (        | C <sup>[1]</sup> |

|                   |                                                                                            | Class A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -                     | -           | -300                   | μA               |

|                   |                                                                                            | Class B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -                     | -           | -250                   | μA               |

|                   |                                                                                            | Class C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -                     | -           | -200                   | μΑ               |

| Iį                | input current in "weak pull-<br>up" input mode                                             | $0 \text{ V} \leq \text{V}_{\text{I}} \leq \text{V}_{\text{DD}};$ Test conditions for the maximum absolute value: $I_{\text{I}(\text{max})}: \text{V}_{\text{I}} = 0 \text{ V}, \text{V}_{\text{DD}} = \text{V}_{\text{DD}(\text{max})}$ of the respective supply voltage class A, B or C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                     | -           | -50                    | μА               |

| I <sub>ILIH</sub> | leakage input current at input voltage beyond V <sub>DD</sub> in "weak pull-up" input mode | $\begin{split} &V_{DD} < V_{I} \leq V_{DD} + 0.3 \text{ V}; \\ -25 \text{ °C} \leq T_{amb} \leq 85 \text{ °C}; \\ &\text{Test conditions: } V_{I} = V_{DD} + 0.3 \text{ V}; \\ &V_{DD} = V_{DD(max)} \text{ of the respective supply voltage class A, B or C;} \\ &T_{amb} = 85 \text{ °C} \end{split}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -                     | -           | 20                     | μА               |

Table 6. Electrical DC characteristics of Input/Output: IO1, IO2 and IO3...continued Conditions:  $V_{DD} = 1.62 \text{ V to } 5.5 \text{ V}$ ;  $V_{SS} = 0 \text{ V}$ ;  $T_{amb} = -25 \text{ °C to } 85 \text{ °C}$ , unless otherwise specified

| Symbol              | Parameter                                                                                                    | Conditions                                                                                                                                                                                                                                                                                                                               |     | Min                          | Тур | Max                    | Unit |

|---------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------------|-----|------------------------|------|

| I <sub>ILIL</sub>   | leakage input current at input voltage below V <sub>SS</sub> in "weak pull-up" input mode                    | $-0.3 \text{ V} \leq \text{V}_{\text{I}} < 0 \text{ V};$ $-25 \text{ °C} \leq \text{T}_{\text{amb}} \leq 30 \text{ °C}$ Test conditions: $\text{V}_{\text{I}} = -0.3 \text{ V};$ $\text{V}_{\text{DD}} = \text{V}_{\text{DD(max)}} \text{ of the respective supply voltage class A, B or C;}$ $\text{T}_{\text{amb}} = 30 \text{ °C}$    |     | -                            | -   | -50                    | μΑ   |

|                     |                                                                                                              | $-0.3 \text{ V} \leq \text{V}_{\text{I}} < 0 \text{ V};$ $30 \text{ °C} < \text{T}_{\text{amb}} \leq 85 \text{ °C}$ Test conditions: $\text{V}_{\text{I}} = -0.3 \text{ V};$ $\text{V}_{\text{DD}} = \text{V}_{\text{DD}(\text{max})} \text{ of the respective supply voltage class A, B or C;}$ $\text{T}_{\text{amb}} = 85 \text{ °C}$ |     | -                            | -   | -275                   | μА   |

| I <sub>ILIHQ</sub>  | leakage input current<br>at input voltage beyond<br>V <sub>DD</sub> (only in "quasi-<br>bidirectional" mode) | $\begin{split} &V_{DD} < V_{I} \leq V_{DD} + 0.3 \text{ V}; \\ -25 \text{ °C} \leq &T_{amb} \leq 85 \text{ °C} \\ &\text{Test conditions: } V_{I} = V_{DD} + 0.3 \text{ V}; \\ &V_{DD} = &V_{DD(max)} \text{ of the respective} \\ &\text{supply voltage class A, B or C;} \\ &T_{amb} = 85 \text{ °C} \end{split}$                      |     | -                            | -   | 100                    | μА   |

| l <sub>ilil</sub> q | leakage input current<br>at input voltage below<br>V <sub>SS</sub> (only in "quasi-<br>bidirectional" mode)  | $-0.3 \text{ V} \le \text{V}_{\text{I}} < 0 \text{ V};$ $-25 \text{ °C} \le \text{T}_{\text{amb}} \le 30 \text{ °C}$ Test conditions: $\text{V}_{\text{I}} = -0.3 \text{ V};$ $\text{V}_{\text{DD}} = \text{V}_{\text{DD(max)}} \text{ of the respective supply voltage class A, B or C;}$ $\text{T}_{\text{amb}} = 30 \text{ °C}$       |     | -                            | -   | -75                    | μΑ   |

|                     |                                                                                                              | $-0.3 \text{ V} \leq \text{V}_{\text{I}} < 0 \text{ V};$ $30 \text{ °C} < \text{T}_{\text{amb}} \leq 85 \text{ °C}$ Test conditions: $\text{V}_{\text{I}} = -0.3 \text{ V};$ $\text{V}_{\text{DD}} = \text{V}_{\text{DD}(\text{max})} \text{ of the respective}$ supply voltage class A, B or C; $\text{T}_{\text{amb}} = 85 \text{ °C}$ |     | -                            | -   | -300                   | μА   |

| V <sub>OH</sub>     | HIGH-level output voltage                                                                                    | I <sub>OH</sub> = -20 μA;<br>Class A condition                                                                                                                                                                                                                                                                                           | [2] | 3.8<br>0.7 × V <sub>DD</sub> | -   | -                      | V    |

|                     |                                                                                                              | I <sub>OH</sub> = -20 μA;<br>Class B or C condition                                                                                                                                                                                                                                                                                      | [2] | 0.7 × V <sub>DD</sub>        | -   | -                      | V    |

| V <sub>OL</sub>     | LOW-level output voltage                                                                                     | Class A or B condition;<br>I <sub>OL</sub> = 1 mA                                                                                                                                                                                                                                                                                        |     | -                            | -   | 0.3                    | V    |

|                     |                                                                                                              | Class C condition;                                                                                                                                                                                                                                                                                                                       |     |                              |     |                        |      |

|                     |                                                                                                              | I <sub>OL</sub> = 1 mA                                                                                                                                                                                                                                                                                                                   |     | -                            | -   | 0.3                    | V    |

|                     |                                                                                                              | I <sub>OL</sub> = 0.5 mA                                                                                                                                                                                                                                                                                                                 |     | -                            | -   | 0.15 × V <sub>DD</sub> | V    |

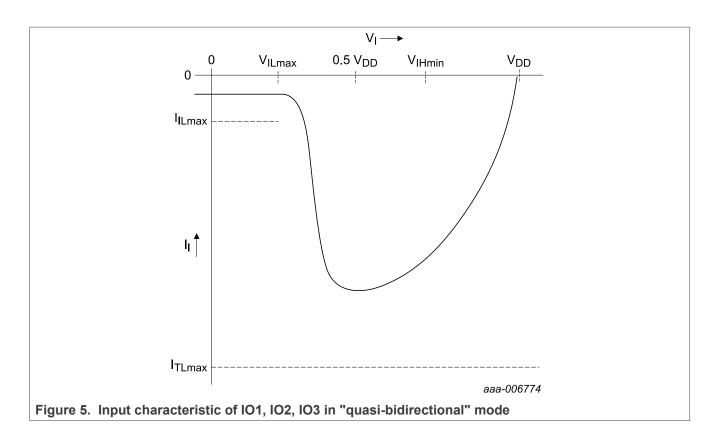

<sup>[1]</sup> IO1, IO2 and IO3 source a transition current when being externally driven from HIGH to LOW. This transition current (I<sub>TL</sub>) reaches its maximum value when the input voltage V<sub>1</sub> is approximately 0.5 V<sub>DD</sub>. Input current I<sub>TL</sub> is tested at input voltage V<sub>1</sub> = 0.5 V<sub>DD</sub>. Current IIL is tested at input voltage V<sub>1</sub> = 0.3 V. Figure 5 shows the input characteristic of this quasi-bidirectional port mode.

MF4SAM3X\_SDS

All information provided in this document is subject to legal disclaimers.

© 2024 NXP B.V. All rights reserved.

<sup>[2]</sup> External pull-up resistor 20 k $\Omega$  to V<sub>DD</sub> assumed. The worst case test condition for parameter V<sub>OH</sub> is present at minimum V<sub>DD</sub>. For class A supply voltage conditions V<sub>DD</sub> = 4.5 V is the worst case with respect to the fix specification limit V<sub>OHmin</sub> = 3.8 V (0.844 V<sub>DD</sub>). The supply voltage-related limit "0.7 V<sub>DD</sub>" is a stricter requirement than the fix value 3.8 V at high V<sub>DD</sub> values (0.7 V<sub>DD</sub> = 3.85 V at V<sub>DD</sub> = 5.5 V). So, in the V<sub>DD</sub> range 4.5 V to 5.5 V, V<sub>OHmin</sub> is specified

as "the larger value of 0.7  $V_{DD}$  and 3.8 V, respectively". The  $V_{OHmin}$  value (0.7  $V_{DD}$ ) cannot be guaranteed in "quasi-bidirectional" mode at an output current of  $I_{OH}$  = -20  $\mu$ A - the strong output drive mode must be used.

Table 7. Electrical DC characteristics of Inputs CLK and RST\_N<sup>[1][2]</sup>

Conditions:  $V_{DD}$  = 1.62 V to 5.5 V;  $V_{SS}$  = 0 V;  $T_{amb}$  = -25 °C to 85 °C, unless otherwise specified

| Symbol             | Parameter                                                     | Conditions                                                                                                                                                                                                                                                                                                                                                                                | Min                   | Тур | Max                    | Unit |

|--------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----|------------------------|------|

| Inputs Cl          | LK (when the IC is not in res                                 | et) and RST_N                                                                                                                                                                                                                                                                                                                                                                             |                       |     | '                      |      |

| V <sub>IH1</sub>   | HIGH-level input voltage                                      |                                                                                                                                                                                                                                                                                                                                                                                           | 0.7 × V <sub>DD</sub> | -   | V <sub>DD</sub> + 0.3  | V    |

| V <sub>IL1</sub>   | LOW-level input voltage                                       |                                                                                                                                                                                                                                                                                                                                                                                           | -0.3                  | -   | 0.25 × V <sub>DD</sub> | V    |

| I <sub>IH1</sub>   | HIGH-level input current<br>(weak pull-down is on)            | $0.7 \ V_{DD} \le V_I \le V_{DD}$ ;<br>Test conditions for the maximum absolute value:<br>$I_{IH1(max)}$ : $V_I = V_{DD}$ ,<br>$V_{DD} = V_{DD(max)}$ of the respective supply voltage class A, B or C                                                                                                                                                                                    | -                     | -   | 20                     | μА   |

| I <sub>IL1</sub>   | LOW-level input current<br>(weak pull-down is on)             | $\begin{array}{l} 0 \; \text{V} \leq \text{V}_{\text{I}} \leq 0.3 \; \text{V}_{\text{DD}}; \\ \text{Test conditions for the maximum} \\ \text{absolute value:} \\ \text{I}_{\text{IL1(max)}}; \; \text{V}_{\text{I}} = 0.3 \; \text{V}_{\text{DD}}, \\ \text{V}_{\text{DD}} = \text{V}_{\text{DD(max)}} \; \text{of the respective} \\ \text{supply voltage class A, B or C} \end{array}$ | 0                     | -   | 20                     | μА   |

| I <sub>I1</sub>    | input current<br>(weak pull-down is on)                       | $0 \text{ V} \le \text{V}_{\text{I}} \le \text{V}_{\text{DD}};$<br>Test conditions for the maximum absolute value: $I_{\text{I1(max)}}: \text{V}_{\text{I}} = \text{V}_{\text{DD}},$ $\text{V}_{\text{DD}} = \text{V}_{\text{DD(max)}}$ of the respective supply voltage class A, B or C                                                                                                  | 0                     | -   | 20                     | μА   |

| Ішн1               | leakage input current at input voltage beyond V <sub>DD</sub> | $V_{DD} < V_{I} \le V_{DD} + 0.3 \text{ V};$<br>$-25 \text{ °C} \le T_{amb} \le 85 \text{ °C}$<br>Test conditions: $V_{I} = V_{DD} + 0.3 \text{ V};$<br>$V_{DD} = V_{DD(max)}$ of the respective supply voltage class A, B or C;<br>$T_{amb} = 85 \text{ °C}$                                                                                                                             | -                     | -   | 20                     | μА   |

| I <sub>ILIL1</sub> | leakage input current at input voltage below V <sub>SS</sub>  | $-0.3 \text{ V} \leq \text{V}_{\text{I}} < 0 \text{ V};$ $-25 \text{ °C} \leq \text{T}_{\text{amb}} \leq 30 \text{ °C}$ Test conditions: $\text{V}_{\text{I}} = -0.3 \text{ V};$ $\text{V}_{\text{DD}} = \text{V}_{\text{DD(max)}} \text{ of the respective supply voltage class A, B or C;}$ $\text{T}_{\text{amb}} = 30 \text{ °C}$                                                     | -                     | -   | -50                    | μΑ   |

|                    |                                                               | $-0.3 \text{ V} \leq \text{V}_{\text{I}} < 0 \text{ V};$ $30 \text{ °C} < \text{T}_{\text{amb}} \leq 85 \text{ °C}$ Test conditions: $\text{V}_{\text{I}} = -0.3 \text{ V};$ $\text{V}_{\text{DD}} = \text{V}_{\text{DD}(\text{max})} \text{ of the respective supply voltage class A, B or C;}$ $\text{T}_{\text{amb}} = 85 \text{ °C}$                                                  | -                     | -   | -200                   | μА   |

Table 7. Electrical DC characteristics of Inputs CLK and RST\_N<sup>[1][2]</sup>...continued Conditions:  $V_{DD} = 1.62 \text{ V to } 5.5 \text{ V; } V_{SS} = 0 \text{ V; } T_{amb} = -25 \text{ °C to } 85 \text{ °C, unless otherwise specified}$

| Symbol             | Parameter                                                     | Conditions                                                                                                                                                                                                                                                                                                                            | Min                   | Тур | Max                    | Uni |

|--------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----|------------------------|-----|

| Input CLK          | (during IC reset)                                             |                                                                                                                                                                                                                                                                                                                                       | <u> </u>              |     |                        |     |

| V <sub>IH2</sub>   | HIGH-level input voltage                                      |                                                                                                                                                                                                                                                                                                                                       | 0.7 × V <sub>DD</sub> | -   | V <sub>DD</sub> + 0.3  | V   |

| V <sub>IL2</sub>   | LOW-level input voltage                                       |                                                                                                                                                                                                                                                                                                                                       | -0.3                  | -   | 0.25 × V <sub>DD</sub> | V   |

| Іін2               | HIGH-level input current<br>(weak pull-up is on)              | $0.7 \ V_{DD} \le V_I \le V_{DD};$<br>Test conditions for the maximum absolute value:<br>$I_{IH2(max)}$ : $V_I = 0.7 \ V_{DD}$ ,<br>$V_{DD} = V_{DD(max)}$ of the respective supply voltage class A, B or C                                                                                                                           | 0                     | -   | -20                    | μΑ  |

| l <sub>IL2</sub>   | HIGH-level input current<br>(weak pull-up is on)              | $0 \text{ V} \le \text{V}_{\text{I}} \le 0.3 \text{ V}_{\text{DD}};$ Test conditions for the maximum absolute value: $I_{\text{IL2(max)}}: \text{V}_{\text{I}} = 0\text{V},$ $\text{V}_{\text{DD}} = \text{V}_{\text{DD(max)}} \text{ of the respective supply voltage class A, B or C}$                                              | -                     | -   | -20                    | μΑ  |

| l <sub>I2</sub>    | input current<br>(weak pull-up is on)                         | $0 \text{ V} \le \text{V}_{\text{I}} \le \text{V}_{\text{DD}};$ Test conditions for the maximum absolute value: $I_{12(\text{max})}: \text{V}_{\text{I}} = 0 \text{ V},$ $\text{V}_{\text{DD}} = \text{V}_{\text{DD}(\text{max})}$ of the respective supply voltage class A, B or C                                                   | 0                     | -   | -20                    | μΑ  |

| ILIH2              | leakage input current at input voltage beyond V <sub>DD</sub> | $\begin{split} &V_{DD} < V_{I} \leq V_{DD} + 0.3 \text{ V}; \\ -25 \text{ °C} \leq &T_{amb} \leq 85 \text{ °C} \\ &\text{Test conditions: } V_{I} = V_{DD} + 0.3 \text{ V}; \\ &V_{DD} = &V_{DD(max)} \text{ of the respective} \\ &\text{supply voltage class A, B or C;} \\ &T_{amb} = 85 \text{ °C} \end{split}$                   | -                     | -   | 20                     | μΑ  |

| I <sub>ILIL2</sub> | leakage input current at input voltage below V <sub>SS</sub>  | $-0.3 \text{ V} \leq \text{V}_{\text{I}} < 0 \text{ V};$ $-25 \text{ °C} \leq \text{T}_{\text{amb}} \leq 30 \text{ °C}$ Test conditions: $\text{V}_{\text{I}} = -0.3 \text{ V};$ $\text{V}_{\text{DD}} = \text{V}_{\text{DD(max)}} \text{ of the respective}$ supply voltage class A, B or C; $\text{T}_{\text{amb}} = 30 \text{ °C}$ | -                     | -   | -50                    | μА  |

|                    |                                                               | -0.3 V $\leq$ V <sub>I</sub> $<$ 0 V;<br>30 °C $<$ T <sub>amb</sub> $\leq$ 85 °C<br>Test conditions: V <sub>I</sub> = -0.3 V;<br>V <sub>DD</sub> = V <sub>DD(max)</sub> of the respective<br>supply voltage class A, B or C;<br>T <sub>amb</sub> = 85 °C                                                                              | -                     | -   | -200                   | μΑ  |

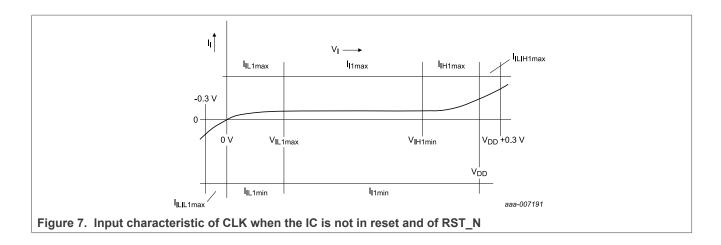

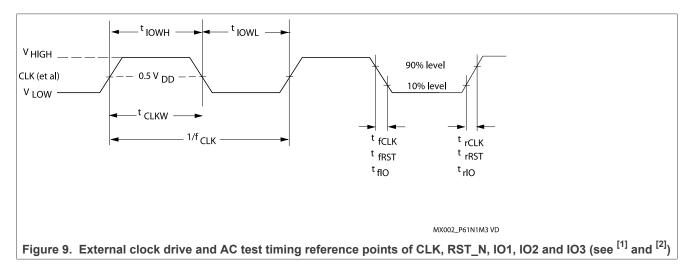

<sup>[1]</sup> The active low RST\_N input and outside reset state also the CLK input internally activate a resistive pull-down device to VSS. Accordingly a current is flowing into the pad at voltages above 0 V. Figure 7 shows this input characteristic. In CLOCKSTOP mode the preferred electrical state on CLK is a LOW level, in order to minimize the power consumption.

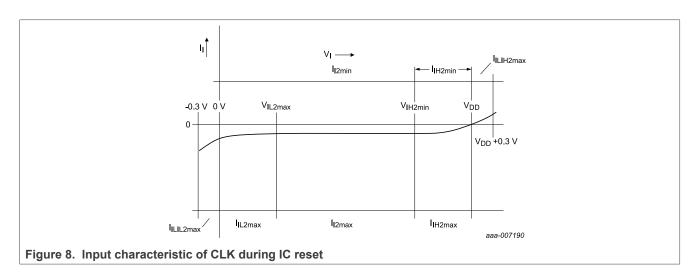

<sup>[2]</sup> The CLK input internally has a resistive pull-up device to VDD activated during IC reset. Accordingly a current is flowing out of the pad at voltages below VDD. Figure 8 shows this input characteristic.

#### Table 8. Electrical DC characteristics of TP1 and TP2

Conditions: (A)  $V_{DD} = 1.62 \text{ V to } 1.98 \text{ V: } V_{DDAE} = V_{DD}$ ;

(B)  $V_{DD}$ = 2.2 V to 5.5 V (that is outside Class C supply range):  $V_{DDAE(NOM)}$  = 1.8 V;

$V_{\rm SS}$  = 0 V;  $T_{amb}$  = -25 °C to 85 °C, unless otherwise specified

| Symbol             | Parameter                                                                                   | Conditions                                                                                                                                                                                                                                          | Min                       | Тур | Max                      | Unit |

|--------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----|--------------------------|------|

| V <sub>IHT</sub>   | HIGH-level input voltage                                                                    |                                                                                                                                                                                                                                                     | 0.7 × V <sub>DDAE</sub>   | -   | V <sub>DDAE</sub> + 0.3  | V    |

| V <sub>ILT</sub>   | LOW-level input voltage                                                                     |                                                                                                                                                                                                                                                     | -0.3                      | -   | 0.25 × V <sub>DDAE</sub> | V    |

| I <sub>IHD</sub>   | HIGH-level input current maximum (resistive pulldown is on)                                 | $0.7 \ V_{DDAE} \le V_{I} \le V_{DDAE};$<br>Test conditions for the maximum absolute value:<br>$V_{I} = V_{DDAE};$<br>$V_{DDAE} = V_{DDAE(max)};$<br>for the minimum absolute value:<br>$V_{I} = 0.7 \ V_{DDAE};$<br>$V_{DDAE} = V_{DDAE(min)}$     | 10                        | -   | 100                      | μΑ   |

| I <sub>ILD</sub>   | LOW-level input current maximum (resistive pulldown is on)                                  | $0 \text{ V} \le \text{V}_{\text{I}} \le 0.3 \text{ V}_{\text{DDAE}};$<br>Test conditions for the maximum absolute value:<br>$\text{V}_{\text{I}} = 0.3 \text{ V}_{\text{DDAE}};$<br>$\text{V}_{\text{DDAE}} = \text{V}_{\text{DDAE}(\text{max})};$ | 0                         | -   | 20                       | μА   |

| I <sub>ILIH3</sub> | leakage input current at input voltage beyond V <sub>DDAE</sub> (resistive pull-down is on) | $V_{DDAE} < V_{I} \le V_{DDAE} + 0.3 \text{ V};$<br>$-25 \text{ °C} \le T_{amb} \le 85 \text{ °C};$<br>Test conditions:<br>$V_{I} = 2.3 \text{ V};$<br>$T_{amb} = 85 \text{ °C}$                                                                    | -                         | -   | 150                      | μΑ   |

| I <sub>ILIL3</sub> | leakage input current at input voltage beyond V <sub>SS</sub> (resistive pull-down is on)   | -0.3 V $\leq$ V <sub>I</sub> $<$ 0 V;<br>-25 °C $\leq$ T <sub>amb</sub> $\leq$ 30 °C;<br>Test conditions:<br>V <sub>I</sub> = -0.3 V;<br>T <sub>amb</sub> = 30 °C                                                                                   | 0                         | -   | -150                     | μА   |