# **NXP Semiconductors**

Data Sheet: Technical Data

Document Number: MPC5606E

Rev. 4, 11/2019

# **MPC5606E**

# MPC5606E Microcontroller Data Sheet

#### NOTE

For BCM89810 document please refer to Broadcom website and download the document

- Single issue, 32-bit CPU core complex (e200z0h)

- Compliant with Power Architecture<sup>®</sup> embedded category

- Variable Length Encoding (VLE) only

- Memory

- 512 KB on-chip Code Flash with ECC and erase/program controller

- additional 64 (4 × 16) KB on-chip Data Flash with ECC for EEPROM emulation

- 96 KB on-chip SRAM with ECC

- Fail-safe protection

- Programmable watchdog timer

- Non-maskable interrupt

- Fault collection unit

- Interrupts and events

- 16-channel eDMA controller

- 16 priority level controller

- Up to 22 external interrupts

- PIT implements four 32-bit timers

- 120 interrupts are routed via INTC

- General purpose I/Os

- Individually programmable as input, output or special function

- **—** 39

- 1 general purpose eTimer unit

- 6 timers each with up/down capabilities

- 16-bit resolution, cascadeable counters

- Quadrature decode with rotation direction flag

- Double buffer input capture and output compare

- Communications interfaces

- 2 LINFlex channels (1 × Master/Slave, 1 × Master Only)

- 3 DSPI controllers with automatic chip select generation (up to 2/2/4 chip selects)

- 1 FlexCAN interface (2.0B Active) with 32 message buffers

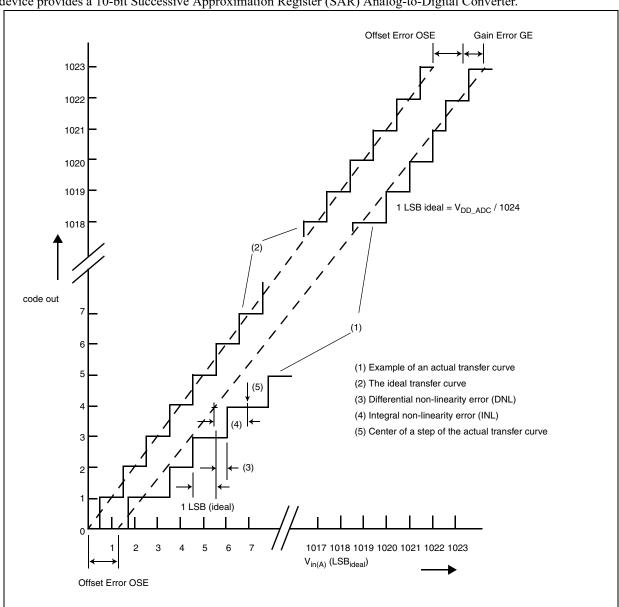

- One 10-bit analog-to-digital converter (ADC)

- 7 input channels

- 4 channels routed to the pins

- 3 internal connections: 1x temperature sensor, 1x core voltage, 1x IO voltage

- Conversion time  $< 1 \mu s$  including sampling time at full precision

- 4 analog watchdogs with interrupt capability

- On-chip CAN/UART bootstrap loader with Boot Assist Module (BAM)

- On-chip TSENS

- 100 Mbps Automotive Ethernet Transceiver

- Supports precision timestamps

- JPEG/MJPEG 8/12bit Encoder

- 6 x stereo channels audio interface

- 2x I<sup>2</sup>C controller module

- · CRC module

- BCM89810 Ethernet PHY

# **Table of Contents**

| 1 | Overv | view                                                  |   | 3.13 1  | 6 MHz RC oscillator electrical characteristics 34            |

|---|-------|-------------------------------------------------------|---|---------|--------------------------------------------------------------|

|   | 1.1   | Device summary                                        |   | 3.14 A  | analog-to-Digital Converter (ADC) electrical characteristics |

|   | 1.2   | Block diagram                                         |   | 3       | 5                                                            |

| 2 | Packa | age pinouts and signal descriptions 6                 |   | 3       | 3.14.1 Input impedance and ADC accuracy 35                   |

|   | 2.1   | Package pinouts                                       |   | 3       | 3.14.2 ADC conversion characteristics 40                     |

|   | 2.2   | Signal descriptions                                   |   | 3.15 T  | emperature sensor electrical characteristics 41              |

|   |       | 2.2.1 Power supply and reference voltage pins 7       |   | 3.16 F  | Flash memory electrical characteristics 41                   |

|   |       | 2.2.2 System pins8                                    |   | 3.17 F  | Function Specification                                       |

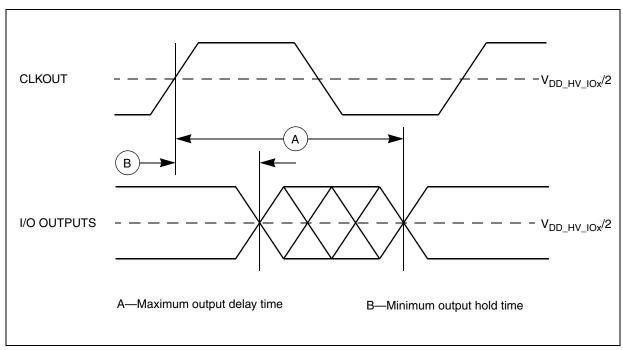

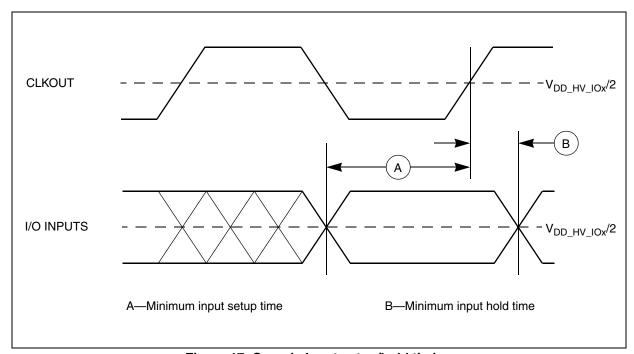

|   |       | 2.2.3 Pin muxing9                                     |   | 3.18 A  | AC specifications                                            |

| 3 | Elect | rical characteristics18                               |   | 3       | 3.18.1 Pad AC specifications                                 |

|   | 3.1   | Introduction                                          |   | 3.19 A  | C timing characteristics                                     |

|   | 3.2   | Parameter classification                              |   |         | 3.19.1 Generic timing diagrams 46                            |

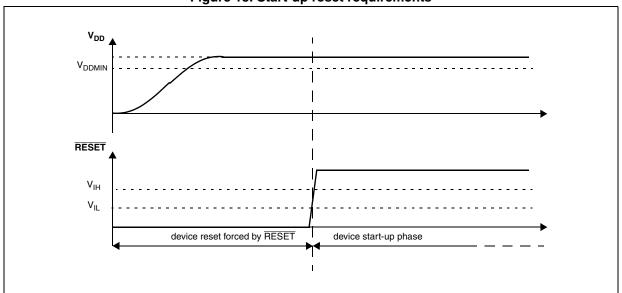

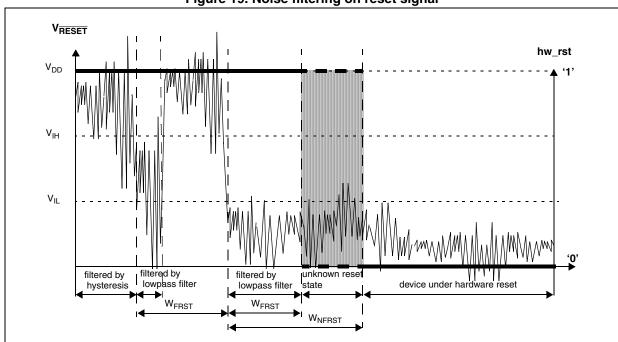

|   | 3.3   | Absolute maximum ratings                              |   | 3       | 3.19.2 RESET_B pin characteristics 48                        |

|   | 3.4   | Recommended operating conditions20                    |   | 3       | 3.19.3 Nexus and JTAG timing 49                              |

|   | 3.5   | Thermal characteristics21                             |   | 3       | 3.19.4 GPIO timing                                           |

|   |       | 3.5.1 General notes for specifications at maximum     |   | 3       | 3.19.5 External interrupt timing (IRQ pin) 52                |

|   |       | junction temperature                                  |   | 3       | 3.19.6 FlexCAN timing                                        |

|   | 3.6   | Electromagnetic Interference (EMI) characteristics23  |   |         | 3.19.7 LINFlex timing                                        |

|   | 3.7   | Electrostatic Discharge (ESD) characteristics         |   | 3       | 3.19.8 DSPI timing                                           |

|   | 3.8   | Power management electrical characteristics24         |   |         | 3.19.9 Video interface timing                                |

|   |       | 3.8.1 Power Management Overview24                     |   |         | 3.19.10Fast ethernet interface                               |

|   |       | 3.8.2 Voltage regulator electrical characteristics 26 |   |         | 3.19.111 <sup>2</sup> C timing                               |

|   |       | 3.8.3 Voltage monitor electrical characteristics 27   |   | 3       | 3.19.12SAI timing                                            |

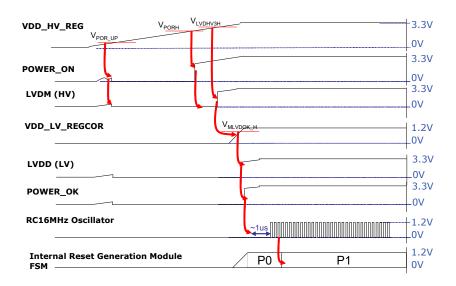

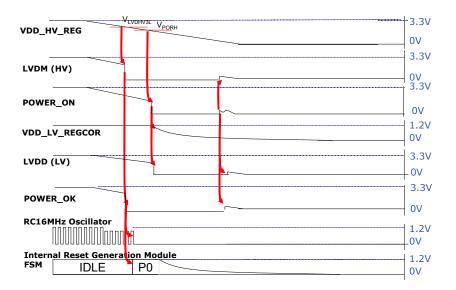

|   | 3.9   | Power Up/Down reset sequencing                        | 4 | Packag  | pe mechanical data                                           |

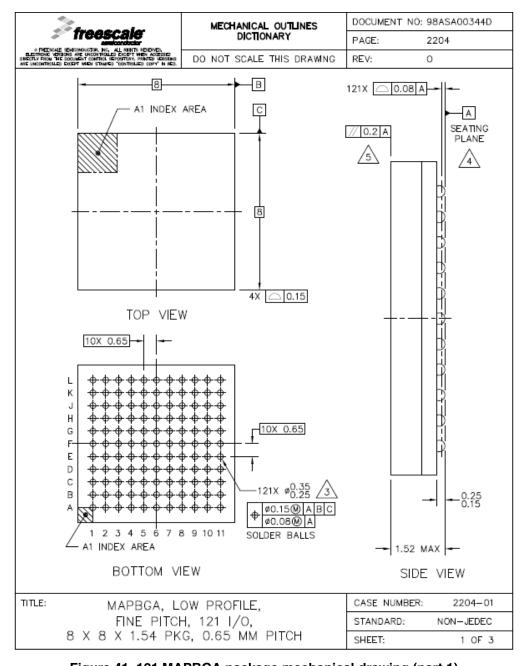

|   | 3.10  | DC electrical characteristics                         |   |         | 21 MAPBGA mechanical outline drawing 65                      |

|   | 3.11  | Main oscillator electrical characteristics            | 5 | Revisio | n History of this Document                                   |

|   | 3.12  | FMPLL electrical characteristics                      |   |         |                                                              |

# 1 Overview

This document provides electrical specifications, pin assignments, and package diagrams for the MPC5606E series of microcontroller units (MCUs).

MPC5606E microcontrollers are members of a new family of next generation microcontrollers built on the Power Architecture. This document describes the features of the family and options available within the family members, and highlights important electrical and physical characteristics of the devices.

The MPC5606E microcontroller integrates MPC5604E device with the Broadcom<sup>(R)</sup> BCM89810 single-port BroadR-Reach<sup>TM</sup> 100 Mbps automotive Ethernet transceiver. All information about configuration of the BCM89810 BroadR-Reach<sup>TM</sup> Ethernet transceivers is available at https://support.broadcom.com/. The user should request for an account to access BCM89810 documentation, if the access is not there.

The MPC5606E microcontroller is a gateway system designed to move data from different sources via Ethernet to a receiving system and vice versa. The supported data sources and sinks are:

- Video data (with 8/10/12 bits per data word)

- Audio data (6× stereo channels)

- RADAR data ( $2 \times 12$  bit with <1 µs per sample, digitized externally and read in via SPI)

- Other serial communication interfaces including CAN, LIN, and SPI

The Ethernet module has a bandwidth of 10/100 Mbits/sec and supports precision time stamps (IEEE1588). Unshielded twisted pair cables are used to transfer data (via Ethernet) in the car, resulting in a significant reduction of wiring costs by providing inexpensive high bandwidth data links.

# 1.1 Device summary

Table 1 summarizes the MPC5606E device.

**Table 1. Device summary**

| Feature            | MPC5606E                                                         |

|--------------------|------------------------------------------------------------------|

| reature            | 121 MAPBGA                                                       |

| CPU                | e200z0h, 64 MHz, VLE only, no SPE                                |

| Flash with ECC     | CFlash: 512 KB (LC) DFlash: 64 KB (LC, area optimized)           |

| RAM with ECC       | 96 KB                                                            |

| DMA                | 16 channels                                                      |

| PIT                | yes                                                              |

| SWT                | yes                                                              |

| FCU                | yes                                                              |

| Ethernet           | 100 Mbits MII-Lite                                               |

| Video Encoder      | 8bpp/12bpp                                                       |

| Audio Interface    | 6x Stereo (4x synchronous + 2x synchronous/asynchronous)         |

| ADC (10-bit)       | 1× 4 channels + V <sub>DD_IO</sub> + V <sub>DDCore</sub> + TSens |

| Timer I/O (eTimer) | 1×6 channels                                                     |

| SCI (LINFlex)      | 2×                                                               |

## Overview

Table 1. Device summary (continued)

| Feature                        | MPC5606E                                                                                                                               |  |  |  |  |  |  |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| reature                        | 121 MAPBGA                                                                                                                             |  |  |  |  |  |  |

| SPI (DSPI)                     | DSPI_0: 2 chip selects<br>DSPI_1: 2 chip selects<br>DSPI_2: 4 chip selects                                                             |  |  |  |  |  |  |

| CAN (FlexCAN)                  | 1X                                                                                                                                     |  |  |  |  |  |  |

| IIC                            | 2×                                                                                                                                     |  |  |  |  |  |  |

| Supply                         | 3.3 V IO 1.2 V Core with dedicated ballast source pin in two modes: • internal ballast or • external supply (using power on reset pin) |  |  |  |  |  |  |

| Phase Lock Loop (PLL)          | 1× FMPLL                                                                                                                               |  |  |  |  |  |  |

| Internal RC Oscillator         | 16 MHz                                                                                                                                 |  |  |  |  |  |  |

| External crystal<br>Oscillator | 4 MHz - 40 MHz                                                                                                                         |  |  |  |  |  |  |

| CRC                            | yes                                                                                                                                    |  |  |  |  |  |  |

| Debug                          | JTAG                                                                                                                                   |  |  |  |  |  |  |

| Ambient Temperature            | −40 to 125 °C                                                                                                                          |  |  |  |  |  |  |

# 1.2 Block diagram

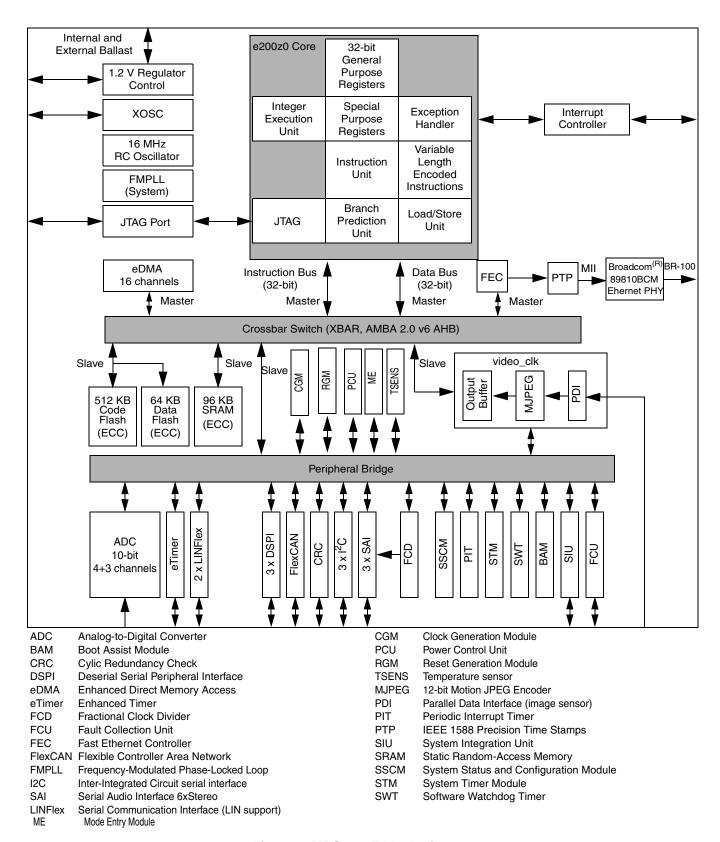

Figure 1 shows a top-level block diagram of the MPC5606E MCU.

Figure 1. MPC5606E block diagram

# 2.1 Package pinouts

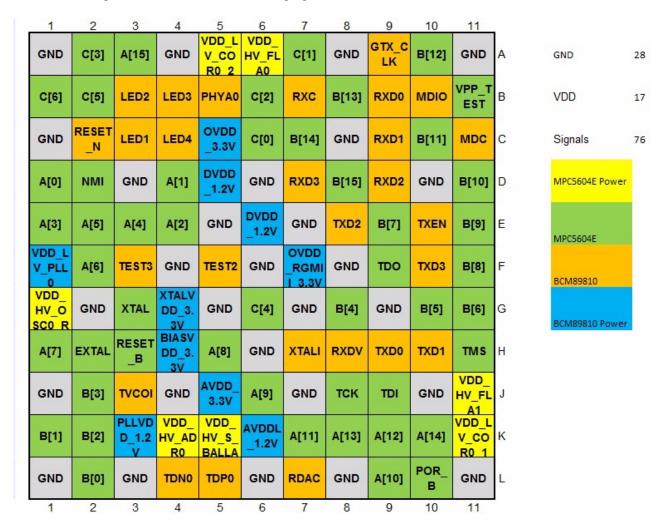

The 121 MAPBGA pinouts are shown in the following figure.

Figure 2. 121 MAPBGA pinout(top view)

# 2.2 Signal descriptions

The following sections provide signal descriptions and related information about the functionality and configuration of the MPC5606E devices.

# 2.2.1 Power supply and reference voltage pins

Table 2 lists the power supply and reference voltage for the MPC5606E devices.

Table 2. Supply pins

|                          |                                       | Supply                                                                                                                                                    | Pin        |

|--------------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Port Pin                 | Multi-bonded Power<br>Supplies/Ground | Description                                                                                                                                               | 121 MAPBGA |

|                          | VREG control and po                   | wer supply pins. Pins available on 121 MAPBGA-pin package.                                                                                                |            |

| V <sub>DD_HV_S_BAL</sub> | V <sub>DD_HV_S_BALLAST0</sub>         | Ballast Source/Supply Voltage                                                                                                                             | K5         |

|                          | ADC0 reference and                    | supply voltage. Pins available on 121 MAPBGA-pin package.                                                                                                 |            |

| V <sub>DD_HV_ADC</sub>   | $V_{DD\_HV\_ADR0}$                    | ADC0 high reference voltage with respect to ground (V <sub>SS_HV_ADC</sub> )                                                                              | K4         |

|                          | Power supply pi                       | ns (3.3 V). Pins available on 121 MAPBGA-pin package.                                                                                                     |            |

| V <sub>DD_HV</sub>       | V <sub>DD_HV_FLA1</sub>               | Code and data flash supply voltage                                                                                                                        | J11        |

| V <sub>DD_HV</sub>       | V <sub>DD_HV_FLA0</sub>               | Code and data flash supply voltage                                                                                                                        | A6         |

| V <sub>DD_HV</sub>       | V <sub>DD_HV_OSC0_REG0</sub>          | Code and data flash supply voltage                                                                                                                        | G1         |

|                          | Power supply pi                       | ns (1.2 V). Pins available on 121 MAPBGA-pin package.                                                                                                     |            |

| V <sub>DD_LV</sub>       | V <sub>DD_LV_PLL0</sub>               | 1.2 V PLL supply voltage                                                                                                                                  | F1         |

| V <sub>DD_LV</sub>       | V <sub>DD_LV_COR0_1</sub>             | 1.2 V supply pins for core logic and code Flash. Decoupling capacitor must be connected between these pins and the nearest V <sub>SS_LV_COR0_1</sub> pin. | K11        |

| V <sub>SS_LV</sub>       | V <sub>SS_LV_COR0_2</sub>             | 1.2 V supply pins for core logic and code Flash. Decoupling capacitor must be connected between these pins and the nearest V <sub>DD_LV_COR0_2</sub> pin. | A5         |

|                          |                                       | BCM89810 Supply Pins.                                                                                                                                     | ,          |

| OVDD_RGMII               | PWR                                   | 2.5V or 3.3 V for RGMII pads; 3.3V for MII pads.                                                                                                          | F7         |

| OVDD                     | PWR                                   | 2.5 V or 3.3V for non RGMII pads. When 2.5V is selected, RESET, MDIO, and LED pins are not 3.3V tolerant                                                  | C5         |

| DVDD                     | PWR                                   | 1.2V power for digital core.                                                                                                                              | D5, E6     |

| AVDDL                    | PWR                                   | 1.2V power for analog core.                                                                                                                               | K6         |

| AVDD                     | PWR                                   | 3.3V power for analog core.                                                                                                                               | J5         |

**Table 2. Supply pins (continued)**

|          |                                       | Supply                                                                                                                                                                | Pin        |

|----------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Port Pin | Multi-bonded Power<br>Supplies/Ground | Description                                                                                                                                                           | 121 MAPBGA |

| XTALVDD  | PWR                                   | 3.3V Crystal Supply.  Ferrite Bead  3.3V  0.1 uF                                                                                                                      | G4         |

| PLLVDD   | PWR                                   | 1.2V PLL Supply.  PLLVDD Ferrite Bead 1.2V  0.1 uF  10 uF                                                                                                             | КЗ         |

| BIASVDD  | PWR                                   | Bias VDD. +3.3V. Normally filtered with a low resistance ferrite bead such as a Murata® BLM11A601S or equivalent, as well as a 0.1µF capacitor.  Ferrite Bead  0.1 uF | H4         |

# 2.2.2 System pins

Table 3 and Table 4 contain information on pin functions for the MPC5606E devices. The pins listed in Table 3 are single-function pins. The pins shown in Table 4 are multi-function pins, programmable via their respective Pad Configuration Register (PCR) values.

Table 3. System pins

| Symbol                 | Description                                                                                                                                                                                                                                                                                   | Direction                  | 121MA<br>PBGA |  |  |  |  |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------|--|--|--|--|

| MP5604E Dedicated pins |                                                                                                                                                                                                                                                                                               |                            |               |  |  |  |  |

| NMI                    | Non-maskable Interrupt                                                                                                                                                                                                                                                                        | Input only                 | D2            |  |  |  |  |

| XTAL                   | Oscillator amplifier output                                                                                                                                                                                                                                                                   | Output only                | G3            |  |  |  |  |

| EXTAL                  | Input for oscillator amplifier circuit and internal clock generator                                                                                                                                                                                                                           | Input only                 | H2            |  |  |  |  |

| TDI <sup>1</sup>       | JTAG test data input                                                                                                                                                                                                                                                                          | Input only                 | J9            |  |  |  |  |

| TMS <sup>1</sup>       | JTAG state machine control                                                                                                                                                                                                                                                                    | Input only                 | H11           |  |  |  |  |

| TCK <sup>1</sup>       | JTAG clock                                                                                                                                                                                                                                                                                    | Input only                 | J8            |  |  |  |  |

| TDO <sup>1</sup>       | JTAG test data output                                                                                                                                                                                                                                                                         | Output only                | F9            |  |  |  |  |

|                        | Reset pin                                                                                                                                                                                                                                                                                     |                            |               |  |  |  |  |

| RESET_B                | Bidirectional reset with Schmitt trigger characteristics and noise filter                                                                                                                                                                                                                     | Bidirectional              | НЗ            |  |  |  |  |

| POR_B                  | Power-on reset                                                                                                                                                                                                                                                                                | Input only                 | L10           |  |  |  |  |

|                        | BCM89810 Supply Pins                                                                                                                                                                                                                                                                          |                            |               |  |  |  |  |

| RESET_N                | RESET. Active-low, Schmitt Trigger input. The BCM89810 requires a hardware RESET prior to normal operation. configuration settings obtained via hardware strap option pins are latched on the rising edge of RESET.                                                                           | I/O <sub>PU</sub> , CS, ST | C2            |  |  |  |  |

| XTALI                  | 25 MHz Crystal Oscillator Input/Output. A continuous 25 MHz reference clock must be supplied to the BCM89810 by connecting a 25 MHz crystal between these two pins or by driving XTALI with an external 25 MHz clock. when using a crystal, connect a loading capacitor from each pin to GND. | I/XT                       | H7            |  |  |  |  |

Additional board pull resistors are recommended when JTAG pins are not being used on the board or application.

# 2.2.3 Pin muxing

Table 4 defines the pin list and muxing for the MPC5606E devices.

Each row of Table 4 shows all the possible ways of configuring each pin, via "alternate functions". The default function assigned to each pin after reset is the ALT0 function. Pins marked as external interrupt capable can also be used to resume from STOP and HALT mode.

MPC5606E devices provide four main I/O pad types depending of the associated functions:

MPC5606E Microcontroller Data Sheet, Rev. 4

- Slow pads are the most common, providing a compromise between transition time and low electromagnetic emission.

- *Medium pads* provide fast enough transition for serial communication channels with controlled current to reduce electromagnetic emission.

- Fast pads provide maximum speed. They are used for improved Nexus debugging capability.

Medium and Fast pads can be used in slow configuration to reduce the electromagnetic emissions, at the cost of reducing AC performance.

Table 4. Pin muxing

| MPC5                |                 |                                        |                                                           |                                                         |                                    | Pad s   | peed <sup>5</sup> | Pin               |

|---------------------|-----------------|----------------------------------------|-----------------------------------------------------------|---------------------------------------------------------|------------------------------------|---------|-------------------|-------------------|

| 604E<br>Port<br>pin | PCR<br>register | Alternate function <sup>1,2,6</sup>    | Functions                                                 | Peripheral <sup>3</sup>                                 | I/O<br>direction <sup>4</sup>      | SRC = 0 | SRC = 1           | 121<br>MAPBG<br>A |

|                     |                 |                                        | F                                                         | Port A (16-bit)                                         |                                    |         |                   |                   |

| A[0]                | PCR[0]          | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>— | GPIO[0] D[0] D[11] SIN EIRQ[0]                            | SIUL<br>SAI0<br>—<br>VID<br>DSPI 1<br>SIUL              | I/O<br>I/O<br>—<br>—<br>I<br>I     | Slow    | Medium            | D1                |

| A[1]                | PCR[1]          | ALTO ALT1 ALT2 ALT3 —                  | GPIO[1] D[1] SOUT D[10] EIRQ[1]                           | SIUL<br>SAI0<br>DSPI1<br>—<br>VID<br>SIUL               | I/O<br>I/O<br>O<br>—<br>I          | Slow    | Medium            | D4                |

| A[2]                | PCR[2]          | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>— | GPIO[2] D[2] SCK D[0] D[9] ETC[5] EIRQ[2]                 | SIUL<br>SAI0<br>DSPI1<br>SAI1<br>VID<br>ETIMER0<br>SIUL | I/O<br>I/O<br>I/O<br>I/O<br>I<br>I | Slow    | Medium            | E4                |

| A[3]                | PCR[3]          | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>— | GPIO[3] D[3] — D[0] D[8] SIN EIRQ[3]                      | SIUL<br>SAI0<br>—<br>SAI2<br>VID<br>DSPI2<br>SIUL       | I/O<br>I/O<br>—<br>I/O<br>I        | Slow    | Medium            | E1                |

| A[4]                | PCR[4]          | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>— | GPIO[4]<br>SYNC<br>SOUT<br>—<br>D[7]<br>ETC[3]<br>EIRQ[4] | SIUL<br>SAI0<br>DSPI2<br>—<br>VID<br>ETIMER0<br>SIUL    | I/O<br>I/O<br>O<br>—<br>I<br>I     | Slow    | Medium            | E3                |

Table 4. Pin muxing (continued)

| MPC5                |                 | Alternate<br>r function <sup>1,2,6</sup>    | Functions                                                         |                                                             |                                    | Pad s   | peed <sup>5</sup> | Pin               |  |

|---------------------|-----------------|---------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------|------------------------------------|---------|-------------------|-------------------|--|

| 604E<br>Port<br>pin | PCR<br>register |                                             |                                                                   | Peripheral <sup>3</sup>                                     | I/O<br>direction <sup>4</sup>      | SRC = 0 | SRC = 1           | 121<br>MAPBG<br>A |  |

| A[5]                | PCR[5]          | ALTO ALT1 ALT2 ALT3 — —                     | GPIO[5]<br>SYNC<br>SCK<br>D[0]<br>CLK<br>ETC[4]<br>EIRQ[5]        | SIUL<br>SAI1<br>DSPI2<br>SAI1<br>VID<br>ETIMER0<br>SIUL     | I/O<br>I/O<br>I/O<br>I/O<br>I<br>I | Medium  | Fast              | E2                |  |

| A[6]                | PCR[6]          | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>—      | GPIO[6]<br>SYNC<br>CS0<br>—<br>VSYNC<br>D[0]<br>ETC[1]<br>EIRQ[6] | SIUL<br>SAI2<br>DSPI2<br>—<br>VID<br>VID<br>ETIMER0<br>SIUL | I/O<br>I/O<br>I/O<br>—<br>I<br>I   | Slow    | Medium            | F2                |  |

| A[7]                | PCR[7]          | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>—<br>— | GPIO[7] BCLK CS1 — HREF D[1] ETC[2] EIRQ[7]                       | SIUL<br>SAI0<br>DSPI2<br>—<br>VID<br>VID<br>ETIMER0<br>SIUL | I/O<br>I/O<br>I/O<br>—<br>I<br>I   | Slow    | Medium            | H1                |  |

| A[8]                | PCR[8]          | ALTO ALT1 ALT2 ALT3 — — —                   | GPIO[8]<br>BCLK<br>CS0<br>D[0]<br>D[6]<br>RX<br>EIRQ[8]           | SIUL<br>SAI1<br>DSPI1<br>SAI2<br>VID<br>LIN1<br>SIUL        | I/O<br>I/O<br>I/O<br>I/O<br>I<br>I | Slow    | Medium            | H5                |  |

| A[9]                | PCR[9]          | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—           | GPIO[9]<br>BCLK<br>CS1<br>TX<br>D[5]<br>EIRQ[9]                   | SIUL<br>SAI2<br>DSPI1<br>LIN1<br>VID<br>SIUL                | I/O<br>I/O<br>I/O<br>O<br>I        | Slow    | Medium            | J6                |  |

| A[10]               | PCR[10]         | ALTO ALT1 ALT2 ALT3 — —                     | GPIO[10]<br>MCLK<br>ETC[5]<br>—<br>D[4]<br>SIN<br>EIRQ[10]        | SIUL<br>SAI2<br>ETIMER0<br>—<br>VID<br>DSPI0<br>SIUL        | I/O<br>I/O<br>I/O<br>—<br>I<br>I   | Slow    | Medium            | L9                |  |

Table 4. Pin muxing (continued)

| MPC5                |                 | Alternate function <sup>1,2,6</sup>    | Functions                                                    |                                                             |                                | Pad speed <sup>5</sup> |         | Pin               |

|---------------------|-----------------|----------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------|--------------------------------|------------------------|---------|-------------------|

| 604E<br>Port<br>pin | PCR<br>register |                                        |                                                              | Peripheral <sup>3</sup>                                     | I/O<br>direction <sup>4</sup>  | SRC = 0                | SRC = 1 | 121<br>MAPBG<br>A |

| A[11]               | PCR[11]         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>— | GPIO[11]<br>TX<br>CS1<br>CS0<br>D[3]<br>RX<br>RX             | SIUL<br>CANO<br>DSPIO<br>DSPI1<br>VID<br>LINO<br>LIN1       | I/O<br>O<br>O<br>I/O<br>I<br>I | Slow                   | Medium  | K7                |

| A[12]               | PCR[12]         | ALTO ALT1 ALT2 ALT3 — —                | GPIO[12]<br>TX<br>CS0<br>TX<br>D[2]<br>RX<br>EIRQ[11]        | SIUL<br>LINO<br>DSPIO<br>LIN1<br>VID<br>CANO<br>SIUL        | I/O<br>O<br>I/O<br>O<br>I<br>I | Slow                   | Medium  | К9                |

| A[13]               | PCR[13]         | ALT0<br>ALT1<br>ALT2<br>ALT3           | GPIO[13]<br>CLK<br>F[0]<br>CS0<br>EIRQ[12]                   | SIUL<br>IIC1<br>FCU0<br>DSPI0<br>SIUL                       | I/O<br>I/O<br>O<br>I/O<br>I    | Slow                   | Medium  | K8                |

| A[14]               | PCR[14]         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—      | GPIO[14] DATA F[1] CS1 SIN EIRQ[13]                          | SIUL<br>IIC1<br>FCU0<br>DSPI0<br>DSPI0<br>SIUL              | I/O<br>I/O<br>O<br>O<br>I      | Slow                   | Medium  | K10               |

| A[15]               | PCR[15]         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>— | GPIO[15]<br>SCK<br>PPS3<br>MCLK<br>SCK<br>ETC[0]<br>EIRQ[18] | SIUL<br>DSPI0<br>CE_RTC<br>SAI1<br>DSPI1<br>ETIMER0<br>SIUL | I/O<br>I/O<br>O<br>I/O<br>I    | Slow                   | Medium  | A3                |

|                     |                 |                                        | 1                                                            | Port B (16-bit)                                             |                                |                        |         |                   |

| B[0]                | PCR[16]         | ALT0<br>ALT1<br>ALT2<br>ALT3           | GPIO[16]<br>TX<br>ALARM2<br>BCLK<br>AN[0]                    | SIUL<br>CAN0<br>CE_RTC<br>SAI1<br>ADC0 <sup>6</sup>         | I/O<br>O<br>O<br>I/O<br>I      | Slow                   | Medium  | L2                |

| B[1]                | PCR[17]         | ALTO<br>ALT1<br>ALT2<br>ALT3<br>—<br>— | GPIO[17]  — D[0] AN[1] RX TRIGGER2                           | SIUL  — SAI1 ADC0 <sup>6</sup> CAN0 CE_RTC                  | I/O<br>—<br>—<br>I/O<br>I<br>I | Slow                   | Medium  | K1                |

MPC5606E Microcontroller Data Sheet, Rev. 4

Table 4. Pin muxing (continued)

| MPC5                |                 |                                        | Functions Peripheral <sup>3</sup>                             |                                                                         | Pad speed <sup>5</sup>           |         | Pin     |                   |

|---------------------|-----------------|----------------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------|---------|---------|-------------------|

| 604E<br>Port<br>pin | PCR<br>register | Alternate function <sup>1,2,6</sup>    |                                                               | Peripheral <sup>3</sup>                                                 | I/O<br>direction <sup>4</sup>    | SRC = 0 | SRC = 1 | 121<br>MAPBG<br>A |

| B[2]                | PCR[18]         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—      | GPIO[18]<br>TX<br>PPS2<br>ALARM1<br>AN[2]<br>TRIGGER1         | SIUL<br>LINO<br>CE_RTC<br>CE_RTC<br>ADC0 <sup>6</sup><br>CE_RTC         | I/O<br>O<br>O<br>O<br>I          | Slow    | Medium  | K2                |

| B[3]                | PCR[19]         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>— | GPIO[19]<br>ETC[2]<br>SOUT<br>PPS1<br>AN[3]<br>RX<br>EIRQ[14] | SIUL<br>ETIMERO<br>DSPIO<br>CE_RTC<br>ADCO <sup>6</sup><br>LINO<br>SIUL | I/O<br>I/O<br>I/O<br>O<br>I<br>I | Slow    | Medium  | J2                |

| B[4]                | PCR[20]         | ALT0<br>ALT1<br>ALT2<br>ALT3           | GPI[20]<br>—<br>—<br>—<br>RX_DV                               | SIUL<br><br><br>FEC                                                     | <br> -<br> -<br> -               | Slow    | Medium  | G8                |

| B[5]                | PCR[21]         | ALT0<br>ALT1<br>ALT2<br>ALT3           | GPIO[21]<br>TX_D0<br>DEBUG[0]                                 | SIUL<br>FEC<br>SSCM                                                     | I/O<br>O<br>I/O                  | Slow    | Medium  | G10               |

| B[6]                | PCR[22]         | ALT0<br>ALT1<br>ALT2<br>ALT3           | GPIO[22]<br>TX_D1<br>DEBUG[1]                                 | SIUL<br>FEC<br>SSCM                                                     | I/O<br>O<br>I/O                  | Slow    | Medium  | G11               |

| B[7]                | PCR[23]         | ALT0<br>ALT1<br>ALT2<br>ALT3           | GPIO[23]<br>TX_D2<br>DEBUG[2]                                 | SIUL<br>FEC<br>SSCM                                                     | I/O<br>O<br>I/O                  | Slow    | Medium  | E9                |

| B[8]                | PCR[24]         | ALT0<br>ALT1<br>ALT2<br>ALT3           | GPIO[24]<br>TX_D3<br>DEBUG[3]                                 | SIUL<br>FEC<br>SSCM                                                     | I/O<br>O<br>I/O                  | Slow    | Medium  | F11               |

| B[9]                | PCR[25]         | ALT0<br>ALT1<br>ALT2<br>ALT3           | GPIO[25]<br>TX_EN<br>DEBUG[4]                                 | SIUL<br>FEC<br>SSCM                                                     | I/O<br>O<br>I/O                  | Slow    | Medium  | E11               |

| B[10]               | PCR[26]         | ALT0<br>ALT1<br>ALT2<br>ALT3           | GPIO[26]<br>MDC<br>DEBUG[5]                                   | SIUL<br>FEC<br>SSCM                                                     | I/O<br>O<br>I/O                  | Slow    | Medium  | D11               |

Table 4. Pin muxing (continued)

| MPC5                |                 |                                        |                                                            |                                                          |                                | Pad speed <sup>5</sup> |         | Pin               |  |

|---------------------|-----------------|----------------------------------------|------------------------------------------------------------|----------------------------------------------------------|--------------------------------|------------------------|---------|-------------------|--|

| 604E<br>Port<br>pin | PCR<br>register | Alternate function <sup>1,2,6</sup>    | Functions                                                  | Peripheral <sup>3</sup>                                  | I/O<br>direction <sup>4</sup>  | SRC = 0                | SRC = 1 | 121<br>MAPBG<br>A |  |

| B[11]               | PCR[27]         | ALT0<br>ALT1<br>ALT2<br>ALT3           | GPIO[27]<br>MDIO<br>DEBUG[6]                               | SIUL<br>FEC<br>SSCM                                      | I/O<br>I/O<br>I/O              | Slow                   | Medium  | C10               |  |

| B[12]               | PCR[28]         | ALT0<br>ALT1<br>ALT2<br>ALT3           | GPIO[28]  — DEBUG[7]  — TX_CLK                             | SIUL<br>—<br>SSCM<br>—<br>FEC                            | I/O<br>—<br>I/O<br>—<br>I      | Slow                   | Medium  | A10               |  |

| B[13]               | PCR[29]         | ALT0<br>ALT1<br>ALT2<br>ALT3           | GPI[29]<br>—<br>—<br>—<br>RX_D0                            | SIUL<br><br><br>FEC                                      | <br> -<br> -<br> -<br>         | Slow                   | Medium  | B8                |  |

| B[14]               | PCR[30]         | ALT0<br>ALT1<br>ALT2<br>ALT3           | GPI[30]<br><br><br><br>RX_D1                               | SIUL<br><br><br>FEC                                      | <br> -<br> -<br> -<br>         | Slow                   | Medium  | C7                |  |

| B[15]               | PCR[31]         | ALT0<br>ALT1<br>ALT2<br>ALT3           | GPI[31]<br>—<br>—<br>—<br>RX_D2                            | SIUL<br>—<br>—<br>—<br>FEC                               | <br> -<br> -<br> -<br>         | Slow                   | Medium  | D8                |  |

|                     |                 |                                        |                                                            | Port C (7 bit)                                           |                                |                        |         |                   |  |

| C[0]                | PCR[32]         | ALTO<br>ALT1<br>ALT2<br>ALT3           | GPI[32]<br><br><br><br>RX_D3                               | SIUL<br><br><br>FEC                                      | <br> -<br> -<br> -<br>         | Slow                   | Medium  | C6                |  |

| C[1]                | PCR[33]         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—      | GPI[33]<br>—<br>—<br>—<br>RX_CLK<br>EIRQ[15]               | SIUL  FEC SIUL                                           | <br> -<br> -<br> -<br> -<br> - | Slow                   | Medium  | A7                |  |

| C[2]                | PCR[34]         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>— | GPIO[34]<br>ETC[0]<br>TX<br>PPS1<br>D[0]<br>RX<br>EIRQ[16] | SIUL<br>ETIMERO<br>CANO<br>CE_RTC<br>VID<br>LINO<br>SIUL | I/O<br>I/O<br>O<br>O<br>I<br>I | Slow                   | Medium  | B6                |  |

Table 4. Pin muxing (continued)

| MPC5                |                 |                                        |                                                                         |                                                               |                                  | Pad s   | peed <sup>5</sup> | Pin               |

|---------------------|-----------------|----------------------------------------|-------------------------------------------------------------------------|---------------------------------------------------------------|----------------------------------|---------|-------------------|-------------------|

| 604E<br>Port<br>pin | PCR<br>register | Alternate function <sup>1,2,6</sup>    | Functions                                                               | Peripheral <sup>3</sup>                                       | I/O<br>direction <sup>4</sup>    | SRC = 0 | SRC = 1           | 121<br>MAPBG<br>A |

| C[3]                | PCR[35]         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>— | GPIO[35]<br>ETC[1]<br>TX<br>SYNC<br>D[1]<br>RX<br>EIRQ[17]              | SIUL<br>ETIMERO<br>LINO<br>SAI1<br>VID<br>CANO<br>SIUL        | I/O<br>I/O<br>O<br>I/O<br>I      | Slow    | Medium            | A2                |

| C[4]                | PCR[36]         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—<br>— | GPIO[36]<br>CLK_OUT<br>ETC[4]<br>MCLK<br>TRIGGER1<br>ABS[0]<br>EIRQ[19] | SIUL<br>MC_CGL<br>ETIMER0<br>SAI0<br>CE_RTC<br>MC_RGM<br>SIUL | I/O<br>O<br>I/O<br>I/O<br>I<br>I | Medium  | Fast              | G6                |

| C[5]                | PCR[37]         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—      | GPIO[37]<br>CLK<br>ETC[3]<br>CS2<br>ABS[2]<br>EIRQ[20]                  | SIUL<br>IIC0<br>ETIMER0<br>DSPI2<br>MC_RGM<br>SIUL            | I/O<br><br>I/O<br>O<br>I         | Slow    | Medium            | B2                |

| C[6]                | PCR[38]         | ALT0<br>ALT1<br>ALT2<br>ALT3<br>—      | GPIO[38]<br>DATA<br>CS0<br>CS3<br>FAB<br>EIRQ[21]                       | SIUL<br>IIC0<br>DSPI1<br>DSPI2<br>MC_RGM<br>SIUL              | I/O<br>—<br>I/O<br>O<br>I        | Slow    | Medium            | B1                |

<sup>&</sup>lt;sup>1</sup> ALT0 is the primary (default) function for each port after reset.

The following conventions are used in the following table:

- I = Input

- O = Output

- I/O = Bidirectional

- OT = Tristateable signal

Alternate functions are chosen by setting the values of the PCR.PA bitfields inside the SIU module. PCR.PA = 00 → ALT0; PCR.PA = 01 → ALT1; PCR.PA = 10 → ALT2; PCR.PA = 11 → ALT3. This is intended to select the output functions; to use one of the input functions, the PCR.IBE bit must be written to '1', regardless of the values selected in the PCR.PA bitfields. For this reason, the value corresponding to an input only function is reported as "—".

<sup>&</sup>lt;sup>3</sup> Module included on the MCU.

Multiple inputs are routed to all respective modules internally. The input of some modules must be configured by setting the values of the PSMIO.PADSELx bitfields inside the SIUL module.

<sup>&</sup>lt;sup>5</sup> Programmable via the SRC (Slew Rate Control) bits in the respective Pad Configuration Register.

On not use ALT multiplexing when ADC channels are used.

- B = Bias

- PU = Internal pull-up

- PD = Internal pull-down

- SOR = Sample on reset

- CS = Continuously sampled

- ST = Schmitt trigger

- XT = Crystal inputs/outputs pin type

- A = Analog pint type

- D = Digital pin type

- G = RGMII pin type

Table 5. Pin muxing for BCM89810

| Functions | I/O<br>Type                | 121 MAPBGA |

|-----------|----------------------------|------------|

| GTX_CLK   | I <sub>PD</sub><br>OT<br>G | A9         |

| LED1      | I <sub>PU,</sub> O         | C3         |

| LED2      | I <sub>PU,</sub> O         | B3         |

| LED3      | I <sub>PU,</sub> O         | B4         |

| LED4      | I <sub>PU,</sub> O         | C4         |

| MDC       | I <sub>PD</sub> , ST       | C11        |

| MDIO      | I/O <sub>PU</sub> , D, ST  | B10        |

| PHYA0     | I <sub>PD</sub> , SOR      | B5         |

| RDAC      | В                          | L7         |

| RESET_N   | I <sub>PU</sub> , CS, ST   | C2         |

| RXC       | OT, G                      | B7         |

| RXD0      | OT, G                      | B9         |

| RXD1      | OT, G                      | C9         |

| RXD2      | OT, G                      | D9         |

| RXD3      | OT, G                      | D7         |

| RXDV      | OT, G                      | Н8         |

| TDN0      | A, A                       | L4         |

| TDP0      | A, A                       | L5         |

| TEST2     | I <sub>PD</sub> , CS       | F5         |

| TEST3     | I <sub>PD</sub> , CS       | F3         |

| TVCOI     | 0                          | J3         |

MPC5606E Microcontroller Data Sheet, Rev. 4

Table 5. Pin muxing (continued)for BCM89810

| Functions | I/O<br>Type         | 121 MAPBGA |

|-----------|---------------------|------------|

| TXD0      | I <sub>PD</sub> , G | H9         |

| TXD1      | I <sub>PD</sub> , G | H10        |

| TXD2      | I <sub>PD</sub> , G | E8         |

| TXD3      | I <sub>PD</sub> , G | F10        |

| TXEN      | I <sub>PD</sub> , G | E10        |

| XTALI     | I/XT                | H7         |

**Electrical characteristics**

# 3 Electrical characteristics

### 3.1 Introduction

This section contains electrical characteristics of the device as well as temperature and power considerations.

This product contains devices to protect the inputs against damage due to high static voltages. However, it is advisable to take precautions to avoid application of any voltage higher than the specified maximum rated voltages.

To enhance reliability, unused inputs can be driven to an appropriate logic voltage level ( $V_{DD}$  or  $V_{SS}$ ). This can be done by the internal pull-up or pull-down, which is provided by the product for most general purpose pins.

The parameters listed in the following tables represent the characteristics of the device and its demands on the system.

In the tables where the device logic provides signals with their respective timing characteristics, the symbol "CC" for Controller Characteristics is included in the Symbol column.

In the tables where the external system must provide signals with their respective timing characteristics to the device, the symbol "SR" for System Requirement is included in the Symbol column.

### 3.2 Parameter classification

The electrical parameters shown in this supplement are guaranteed by various methods. To give the customer a better understanding, the classifications listed in Table 3 are used and the parameters are tagged accordingly in the tables where appropriate.

| Classification tag | Tag description                                                                                                                                                                                                        |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Р                  | Those parameters are guaranteed during production testing on each individual device.                                                                                                                                   |

| С                  | Those parameters are achieved by the design characterization by measuring a statistically relevant sample size across process variations.                                                                              |

| Т                  | Those parameters are achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted. All values shown in the typical column are within this category. |

| D                  | Those parameters are derived mainly from simulations.                                                                                                                                                                  |

Table 3. Parameter classifications

#### **NOTE**

The classification is shown in the column labeled "C" in the parameter tables where appropriate.

# 3.3 Absolute maximum ratings

Table 4. Absolute Maximum Ratings<sup>1</sup>

| Symbol                               |    | Parameter                                                                                                                            | Conditions                                                            | Min                         | Max <sup>2</sup>              | Unit |

|--------------------------------------|----|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------|-------------------------------|------|

| V <sub>SS</sub>                      | SR | Device ground                                                                                                                        | _                                                                     | V <sub>SS</sub>             | $V_{SS}$                      | V    |

| V <sub>DD_HV_IO</sub>                | SR | 3.3 V Input/Output Supply Voltage (supply). Code Flash supply with V <sub>DD_HV_IO3</sub> and Data Flash with V <sub>DD_HV_IO2</sub> | _                                                                     | V <sub>SS _</sub> 0.3       | V <sub>SS</sub> + 6.0         | V    |

| V <sub>SS_HV_IO</sub>                | SR | 3.3 VInput/Output Supply Voltage (ground). Code Flash ground with V <sub>SS_HV_IO3</sub> and Data Flash with V <sub>SS_HV_IO2</sub>  | _                                                                     | V <sub>SS _</sub> 0.1       | V <sub>SS</sub> + 0.1         | V    |

| V <sub>DD_HV_OSC</sub>               | SR | 3.3 V Crystal Oscillator Amplifier<br>Supply voltage (supply)                                                                        | double-bounde                                                         |                             | <sub>V_IO</sub> segments. See | _    |

| V <sub>SS_HV_OSC</sub>               | SR | 3.3 V Crystal Oscillator Amplifier Supply voltage (ground)                                                                           | V <sub>DD_HV_IO</sub> and                                             | V <sub>SS_HV_IO</sub> speci | fications.                    |      |

| V <sub>DD_HV_ADC0</sub> <sup>3</sup> | SR | 3.3 V ADC_0 Supply and High<br>Reference voltage                                                                                     | _                                                                     | V <sub>SS</sub> _ 0.3       | V <sub>SS</sub> + 6.0         | V    |

| V <sub>SS_HV_ADC0</sub>              | SR | 3.3 V ADC_0 Ground and Low<br>Reference voltage                                                                                      |                                                                       | V <sub>SS</sub> _ 0.1       | V <sub>SS</sub> + 0.1         | V    |

| V <sub>DD_HV_REG</sub>               | SR | 3.3 V Voltage Regulator Supply voltage                                                                                               | _                                                                     | V <sub>SS</sub> _ 0.3       | V <sub>SS</sub> + 6.0         | V    |

| TV <sub>DD</sub>                     | SR | Slope characteristics on all VDD during power up <sup>4</sup>                                                                        | _                                                                     | _                           | 0.1                           | V/us |

| V <sub>DD_LV_COR</sub>               | SR | 1.2 V supply pins for core logic (supply)                                                                                            | _                                                                     | V <sub>SS</sub> _ 0.3       | V <sub>SS</sub> + 1.4         | V    |

| V <sub>SS_LV_COR</sub>               | SR | 1.2 V supply pins for core logic (ground)                                                                                            | _                                                                     | V <sub>SS</sub> _ 0.1       | V <sub>SS</sub> + 0.1         | V    |

| V <sub>IN</sub>                      | SR | Voltage on any pin with respect to ground (V <sub>SS_HV_IO</sub> )                                                                   | _                                                                     | V <sub>SS_HV_IO</sub> _0.3  | V <sub>DD_HV_IO</sub> +0.5    | V    |

| I <sub>INJPAD</sub>                  | SR | Input current on any pin during overload condition                                                                                   |                                                                       | -10                         | 10                            | mA   |

| I <sub>INJSUM</sub>                  | SR | Absolute sum of all input currents during overload condition                                                                         | _                                                                     | -50                         | 50                            | mA   |

| T <sub>STORAGE</sub>                 | SR | Storage temperature                                                                                                                  | _                                                                     | <b>-</b> 55                 | 150                           | °C   |

| T <sub>J</sub>                       | SR | Junction temperature under bias                                                                                                      | _                                                                     | -40                         | 132                           | °C   |

| T <sub>A</sub>                       | SR | Ambient temperature under bias                                                                                                       | f <sub>CPU</sub> <64 MHz                                              | -40                         | 125                           | °C   |

|                                      |    |                                                                                                                                      | f <sub>CPU</sub> <64 MHz<br>Video use<br>case with<br>internal supply | -40                         | 105                           | °C   |

|                                      |    | BCM89810 Absolute                                                                                                                    | Maximum Ratin                                                         | ngs                         |                               | •    |

| OVDD                                 |    | Supply voltage                                                                                                                       |                                                                       | GND-0.3                     | 3.8                           | V    |

|                                      |    |                                                                                                                                      |                                                                       |                             |                               |      |

#### **Electrical characteristics**

| Symbol           | Parameter           | Conditions | Min     | Max <sup>2</sup> | Unit |

|------------------|---------------------|------------|---------|------------------|------|

| AVDD             | Supply voltage      |            | GND-0.3 | 3.8              | ٧    |

| BIASVDD          | Supply voltage      |            | GND-0.3 | 3.8              | V    |

| XTALVDD          | Supply voltage      |            | GND-0.3 | 3.8              | V    |

| AVDDL            | Supply voltage      |            | GND-0.3 | 1.4              | V    |

| DVDD             | Supply voltage      |            | GND-0.3 | 1.4              | V    |

| T <sub>STG</sub> | Storage temperature |            | -40     | 125              | °C   |

| V <sub>ESD</sub> | ESD protection      |            | -2500   | 2500             | V    |

<sup>&</sup>lt;sup>1</sup> Functional operating conditions are given in the DC electrical characteristics. Absolute maximum ratings are stress ratings only, and functional operation at the maxima is not guaranteed. Stress beyond the listed maxima may affect device reliability or cause permanent damage to the device.

# 3.4 Recommended operating conditions

#### NOTE

For BCM89810 document please refer to Broadcom website and download the document

Table 5. Recommended operating conditions

| Symbol Parameter                     |    | Conditions                                                 | Min                                                                             | Max <sup>1</sup> | Unit                   |   |

|--------------------------------------|----|------------------------------------------------------------|---------------------------------------------------------------------------------|------------------|------------------------|---|

| V <sub>SS</sub>                      | SR | Device ground                                              | _                                                                               | V <sub>SS</sub>  | $V_{SS}$               | V |

| V <sub>DD_HV_IO</sub>                | SR | 3.3 V input/output supply voltage                          | _                                                                               | 3.0              | 3.6                    | ٧ |

| V <sub>SS_HV_IO</sub>                | SR | Input/output ground voltage                                | _                                                                               | 0                | 0                      | ٧ |

| V <sub>DD_HV_OSC</sub>               | SR | 3.3 V Crystal Oscillator Amplifier Supply voltage (supply) | The oscillator and are double-bound                                             | ed with the \    | V <sub>DD</sub> HV IOx | _ |

| V <sub>SS_HV_OSC</sub>               | SR | 3.3 V Crystal Oscillator Amplifier Supply voltage (ground) | segments. See V <sub>DD_HV_IOx</sub> and V <sub>SS_HV_IOx</sub> specifications. |                  | na                     |   |

| V <sub>DD_HV_ADC0</sub> <sup>2</sup> | SR | 3.3 V ADC_0 Supply and High Reference voltage              | _                                                                               | 3.0              | 3.6                    | V |

| V <sub>DD_HV_REG</sub>               | SR | 3.3 V voltage regulator supply voltage                     | _                                                                               | 3.0              | 3.6                    | ٧ |

| V <sub>DD_LV_EXTCOR</sub>            | SR | Externally supplied core voltage                           | _                                                                               | 1.15             | 1.32                   | ٧ |

| V <sub>DD_LV_REGCOR</sub>            | SR | Internal supply voltage                                    | _                                                                               | _                | _                      | ٧ |

| V <sub>SS_LV_REGCOR</sub>            | SR | Internal reference voltage                                 | _                                                                               | 0                | 0                      | ٧ |

| V <sub>DD_LV_COR</sub>               | SR | Internal supply voltage                                    | _                                                                               | _                | _                      | ٧ |

| V <sub>SS_LV_COR</sub>               | SR | Internal reference voltage                                 |                                                                                 | 0                | 0                      | ٧ |

MPC5606E Microcontroller Data Sheet, Rev. 4

Absolute maximum voltages are currently maximum burn-in voltages. Absolute maximum specifications for device stress have not yet been determined.

MPC5606E's I/O, flash, and oscillator circuit supplies are interconnected. The ADC supply managed independently from other supplies.

<sup>&</sup>lt;sup>4</sup> Guaranteed by device validation.

Table 5. Recommended operating conditions (continued)

| Symbol                  |    | Parameter                        | Conditions                                                            | Min | Max <sup>1</sup> | Unit |

|-------------------------|----|----------------------------------|-----------------------------------------------------------------------|-----|------------------|------|

| V <sub>SS_HV_ADC0</sub> | SR | Ground and Low Reference voltage | _                                                                     | 0   | 0                | ٧    |

| TJ                      | SR | Junction temperature under bias  |                                                                       | -40 | 132              | °C   |

| T <sub>A</sub>          | SR | Ambient temperature under bias   | f <sub>CPU</sub> <64 MHz                                              | -40 | 125              | °C   |

|                         |    |                                  | f <sub>CPU</sub> <64 MHz<br>Video use case<br>with internal<br>supply | -40 | 105              | °C   |

<sup>&</sup>lt;sup>1</sup> Full functionality cannot be guaranteed when voltage drops below 3.0 V. In particular, ADC electrical characteristics and I/Os DC electrical specification may not be guaranteed.

## 3.5 Thermal characteristics

Table 6. Thermal characteristics for 121 MAPBGA

| Symbol             | Parameter                                             | Conditions            | Typical value | Unit |

|--------------------|-------------------------------------------------------|-----------------------|---------------|------|

| $R_{\theta JA}$    | Junction to Ambient Natural Convection <sup>12</sup>  | Single layer board—1s | 42.46         | °C/W |

| $R_{\theta JA}$    | Junction to Ambient Natural Convection <sup>123</sup> | Four layer board—2s2p | 27.18         | °C/W |

| $R_{\theta JMA}$   | Junction to Ambient (@200 ft/min) <sup>13</sup>       | Single layer board—1s | 34.67         | °C/W |

|                    |                                                       | Four layer board—2s2p | 23.75         | °C/W |

| $R_{\theta JB}$    | Junction to Board <sup>2</sup>                        | _                     | 21.27         | °C/W |

| $R_{\theta JCtop}$ | Junction to case <sup>3</sup>                         | _                     | 11.88         | °C/W |

| $\Psi_{JT}$        | Junction to package top <sup>4</sup>                  | Natural Convection    | 0.12          | °C/W |

Junction-to-Ambient Thermal Resistance determined per JEDEC JESD51-3 and JESD51-6. Thermal test board meets JEDEC specification for this package.

# 3.5.1 General notes for specifications at maximum junction temperature

An estimation of the chip junction temperature, T<sub>J</sub>, can be obtained from Equation 1:

$$T_{J} = T_{A} + (R_{\theta JA} * P_{D})$$

Eqn. 1

where:

MPC5606E Microcontroller Data Sheet, Rev. 4

MPC5606E's I/O, flash, and oscillator circuit supplies are interconnected. The ADC supply managed independently from other supplies.

Junction-to-Board thermal resistance determined per JEDEC JESD51-8. Thermal test board meets JEDEC specification for the specified package.

Junction-to-Case at the top of the package determined using MIL-STD 883 Method 1012.1. The cold plate temperature is used for the case temperature. Reported value includes the thermal resistance of the interface layer.

Thermal characterization parameter indicating the temperature difference between the package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT

#### **Electrical characteristics**

$T_A$  = ambient temperature for the package (°C)  $R_{\theta JA}$  = junction to ambient thermal resistance (°C/W)  $P_D$  = power dissipation in the package (W)

The junction to ambient thermal resistance is an industry standard value that provides a quick and easy estimation of thermal performance. There are two values in common usage: the value determined on a single layer board and the value obtained on a board with two planes. For packages such as the PBGA, these values can be different by a factor of two. Which value is closer to the application depends on the power dissipated by other components on the board. The value obtained on a single layer board is appropriate for the tightly packed printed circuit board. The value obtained on the board with the internal planes is usually appropriate if the board has low power dissipation and the components are well separated.

When a heat sink is used, the thermal resistance is expressed in Equation 2 as the sum of a junction to case thermal resistance and a case to ambient thermal resistance:

$$R_{\theta IA} = R_{\theta IC} + R_{\theta CA}$$

Eqn. 2

where:

$\begin{array}{ll} R_{\theta JA} & = \text{junction to ambient thermal resistance (°C/W)} \\ R_{\theta JC} & = \text{junction to case thermal resistance (°C/W)} \\ R_{\theta CA} & = \text{case to ambient thermal resistance (°C/W)} \end{array}$

$R_{\theta JC}$  is device related and cannot be influenced by the user. The user controls the thermal environment to change the case to ambient thermal resistance,  $R_{\theta CA}$ . For instance, the user can change the size of the heat sink, the air flow around the device, the interface material, the mounting arrangement on printed circuit board, or change the thermal dissipation on the printed circuit board surrounding the device.

To determine the junction temperature of the device in the application when heat sinks are not used, the Thermal Characterization Parameter ( $\Psi_{JT}$ ) can be used to determine the junction temperature with a measurement of the temperature at the top center of the package case using Equation 3:

$$T_{I} = T_{T} + (\Psi_{IT} \times P_{D})$$

Eqn. 3

where:

$T_T$  = thermocouple temperature on top of the package (°C)

Ψ<sub>JT</sub> = thermal characterization parameter (°C/W) P<sub>D</sub> = power dissipation in the package (W)

The thermal characterization parameter is measured per JESD51-2 specification using a 40 gauge type T thermocouple epoxied to the top center of the package case. The thermocouple should be positioned so that the thermocouple junction rests on the package. A small amount of epoxy is placed over the thermocouple junction and over about 1 mm of wire extending from the junction. The thermocouple wire is placed flat against the package case to avoid measurement errors caused by cooling effects of the thermocouple wire.

#### References:

Semiconductor Equipment and Materials International

3081 Zanker Road

San Jose, CA 95134 U.S.A.

(408) 943-6900

MIL-SPEC and EIA/JESD (JEDEC) specifications are available from Global Engineering Documents at 800-854-7179 or 303-397-7956.

JEDEC specifications are available on the WEB at http://www.jedec.org.

1. C.E. Triplett and B. Joiner, *An Experimental Characterization of a 272 PBGA Within an Automotive Engine Controller Module*, Proceedings of SemiTherm, San Diego, 1998, pp. 47-54.

### MPC5606E Microcontroller Data Sheet, Rev. 4

- 2. G. Kromann, S. Shidore, and S. Addison, *Thermal Modeling of a PBGA for Air-Cooled Applications*, Electronic Packaging and Production, pp. 53-58, March 1998.

- 3. B. Joiner and V. Adams, *Measurement and Simulation of Junction to Board Thermal Resistance and Its Application in Thermal Modeling*, Proceedings of SemiTherm, San Diego, 1999, pp. 212-220.

# 3.6 Electromagnetic Interference (EMI) characteristics

Table 7. EMI Testing Specifications<sup>1</sup>

| Symbol    | Parameter        | Conditions                            | Clocks                                                    | Frequency<br>Range | Level<br>(Typ) | Unit |

|-----------|------------------|---------------------------------------|-----------------------------------------------------------|--------------------|----------------|------|

| Radiated  | V <sub>EME</sub> | $V_{DD} = 3.3 \text{ V}$              | Oscillator Frequency = 8                                  | 150 kHz-50 MHz     | 2              | dBμV |

| emissions |                  | T <sub>A</sub> = +25 °C               | MHz;<br>System Bus Frequency =                            | 50–150 MHz         | 14             |      |

|           |                  | Device                                | 64 MHz;                                                   | 150–500 MHz        | 11             |      |

|           |                  | Configuration, test conditions and EM | CPU Freq = 64MHZ No PLL Frequency Modulation              | 500–1000 MHz       | 7              |      |

|           |                  | testing per standard IEC61967-2.      |                                                           | IEC Level          | М              |      |

|           |                  |                                       | External Oscillator Freq = 8 MHz System Bus Freq = 64 MHz | 150 kHz-50 MHz     | 1              | dΒμV |

|           |                  |                                       |                                                           | 50–150 MHz         | 11             |      |

|           |                  |                                       |                                                           | 150–500 MHz        | 7              |      |

|           | CPU Freq = 64MHZ | 500–1000 MHz                          | 1                                                         |                    |                |      |

|           |                  |                                       | 2% PLL Freq Modulation                                    | IEC Level          | N              |      |

|           |                  |                                       |                                                           |                    |                |      |

<sup>&</sup>lt;sup>1</sup> EMI testing and I/O port waveforms per standard IEC61967-2.

# 3.7 Electrostatic Discharge (ESD) characteristics

Table 8. ESD ratings<sup>1,2</sup>

| Symbol                |    | Parameter                                      | Conditions | Value         | Unit |

|-----------------------|----|------------------------------------------------|------------|---------------|------|

| V <sub>ESD(HBM)</sub> | SR | Electrostatic discharge (Human Body Model)     | _          | 2000          | V    |

| V <sub>ESD(CDM)</sub> | SR | Electrostatic discharge (Charged Device Model) | _          | 750 (corners) | V    |

|                       |    |                                                |            | 500 (other)   |      |

All ESD testing is in conformity with CDF-AEC-Q100 Stress Test Qualification for Automotive Grade Integrated Circuits.

A device will be defined as a failure if after exposure to ESD pulses the device no longer meets the device specification requirements. Complete DC parametric and functional testing shall be performed per applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification

# 3.8 Power management electrical characteristics

# 3.8.1 Power Management Overview

The device supports the following power modes:

- Internal voltage regulation mode

- External voltage regulation mode

# 3.8.1.1 MPC5604E Internal voltage regulation mode

In this mode, the following supplies are involved:

•  $V_{DD\ HV\ IO}(3.3V)$  — This is the main supply provided externally.

#### NOTE

1.2V is not generated internally for BCM89810 so the user has to use external power supply mode for applications where BCM89810 is used.

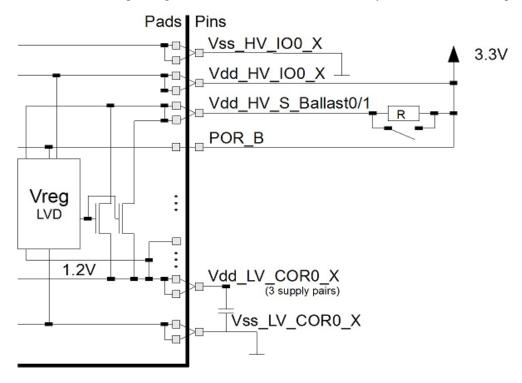

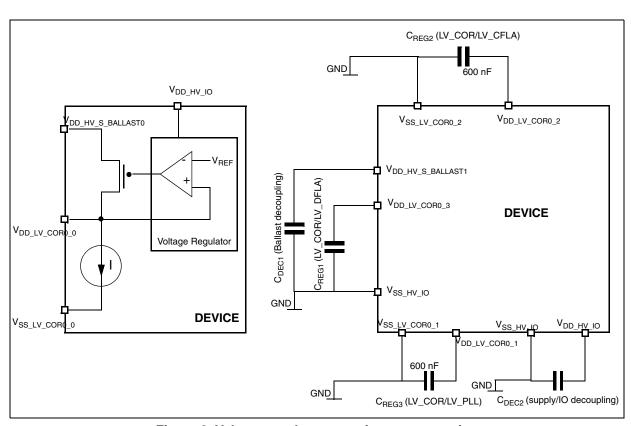

• V<sub>DD\_LV\_COR</sub> (1.2V) — This is the core logic supply. In the internal regulation mode, the core supply is derived from the main supply via an on-chip linear regulator driving an internal PMOS ballast transistor. The PMOS ballast transistors are located in the pad ring and their source connectors are directly bonded to a dedicated pin. See Figure 6.

Figure 6. Internal Regulation Mode

The core supply can also be provided externally. Table 9 shows how to connect  $V_{DD\_HV\_S\_BALLAST}$  pin for internal and external core supply mode.

### **NOTE**

$V_{DD\ HV\ S}$  BALLAST pin is the supply pin, which carries the entire core logic current in the internal regulation mode, while in external regulation mode it is used as a signal to bypass the regulator.

| Table 9. Core Sup | ply Select |

|-------------------|------------|

|                   |            |

| Mode                                                         | V <sub>DD_HV_S_Ballast</sub>  |

|--------------------------------------------------------------|-------------------------------|

| Internal supply mode (via internal PMOS ballast transistors) | V <sub>DD_HV_IO</sub> (3.3V)  |

| External supply mode (e.g., via external switched regulator) | V <sub>DD_LV_COR</sub> (1.2V) |

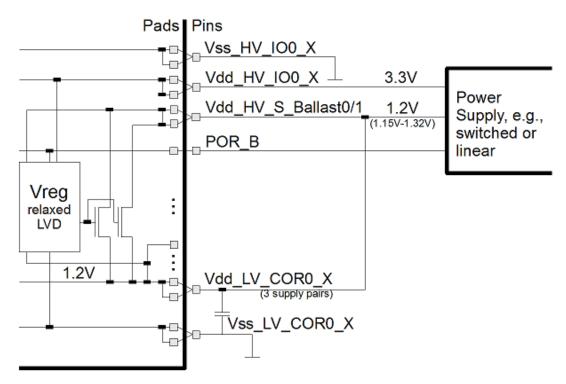

#### 3.8.1.2 MPC5604E External voltage regulation mode

In the external regulation mode, the core supply is provided externally using a switched regulator. This saves on-chip power consumption by avoiding the voltage drop over the ballast transistor. The external supply mode is selected via a board level supply change at the  $V_{DD\ HV\ S\ BALLAST}$  pin.

Figure 7. External Regulation Mode

MPC5606E Microcontroller Data Sheet, Rev. 4 **NXP Semiconductors** 25

#### **NOTE**

In external regulation mode, POR\_B pin should be used to control the power on RESET for the device. POR\_B should be kept low (asserted) as long as the input supplies are unstable or below the specified operating range. Failure to do so may lead to unexpected device operation and erratic reset recovery.

# 3.8.1.3 Recommended power supply sequencing<sup>1</sup>

For MPC5606E, the external supplies need to be maintained as per the following relations:

- $V_{DD\ HV\ IO}$  should be always greater or equal to  $V_{DD\ HV\ S\ Ballast}$

- $V_{DD\ HV\ IO}$  should be always greater than  $V_{DD\ LV\ COR0\ X}$

- ullet  $V_{DD\ HV\ IO}$  should be always greater than  $V_{DD\ HV\ ADC}$

# 3.8.2 Voltage regulator electrical characteristics

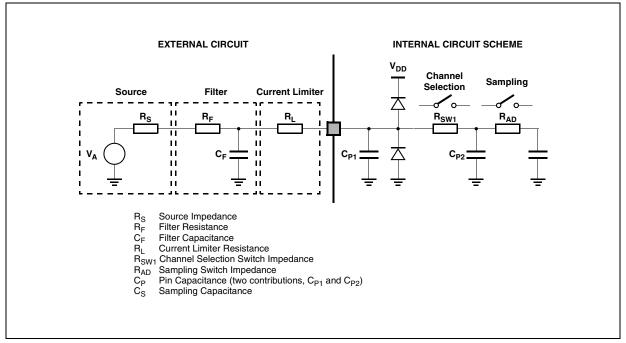

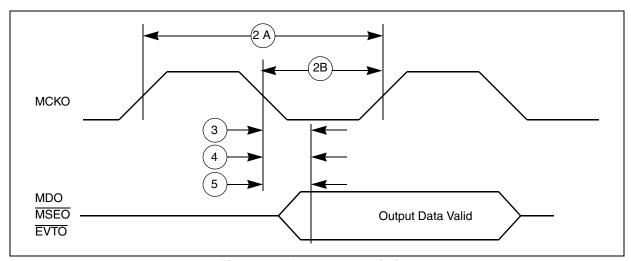

Figure 8. Voltage regulator capacitance connection