(IBM Order Number)

MPC601EC/D (Motorola Order Number)

REV 3

# Advance Information

# **PowerPC 601™ RISC Microprocessor** Hardware Specifications

The PowerPC 601 microprocessor is the first implementation of the PowerPC<sup>TM</sup> family of reduced instruction set computer (RISC) microprocessors. This document contains pertinent physical characteristics of the 601 and 601v. For functional characteristics of the processor, refer to the PowerPC 601 RISC Microprocessor User's Manual.

This document contains the following topics:

| Topic                                                                    | Page |

|--------------------------------------------------------------------------|------|

| Section 1.1, "PowerPC 601 Microprocessor Overview"                       | 2    |

| Section 1.2, "General Parameters"                                        | 3    |

| Section 1.3, "PowerPC 601 Microprocessor Electrical Specifications"      | 4    |

| Section 1.4, "PowerPC 601 Microprocessor Thermal Management Information" | " 14 |

| Section 1.5, "PowerPC 601 Microprocessor Pinout Diagram"                 | 16   |

| Section 1.6, "PowerPC 601 Microprocessor Pinout Listing"                 | 17   |

| Section 1.7, "PowerPC 601 Microprocessor Package Description"            | 19   |

| Appendix A, "General Handling Recommendations"                           | 21   |

In this document, the terms PowerPC 601 RISC microprocessor, 601, and 601v are used to denote the first microprocessor from the PowerPC Architecture™ family. The PowerPC 601 microprocessors are available from IBM as PPC601 and from Motorola as MPC601.

PowerPC, PowerPC 601, and PowerPC Architecture are trademarks of International Business Machines Corp. used by Motorola under license from International Business Machines Corp.

This document contains information on a new product under development by Motorola and IBM. Motorola and IBM reserve the right to change or discontinue this product without notice.

Instruction set and other portions © International Business Machines Corp. 1991-1995

# 1.1 PowerPC 601 Microprocessor Overview

The 601 is the first implementation of the PowerPC family of RISC microprocessors. The 601 implements the 32-bit portion of the PowerPC architecture, which provides 32-bit effective addresses, integer data types of 8, 16, and 32 bits, and floating-point data types of 32 and 64 bits. For 64-bit PowerPC implementations, the PowerPC architecture provides 64-bit integer data types, 64-bit addressing, and other features required to complete the 64-bit architecture.

The 601 is a superscalar processor capable of issuing and retiring three instructions per clock, one to each of three execution units. Instructions can complete out of order for increased performance; however, the 601 makes execution appear sequential.

The 601 integrates three execution units—an integer unit (IU), a branch processing unit (BPU), and a floating-point unit (FPU). The ability to execute three instructions in parallel and the use of simple instructions with rapid execution times yield high efficiency and throughput for 601-based systems. Most integer instructions execute in one clock cycle. The FPU is pipelined so a single-precision multiply-add instruction can be issued every clock cycle.

The 601 provides an on-chip, 32-Kbyte, eight-way set-associative, physically addressed, unified instruction and data cache and an on-chip memory management unit (MMU). The MMU contains a 256-entry, two-way set-associative, unified translation lookaside buffer (UTLB) and provides support for demand-paged virtual memory address translation and variable-sized block translation. Both the UTLB and the cache use least recently used (LRU) replacement algorithms.

The 601 has a 64-bit data bus and a 32-bit address bus. The 601 interface protocol allows multiple masters to compete for system resources through a central external arbiter. Additionally, on-chip snooping logic maintains cache coherency in multiprocessor applications. The 601 supports single-beat and burst data transfers for memory accesses; it also supports both memory-mapped I/O and direct-store addressing.

The 601 uses an advanced CMOS (complementary metal-oxide semiconductor) process technology and maintains full interface compatibility with TTL devices. The 601v is functionally equivalent to the 601, but operates with reduced internal voltages and with reduced power dissipation.

# 1.1.1 PowerPC 601 Microprocessor Features

Major features of the 601 and 601v are as follows:

- High-performance, superscalar microprocessor

- As many as three instructions in execution per clock (one to each of the three execution units)

- Single clock cycle execution for most instructions

- Pipelined FPU for all single-precision and most double-precision operations

- Three independent execution units and two register files

- High instruction and data throughput

- Zero-cycle branch capability

- Programmable static branch prediction on unresolved conditional branches

- Instruction unit capable of fetching eight instructions per clock from the cache

- An eight-entry instruction queue that provides lookahead capability

- Interlocked pipelines with feed-forwarding that control data dependencies in hardware

- Unified 32-Kbyte cache—eight-way set-associative, physically addressed; LRU replacement algorithm

- Memory unit with a two-element read queue and a three-element write queue

- Run-time reordering of loads and stores

- Address translation facilities for 4-Kbyte page size, variable block size, and 256-Mbyte segment size

- A 256-entry, two-way set-associative UTLB

- Four-entry BAT array providing 128-Kbyte to 8-Mbyte blocks

- Four-entry, first-level ITLB

- Hardware table search (caused by UTLB misses) through hashed page tables

- 52-bit virtual address; 32-bit physical address

- Facilities for enhanced system performance

- Bus interface can run at integer factor of operating frequency

- A 64-bit split-transaction external data bus with burst transfers

- Support for address pipelining and limited out-of-order bus transactions

- Snooped copy-back queues for cache block (sector) copy-back operations

- Bus extensions for I/O controller interface operations

- Multiprocessing support features that include the following:

- Hardware enforced, four-state cache coherency protocol (MESI)

- Separate port into cache tags for bus snooping

# 1.2 General Parameters

Table 1 provides a summary of the general parameters of the 601 and 601v.

Table 1. General Parameters of the PowerPC 601 Microprocessor

| Characteristic       | 50, 66, 80 MHz                       | 100 MHz (601v)                        |

|----------------------|--------------------------------------|---------------------------------------|

| Technology           | 0.65 μm CMOS<br>4-level metal        | 0.5 μm CMOS<br>5-level metal          |

| Package              | 304-pin C4FP<br>Surface mount        | 304-pin C4FP<br>Surface mount         |

| Power supplies       | 3.6 V (5%)                           | 2.5 V ± 5% (core)<br>5.0 V ± 5% (I/O) |

| Chip size            | 10.95 mm x 10.95 mm                  | 8.6 mm x 8.6 mm                       |

| Maximum input rating | Chip can sustain 50 mA into any pin. | Chip can sustain 50 mA into any pin.  |

The "v" in 601v denotes that this processor operates at different power supply voltages than other versions of the 601.

# 1.3 PowerPC 601 Microprocessor Electrical Specifications

This section provides both the AC and DC electrical specifications for the 601 and 601v. The following specifications are preliminary and subject to change without notice.

## 1.3.1 PowerPC 601 Microprocessor DC Electrical Characteristics

Table 2 provides the maximum ratings for the 601 and 601v.

**Table 2. Maximum Ratings**

| Rating                                            | Symbol             | Va                             | lue                      | Unit |

|---------------------------------------------------|--------------------|--------------------------------|--------------------------|------|

| 601 and 601v chip performance                     | F <sub>max</sub>   | 50, 66, 80                     | 100 (601v)               | MHz  |

| Supply voltage (core logic)                       | Vdd <sub>INT</sub> | 3.9                            | 2.9                      | V    |

| Supply voltage (I/O circuits)                     | Vdd <sub>I/O</sub> | 3.9                            | 5.5                      | V    |

| Input voltage (Vdd <sub>I/O</sub> = 3.6 V)        | V <sub>in</sub>    | Vdd <sub>I/O</sub> + 2.1       | _                        | V    |

| Input voltage (Vdd <sub>I/O</sub> = 5.0 V)        | V <sub>in</sub>    | _                              | Vdd <sub>I/O</sub> + 0.7 | V    |

| Maximum operating junction temperature            | Ŧį                 | TBD                            | TBD                      | °C   |

| Operating junction temperature range for AC specs | Тј                 | 10 to 85                       | 10 to 85                 | °C   |

| Storage temperature range                         | T <sub>stg</sub>   | 1 °C to 60 °C, relative humidi |                          | °C   |

**Note**: The 601v (100 MHz) requires two power supplies— $Vdd_{INT}$  and  $Vdd_{I/O}$ . The  $Vdd_{I/O}$  level should not exceed the  $Vdd_{INT}$  level by 2.5 volts.  $Vdd_{INT}$  should not be raised greater than 0.5 volts above  $Vdd_{I/O}$ . It is recommended that  $Vdd_{I/O}$  and  $Vdd_{I/O}$  be brought up and powered down simultaneously.

Table 3 provides the DC electrical characteristics for the 601 and 601v.

**Table 3. DC Electrical Characteristics**

| Characteristic                                                                                                                     | Notes                                                          | Symbol                                                   | Min | Max               | Unit           |

|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------|-----|-------------------|----------------|

| Input high voltage                                                                                                                 |                                                                | V <sub>IH</sub>                                          | 2   | 5.5               | V              |

| Input low voltage                                                                                                                  |                                                                | V <sub>IL</sub>                                          | GND | 0.8               | V              |

| Input leakage current<br>GND $<$ V $_{in}$ $<$ Vdd $_{I/O}$ + 1.0 V<br>Vdd $_{I/O}$ + 1.0 V $<$ V $_{in}$ $<$ Vdd $_{I/O}$ + 1.9 V | Vdd <sub>I/O</sub> = 3.6 V<br>Note 1                           | I <sub>in</sub>                                          |     | 10<br>100         | μΑ<br>μΑ       |

| Input leakage current (601v)<br>GND < V <sub>in</sub> < Vdd <sub>I/O</sub> + 0.6 V                                                 | Vdd <sub>I/O</sub> = 5.0 V<br>Note 1                           | I <sub>in</sub>                                          | _   | 10                | μΑ             |

|                                                                                                                                    | @ 85 °C T <sub>j</sub><br>Vdd <sub>I/O</sub> = 3.6 V<br>Note 2 | I <sub>TSI</sub><br>I <sub>TSI</sub><br>I <sub>TSI</sub> |     | 10<br>1000<br>100 | μΑ<br>μΑ<br>μΑ |

**Table 3. DC Electrical Characteristics (Continued)**

| Characteristic                                                                                                                                               | Notes                                                | Symbol                               | Min      | Max                               | Unit     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--------------------------------------|----------|-----------------------------------|----------|

| Hi-Z (off-state) leakage current (601—100 MHz) GND <v<sub>in<vdd<sub>I/O Vdd <sub>I/O</sub><v<sub>in<vdd <sub="">I/O+ 0.25 V</vdd></v<sub></vdd<sub></v<sub> | @ 85 °C T <sub>j</sub><br>Vdd <sub>I/O</sub> = 5.0 V | I <sub>TSI</sub><br>I <sub>TSI</sub> | 2005     | 10<br>1000                        | μΑ<br>μΑ |

| Signal input current<br>V <sub>IL</sub> = 0.8 V and V <sub>IH</sub> = 2.0 V                                                                                  |                                                      | I <sub>IL</sub> , I <sub>IH</sub>    | <u>C</u> | 100                               | μΑ       |

| Output high voltage<br>I <sub>OH</sub> = -10 mA or I <sub>OH</sub> = -20 mA<br>(SC_DRIVE enabled)                                                            |                                                      | V <sub>OH</sub>                      | 2.4      | _                                 | V        |

| Output low voltage (601—50, 66, 80 MHz) $I_{OL} = 10 \text{ mA}$ $I_{OL} = 20 \text{ mA (SC\_DRIVE enabled)}$                                                | Note 3                                               | V <sub>OL</sub><br>V <sub>OL</sub>   |          | 0.45<br>0.55                      | V        |

| Output low voltage (601—100MHz)  I <sub>OL</sub> = 10 mA  I <sub>OL</sub> = 20 mA (SC_DRIVE enabled)                                                         | Note 3                                               | V <sub>OL</sub><br>V <sub>OL</sub>   |          | 0.50<br>0.60                      | V<br>V   |

| 2X_PCLK input low voltage                                                                                                                                    | Note 4                                               | V <sub>il2XP</sub>                   | 0        | 0.6                               | V        |

| 2X_PCLK input high voltage                                                                                                                                   | Note 4                                               | V <sub>ih2XP</sub>                   | 1.8      | 5.5                               | V        |

| Capacitance <sup>5</sup> $V_{in} = 0 \text{ V, f} = 1 \text{ MHz}$ $F_{max} = 50, 66, \text{ and } 80 \text{ MHz}$ $F_{max} = 100 \text{ MHz}$               | Note 5                                               | C <sub>in</sub>                      |          | 10<br>15                          | pF<br>pF |

| Power dissipation (ambient)                                                                                                                                  | 50 MHz                                               | P <sub>D</sub>                       | _        | 5.6 (Typical)<br>6.5 (Worst case) | W        |

| Power dissipation (ambient)                                                                                                                                  | 66 MHz                                               | P <sub>D</sub>                       | _        | 7.0 (Typical)<br>8.2 (Worst case) | W        |

| Power dissipation (ambient)                                                                                                                                  | 80 MHz                                               | P <sub>D</sub>                       | _        | 8.0 (Typical)<br>9.2 (Worst case) | W        |

| Power dissipation (ambient)                                                                                                                                  | 100 MHz<br>Note 6                                    | P <sub>D</sub>                       | _        | 4.0 (Typical)<br>6.0 (Worst case) | W        |

| Vdd <sub>INT</sub> average power supply current                                                                                                              | 100 MHz                                              | Idd <sub>INT</sub>                   |          | 1835 (Worst case)                 | mA       |

| Vdd <sub>I/O</sub> average power supply current                                                                                                              | 100 MHz                                              | Idd <sub>I/O</sub>                   |          | 180 (Worst case)                  | mA       |

#### Notes:

- 1. The 601v (100 MHz) requires 5.0 V Vdd $_{I/O}$ , and will not operate properly at 3.6 V. The 601 (50, 66, and 80 MHz) requires a common supply of 3.6 V for both Vdd $_{INT}$  and Vdd $_{I/O}$ .

- 2. Not applicable when  $Vdd_{I/O} = 5.0 \text{ V}$  (601v, 100 MHz)

- 3. Double drive ( $I_{OH}$  and  $I_{OL}$  = 20 mA) is only available for the following signals— $\overline{DBB}$ ,  $\overline{ABB}$ ,  $\overline{TS}$ ,  $\overline{XATS}$ ,  $\overline{ARTRY}$ , and  $\overline{SHD}$ , and is enabled by asserting SC\_DRIVE.

- 4. Unique 2X\_PCLK input voltages only apply for a 601v (100 MHz) processor.

- 5. Capacitance is periodically sampled rather than 100% tested.

- 6. Typical power dissipation measured at  $Vdd_{INT} = 2.5 \text{ V}$ ,  $Vdd_{I/O} = 5.0 \text{ V}$  while running SPECfp92 suite. System thermal designs should accommodate worst case power dissipation.

#### 1.3.2 PowerPC 601 Microprocessor AC Electrical Characteristics

This section provides the AC electrical characteristics for the 601 and 601v.

#### 1.3.2.1 Input AC Specifications

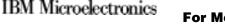

Table 4 provides the clock AC timing specifications as defined in Figure 1

#### **Table 4. Clock AC Timing Specifications**

$Vdd_{I/O} = Nominal \pm 5\%$ ,  $Vdd_{INT} = 3.6 \text{ V} \pm 5\%$  or  $2.5 \text{ V} \pm 5\%$  V (601v, 100 MHz), GND = 0 V dc,  $T_i$  MAX = 85 °C

| Num | Characteristic                            | 50               | MHz | 66               | 66 MHz |                  | MHz | 100               | MHz               | Unit  |

|-----|-------------------------------------------|------------------|-----|------------------|--------|------------------|-----|-------------------|-------------------|-------|

| Num | Characteristic                            | Min              | Max | Min              | Max    | Min              | Max | Min               | Max               | Oille |

|     | Frequency of operation                    | rtc <sup>1</sup> | 50  | rtc <sup>1</sup> | 66     | rtc <sup>1</sup> | 80  | rtc <sup>1</sup>  | 100               | MHz   |

|     | 2X_PCLK rising edge jitter                | _                | _   | _                |        | _                | _   | _                 | ±150 <sup>2</sup> | ps    |

| 1   | 2X_PCLK cycle time                        | 10               | _   | 7.5              | 3      | 6.25             | _   | 5.0               | _                 | ns    |

| 2/1 | 2X_PCLK duty cycle measured at 1.4 V      | 35               | 65  | 35               | 65     | 35               | 65  | 40                | 60                | %     |

| 2a  | 2X_PCLK minimum pulse width at 1.8 V      | _                | _   | 0                | _      | _                | _   | 1.45 <sup>3</sup> | _                 | ns    |

| 2b  | 2X_PCLK minimum pulse width at 0.6 V      | _                | - 5 | )//              | _      | _                | _   | 1.27 <sup>3</sup> | _                 | ns    |

| 3   | PCLK_EN setup to falling edge of 2X_PCLK  | 0.84             | 5   | 0.74             | _      | 0.74             | _   | 0.74              | _                 | ns    |

| 4   | PCLK_EN hold from falling edge of 2X_PCLK | 1.84             | 4   | 1.8 <sup>4</sup> | _      | 1.5 <sup>4</sup> | _   | 1.5 <sup>4</sup>  | _                 | ns    |

Notes: 1. Actual minimum gated by real time clock frequency

- 2. Maximum allowable sum of cycle-to-cycle or long-term jitter

- 3. Guaranteed by design/characterization

- 4. PCLK\_EN is measured from the 1.4 V level of the signal in question to the 1.4 V level of the input 2X\_PCLK.

Notes: V<sub>IH</sub> = 2.0 V, V<sub>IL</sub> = 0.8 V. For the 2X\_PCLK of the 601v (100 MHz), V<sub>IH</sub> = 1.8 V, V<sub>IL</sub> = 0.6 V. The timing diagram should only be referenced in regard to the edge-to-edge measurement of the timing specifications. It is not intended as a functional description of the input and output signals. Refer to the *PowerPC 601 RISC Microprocessor User's Manual* for functional descriptions and their related diagrams for device operation.

Figure 1. PowerPC 601 Microprocessor Clock Input Timing Diagram

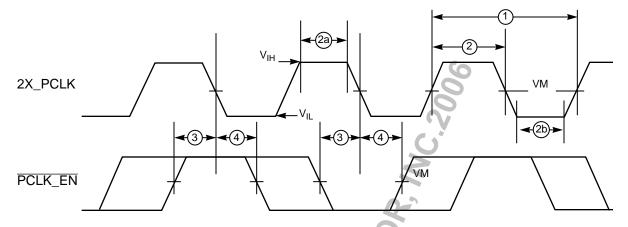

Table 5 provides the input AC timing specifications as defined in Figure 2.

#### **Table 5. Input AC Timing Specifications**

$Vdd_{I/O} = Nominal \pm 5\%$ ,  $Vdd_{INT} = 3.6 \text{ V} \pm 5\%$  or  $2.5 \text{ V} \pm 5\%$  V (601v, 100 MHz), GND = 0 V dc,  $T_i MAX = 85 ^{\circ}C$

| Num  | N<br>O<br>T | Characteristic                                                                                            | 50  | MHz | 66  | MHz | 80 N | /lHz <sup>5</sup> |     | MHz <sup>6</sup><br>)1v) | U N - |

|------|-------------|-----------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|------|-------------------|-----|--------------------------|-------|

|      | Ė           |                                                                                                           | Min | Max | Min | Max | Min  | Max               | Min | Max                      | Ť     |

| 9.0  | 1           | BCLK_EN setup to rising edge of 2X_PCLK (qualified with PCLK_EN being low)                                | 14  | _   | 10  | _   | 7.7  | _                 | 7.8 | _                        | ns    |

| 10.0 | 1           | BCLK_EN hold from rising edge of 2X_PCLK (qualified with PCLK_EN being low)                               | 0.0 | _   | 0.0 | _   | 0.0  | _                 | 0.0 | _                        | ns    |

| 9.1  | 1,2         | Input setup to rising edge of 2X_PCLK for the following signals: ARTRY, DBWO, TS, XATS.                   | 2.7 | _   | 2.5 | _   | 2.7  | _                 | 2.7 | _                        | ns    |

| 10.1 | 1,2         | Input hold from rising edge of 2X_PCLK for the following signals: ARTRY, DBWO, TS, XATS                   | 1.8 | _   | 1.5 | _   | 1.8  | _                 | 1.8 | _                        | ns    |

| 9.2  | 1,2         | Input setup to rising edge of 2X_PCLK for the following signals: ABB, AACK, BG, TA, DBB, DBG, DRTRY, TEA  | 2.7 | _   | 2.5 | _   | 2.7  | _                 | 2.7 | _                        | ns    |

| 10.2 | 1,2         | Input hold from rising edge of 2X_PCLK for the following signals: ABB, AACK, BG, TA, DBB, DBG, DRTRY, TEA | 1.8 | _   | 1.5 | _   | 1.8  | _                 | 1.8 | _                        | ns    |

#### **Table 5. Input AC Timing Specifications (Continued)**

$Vdd_{I/O} = Nominal \pm 5\%, Vdd_{INT} = 3.6 V \pm 5\% \text{ or } 2.5 V \pm 5\% \text{ V } (601v, 100 \text{ MHz}), GND = 0 V dc, T<sub>i</sub> MAX = 85 °C V dc, T<sub>$ </sub>

| Num  | N<br>O<br>T | Characteristic                                               |     |     | MHz 80 MHz <sup>5</sup> |     |     | 100 I<br>(60 | U N - |     |    |

|------|-------------|--------------------------------------------------------------|-----|-----|-------------------------|-----|-----|--------------|-------|-----|----|

|      | Ė           |                                                              | Min | Max | Min                     | Max | Min | Max          | Min   | Max | Ť  |

| 9.3  | 1,3         | Input setup to rising edge of 2X_PCLK for test signals       | 2.5 | _   | 2.5                     | 70  | 2.5 | _            | 2.5   | _   | ns |

| 10.3 | 1,3         | Input hold from rising edge of 2X_PCLK for test signals      | 4.0 | _   | 3.5                     | W.  | 4.0 | _            | 4.0   | _   | ns |

| 9.4  | 1,2,4       | Input setup to rising edge of 2X_PCLK for all other signals  | 2.5 | _   | 2.5                     | _   | 2.5 | _            | 2.5   | _   | ns |

| 10.4 | 1,2,4       | Input hold from rising edge of 2X_PCLK for all other signals | 2.0 | _   | 1.7                     | _   | 2.0 | _            | 2.0   | _   | ns |

#### Input AC timing notes:

- 1. All input specs are measured from the TTL level of the signal in question to the 1.4 V level of the input 2X\_PCLK rising edge, except for PCLK\_EN.

- 2. Input setup and hold times are measured relative to the bus transition point. An internal clock phase is generated by having the PCLK\_EN negated and then asserted on two consecutive falling edges of the 2X\_PCLK. On the assertion of this internal clock, if the BCLK\_EN is asserted, then a bus transition will occur on the next rising edge of the 2X\_PCLK.

- 3. Test signals include: SYS\_QUIESC, RESUME, SCAN\_CTL, SCAN\_CLK, and SCAN\_SIN.

- 4. Signals included are: TSIZ0–TSIZ2, TBST, GBL, TT0–TT3, A0–A31, AP0–AP3, DH0–DH31, DL0–DL31, DP0–DP7, and SHD.

- 5. This specification is for an 80-MHz processor with the interface running at half the processor frequency (40 MHz).

- 6. This specification is for a 100-MHz 601v processor with the interface running at half the processor frequency

**Notes**: 1. The timing diagram should only be referenced in regard to the edge-to-edge measurement of the timing specifications. It is not intended as a functional description of the input and output signals. Refer to the *PowerPC 601 RISC Microprocessor User's Manual* for functional descriptions and their related diagrams for device operation.

2. VM = Midpoint voltage (1.4 V)

Figure 2. PowerPC 601 Microprocessor Input Timing Diagram

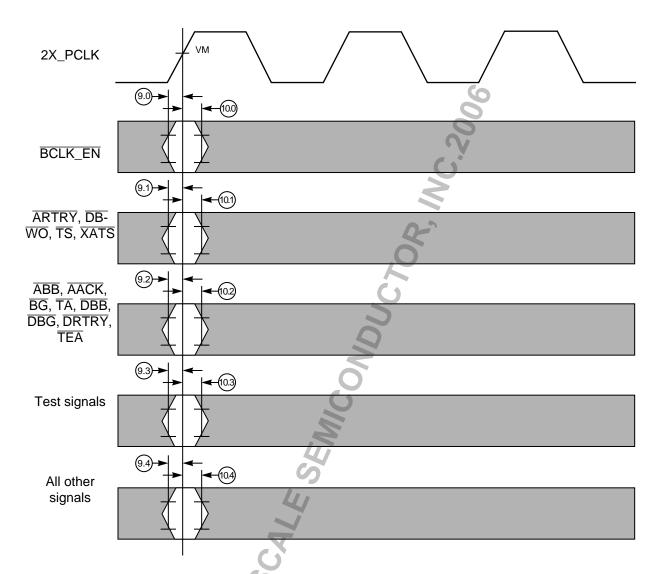

#### 1.3.2.2 Output AC Specifications

The output specifications of the 601 and 601v for both driving high and driving low depend on the capacitive loading on each output and the drive capability enabled for that output. Additionally, the timing specifications for outputs driving low depend on the voltage swing required to drive to 0.8 V (either 5.5–0.8 V or 3.6–0.8 V).

Table 7 provides the output AC timing specifications (shown in Figure 3) as absolute values for a theoretical 0 pF load. In order to derive the actual timing specifications guaranteed for a given set of conditions (capacitive loading, drive capability, and voltage swing), the loading factors provided in Table 6 must be used. The actual specifications are defined as follows:

$t_{\text{nd (actual)}} = t_{\text{table}} + (\text{loading factor } *C_{\text{load}})$

#### where:

$t_{pd (actual)}$  = the specification guaranteed

$t_{table}$  = the value from Table 7

$C_{load}$  = the capacitive loading on that signal in the system (minimum of 20 pF must be used)

For example, if an output buffer for a 50-MHz device is driving a load of 100 pF, the output propagation delay, due to the capacitive load, driving high would be calculated as follows:

$t_{pd (actual)} = 10.5 \text{ ns} + (100 \text{ pF} * 0.047 \text{ ns/pF}) = 15.2 \text{ ns}.$

**Table 6. Loading Factors for Output Signals**

| Loading Factor for Selected     | 50                  | MHz                 | 66 I                | ИНZ                 | 1 08                | ИНz                 | 100 MHz<br>(601v)   |                     |

|---------------------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| Buffer Size                     | Normal <sup>1</sup> | Double <sup>2</sup> |

| Driving low<br>(5.5 V to 0.8 V) | 0.088               | 0.053               | 0.080               | 0.048               | 0.072               | 0.043               | 0.072               | 0.039               |

| Driving low<br>(3.6 V to 0.8V)  | 0.060               | 0.036               | 0.055               | 0.033               | 0.051               | 0.030               | 0.049               | 0.029               |

| Driving high (0.0 V to 2.0 V)   | 0.047               | 0.028               | 0.042               | 0.025               | 0.037               | 0.022               | 0.035               | 0.018               |

Notes: 1. Normal mode means that SC\_DRIVE is negated.

2. Double drive is only available for the following signals: ABB, DBB, SHD, ARTRY, TS, and XATS. Double drive is enabled by strapping the SC\_DRIVE pin to Vdd. (Double drive mode increases the capacitive drive capability of the signal by enabling a second driver.)

#### Table 7. Output AC Timing Specifications (Theoretical 0 pF load)

$Vdd_{I/O} = Nominal \pm 5\%, Vdd_{INT} = 3.6 \ V \pm 5\% \ or \ 2.5 \ V \pm 5\% \ V \ (601v, \ 100 \ MHz), \ GND = 0 \ V \ dc, \ T_j \ MAX = 85 \ ^{\circ}C$  Actual specifications must be derived for a minimum of 20 pF capacitive load (see Table 6).

| Num       | Note          | Characteristic                                                                           | <b>50</b> l | MHz  | 66   | MHz  | 80 N | /Hz <sup>8</sup> |     | MHz <sup>9</sup><br>l1v) | UNI |

|-----------|---------------|------------------------------------------------------------------------------------------|-------------|------|------|------|------|------------------|-----|--------------------------|-----|

|           |               |                                                                                          | Min         | Max  | Min  | Max  | Min  | Max              | Min | Max                      | T   |

| 20.0      | 1–4,<br>7     | 2X_PCLK rising edge to SHD, ARTRY, ABB, DBB, TS, XATS output driven (output enable time) | 3           | _    | 3    | -W   | 3    | _                | 1.9 | _                        | ns  |

| 20.1      | 1, 7          | 2X_PCLK rising edge to all other outputs driven (output enable time)                     | 3           | _    | 3    |      | 3    | _                | 1.9 | _                        | ns  |

| 21.0      | 1–4           | 2X_PCLK rising edge to SHD, ARTRY, ABB, DBB, TS, XATS output valid                       | _           | 8.5  | 2/2/ | 7.5  | _    | 8.5              | _   | 8.5                      | ns  |

| 21.1      | 1             | 2X_PCLK rising edge to all other outputs valid                                           | _           | 10.5 | -    | 8.5  | _    | 10.5             | _   | 10.5                     | ns  |

| 22.0      | 1, 2,<br>5, 7 | 2X_PCLK to TS, XATS output invalid (output hold)                                         | 3           |      | 3    | _    | 3    | _                | 1.6 | _                        | ns  |

| 22.1      | 1, 7          | 2X_PCLK to all other outputs invalid (output hold)                                       | 3           |      | 3    | _    | 3    | _                | 1.2 | _                        | ns  |

| 23.0      | 1, 2,<br>5    | 2X_PCLK rising edge to TS, XATS output high impedance                                    | 45          | 8.5  | _    | 7.5  | _    | 8.5              | _   | 8.5                      | ns  |

| 23.1      | 1             | 2X_PCLK rising edge to all other outputs high impedance                                  | 7           | 10.5 | _    | 8.5  | _    | 10.5             | _   | 10.5                     | ns  |

| 24        | 1–3           | 2X_PCLK rising edge to SHD, ARTRY precharge enable                                       | 1           | 8.5  | 1    | 7.5  | 1    | 8.5              | 0.7 | 8.5                      | ns  |

| 25        | 1–3           | 2X_PCLK rising edge to SHD, ARTRY precharge disable                                      | _           | 21.0 | _    | 16.0 | _    | 21.0             | _   | 21.0                     | ns  |

| 26,<br>29 | 5             | Width of precharge for SHD, ARTRY, ABB, DBB                                              | 11          | _    | 9    | _    | 7    | _                | 6.0 | _                        | ns  |

#### Table 7. Output AC Timing Specifications (Theoretical 0 pF load) (Continued)

$Vdd_{I/O}$  = Nominal  $\pm$  5%,  $Vdd_{INT}$  = 3.6 V  $\pm$  5% or 2.5 V  $\pm$  5% V (601v, 100 MHz), GND = 0 V dc,  $T_j$  MAX = 85 °C Actual specifications must be derived for a minimum of 20 pF capacitive load (see Table 6).

| Num | lum Note Characteristic |                                                  | 50 MHz<br>Characteristic |      | 66 MHz |     | 80 MHz <sup>8</sup> |      | 100 MHz <sup>9</sup><br>(601v) |      | U N |

|-----|-------------------------|--------------------------------------------------|--------------------------|------|--------|-----|---------------------|------|--------------------------------|------|-----|

|     |                         |                                                  | Min                      | Max  | Min    | Max | Min                 | Max  | Min                            | Max  | Ť   |

| 27  | 1–2,<br>7               | 2X_PCLK rising edge to ABB, DBB precharge enable | 3                        | 8.5  | 3      | 7.5 | 3                   | 8.5  | 1.9                            | 8.5  | ns  |

| 28  | 6                       | 2X_PCLK rising edge to ABB, DBB disable          | _                        | 21.0 | _      | 16  | _                   | 21.0 | _                              | 21.0 | ns  |

#### **Output AC timing notes:**

- 1. All output specs are measured from the 1.4 V level of the 2X\_PCLK input to the TTL level of the signal in question. Note that functional timing is derived from the rising edge of 2X\_PCLK gated by PCLK\_EN and BCLK\_EN, as described above.

- 2.The shared outputs TS, ABB, DBB, SHD, ARTRY, and XATS signals require pull-up resistors to hold them negated when there is no bus master driving.

- 3. Because SHD and ARTRY may be asserted by more than one device at the same time, they are negated in a unique fashion. They are tri-stated in the second bus clock cycle after AACK assertion. In the next cycle, they are precharged for one 2X\_PCLK period regardless of BCLK\_EN. This protocol prevents driver contention on these signals. This precharge may be disabled by setting HID0 (bit 29).

- 4. Double drive is only available for the following signals: ABB, DBB, SHD, ARTRY, TS, and XATS. Double drive is enabled by strapping the SC\_DRIVE pin to Vdd. (Double drive mode increases the capacitive drive capability of the signal by enabling a second driver.)

- 5. If the chip is operated at a frequency less than that which is specified, the width of precharge will be approximately one 2X\_PCLK period plus 1 ns.

- 6. ABB and DBB disable assumes continuous clock operation. If clock operations are stopped, the disable may extend until clock operations are restarted.

- 7. Minimum output enable and output hold times are guaranteed by design.

- 8. This specification is for an 80-MHz processor with the interface running at half the processor frequency (40 MHz).

- 9. This specification is for a 100-MHz 601v processor with the interface running at half the processor frequency (50 MHz).

**Note**: The diagram should only be referenced in regard to the edge-to-edge measurement of the timing specifications. It is not intended as a functional description of the input and output signals. Refer to the *PowerPC 601 RISC Microprocessor User's Manual* for functional descriptions and their related diagrams for device operation.

Figure 3. PowerPC 601 Microprocessor Output Timing Diagram

# 1.4 PowerPC 601 Microprocessor Thermal **Management Information**

This section provides thermal management information for the 601 and 601v.

The 601 will meet its electrical specifications when operated at a maximum T<sub>i</sub> (junction temperature) of 85 °C. To ensure that the processor does not exceed its maximum operating temperature, the proper heat sink and heat sink interface material must be selected. Table 8 provides  $\theta_{IH}$  (thermal resistance from junction to heat sink) for three typical heat sink to chip interfaces. Note that  $\theta_{iH}$  is dependent on the chip size.

Table 8.  $\theta_{JH}$  for Three Typical Heat Sink to Chip Interfaces

| Chip Size              | θ <sub>jH</sub> #1 | θ <sub>jH</sub> #2 | θ <sub>jH</sub> #3 | $\theta_{constriction}$ |

|------------------------|--------------------|--------------------|--------------------|-------------------------|

| 10.95 x 10.95 mm—(601) | 0.95 °C/Watt       | 2.9 °C/Watt        | 0.66 °C/Watt       | 0.2 °C/Watt             |

| 8.6 x 8.6 mm—(601v)    | 1.54 °C/Watt       | 4.7 °C/Watt        | 1.07 °C/Watt       | 0.3 °C/Watt             |

#### 1.4.1 Heat Sink Selection

Estimate the required heat sink performance using the following expression:

$$\theta_{HA} = \left[ \left( \left( T_j - T_a \right) / P \right) - \theta_{JH} - \theta_{const} \right] / cf$$

Where:

Thermal resistance from heat sink base to air

Junction temperature—maximum = 85 °C Device power dissipation (see Table 3)

$\theta_{

m JH}$ Thermal resistance from junction to heat sink

Constriction resistance into heat sink  $\theta_{\rm const} =$

Altitude correction factor (7000 ft. elevation)

$T_a$ Ambient temperature

For a conservative sizing, the maximum values of T<sub>i</sub>, T<sub>a</sub>, and power (P) should be used in the above expression. A more accurate sizing can be made by taking into account the statistical variation of these variables. However, that type of analysis is beyond the scope of this reference.

$<sup>\</sup>theta_{JH}$  #1 is 0.038 inches of AI Epoxy, k-1.06 W/mK with 80% coverage  $\theta_{JH}$  #2 is Chomerics tape, 0.139 mm thick, k = 0.4 W/mK, 100% coverage  $\theta_{JH}$  #3 is 0.003 inches of Thermoset grease, k =1.2 W/mK, 80% coverage

#### 1.4.2 Thermal Management Example

The following example provides the information necessary to make a heat sink selection. For a typical desktop application which uses an 80-MHz 601 (8 W typical, 9.2 W worst case power) and has a maximum ambient air temperature of 40  $^{\rm o}$ C, the allowable thermal resistance of the heat sink ( $\theta_{\rm HA}$ ) can be determined.

```

Thermal resistance (junction to case) = \theta_{JH} = 0.95 °C/Watt (junction to case) (assuming AI epoxy interface)

Maximum T_j (junction temperature) = 85 °C

Maximum ambient air temperature T_a = 40 °C

cf = 1.15 (correction factor for 7000-ft. elevation)

\theta_{HA} = [( (T_j - T_a) / chip power) – \theta_{JH} – \theta_{constriction}] x 1/cf

\theta_{HA} = [((85 °C – 40 °C)/ 9.2 W) – 0.95 °C/Watt – 0.2 °C/Watt)] x 1/1.15

\theta_{HA} = 3.25 °C/Watt (It is the maximum thermal resistance of the heat sink required to maintain 85 °C maximum junction temperature.)

```

# 1.4.3 Estimation of T<sub>i</sub>

Factors such as air-ducting and preheating can significantly affect the thermal performance of the processor. As such, the processor operating temperature should be verified for each application.

Since the processor junction temperature is not readily measurable, it is necessary to estimate this value. If the base temperature of the heat sink is known, the relationship to junction temperature can be easily derived as follows:

$$\begin{split} T_j &= T_H + Power \ x \ \theta_{JH} \\ \textbf{where:} \ T_H &= heat \ sink \ base \ temperature \end{split}$$

The heat sink base temperature can be obtained by a simple thermocouple measurement.

If the actual module power dissipation is available, this value should be substituted for chip power. Otherwise, an estimate of the nominal and maximum junction temperature can be made by substituting the nominal and maximum device power dissipation values from Table 3.

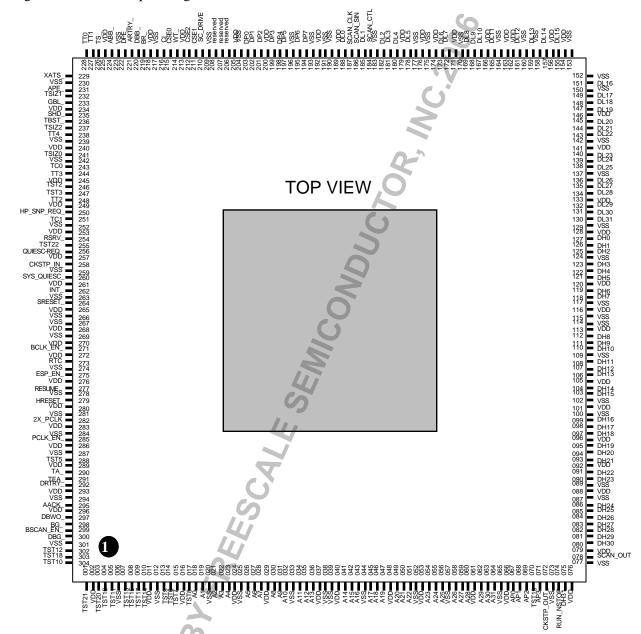

# 1.5 PowerPC 601 Microprocessor Pinout Diagram

Figure 4 contains the pin assignments for the 601 and 601v.

Figure 4. PowerPC 601 Microprocessor Pin Assignments

# 1.6 PowerPC 601 Microprocessor Pinout Listing

Table 9 provides the pinout listing for the 601 and 601v.

Table 9. PowerPC 601 Microprocessor Pinout Listing

| Signal Name | Pin Number                                                                                                                                                    | Active | I/O    |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|

| 2X_PCLK     | 282                                                                                                                                                           | High   | Input  |

| A0-A31      | 18, 19, 21, 22, 23, 26, 27, 28, 30, 31, 32, 34, 35, 36, 41, 42, 43, 45, 46, 47, 49, 50, 51, 54, 55, 56, 58, 59, 60, 62, 63, 64                                | High   | I/O    |

| AACK        | 295                                                                                                                                                           | Low    | Input  |

| ABB         | 224                                                                                                                                                           | Low    | Output |

| AP0-AP3     | 67, 68, 69, 71                                                                                                                                                | High   | I/O    |

| ĀPĒ         | 231                                                                                                                                                           | Low    | Output |

| ARTRY       | 221                                                                                                                                                           | Low    | I/O    |

| BCLK_EN     | 271                                                                                                                                                           | Low    | Input  |

| BG          | 298                                                                                                                                                           | Low    | Input  |

| BR          | 219                                                                                                                                                           | Low    | Output |

| BSCAN_EN    | 299                                                                                                                                                           | High   | Input  |

| CI          | 216                                                                                                                                                           | Low    | Output |

| CKSTP_IN    | 258                                                                                                                                                           | Low    | Input  |

| CKSTP_OUT   | 72                                                                                                                                                            | Low    | Output |

| CSE0-CSE2   | 215, 211, 212                                                                                                                                                 | High   | Output |

| DBB         | 220                                                                                                                                                           | Low    | I/O    |

| DBG         | 300                                                                                                                                                           | Low    | Input  |

| DBWO        | 297                                                                                                                                                           | Low    | Input  |

| DH0-DH31    | 127, 126, 125, 123, 122, 121, 119, 118, 112, 111, 110, 108, 107, 106, 104, 103, 99, 98, 97, 95, 94, 93, 91, 90, 86, 85, 84, 83, 82, 81, 80, 75                | High   | I/O    |

| DL0-DL31    | 188,185, 182, 181, 180, 178, 173, 172, 169, 168, 167, 165, 161, 159, 157, 155, 151, 149, 148, 147, 145, 144, 143, 140, 139, 138, 136, 135, 134, 132, 131, 130 | High   | I/O    |

| DP0-DP7     | 203, 202, 201, 199, 198, 197, 195, 194                                                                                                                        | High   | I/O    |

| DPE         | 222                                                                                                                                                           | Low    | Output |

| DRTRY       | 292                                                                                                                                                           | Low    | Input  |

| ESP_EN      | 275                                                                                                                                                           | Low    | Input  |

| GBL         | 233                                                                                                                                                           | Low    | I/O    |

|             |                                                                                                                                                               |        | _      |

Table 9. PowerPC 601 Microprocessor Pinout Listing (Continued)

| Signal Name                                 | Pin Number                               | Active                            | I/O    |

|---------------------------------------------|------------------------------------------|-----------------------------------|--------|

| HP_SNP_REQ                                  | 250                                      | Low                               | Input  |

| HRESET                                      | 279                                      | Low                               | Input  |

| ĪNT                                         | 262                                      | Low                               | Input  |

| PCLK_EN                                     | 285                                      | Low                               | Input  |

| QUIESC_REQ                                  | 256                                      | High                              | Output |

| Reserved                                    | 206, 207                                 | Tie high<br>(Vdd <sub>I/O</sub> ) | _      |

| Reserved                                    | 208                                      | Tie low                           | _      |

| RESUME                                      | 277                                      | High                              | Input  |

| RSRV                                        | 254                                      | Low                               | Output |

| RTC                                         | 273                                      | High                              | Input  |

| RUN_NSTOP                                   | 74                                       | High                              | Output |

| SCAN_CLK                                    | 187                                      | High                              | Input  |

| SCAN_CTL                                    | 184                                      | High                              | Input  |

| SCAN_OUT                                    | 78                                       | High                              | Output |

| SCAN_SIN                                    | 186                                      | High                              | Input  |

| SC_DRIVE                                    | 210                                      | High                              | Input  |

| SHD                                         | 235                                      | Low                               | I/O    |

| SRESET                                      | 264                                      | Low                               | Input  |

| SYS_QUIESC                                  | 260                                      | Low                               | Input  |

| TA                                          | 290                                      | Low                               | Input  |

| TBST                                        | 236                                      | Low                               | I/O    |

| TC0-TC1                                     | 243, 251                                 | High                              | Output |

| TEA                                         | 291                                      | Low                               | Input  |

| TSIZ0-TSIZ2                                 | 241, 232, 237                            | High                              | I/O    |

| TST7, TST8,<br>TST10–TST17,<br>TST22        | 15, 17, 304, 5, 302, 7, 10, 8, 4, 9, 255 | Tie high<br>(Vdd <sub>I/O</sub> ) | Input  |

| TST18, TST20,<br>TST21, TST5,<br>TST6, TST9 | 303, 3, 1, 288, 14, 13                   | Tie low                           | Input  |

| TST19, TST2, TST3                           | 70, 246, 247                             | Do not connect                    | Output |

| TS                                          | 226                                      | Low                               | I/O    |

| TT0-TT4                                     | 228, 227, 248, 244, 238,                 | High                              | I/O    |

Table 9. PowerPC 601 Microprocessor Pinout Listing (Continued)

| Signal Name        | Pin Number                                                                                                                                                                                                                                                                            | Active | I/O    |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|

| Vdd <sub>INT</sub> | 2, 11, 16, 37, 53, 61, 76, 88, 92, 113, 128, 133, 162, 163, 171, 179, 189, 200, 205, 225, 240, 253, 257, 265, 268, 270, 280, 283, 293                                                                                                                                                 | High   | Input  |

| Vdd <sub>l/O</sub> | 24, 29, 40, 48, 66, 79, 96, 101, 105, 116, 120, 141, 146, 154, 156, 166, 174, 176, 192, 213, 218, 234, 245, 249, 261, 272, 276, 286, 289, 296                                                                                                                                         | High   | Input  |

| Vss                | 6, 12, 20, 25, 33, 38, 39, 44, 52, 57, 65, 73, 77, 87, 89, 100, 102, 109, 114, 115, 117, 124, 129, 137, 142, 150, 152, 153, 158, 160, 164, 170, 175, 177, 183, 190, 191, 193, 196, 204, 209, 217, 223, 230, 239, 242, 252, 259, 263, 266, 267, 269, 274, 278, 281, 284, 287, 294, 301 | Low    | Input  |

| WT                 | 214                                                                                                                                                                                                                                                                                   | Low    | Output |

| XATS               | 229                                                                                                                                                                                                                                                                                   | Low    | I/O    |

**Note**: For the 50, 66, and 80 MHz versions of the 601, Vdd<sub>INT</sub> and Vdd<sub>I/O</sub> are not implemented as separate supplies on the chip, and should be powered with the same potential.

# 1.7 PowerPC 601 Microprocessor Package Description

The following sections provide the package parameters and the mechanical dimensions for the 601 and 601v.

## 1.7.1 Package Parameters

The package parameters are as provided in the following list. The package type is 40-mm, 304-pin ceramic quad flat pack.

Package outline 40 mm

Interconnects 304

Pitch 0.5 mm

Lead plating Ni Au

Solder joint Sn/PB (10/90)

Lead encapsulation HYSOL 4323

C4 encapsulation EPX 5341

Maximum module height 3.1 mm

Co-planarity specification 0.08 mm

**Note**: No solvent can be used with the C4FP.

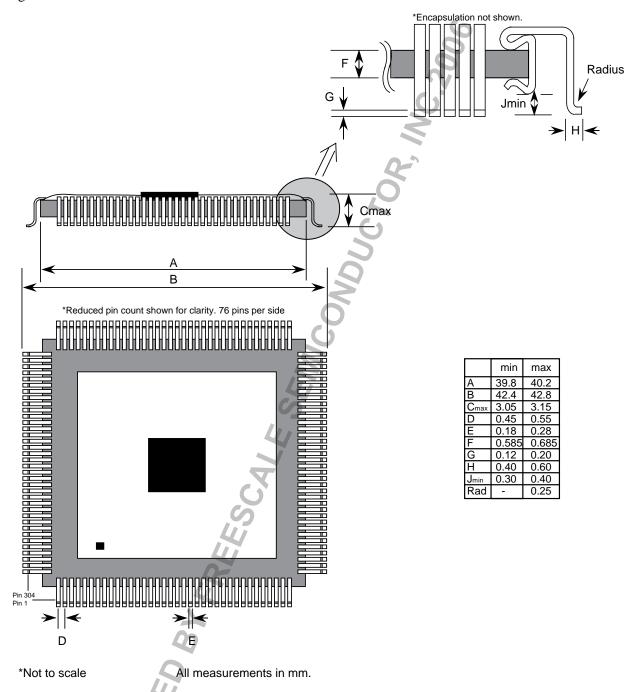

## 1.7.2 PowerPC 601 Microprocessor Mechanical Dimensions

Figure 5 shows the mechanical dimensions for the 601 and 601v.

Figure 5. Mechanical Dimensions of the PowerPC 601 Microprocessor Package

# Appendix A General Handling Recommendations

The following list provides a few guidelines for package handling:

- Handle the electrostatic discharge sensitive (ESD) package with care before, during, and after processing.

- Do not apply any load to exceed 3 Kg after assembly.

- Components should not be hot dip tinned

- The package encapsulation is an acrylated urethane. Use adequate ventilation (local exhaust) for all elevated temperature processes.

The package parameters are as follows:

| Heat sink adhesive    | AIEG-7655 |

|-----------------------|-----------|

| IBM reference drawing | 99F4869   |

Test socket Yamaichi IC51-3044-1543-REV C

Signal 187 Power/ground 117 Total 304

# A.1 Package Environmental, Operation, Shipment, and Storage Requirements

The environmental, operation, shipment, and storage requirements are as follows:

- Make sure that the package is suitable for continuous operation under business office environments.

- Operating environment: 10 °C to 40 °C, 8% to 80% relative humidity

- Storage environment: 1 °C to 60 °C, 5% to 80% relative humidity

- Shipping environment: 40 °C to 60 °C, 5% to 100% relative humidity

- This component is qualified to meet JEDEC moisture Class 2

- After expiration of shelf life, packages may be baked at 120 °C (+10/–5 °C) for 4 hours minimum and packaged.

# A.2 Card Assembly Recommendations

This section provides recommendations for card assembly process. Follow these guidelines for card assembly.

- This component is supported for aqueous, IR, convection reflow, and vapor phase card assembly processes.

- The temperature of packages should not exceed 220 °C for longer than 5 minutes.

- The package entering a cleaning cycle must not be exposed to temperature greater than that occurring during solder reflow or hot air exposure.

- It is not recommended to re-attach a package that is removed after card assembly.

### A.2.1 Card Assembly Process

During the card assembly process, no solvent can be used with the C4FP, and no more than 3 Kg of force must be applied normal to the top of the package prior to, during, or after card assembly. Other details of the card assembly process follow:

**Solder paste** Either water soluble (for example, Alpha 1208) or no clean

**Solder stencil thickness** 0.152 mm

**Solder stencil aperature** Width reduced to 0.03 mm from the board pad width

Placement tool Panasonic MPA3 or equivalent

Solder reflow Infrared, convection, or vapor phase

**Solder reflow profile** Infrared and/or convection

•Average ramp-up—0.48 to 1.8 °C/second

•Time above 183 °C—45 to 145 seconds

•Minimum lead temperature—200 °C

•Maximum lead temperature—240 °C

•Maximum C4FP temperature—245 °C

#### Vapor phase

- •Preheat (board)—60 °C to 150 °C

- •Time above 183 °C—60 to 145 seconds

- •Minimum lead temperature—200 °C

- Maximum C4FP temperature—220 °C

- Egress temperature—below 150 °C

#### Clean after reflow

De-ionized (D.I.) water if water-soluble paste is used

- •Cleaner requirements—conveyorized, in-line

- •Minimum of four washing chambers

- —Pre-clean chamber: top and bottom sprays, minimum top-side pressure of 25 psig, water temperature of 70 °C minimum, dwell time of 24 seconds minimum, water is not re-used, water flow rate of 30 liters/minute.

- —Wash chamber #1: top and bottom sprays, minimum top-side pressure of 48 psig, minimum bottom-side pressure of 44 psig, water temperature of 62.5 °C (±2.5 °C), dwell time of 48 seconds minimum, water flow rate of 350 liters/minute.

- —Wash chamber #2: top and bottom sprays, minimum top-side pressure of 32 psig, minimum bottom-side pressure of 28 psig, water temperature of 72.5 °C (±2.5 °C), dwell time of 48 seconds minimum, water flow rate of 325 liters/minute.

- —Final rinse chamber: top and bottom sprays, minimum top-side pressure of 25 psig, water temperature of 72.5 °C minimum, dwell time of 24 seconds minimum, water flow rate of 30 liters/minute.

- •No cleaning required if "no clean solder paste" is used

Touch-up and repair C4FP removal C4FP replace Water soluble (for example, Kester 450) or No Clean Flux Hot air rework Hand solder

Information in this document is provided solely to enable system and software implementers to use PowerPC microprocessors. There are no express or implied copyright or patent licenses granted hereunder by Motorola or IBM to design, modify the design of, or fabricate circuits based on the information in this document.

The PowerPC 601 microprocessor embodies the intellectual property of Motorola and of IBM. However, neither Motorola nor IBM assumes any responsibility or liability as to any aspects of the performance, operation, or other attributes of the microprocessor as marketed by the other party or by any third party. Neither Motorola nor IBM is to be considered an agent or representative of the other, and neither has assumed, created, or granted hereby any right or authority to the other, or to any third party, to assume or create any express or implied obligations on its behalf. Information such as errata sheets and data sheets, as well as sales terms and conditions such as prices, schedules, and support, for the product may vary as between parties selling the product. Accordingly, customers wishing to learn more information about the products as marketed by a given party should contact that party.

Both Motorola and IBM reserve the right to modify this manual and/or any of the products as described herein without further notice. NOTHING IN THIS MANUAL, NOR IN ANY OF THE ERRATA SHEETS, DATA SHEETS, AND OTHER SUPPORTING DOCUMENTATION, SHALL BE INTERPRETED AS THE CONVEYANCE BY MOTOROLA OR IBM OF AN EXPRESS WARRANTY OF ANY KIND OR IMPLIED WARRANTY, REPRESENTATION, OR GUARANTEE REGARDING THE MERCHANTABILITY OR FITNESS OF THE PRODUCTS FOR ANY PARTICULAR PURPOSE. Neither Motorola nor IBM assumes any liability or obligation for damages of any kind arising out of the application or use of these materials. Any warranty or other obligations as to the products described herein shall be undertaken solely by the marketing party to the customer, under a separate sale agreement between the marketing party and the customer. In the absence of such an agreement, no liability is assumed by Motorola, IBM, or the marketing party for any damages, actual or otherwise.

"Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals," must be validated for each customer application by customer's technical experts. Neither Motorola nor IBM convey any license under their respective intellectual property rights nor the rights of others. Neither Motorola nor IBM makes any claim, warranty, or representation, express or implied, that the products described in this manual are designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the product could create a situation where personal injury or death may occur. Should customer purchase or use the products for any such unintended or unauthorized application, customer shall indemnify and hold Motorola and IBM and their respective officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola or IBM was negligent regarding the design or manufacture of the part.

Motorola and (A) are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

IBM is a registered trademark of International Business Machines Corp. IBM Mirror Indias., **PowerPC**, PowerPC, PowerPC 601, and PowerPC Architecture are trademarks of International Business Machines Corp. used by Motorola under license from International Business Machines Corp. International Business Machines Corp. is an Equal Opportunity/Affirmative Action Employer.

#### **Motorola Literature Distribution Centers:**

USA: Motorola Literature Distribution, P.O. Box 20912, Phoenix, Arizona 85036.

EUROPE: Motorola Ltd., European Literature Centre, 88 Tanners Drive, Blakelands, Milton Keynes, MK14 5BP, England. JAPAN: Nippon Motorola Ltd., 4-32-1, Nishi-Gotanda, Shinagawa-ku, Tokyo 141 Japan.

ASIA-PACIFIC: Motorola Semiconductors H.K. Ltd., Silicon Harbour Centre, No. 2 Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong.

**Technical Information**: Motorola Inc. Semiconductor Products Sector Technical Responsiveness Center; (800) 521-6274. **Document Comments**: FAX (512) 891-2638, Attn: RISC Applications Engineering.

#### IBM Microelectronics:

USA: IBM Microelectronics, Mail Stop A25/862-1, PowerPC Marketing, 1000 River Street, Essex Junction, VT 05452-4299; Tel.: (800) PowerPC [(800) 769-3772]; FAX (800) POWERfax [(800) 769-3732].

EUROPE: IBM Microelectronics, PowerPC Marketing, Dept. 1045, 224 Boulevard J.F. Kennedy, 91105 Corbeil-Essonnes CEDEX, France; Tel. (33) 1-60-88 5167; FAX (33) 1-60-88 4920.

JAPAN: IBM Microelectronics, PowerPC Marketing, Dept., R0260, 800 Ichimiyake, Yasu-cho, Yasu-gun, Shinga-ken, Japan 520-23; Tel. (81) 775-87-4745; FAX (81) 775-87-4735.

IBM Microelectronics