MPC603/D (Motorola Order Number)

> 6/94 REV 3

# Advance Information PowerPC™ 603 RISC Microprocessor Technical Summary

This document provides an overview of the PowerPC 603<sup>TM</sup> microprocessor features, including a block diagram showing the major functional components. It also provides an overview of the PowerPC Architecture<sup>TM</sup>, and information about how the 603 implementation complies with the architectural definitions.

This document is divided into three parts:

- Part 1, "PowerPC 603 Microprocessor Overview," provides an overview of the 603 features, including a block diagram showing the major functional components.

- Part 2, "Levels of the PowerPC Architecture," describes the three levels of the PowerPC architecture.

- Part 3, "PowerPC 603 Microprocessor: Implementation," describes the PowerPC architecture in general, and specific details about the implementation of the 603 as a low-power, 32-bit member of the PowerPC processor family.

In this document, the terms "PowerPC 603 microprocessor" and "603" are used to denote the second microprocessor from the PowerPC architecture family. The PowerPC 603 microprocessors are available from IBM as PPC603 and from Motorola as MPC603.

PowerPC, PowerPC Architecture, POWER Architecture, PowerPC 603, and PowerPC 601 are trademarks of International Business Machines Corp. used by Motorola under license from IBM Corp.

This document contains information on a new product under development. Specifications and information herein are subject to change without notice.

© Motorola Inc. 1994

Portions hereof © International Business Machines Corp. 1991–1994

# Part 1 PowerPC 603 Microprocessor Overview

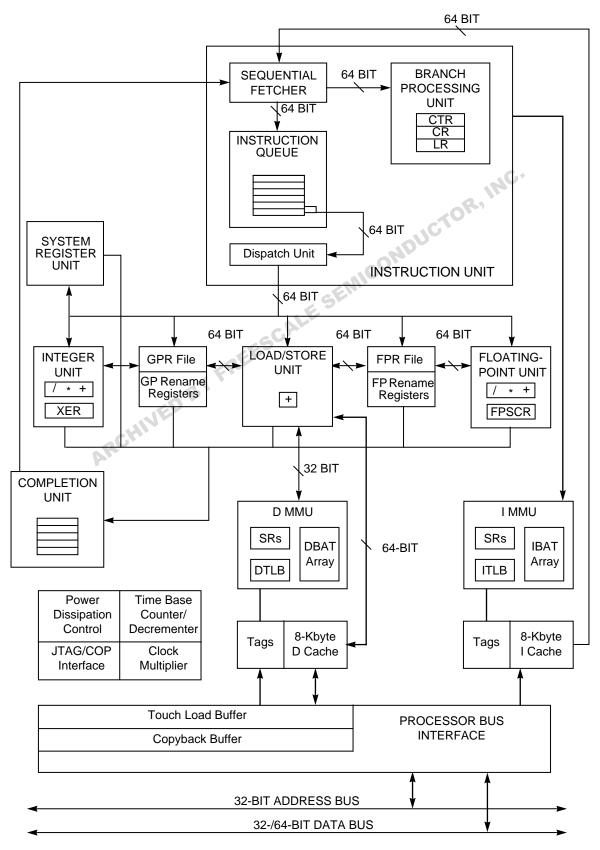

This section describes the features of the 603, provides a block diagram showing the major functional units, and gives an overview of how the 603 operates.

The 603 is the first low-power implementation of the PowerPC microprocessor family of reduced instruction set computer (RISC) microprocessors. The 603 implements the 32-bit portion of the PowerPC architecture, which provides 32-bit effective addresses, integer data types of 8, 16, and 32 bits, and floating-point data types of 32 and 64 bits. For 64-bit PowerPC microprocessors, the PowerPC architecture provides 64-bit integer data types, 64-bit addressing, and other features required to complete the 64-bit architecture.

The 603 provides four software controllable power-saving modes. Three of the modes (the nap, doze, and sleep modes) are static in nature, and progressively reduce the amount of power dissipated by the processor. The fourth is a dynamic power management mode that causes the functional units in the 603 to automatically enter a low-power mode when the functional units are idle without affecting operational performance, software execution, or any external hardware.

The 603 is a superscalar processor capable of issuing and retiring as many as three instructions per clock. Instructions can execute out of order for increased performance; however, the 603 makes completion appear sequential.

The 603 integrates five execution units—an integer unit (IU), a floating-point unit (FPU), a branch processing unit (BPU), a load/store unit (LSU), and a system register unit (SRU). The ability to execute five instructions in parallel and the use of simple instructions with rapid execution times yield high efficiency and throughput for 603-based systems. Most integer instructions execute in one clock cycle. The FPU is pipelined so a single-precision multiply-add instruction can be issued every clock cycle.

The 603 provides independent on-chip, 8-Kbyte, two-way set-associative, physically addressed caches for instructions and data and on-chip instruction and data memory management units (MMUs). The MMUs contain 64-entry, two-way set-associative, data and instruction translation lookaside buffers (DTLB and ITLB) that provide support for demand-paged virtual memory address translation and variable-sized block translation. The TLBs and caches use a least recently used (LRU) replacement algorithm. The 603 also supports block address translation through the use of two independent instruction and data block address translation (IBAT and DBAT) arrays of four entries each. Effective addresses are compared simultaneously with all four entries in the BAT array during block translation. In accordance with the PowerPC architecture, if an effective address hits in both the TLB and BAT array, the BAT translation takes priority.

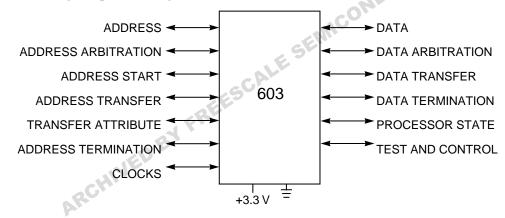

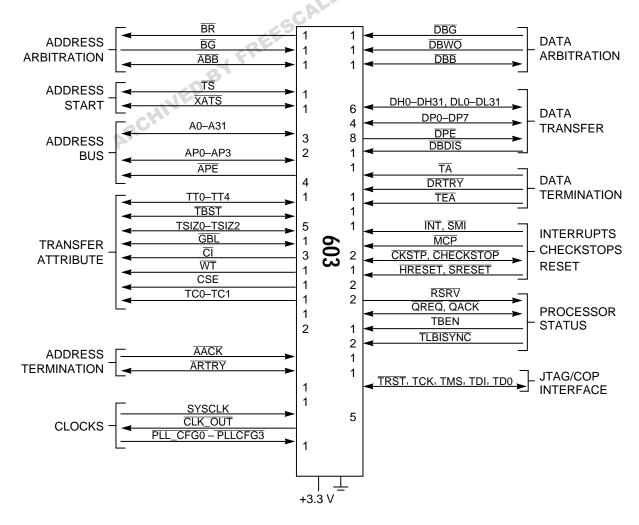

The 603 has a selectable 32- or 64-bit data bus and a 32-bit address bus. The 603 interface protocol allows multiple masters to compete for system resources through a central external arbiter. The 603 provides a three-state coherency protocol that supports the exclusive, modified, and invalid cache states. This protocol is a compatible subset of the MESI (modified/exclusive/shared/invalid) four-state protocol and operates coherently in systems that contain four-state caches. The 603 supports single-beat and burst data transfers for memory accesses; it also supports both memory-mapped I/O and direct-store interface addressing.

The 603 uses an advanced, 3.3-V CMOS process technology and maintains full interface compatibility with TTL devices.

# 1.1 PowerPC 603 Microprocessor Features

This section describes details of the 603's implementation of the PowerPC architecture. Major features of the 603 are as follows:

- High-performance, superscalar microprocessor

- As many as three instructions issued and retired per clock

- As many as five instructions in execution per clock

- Single-cycle execution for most instructions

- Pipelined FPU for all single-precision and most double-precision operations

- Five independent execution units and two register files

- BPU featuring static branch prediction

- A 32-bit IU

- Fully IEEE 754-compliant FPU for both single- and double-precision operations

- LSU for data transfer between data cache and GPRs and FPRs

- SRU that executes condition register (CR) and special-purpose register (SPR) instructions JCTOR, INC.

- Thirty-two GPRs for integer operands

- Thirty-two FPRs for single- or double-precision operands

- High instruction and data throughput

- Zero-cycle branch capability (branch folding)

- Programmable static branch prediction on unresolved conditional branches

- Instruction fetch unit capable of fetching two instructions per clock from the instruction cache

- A six-entry instruction queue that provides look-ahead capability

- Independent pipelines with feed-forwarding that reduces data dependencies in hardware

- 8-Kbyte data cache—two-way set-associative, physically addressed; LRU replacement algorithm

- 8-Kbyte instruction cache—two-way set-associative, physically addressed; LRU replacement algorithm

- Cache write-back or write-through operation programmable on a per page or per block basis

- BPU that performs CR look-ahead operations

- Address translation facilities for 4-Kbyte page size, variable block size, and 256-Mbyte segment size

- A 64-entry, two-way set-associative ITLB

- A 64-entry, two-way set-associative DTLB

- Four-entry data and instruction BAT arrays providing 128-Kbyte to 256-Mbyte blocks

- Software table search operations and updates supported through fast trap mechanism

- 52-bit virtual address; 32-bit physical address

- Facilities for enhanced system performance

- A 32- or 64-bit split-transaction external data bus with burst transfers

- Support for one-level address pipelining and out-of-order bus transactions

- Bus extensions for direct-store interface operations

- Integrated power management

- Low-power 3.3-volt design

- Internal processor/bus clock multiplier that provides 1/1, 2/1, 3/1, and 4/1 ratios

- Three power saving modes: doze, nap, and sleep

- Automatic dynamic power reduction when internal functional units are idle

- In-system testability and debugging features through JTAG boundary-scan capability

# 1.2 Block Diagram

Figure 1 provides a block diagram of the 603 that illustrates how the execution units—IU, FPU, BPU, LSU, and SRU—operate independently and in parallel.

The 603 provides address translation and protection facilities, including an ITLB, DTLB, and instruction and data BAT arrays. Instruction fetching and issuing is handled in the instruction unit. Translation of addresses for cache or external memory accesses are handled by the MMUs. Both units are discussed in more detail in Sections 1.3, "Instruction Unit," and 1.5.1, "Memory Management Units (MMUs)."

# 1.3 Instruction Unit

As shown in Figure 1, the 603 instruction unit, which contains a fetch unit, instruction queue, dispatch unit, and BPU, provides centralized control of instruction flow to the execution units. The instruction unit determines the address of the next instruction to be fetched based on information from the sequential fetcher and from the BPU.

The instruction unit fetches the instructions from the instruction cache into the instruction queue. The BPU extracts branch instructions from the fetcher and uses static branch prediction on unresolved conditional branches to allow the instruction unit to fetch instructions from a predicted target instruction stream while a conditional branch is evaluated. The BPU folds out branch instructions for unconditional branches or conditional branches unaffected by instructions in progress in the execution pipeline.

Instructions issued beyond a predicted branch do not complete execution until the branch is resolved, preserving the programming model of sequential execution. If any of these instructions are to be executed in the BPU, they are decoded but not issued. Instructions to be executed by the FPU, IU, LSU, and SRU are issued and allowed to complete up to the register write-back stage. Write-back is allowed when a correctly predicted branch is resolved, and instruction execution continues without interruption along the predicted path.

If branch prediction is incorrect, the instruction unit flushes all predicted path instructions, and instructions are issued from the correct path.

Figure 1. PowerPC 603 Microprocessor Block Diagram

## 1.3.1 Instruction Queue and Dispatch Unit

The instruction queue (IQ), shown in Figure 1, holds as many as six instructions and loads up to two instructions from the instruction unit during a single cycle. The instruction fetch unit continuously loads as many instructions as space in the IQ allows. Instructions are dispatched to their respective execution units from the dispatch unit at a maximum rate of two instructions per cycle. Dispatching is facilitated to the IU, FPU, LSU, and SRU by the provision of a reservation station at each unit. The dispatch unit performs source and destination register dependency checking, determines dispatch serializations, and inhibits subsequent instruction dispatching as required.

For a more detailed overview of instruction dispatch, see Section 3.7, "Instruction Timing."

# 1.3.2 Branch Processing Unit (BPU)

The BPU receives branch instructions from the fetch unit and performs CR look-ahead operations on conditional branches to resolve them early, achieving the effect of a zero-cycle branch in many cases.

The BPU uses a bit in the instruction encoding to predict the direction of the conditional branch. Therefore, when an unresolved conditional branch instruction is encountered, the 603 fetches instructions from the predicted target stream until the conditional branch is resolved.

The BPU contains an adder to compute branch target addresses and three user-control registers—the link register (LR), the count register (CTR), and the CR. The BPU calculates the return pointer for subroutine calls and saves it into the LR for certain types of branch instructions. The LR also contains the branch target address for the Branch Conditional to Link Register (**bclr***x*) instruction. The CTR contains the branch target address for the Branch Conditional to Count Register (**bcctr***x*) instruction. The contents of the LR and CTR can be copied to or from any GPR. Because the BPU uses dedicated registers rather than GPRs or FPRs, execution of branch instructions is largely independent from execution of integer and floating-point instructions.

# 1.4 Independent Execution Units

The PowerPC architecture's support for independent execution units allows implementation of processors with out-of-order instruction execution. For example, because branch instructions do not depend on GPRs or FPRs, branches can often be resolved early, eliminating stalls caused by taken branches.

In addition to the BPU, the 603 provides four other execution units and a completion unit, which are described in the following sections.

# 1.4.1 Integer Unit (IU)

The IU executes all integer instructions. The IU executes one integer instruction at a time, performing computations with its arithmetic logic unit (ALU), multiplier, divider, and integer exception register (XER). Most integer instructions are single-cycle instructions. Thirty-two general-purpose registers are provided to support integer operations. Stalls due to contention for GPRs are minimized by the automatic allocation of rename registers. The 603 writes the contents of the rename registers to the appropriate GPR when integer instructions are retired by the completion unit.

# 1.4.2 Floating-Point Unit (FPU)

The FPU contains a single-precision multiply-add array and the floating-point status and control register (FPSCR). The multiply-add array allows the 603 to efficiently implement multiply and multiply-add operations. The FPU is pipelined so that single-precision instructions and double-precision instructions can be issued back-to-back. Thirty-two floating-point registers are provided to support floating-point operations. Stalls due to contention for FPRs are minimized by the automatic allocation of rename registers. The 603

writes the contents of the rename registers to the appropriate FPR when floating-point instructions are retired by the completion unit.

The 603 supports all IEEE 754 floating-point data types (normalized, denormalized, NaN, zero, and infinity) in hardware, eliminating the latency incurred by software exception routines. (The term, 'exception' is also referred to as 'interrupt' in the architecture specification.)

# 1.4.3 Load/Store Unit (LSU)

The LSU executes all load and store instructions and provides the data transfer interface between the GPRs, FPRs, and the cache/memory subsystem. The LSU calculates effective addresses, performs data alignment, and provides sequencing for load/store string and multiple instructions.

Load and store instructions are issued and translated in program order; however, the actual memory accesses can occur out of order. Synchronizing instructions are provided to enforce strict ordering.

Cacheable loads, when free of data dependencies, execute in a speculative manner with a maximum throughput of one per cycle and a two-cycle total latency. Data returned from the cache is held in a rename register until the completion logic commits the value to a GPR or FPR. Stores cannot be executed speculatively and are held in the store queue until the completion logic signals that the store operation is to be completed to memory. The time required to perform the actual load or store operation varies depending on whether the operation involves the cache, system memory, or an I/O device.

# 1.4.4 System Register Unit (SRU)

The SRU executes various system-level instructions, including condition register logical operations and move to/from special-purpose register instructions. In order to maintain system state, most instructions executed by the SRU are completion-serialized; that is, the instruction is held for execution in the SRU until all prior instructions issued have completed. Results from completion-serialized instructions executed by the SRU are not available or forwarded for subsequent instructions until the instruction completes.

# 1.4.5 Completion Unit

The completion unit tracks instructions from dispatch through execution, and then retires, or "completes" them in program order. Completing an instruction commits the 603 to any architectural register changes caused by that instruction. In-order completion ensures the correct architectural state when the 603 must recover from a mispredicted branch or any exception.

Instruction state and other information required for completion is kept in a first-in-first-out (FIFO) queue of five completion buffers. A single completion buffer is allocated for each instruction once it enters the dispatch unit. An available completion buffer is a required resource for instruction dispatch; if no completion buffers are available, instruction dispatch stalls. A maximum of two instructions per cycle are completed in order from the queue.

# 1.5 Memory Subsystem Support

The 603 provides support for cache and memory management through dual instruction and data memory management units. The 603 also provides dual 8-Kbyte instruction and data caches, and an efficient processor bus interface to facilitate access to main memory and other bus subsystems. The memory subsystem support functions are described in the following subsections.

# 1.5.1 Memory Management Units (MMUs)

The 603's MMUs support up to 4 Petabytes (2<sup>52</sup>) of virtual memory and 4 Gigabytes (2<sup>32</sup>) of physical memory (referred to as real memory in the architecture specification) for instruction and data. The MMUs also control access privileges for these spaces on block and page granularities. Referenced and changed

status is maintained by the processor for each page to assist implementation of a demand-paged virtual memory system.

The LSU calculates effective addresses for data loads and stores, performs data alignment to and from cache memory, and provides the sequencing for load and store string and multiple word instructions. The instruction unit calculates the effective addresses for instruction fetching.

After an address is generated, the higher-order bits of the effective address are translated by the appropriate MMU into physical address bits. Simultaneously, the lower-order address bits (that are untranslated and therefore, considered both logical and physical), are directed to the on-chip caches where they form the index into the two-way set-associative tag array. After translating the address, the MMU passes the higher-order bits of the physical address to the cache, and the cache lookup completes. For cache-inhibited accesses or accesses that miss in the cache, the untranslated lower-order address bits are concatenated with the translated higher-order address bits; the resulting 32-bit physical address is then used by the memory unit and the system interface, which accesses external memory.

The MMU also directs the address translation and enforces the protection hierarchy programmed by the operating system in relation to the supervisor/user privilege level of the access and in relation to whether the access is a load or store.

For instruction accesses, the MMU performs an address lookup in both the 64 entries of the ITLB, and in the IBAT array. If an effective address hits in both the ITLB and the IBAT array, the IBAT array translation takes priority. Data accesses cause a lookup in the DTLB and DBAT array for the physical address translation. In most cases, the physical address translation resides in one of the TLBs and the physical address bits are readily available to the on-chip cache.

When the physical address translation misses in the TLBs, the 603 provides hardware assistance for software to perform a search of the translation tables in memory. The hardware assist consists of the following features:

- Automatic storage of the missed effective address in the IMISS and DMISS registers

- Automatic generation of the primary and secondary hashed real address of the page table entry group (PTEG), which are readable from the HASH1 and HASH2 register locations

- The HASH data is generated from the contents of the IMISS or DMISS register. Which register is selected depends on which miss (instruction or data) was last acknowledged.

- Automatic generation of the first word of the page table entry (PTE) for which the tables are being searched

- A real page address (RPA) register that matches the format of the lower word of the PTE

- Two TLB access instructions (**tlbli** and **tlbld**) that are used to load an address translation into the instruction or data TLBs

- Shadow registers for GPRs 0–3 that allow miss code to execute without corrupting the state of any

of the existing GPRs

These shadow registers are only used for servicing a TLB miss.

See Section 3.6.2, "PowerPC 603 Microprocessor Memory Management," for more information about memory management for the 603.

#### 1.5.2 Cache Units

The 603 provides independent 8-Kbyte, two-way set-associative instruction and data caches. The cache line size is 32 bytes in length. The caches are designed to adhere to a write-back policy, but the 603 allows control of cacheability, write policy, and memory coherency at the page and block levels. The caches use a least recently used (LRU) replacement policy.

As shown in Figure 1, the caches provide a 64-bit interface to the instruction fetch unit and load/store unit. The surrounding logic selects, organizes, and forwards the requested information to the requesting unit. Write operations to the cache can be performed on a byte basis, and a complete read-modify-write operation to the cache can occur in each cycle.

The load/store and instruction fetch units provide the caches with the address of the data or instruction to be fetched. In the case of a cache hit, the cache returns two words to the requesting unit.

Since the 603 data cache tags are single ported, simultaneous load or store and snoop accesses cause resource contention. Snoop accesses have the highest priority and are given first access to the tags, unless the snoop access coincides with a tag write, in which case the snoop is retried and must re-arbitrate for access to the cache. Loads or stores that are deferred due to snoop accesses are executed on the clock cycle following the snoop.

# 1.6 Processor Bus Interface

Because the caches on the 603 are on-chip, write-back caches, the predominant type of transaction for most applications is burst-read memory operations, followed by burst-write memory operations, single-beat (noncacheable or write-through) memory read and write operations, and direct-store interface operations. Additionally, there can be address-only operations, variants of the burst and single-beat operations, (for example, global memory operations that are snooped and atomic memory operations), and address retry activity (for example, when a snooped read access hits a modified line in the cache).

Memory accesses can occur in single-beat (1–8 bytes) and four-beat burst (32 bytes) data transfers when the bus is configured as 64 bits, and in single-beat (1–4 bytes), two-beat (8 bytes), and eight-beat (32 bytes) data transfers when the bus is configured as 32 bits. The address and data buses operate independently to support pipelining and split transactions during memory accesses. The 603 can pipeline its own transactions to a depth of one level.

Access to the system interface is granted through an external arbitration mechanism that allows devices to compete for bus mastership. This arbitration mechanism is flexible, allowing the 603 to be integrated into systems that implement various fairness and bus parking procedures to avoid arbitration overhead.

Typically, memory accesses are weakly ordered—sequences of operations, including load/store string and multiple instructions, do not necessarily complete in the order they begin—maximizing the efficiency of the bus without sacrificing coherency of the data. The 603 allows read operations to precede store operations (except when a dependency exists). Because the processor can dynamically optimize run-time ordering of load/store traffic, overall performance is improved.

# 1.7 System Support Functions

The 603 implements several support functions that include power management, time base/decrementer registers for system timing tasks, an IEEE 1149.1(JTAG)/common on-chip processor (COP) test interface, and a phase-locked loop (PLL) clock multiplier. These system support functions are described in the following subsections.

# 1.7.1 Power Management

The 603 provides four power modes selectable by setting the appropriate control bits in the machine state register (MSR) and hardware implementation register 0 (HID0) registers. The four power modes are as follows:

- Full-power—This is the default power state of the 603. The 603 is fully powered and the internal functional units are operating at the full processor clock speed. If the dynamic power management mode is enabled, functional units that are idle will automatically enter a low-power state without affecting performance, software execution, or external hardware.

- Doze–All the functional units of the 603 are disabled except for the time base/decrementer registers and the bus snooping logic. When the processor is in doze mode, an external asynchronous interrupt, a system management interrupt, a decrementer exception, a hard or soft reset, or machine check brings the 603 into the full-power state. The 603 in doze mode maintains the PLL in a fully powered state and locked to the system external clock input (SYSCLK) so a transition to the full-power state takes only a few processor clock cycles.

- Nap—The nap mode further reduces power consumption by disabling bus snooping, leaving only the time base register and the PLL in a powered state. The 603 returns to the full-power state upon receipt of an external asynchronous interrupt, a system management interrupt, a decrementer exception, a hard or soft reset, or a machine check input (MCP). A return to full-power state from a nap state takes only a few processor clock cycles.

- Sleep—Sleep mode reduces power consumption to a minimum by disabling all internal functional

units, after which external system logic may disable the PLL and SYSCLK. Returning the 603 to

the full-power state requires the enabling of the PLL and SYSCLK, followed by the assertion of an

external asynchronous interrupt, a system management interrupt, a hard or soft reset, or a machine

check input (MCP) signal after the time required to relock the PLL.

## 1.7.2 Time Base/Decrementer

The time base is a 64-bit register (accessed as two 32-bit registers) that is incremented once every four bus clock cycles; external control of the time base is provided through the time base enable (TBEN) signal. The decrementer is a 32-bit register that generates a decrementer exception after a programmable delay. The contents of the decrementer register are decremented once every four bus clock cycles, and the decrementer exception is generated as the count passes through zero.

# 1.7.3 IEEE 1149.1 (JTAG)/COP Test Interface

The 603 provides IEEE 1149.1 and COP functions for facilitating board testing and chip debug. The IEEE 1149.1 test interface provides a means for boundary-scan testing the 603 and the board to which it is attached. The COP function shares the IEEE 1149.1 test port, provides a means for executing test routines, and facilitates chip and software debugging.

# 1.7.4 Clock Multiplier

The internal clocking of the 603 is generated from and synchronized to the external clock signal, SYSCLK, by means of a voltage-controlled oscillator-based PLL. The PLL provides programmable internal processor clock rates of 1x, 2x, 3x, and 4x multiples of the externally supplied clock frequency. The bus clock is the same frequency and is synchronous with SYSCLK.

# Part 2 Levels of the PowerPC Architecture

The PowerPC architecture consists of the following layers, and adherence to the PowerPC architecture can be measured in terms of which of the following levels of the architecture is implemented:

PowerPC user instruction set architecture (UISA)—Defines the base user-level instruction set, user-level registers, data types, floating-point exception model, memory models for a uniprocessor environment, and programming model for a uniprocessor environment.

- PowerPC virtual environment architecture (VEA)—Describes the memory model for a

multiprocessor environment, defines cache control instructions, and describes other aspects of

virtual environments. Implementations that conform to the VEA also adhere to the UISA, but may

not necessarily adhere to the OEA.

- PowerPC operating environment architecture (OEA)—Defines the memory management model, supervisor-level registers, synchronization requirements, and the exception model. Implementations that conform to the OEA also adhere to the UISA and the VEA.

The PowerPC architecture allows a wide range of designs for such features as cache and system interface implementations.

# Part 3 PowerPC 603 Microprocessor: Implementation

The PowerPC architecture is derived from the IBM POWER Architecture<sup>TM</sup> (Performance Optimized with Enhanced RISC architecture). The PowerPC architecture shares the benefits of the POWER architecture optimized for single-chip implementations. The PowerPC architecture design facilitates parallel instruction execution and is scalable to take advantage of future technological gains.

This section describes the PowerPC architecture in general, and specific details about the implementation of the 603 as a low-power, 32-bit member of the PowerPC processor family.

- Features—Section 3.1, "Features," describes general features that the 603 shares with the PowerPC microprocessor family.

- Registers and programming model—Section 3.2, "PowerPC Registers and Programming Model," describes the registers for the operating environment architecture common among PowerPC processors and describes the programming model. It also describes the additional registers that are unique to the 603.

- Instruction set and addressing modes—Section 3.3, "Instruction Set and Addressing Modes," describes the PowerPC instruction set and addressing modes for the PowerPC operating environment architecture, and defines and describes the PowerPC instructions implemented in the 603.

- Cache implementation—Section 3.4, "Cache Implementation," describes the cache model that is defined generally for PowerPC processors by the virtual environment architecture. It also provides specific details about the 603 cache implementation.

- Exception model—Section 3.5, "Exception Model," describes the exception model of the PowerPC operating environment architecture and the differences in the 603 exception model.

- Memory management—Section 3.6, "Memory Management," describes generally the conventions for memory management among the PowerPC processors. This section also describes the 603's implementation of the 32-bit PowerPC memory management specification.

- Instruction timing—Section 3.7, "Instruction Timing," provides a general description of the instruction timing provided by the superscalar, parallel execution supported by the PowerPC architecture and the 603.

- System interface—Section 3.8, "System Interface," describes the signals implemented on the 603.

# 3.1 Features

The 603 is a high-performance, superscalar PowerPC microprocessor. The PowerPC architecture allows optimizing compilers to schedule instructions to maximize performance through efficient use of the PowerPC instruction set and register model. The multiple, independent execution units allow compilers to optimize instruction throughput. Compilers that take advantage of the flexibility of the PowerPC architecture can additionally optimize system performance of the PowerPC processors.

Specific features of the 603 are listed in Section 1.1, "PowerPC 603 Microprocessor Features."

# 3.2 PowerPC Registers and Programming Model

The PowerPC architecture defines register-to-register operations for most computational instructions. Source operands for these instructions are accessed from the registers or are provided as immediate values embedded in the instruction opcode. The three-register instruction format allows specification of a target register distinct from the two source operands. Load and store instructions transfer data between registers and memory.

PowerPC processors have two levels of privilege—supervisor mode of operation (typically used by the operating system) and user mode of operation (used by the application software). The programming models incorporate 32 GPRs, 32 FPRs, special-purpose registers (SPRs), and several miscellaneous registers. Each PowerPC microprocessor also has its own unique set of hardware implementation (HID) registers.

Having access to privileged instructions, registers, and other resources allows the operating system to control the application environment (providing virtual memory and protecting operating-system and critical machine resources). Instructions that control the state of the processor, the address translation mechanism, and supervisor registers can be executed only when the processor is operating in supervisor mode.

The following sections summarize the PowerPC registers that are implemented in the 603.

# 3.2.1 General-Purpose Registers (GPRs)

The PowerPC architecture defines 32 user-level, general-purpose registers (GPRs). These registers are either 32 bits wide in 32-bit PowerPC microprocessors and 64 bits wide in 64-bit PowerPC microprocessors. The GPRs serve as the data source or destination for all integer instructions.

# 3.2.2 Floating-Point Registers (FPRs)

The PowerPC architecture also defines 32 user-level, 64-bit floating-point registers (FPRs). The FPRs serve as the data source or destination for floating-point instructions. These registers can contain data objects of either single- or double-precision floating-point formats.

# 3.2.3 Condition Register (CR)

The CR is a 32-bit user-level register that consists of eight four-bit fields that reflect the results of certain operations, such as move, integer and floating-point compare, arithmetic, and logical instructions, and provide a mechanism for testing and branching.

# 3.2.4 Floating-Point Status and Control Register (FPSCR)

The floating-point status and control register (FPSCR) is a user-level register that contains all exception signal bits, exception summary bits, exception enable bits, and rounding control bits needed for compliance with the IEEE 754 standard.

# 3.2.5 Machine State Register (MSR)

The machine state register (MSR) is a supervisor-level register that defines the state of the processor. The contents of this register are saved when an exception is taken and restored when the exception handling completes. The 603 implements the MSR as a 32-bit register; 64-bit PowerPC processors implement a 64-bit MSR.

## 3.2.6 Segment Registers (SRs)

For memory management, 32-bit PowerPC microprocessors implement sixteen 32-bit segment registers (SRs). To speed access, the 603 implements the segment registers as two arrays; a main array (for data memory accesses) and a shadow array (for instruction memory accesses). Loading a segment entry with the Move to Segment Register (mtsr) instruction loads both arrays.

# 3.2.7 Special-Purpose Registers (SPRs)

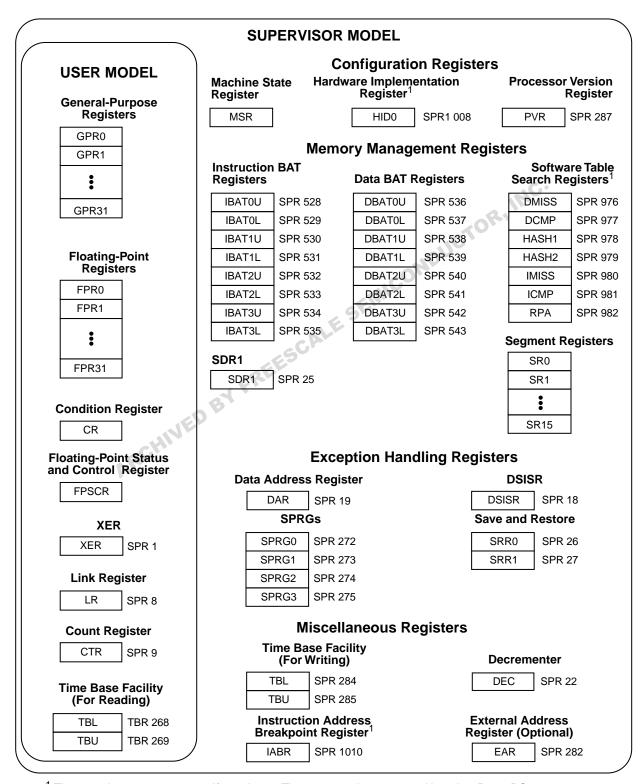

The PowerPC operating environment architecture defines numerous special-purpose registers that serve a variety of functions, such as providing controls, indicating status, configuring the processor, and performing special operations. During normal execution, a program can access the registers, shown in Figure 2, depending on the program's access privilege (supervisor or user, determined by the privilege-level (PR) bit in the MSR). Note that registers such as the GPRs and FPRs are accessed through operands that are part of the instructions. Access to registers can be explicit (that is, through the use of specific instructions for that purpose such as Move to Special-Purpose Register (mtspr) and Move from Special-Purpose Register (mfspr) instructions) or implicit, as the part of the execution of an instruction. Some registers are accessed SCALE SENII both explicitly and implicitly

In the 603, all SPRs are 32 bits wide.

#### 3.2.7.1 User-Level SPRs

The following 603 SPRs are accessible by user-level software:

- Link register (LR)—The link register can be used to provide the branch target address and to hold the return address after branch and link instructions. The LR is 32 bits wide in 32-bit implementations.

- Count register (CTR)—The CTR is decremented and tested automatically as a result of branch-andcount instructions. The CTR is 32 bits wide in 32-bit implementations.

- Integer exception register (XER)—The 32-bit XER contains the summary overflow bit, integer carry bit, overflow bit, and a field specifying the number of bytes to be transferred by a Load String Word Indexed (lswx) or Store String Word Indexed (stswx) instruction.

### 3.2.7.2 Supervisor-Level SPRs

The 603 also contains SPRs that can be accessed only by supervisor-level software. These registers consist of the following:

- The 32-bit DSISR defines the cause of data access and alignment exceptions.

- The data address register (DAR) is a 32-bit register that holds the address of an access after an alignment or DSI exception.

- Decrementer register (DEC) is a 32-bit decrementing counter that provides a mechanism for causing a decrementer exception after a programmable delay.

- The 32-bit SDR1 specifies the page table format used in virtual-to-physical address translation for pages. (Note that physical address is referred to as real address in the architecture specification.)

- The machine status save/restore register 0 (SRR0) is a 32-bit register that is used by the 603 for saving the address of the instruction that caused the exception, and the address to return to when a Return from Interrupt (rfi) instruction is executed.

- The machine status save/restore register 1 (SRR1) is a 32-bit register used to save machine status on exceptions and to restore machine status when an **rfi** instruction is executed.

- The 32-bit SPRG0-SPRG3 registers are provided for operating system use.

- The external access register (EAR) is a 32-bit register that controls access to the external control facility through the External Control In Word Indexed (eciwx) and External Control Out Word Indexed (ecowx) instructions.

- The time base register (TB) is a 64-bit register that maintains the time of day and operates interval timers. The TB consists of two 32-bit fields—time base upper (TBU) and time base lower (TBL).

- The processor version register (PVR) is a 32-bit, read-only register that identifies the version (model) and revision level of the PowerPC processor.

- Block address translation (BAT) arrays—The PowerPC architecture defines 16 BAT registers, divided into four pairs of data BATs (DBATs) and four pairs of instruction BATs (IBATs). See Figure 2 for a list of the SPR numbers for the BAT arrays.

The following supervisor-level SPRs are implementation-specific to the 603:

- The DMISS and IMISS registers are read-only registers that are loaded automatically upon an instruction or data TLB miss.

- The HASH1 and HASH2 registers contain the physical addresses of the primary and secondary page table entry groups (PTEGs).

- The ICMP and DCMP registers contain a duplicate of the first word in the page table entry (PTE) for which the table search is looking.

- The required physical address (RPA) register is loaded by the processor with the second word of the correct PTE during a page table search.

- The hardware implementation (HID0) register provides means for enabling the 603's checkstops and features.

- The instruction address breakpoint register (IABR) is loaded with an instruction address that is compared to instruction addresses in the dispatch queue. When an address match occurs, an instruction address breakpoint exception is generated.

Figure 2 shows all the 603 registers available at the user and supervisor level. The numbers to the right of the SPRs indicate the number that is used in the syntax of the instruction operands to access the register.

<sup>&</sup>lt;sup>1</sup> These registers are 603–specific registers. They may not be supported by other PowerPC processors.

Figure 2. PowerPC 603 Microprocessor Programming Model—Registers

# 3.3 Instruction Set and Addressing Modes

The following subsections describe the PowerPC instruction set and addressing modes in general.

# 3.3.1 PowerPC Instruction Set and Addressing Modes

All PowerPC instructions are encoded as single-word (32-bit) opcodes. Instruction formats are consistent among all instruction types, permitting efficient decoding to occur in parallel with operand accesses. This fixed instruction length and consistent format greatly simplifies instruction pipelining.

#### 3.3.1.1 PowerPC Instruction Set

The PowerPC instructions are divided into the following categories:

- Integer instructions—These include computational and logical instructions. :MICONDUC

- Integer arithmetic instructions

- Integer compare instructions

- Integer logical instructions

- Integer rotate and shift instructions

- Floating-point instructions—These include floating-point computational instructions, as well as instructions that affect the FPSCR.

- Floating-point arithmetic instructions

- Floating-point multiply/add instructions

- Floating-point rounding and conversion instructions

- Floating-point compare instructions

- Floating-point status and control instructions

- Load/store instructions—These include integer and floating-point load and store instructions.

- Integer load and store instructions

- Integer load and store multiple instructions

- Floating-point load and store

- Primitives used to construct atomic memory operations (lwarx and stwex. instructions)

- Flow control instructions—These include branching instructions, condition register logical instructions, trap instructions, and other instructions that affect the instruction flow.

- Branch and trap instructions

- Condition register logical instructions

- Processor control instructions—These instructions are used for synchronizing memory accesses and management of caches, TLBs, and the segment registers.

- Move to/from SPR instructions

- Move to/from MSR

- Synchronize

- Instruction synchronize

- Memory control instructions—These instructions provide control of caches, TLBs, and segment registers.

- Supervisor-level cache management instructions

- User-level cache instructions

- Segment register manipulation instructions

- Translation lookaside buffer management instructions

Note that this grouping of the instructions does not indicate which execution unit executes a particular instruction or group of instructions.

Integer instructions operate on byte, half-word, and word operands. Floating-point instructions operate on single-precision (one word) and double-precision (one double word) floating-point operands. The PowerPC architecture uses instructions that are four bytes long and word-aligned. It provides for byte, half-word, and word operand loads and stores between memory and a set of 32 GPRs. It also provides for word and double-word operand loads and stores between memory and a set of 32 floating-point registers (FPRs).

Computational instructions do not modify memory. To use a memory operand in a computation and then modify the same or another memory location, the memory contents must be loaded into a register, modified, and then written back to the target location with distinct instructions.

PowerPC processors follow the program flow when they are in the normal execution state. However, the flow of instructions can be interrupted directly by the execution of an instruction or by an asynchronous event. Either kind of exception may cause one of several components of the system software to be invoked.

## 3.3.1.2 Calculating Effective Addresses

The effective address (EA) is the 32-bit address computed by the processor when executing a memory access or branch instruction or when fetching the next sequential instruction.

The PowerPC architecture supports two simple memory addressing modes:

- EA =  $(\mathbf{r}A|0)$  + offset (including offset = 0) (register indirect with immediate index)

- $EA = (\mathbf{r}A|0) + \mathbf{r}B$  (register indirect with index)

These simple addressing modes allow efficient address generation for memory accesses. Calculation of the effective address for aligned transfers occurs in a single clock cycle.

For a memory access instruction, if the sum of the effective address and the operand length exceeds the maximum effective address, the memory operand is considered to wrap around from the maximum effective address to effective address 0.

Effective address computations for both data and instruction accesses use 32-bit unsigned binary arithmetic. A carry from bit 0 is ignored in 32-bit implementations.

# 3.3.2 PowerPC 603 Microprocessor Instruction Set

The 603 instruction set is defined as follows:

- The 603 provides hardware support for all 32-bit PowerPC instructions.

- The 603 provides two implementation-specific instructions used for software table search operations following TLB misses:

- Load Data TLB Entry (tlbld)

- Load Instruction TLB Entry (tlbli)

- The 603 implements the following instructions which are defined as optional by the PowerPC architecture:

- External Control In Word Indexed (eciwx)

- External Control Out Word Indexed (ecowx)

- Floating Select (fsel)

- Floating Reciprocal Estimate Single-Precision (fres)

- Floating Reciprocal Square Root Estimate (frsqrte)

- Store Floating-Point as Integer Word (stfiwx)

# 3.4 Cache Implementation

The following subsections describe the PowerPC architecture's treatment of cache in general, and the 603specific implementation, respectively.

# 3.4.1 PowerPC Cache Characteristics

The PowerPC architecture does not define hardware aspects of cache implementations. For example, some PowerPC processors, including the 603, have separate instruction and data caches (Harvard architecture), while others, such as the PowerPC 601<sup>TM</sup> microprocessor, implement a unified cache.

PowerPC microprocessors control the following memory access modes on a page or block basis:

- Write-back/write-through mode

- Cache-inhibited mode

- Memory coherency

DUCTOR, Note that in the 603, a cache line is defined as eight words. The VEA defines cache management instructions that provide a means by which the application programmer can affect the cache contents.

## 3.4.2 PowerPC 603 Microprocessor Cache Implementation

The 603 has two 8-Kbyte, two-way set-associative (instruction and data) caches. The caches are physically addressed, and the data cache can operate in either write-back or write-through mode as specified by the PowerPC architecture.

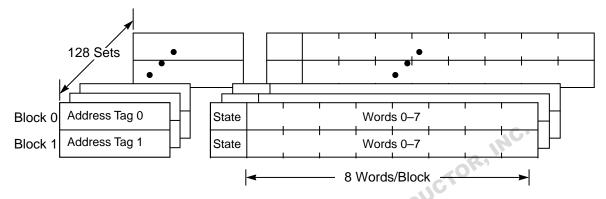

The data cache is configured as 128 sets of 2 lines each. Each line consists of 32 bytes, two state bits, and an address tag. The two state bits implement the three-state MEI (modified/exclusive/invalid) protocol. Each line contains eight 32-bit words. Note that the PowerPC architecture defines the term block as the cacheable unit. For the 603, the block size is equivalent to a cache line. A block diagram of the data cache organization is shown in Figure 3.

The instruction cache also consists of 128 sets of 2 lines, and each line consists of 32 bytes, an address tag, and a valid bit. The instruction cache may not be written to except through a line fill operation. The instruction cache is not snooped, and cache coherency must be maintained by software. A fast hardware invalidation capability is provided to support cache maintenance. The organization of the instruction cache is very similar to the data cache shown in Figure 3.

Each cache line contains eight contiguous words from memory that are loaded from an 8-word boundary (that is, bits A27–A31 of the effective addresses are zero); thus, a cache line never crosses a page boundary. Misaligned accesses across a page boundary can incur a performance penalty.

The 603's cache lines are loaded in four beats of 64 bits each. The burst load is performed as "critical double word first." The cache that is being loaded is blocked to internal accesses until the load completes. The critical double word is simultaneously written to the cache and forwarded to the requesting unit, thus minimizing stalls due to load delays.

To ensure coherency among caches in a multiprocessor (or multiple caching-device) implementation, the 603 implements the MEI protocol. These three states, modified, exclusive, and invalid, indicate the state of the cache block as follows:

- Modified—The cache line is modified with respect to system memory; that is, data for this address is valid only in the cache and not in system memory.

- Exclusive—This cache line holds valid data that is identical to the data at this address in system memory. No other cache has this data.

- Invalid—This cache line does not hold valid data.

Cache coherency is enforced by on-chip bus snooping logic. Since the 603's data cache tags are single ported, a simultaneous load or store and snoop access represent a resource contention. The snoop access is given first access to the tags. The load or store then occurs on the clock following the snoop.

Figure 3. Data Cache Organization

# 3.5 Exception Model

The following subsections describe the PowerPC exception model and the 603 implementation, respectively.

# 3.5.1 PowerPC Exception Model

The PowerPC exception mechanism allows the processor to change to supervisor state as a result of external signals, errors, or unusual conditions arising in the execution of instructions, and differ from the arithmetic exceptions defined by the IEEE for floating-point operations. When exceptions occur, information about the state of the processor is saved to certain registers and the processor begins execution at an address (exception vector) predetermined for each exception. Processing of exceptions occurs in supervisor mode.

Although multiple exception conditions can map to a single exception vector, a more specific condition may be determined by examining a register associated with the exception—for example, the DSISR and the FPSCR. Additionally, some exception conditions can be explicitly enabled or disabled by software.

The PowerPC architecture requires that exceptions be handled in program order; therefore, although a particular implementation may recognize exception conditions out of order, they are presented strictly in order. When an instruction-caused exception is recognized, any unexecuted instructions that appear earlier in the instruction stream, including any that have not yet entered the execute state, are required to complete before the exception is taken. Any exceptions caused by those instructions are handled first. Likewise, exceptions that are asynchronous and precise are recognized when they occur, but are not handled until the instruction currently in the completion stage successfully completes execution or generates an exception, and the completed store queue is emptied.

Unless a catastrophic condition causes a system reset or machine check exception, only one exception is handled at a time. If, for example, a single instruction encounters multiple exception conditions, those conditions are encountered sequentially. After the exception handler handles an exception, the instruction execution continues until the next exception condition is encountered. However, in many cases there is no attempt to re-execute the instruction. This method of recognizing and handling exception conditions sequentially guarantees that exceptions are recoverable.

Exception handlers should save the information stored in SRR0 and SRR1 early to prevent the program state from being lost due to a system reset and machine check exception or to an instruction-caused exception in the exception handler, and before enabling external interrupts.

The PowerPC architecture supports four types of exceptions:

- Synchronous, precise—These are caused by instructions. All instruction-caused exceptions are handled precisely; that is, the machine state at the time the exception occurs is known and can be completely restored. This means that (excluding the trap and system call exceptions) the address of the faulting instruction is provided to the exception handler and that neither the faulting instruction nor subsequent instructions in the code stream will complete execution before the exception is taken. Once the exception is processed, execution resumes at the address of the faulting instruction (or at an alternate address provided by the exception handler). When an exception is taken due to a trap or system call instruction, execution resumes at an address provided by the handler.

- Synchronous, imprecise—The PowerPC architecture defines two imprecise floating-point exception modes, recoverable and nonrecoverable. Even though the 603 provides a means to enable the imprecise modes, it implements these modes identically to the precise mode (that is, all enabled floating-point enabled exceptions are always precise on the 603).

- Asynchronous, maskable—The external, SMI, and decrementer interrupts are maskable asynchronous exceptions. When these exceptions occur, their handling is postponed until the next instruction, and any exceptions associated with that instruction, completes execution. If there are no instructions in the execution units, the exception is taken immediately upon determination of the correct restart address (for loading SRRO).

- Asynchronous, nonmaskable—There are two nonmaskable asynchronous exceptions: system reset and the machine check exception. These exceptions may not be recoverable, or may provide a limited degree of recoverability. All exceptions report recoverability through the MSR[RI] bit.

## 3.5.2 PowerPC 603 Microprocessor Exception Model

As specified by the PowerPC architecture, all 603 exceptions can be described as either precise or imprecise and either synchronous or asynchronous. Asynchronous exceptions (some of which are maskable) are caused by events external to the processor's execution; synchronous exceptions, which are all handled precisely by the 603, are caused by instructions. The 603 exception classes are shown in Table 1.

| Synchronous/Asynchronous  | Precise/Imprecise | Exception Type                                             |

|---------------------------|-------------------|------------------------------------------------------------|

| Asynchronous, nonmaskable | Imprecise         | Machine check<br>System reset                              |

| Asynchronous, maskable    | Precise           | External interrupt Decrementer System management interrupt |

| Synchronous               | Precise           | Instruction-caused exceptions                              |

Table 1. PowerPC 603 Microprocessor Exception Classifications

Although exceptions have other characteristics as well, such as whether they are maskable or nonmaskable, the distinctions shown in Table 1 define categories of exceptions that the 603 handles uniquely. Note that Table 1 includes no synchronous imprecise instructions. While the PowerPC architecture supports imprecise handling of floating-point exceptions, the 603 implements these exception modes as precise exceptions.

The 603's exceptions, and conditions that cause them, are listed in Table 2. Exceptions that are specific to the 603 are indicated.

**Table 2. Exceptions and Conditions**

| Exception<br>Type  | Vector Offset<br>(hex) | Causing Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reserved           | 00000                  | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| System reset       | 00100                  | A system reset is caused by the assertion of either SRESET or HRESET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Machine check      | 00200                  | A machine check is caused by the assertion of the TEA signal during a data bus transaction, assertion of MCP, or an address or data parity error.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| DSI                | 00300                  | The cause of a DSI exception can be determined by the bit settings in the DSISR, listed as follows:  1 Set if the translation of an attempted access is not found in the primary hash table entry group (HTEG), or in the rehashed secondary HTEG, or in the range of a DBAT register; otherwise cleared.  4 Set if a memory access is not permitted by the page or DBAT protection mechanism; otherwise cleared.  5 Set if the access was to an I/O segment (SR[T] =1) by an eciwx, ecowx, lwarx, or stwcx. instruction; otherwise cleared.  6 Set for a store operation and cleared for a load operation.  11 Set if eciwx or ecowx is used and EAR[E] is cleared. |

| ISI                | 00400                  | <ul> <li>An ISI exception is caused when an instruction fetch cannot be performed for any of the following reasons:</li> <li>The effective (logical) address cannot be translated. That is, there is a page fault for this portion of the translation, so an ISI exception must be taken to load the PTE (and possibly the page) into memory.</li> <li>The fetch access is to a direct-store segment.</li> <li>The fetch access violates memory protection. If the key bits (Ks and Kp) in the segment register and the PP bits in the PTE are set to prohibit read access, instructions cannot be fetched from this location.</li> </ul>                            |

| External interrupt | 00500                  | An external interrupt is caused when MSR[EE] = 1 and the INT signal is asserted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Alignment          | 00600                  | An alignment exception is caused when the 603 cannot perform a memory access for any of several reasons, such as when the operand of a floating-point load or store operation is in an I/O segment (SR[T] = 1).                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

**Table 2. Exceptions and Conditions (Continued)**

| Exception<br>Type                    | Vector Offset<br>(hex) | Causing Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|--------------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Program                              | 00700                  | A program exception is caused by one of the following exception conditions, which correspond to bit settings in SRR1 and arise during execution of an instruction:  • Floating-point enabled exception—A floating-point enabled exception condition is generated when the following condition is met:  (MSR[FE0]   MSR[FE1]) & FPSCR[FEX] is 1.  FPSCR[FEX] is set by the execution of a floating-point instruction that causes an enabled exception or by the execution of one of the "move to FPSCR" instructions that results in both an exception condition bit and its corresponding enable bit being set in the FPSCR.  • Illegal instruction—An illegal instruction program exception is generated when execution of an instruction is attempted with an illegal opcode or illegal combination of opcode and extended opcode fields (including PowerPC instructions not implemented in the 603), or when execution of an optional instruction not provided in the 603 is attempted (these do not include those optional instructions that are treated as no-ops).  • Privileged instruction—A privileged instruction type program exception is generated when the execution of a privileged instruction is attempted and the MSR register user privilege bit, MSR[PR], is set. In the 603, this exception is generated for mtspr or mfspr with an invalid SPR field if SPR[0] = 1 and MSR[PR] = 1. This may not be true for all PowerPC processors.  • Trap—A trap type program exception is generated when any of the conditions specified in a trap instruction is met. |  |

| Floating-point unavailable           | 00800                  | A floating-point unavailable exception is caused by an attempt to execute a floating-point instruction (including floating-point load, store, and move instructions) when the floating-point available bit is disabled, (MSR[FP] = 0).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| Decrementer                          | 00900                  | The decrementer exception occurs when the most significant bit of the decrementer (DEC) register transitions from 0 to 1. Must also be enabled with the MSR[EE] bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| Reserved                             | 00A00-00BFF            | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| System call                          | 00C00                  | A system call exception occurs when a System Call (sc) instruction is executed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| Trace                                | 00D00                  | A trace exception is taken when MSR[SE] =1 or when the currently completing instruction is a branch and MSR[BE] =1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| Reserved                             | 00E00                  | The 603 does not generate an exception to this vector. Other PowerPC processors may use this vector for floating-point assist exceptions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Reserved                             | 00E10-00FFF            | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |