Freescale Semiconductor Advance Information Document Number: MPC7410ECS04AD Rev. 1.1, 04/2005

# MPC7410 RISC Microprocessor Hardware Specifications Addendum for the MPC7410RX*nnn*PD Series

This document describes part-number-specific changes to recommended operating conditions and revised electrical specifications, as applicable, from those described in the general *MPC7410 Hardware Specifications* (Document no. MPC7410EC).

Specifications provided in this document supersede those in the *MPC7410 Hardware Specifications*, for the part numbers listed in Table A only. Specifications not addressed herein are unchanged. Because this document is frequently updated, refer to http://www.freescale.com or to your Freescale sales office for the latest version.

Note that headings and table numbers in this document are not consecutively numbered. They are intended to correspond to the heading or table affected in the general hardware specification. Part numbers addressed in this document are listed in Table A. For more detailed ordering information, see Table 17. Freescale Part Numbers Affected: XPC7410RX450PD XPC7410RX500PD XPC7410RX533PD

This document contains information on a new product. Specifications and information herein are subject to change without notice.

© Freescale Semiconductor, Inc., 2002, 2005. All rights reserved.

| Freescale Part     | Operat  | ing Condition       | s                                                   |                                                                          |

|--------------------|---------|---------------------|-----------------------------------------------------|--------------------------------------------------------------------------|

| Number CPU         |         | Т <sub>Ј</sub> (°С) | Significant Differences from Hardware Specification |                                                                          |

| XPC7410RX450P<br>D | 450 MHz | 2.0V±50mV           | 0 to 65                                             | Modified Voltage & Temperature Specification to achieve 450Mhz frequency |

| XPC7410RX500P<br>D | 500 MHz | 2.0V±50mV           | 0 to 65                                             | Modified Voltage & Temperature Specification to achieve 500Mhz frequency |

| XPC7410RX533P<br>D | 533 MHz | 2.0V±50mV           | 0 to 65                                             | Modified Voltage & Temperature Specification to achieve 533Mhz frequency |

Note:

The X prefix in a Freescale part number designates a "Pilot Production Prototype" as defined by Freescale SOP 3-13. These are from a limited production volume of prototypes manufactured, tested and Q.A. inspected on a qualified technology to simulate normal production. These parts have only preliminary reliability and characterization data. Before pilot production prototypes may be shipped, written authorization from the customer must be on file in the applicable sales office acknowledging the qualification status and the fact that product changes may still occur while shipping pilot production prototypes.

## 2 Features

This section summarizes changes to the features of the MPC7410 described in the *MPC7410 Hardware Specifications*, which are none.

## **4.1 DC Electrical Characteristics**

Table 3 provides the recommended operating conditions for the MPC7410 part numbers described herein.

Table 3. Recommended Operating Conditions

| Character                    | istic                            | Symbol            | Recommended<br>Value | Unit |  |

|------------------------------|----------------------------------|-------------------|----------------------|------|--|

| Core supply voltage          |                                  | Vdd               | 2.0V ± 50mV          | V    |  |

| PLL supply voltage           |                                  | AVdd              | 2.0V ±5 0mV          | V    |  |

| L2 DLL supply voltage        |                                  | L2AVdd 2.0V ± 50m |                      |      |  |

| Processor bus supply voltage | BVSEL = 1 or<br>BVSEL = HRESET   | OVdd              | 2.5V ± 125mV         | V    |  |

|                              | BVSEL = GND                      | OVdd              | 1.8V ± 90mV          | V    |  |

| L2 bus supply voltage        | L2VSEL = 1 or<br>L2VSEL = HRESET | L2OVdd            | 2.5V ± 125mV         | V    |  |

|                              | L2VSEL = GND                     | L2OVdd            | 1.8V ± 90mV          | V    |  |

| Input voltage                | Processor bus                    | V <sub>in</sub>   | GND to OVdd          | V    |  |

|                              | L2 Bus                           | V <sub>in</sub>   | GND to L2OVdd        | V    |  |

|                              | JTAG Signals                     | V <sub>in</sub>   | GND to OVdd          | V    |  |

| Characteristic           | Symbol | Recommended<br>Value | Unit |

|--------------------------|--------|----------------------|------|

| Die-junction temperature | Тj     | 0-65                 | °C   |

| Noto                     | 1      |                      |      |

Note:

These are the recommended and tested operating conditions. Proper device operation outside of these conditions is not guaranteed.

## Table 6 provides the power consumption for the MPC7410 part at the frequencies described herein.Table 6. Power Consumption for MPC7410

|                                 | Processor<br>(CPU)<br>Frequency | Processor<br>(CPU)<br>Frequency | Processor<br>(CPU)<br>Frequency | Unit | Notes |  |  |  |  |

|---------------------------------|---------------------------------|---------------------------------|---------------------------------|------|-------|--|--|--|--|

|                                 | 450Mhz                          | 500Mhz                          | 533Mhz                          |      |       |  |  |  |  |

| Full-On Mode                    |                                 |                                 |                                 |      |       |  |  |  |  |

| Typical                         | 5.9                             | 6.5                             | 6.9                             | W    | 1, 3  |  |  |  |  |

| Maximum                         | 13.2                            | 14.7                            | 15.6                            | W    | 1, 2  |  |  |  |  |

| Doze Mode                       |                                 |                                 |                                 |      |       |  |  |  |  |

| Maximum                         | 4.5                             | 5                               | 5.3                             | W    | 1, 2  |  |  |  |  |

| Nap Mode                        |                                 |                                 |                                 |      |       |  |  |  |  |

| Maximum                         | 2.13                            | 2.25                            | 2.33                            | W    | 1, 2  |  |  |  |  |

| Sleep Mode                      |                                 |                                 |                                 |      |       |  |  |  |  |

| Maximum                         | 2.13                            | 2.25                            | 2.33                            | W    | 1, 2  |  |  |  |  |

| Sleep Mode—PLL and DLL Disabled |                                 |                                 |                                 |      |       |  |  |  |  |

| Typical                         | 0.5                             | 0.5                             | 0.5                             | W    | 1, 3  |  |  |  |  |

| Maximum                         | 2.0                             | 2.0                             | 2.0                             | W    | 1, 2  |  |  |  |  |

Notes:

- These values apply for all valid processor bus and L2 bus ratios. The values do not include I/O Supply Power (OVdd and L2OVdd) or PLL/DLL supply power (AVdd and L2AVdd). OVdd and L2OVdd power is system dependent, but is typically <10% of Vdd power. Worst case power consumption for AVdd = 15 mw and L2AVdd = 15 mW.

- 2. Maximum power is measured at 65 °C and Vdd = 2.0V while running an entirely cache-resident, contrived sequence of instructions which keep the execution units, including AltiVec, maximally busy.

- 3. Typical power is an average value measured at 65 °C and Vdd = 2.0V in a system while running typical benchmarks.

**DC Electrical Characteristics**

### 4.2.1 Clock AC Specifications

Table 7 provides the additional clock AC timing specifications described in this document. Refer to the *MPC7410 Hardware Specification* for the remaining frequencies.

| Table 7. Clock AC Timing Specificati | ions |

|--------------------------------------|------|

|--------------------------------------|------|

At recommended operating conditions (See Table 3.)

| Characteristic                          | Symbol                                     | 450 MHz |      | 500 MHz |      | 533 | MHz  | Unit | Notes  |

|-----------------------------------------|--------------------------------------------|---------|------|---------|------|-----|------|------|--------|

| Characteristic                          | Symbol                                     | Min     | Max  | Min     | Max  | Min | Max  | Unit | 110100 |

| Processor frequency                     | f <sub>core</sub>                          | 300     | 450  | 300     | 500  | 300 | 533  | MHz  |        |

| VCO frequency                           | f <sub>VCO</sub>                           | 600     | 900  | 600     | 1000 | 600 | 1066 | MHz  |        |

| SYSCLK frequency                        | f <sub>SYSCLK</sub>                        | 33      | 133  | 33      | 133  | 33  | 133  | MHz  | 1      |

| SYSCLK cycle time                       | t <sub>SYSCLK</sub>                        | 7.5     | 30   | 7.5     | 30   | 7.5 | 30   | ns   |        |

| SYSCLK rise and fall time               | t <sub>KR</sub>                            | _       | 1.0  | _       | 1.0  | _   | 1.0  | ns   | 2      |

|                                         | t <sub>KF</sub>                            |         | 0.5  | _       | 0.5  | _   | 0.5  | ns   | 3      |

| SYSCLK duty cycle<br>measured at OVdd/2 | t <sub>KHKL</sub> /t <sub>SYS</sub><br>CLK | 40      | 60   | 40      | 60   | 40  | 60   | %    | 4      |

| SYSCLK jitter                           |                                            | _       | ±150 | —       | ±150 | —   | ±150 | ps   | 5      |

| Internal PLL relock time                |                                            | _       | 100  | —       | 100  | —   | 100  | μS   | 6      |

### Note:

See general hardware specification.

### 4.2.2 Processor Bus AC Specifications

Table 8 provides the processor bus AC timing specifications for the MPC7410 part described in this document.

### Table 8. Processor Bus AC Timing Specifications

At Vdd=AVdd=2.0V $\pm$ 50mV; 0  $\leq$  Tj  $\leq$  65°C, OVdd = 2.5V $\pm$ 0.125V and OVdd = 1.8V $\pm$ 0.090V, 60X bus at 133MHz

| Parameter                               | Symbol             | -   | 00, 533<br>hz | Unit        | Notes   |

|-----------------------------------------|--------------------|-----|---------------|-------------|---------|

|                                         |                    | Min | Max           |             |         |

| Mode select input setup to HRESET       | t <sub>MVRH</sub>  | 8   | —             | t<br>sysclk | 2,3,4,5 |

| HRESET to mode select input hold        | t <sub>MXRH</sub>  | 0   | _             | ns          | 2,3,5   |

| Setup Times:                            |                    |     |               | ns          | 10      |

| Address/Transfer Attribute              | t <sub>AVKH</sub>  | 1.4 |               |             | 6       |

| Transfer Start (TS)<br>Data/Data Parity | t <sub>TSVKH</sub> | 1.4 |               |             | —       |

| ARTRY/SHD0/SHD1                         | t <sub>DVKH</sub>  | 1.4 | —             |             | 7       |

| All Other Inputs                        | t <sub>ARVKH</sub> | 1.4 | —             |             | —       |

|                                         | t <sub>IVKH</sub>  | 1.4 | —             |             | 8       |

### Table 8. Processor Bus AC Timing Specifications (continued)

At Vdd=AVdd=2.0V $\pm$ 50mV; 0  $\leq$  Tj  $\leq$  65°C, OVdd = 2.5V $\pm$ 0.125V and OVdd = 1.8V $\pm$ 0.090V, 60X bus at 133MHz

| Parameter                                                                              | Symbol              | 450, 50<br>M | 00, 533<br>hz | Unit                | Notes          |

|----------------------------------------------------------------------------------------|---------------------|--------------|---------------|---------------------|----------------|

|                                                                                        |                     | Min          | Max           |                     |                |

| Input Hold Times:                                                                      |                     |              |               | ns                  | 11             |

| Address/Transfer Attribute                                                             | t <sub>AXKH</sub>   | 0            | —             |                     | 6              |

| Transfer Start (TS)<br>Data/Data Parity                                                | t <sub>тsxкн</sub>  | 0            | —             |                     | —              |

| ARTRY/SHD0/SHD1                                                                        | t <sub>DXKH</sub>   | 0            | —             |                     | 7              |

| All Other Inputs                                                                       | t <sub>ARXKH</sub>  | 0            | —             |                     | —              |

|                                                                                        | t <sub>IXKH</sub>   | 0            | —             |                     | 8              |

| Valid Times:                                                                           |                     |              |               | ns                  | 12             |

| Address/Transfer Attribute                                                             | t <sub>KHAV</sub>   |              | 3.0           |                     | 6              |

| TS, ABB, DBB<br>Data                                                                   | t <sub>KHTSV</sub>  | —            | 3.0           |                     | —              |

| Data Parity                                                                            | t <sub>KHDV</sub>   |              | 3.5           |                     | 7              |

| ARTRY/SHD0/SHD1                                                                        | t <sub>KHDPV</sub>  |              | 3.5           |                     | 7              |

| All Other Outputs                                                                      | t <sub>KHARV</sub>  |              | 2.3           |                     | —              |

|                                                                                        | t <sub>KHOV</sub>   |              | 3.0           |                     | 9              |

| Output Hold Times:                                                                     |                     |              |               | ns                  | 13             |

| Address/Transfer Attribute                                                             | t <sub>KHAX</sub>   | 0.75         | —             |                     | 6              |

| TS, ABB, DBB<br>Data/Data Parity                                                       | <sup>t</sup> кнтsx  | 0.75         | —             |                     | —              |

| ARTRY/SHD0/SHD1                                                                        | t <sub>KHDX</sub>   | 0.6          | —             |                     | 7              |

| All Other Outputs                                                                      | t <sub>KHARX</sub>  | 0.75         | —             |                     | —              |

|                                                                                        | t <sub>KHOX</sub>   | 0.75         | —             |                     | 9              |

| SYSCLK to Output Enable                                                                | t <sub>KHOE</sub>   | 0.5          | _             | ns                  | 14             |

| SYSCLK to Output High Impedance<br>(all except TS, ABB/AMON(0), ARTRY/SHD, DBB/DMON(0) | <sup>t</sup> кноz   | —            | 3.5           | ns                  | 15             |

| SYSCLK to TS, ABB/AMON(0), DBB/DMON(0) High Impedance after precharge                  | t <sub>KHABPZ</sub> | _            | 1.0           | t <sub>sysclk</sub> | 4,15,<br>16,17 |

| Maximum Delay to ARTRY/SHD0/SHD1 Precharge                                             | t <sub>KHARP</sub>  | —            | 1             | t<br>sysclk         | 4,17           |

| SYSCLK to ARTRY/SHD0/SHD1 High Impedance After Precharge                               | t <sub>KHARPZ</sub> |              | 2             | t <sub>sysclk</sub> | 4,17           |

### Note:

See general hardware specification.

**DC Electrical Characteristics**

### 4.2.3 L2 Clock AC Specifications

Table 9 provides the L2CLK Output AC Timing Specifications for the MPC7410 part described in this document.

### Table 9. L2CLK Output AC Timing Specifications

At recommended operating conditions (See Table 3.)

| Parameter                   | Symbol                                    | 450 MHz |      | 500 MHz |      | 533  | MHz  | Unit  | Notes |

|-----------------------------|-------------------------------------------|---------|------|---------|------|------|------|-------|-------|

| Falameter                   | Symbol                                    | Min     | Max  | Min     | Max  | Min  | Max  | onit  | NOLES |

| L2CLK frequency             | f <sub>L2CLK</sub>                        | 150     | 225  | 150     | 250  | 150  | 266  | MHz   | 1     |

| L2CLK cycle time            | t <sub>L2CLK</sub>                        | 4.4     | 6.67 | 4.0     | 6.67 | 3.76 | 6.67 | ns    |       |

| L2CLK duty cycle            | t <sub>CHCL</sub> /t <sub>L2</sub><br>СLК | 5       | 50   |         | 50   | 50   |      | %     | 2     |

| Internal DLL-relock<br>time |                                           | 640     | _    | 640     | _    | 640  | _    | L2CLK | 4     |

| DLL capture window          |                                           |         | ±200 |         | ±200 |      | ±200 | ns    | 5     |

### Note:

See general hardware specification.

### 4.2.4 L2 Bus AC Specifications

Table 10 provides the L2 Bus Interface AC Timing Specifications for the frequencies described in this document.

### Table 10. L2 Bus Interface AC Timing Specifications

At Vdd=AVdd=L2AVdd= 2.05V $\pm$ 50mV; 0  $\leq$  Tj  $\leq$  65°C, L2OVdd = 2.5V $\pm$ 0.125V and L2OVdd =1.8V $\pm$ 0.090V

| Parameter                                                                                                                                                                                    | Symbol                                   | 450                       | MHz                        | 500 MHz                  |                           | 533 MHz                   |                           | Unit | Notes |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|---------------------------|----------------------------|--------------------------|---------------------------|---------------------------|---------------------------|------|-------|

| Falanielei                                                                                                                                                                                   | Symbol                                   | Min                       | Max                        | Min                      | Мах                       | Min                       | Max                       | Onit | NOLES |

| L2SYNC_IN rise and fall time                                                                                                                                                                 | t <sub>L2CR</sub> &<br>t <sub>L2CF</sub> |                           | 1.0                        |                          | 1.0                       |                           | 1.0                       | ns   | 1     |

| Setup Times:<br>Data and parity                                                                                                                                                              | t <sub>DVL2CH</sub>                      | 1.375                     | _                          | 1.250                    | _                         | 1.168                     | _                         | ns   | 2     |

| Input Hold Times:<br>Data and parity                                                                                                                                                         | t <sub>DXL2CH</sub>                      | _                         | 0.0                        | _                        | 0.0                       | _                         | 0.0                       | ns   | 2     |

| Valid Times:<br>All outputs when L2CR[14-15] =<br>00<br>All outputs when L2CR[14-15] =<br>01<br>All outputs when L2CR[14-15] =<br>10<br>All outputs when L2CR[14-15] =<br>11                 | t <sub>l2CHOV</sub>                      | -<br>-<br>-               | 2.375<br>TBD<br>TBD<br>TBD | -<br>-<br>-              | 2.25<br>TBD<br>TBD<br>TBD | -<br>-<br>-               | 2.17<br>TBD<br>TBD<br>TBD | ns   | 3,4   |

| Output Hold Times<br>All outputs when L2CR[14-15] =<br>00<br>All outputs when L2CR[14-15] =<br>01<br>All outputs when L2CR[14-15] =<br>10<br>All outputs when L2CR[14-15] =<br>11            | t <sub>L2CHOX</sub>                      | 0.55<br>TBD<br>TBD<br>TBD | -                          | 0.5<br>TBD<br>TBD<br>TBD | -                         | 0.47<br>TBD<br>TBD<br>TBD | -                         | ns   | 3     |

| L2SYNC_IN to high impedance:<br>All outputs when L2CR[14-15] =<br>00<br>All outputs when L2CR[14-15] =<br>01<br>All outputs when L2CR[14-15] =<br>10<br>All outputs when L2CR[14-15] =<br>11 | t <sub>L2CHOZ</sub>                      | -<br>-<br>-               | 2.0<br>2.5<br>3.0<br>3.5   | -<br>-<br>-              | 2.0<br>2.5<br>3.0<br>3.5  | -<br>-<br>-               | 2.0<br>2.5<br>3.0<br>3.5  | ns   |       |

Note:

See general hardware specification.

Document Revision History

## **9 Document Revision History**

Table 16 provides a revision history for this document.

| Table 16. Document Revision History |

|-------------------------------------|

|-------------------------------------|

| Revision | Date       | Substantive Changes                                                                                                         |  |

|----------|------------|-----------------------------------------------------------------------------------------------------------------------------|--|

| 1.1      | 04/19/2005 | Document template update                                                                                                    |  |

|          |            | Document ID change from MPC7410RXPDPNS for Part Number Specification to MPC7410ECS04AD for Hardware Specification Addendum. |  |

| 1        |            | Minor formatting                                                                                                            |  |

|          |            | Section 1.10.1 - added Table 17 - Part-Marking Nomenclature                                                                 |  |

| 0        |            | Initial Release                                                                                                             |  |

## **10 Ordering Information**

### **10.1 Part Numbers Addressed by this Specification**

Table 17 provides the ordering information for the MPC7410 part described in this document.

| Table 17. | Part-Marking | Nomenclature |

|-----------|--------------|--------------|

|           |              |              |

| MPC              | 7410               | RX        | XXX                                 | X                              | X                       |

|------------------|--------------------|-----------|-------------------------------------|--------------------------------|-------------------------|

| Product<br>Code  | Part<br>Identifier | Package   | Processor<br>Frequency <sup>1</sup> | Application Modifier           | Revision Level          |

| XPC <sup>2</sup> | 7410               | RX = CBGA | 450<br>500<br>533                   | P: 2.0 V ± 50 mV<br>0 to 65 °C | D: 1.3; PVR = 800C 1103 |

### Notes:

1. Processor core frequencies supported by parts addressed by this specification only. Parts addressed by other specifications may support other maximum core frequencies.

2. The X prefix in a Freescale part number designates a "Pilot Production Prototype" as defined by Freescale SOP 3-13. These are from a limited production volume of prototypes manufactured, tested and Q.A. inspected on a qualified technology to simulate normal production. These parts have only preliminary reliability and characterization data. Before pilot production prototypes may be shipped, written authorization from the customer must be on file in the applicable sales office acknowledging the qualification status and the fact that product changes may still occur while shipping pilot production prototypes.

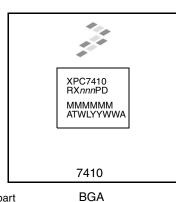

## 10.3 Part Marking

Parts are marked as the example shown in

Figure 26.

### Notes:

nnn is the speed grade of the part

MMMMMM is the 6-digit mask number

ATWLYYWWA is the traceability code

CCCCC is the country of assembly (this space is left blank if parts are assembled in the United States)

Figure 26. Freescale Part Marking for BGA Device

**Ordering Information**

### THIS PAGE INTENTIONALLY LEFT BLANK

**Ordering Information**

### THIS PAGE INTENTIONALLY LEFT BLANK

#### How to Reach Us:

Home Page: www.freescale.com

email: support@freescale.com

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 (800) 521-6274 480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064, Japan 0120 191014 +81 2666 8080 support.japan@freescale.com

### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate, Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 (800) 441-2447 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor @hibbertgroup.com

Document Number: MPC7410ECS04AD Rev. 1.1 04/2005 Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc., 2002, 2005.