# NAFE33350

## Software Configurable Universal Low-Power AO-AFE

Rev. 1.0 — 14 January 2026

Product data sheet

### Document information

| Information | Content                                                                                                                                                                                                                                                                                |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | NAFE33350, industrial, software-configurable, low-power, Universal Analog Output (UAO), Analog Front End (AFE), 18-bit DAC                                                                                                                                                             |

| Abstract    | The NAFE33350 is a software-configurable universal output AFE that meets high-precision control requirements of industrial applications, such as programmable logic controllers (PLC), distributed control systems (DCS), industrial HMI, factory automation, and building automation. |

## 1 General description

The NAFE33350 is a software-configurable universal analog output (AO) analog front-end (AFE) that meets high-precision control requirements of industrial-grade applications. The AO-AFE integrates the following components.

- A precision 18-bit digital-to-analog converter (DAC)

- A low-drift voltage reference

- Low-offset drift buffers

- A 70 V input-protection circuit for EMC and miswiring scenarios

For open circuit and short-circuit detection, the output stage includes built-in diagnostic and protection circuitry.

The AO AFE is suitable for programmable logic controllers (PLC), analog output modules, isolated industrial control systems, and process control.

## 2 Features and benefits

- High-precision pin-to-pin and firmware compatible AO-AFE family

- Software configurable voltage and current analog output with multiple ranges

- Integrated voltage references

- Factory calibrated voltage and current output

- Precise and fast response AO-AFE architecture provides

- 18-bit DAC

- DAC 0 ksps to 100 ksps data rate

- $\pm 12.5$  V,  $\pm 25$  mA

- $\pm 0.01$  % accuracy at room

- $\pm 0.08$  % accuracy over temperature (Voltage mode after room calibration)

- INL and 2 LSB max @ 18-bit

- Robust and flexible

- $\pm 36$  V protected I/O (external transient voltage suppressor (TVS), required)

- $\pm 7$  V to  $\pm 28$  V wide supply range, HVDD-HVSS = 14 V to 48 V

- -40 °C to 125 °C temperature range

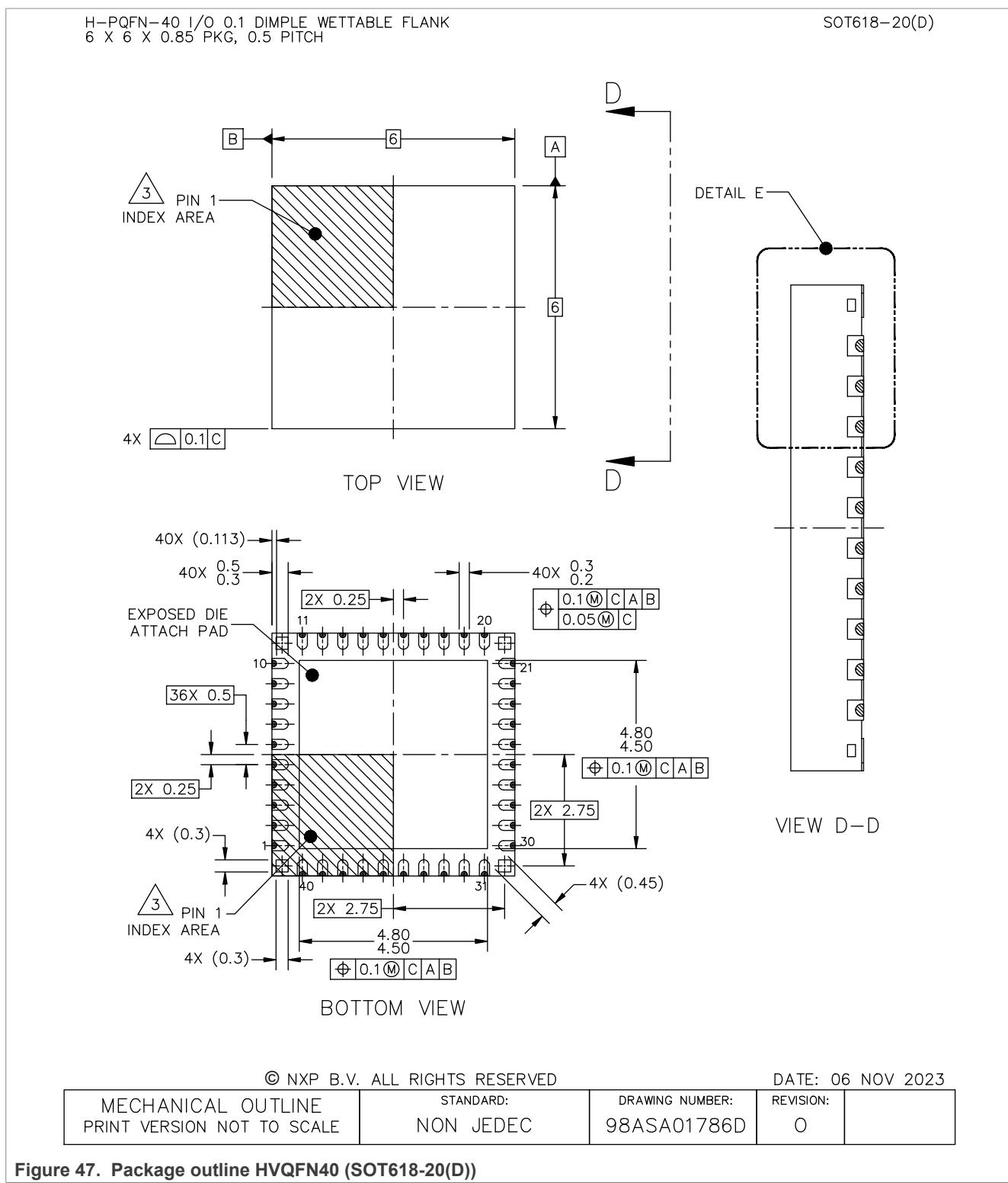

- 6 mm x 6 mm small HVQFN-40 package

### 2.1 IEC EMC ratings

- IEC61004-2 ESD

- IEC61004-4 Electrical Fast Transient/Burst Test (EFT)

- IEC61004-5 2 kV Surge Immunity Test

### 2.2 ESD stress rating and latch-up

[Section 2.2](#) describes the ESD stress rating and latch-up for NAFE33350.

**Table 1. ESD stress rating and latch-up**

| Description                            | Max        | Units |

|----------------------------------------|------------|-------|

| Human body model (HBM) on all pins     | $\pm 4500$ | V     |

| Charged device model (CDM) on all pins | $\pm 750$  | V     |

| Latch-up at 150 °C                     | $\pm 200$  | mA    |

**Note:** [Section 2.2](#) describes only the stress ratings. Functional operation of the product at conditions at or above its ratings is not implied.

### 3 Applications

- Precise voltage and current source systems

- PLC, DCS I/O modules

- Industrial automation and process control

## 4 Ordering information

The NAFE33350 is part of a software-compatible family of products that can be used to design a flexible and scalable analog output module.

**Table 2. Part family**

| NAFE33350 DS <sup>[1]</sup> |                                          |   |                                                                         |                                                |                     |

|-----------------------------|------------------------------------------|---|-------------------------------------------------------------------------|------------------------------------------------|---------------------|

| NAFE                        | 3                                        | 3 | 3                                                                       | 5                                              | 0                   |

| NXP analog front-end        | Power<br>3 = Low power<br>9 = High speed | 3 | Reference<br>3 = Factory<br>calibrated<br>1 = Non-factory<br>calibrated | Resolution (DAC)<br>5 = 18<br>4 = 16<br>3 = 14 | Channels<br>0: 1 AO |

[1] Contact your NXP sales representative for further information and available part numbers, part variants with different resolution, number of I/Os, and calibration.

**Table 3. Ordering information**

| Type number     | Topside mark | Package |                                                                                                     |  | Version      |

|-----------------|--------------|---------|-----------------------------------------------------------------------------------------------------|--|--------------|

|                 |              | Name    | Description                                                                                         |  |              |

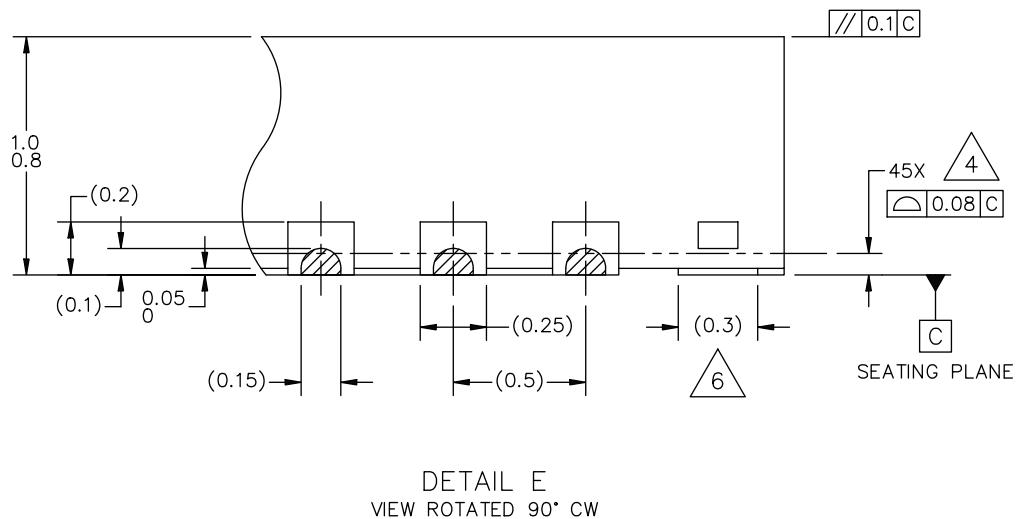

| NAFE33350 B40BS | FE33350      | HVQFN40 | Plastic thermal enhanced thin quad flat package; no leads; 40 terminals; body 6 mm x 6 mm x 0.85 mm |  | SOT618-20(D) |

**Table 4. Ordering options**

| Type number     | Orderable part number | Package | Packing method | Minimum order quantity | Temperature                            |

|-----------------|-----------------------|---------|----------------|------------------------|----------------------------------------|

| NAFE33350 B40BS | NAFE33350 B40BSMP     | HVQFN40 | Reel 13" Q2 DP | 4000                   | T <sub>amb</sub> = -40 °C<br>to 125 °C |

|                 | NAFE33350B40BSZ       |         | Reel 7" Q1 DP  | 1000                   |                                        |

## 5 Block diagram

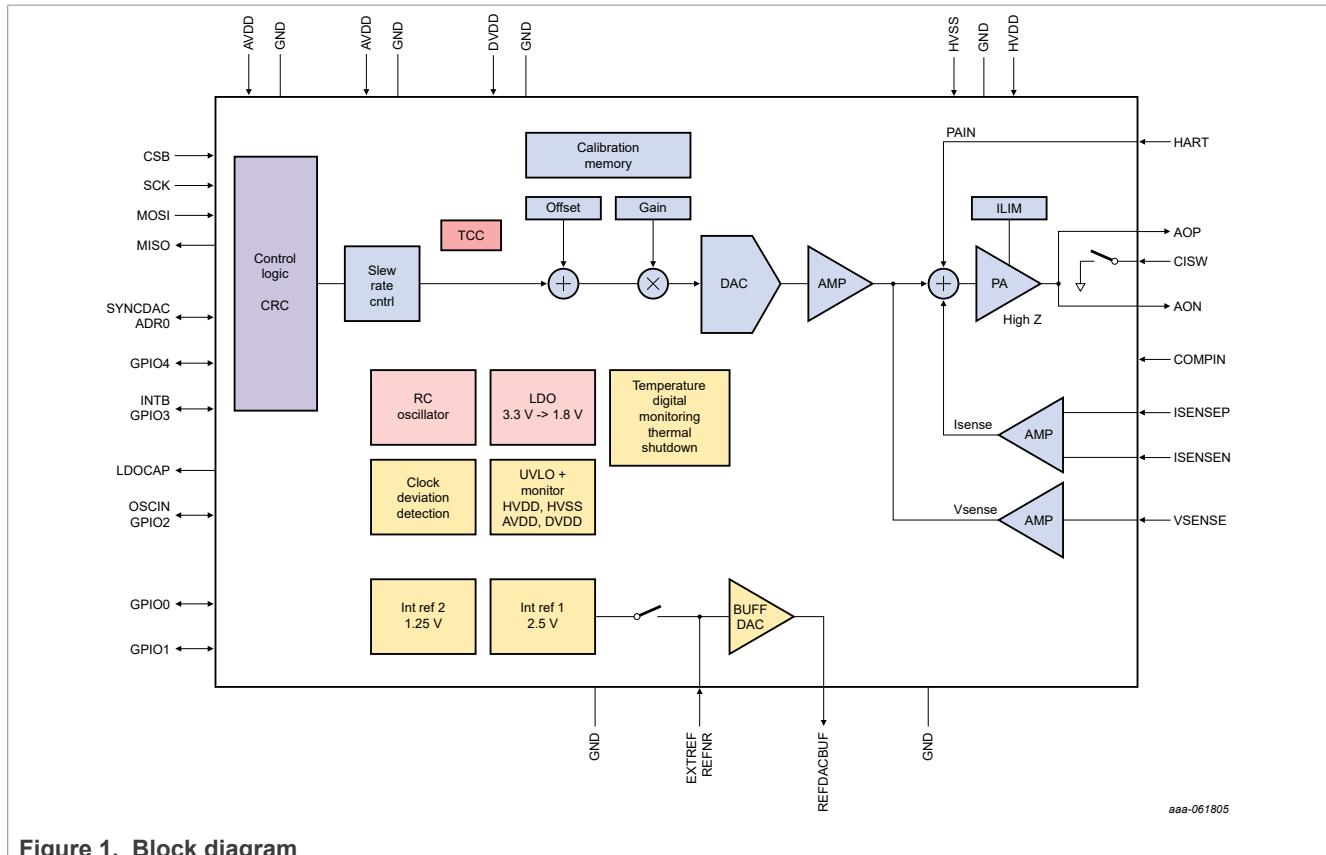

Figure 1 shows the labeled block diagram of NAFE33350.

Figure 1. Block diagram

## 6 Pinning information

This chapter explains the configuration and assignment of pins on NAFE33350.

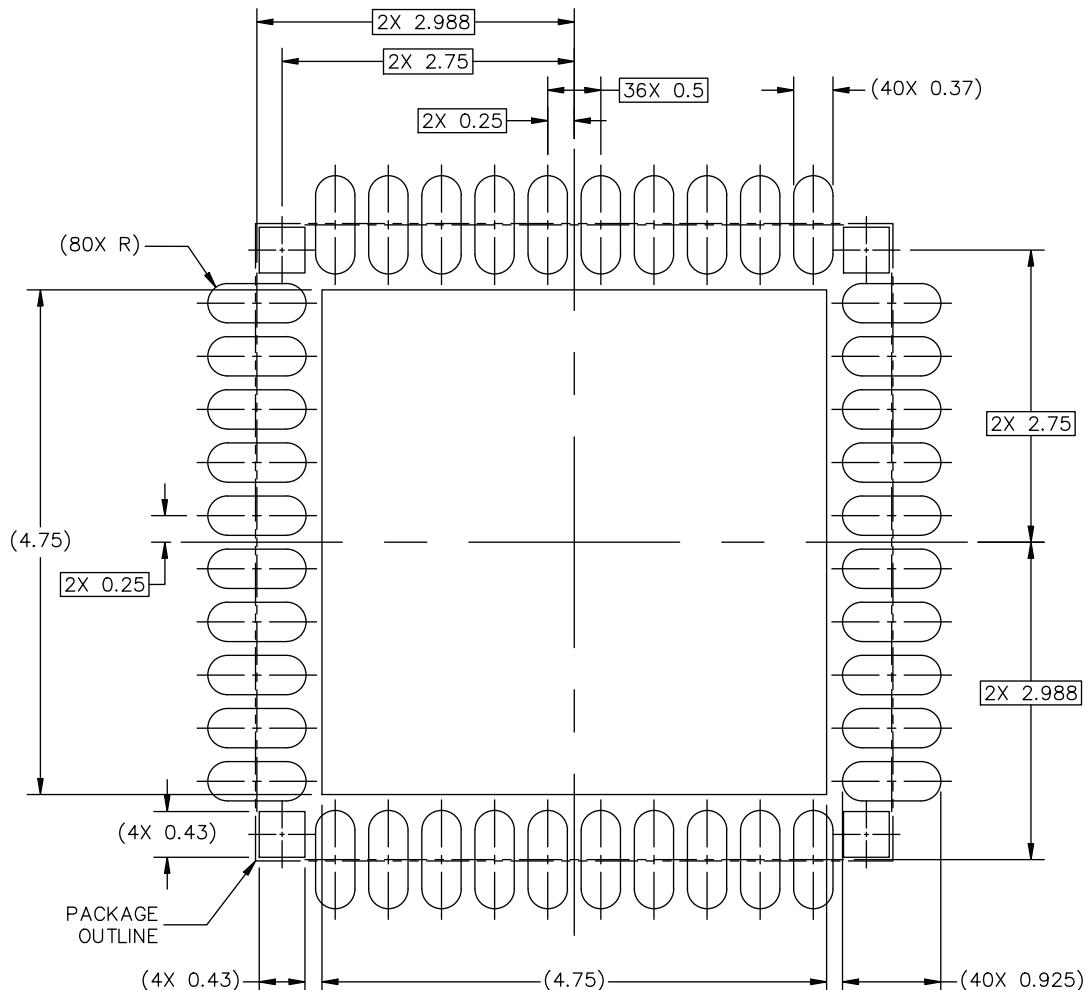

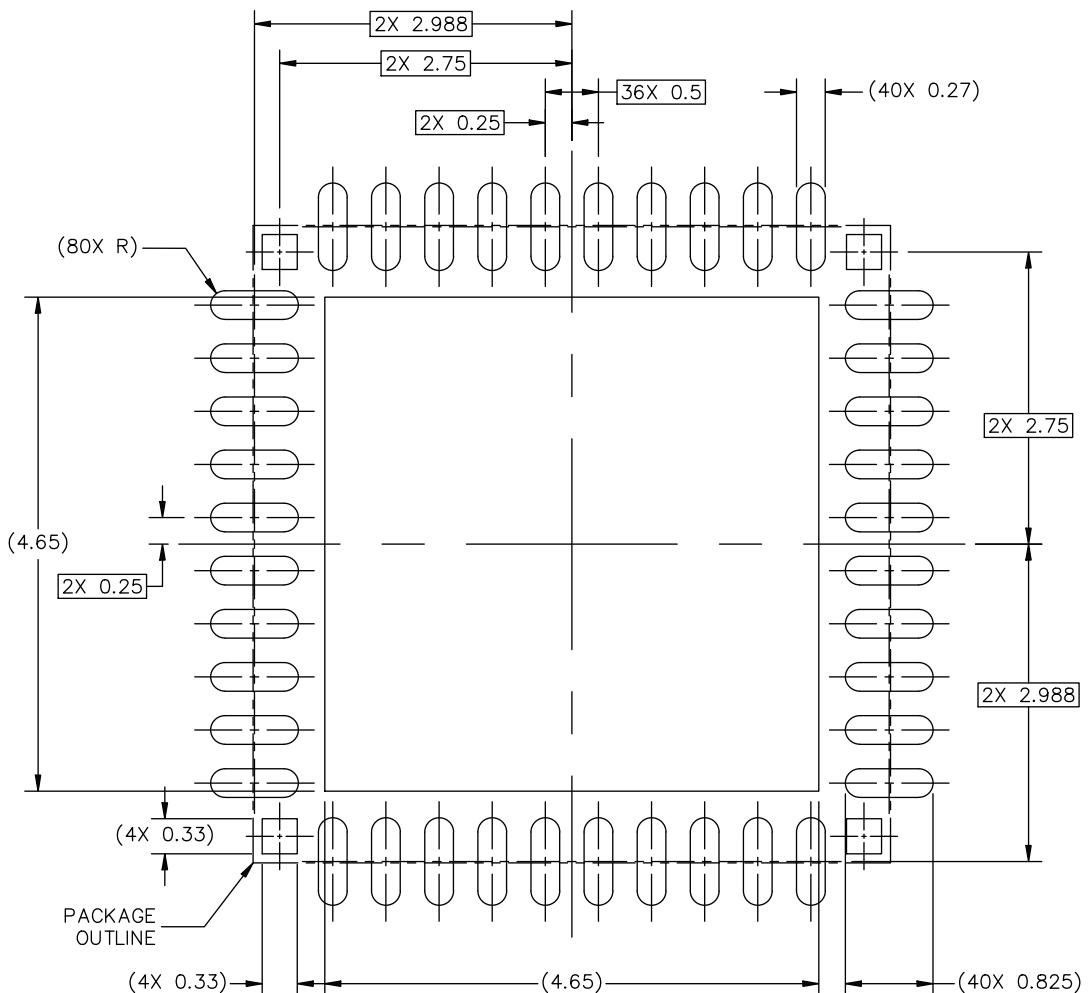

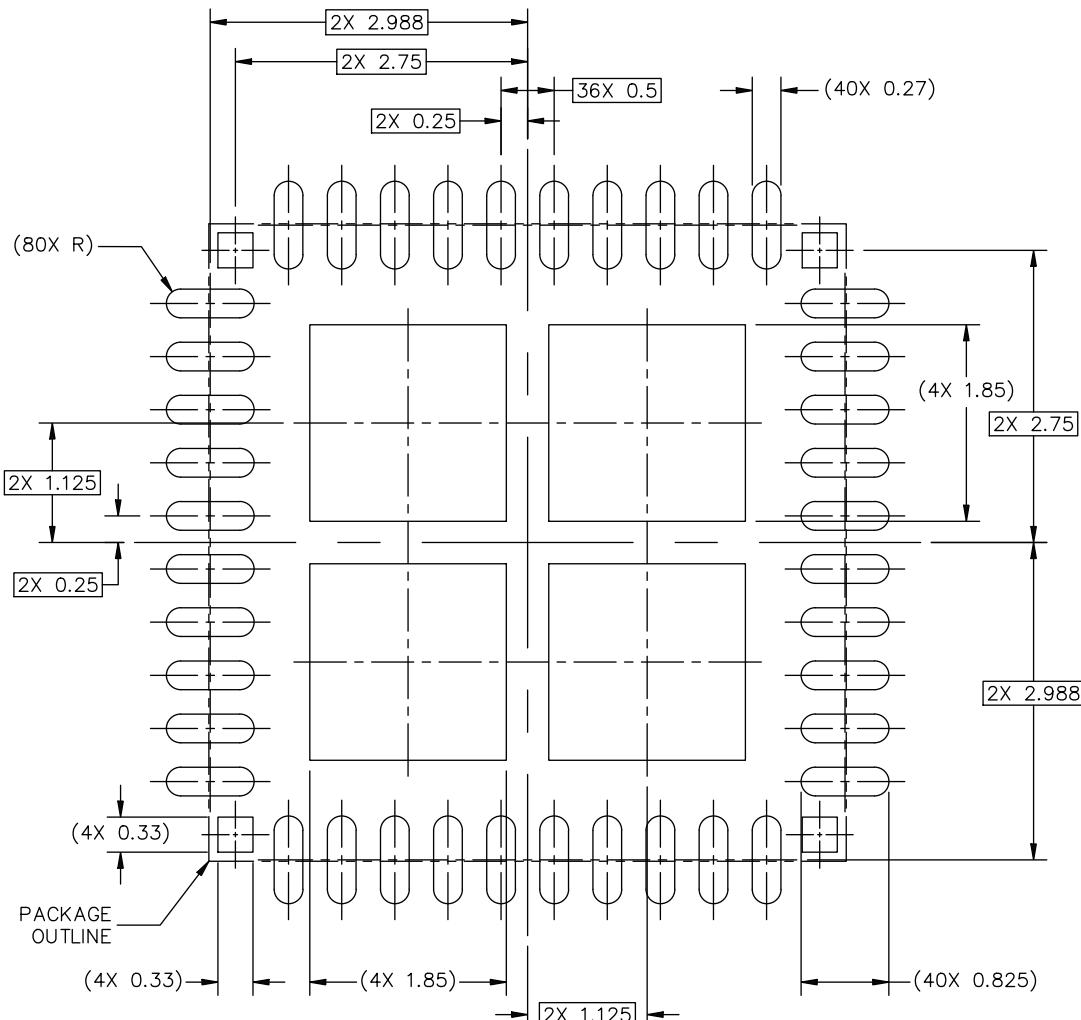

### 6.1 Pinning

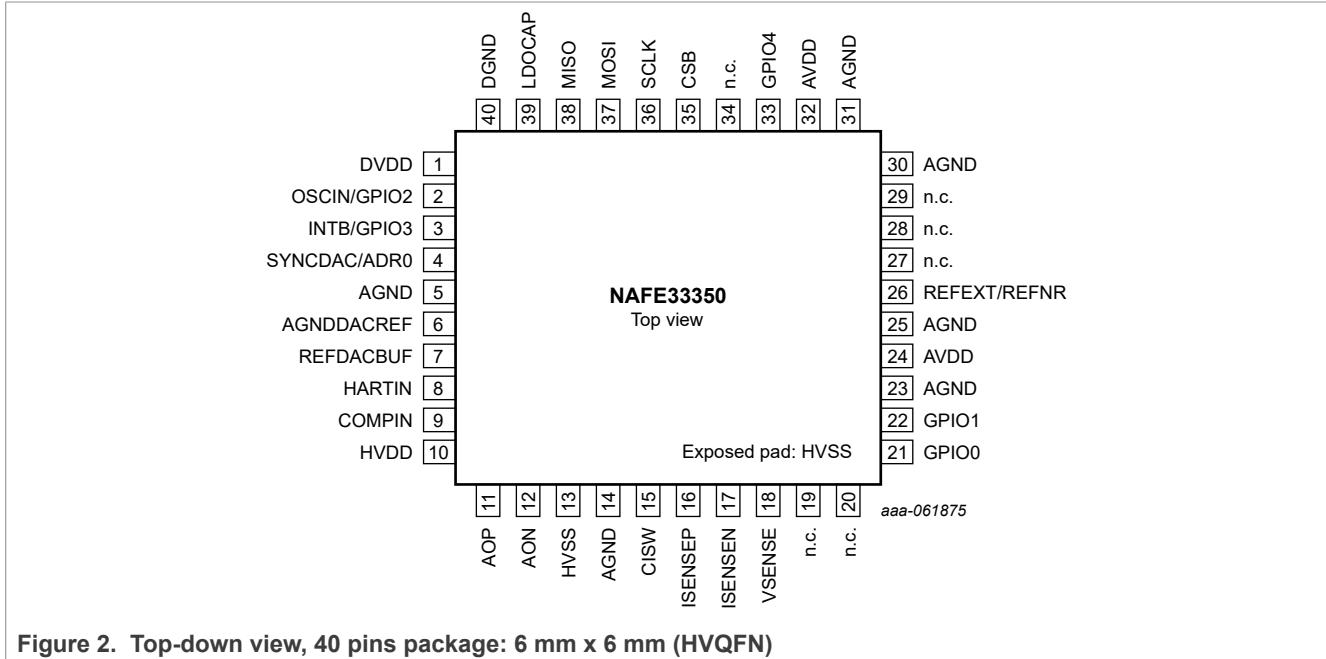

[Figure 2](#) shows the pinning for NAFE33350.

Figure 2. Top-down view, 40 pins package: 6 mm x 6 mm (HVQFN)

### 6.2 Pin description

[Table 5](#) provides detailed description of various pins on NAFE33350.

Table 5. Pin number and pin description

| Number | Name          | I/O | Functional description                                                                                                                                                                                                                                                                                 |

|--------|---------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | DVDD          |     | 3.3 V digital power supply.                                                                                                                                                                                                                                                                            |

| 2      | OSCIN/GPIO2   | DI  | External clock input and GPIO2 multifunction pin. The default is an external clock input pin. If the external clock function is not used, it can be left floating. When it is configured as GPIO functionality, it functions as a GPIO. Also refer to auto clock source selection for further details. |

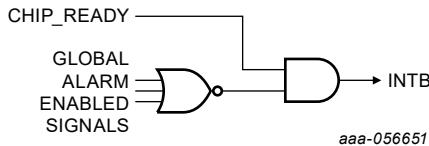

| 3      | INTB/GPIO3    | DO  | Interrupt flag output (active-low) and GPIO3 multifunction pin. The default is INTB and it can be configured as GPIO3.                                                                                                                                                                                 |

| 4      | SYNC DAC/ADR0 | DI  | DAC synchronized input and ADR0 multifunction pin. The default is SYNC DAC and it can be configured as ADR0. It can be grounded if SYNC DAC is not used.                                                                                                                                               |

| 5      | AGND          |     | Analog ground.                                                                                                                                                                                                                                                                                         |

| 6      | AGNDDACREF    | AI  | DAC voltage reference GND sense.                                                                                                                                                                                                                                                                       |

| 7      | REF DACBUF    | AO  | DAC voltage reference output bypass. Connect a 0.1 $\mu$ F bypass capacitor close to the pin.                                                                                                                                                                                                          |

| 8      | HARTIN        | AI  | HART signal input. A coupling capacitor is required.                                                                                                                                                                                                                                                   |

| 9      | COMPIN        | AO  | External compensation for the output driver amplifier. External passive compensation network can be connected between AO and COMP_IN pins.                                                                                                                                                             |

Table 5. Pin number and pin description...continued

| Number | Name          | I/O    | Functional description                                                                                                                                                                                                        |

|--------|---------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10     | HVDD          |        | High-voltage positive supply.                                                                                                                                                                                                 |

| 11     | AOP           | AO     | High-side analog output. This pin is connected to the anode of an off-chip Schottky diode. The cathode of the Schottky diode is connected to the AO onboard terminal through an off-chip current sensing resistor (50 Ω TYP). |

| 12     | AON           | AO     | Low-side analog output. This pin is connected to the cathode of an off-chip Schottky diode. The anode of the Schottky diode is connected to the AO onboard terminal through an off-chip current sensing resistor (50 Ω TYP).  |

| 13     | HVSS          |        | High-voltage negative supply.                                                                                                                                                                                                 |

| 14     | AGND          |        | Analog ground.                                                                                                                                                                                                                |

| 15     | CISW          | AI     | Current input switch pin (CISW). This pin is connected to the AO onboard terminal through the current sensing resistor connected to the AOP and AON pins.                                                                     |

| 16     | ISENSEP       | AI     | Positive input for an external current sense resistor. Must have an RC filter (5 kΩ and 100 pF).                                                                                                                              |

| 17     | ISENSEN       | AI     | Negative input for an external current sense resistor. Must have an RC filter (5 kΩ and 100 pF).                                                                                                                              |

| 18     | VSENSE        | AI     | Voltage sense input must have an RC filter (5 kΩ and 100 pF).                                                                                                                                                                 |

| 19     | RES           |        | Reserved. Connect to AGND.                                                                                                                                                                                                    |

| 20     | RES           |        | Reserved. Connect to AGND.                                                                                                                                                                                                    |

| 21     | GPIO0         | DI, DO | General-purpose digital I/O. Connect to AGND if not used.                                                                                                                                                                     |

| 22     | GPIO1         | DI, DO | General-purpose digital I/O. Connect to AGND if not used.                                                                                                                                                                     |

| 23     | AGND          |        | Analog ground.                                                                                                                                                                                                                |

| 24     | AVDD          |        | 3.3 V analog power supply.                                                                                                                                                                                                    |

| 25     | AGND          |        | Analog ground.                                                                                                                                                                                                                |

| 26     | REFEXT/REFNR  | AI     | External reference voltage input/internal reference output bypass.                                                                                                                                                            |

| 27     | Not Connected |        |                                                                                                                                                                                                                               |

| 28     | Not Connected |        |                                                                                                                                                                                                                               |

| 29     | Not Connected |        |                                                                                                                                                                                                                               |

| 30     | AGNDREF       | AI     | Voltage reference GND sense.                                                                                                                                                                                                  |

| 31     | AGND          |        | Analog ground.                                                                                                                                                                                                                |

| 32     | AVDD          |        | 3.3 V analog power supply.                                                                                                                                                                                                    |

| 33     | GPIO4         | DI, DO | General-purpose digital I/O. Connect to AGND if not used.                                                                                                                                                                     |

| 34     | RES           | DO     | Reserved. Leave floating.                                                                                                                                                                                                     |

| 35     | CSB           | DI     | Chip select input, active-low.                                                                                                                                                                                                |

| 36     | SCLK          | DI     | SPI clock input.                                                                                                                                                                                                              |

| 37     | COTI          | DI     | SPI data input.                                                                                                                                                                                                               |

| 38     | CITO          | DO     | SPI data output.                                                                                                                                                                                                              |

| 39     | LDOCAP        |        | 1.8 V regulator output bypass.                                                                                                                                                                                                |

| 40     | DGND          |        | Digital ground.                                                                                                                                                                                                               |

|        | EP            |        | Exposed pad (HVSS).                                                                                                                                                                                                           |

## 7 Functional description

The NAFE33350 is a universal AO software-configurable AFE for high-precision and high-accuracy measurements. Both the voltage output and the current output have the full range (or the overload range) of 1.25 times the linear range.

The maximum voltage overload is  $\pm 12.5$  V and the correspondent max linear range is  $\pm 10$  V.

The maximum current overload is  $\pm 25$  mA and the correspondent max linear range is  $\pm 20$  mA.

Linear voltage ranges:

- $\pm 10$  V;  $\pm 5$  V.

- Load resistance  $> 1$  k $\Omega$ .

In addition, the NAFE33350 fits the most common output current ranges and load resistance.

- $\pm 20$  mA; 0 mA to  $+20$  mA; 4 mA-20 mA

- Load resistance from 0  $\Omega$ ; 1 k $\Omega$

The NAFE33350 includes a feedback path for the voltage and current output ( $V_{sense}$ ,  $I_{sense}$ ).

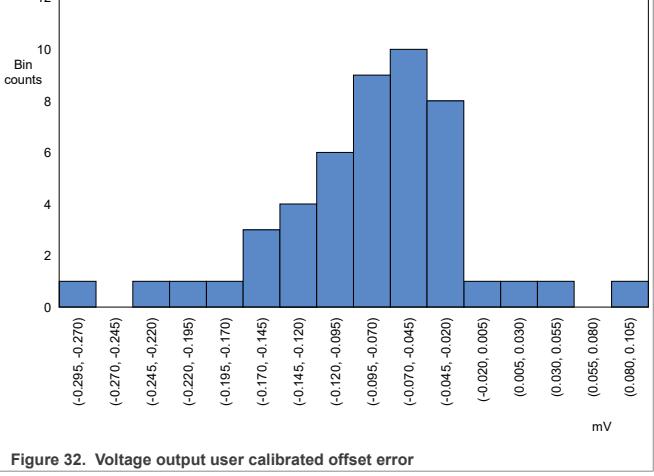

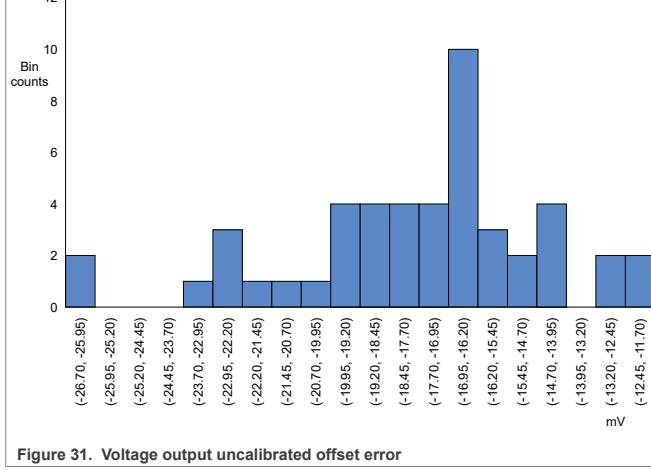

### 7.1 Digital factory calibration

To save time and the cost of calibration, select the parts that are already digitally calibrated and do not require further and long calibration procedures. The NAFE33350 integrates a non-volatile memory (NVM). NVM allows digital calibration of the AFE in the factory and stores the coefficient values for offset and gain in the NVM memory.

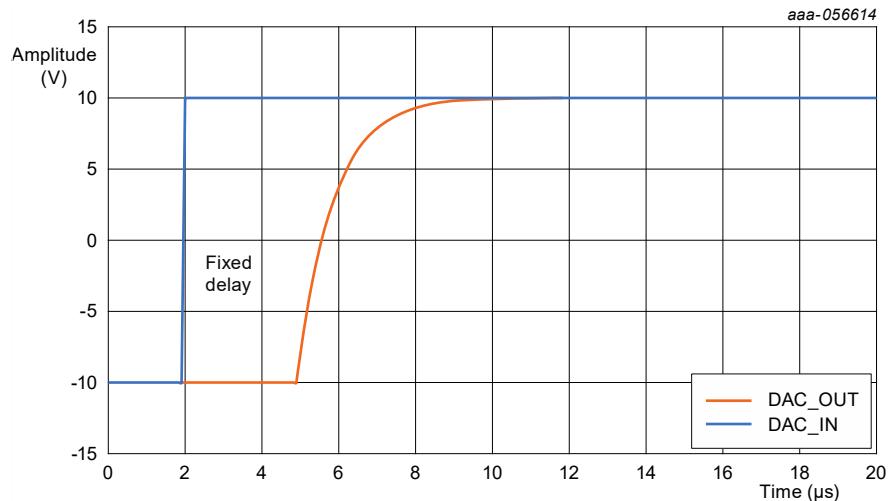

### 7.2 Precise and fast analog output

The NAFE33350 integrates a high-precision DAC, low-drift voltage reference, and a precise high-voltage amplifier to generate small and wide output signals. In addition, the DAC and the amplifier have been designed to provide fast-output response with 10  $\mu$ s settling time.

The total error of an end-to-end acquisition system is:

- $\pm 0.01$  % of full-scale range at 25 °C with factory calibration

- $\pm 10$  ppm of full scale/°C temperature coefficient (Voltage mode)

- $\pm 0.05$  % of full-scale range over I/O module temperature range from 0 °C to 60 °C

The NAFE33350 provides a wide range of programmable data rate. The fast data rate fits systems with fast response time requirements.

The host processor update rate determines the DAC output data rate.

The update rate is 0 ksps to 100 ksps.

To provide a fast response, the precise high-voltage (HV) amplifiers are designed with a wide GBW product and a fast slew rate for short settling time. The DAC is designed with a fast update rate and low propagation delay.

[Figure 3](#) shows the main delay sources of the output settling time.

Figure 3. Main delay sources of output settling time

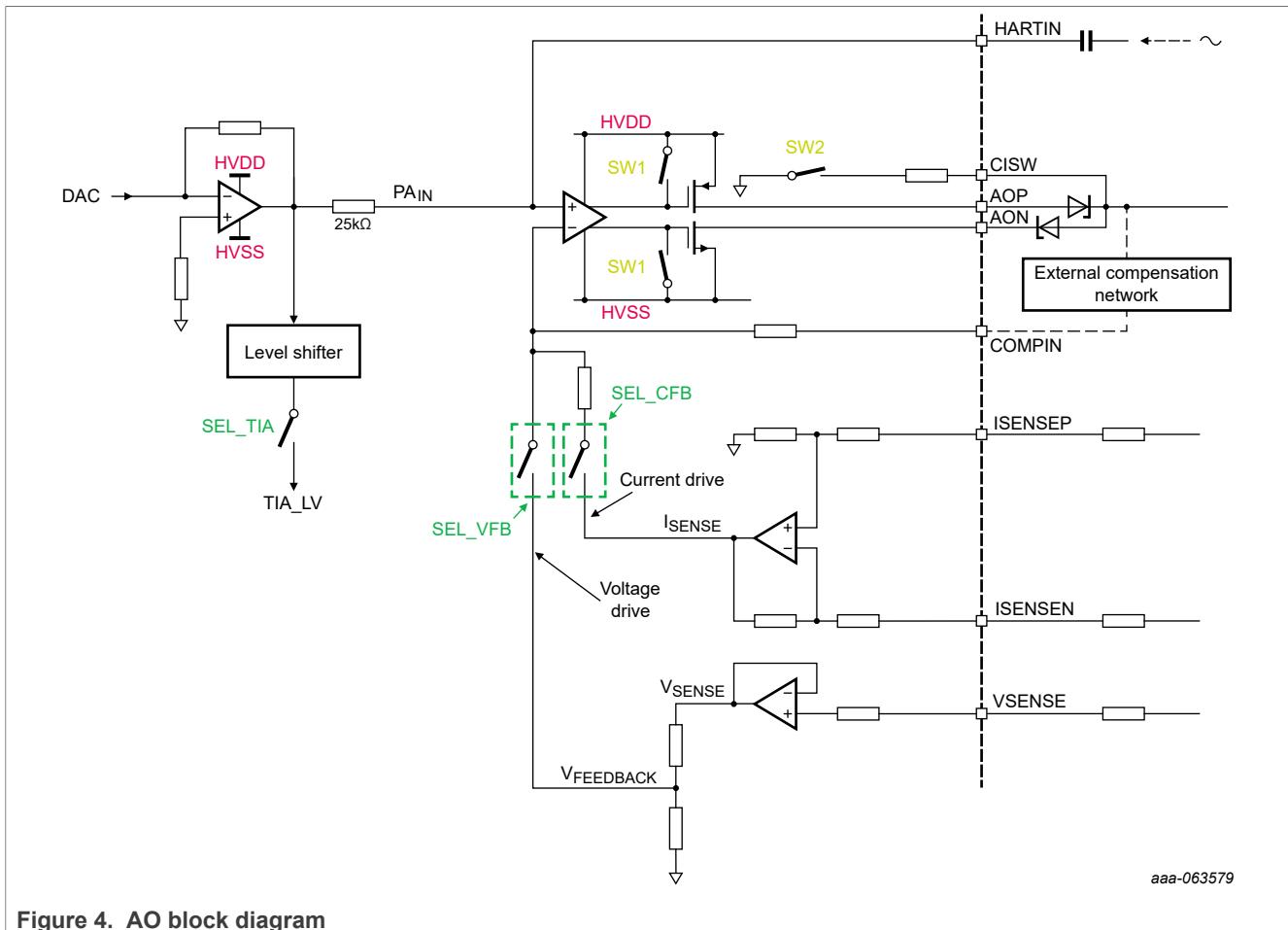

### 7.3 AO signal path

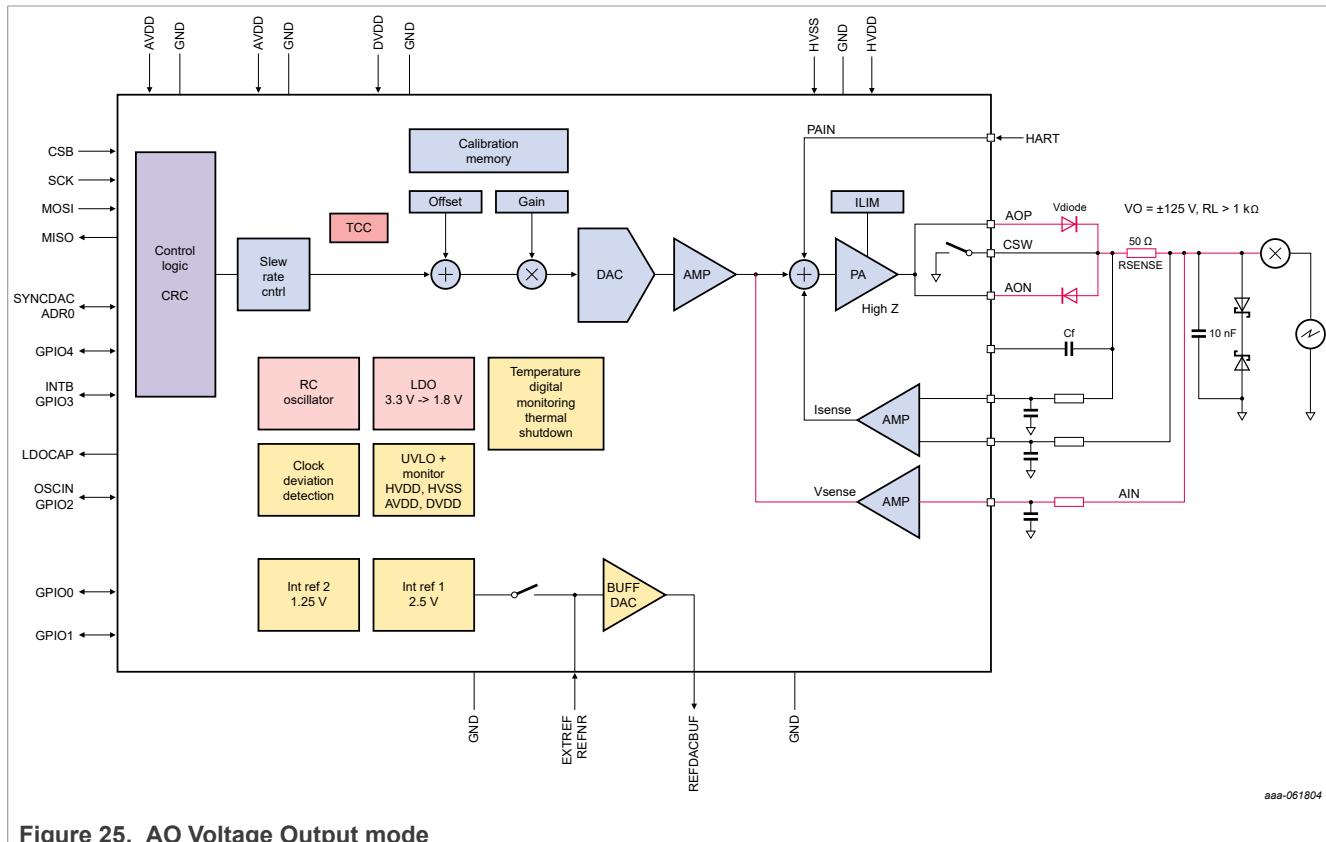

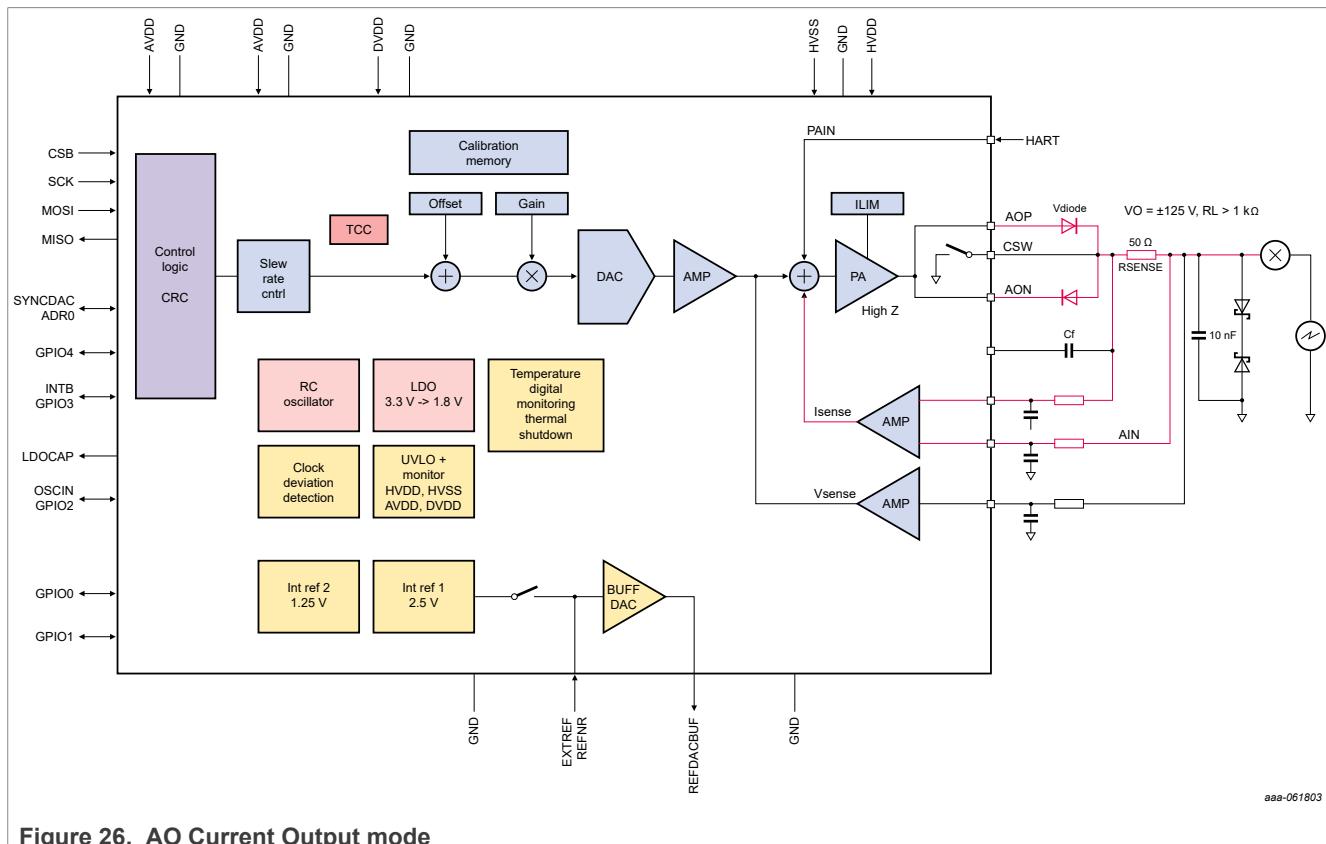

The analog output can be configured as Voltage-output mode and Current-output mode.

As shown in [Figure 4](#), an on-chip precise DAC is used as output signal source followed by a gain stage and Power Amplifier, which can be configured for voltage output, current output, or high-impedance (Hi-Z state).

#### 7.3.1 Power amplifier output

As shown in [Figure 4](#), there are several switches in the output stage, which allow different modes of operation. For example, AO pin - high-Z, voltage output (VO), and current output (CO).

Figure 4. AO block diagram

Two switches are connected at the analog-output pin. The High-Z switch SW1 connects or disconnects the PA out to analog output pin while the ShortGND switch SW2 connect the output pin to GND.

To configure the device in Output mode, SW1 must be closed and SW2 open. The appropriate power amplifier (PA) feedback path (VFB or CFB) must be enabled using SEL\_VFB or SEL\_CFB respectively. PA input feedback path can be floated for high-Z mode at the AO.

### Analog Output Mode (AO\_MODE)

Pre-configured AO modes.

1. 00\b: high-Z mode, PA\_ON = 0, VSA\_ON = x, CSA\_ON = x

2. 10\b: Voltage-output mode, PA\_ON = 1, VSA\_ON = 1, CSA\_ON = x

3. 11\b: Current-output mode, PA\_ON = 1, VSA\_ON = x, CSA\_ON = 1

4. VSA ON = 1 turn ON VSA.

5. Exception: AO\_MODE = 10\b

6. Voltage-output mode force VSA ON = 1, this bit cannot be overwritten.

7. CSA ON = 1 turn ON CSA.

8. Exception: AO\_mode = 11\b

9. Current-output mode force CSA ON = 1, this bit cannot be overwritten.

10. CISW\_ON = 1 turn on the current input switch connected to the ground.

11. CISW is used with external Rsense for Current-input mode configuration.

**Note:** To avoid short-circuit, CSIW\_ON must be 0\h when the PA\_ON = 1 if the CISW pin is connected to the AOP/AON path.

### 7.3.2 Output modes

NAFE33350 supports both Voltage Output and Current Output modes with programmable FS ranges of 12.5 V and  $\pm 25$  mA, respectively.

#### 7.3.2.1 Voltage output

NAFE33350 voltage output can drive the maximum Rload of  $10\text{ M}\Omega$  and maximum Cload of  $2\text{ }\mu\text{F}$ . The output settling time depends on the combined RC loading at the AO pin.

The voltage output settles to 0.1 % accuracy for 10 V output swing with no Rload as below:

- 50  $\mu\text{s}$  with Rload = open and Cload =  $20\text{ nF}$

- 0.5 ms with Rload = open and Cload =  $2\text{ }\mu\text{F}$

The NAFE33350 settles to 0.1 % of 10 V swing within 10  $\mu\text{s}$  for Cload in the range of  $1\text{ nF} - 10\text{ nF}$ . If Cload >  $20\text{ nF}$ , the system hits the current limit and overcurrent drives the device into high-Z protection mode. To avoid it, use the slew rate control to ramp up the DAC softly. Alternatively, use the current limiter to clamp the current to a specified level within the current limiter duration. The current limiter response time depends on the load capacitance. An external component can also be used to dampen the overvoltage and overcurrent condition at the device input pins. For overcurrent protection details, see [Section 7.3.6](#).

#### 7.3.2.2 Current output

NAFE33350 current output can drive the maximum Rload of  $10\text{ k}\Omega$  and maximum Lload of  $1\text{ mH}$ .

The current output settles to 0.1 % accuracy for a 25 mA output swing with no Rload as below:

- 50  $\mu\text{s}$  with Rload = open and Lload =  $47\text{ }\mu\text{H}$

- 0.5 ms with Rload = open and Lload =  $1\text{ mH}$

The user can achieve fast settling and limit the maximum current during the step response by keeping load inductance below  $10\text{ }\mu\text{H}$ . If Lload >  $10\text{ }\mu\text{H}$ , avoid overcurrent triggered High-Z protection mode by using the slew rate control to ramp up the DAC softly. Alternatively, place an RC filter at the HART input pin. For details, see [Overcurrent protection in Current input mode](#). If required, an external component (such as a TVS diode) can be used to mitigate the current surge at the AO pin.

### 7.3.3 DAC output slew rate control

The slew rate control feature of the NAFE33350 controls the rate at which the output value changes. This feature is available on both the current and voltage outputs. You can program the slew rate control parameters in register AO\_SLR\_CTRL defined in [Table 12](#). With the slew rate control feature disabled, the output value changes at a rate limited by the output drive circuitry and the attached load. To reduce the slew rate, enable the slew rate control feature. With the feature enabled via the SLREN bit of the slew rate control register (see [Table 7](#)), the output steps digitally instead of slewing directly between two values. The slew rate control register digitally defines the rate of these steps through two accessible parameters, as shown in [Table 6](#) and [Table 7](#).

You can program the slew rate control parameters in register AO\_SLR\_CTRL defined in [Table 12](#). The parameters are SLR\_CLOCK and SR\_STEP. SR\_CLOCK defines the rate at which the digital slew is updated. For example, if the selected update rate is 8 kHz, the output updates every 125  $\mu\text{s}$ . The SLR\_STEP defines by how much the output value changes at each update. Together, both parameters define the rate of change of the output value. [Table 6](#) and [Table 7](#) outline the range of values for both the SLR\_CLOCK and SLR\_STEP parameters.

**Table 6. Slew rate update clock selection**

| SLR_CLOCK [2:0] | Update clock frequency in Hz |

|-----------------|------------------------------|

| 0 0 0           | 4000                         |

| 0 0 1           | 6000                         |

| 0 1 0           | 9000                         |

| 0 1 1           | 12000                        |

| 1 0 0           | 40000                        |

| 1 0 1           | 60000                        |

| 1 1 0           | 90000                        |

| 1 1 1           | 150000                       |

**Table 7. Slew rate steps**

| DAC's resolution  | SLR_STEP |      |      |      |       |       |       |        |

|-------------------|----------|------|------|------|-------|-------|-------|--------|

|                   | 0        | 1    | 2    | 3    | 4     | 5     | 6     | 7      |

| Step_size: 18-bit | 1024     | 2048 | 4096 | 8192 | 16384 | 32768 | 65536 | 131072 |

| Step_size: 16-bit | 256      | 512  | 1024 | 2048 | 4096  | 8192  | 16384 | 32768  |

| Step_size: 14-bit | 64       | 128  | 256  | 512  | 1024  | 2048  | 4096  | 8192   |

| Step_size: 12-bit | 16       | 32   | 64   | 128  | 256   | 512   | 1024  | 2048   |

When the slew rate control feature is enabled, SLREN = 1, all output changes occur at the programmed slew rate. For example, when you assert the RESET command, the output slews to the clear value at the programmed slew rate. It is assumed that the clear channel is enabled for clearing. The update clock frequency for any given value is the same for all output ranges. However, the step size varies across output ranges for a given value of step size because the LSB size is different for each output range.

The following equation describes the slew rate as a function of the step size, the update clock frequency, and the LSB size:

$$\text{Slew time} = \text{Output change} / (\text{Step size} * \text{Update clock freq.} * \text{LSB size})$$

Where: Slew time is expressed in seconds.

Output change is expressed in amps for IOUT or volts for VOUT.

### 7.3.3.1 DAC conversion during digital slew active

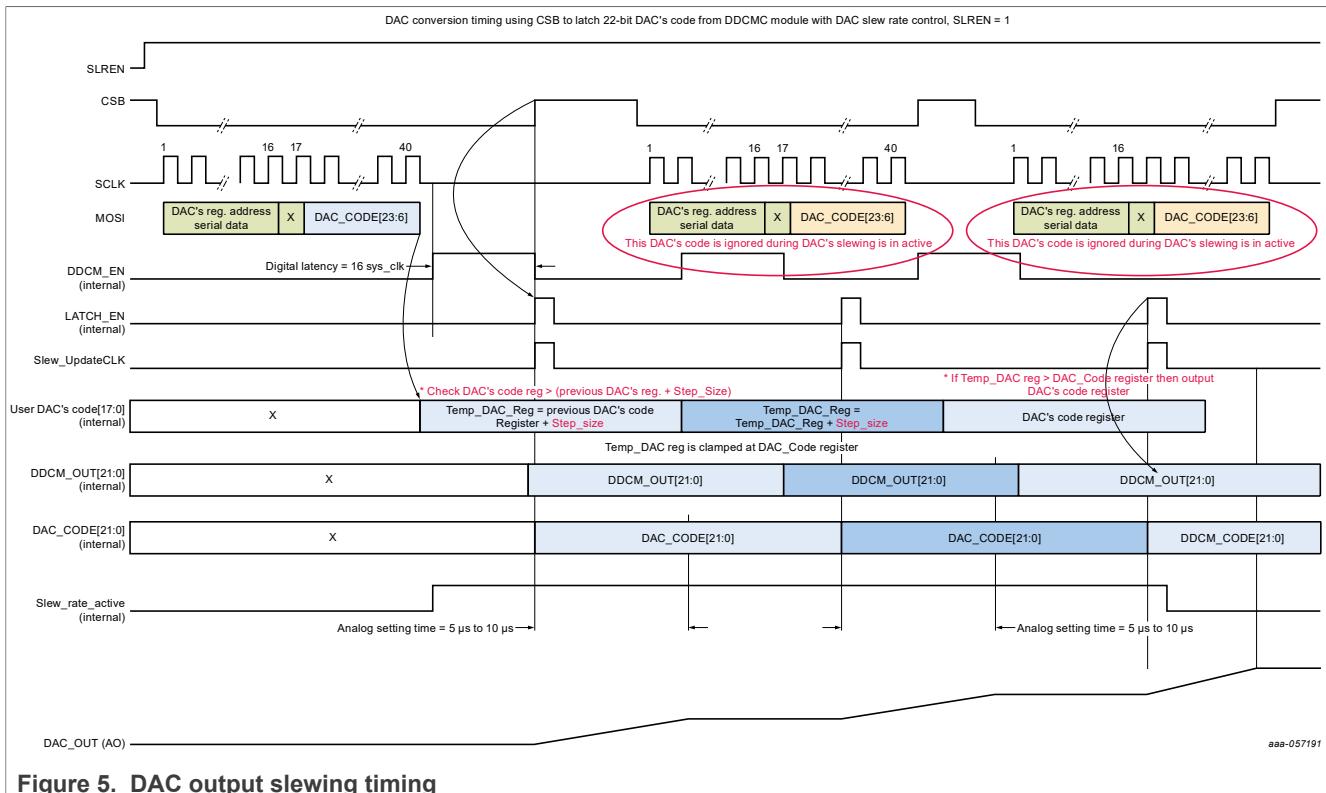

When the DAC slew is active, new DAC codes sent from the SPI host is ignored. The host must wait for the completion of the current DAC conversion. [Figure 5](#) shows that the DAC code sent from the SPI host during the DAC output slewing active.

Figure 5. DAC output slewing timing

### 7.3.4 Auto-DAC waveform generator

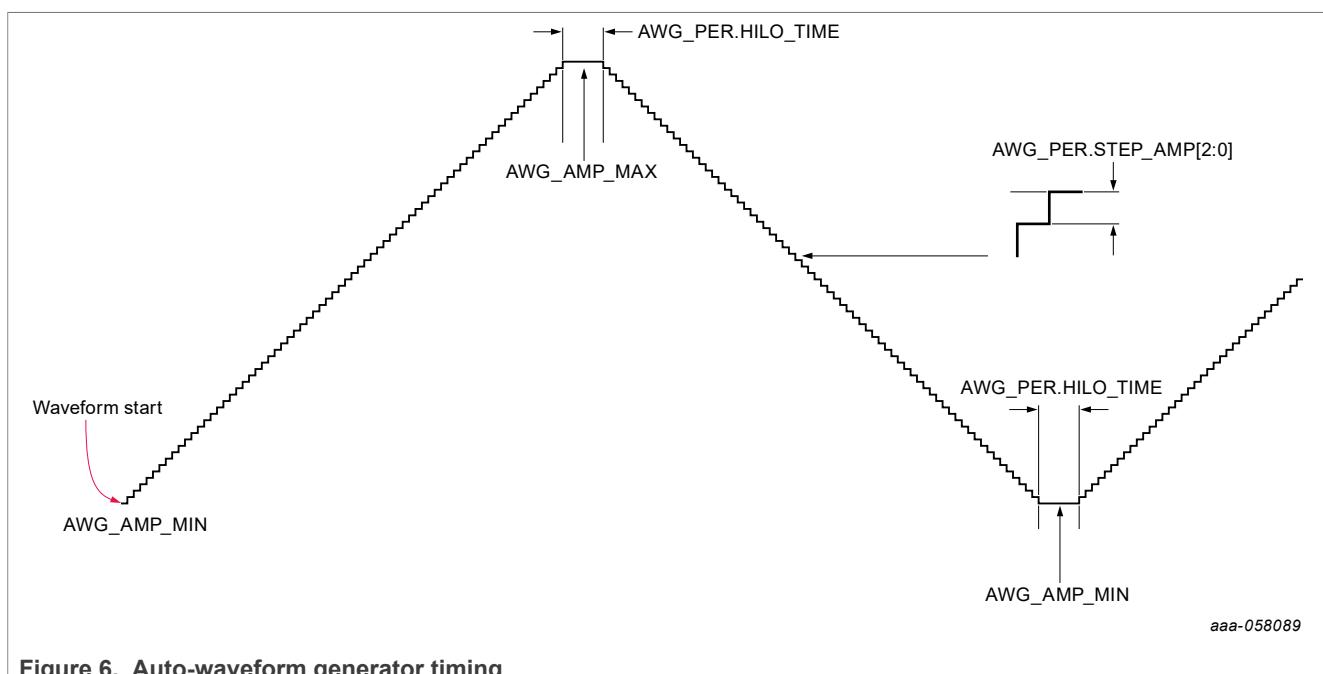

The SPI host sending the DAC command CMD\_WGEN can trigger the Auto-DAC waveform generator. Before issuing this command, all the waveform parameters in AWG\_AMP\_MAX[23:0], AWG\_AMP\_MIN[23:0], STEP\_AMP[2:0], and STEP\_FREQ[2:0] registers are programmed to get the desired output waveform. See [Table 12](#) and [Table 13](#) for the register address of these AWG parameters. CMD\_WGEN\_START continuously executes until CMD\_WGEN\_STOP is told to stop. When the waveform generator is enabled, AIO\_CHOP is ignored. The chopping feature is not supported for auto-waveform generator.

Table 8. Step frequency selection

| STEP_FREQ[2:0] | Update clock frequency in Hz |

|----------------|------------------------------|

| 0 0 0          | 4000                         |

| 0 0 1          | 6000                         |

| 0 1 0          | 9000                         |

| 0 1 1          | 12000                        |

| 1 0 0          | 40000                        |

| 1 0 1          | 60000                        |

| 1 1 0          | 90000                        |

| 1 1 1          | 150000                       |

**Table 9. Auto-DAC waveform generator step size**

| DAC' resolution   | STEP_AMP[2:0] |      |      |      |       |       |       |        |

|-------------------|---------------|------|------|------|-------|-------|-------|--------|

|                   | 0             | 1    | 2    | 3    | 4     | 5     | 6     | 7      |

| Step_size: 18-bit | 1024          | 2048 | 4096 | 8192 | 16384 | 32768 | 65536 | 131072 |

| Step_size: 16-bit | 256           | 512  | 1024 | 2048 | 4096  | 8192  | 16384 | 32768  |

| Step_size: 14-bit | 64            | 128  | 256  | 512  | 1024  | 2048  | 4096  | 8192   |

**Figure 6. Auto-waveform generator timing**

**Note:** For some instances with different programming STEP\_AMP value, AWG\_AMP\_MAX, or AWG\_AMP\_MIN value it is not possible to reach exactly. In these cases, the maximum, minimum code must be clamped to AWG\_AMP\_MAX, AWG\_AMP\_MIN value respectively.

$$AMP_{min to max\ steps} = (Amp\ max - Amp\ min) / (step\ size * LSB)$$

*AMPmintonmax time* = (*AMPmintonmax steps*) / *step freq*

$$Waveform\_period = 2 * (AMPmin to max\_time + HILO\_time)$$

$$\text{Waveform\_freq} = 1 / \text{Waveform\_period}$$

For example:

For 18 bits

$$LSB = (25) / 2^{18} = 95.367 \mu V$$

If Step size(Code = 0) = 1024, Amp max = 12.5 V, Amp min = -12.5 V, then AMPmintomax steps = 256.

If Step period(Code = 0) = 4000, then AMPmintomax time = 0.064 s.

If HILO time = 0, then WF freq = 7.8125 Hz.

**Table 10. Generated waveform frequency with HILO time = 0**

| Generated waveform frequency (Hz) |                  | STEP_Amp (18-bit) |          |           |           |           |           |            |            |

|-----------------------------------|------------------|-------------------|----------|-----------|-----------|-----------|-----------|------------|------------|

|                                   |                  | 0                 | 1        | 2         | 3         | 4         | 5         | 6          | 7          |

| Code                              | Step_period (Hz) | 1024              | 2048     | 4096      | 8192      | 16384     | 32768     | 65536      | 131072     |

| 0                                 | 4000             | 7.8125            | 15.6250  | 31.2500   | 62.5000   | 125.0000  | 250.0000  | 500.0000   | 1000.0000  |

| 1                                 | 6000             | 11.7188           | 23.4375  | 46.8750   | 93.7500   | 187.5000  | 375.0000  | 750.0000   | 1500.0000  |

| 2                                 | 9000             | 17.5781           | 35.1563  | 70.3125   | 140.6250  | 281.2500  | 562.5000  | 1125.0000  | 2250.0000  |

| 3                                 | 12000            | 23.4375           | 46.8750  | 93.7500   | 187.5000  | 375.0000  | 750.0000  | 1500.0000  | 3000.0000  |

| 4                                 | 40000            | 78.1250           | 156.2500 | 312.5000  | 625.0000  | 1250.0000 | 2500.0000 | 5000.0000  | 10000.0000 |

| 5                                 | 60000            | 117.1875          | 234.3750 | 468.7500  | 937.5000  | 1875.0000 | 3750.0000 | 7500.0000  | 15000.0000 |

| 6                                 | 90000            | 175.7813          | 351.5625 | 703.1250  | 1406.2500 | 2812.5000 | 5625.0000 | 11250.0000 | 22500.0000 |

| 7                                 | 150000           | 292.9688          | 585.9375 | 1171.8750 | 2343.7500 | 4687.5000 | 9375.0000 | 18750.0000 | 37500.0000 |

### 7.3.5 $\pm 36$ V at the screw terminal AO pin

The IO module is protected at the AO screw terminal pin for voltage surge (IEC61004-5), with the help of TVS mounted on the board. The TVS must clamp the voltage within  $\pm 36$  V.

The device must sustain  $\pm 36$  V DC protection at the AO screw terminal pin with the help of a Schottky diode and series resistor, see [Figure 25](#).

When the device is in the High-Z mode, the device must not load the AO pin at the screw terminal up to  $\pm 36$  V.

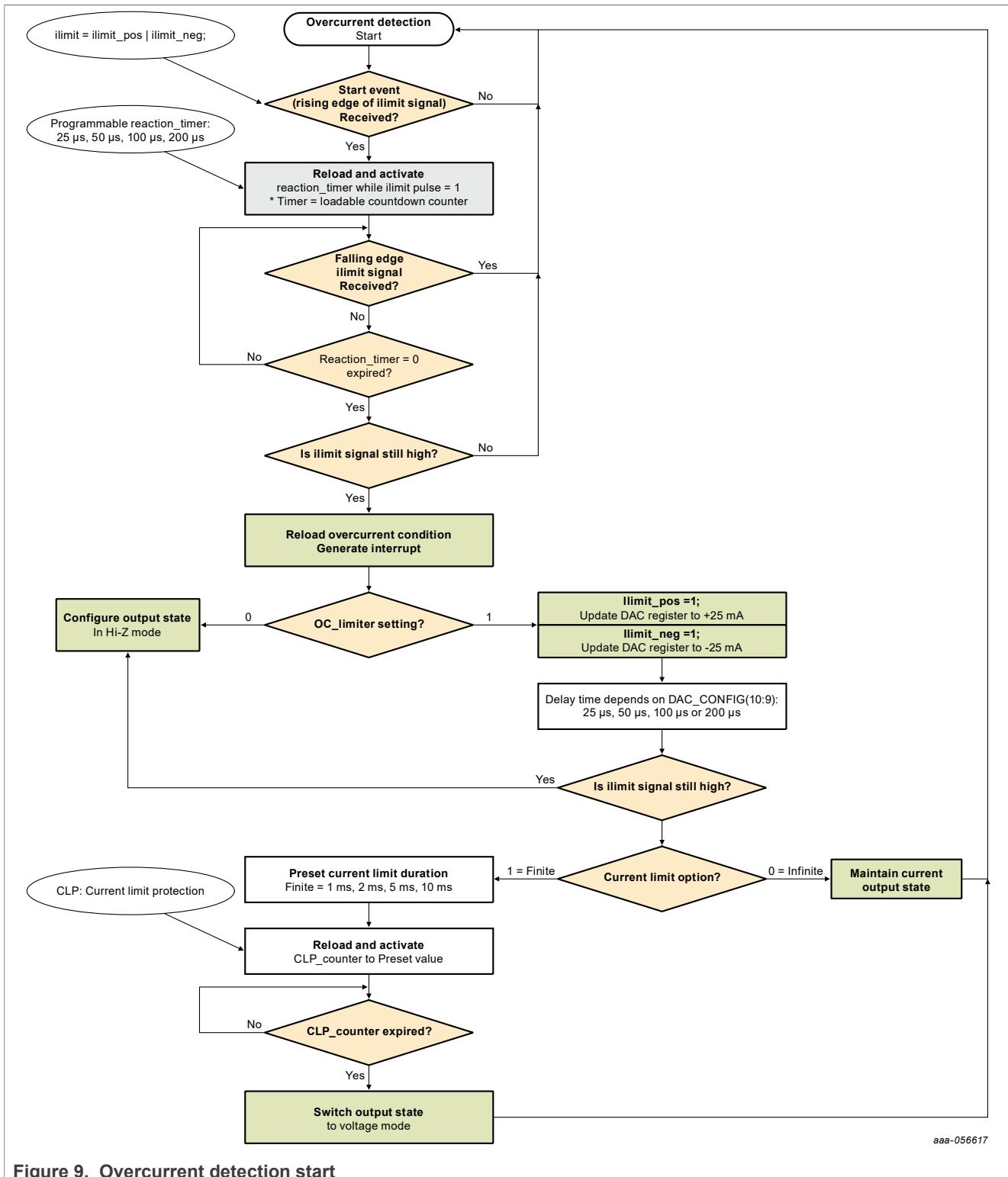

### 7.3.6 Overcurrent protection in Voltage-output mode

The NAFE33350 is protected against overload and short-circuit.

Since the AO-AFE can operate in Voltage mode with different load, the current limit must be smart and configurable to adapt to different scenarios.

A typical scenario is the Voltage mode with capacitive load. In this case, during a voltage transient a surge current happens to charge the capacitor. The slew rate, voltage-step amplitude, and load capacitor determine the surge current. The overcurrent protection must be able to manage the short surge current to satisfy the settling time of the system. At the same time, the device must be protected from a real short.

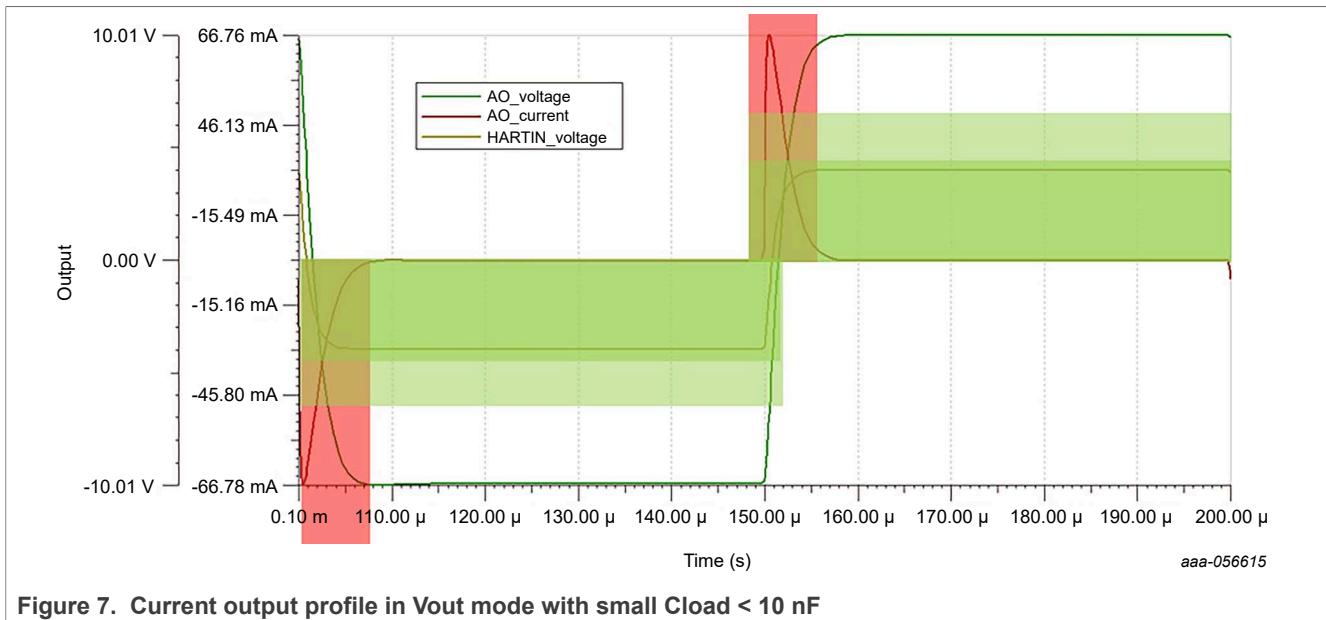

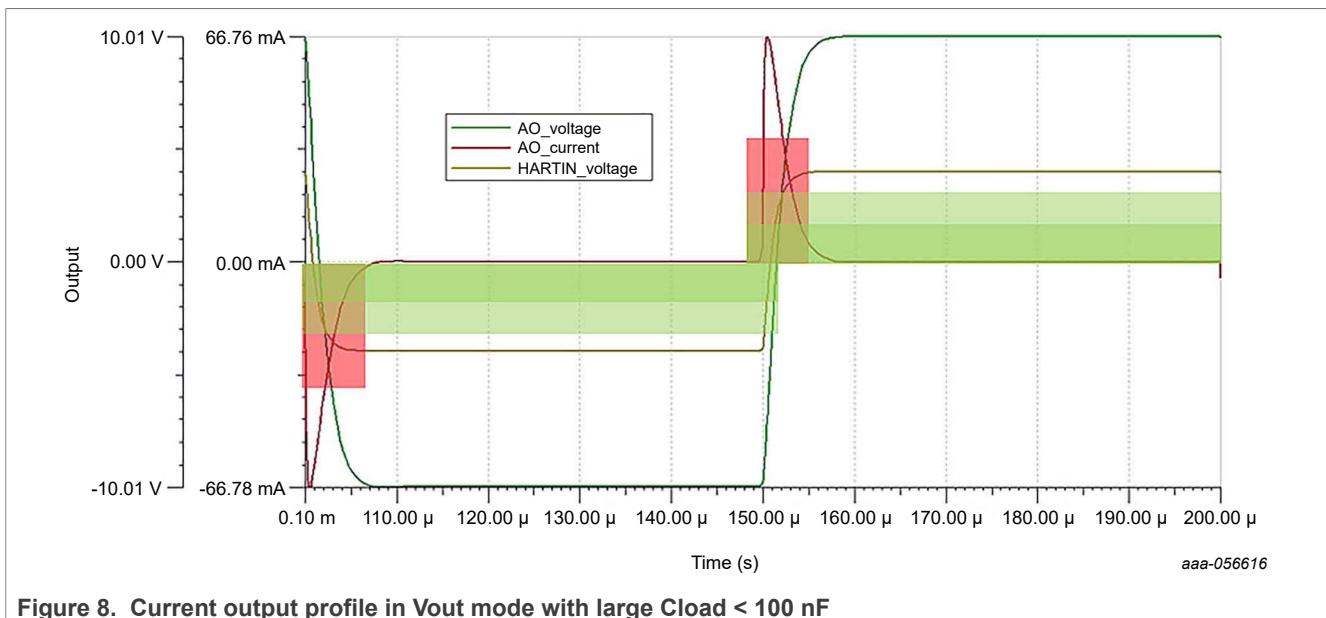

For this reason, dual protection mechanisms are considered with a different current threshold and reaction time. The fast-reaction and high-current threshold (red area in [Figure 7](#) and [Figure 8](#)) protects against severe short-circuit, while the slow-reaction and low-current threshold (green area in [Figure 7](#) and [Figure 8](#)) protect against long-period overload.

The figures below report the time-dependent threshold profile and the current surge. When the surge current is below the current protection profile, see [Figure 7](#), the protection circuit is not activated and the AO-AFE can charge the capacitor without interruption.

If the surge exceeds the short-circuit limit of 70 mA or lasts longer than the reaction time of 5  $\mu$ A, the protection circuit activates and the part goes in High-Z mode. For details, see [Figure 8](#). The following section explains how to handle such situations by using a device-programmable current limiter.

Figure 7. Current output profile in Vout mode with small Cload &lt; 10 nF

Figure 8. Current output profile in Vout mode with large Cload &lt; 100 nF

Once a short-circuit is detected, the fast-current limiter limits the current to a max value of  $\sim 150 \text{ mA}$ .

### 7.3.6.1 Overcurrent limits

This section describes short-circuit and overload circuit limits.

#### 7.3.6.1.1 Short-circuit limits

- Short current threshold  $\sim \pm 70 \text{ mA}$  (output stage coarse current limiter)

- Reaction time  $< 5 \mu\text{s}$  (faster)

- The current limiter limits the maximum current at  $\sim \pm 70 \text{ mA}$

- Overload is detected in approximately  $1 \mu\text{s} - 2 \mu\text{s}$ , but not activated if the overload lasts  $<$  programmable  $10 \mu\text{s} / 20 \mu\text{s} / 50 \mu\text{s} / 100 \mu\text{s}$

### 7.3.6.1.2 Overload circuit limits

- Overload current threshold can be programmed to 5 mA,  $\pm 10$  mA,  $\pm 20$  mA, or  $\pm 25$  mA.

- If the overload condition happens, even after the deglitch timer, you can trigger the High-Z protection mode or initiate the programmable current limiter.

- Reaction time (for the current limit to settle) can be programmed to 25  $\mu$ s, 50  $\mu$ s, 100  $\mu$ s, 200  $\mu$ s with the default being 25  $\mu$ s.

- After the reaction time expires and if the overload (comparator output) is still active high, the output stage does the following:

- Switch to Current-input mode and set a configured current limit output (< abs ( $\pm 25$ ) mA).

- Set to High-Z (default safe state).

- You can write the programmed overload threshold on the shadow register. The default value is  $\pm 25$  mA.

- If, after a defined reaction time (current settling time), the current output is still over the current threshold, then the output stage is set in High-Z. An alarm is issued and the output stage status register is updated accordingly.

- If, after a defined reaction time (current settling time), the current output is under the current threshold, then the output stage maintains the current output for a defined period as below:

- Current limiter period:

- Infinite.

- Finite = 1 ms, 2 ms, 5 ms, 10 ms.

- After the current limiter period, the digital control logic switches from Current mode to Voltage mode.

Figure 9. Overcurrent detection start

## 7.4 Transimpedance amplifier

A transimpedance amplifier (TRIAMP) is used to readback the voltage output as feedback for the output power amplifier.

## 7.5 Common system

The common system of the NAFE33350 device comprises selectable voltage reference source, clock source, and GPIOs.

### 7.5.1 Voltage reference sources

This section describes the voltage reference selector, low-drift internal voltage reference, external-voltage reference, and internally buffered reference for DAC.

#### 7.5.1.1 Voltage reference selector

The voltage reference selector enables the selection of internal or external reference. The device uses an internal reference by default on power up and the user can assert SYS\_CONFIG.REF\_SEL to use an external 2.5 V reference.

#### 7.5.1.2 Low-drift internal voltage reference

The AO-AFE integrates a precise voltage reference with a low-temperature coefficient to reduce the drift error overtemperature.

#### 7.5.1.3 External-voltage reference input

The AO-AFE features a dedicated input pin to allow the connection to an external voltage reference.

#### 7.5.1.4 Internally buffered reference for DAC

The AO-AFE has an independent internal buffer (sourced by either internal or external reference) to provide individual reference sources to the DAC block. To activate the DAC reference buffer, ensure that AO\_SYSCFG.AO\_ON is set as either 0x10 or 0x11. See, see [Table 12](#).

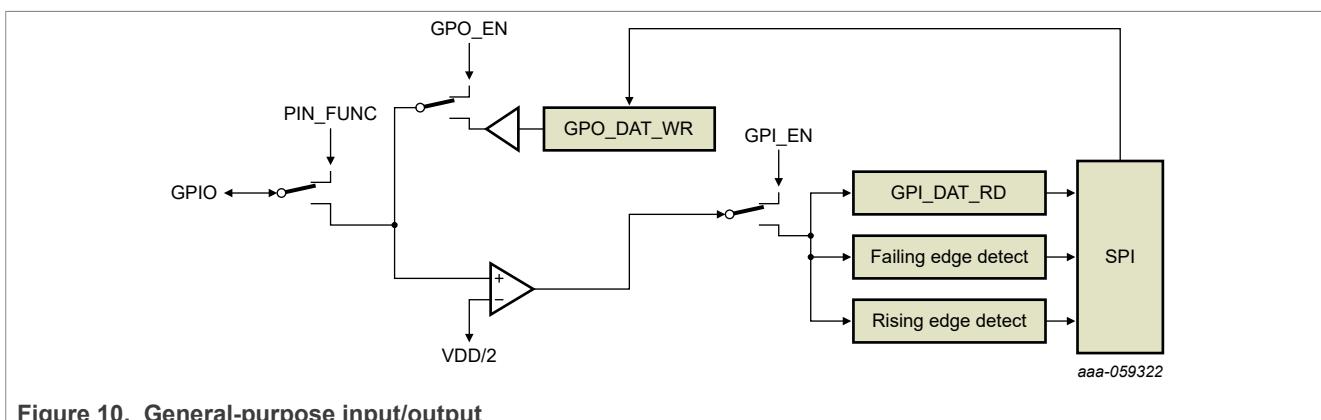

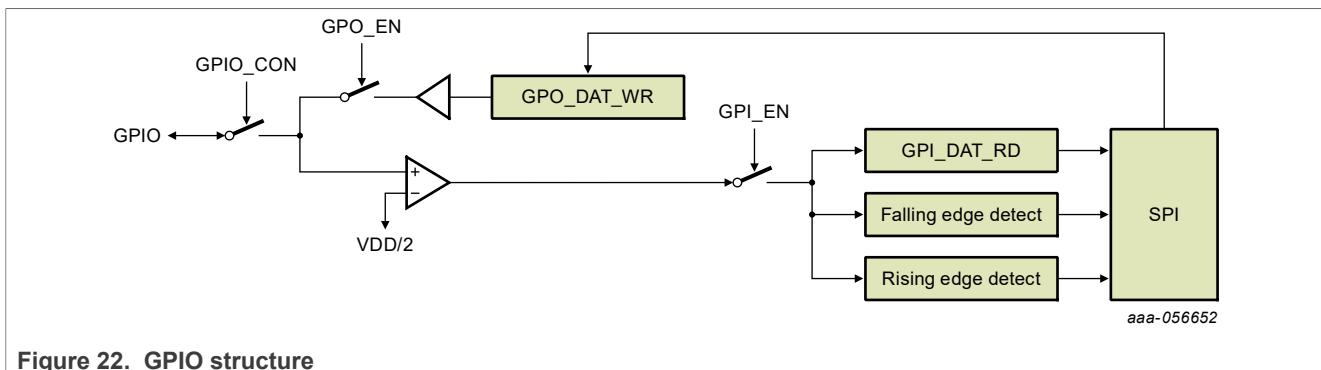

## 7.5.2 General-purpose input/output

The AO-AFE has five pins (2, 3, 21, 22, 33) that serve dual purposes and can be configured as GPIO. The operating input and output voltage ranges are 0 V to VDD when these pins are configured as GPIO.

Figure 10. General-purpose input/output

The GPIO control and data registers are organized by 4x5 bits register.

1. GPII\_DATA (0x23\h): Read (R) only register and it detects a level logic from the pad.

2. GPO\_ENABLE (0x24\h): Read/write (R/W) GPO\_EN register. It enables an output path.

3. GPIO\_FUNCTION(0X25\h): R/W PIN\_FUNC register.

4. GPI\_ENABLE (0x26\h): R/W GPI\_ENABLE. It enables the input path to allow reading data from the pad, looping back from the GPO\_DATA register and/or GPIO edges detection.

GPIO both edges detection results in 2x5-bit register 0x27 for positive and 0x28 for negative respectively are implemented as follows.

While GPI\_EN = 1 and GPIO\_CON = 1, during any transition from  $0 \geq 1$  (positive edge) or  $1 \geq 0$  (negative edge), the edge detection register is set to 1. This edge detection register is defined as sticky by nature and requires the host to clear it by writing 1 to the bit that is set to 1 (W1C).

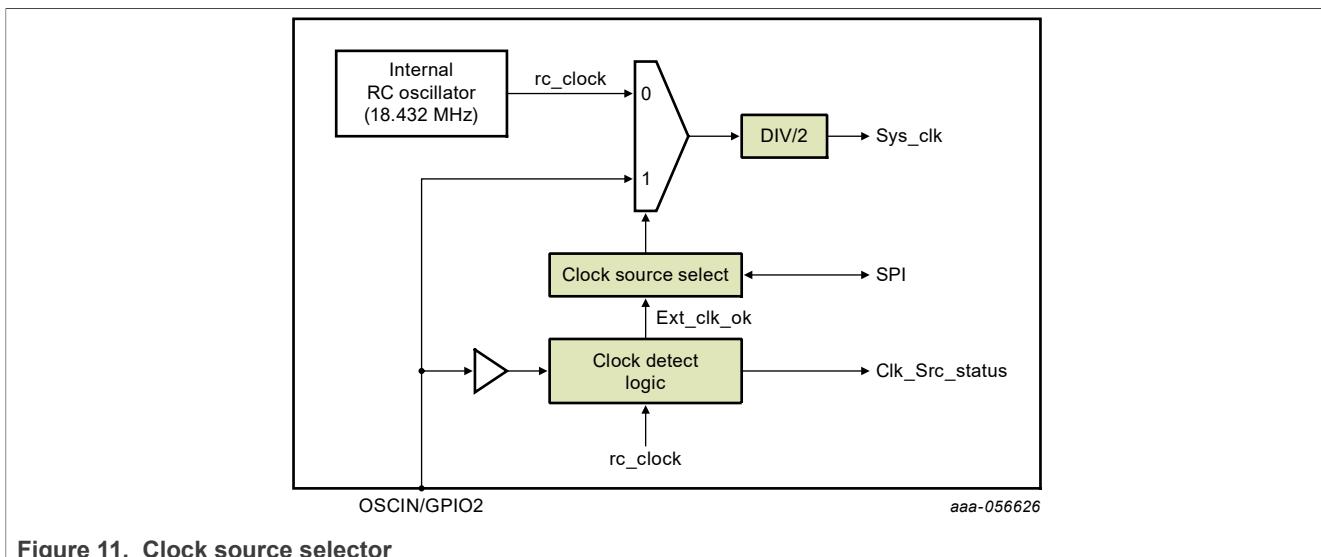

### 7.5.3 Clock sources

The NAFE33350 provides flexible and configurable operating modes that can function with two different clock sources: internal RC oscillator and external oscillator.

[Figure 11](#) shows the clock architecture.

Figure 11. Clock source selector

#### 7.5.3.1 Internal RC oscillator

The AFE integrates an internal oscillator to allow autonomous and cost-effective operation without support of any external clock source.

The internal oscillator nominal frequency is 18.432 MHz.

#### 7.5.3.2 External oscillator

The AFE can also operate with an external oscillator to enable applications that require synchronization between the AFE and the host. It also allows coherent sampling of the input signal.

Ensure that the external oscillator is applied to pin OSCIN. If not used, OSCIN can be left floating.

#### 7.5.3.3 Clock selection

At power on, the AFE starts with the internal RC oscillator.

The NAFE33350 provides the following mechanisms for system clock selection:

- User selection via system register configuration

- The AO-AFE detects the presence of the external oscillator before activating the external oscillator input.

- If the external oscillator is not detected, the AFE continues to operate with the internal clock and provides an error message via the error status register.

For details, see [Table 14](#).

#### 7.5.3.4 User selection of clock sources

The user selection option allows the user to select the desired clock after power on. The clock source can be selected by writing to the clock source system configuration register.

Check the presence of the external clock while making external clock selection in the system configuration register to ensure proper functioning of the NAFE33350. If the external clock is detected and the NAFE33350 switches to the external clock, the system status register is updated accordingly. If the external clock is not detected, the NAFE33350 maintains the previous clock configuration.

#### 7.5.3.5 Clock frequency drift detection

Whenever `clock_src_sel [1:0]` is set to 2'b11 or 2'b10, the clock period monitoring is activated. This circuit continuously measures the clock frequency difference between the external clock and the internal RC oscillator INTOSC.

The default value of the clock frequency difference is set to 20 % at power-on reset (POR). The clock comparison logic issues an alarm when the running average clock count difference is greater than 20 %. The alarm status bit for clock variation is user accessible via SPI register. The average time window is ~64 ms. If the external clock is selected as the system clock source and the `EXTCLK_FREQ_ALARM` bit is enabled, the external clock alarm interrupt is triggered. The trigger occurs when (`EXTCLK_FREQ_INT = 1`) and the `EXTCLK` is not within the 20 % period difference.

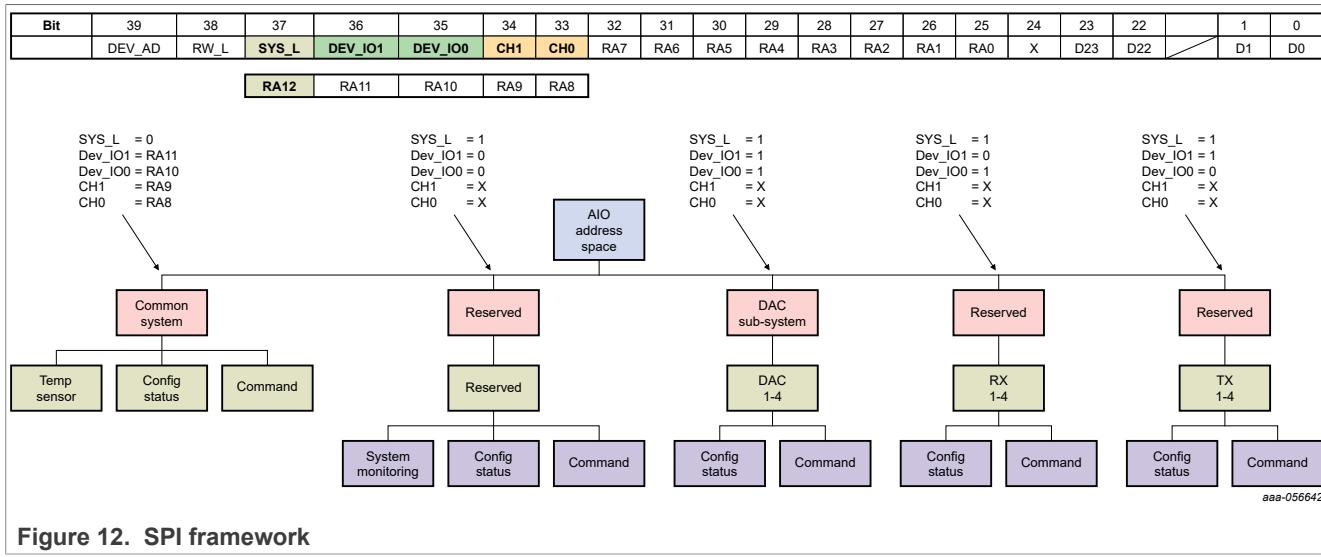

### 7.6 User register map

The user register maps are categorized into the following:

1. Output channel configuration, status, and data registers

2. System configuration, status, and alarm registers

3. Calibration coefficients, PN, and SN

**Table 11. 24-bit user registers - AI channel data**

| 24-bit user registers - AI channel data |      |                         |    |          |                                                                                                                                                            |

|-----------------------------------------|------|-------------------------|----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AI_DATA0..7 0x30h - 0x37h               | 23:0 | DATA0 ... DATA7         | R  | 0x000000 | Channel output data. Each channel has a corresponding data register. DATA0[23:0] is converted data output of CH0...DATA7[23:0] is converted output of CH7. |

| AI_CH_OVR_THR 0x38h - 0x3Fh             | 23:0 | OVR_THRS0 ... OVR_THRS7 | RW | 0x000000 | Overrange threshold setting for each logical data channel.                                                                                                 |

| AI_CH_UDR_THR 0x40h - 0x47h             | 23:0 | UDR_THRS0 ... UDR_THRS7 | RW | 0x000000 | Underrange threshold setting for each logical data channel.                                                                                                |

**Table 12. 16-bit user registers - output channel configuration registers**

| 16-bit user registers - output channel configuration registers |    |          |    |     |                                                                                                                        |

|----------------------------------------------------------------|----|----------|----|-----|------------------------------------------------------------------------------------------------------------------------|

| AIO_CONFIG 0x20h                                               | 15 | Reserved | R  | 0x0 | VSA ON = 1 turn ON VSA. Exception: AO_MODE = 10b Voltage output mode force VSA ON = 1, this bit cannot be overwritten. |

|                                                                | 14 | VSA ON   | RW | 0x0 |                                                                                                                        |

Table 12. 16-bit user registers - output channel configuration registers...continued

| 16-bit user registers - output channel configuration registers |       |                    |    |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------|-------|--------------------|----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                | 13    | CSA ON             | RW | 0x0  | CSA ON = 1 turn ON CSA. Exception: AO_mode = 11b Current output mode force CSA ON = 1, this bit cannot be overwritten.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                | 12    | CISW_ON            | RW | 0x0  | CISW_ON = 1 turn ON the current input switch connected to the ground. CISW is used with external Rsense for Current input mode configuration.<br><b>Note:</b> To avoid short-circuit, CISW_ON must be 0h when the PA_ON = 1, if the CISW pin is connected to the AOP/AON path.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                | 11:7  | Reserved           | R  | 0x0  | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                | 6:5   | AO_MODE            | RW | 0x0  | AO_MODE Pre-configured AO modes. 00b: Hi-Z mode, PA_ON = 0, VSA_ON = x, CSA_ON = x; 10b: Voltage output mode, PA_ON = 1, VSA_ON = 1, CSA_ON = x; 11b: Current output mode, PA_ON = 1, VSA_ON = x, CSA_ON = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                | 4     | UNIPOLAR_AO_MODE   | RW | 0x0  | Select AO mode: 0h = Bipolar AO mode 1h = Unipolar AO mode. See <a href="#">Section 7.14</a> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                | 3:2   | Reserved           | R  | 0x0  | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                | 1:0   | AO_TCC             | RW | 0x00 | Proprietary AO temperature coefficient correction: 00b = select AO_TCC for VO mode 01b = select AO_TCC for CO mode 1xb = Disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| AO_CAL_COEF<br>0x21h                                           | 15    | Reserved           | R  | 0x0  | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                | 14:12 | DAC_CAL_COEF       | RW | 0x0  | Pointer to select DAC gain and offset calibration coefficients [3-BITS]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                | 11:0  | Reserved           | R  | 0x0  | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| AIO_PROT_CFG<br>0x22h                                          | 15:13 | AO_CLIM_PER        | RW | 0x0  | Select the output current limit duration at AOP, AON:<br>0h = 1 ms, 1h = 2 ms, 2h = 5 ms, 3h = 10 ms; 4h = 20 ms; 5h = 50 ms; 6h = 20 ms; 7h = infinite.<br>When the timer expires, if the AO_CLIM_PER timer duration is finite, the AO mode is changed back to VO mode.<br>If the AO_CLIM_PER timer duration is infinite, it remains in limited current mode.                                                                                                                                                                                                                                                                                                                                                       |

|                                                                | 12:11 | AO_OVRLOAD_CUR_THR | RW | 0x0  | Select the output overload current thresholds at AOP, AON pin: 0h = ±25 mA; 1h = ±20 mA; 2h = ±10 mA; 3h = ±5 mA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                | 10:9  | AO_OVRCUR_DEG      | RW | 0x0  | Set the output overcurrent deglitch timer duration. AO_OVRCUR_DEG is re-armed whenever DAC code or AO mode change. Then, the timer is triggered upon an AO_SHRT_L or AO_OVRLOAD_L alarm and lasts for a duration of 0h = 10 µs; 1h = 20 µs; 2h = 50 µs; 3h = 100 µs.<br>When the timer expires, if AO_SHRT_L = 1 persists, the AO is put into High-Z mode and the AO_STATUS is set to 01b if (AO_SHRT_L = 0) and (AO_OVRLOAD_L = 0) and (AO_OVRLAOD_PROT = 0), the AO is put into High-Z mode and the AO_STATUS is set to 01b if (AO_SHRT_L = 0) and (AO_OVRLOAD_L = 1) and (AO_OVRLAOD_PROT = 1), the AO is put into limited current mode and the AO_STATUS is set to 11h. A_CLIM_SD controls the initial duration. |

|                                                                | 8     | AO_OVRLOAD_PROT    | RW | 0x0  | Set the overload protection behavior and post the AO_OVR_CUR_RT reaction timer: In the event of a programmable overload condition (set by AO_OVRLOAD_CUR_THR), if 0h = configure AO in High-Z mode and set AO_STATUS = 3h<br>1h = configure AO in current limiter mode and set AO_STATUS = 2h during AO_CLIM_SD.                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                | 7:6   | AO_CLIM_SD         | RW | 0x0  | Configure the output current limiter settling delay timer to allow the current limiter to settle.<br>0h = 25 µs; 1h = 50 µs; 2h = 100 µs; 3h = 200 µs.<br>When the timer expires, if (AO_SHRT_L = 1), the AO is put into High-Z mode, and AO_STATUS alarm is set to 01b; if (AO_SHRT_L = 0) and (AO_OVRLOAD_L = 0), the AO stays in limited current mode during AO_CLIM_PER, and the AO_STATUS alarm is set to 11b. During the AO_CLIM_PER period, (AO_SHRT_L = 1)   (AO_OVRLOAD_L = 1) puts the AO into High-Z mode and AO_STATUS alarm is set to 01b.                                                                                                                                                              |

|                                                                | 5:4   | CISW_OVRCUR_DEG    | RW | 0x0  | CISW input overcurrent deglitch timer duration 0h = 10 µs; 1h = 20 µs; 2h = 50 µs; 3h = 100 µs;<br>When the timer expires, if CISW_SHRT_L = 1, the CISW is turned OFF, and the CISW_STATUS bit is reset. If (CISW_SHRT_L = 0) and (CISW_OVRLOAD_L = 1), the CISW current limiter mode is activated, and the CISW_STATUS bit is set. If (CISW_SHRT_L = 0) and (CISW_OVRLOAD_L = 0), the CISW remains turned ON.                                                                                                                                                                                                                                                                                                       |

Table 12. 16-bit user registers - output channel configuration registers...continued

| 16-bit user registers - output channel configuration registers |             |                  |              |                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              |  |        |              |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|----------------------------------------------------------------|-------------|------------------|--------------|-------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--|--------|--------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|                                                                | 3:2         | CISW_CLIM_PER    | RW           | 0x0                                                                     | CISW input over the current limit period: 0\h = 1 ms; 1\h = 2 ms; 2\h = 5 ms; 3\h = 10 ms                                                                                                                                                                                                                                                                                                                                                                                       |              |  |        |              |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|                                                                | 1:0         | CISW_CLIM_SD     | RW           | 0x0                                                                     | CISW input current limiter settling delay timer 0\h = 25 $\mu$ s; 1\h = 50 $\mu$ s; 2\h = 100 $\mu$ s; 3\h = 200 $\mu$ s;<br>After the timer expires, if CISW_SHRT_L = 1 or CISW_OVRLOAD_L = 1 persists, the AO is set in High-Z mode. If AO_SHRT_L = 0 and AO_OVRLOAD = 0, the AO stays in current limiter mode during AO_CLIM_PER.<br>During the CISW_CLIM_PER, if CISW_SHRT_L = 1 or CISW_OVRLOAD = 1, the CISW is opened.                                                   |              |  |        |              |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| AO_SLR_CTRL<br>0x23\h                                          | 15          | SLREN            | RW           | 0x0                                                                     | Slew rate enabled = 1; default 0: disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |  |        |              |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|                                                                | 14:12       | SLR_STEP         | RW           | 0x0                                                                     | Slew rate step. See <a href="#">Table 7</a> .                                                                                                                                                                                                                                                                                                                                                                                                                                   |              |  |        |              |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|                                                                | 11:9        | SLR_CLOCK        | RW           | 0x0                                                                     | Slew rate update clock. See <a href="#">Table 6</a> .                                                                                                                                                                                                                                                                                                                                                                                                                           |              |  |        |              |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|                                                                | 8           | Reserved         | R            | 0x0                                                                     | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |  |        |              |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|                                                                | 7:0         | Reserved         | R            | 0x0                                                                     | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |  |        |              |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| AWG_PER 0x24\h                                                 | 15:13       | STEP_AMP         | RW           | 0x0                                                                     | Programmable step size: eight-step sizes, amplitude step. See <a href="#">Section 7.3.4</a> .                                                                                                                                                                                                                                                                                                                                                                                   |              |  |        |              |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|                                                                | 12:10       | STEP_freq        | RW           | 0x0                                                                     | Programmable frequency update: eight freq. update. See <a href="#">Table 8</a> .                                                                                                                                                                                                                                                                                                                                                                                                |              |  |        |              |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|                                                                | 9:0         | HILO_TIME        | RW           | 0x000                                                                   | Programmable high/low time in term of number of STEP_PERIOD(= 1/STEP_FREQ). See <a href="#">Table 10</a> .                                                                                                                                                                                                                                                                                                                                                                      |              |  |        |              |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| AO_SYSCFG<br>0x25\h                                            | 15          | SYNCDAC_EN       | RW           | 0x0                                                                     | If SYNCDAC_EN = 0b, the DAC code is latched by the rising edge of CSB. If SYNCDAC_EN = 1b, the DAC code is latched by the rising edge of the External SYNCDAC pulse.<br><b>Note:</b> The SYNCDAC pin serves as the device address (ADR0) at POR. During POR, if the ADR0 is at logic level HIGH, the address is set to 1, otherwise it is set to 0. After POR the pin functions as SYNCDAC.                                                                                     |              |  |        |              |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|                                                                | 14          | DAC_DATA_16BIT   | RW           | 0x0                                                                     | 0\h = NUMBER OF SPI DAC DATA = 3 BYTE [24-BIT]<br>1\h = NUMBER OF SPI DAC DATA = 2 BYTE [16-BIT]                                                                                                                                                                                                                                                                                                                                                                                |              |  |        |              |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|                                                                | 13          | STATUS_STICKY_AO | RW           | 0x0                                                                     | Prepended status bits behavior when reporting AO_OC or CI_OC status while STATUS_EN = 1.<br>1\h = sticky; 0\h = live.                                                                                                                                                                                                                                                                                                                                                           |              |  |        |              |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|                                                                | 12          | Reserved         | R            | 0x0                                                                     | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |  |        |              |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|                                                                | 11:10       | AO_ON            | RW           | 0x0                                                                     | <table border="1"> <tr> <th colspan="2">(AO_ON[1:0])</th> <th>DAC_en</th> <th>DACREFBUF_en</th> </tr> <tr> <td>0</td> <td>0</td> <td>0</td> <td>0</td> </tr> <tr> <td>0</td> <td>1</td> <td>0</td> <td>1</td> </tr> <tr> <td>1</td> <td>0</td> <td>1</td> <td>1</td> </tr> <tr> <td>1</td> <td>1</td> <td>1</td> <td>1</td> </tr> </table><br><b>Note:</b> Set AO_ON = 11 along with AO_MODE = 10b or 11b if an internal DAC is used for generating voltage and current output. | (AO_ON[1:0]) |  | DAC_en | DACREFBUF_en | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| (AO_ON[1:0])                                                   |             | DAC_en           | DACREFBUF_en |                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              |  |        |              |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| 0                                                              | 0           | 0                | 0            |                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              |  |        |              |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| 0                                                              | 1           | 0                | 1            |                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              |  |        |              |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| 1                                                              | 0           | 1                | 1            |                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              |  |        |              |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

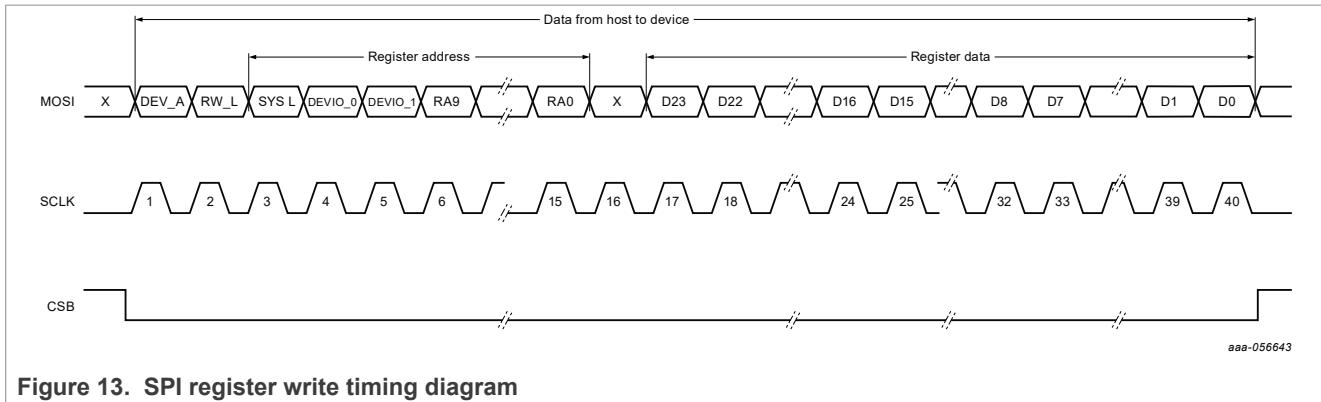

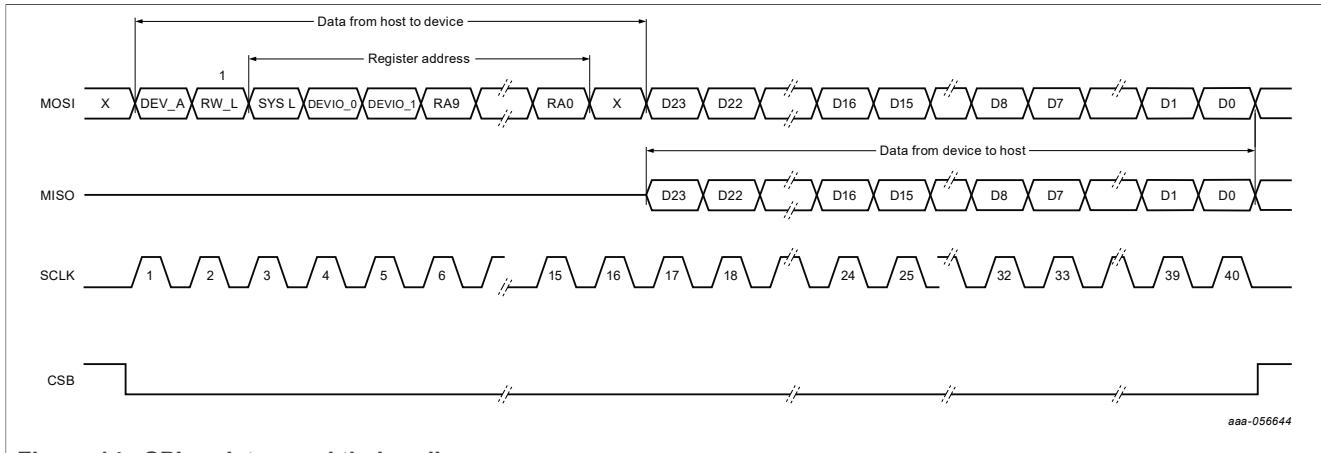

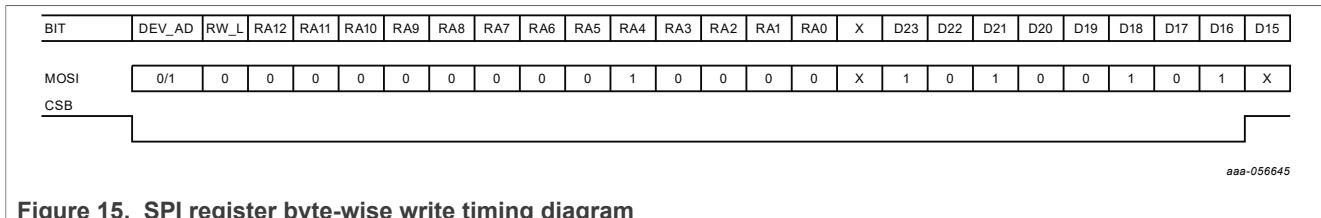

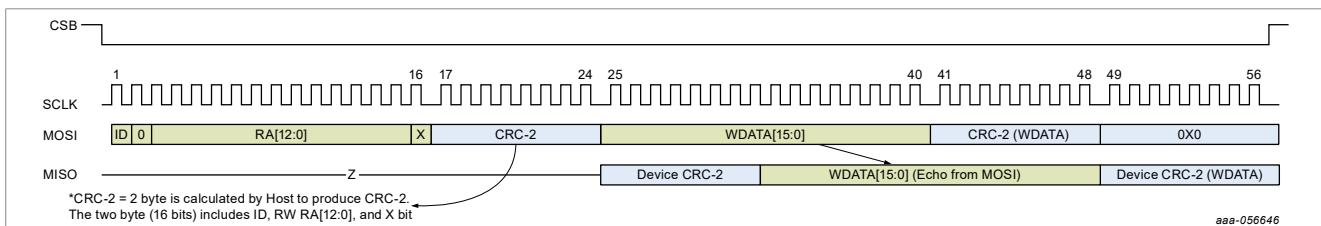

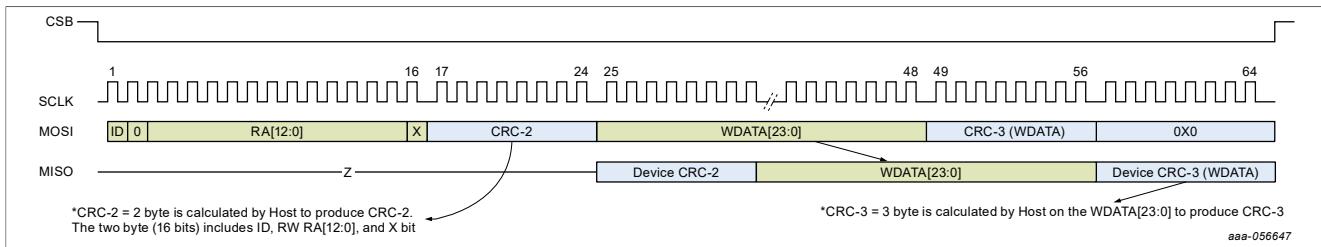

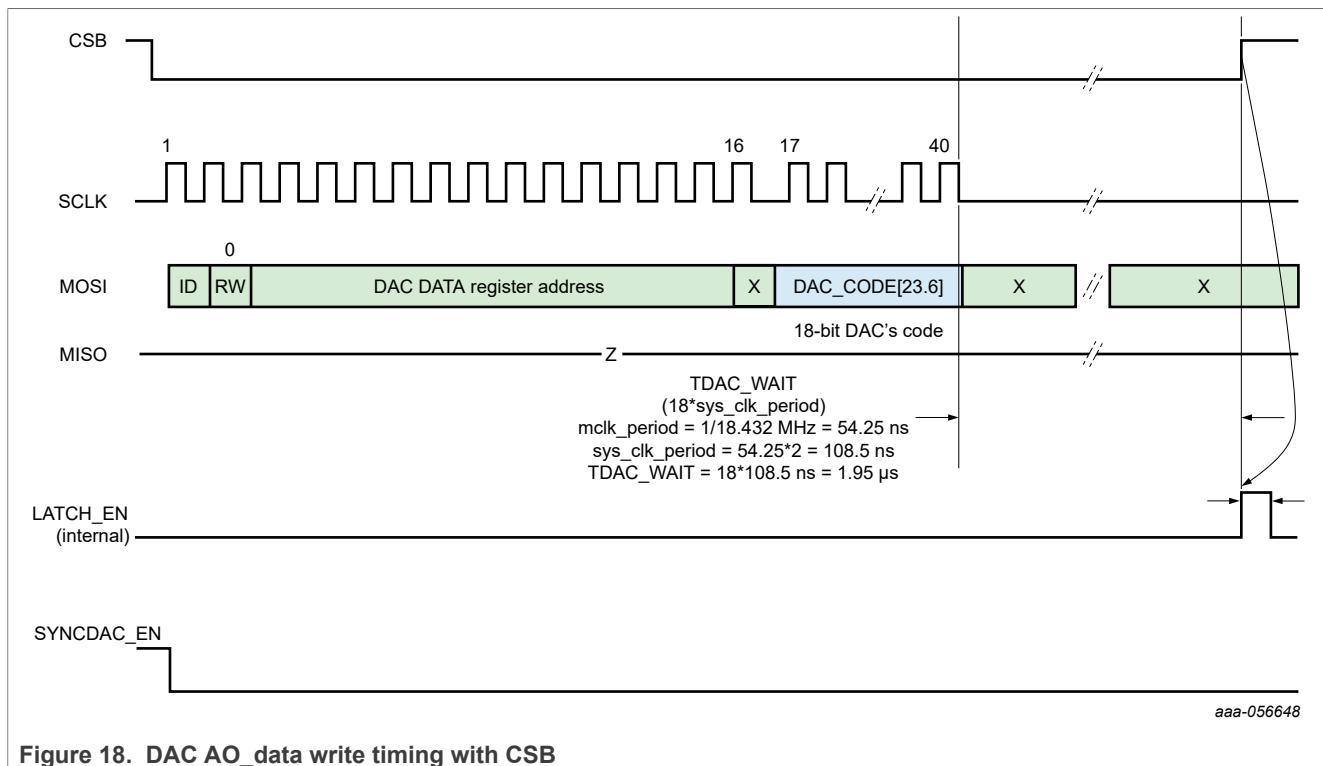

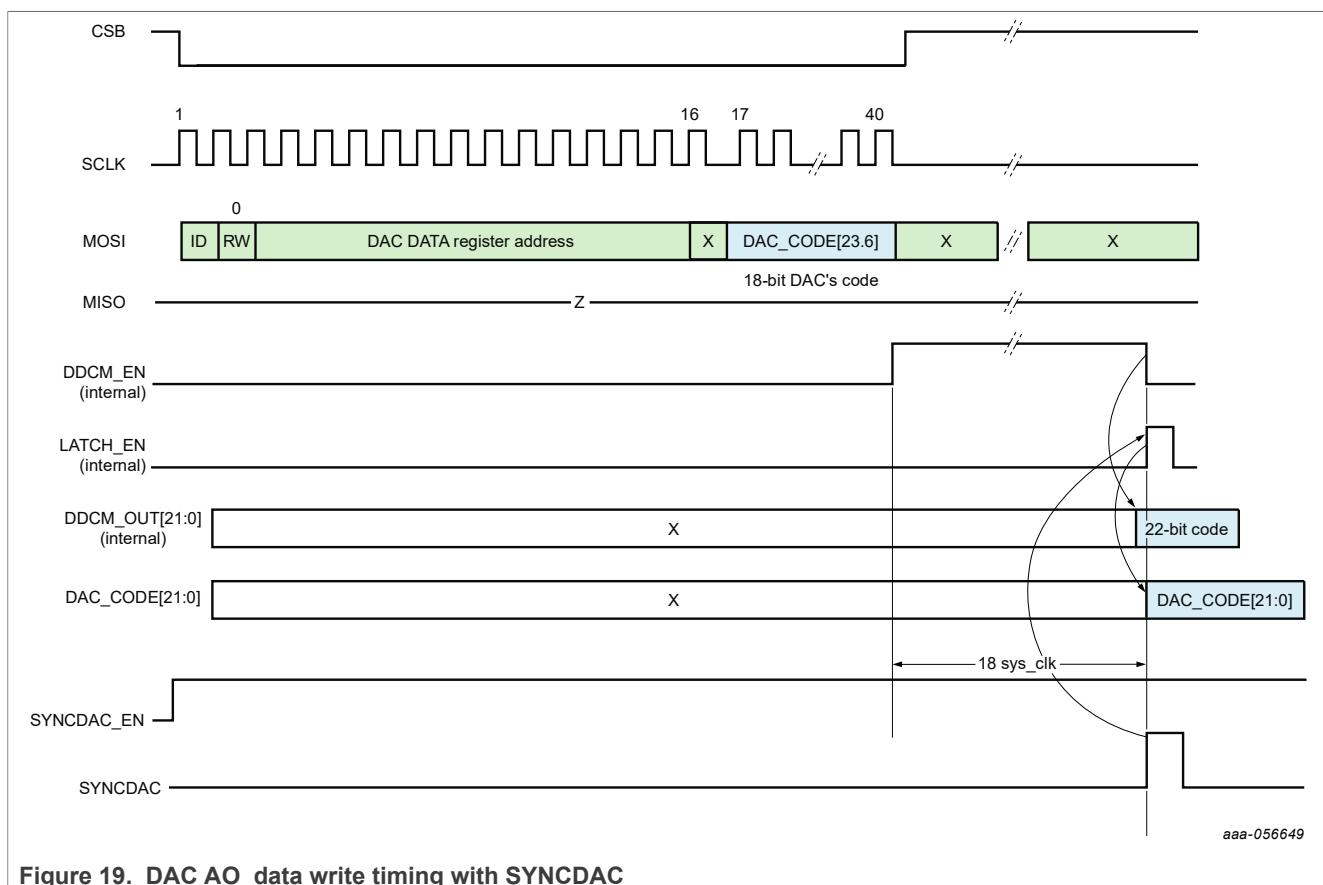

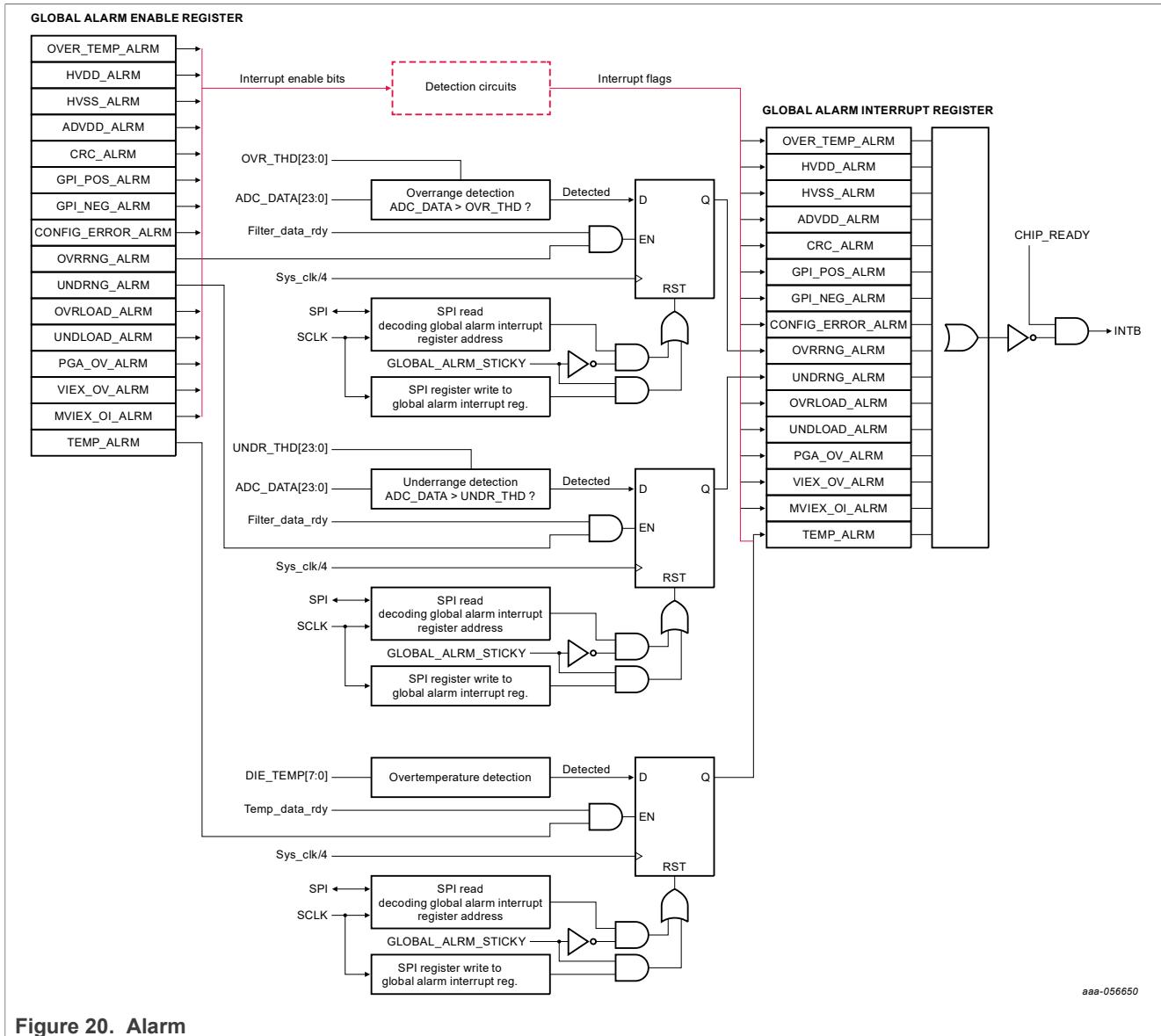

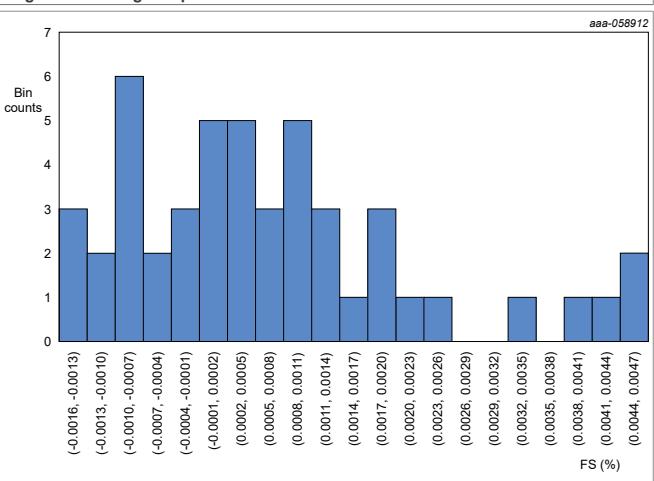

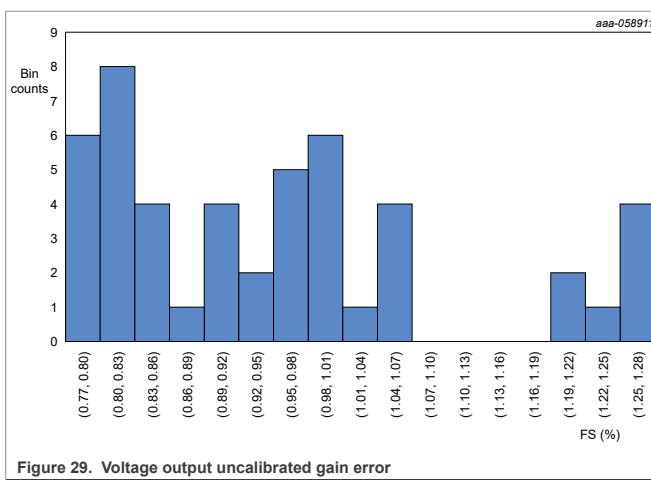

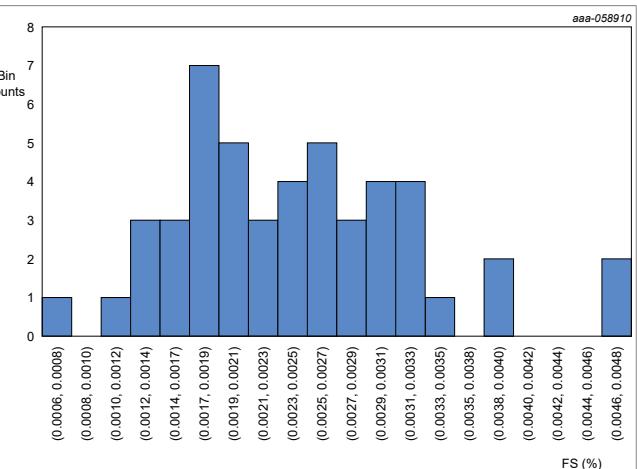

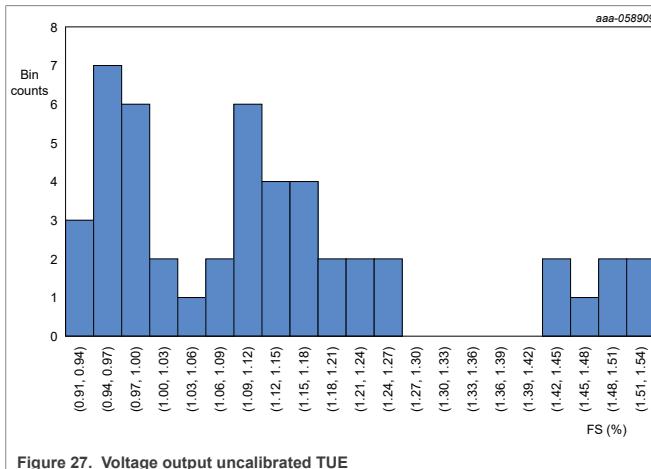

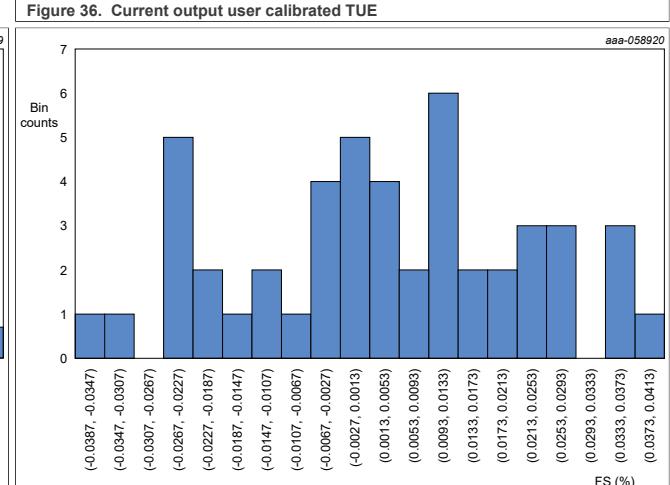

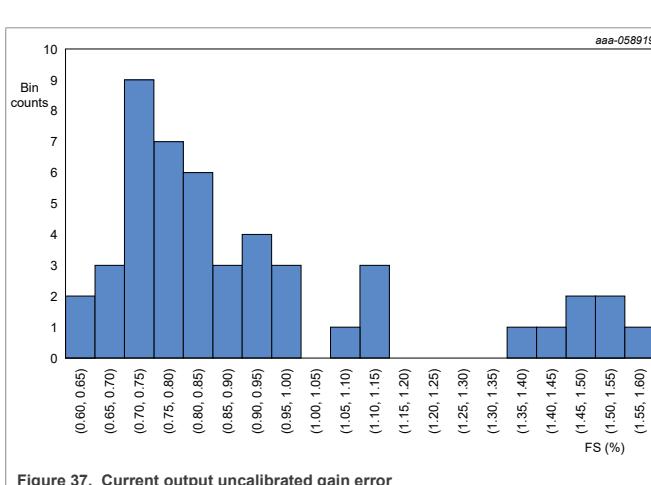

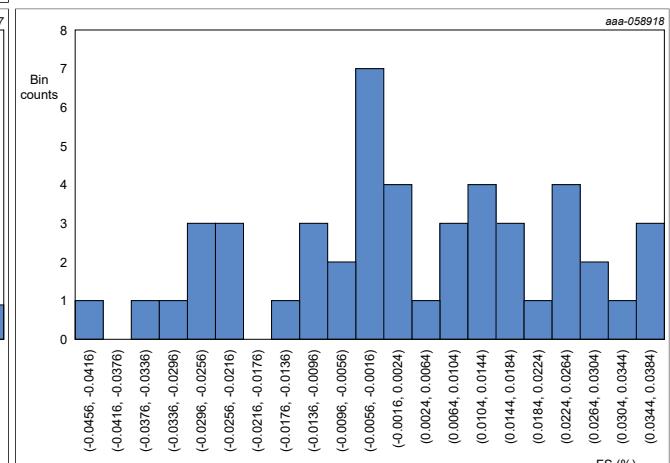

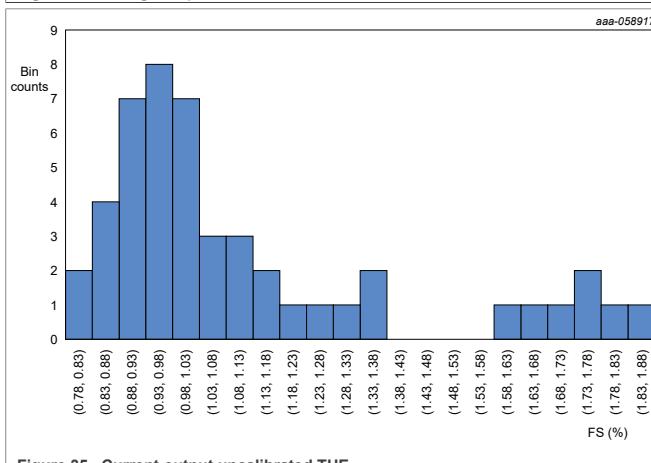

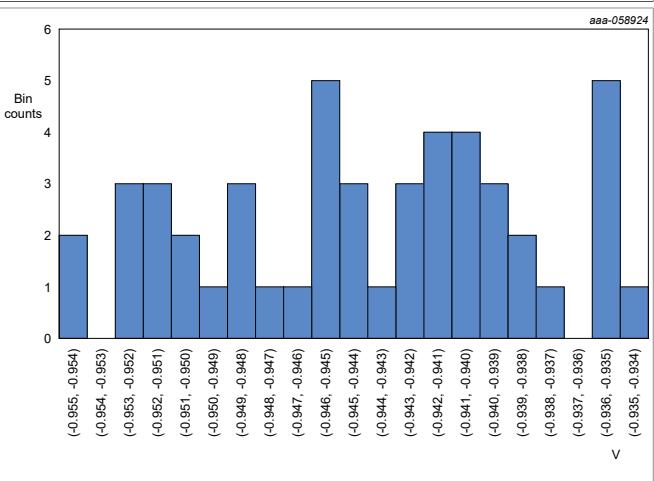

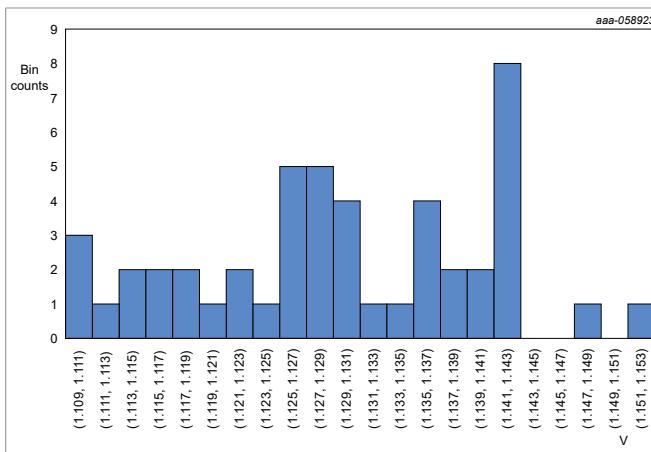

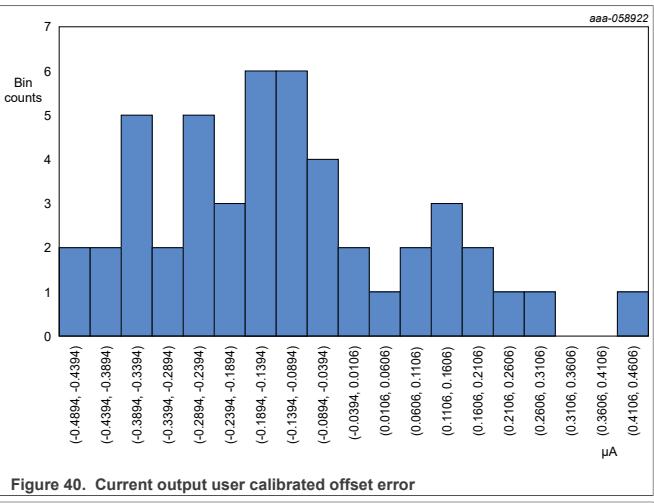

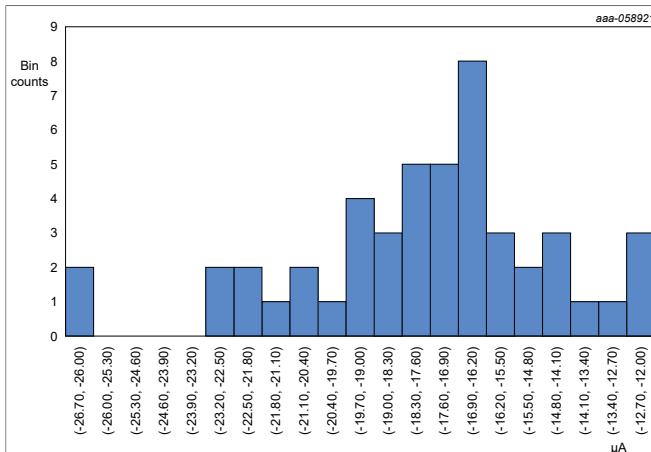

| 1                                                              | 1           | 1                | 1            |                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              |  |        |              |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |