# PTN3222EUK

## eUSB2 to USB2 redriver with 1.2 V IO

Rev. 1.1 — 1 December 2023

Product data sheet

# 1 General description

PTN3222 is a 1-port eUSB2 to USB2 redriver IC that performs translation between eUSB2 and USB2 signaling schemes. It is meant to be used in systems that have eUSB2 interface on one side and USB2 interface on the other side. It supports host repeater, device repeater or dual role repeater function.

PTN3222 implements Repeater mode (eUSB2 to USB2 redriver) and it supports Link Power management features. PTN3222 is targeted to be USB2 compliant and eUSB2 conformant. It supports all three speeds/data rates: Low Speed (1.5 Mbps), Full Speed (12 Mbps) and High Speed (480 Mbps).

PTN3222 provides a target I<sup>2</sup>C register interface to initialize the required functionality and features as per the platform application need. The I<sup>2</sup>C target address is selectable using a quaternary input pin (that selects one of the four addresses). The RST\_N pin is used to reset the IC without power cycling.

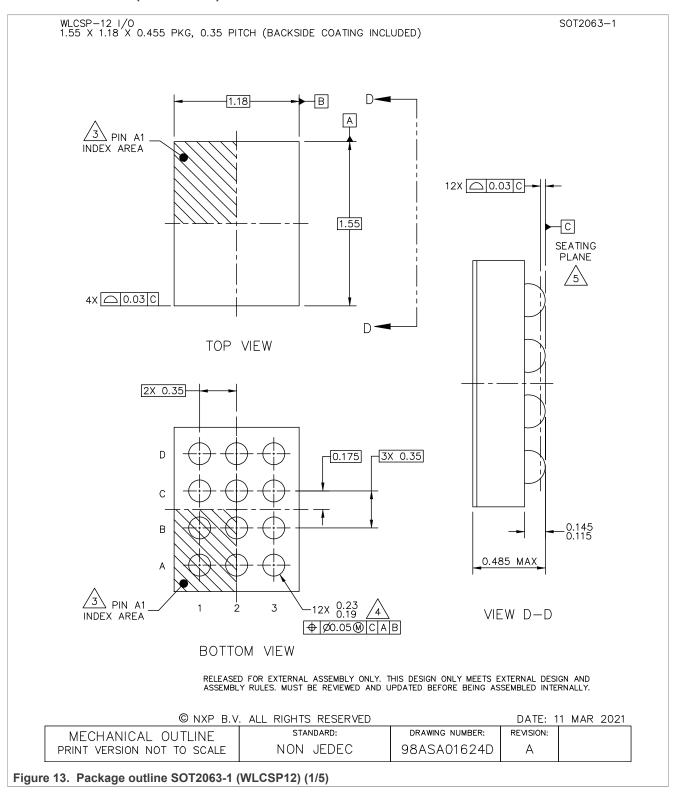

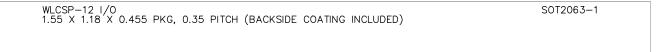

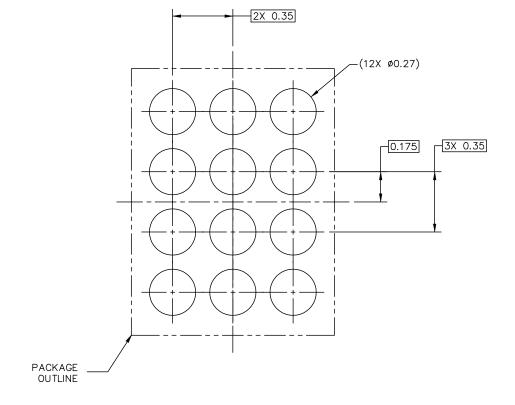

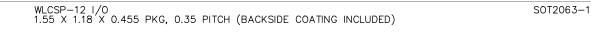

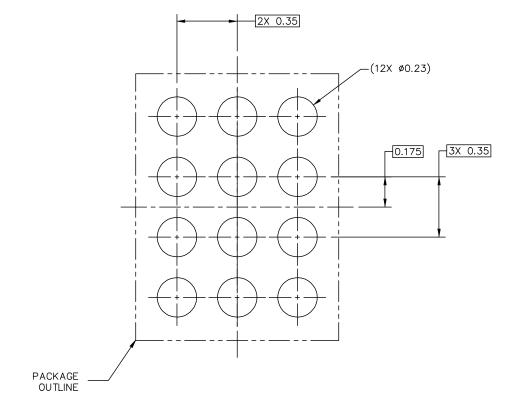

It is powered by two power supplies (VDD3V3, VDD1V8) and is available in a small thin WLCSP12 package (1.55 mm x 1.18 mm x 0.455 mm body, 0.35 mm pitch).

This product is meant for use in 1.2 V IO (SCL, SDA, RST N) applications only.

#### 2 Features and benefits

- 1-port eUSB2 to USB2 redriver functionality

- Conforms to USB2 specification along with relevant ECNs

- Conforms to eUSB2 specification v1.1

- · Supports host only repeater, device only repeater and dual mode repeater role

- Supports all USB2.0 data rates

- Low speed operation (1.5 Mbps)

- Full speed operation (12 Mbps)

- High speed operation (480 Mbps)

- Supports RAP accesses for a select set of register accesses

- Integrated and selectable pullup and pulldown resistors on both eUSB2 and USB2 ends

- · Signal Integrity (SI) configurability

- eUSB2 Tx de-emphasis, Rx equalization, Rx squelch threshold, Tx output swing

- USB2 HS disconnect detection threshold, Rx squelch threshold, Rx termination, Rx equalization, Tx deemphasis, Tx slew rate, Tx output swing

- Supports BC1.2 power provider CDP configuration capability in host mode

- · Low current consumption

- Supports eUSB2 and USB2 power management

- Implements Deep standby mode for lowest power consumption

- · Robustness features

- USB2 data pins tolerate 5.5 V (DC) for 24 hours

- USB2 data pins withstand short to GND for 24 hours

- USB2 data pins withstand collision on DP/DN pins due to faulty USB devices

- · GPIOs and high speed data pins are backpower safe

- I<sup>2</sup>C target interface supports standard mode, fast mode and fast mode plus

- I<sup>2</sup>C pins and RST N pins operate in 1.2 V IO domain (please refer to Section 12 for parametric details)

- Power supplies VDD3V3, VDD1V8

- ESD HBM 2 kV CDM 500 V

- Operating ambient temperature range -40 °C to +85 °C

- Available in WLCSP12 package

# 3 Applications

- eUSB2 to USB2 repeater function in platforms (e.g. hosts, devices, hubs, routers, protocol bridges, etc.) with Standard A/ Standard B/ Micro-B/USB Type-C connector scenarios

- Host only repeater

- Device only repeater

- Dual role repeater (as determined dynamically in the application)

# 4 Ordering information

#### Table 1. Ordering information

| Type number | Package | Package                                                                                                                             |           |  |  |  |  |  |  |

|-------------|---------|-------------------------------------------------------------------------------------------------------------------------------------|-----------|--|--|--|--|--|--|

|             | Name    | Description                                                                                                                         | Version   |  |  |  |  |  |  |

| PTN3222EUK  |         | WLCSP12, wafer level chip scale package, 12 terminals, 0.35 mm pitch, 1.55 mm x 1.18 mm x 0.455 mm body (backside coating included) | SOT2063-1 |  |  |  |  |  |  |

# 4.1 Ordering options

## Table 2. Ordering options

| Type number | Orderable part number | Package | <b>3</b>                                                | Minimum<br>order<br>quantity | Temperature                 |

|-------------|-----------------------|---------|---------------------------------------------------------|------------------------------|-----------------------------|

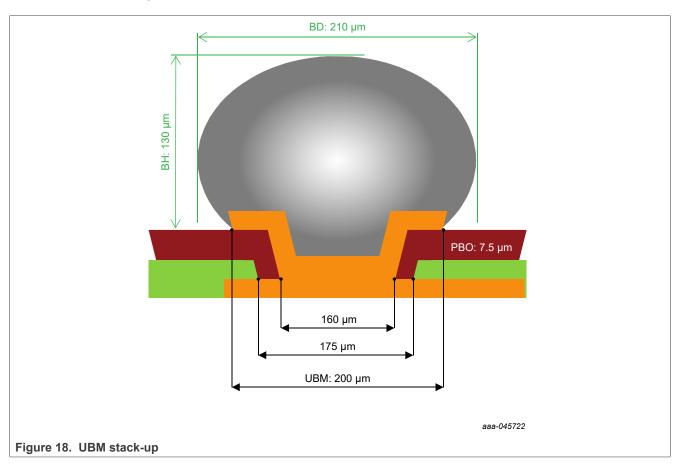

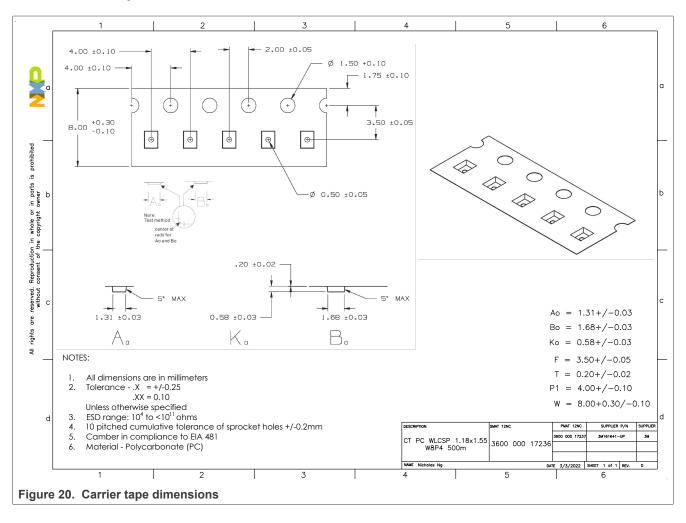

| PTN3222EUK  | PTN3222EUKZ           | WLCSP12 | Reel dry pack, SMD, 13" Q1 standard product orientation | 8000                         | $T_{amb}$ = -40 °C to 85 °C |

## 4.2 Top side marking

Table 3. Top side marking

| Line number | Character | Content                | Remarks                                    |

|-------------|-----------|------------------------|--------------------------------------------|

| Line A      | 1         | Pin 1 dot              | Pin 1 indication                           |

|             | 2-3       | Product life cycle     | Product status: • "2E": Production silicon |

| Line B      | 1-3       | Production information | Lot ID                                     |

| Line C      | 1-2       | Production information | Lot ID                                     |

|             | 3         | Production information | Wafer number                               |

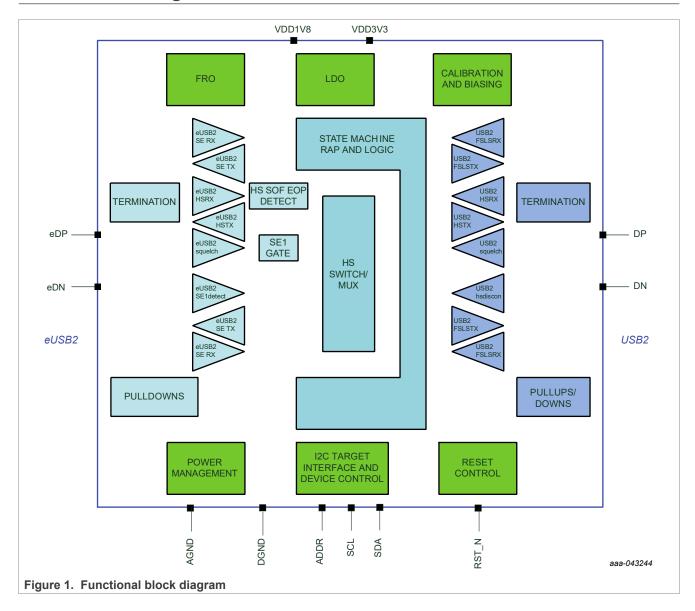

# 5 Functional diagram

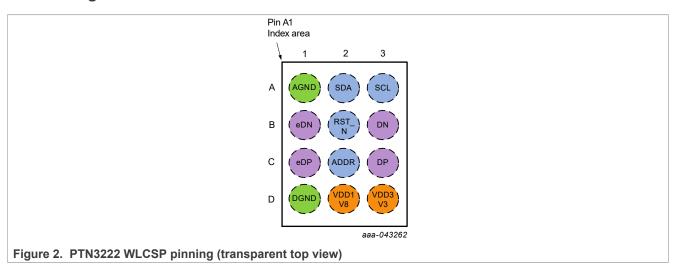

# 6 Pinning information

# 6.1 Pinning

# 6.2 Pin description

Table 4. Pin description

| Pin | Symbol | Direction | Pad power<br>domain | Туре                 | Description                                                                                                                                                                                                                          |

|-----|--------|-----------|---------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D1  | DGND   | OUT       |                     | Power                | Digital ground. This pin is connected to low noise ground plane and avoids long PCB traces                                                                                                                                           |

| D2  | VDD1V8 | IN        |                     | Power                | 1.8 V power supply. 0.47 µF and 33 pF decoupling capacitors are placed on this pin on the PCB                                                                                                                                        |

| D3  | VDD3V3 | IN        |                     | Power                | 3.3 V power supply. 0.47 µF and 33 pF decoupling capacitors are placed on this pin on the PCB                                                                                                                                        |

| C1  | eDP    | 10        | VDD1V8              | Analog input/output  | Positive terminal of eUSB2 analog transceiver interface                                                                                                                                                                              |

| C2  | ADDR   | IN        | VDD1V8              | Analog input         | Quaternary pin for I <sup>2</sup> C target address selection (sampled once after POR and when power supplies are stable and valid). The external pullup resistor shall be placed close enough to the decoupling capacitors of VDD1V8 |

| С3  | DP     | Ю         | VDD1V8, VDD3V3      | Analog input/output  | Positive terminal of USB2 analog transceiver interface DP pin has an internal 2 M $\Omega$ pulldown resistor enabled under all situations                                                                                            |

| B1  | eDN    | 10        | VDD1V8              | Analog input/output  | Negative terminal of eUSB2 analog transceiver interface                                                                                                                                                                              |

| B2  | RST_N  | IN        |                     | Digital input        | It is Active Low input signal meant to perform IC reset operation.  This pin needs an external 10 kΩ pullup resistor connected to VDD1V2                                                                                             |

| В3  | DN     | IO        | VDD1V8, VDD3V3      | Analog input/output  | Negative terminal of USB2 analog transceiver interface DN pin has an internal 2 M $\Omega$ pulldown resistor enabled under all situations                                                                                            |

| A1  | AGND   | OUT       |                     | Power                | Analog low noise ground. This pin should connect to PCB ground plane, avoid long PCB traces and not be routed near noisy circuits                                                                                                    |

| A2  | SDA    | Ю         | VDD1V8              | Digital input/output | I <sup>2</sup> C data input/output. There is no internal pull up resistor, and an external pull up resistor to I <sup>2</sup> C pullup voltage must be used on the PCB                                                               |

| A3  | SCL    | I         | VDD1V8              | Digital input        | I <sup>2</sup> C clock input. There is no internal pull up resistor, and an external pull up resistor to I <sup>2</sup> C pullup voltage must be used on the PCB                                                                     |

PTN3222EUK

All information provided in this document is subject to legal disclaimers.

# 7 Functional description

PTN3222 consists of the following major functions:

- · eUSB2 repeater

- BC1.2 support

- I<sup>2</sup>C interface

- · Reset schemes

#### 7.1 Reset

PTN3222 supports the following reset schemes:

- POR

- · Software reset

- RST N pin

When in reset, PTN3222's SCL and SDA IO pins are in high impedance state to prevent the I<sup>2</sup>C bus from being altered or corrupted in any way.

All three reset schemes clear I<sup>2</sup>C registers but Software reset and RST\_N pin do not reset digital circuity related to RST\_N pin function itself. PTN3222 remains in the mode specified in OTP after exiting reset. When in reset, PTN3222's SCL and SDA IO pins are in high impedance state such that the I<sup>2</sup>C bus is not altered or corrupted in any way.

## 7.2 Operating modes

PTN3222 has several operating modes: a specific operating mode is selected depending on repeater configuration, link and connection status. <u>Table 5</u> below gives a high level overview of the major building blocks that are kept powered in different modes.

Table 5. Status of design blocks in different power modes

| Power Mode                          | I <sup>2</sup> C interface | FS/LS front ends      | HS Front ends                  |

|-------------------------------------|----------------------------|-----------------------|--------------------------------|

| OFF                                 | OFF                        | OFF                   | OFF                            |

| Deep standby                        | ON                         | OFF                   | OFF                            |

| Connect Detect (Detached condition) | ON                         | ON (SE detector only) | OFF                            |

| L1 sleep                            | ON                         | ON (SE detector only) | HS OFF; only SE detector is ON |

| L2 suspend                          | ON                         | ON (SE detector only) | HS OFF; only SE detector is ON |

| Active LS/FS                        | ON                         | ON                    | OFF                            |

| Active HS                           | ON                         | OFF                   | ON                             |

#### 7.3 eUSB2 repeater

This subsystem includes eUSB2 analog front end circuitry, repeater state machine, USB2 analog front end circuitry and the associated power management circuits. The USB2 DP/DN pin have internal 2 M $\Omega$  pulldown resistors enabled under all situations.

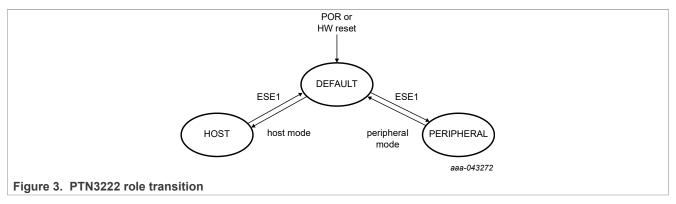

PTN3222 is designed to function as a host repeater or a peripheral repeater. <u>Figure 3</u> illustrates the role transition and associated arcs that enable role change.

PTN3222EUK

All information provided in this document is subject to legal disclaimers.

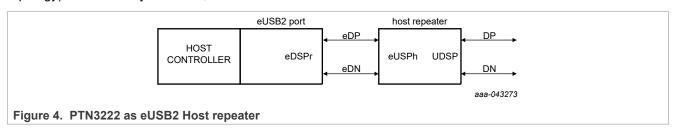

Figure 4 illustrates the eUSB2 Host repeater usage in a typical Host platform application.

On one side, the repeater interfaces with USB2 peripheral (that is either plugged in directly or via cable/channel topology) and on the system side, it interfaces with host controller w/eUSB2 PHY.

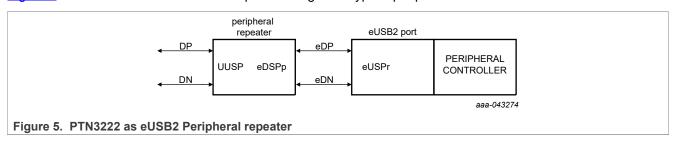

Figure 5 illustrates the eUSB2 Device repeater usage in a typical peripheral environment.

PTN3222 implements aggressive power management to optimize on overall power consumption under the various operating modes. It supports USB Link Power Management and supports L1 and L2 power states.

PTN3222 supports RAP – allowing customer facing registers only. The type of access is controlled via an I<sup>2</sup>C register. There is no built-in arbitration support available if and when same register is being accessed through RAP commands and I<sup>2</sup>C interface. The system application is expected not to issue simultaneous accesses, avoid register overwrites leading to incorrect behavior and response from PTN3222.

PTN3222 accepts RAP messages at any time even though host is expected to issue RAP messages only during initialization. In case, if the host would use RAP messages to read status register(s) or update any control register(s), PTN3222 does not inhibit or put limits on RAP messages as long as it is in the mode wherein customer I<sup>2</sup>C registers are accessible.

## 7.3.1 Over-Voltage Protection on USB2 DP/DN pins

PTN3222 implements Over Voltage Protection (OVP) circuitry, which activates whenever an OV condition occurs on USB2 DP/DN pins, PTN3222 operates autonomously without host software intervention. The following describes a possible sequence of steps that may occur due to OV event:

1. PTN3222 checks DP/DN pin(s) for over voltage condition that is higher than V<sub>OVP,Th</sub> (Low to High Threshold case) and it shuts down the USB2 analog IO as long as the event persists

PTN3222EUK

All information provided in this document is subject to legal disclaimers.

- 2. PTN3222 enables USB2 analog IO path once the pin voltage falls below V<sub>OVP,Th</sub> (High to Low Threshold case)

- 3. The SoC host and eUSB2 redriver would lose communication with the USB2 entity since the analog path has been disabled

- 4. So, the SoC host may try the following options to reestablish the link

- a. issue CM.Reset in an attempt to issue a USB Bus Reset or,

- b. issue Port reset to the local redriver and also toggle VBUS to re-establish the connection and restart the data transport.

Note that option (a) may not be successful depending on the nature of the fault but is the fastest and least aggressive error recovery method. Use of Port Reset and toggling of VBUS are guaranteed to work, but comes with a downside of longer time duration to reestablish the link.

#### 7.4 BC1.2 support

PTN3222 has a built-in support for enabling CDP (Charging Downstream Port) feature that allows a mobile device to detect and charge at higher current from the host platform. For the BC1.2 support, this IC implements a controlled voltage source that can be enabled on USB2 DN pin via an I<sup>2</sup>C register bit. The host processor can enable this feature via I<sup>2</sup>C during USB disconnect condition and the PTN3222 can autonomously disable this on a USB connect event and reset this I<sup>2</sup>C configuration bit.

This feature is expected to be applied when in host repeater mode only. However, the PTN3222 does not inhibit enabling of this feature in device repeater mode.

# 7.5 I<sup>2</sup>C operation

PTN3222 is an I<sup>2</sup>C target only device, and it responds to I<sup>2</sup>C commands in any operating mode as long as VDD3V3/VDD1V8 supplies are available. PTN3222 does not support clock stretching but it tolerates other I<sup>2</sup>C targets performing clock stretching under the legal conditions defined by [1]. Also, it does not support I<sup>2</sup>C General call address (and therefore does not issue an acknowledgement too), I<sup>2</sup>C Software reset command nor 10-bit addressing. It acknowledges all 128 register offset addresses though there are certain undefined/reserved locations as indicated in the register map.

Each I<sup>2</sup>C operation involving writing to or reading from one or more consecutive registers is referred to as a transaction. Consecutive registers are defined as a series of incrementing register addresses, regardless of whether a given address has a definition in the register map.

A transaction may be a part of a series of transactions addressed to multiple different targets or to the same target repeatedly with different register address offsets, with each transaction separated by repeated-START conditions. PTN3222 does not inhibit other types of transactions as prescribed in I<sup>2</sup>C specification.

Register address aliasing is not supported in PTN3222. When read or write transactions with multiple consecutive registers are performed, the register address rolls over to 0x00 once the maximum register offset of 0xFF is reached.

When an undefined or invalid register address is being addressed for read or write operation, PTN3222 acknowledges the I<sup>2</sup>C transaction, but returns 0xFF for a read operation, or takes no action for a write operation.

# 7.5.1 I<sup>2</sup>C target address

PTN3222's 7-bit I<sup>2</sup>C target address is given in <u>Table 6</u>. Bits 3 and 4 can take one of the four possible values based on the quaternary address selection pin (ADDR).

PTN3222EUK

Table 6. PTN3222 target address definition

| ADDR pin configuration                                         | Bit 7 | Bit 6 | Bit 5 | AI    | DDR   | Bit 2 | Bit 1 | Bit 0 |

|----------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

|                                                                |       |       |       | Bit 4 | Bit 3 |       |       |       |

| Connected to 1.8 V supply directly                             | 1     | 0     | 0     | 0     | 0     | 1     | 1     | R/W   |

| Connected to 1.8 V supply via 56 kΩ (+/-10 %) pull up          | 1     | 0     | 0     | 0     | 1     | 1     | 1     | R/W   |

| Connected to 1.8 V supply via 200 k $\Omega$ (+/-10 %) pull up | 1     | 0     | 0     | 1     | 0     | 1     | 1     | R/W   |

| Connected to GND directly                                      | 1     | 0     | 0     | 1     | 1     | 1     | 1     | R/W   |

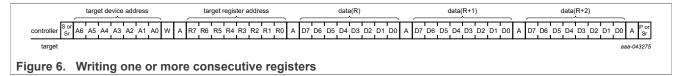

#### 7.5.2 Example of writing one or more registers

PTN3222 recognizes the following procedure as a request to write to one or more registers:

- 1. I<sup>2</sup>C controller asserts START condition or repeated-START condition

- 2. Controller addresses PTN3222 target interface with R/W bit set as "Write"

- 3. Target acknowledges the request by asserting an ACK

- 4. Controller writes the desired starting register address

- 5. Target acknowledges the register address with ACK, even if register address is not part of the defined register map

- 6. Controller writes the data for that register address and the target updates the register value once all 8 bits of data have been written

- 7. Target acknowledges the data with an ACK

- 8. If the controller wishes to write to the next consecutive register address, it supplies another data byte, which the target ACKs. The controller can continue writing data bytes for consecutive registers. If the controller writes to more consecutive registers than what exists in the register map, the target discards the extra data bytes, but ACKs for each such write

When the controller has finished writing the desired register(s), it issues either a STOP condition or a repeated-START condition.

<u>Figure 6</u> provides an illustrative example where the controller chooses to write to three consecutive registers starting with register "R".

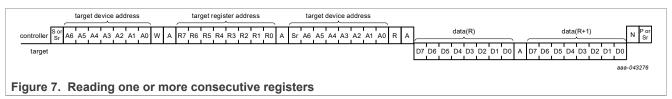

#### 7.5.3 Example of reading one or more registers

The target recognizes the following procedure as a request to read one or more registers:

- 1. Controller asserts START condition or repeated-START condition

- 2. Controller addresses PTN3222's target address with R/W bit set as "Write"

- 3. Target acknowledges the request by asserting ACK

- 4. Controller writes the desired starting register address

- 5. Target acknowledges the register address with ACK, even if the register address is not part of the defined register map

- 6. Controller issues a repeated-START condition

- 7. Controller addresses PTN3222's target address with R/W bit set as "Read"

PTN3222EUK

All information provided in this document is subject to legal disclaimers.

- 8. In the following clock pulses, the target clocks out the value of the requested register

- 9. If controller wishes to read the next consecutive register, it issues an ACK and then provides another set of clock pulses, whereby the target supplies the value of the next register. As long as the controller continues to issue ACK and supply additional clock pulses, the target continues to supply the value of consecutive registers. If the controller attempts to read consecutive registers that do not exist in the defined register space, the target can return undefined data value of 0xFF.

- 10. When the controller does not wish to read additional consecutive registers, it supplies a NACK in response to the final register value it wishes to read and then issues a STOP or repeated-START condition.

<u>Figure 7</u> provides an illustrative example where the controller chooses to read from two consecutive registers starting with register "R".

# 8 System application

#### 8.1 Use cases

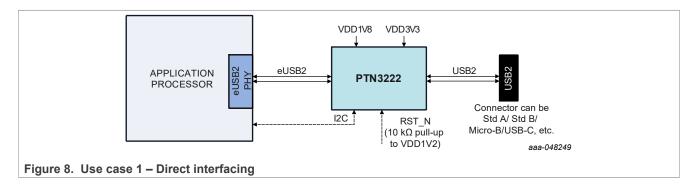

PTN3222 is targeted to be used in various USB interface application cases. It interfaces to a host or device controller with eUSB2 PHY interface and on the other side, it interfaces directly to a connector/cable topology or another interface IC. Different connector configurations are possible: custom, USB Standard A/Standard B, USB Micro-B, USB Type-C, etc. For all use cases, it is not necessary for the host to initialize the I<sup>2</sup>C registers after POR or reset event. On the contrary, PTN3222 functions without any I<sup>2</sup>C configuration by relying on registers getting initialized after POR event.

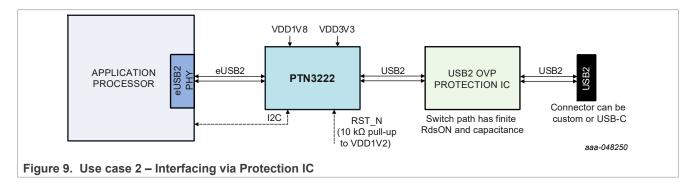

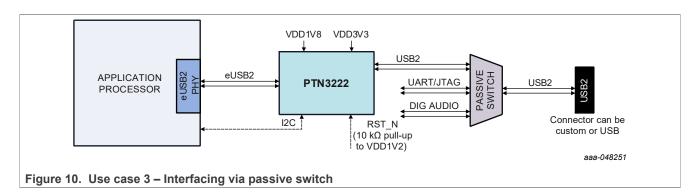

A few use case illustrations are shown in <u>Figure 8</u> through <u>Figure 10</u>; these figures do not capture all components (supply decoupling capacitors, ESD, CMF, etc.) in the channel topology.

#### 1. Direct interface to connector

This connectivity scheme is a straightforward topology and it may be relevant for generic IOT and certain computing applications. In certain applications, I<sup>2</sup>C interface may not be connected and the repeater is expected to start operating after POR based on POR/default register settings.

#### 2. Interface via USB protection IC

This connectivity scheme is relevant for applications where there is a risk/chance of high voltage appearing on the USB data pins (e.g. USB-C). In certain applications, I<sup>2</sup>C interface may not be connected and the repeater is expected to start operating after POR based on POR/default register settings. Care must be

PTN3222EUK

All information provided in this document is subject to legal disclaimers

taken to select suitable protection IC that has certain USB2 signal attenuation/Rdson. Also, the default power-up scenario must be analyzed.

3. Interface to connector via passive signal switch

This connectivity scheme provides the option to switch various debug and communication signals on to the same connector. In certain applications, I<sup>2</sup>C interface may not be connected and the repeater is expected to start operating after POR based on POR/default register settings. The passive signal switch must be selected to ensure low signal attenuation and also the power-up scenario must be carefully analyzed.

#### 8.2 Power supply requirement

PTN3222 requires two power supplies (VDD3V3 and VDD1V8) to operate. It does not function until both supplies have ramped up and reached valid operating range. There is no specific power on or off sequencing requirement. In addition, the two supplies can follow different ramp-up and ramp down rates. The supply ramp limits are specified in Section 11.

PTN3222 does not suffer from backpower issue (VDD node getting powered via a non-power pin).

The power supply decoupling capacitors shall be soldered close to power pins.

#### 8.3 Ground requirement

PTN3222 has two ground pins, AGND and DGND.

Both pins provide connection to GND plane with low ground noise in the application PCB.

PTN3222EUK

All information provided in this document is subject to legal disclaimers.

# 8.4 ESD requirements

PTN3222 supports 2 kV HBM and 500 V CDM on all pins. To achieve system level ESD protection (e.g. IEC61000-4-2 Level 4 8 kV contact discharge, 15 kV air discharge) on DP/DN pins, dedicated and matched ESD diodes shall be used near the connector. Matching of diodes is important to minimize DP/DN skew.

# 9 Register set

The device is controlled and monitored by registers accessible via the I<sup>2</sup>C bus. All registers can be accessed in standard mode or fast mode using single or sequential reads or writes. Register bit field types are defined in Table 7.

Table 7. Register type definitions

| Access Type     | Description                                                                                                                                                   |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RW              | Bit field can be read from and written to                                                                                                                     |

| RO              | Bit field value can only be read                                                                                                                              |

| WO              | Bit field value is write only. Reading value has no meaning, and results in no action being taken                                                             |

| RAZ             | Bit field contents are read as zero. Writes do not have any effect                                                                                            |

| R/W1, W0 Ignore | Bit field value is readable, and writing 'b1 to each bit in the bit field sets value to 'b1. Writing 'b0 to a this bit field results in no action being taken |

# 9.1 Register overview

Table 8 lists all the registers used for PTN3222. Default POR values of registers are also shown in this table.

Table 8. Register overview

| Address        | Register Name                        | Access | RESET |                                | Default        |              |                              |                              |             |                           |             |                      |                   |

|----------------|--------------------------------------|--------|-------|--------------------------------|----------------|--------------|------------------------------|------------------------------|-------------|---------------------------|-------------|----------------------|-------------------|

|                |                                      |        | Re    | Software<br>Reset (or<br>RST_N | Value<br>(Hex) | 7            | 6                            | 5                            | 4           | 3                         | 2           | 1                    | 0                 |

| 0x00           | RESERVED                             | RAZ    |       |                                | 00             |              |                              |                              |             |                           |             |                      |                   |

| 0x01           | RESET<br>CONTROL                     | RW     | •     |                                | 00             |              |                              |                              |             |                           |             |                      | Software<br>Reset |

| 0x02           | LINK<br>CONTROL 1                    | RW     | •     | •                              | 00             | Speed contro | ol                           | Role control                 |             |                           | Operational | mode                 |                   |

| 0x03           | LINK<br>CONTROL 2                    | RW     | •     | •                              | 00             |              |                              |                              |             |                           |             |                      | Force<br>ESE1     |

| 0x04           | eUSB2 RX<br>CONTROL                  | RW     | •     | •                              | 20             |              |                              | eUSB2 HS R<br>detection thre |             |                           | eUSB2 HS    | Rx equalization      | on                |

| 0x05           | eUSB2 TX<br>CONTROL                  | RW     | •     | •                              | 10             |              |                              | eUSB2 HS T<br>swing          | x output    |                           |             | eUSB2 HS<br>emphasis | Tx De-            |

| 0x06           | USB2 RX<br>CONTROL                   | RW     | •     | •                              | 40             |              | USB2 Rx so                   | quelch detectior             | threshold   |                           | USB2 HS R   | x equalizatior       | 1                 |

| 0x07           | USB2 TX<br>CONTROL 1                 | RW     | •     | •                              | 00             |              |                              | USB2 HS Tx<br>emphasis bit   |             | on USB2 HS Tx De-emphasis |             | is                   |                   |

| 0x08           | USB2 TX<br>CONTROL 2                 | RW     | •     | •                              | 62             |              | USB2 FS<br>rise/fall<br>time | USB2 HS ris                  | e/fall time |                           | USB2 HS T   | x output swin        | 9                 |

| 0x09           | USB2 HS TER<br>MINATION              | RW     | •     | •                              | 02             |              |                              |                              |             |                           | USB2 HS te  | ermination cor       | ntrol             |

| 0x0A           | USB2 HS DIS<br>CONNECT THR<br>ESHOLD | RW     | •     | •                              | 00             |              |                              |                              |             |                           |             | USB2 HS detection th |                   |

| 0x0B           | RESERVED                             | RO     |       |                                | XX             |              |                              |                              |             |                           |             |                      |                   |

| 0x0D           | RAP_Signature                        | RW     |       |                                | 00             | RAP_Signat   | ure                          | '                            | '           | 1                         | '           | -                    | '                 |

| 0x0E           | VDX_<br>CONTROL                      | RW     | •     | •                              | 00             |              |                              |                              |             |                           |             |                      | VDx_<br>enable    |

| 0x0F           | DEVICE<br>STATUS                     | RO     | •     | •                              |                |              |                              |                              |             | Speed of or<br>status     | peration    | Repeater s           | tatus             |

| 0x10           | LINK STATUS                          | RO     | •     | •                              |                |              |                              |                              |             |                           | Device and  | Link status          |                   |

| 0x11 -<br>0x12 | RESERVED                             | RAZ    |       |                                | xx             |              |                              |                              |             |                           |             |                      |                   |

| 0x13           | REVISION_ID                          | RO     |       |                                | A2             | BASE = b'10  | 10                           |                              |             | METAL_= b                 | 0010        |                      |                   |

| 0x14           | CHIP_ID_0                            | RO     |       |                                | 22             | CHIP_ID[7:0  | ]=0x22                       |                              |             |                           |             |                      |                   |

| 0x15           | CHIP_ID_1                            | RO     |       |                                | 32             | CHIP_ID[15:  | 8]=0x32                      |                              |             |                           |             |                      |                   |

| 0x16           | CHIP_ID_2                            | RO     |       |                                | 02             | p,0000       |                              |                              |             |                           |             | b'11                 |                   |

|                | RESERVED                             | RO     |       |                                | XX             | Reserved re  | gister space                 |                              |             |                           | -           |                      |                   |

# 9.2 I<sup>2</sup>C registers and descriptions

# 9.2.1 Functional registers

The offset addresses with defined bit definitions are meant for functional registers, and can be accessed by the I<sup>2</sup>C controller at any time after POR. For normal operation, these registers are sufficient to setup the IC to known working conditions. Customers are advised not to write reserved values into the register bit fields. Read from the reserved bit field(s) need not match with what's written. Functional behavior is not guaranteed if such an operation is performed.

Table 9. Register 0x00 - Reserved

| Regist | er offset | Register Name |         |            | Register Description |

|--------|-----------|---------------|---------|------------|----------------------|

| 0x00   |           | RESEF         | ESERVED |            |                      |

| Bit    | Bit Name  |               | R/W     | Reset      | Description          |

| 7:0    | RSVD      |               | RAZ     | p,00000000 | Reserved             |

#### Table 10. Register 0x01 - RESET CONTROL

| Regist | egister offset Register Name |       |         | Register Description |                                                                                                                                                                                                                                         |

|--------|------------------------------|-------|---------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x01   |                              | Reset | Control |                      | This register is meant to initiate reset of the chip via I <sup>2</sup> C write                                                                                                                                                         |

| Bit    | Bit Name                     |       | R/W     | Reset                | Description                                                                                                                                                                                                                             |

| 7:1    | RSVD                         |       | RAZ     | p,0000000            | Reserved                                                                                                                                                                                                                                |

| 0      | Software Reset               |       | R/W     | b'0                  | This is a Self-clearing bit. The host writes '1' to this bit to initiate software reset and this bit automatically clears to '0'.  All R/W registers are reset to POR settings.  Writing '0' does not have any effect. Reads return '0' |

# Table 11. Register 0x02 - LINK CONTROL 1

| Registe | r offset      | Register Name  | )     | Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------|---------------|----------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x02    |               | Link Control 1 |       | This register is meant to force the repeater role and speed of operation to fixed settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Bit     | Bit Name      | R/W            | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7:6     | Speed control | RW             | b'00  | The bitfield determines the POR setting of USB2 speed: 00– Manage the speed via Auto negotiation 01– LS/FS only 10-11- Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5:4     | Role control  | RW             | p,00  | Determines the redriver role  00 – Dual role  Support both host and device eUSB2 Port Configuration negotiation. This is the expected normal operating setting managed via Host eUSB2 exchanges.  01 - Force Host role  When bits are '01', it forces the repeater into USB Host role irrespective of any configuration command getting received via eUSB2. But the repeater would acknowledge the configuration message from the host.  10- Force Device role  When the bits are '10', it forces the repeater into USB Device/Peripheral role irrespective of any configuration command getting received via eUSB2. But the repeater would acknowledge the configuration message from the host.  11- Reserved  Forced host/device role setting is used in conjunction only with setting '2' of Link Control 2[2:0] bits |

| 3       | RSVD          | RAZ            | b'0   | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

Table 11. Register 0x02 - LINK CONTROL 1...continued

| Register o | ffset          | Regist | er Name |       | Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------|----------------|--------|---------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2:0 C      | perational Mod | e      | RW      | p,000 | The bits set the operational mode of the repeater 0=Auto negotiation on the link (mode determined via control messages and link negotiation)  1= Deep standby mode (eUSB2 pins are pulled down, USB2 pins are held in weak pulldown condition and I²C register contents are preserved)  2 - Connect.Detect state. Used for force the repeater into its Connect.Detect state (refer to eUSB specification) This is acted upon only at the time the write occurs to this register. If an overriding condition is present, such as RST_N=0, then writing to this register with this setting is ignored, even when the overriding condition goes away  Note that in this case Role Control field (in register 0x02) must have only a single bit set. Those bits are used to tell the repeater which role to jump into - This command places the repeater into the appropriate Connect.Detect state (based on specified role in Role Control). After the state transition occurs, the repeater automatically reacts from there as appropriate to the eUSB/USB2 bus conditions.  3 - Compliance Mode (HS L0 condition). This is equivalent to the reception of the Control Message CM.Test. It allows the system to force the repeater into HS.L0 state. The role is defined by the Role Control bits. Note that in this case, Role Control setting must have only a single bit set. If both or neither bit is set, then this command is ignored |

Table 12. Register 0x03 - LINK CONTROL 2

| Regis | ster offset | Register Name  |     |           | Register Description                                                                                                                                                                                                                                                                                                                          |  |  |

|-------|-------------|----------------|-----|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 0x03  |             | Link Control 2 |     |           | This register programs specific feature of the repeater                                                                                                                                                                                                                                                                                       |  |  |

| Bit   | Bit Name    | -              | R/W | Reset     | Description                                                                                                                                                                                                                                                                                                                                   |  |  |

| 7:1   | 7:1 RSVD    |                | RAZ | p,0000000 | Reserved                                                                                                                                                                                                                                                                                                                                      |  |  |

| 0     | Force ESE1  |                | RW  | b'0       | Bit to force Extended SE1 signaling 0 => No action 1 => Self Clearing bit. When written to 1, Repeater generates extended SE1 onto the eUSB pins.  Normally, only the Host Repeater performs this action upon a HS disconnect detection. But this feature allows the system to force an extended SE1 as needed via I <sup>2</sup> C interface |  |  |

Table 13. Register 0x04 - eUSB2 RX CONTROL

| Regis | ster offset                             | Register | r Name           |       | Register Description                                                                                                                                                                                                                                                                                     |  |  |

|-------|-----------------------------------------|----------|------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 0x04  | 0x04                                    |          | eUSB2 Rx Control |       | This register programs the eUSB2 Rx equalization and squelch detection threshold settings                                                                                                                                                                                                                |  |  |

| Bit   | Bit Name                                |          | R/W              | Reset | Description                                                                                                                                                                                                                                                                                              |  |  |

| 7:6   | RSVD                                    |          | RAZ              | b'00  | Reserved                                                                                                                                                                                                                                                                                                 |  |  |

| 5:4   | eUSB2 HS Rx Squelch detection threshold |          |                  |       | The bits determine the squelch detector (Low to High transition) threshold level for HS signaling on eUSB2 pins 00 = 50 mV 01 = 65 mV 10 = 85 mV 11 = 95 mV All settings are within +/-25 mV of nominal value mentioned above Squelch detector implements hysteresis of 10 mV to improve noise immunity. |  |  |

| 3     | RSVD                                    |          | RAZ              | b'0   | Reserved                                                                                                                                                                                                                                                                                                 |  |  |

| 2:0   | eUSB2 HS Rx<br>equalization             |          | RW               | p.000 | The bits determine the nominal eUSB2 receive equalization gain (@ 240 MHz) with respect to DC gain. All settings are within +/-1 dB of nominal value mentioned below 000 = 0 dB 001 = 1 dB 010 = 2 dB 011 = 3 dB 100 = 4 dB 101 to 111 = Reserved                                                        |  |  |

Table 14. Register 0x05 – eUSB2 TX CONTROL

| Regis | ster offset                 | Regis | ter Nam  | е     | Register Description                                                                                                                                                                                                             |  |  |

|-------|-----------------------------|-------|----------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 0x05  | 0x05                        |       | 2 Tx Con | trol  | This register configures the Transmit side settings – output signal swing and de-emphasis level on eUSB2 side                                                                                                                    |  |  |

| Bit   | Bit Name                    |       | R/W      | Reset | Description                                                                                                                                                                                                                      |  |  |

| 7:6   | RSVD                        |       | RAZ      | b'00  | Reserved                                                                                                                                                                                                                         |  |  |

| 5:4   | eUSB2 HS Tx output<br>swing |       | RW       | b'01  | The bits set the output signal swing for HS signaling on eUSB2 Tx side (when the interface is terminated)  00 = 180 mV  01 = 200 mV  10 = 220 mV  11 = 240 mV  All settings are within +/-40 mV of nominal value mentioned above |  |  |

| 3:2   | RSVD                        |       | RAZ      | b'00  | Reserved                                                                                                                                                                                                                         |  |  |

| 1:0   | eUSB2 HS Tx De-<br>emphasis |       | RW       | p,00  | The bits determine the Tx de-emphasis (nominal) level for HS signaling on eUSB2 pins. The de-emphasis duration is between 0.75 to 1 HS bit time.  00 = 0 dB  01 = 1 dB  10 = 2 dB                                                |  |  |

PTN3222EUK

Product data sheet

All information provided in this document is subject to legal disclaimers.

Table 14. Register 0x05 - eUSB2 TX CONTROL...continued

| Register offset | Register Name | Register Description                             |                                 |

|-----------------|---------------|--------------------------------------------------|---------------------------------|

|                 |               | 11 = 3 dB                                        |                                 |

|                 |               | All settings other than '00' are mentioned below | within +/-1 dB of nominal value |

# Table 15. Register 0x06 – USB2 RX CONTROL

| Regis | ter offset                             | Register        | Name |       | Register Description                                                                                                                                                                                                                                                                                                                                                                           |

|-------|----------------------------------------|-----------------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x06  |                                        | USB2 Rx Control |      |       | The register programs the Rx equalization and squelch detection threshold levels on USB2 pins (applicable for HS signaling only)                                                                                                                                                                                                                                                               |

| Bit   | Bit Name                               |                 | R/W  | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                    |

| 7     | RSVD                                   |                 | RAZ  | b'0   | Reserved                                                                                                                                                                                                                                                                                                                                                                                       |

| 6:4   | USB2 HS Rx squelch detection threshold |                 | RW   | b'100 | The 3 bits determine the squelch detector (low to high transition) threshold level for HS signaling at USB2 pins 000 = Reserved; not for use 001 = 65 mV 010 = 85 mV 011 = 95 mV 100 = 110 mV 101 = 125 mV 110 = 140 mV 111 = 155 mV 111 = 155 mV All settings are within +/-25 mV of nominal value mentioned above Squelch detector implements hysteresis of 10 mV to improve noise immunity. |

| 3     | RSVD                                   |                 | RAZ  | b'0   | Reserved                                                                                                                                                                                                                                                                                                                                                                                       |

| 2:0   | USB2 HS Rx equalization                |                 | RW   | p,000 | The 3 bits determine the nominal USB2 receive equalization gain (@ 240 MHz) with respect to DC gain. All settings are within +/-1 dB of nominal value mentioned below 000 = 0 dB 001 = 1 dB 010 = 2 dB 011 = 3 dB 100 = 4 dB 101 to 111 = Reserved                                                                                                                                             |

Table 16. Register 0x07 - USB2 TX CONTROL 1

| Regis | ster offset                             | Regist            | ter Name | 9     | Register Description                                                                                                                                                                                                                               |

|-------|-----------------------------------------|-------------------|----------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x07  |                                         | USB2 Tx Control 1 |          |       | This register configures the Transmit side settings – output signal swing and de-emphasis level on USB2 side                                                                                                                                       |

| Bit   | Bit Name                                |                   | R/W      | Reset | Description                                                                                                                                                                                                                                        |

| 7:6   | RSVD                                    |                   | RAZ      | b'00  | Reserved                                                                                                                                                                                                                                           |

| 5:4   | USB2 HS Tx De-<br>emphasis bit duration |                   | RW       | b'00  | The bits set the de-emphasis bit time (UI) for HS signaling on USB2  Tx side  00 = 0  01 = 0.5UI  10 = 0.8UI  11 = Reserved  All settings are within +/-0.2UI of nominal value mentioned above                                                     |

| 3     | RSVD                                    |                   | RAZ      | b'0   | Reserved                                                                                                                                                                                                                                           |

| 2:0   | USB2 HS Tx De-<br>emphasis              |                   | RW       | b'000 | The bits determine the Tx de-emphasis (nominal) level for HS signaling on USB2 pins 000 = 0 dB 001 = 1 dB 010 = 2 dB 011 = 3 dB 100 = 4 dB 101 = 5 dB 110 = 6 dB All settings other than '000' are within +/-1 dB of nominal value mentioned above |

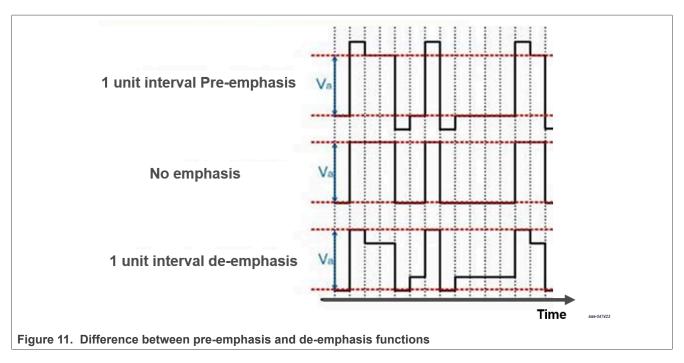

PTN3222 implements de-emphasis feature for channel loss compensation of high frequency content of both eUSB2 and USB2 signals.

Figure 11 illustrates the difference between pre-emphasis and de-emphasis functions.

With de-emphasis, when a steady pattern of 0s or 1s is being redriven, the transmit signal swing is reduced as per de-emphasis level and for an alternating pattern of 0s and 1s, the full signal swing is transmitted as per transmit signal swing level.

On the other hand, with pre-emphasis function, the full signal amplitude is retained when a steady pattern of 0s or 1s is being redriven and for an alternating pattern of 0s and 1s, the transmit signal swing is boosted as per pre-emphasis level.

The de-emphasis settings map to specific output current drive level as illustrated in <u>Table 17</u>. The current drive level is with reference to 17.78 mA current considering 45  $\Omega$  terminations at both ends of the connection and 400 mV output swing level.

Table 17. De-emphasis level to USB2 Tx output swing level

| USB2 Tx De-                                                | emphasi | s = 0.8UI (ty               | ypical)                             |                             |                                     |                             |                                     |                             |                                     |                             |                                     |                             |                                     |                             |                                     |

|------------------------------------------------------------|---------|-----------------------------|-------------------------------------|-----------------------------|-------------------------------------|-----------------------------|-------------------------------------|-----------------------------|-------------------------------------|-----------------------------|-------------------------------------|-----------------------------|-------------------------------------|-----------------------------|-------------------------------------|

| USB2 Tx output<br>swing Non-<br>transition Voltage<br>(mV) |         |                             |                                     | Tx De-emphasis setting = 1  |                                     | Tx De-emphasis setting = 2  |                                     | Tx De-emphasis setting = 3  |                                     | Tx De-emphasis setting = 4  |                                     | Tx De-emphasis setting = 5  |                                     | Tx De-emphasis setting = 6  |                                     |

|                                                            |         | Transition<br>level<br>(mV) | Non-<br>Transition<br>level<br>(mV) |

| Setting= 0                                                 | 350     | 352                         | 352                                 | 347                         | 304                                 | 347                         | 270                                 | 347                         | 237                                 | 347                         | 212                                 | 347                         | 194                                 | 340                         | 169                                 |

| Setting= 1                                                 | 400     | 399                         | 399                                 | 394                         | 344                                 | 394                         | 309                                 | 390                         | 267                                 | 390                         | 239                                 | 390                         | 219                                 | 385                         | 190                                 |

| Setting= 2                                                 | 450     | 451                         | 451                                 | 447                         | 388                                 | 447                         | 352                                 | 442                         | 305                                 | 442                         | 279                                 | 442                         | 244                                 | 442                         | 220                                 |

| Setting= 3                                                 | 500     | 498                         | 498                                 | 492                         | 434                                 | 492                         | 390                                 | 487                         | 337                                 | 487                         | 305                                 | 487                         | 269                                 | 487                         | 244                                 |

| Setting= 4                                                 | 550     | 551                         | 551                                 | 546                         | 473                                 | 544                         | 427                                 | 544                         | 375                                 | 544                         | 337                                 | 538                         | 301                                 | 538                         | 269                                 |

| Setting= 5                                                 | 600     | 600                         | 600                                 | 595                         | 520                                 | 595                         | 469                                 | 595                         | 416                                 | 584                         | 366                                 | 584                         | 330                                 | 580                         | 295                                 |

| Setting= 6                                                 | 650     | 656                         | 656                                 | 649                         | 566                                 | 645                         | 509                                 | 645                         | 454                                 | 634                         | 398                                 | 634                         | 355                                 | 618                         | 310                                 |

| Setting= 7                                                 | 700     | 703                         | 703                                 | 702                         | 613                                 | 692                         | 537                                 | 680                         | 474                                 | 680                         | 423                                 | 675                         | 372                                 | 675                         | 344                                 |

Table 18. Register 0x08 – USB2 TX CONTROL 2

| Regis | ster offset            | Regist | er Name   | Э     | Register Description                                                                                                                                                                                                                                                                      |

|-------|------------------------|--------|-----------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x08  |                        | USB2   | Tx Contr  | ol 2  | This register configures the Transmit side settings – Tx output driver slew rate and output signal swing on USB2 side                                                                                                                                                                     |

| Bit   | Bit Name               |        | R/W Reset |       | Description                                                                                                                                                                                                                                                                               |

| 7     | RSVD                   |        | RAZ       | b'0   | Reserved                                                                                                                                                                                                                                                                                  |

| 6     | USB2 FS rise/fall time |        | RW        | b'1   | This bit determines the FS Tx driver rise/fall time on USB2 pins 0 = 8 to 20 ns 1 = 4 to 10 ns Load conditions are as defined in USB standard                                                                                                                                             |

| 5:4   | USB2 HS rise/fall time |        | RW        | b'10  | The 2 bits determine the Tx driver slew rate for HS signaling on USB2 pins.  00 = 500 to 900 ps  01 = 400 to 800 ps  10 = 300 to 700 ps  11 = Reserved  Load conditions are as defined in USB standard                                                                                    |

| 3     | RSVD                   |        | RAZ       | 0     | Reserved                                                                                                                                                                                                                                                                                  |

| 2:0   | Tx output signal swing |        | RW        | b'010 | The 3 bits determine the Tx output signal swing level for HS signaling on USB2 pins (when the interface is terminated)  000 = 350 mV  001 = 400 mV  010 = 450 mV  011 = 500 mV  100 = 550 mV  101 = 600 mV  111 = 700 mV  All settings are within +/-10% of nominal value mentioned above |

Table 19. Register 0x09 - USB2 HS TERMINATION

| 0   |                         | Regist                      | er Name | •       | Register Description                                                                                                                                                                                                                                                                                                                                                      |

|-----|-------------------------|-----------------------------|---------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |                         | USB2 HS Termination control |         |         | This register sets the HS termination values on USB2 pins                                                                                                                                                                                                                                                                                                                 |

| Bit | Bit Name                |                             | R/W     | Reset   | Description                                                                                                                                                                                                                                                                                                                                                               |

| 7:3 | RSVD                    |                             | RAZ     | p,00000 | Reserved                                                                                                                                                                                                                                                                                                                                                                  |

| 2:0 | USB2 HS Term<br>control | ination                     | RW      | b'010   | The bits determine the HS termination on USB2 pins (differential impedance is specified here) $000 = 100 \ \Omega \ differential$ $001 = 95 \ \Omega \ differential$ $010 = 90 \ \Omega \ differential$ $011 = 85 \ \Omega \ differential$ $100 = 80 \ \Omega \ differential$ $101 \ to \ 111 = Reserved$ All settings are within +/-10% of nominal value mentioned above |

Table 20. Register 0x0A - USB2 HS DISCONNECT THRESHOLD

| Regis | ter offset                       | Register Na | me       | Register Description                                                                                                                                                                                                                                                   |  |  |

|-------|----------------------------------|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 0x0A  |                                  | USB2 HS dis |          | This register sets the HS disconnect threshold level on USB2 pins                                                                                                                                                                                                      |  |  |

| Bit   | Bit Name R/W Reset               |             | Reset    | Description                                                                                                                                                                                                                                                            |  |  |