# rreescale Semiconductor

**Engineering Bulletin**

Rev. 3, 12/2005

# Functional Differences Between Masks 3F48S and 1K30A of the DSP56301

This document describes the differences between masks of the DSP56301: mask 1K30A and the preceding mask 3F48S. The newer 1K30A mask uses the communications design rules (CDRII) process. The 1K30A mask set also has new I/O and a new PLL, with the requisite change in the PLL capacitor equation (PCAP).

### 1 1K30A Mask Set

The 1K30A mask set replaced the 3F48S mask set in production.

# 2 PLL Input Capacitor (C<sub>PCAP</sub>)

The process change results in a changed requirement for computing the size of  $C_{PCAP}$  the capacitor used with the PCAP input. **Table 1** lists the new formulas for computing the value of this input capacitor for the DSP.

# 3 ESD Protection

The 1K30A mask set incorporates improved I/O structures to ensure Electro-Static Discharge (ESD) protection to qualification levels of 2000 volts Human Body Model (HBM) and 200 volts Machine Model (MM).

#### **CONTENTS**

| 1  | 1K30A Mask Set                           | 1   |

|----|------------------------------------------|-----|

| 2  | PLL Input Capacitor (C <sub>PCAP</sub> ) | 1   |

| 3  | ESD Protection                           | 1   |

| 4  | Differences Overview                     | 2   |

| 5  | Asynchronous Bus Arbitration             | 2   |

| 6  | Boot Mode Changes                        | 5   |

|    | Identification Registers                 |     |

| 8  | Errata Removal                           | 7   |

|    | Documentation Errata                     |     |

| 1( | ) Errata Deletion                        | 2.1 |

# 4 Differences Overview

The primary functional differences between the mask sets are due to inherent differences between the two design technologies. **Table 1** compares the mask sets.

Table 1. Functional Comparison of 3F48S and 1K30A

| Footure                                  | 3F4                                                                                  | 8S           |              | 1K30A                                                                            |              |              |  |  |  |

|------------------------------------------|--------------------------------------------------------------------------------------|--------------|--------------|----------------------------------------------------------------------------------|--------------|--------------|--|--|--|

| Feature                                  | Recommended                                                                          | Min          | Max          | Recommended                                                                      | Min          | Max          |  |  |  |

| Technology                               | 0.5 micron                                                                           | _            | _            | Sub 0.4 micron                                                                   | _            | _            |  |  |  |

| PLL input capacitor (C <sub>PCAP</sub> ) | Uses the following rules:<br>For MF ≤4:<br>C <sub>PCAP</sub> = [(500 × MF) – 150] pF | (MF × 425) – | (MF × 590) – | Use the following rules:<br>For MF ≤4:<br>C <sub>PCAP</sub> = [(680 × MF) – 120] | (MF × 580) – | (MF × 780) – |  |  |  |

|                                          | For MF > 4:                                                                          | 125          | 175          | pF                                                                               | 100          | 140          |  |  |  |

|                                          | $C_{PCAP} = (690 \times MF) pF$                                                      | MF × 520     |              | For MF > 4:<br>$C_{PCAP} = (1100 \times MF) pF$                                  | MF × 830     | MF × 1470    |  |  |  |

# 5 Asynchronous Bus Arbitration

In the Operating Mode Register (OMR) of the 1K30A is a new Asynchronous Bus Arbitration (ABE) bit to support external access at high frequencies. As **Figure 1** shows, bit 13 in the OMR enables Asynchronous Bus Arbitration. For convenience, **Table 2** defines all the OMR bits available in the 1K30A mask set of the DSP56301. The new ABE bit is highlighted in a bold red font.

|    |                                      |            | S               | CS     |       |                          |      |                                      |        |                  | EO     | М      |                     |                          |         |       |        |       | CC    | M     |       |     |    |

|----|--------------------------------------|------------|-----------------|--------|-------|--------------------------|------|--------------------------------------|--------|------------------|--------|--------|---------------------|--------------------------|---------|-------|--------|-------|-------|-------|-------|-----|----|

| 23 | 22                                   | 21         | 20              | 19     | 18    | 17                       | 16   | 15                                   | 14     | 13               | 12     | 11     | 10                  | 9                        | 8       | 7     | 6      | 5     | 4     | 3     | 2     | 1   | 0  |

|    |                                      |            | SEN             | WRP    | EOV   | EUN                      | XYS  | ATE                                  | APD    | ABE              | BRT    | TAS    | BE                  | CDF                      | P1:0    | MS    | SD     |       | EBD   | MD    | MC    | MB  | MA |

|    |                                      |            |                 |        |       |                          |      |                                      | ATE    | —Addı            | ress T | race   | Enab                | le                       |         |       | MS     | —Ме   | emory | Swite | ch Mo | ode |    |

|    |                                      |            |                 |        |       |                          |      |                                      | APD    | —Addı<br>Priorit |        |        | tion                |                          |         |       | SD     | —Sto  | p De  | lay   |       |     |    |

|    |                                      |            |                 |        |       |                          |      | ABE—Async. Bus Arbitration<br>Enable |        |                  |        |        |                     | EBD—External Bus Disable |         |       |        |       |       |       |       |     |    |

|    | SEN                                  | —Sta       | ack E           | xtens  | ion E | nable                    |      | BRT—Bus Release Timing               |        |                  |        |        |                     | MD—Operating Mode D      |         |       |        |       |       |       |       |     |    |

|    | WRP                                  | —Ex<br>Fla | tende<br>ig     | ed Sta | ick W | rap                      |      | TAS—TA Synchronize Select            |        |                  |        |        | MC—Operating Mode C |                          |         |       |        |       |       |       |       |     |    |

|    | EOV                                  |            | tende<br>erflow |        |       |                          |      | BE—Burst Mode Enable                 |        |                  |        |        |                     |                          | MB      | —Op   | eratir | ig Mo | de B  |       |       |     |    |

|    | EUN—Extended Stack<br>Underflow Flag |            |                 |        |       | CDP1—Core-DMA Priority 1 |      |                                      |        |                  |        |        | MA                  | —Op                      | eratir  | ng Mo | de A   |       |       |       |       |     |    |

|    | XYS                                  |            | ack E           | xtens  | ion S | pace                     |      | (                                    | CDP0   | —Core            | e-DMA  | A Prio | rity 0              |                          |         |       |        |       |       |       |       |     |    |

|    | — R                                  | eser       | ved bi          | t; rea | d as  | zero;                    | shou | d be                                 | writte | n with           | zero f | or fut | ure co              | ompa                     | tibilit | у     |        |       |       |       |       |     |    |

Figure 1. Operating Mode Register (OMR)

Functional Differences Between Masks 3F48S and 1K30A of the DSP56301, Rev. 3

Table 2. Operating Mode Register (OMR) Bit Definitions

| Bit<br>Number | Bit<br>Name | Reset<br>Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------|-------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23–21         |             | 0              | Reserved. Set to 0 for future compatibility.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 20            | SEN         | 0              | Stack Extension Enable Enables/disables the stack extension in data memory. If the SEN bit is set, the extension is enabled. Hardware reset clears this bit, so the default out of reset is a disabled stack extension.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 19            | WRP         | 0              | Stack Extension Wrap Flag Set when copying from the on-chip hardware stack (System Stack Register file) to the stack extension memory begins. You can use this flag during the debugging phase of the software development to evaluate and increase the speed of software-implemented algorithms. The WRP flag is a <i>sticky bit</i> (that is, cleared only by hardware reset or by an explicit MOVE operation to the OMR).                                                                                                                                                                                                                                                                                                                                                  |

| 18            | EOV         | 0              | Stack Extension Overflow Flag Set when a stack overflow occurs in Stack Extended mode. Extended stack overflow is recognized when a push operation is requested while SP = SZ (Stack Size register), and the Extended mode is enabled by the SEN bit. The EOV flag is a <i>sticky bit</i> (that is, cleared only by hardware reset or by an explicit MOVE operation to the OMR). The transition of the EOV flag from zero to one causes a Priority Level 3 (Non-maskable) stack error exception.                                                                                                                                                                                                                                                                              |

| 17            | EUN         | 0              | Stack Extension Underflow Flag Set when a stack underflow occurs in Extended Stack mode. Extended stack underflow is recognized when a pull operation is requested, SP = 0, and the SEN bit enables Extended mode. The EUN flag is a <i>sticky bit</i> (that is, cleared only by hardware reset or by an explicit MOVE operation to the OMR). Transition of the EUN flag from zero to one causes a Priority Level 3 (Non-maskable) stack error exception.  NOTE: While the chip is in Extended Stack mode, the UF bit in the SP acts like a normal counter bit.                                                                                                                                                                                                               |

| 16            | XYS         | 0              | Stack Extension XY Select  Determines whether the stack extension is mapped onto X or Y memory space. If the bit is clear, then the stack extension is mapped onto the X memory space. If the XYS bit is set, the stack extension is mapped to the Y memory space.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 15            | ATE         | 0              | Address Trace Enable When set, the Address Trace Enable (ATE) bit enables Address Trace mode. The Address Trace mode is a debugging tool that reflects internal memory accesses at the external address lines.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 14            | APD         | 0              | Address Attribution Priority Disable Disables the priority assigned to the Address Attribute signals (AA0-AA3). When APD = 0 (default setting), the four Address Attribute signals each have a certain priority: AA3 has the highest priority, AA0 has the lowest priority. Therefore, only one AA signal can be active at one time. This allows continuous partitioning of external memory; however, certain functions, such as using the AA signals as additional address lines, require the use of additional interface hardware. When APD is set, the priority mechanism is disabled, allowing more than one AA signal to be active simultaneously. Therefore, the AA signals can be used as additional address lines without the need for additional interface hardware. |

| 13            | ABE         | 0              | Asynchronous Bus Arbitration Enable Eliminates the setup and hold time requirements (with respect to CLKOUT) for $\overline{BB}$ and $\overline{BG}$ , and substitutes a required non-overlap interval between the deassertion of one $\overline{BG}$ input to a DSP56300 family device and the assertion of a second BG input to a second DSP56300 family device on the same bus. When the ABE bit is set, the $\overline{BG}$ and $\overline{BB}$ inputs are synchronized. This synchronization causes a delay between a change in $\overline{BG}$ or $\overline{BB}$ until this change is actually accepted by the receiving device.                                                                                                                                       |

Functional Differences Between Masks 3F48S and 1K30A of the DSP56301, Rev. 3

#### chronous Bus Arbitration

Table 2. Operating Mode Register (OMR) Bit Definitions (Continued)

| Bit<br>Number | Bit<br>Name | Reset<br>Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------|-------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12            | BRT         | 0              | Bus Release Timing Selects between fast or slow bus release. If BRT is cleared, a Fast Bus Release mode is selected (that is, no additional cycles are added to the access and BB is not guaranteed to be the last Port A pin that is tri-stated at the end of the access). If BRT is set, a Slow Bus Release mode is selected (that is, an additional cycle is added to the access, and BB is the last Port A pin that is tri-stated at the end of the access).                                                                                                                                                                        |

| 11            | TAS         |                | TA Synchronize Select Selects the synchronization method for the input Port A pin— $\overline{TA}$ (Transfer Acknowledge). If TAS is cleared, you are responsible for asserting the $\overline{TA}$ pin in synchrony with the chip clock, as described in the technical data sheet. If TAS is set, the $\overline{TA}$ input pin is synchronized inside the chip, thus eliminating the need for an off-chip synchronizer. Note that the TAS bit has no effect when the $\overline{TA}$ pin is deasserted: you are responsible for deasserting the $\overline{TA}$ pin in synchrony with the chip clock, regardless of the value of TAS. |

| 10            | BE          | 0              | Cache Burst Mode Enable Enables/disables Burst mode in the memory expansion port during an instruction cache miss. If the bit is cleared, Burst mode is disabled and only one program word is fetched from the external memory when an instruction cache miss condition is detected. If the bit is set, Burst mode is enabled, and up to four program words are fetched from the external memory when an instruction cache miss is detected.                                                                                                                                                                                            |

|               |             |                | Core-DMA Priority Specify the priority of core and DMA accesses to the external bus.  00 Determined by comparing status register CP[1:0] to the active DMA channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 9–8           | CPD         | 1              | priority  01 DMA accesses have higher priority than core accesses  10 DMA accesses have the same priority as the core accesses  11 DMA accesses have lower priority than the core accesses                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7             | MS          | 0              | Memory Switch Mode Allows some internal data memory (X, Y, or both) to become part of the chip internal Program RAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|               |             |                | <ol> <li>Program data placed in the Program RAM/Instruction Cache area changes its placement after the MS bit is set (that is, the Instruction Cache always uses the highest internal Program RAM addresses).</li> <li>To ensure proper operation, place six NOP instructions after the instruction that changes the MS bit.</li> <li>To ensure proper operation, do not set the MS bit while the Instruction Cache is enabled (CE bit is set in SR).</li> </ol>                                                                                                                                                                        |

| 6             | SD          | 0              | Stop Delay Mode  Determines the length of the delay invoked when the core exits the Stop state. The STOP instruction suspends core processing indefinitely until a defined event occurs to restart it. If SD is cleared, a 128K clock cycle delay is invoked before a STOP instruction cycle continues. However, if SD, the delay before the instruction cycle continues is 16 clock cycles. The long delay allows a clock stabilization period for the internal clock to begin oscillating and to stabilize. When a stable external clock is used, the shorter delay allows faster start-up of the DSP56300 core.                      |

| 5             |             | 0              | Reserved. Set to 0 for future compatibility.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4             | EBD         | 0              | External Bus Disable Disables the external bus controller to reduce power consumption when external memories are not used. When EBD is set, the external bus controller is disabled and external memory cannot be accessed. When EBD is cleared, the external bus controller is enabled and external access can be performed. Hardware reset clears the EBD bit.                                                                                                                                                                                                                                                                        |

Functional Differences Between Masks 3F48S and 1K30A of the DSP56301, Rev. 3

Table 2. Operating Mode Register (OMR) Bit Definitions (Continued)

| Bit    | Bit   | Reset | Description                                                                                                                                                                                                                                                                                           |

|--------|-------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number | Name  | Value |                                                                                                                                                                                                                                                                                                       |

| 3–0    | MD-MA |       | Chip Operating Mode Indicate the operating mode of the DSP56300 core. On hardware reset, these bits are loaded from the external mode select pins, MODD, MODC, MODB, and MODA, respectively. After the DSP56300 core leaves the Reset state, MD, MC, MB, and MA can be changed under program control. |

# 6 Boot Mode Changes

The 1K30A mask set of the DSP56301 modifies the boot modes of the microprocessor in order to add the ability to boot from a serial EPROM (see **Table 3**). Adding this new booting capability requires that MODD no longer be a "don't care." The MODD column of **Table 3** shows the correct MODD setting for each boot mode. These settings are communicated to customers in Product Change Notice (PCN) No. 4302. Changes in boot mode that occur with 1K30A appear in bold red font.

Table 3. New DSP56301 Boot Modes for CDR2

| <b>Boot Mode</b> | MODD | 3F48S                                                                    | 1K30A                                                                |

|------------------|------|--------------------------------------------------------------------------|----------------------------------------------------------------------|

| 0                | 0    | expanded mode                                                            | expanded mode                                                        |

| 1                | 0    | bootstrap from byte-wide memory                                          | reserved                                                             |

| 2                | 0    | bootstrap through SCI                                                    | bootstrap through SCI                                                |

| 3                | 0    | reserved                                                                 | reserved (burn-in)                                                   |

| 4                | 0    | host bootstrap PCI mode (32 bit wide)                                    | bootstrap from serial EEPROM                                         |

| 5                | 0    | host bootstrap 16-bit wide UB mode (ISA)                                 | reserved                                                             |

| 6                | 0    | host bootstrap 8-bit wide UB mode in double-<br>strobe pin configuration | host bootstrap 8-bit wide UB mode in double-strobe pin configuration |

| 7                | 0    | host bootstrap 8-bit wide UB mode in single-strobe pin configuration     | reserved                                                             |

| 8                | 1    | expanded mode                                                            | expanded mode                                                        |

| 9                | 1    | bootstrap from byte-wide memory                                          | bootstrap from byte-wide memory                                      |

| А                | 1    | bootstrap through SCI                                                    | bootstrap through SCI                                                |

| В                | 1    | host bootstrap in onyx-to-onyx mode                                      | host bootstrap in onyx-to-onyx mode                                  |

| С                | 1    | host bootstrap PCI mode (32-bit wide)                                    | host bootstrap PCI mode (32 bit wide)                                |

| D                | 1    | host bootstrap 16-bit wide UB mode (ISA)                                 | host bootstrap 16-bit wide UB mode (ISA)                             |

| Е                | 1    | host bootstrap 8-bit wide UB mode in double-<br>strobe pin configuration | host bootstrap 8-bit wide UB mode in double-strobe pin configuration |

Functional Differences Between Masks 3F48S and 1K30A of the DSP56301, Rev. 3

Table 3. New DSP56301 Boot Modes for CDR2

| Boot Mode | MODD | 3F48S                                                                | 1K30A                                                                |

|-----------|------|----------------------------------------------------------------------|----------------------------------------------------------------------|

| F         | 1    | host bootstrap 8-bit wide UB mode in single-strobe pin configuration | host bootstrap 8-bit wide UB mode in single-strobe pin configuration |

# 7 Identification Registers

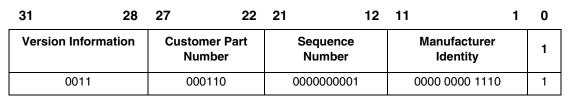

Values in the Device Identification register (IDR) and JTAG Identification (ID) register are changed to reflect the new 1K30A mask set, as shown in **Figure 2** and **Figure 3**.

The IDR is a 24-bit, read-only factory-programmed register that identifies DSP56300 family members. It specifies the derivative number and revision number of the device. This information is used in testing or by software. **Figure 2** shows the contents of the IDR for mask set 1K30A. Revision numbers are assigned as follows: \$0 is revision 0, \$1 is revision A, and so on.

| 23 |           | 16 | 15     |          | 12 | 11 |                   | 0 |

|----|-----------|----|--------|----------|----|----|-------------------|---|

|    | Reserved  |    | Revisi | ion Numb | er |    | Derivative Number |   |

|    | 0000 0000 |    |        | 0011     |    |    | 0011 0000 0001    |   |

Figure 2. Identification Register Configuration (Revision 3)

The JTAG ID register is a 32-bit read-only factory-programmed register that distinguishes the component on a board according to the IEEE 1149.1 standard. **Figure 3** shows the JTAG ID register configuration for mask set 1K30A. Version information corresponds to the revision number (\$0 for revision 0, \$1 for revision A, etc.).

Figure 3. JTAG Identification Register Configuration (Revision 3)

Functional Differences Between Masks 3F48S and 1K30A of the DSP56301, Rev. 3

# 8 Errata Removal

The 1K30A mask set removes all known functional errata on the 3F48S mask set. This section shows the functional errata that the 1K30A mask set removes. For further documentation updates, consult the errata for each device. The specific differences in errata items are listed in the following tables. A detailed description of each errata item is available at the Freescale website listed on the back page of this document. The silicon errata present on the 3F48S mask but not on the 1K30A masks are listed as follows:

| Errata<br>No. | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Status            |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| ES16          | Description:  When the chip is powered up with PLL enabled (PINIT = 1), the skew between EXTAL and CLKOUT after the PLL locks cannot be guaranteed at high frequency (over 50 MHz, not 100% tested).  Workaround: If skew between EXTAL and CLKOUT is needed, power up with PINIT = 0, and then enable the PLL by software.                                                                                                                                                                                                                                                                                                                                                                                                                                                | Fixed on<br>1K30A |

| ES30          | Description:  After the BB pin output is driven high and released, the pin output voltage level may not reach V <sub>CC</sub> . The issue depends on the application board layout and the parameters of the chip process.  Workaround: Use a restricted board layout that includes a 1 kΩ pull-up resistor connected to the BB pin with a 100 Ω resistor connected in series with, and as close as possible to, the pin. The board route from the BB pin to any component should guarantee the following parameters:  • Route inductance < 40 nH  • Route capacitance < 15 pF  • Input capacitance < 8 pF  Such restrictions guarantee that when BB is driven high (deasserted), the output voltage level will be above 2.25 V at V <sub>CC</sub> = 3.3 V.                 | Fixed on<br>1K30A |

| ES36          | Description:  If the stack extension is enabled, the instructions listed below should not be placed as the next-to-last or as the last instruction of a DO loop (that is, should not appear at LA-1 or LA).  The instructions are:  • XY Memory Data Move (A-6.76)  X Memory Move (A-6.71)  Y Memory Move (A-6.73)  Long Memory Data Move (A-6.75)  Immediate Short Data Move (A-6.68)  Register to Register Data Move (A-6.69)  Address Register Update (A-6.70)  X Memory and Register Data Move (A-6.72)  Y Memory and Register Data Move (A-6.74)  Arithmetic Instructions that allow Parallel Moves listed above  IFcc and IFcc.U (A-6.41)  Workaround:  Insert a NOP or other instruction not listed above as the next-to-last and last instructions in the DO loop. | Fixed on<br>1K30A |

| ES37          | Description: In PCI mode, improper HI32 operation may result if the HTXR/HRXS registers are accessed by the PCI master at byte address Base_Address + (N × 2048 + 16), where N is an integer from 1–31.  Workaround: Not available.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Fixed on<br>1K30A |

| ES41          | Description: The HCLK pin of the HI32 presents an input capacitive load of almost 30 pF, which exceeds the permissible maximum load of 12 pF as specified in the PCI Specification Version 2.1. This may cause improper HI32 operation in PCI systems. The effect of this extra load may vary from system to system, depending on PCI clock driver strength.  Workaround: Use a zero-propagation-delay external PLL device (e.g., CY2305) to buffer the PCI clock signal. This solution does not enable spread-spectrum PCI clocking.                                                                                                                                                                                                                                      | Fixed on<br>1K30A |

#### a Removal

| Errata<br>No. | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Status            |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| ES42          | Description:  When a Direct Memory Access (DMA) channel is in Line mode (that is, the DMA Transfer Mode is DTM = 010) with address modes defined by DMA Three Dimensional mode D3D = 0 and DMA = 10010x (that is, the DMA Counter (DCO) is in mode A), and the DCO value is greater than \$FFF, then the DMA does not function properly. This address mode implies "no update" at the destination and "no update" or "post increment by 1" mode at the source.  Workaround:  Use Block Transfer mode (that is, DTM = 000). For the DCO and DMA Address Mode (DAM) settings described in this erratum, the Line Transfer mode of DMA is identical to its Block Transfer mode, so this combination is redundant. In fact, a block containing only one line is still a block.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Fixed on<br>1K30A |

| ES44          | Description:  Let's say that "channel A" is the DMA channel servicing the HI32, and that "channel B" is another DMA channel that has been disabled by software. Then, depending on the DMA Request Source field (DRS[4:0]) of the two channels, channel A may be stalled by channel B being disabled. Channel A may be stalled when the DMA Channel Enable (DE) bit in the DMA Control Register is cleared by software in the following cases:  • DE bit of channel B cleared by software because of  —a Transfer Done from DMA channel 0 (DRSb = 00100) or  —an ESSI1 Receive Data (DRSb = 01100) or then channel A may be stalled by a Host Slave Receive Data (DRSa = 11100).  • DE bit of channel B cleared by software because of  —a Transfer Done from DMA channel 1 (DRSb = 00101) or  —an ESSI1 Transmit Data (DRSb = 01101) or then channel A may be stalled by a Host Master Receive Data (DRSa = 11101).  • DE bit of channel B cleared by software because of  —a Transfer Done from DMA channel 2 (DRSb = 00110) or  —an SCI Receive Data (DRSb = 01110) or then channel A may be stalled by a Host Slave Transmit Data (DRSa = 11110).  • DE bit of channel B cleared by software because of  — a Transfer Done from DMA channel 3 (DRSb = 00111) or  — an SCI Transmit Data (DRSb = 01111) or then channel A may be stalled by a Host Master Transmit Data (DRSa = 11111).  Workaround:  Use either one of the following alternatives:  • Clear and set the DE bit of channel A immediately after you clear the DE bit of channel B.  • Avoid a software clear of the DE bit of channel B. | Fixed on<br>1K30A |

| ES45          | Description:  When the Host Command Vector Register (HCVR) is written in Peripheral Component Interconnect (PCI) mode while the Receive Buffer Lock Enable (RBLE) bit is set in the DSP PCI Control Register (DPCR), the Host Data Transfer Complete (HDTC) status bit in DSP PCI Status Register (DPSR) may be set falsely, thus also causing an HDTC interrupt if that interrupt has been enabled by the Transfer Complete Interrupt Enable (TCIE) bit in the DPCR.  Workaround:  Use either one of the following alternatives:  Clear HDTC, if it is set, by writing it with 1 in the Host Command Interface Status Register (ISR).  Clear HDTC, if it is set, by writing it with 1; use software-dependent information to distinguish between a false and true HDTC setting. For example, you do either of the following:  —Alter the destination address pointer if the DSP Receive Data Register (DRXR) data is being transferred by the DSP core. The pointer is changed if the HDTC setting is true.  —Alter the destination address or counter registers of the DMA channel if the DRXR data is being transferred by the DMA. The registers are changed if the HDTC setting is true.                                                                                                                                                                                                                                                                                                                                                                                                              | Fixed on<br>1K30A |

| ES47          | Description:  If the DMA channel and the core access the same 1/4 K internal X data, Y data, or program memory page, and the DMA interrupt is enabled, a false interrupt may occur in addition to the correct one.  Workaround:  Ensure that the channel's DTD status bit in the DSTR is set before jumping to the Interrupt Service Routine (that is, the interrupt is correct only when DTD is set).  Example:  ORG P:I_DMA0  JSSET #M_DTD0,X:M_DSTR,ISR; ISR is the Interrupt Service; Routine label for DMA channel 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Fixed on<br>1K30A |

Functional Differences Between Masks 3F48S and 1K30A of the DSP56301, Rev. 3

| Errata<br>No. | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Status            |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| ES53          | Description:  Using the JTAG instruction code 1111 (\$F) or 1101 (\$D) for the BYPASS instruction may cause the chip to enter Debug mode (which then correctly sets the Status bits (OS[1:0]) in the OnCE Status and Control Register (OSCR[7:6]) and asserts the DE output to acknowledge the Debug mode status).  Workaround:  Use one of the following alternatives:  If possible, do not use instruction code 1111 (\$F) or 1101 (\$D) for the BYPASS instruction. Use one of the other defined BYPASS instruction codes (that is, any code from 1000−1100 (\$8−\$C) or 1110 (\$E)).  If you must use instruction code 1111 (\$F) or 1101 (\$D), use the following procedure: | Fixed on<br>1K30A |

|               | <ul> <li>—While the \$F or \$D instruction code is in the Instruction Register, ensure that the JTAG Test Access Port (TAP) state machine does not pass through the JTAG Test-Logic-Reset state while accessing any JTAG registers (that is, Instruction Register, Boundary Scan Register, or ID Register).</li> <li>—Before using any other JTAG instruction, load one of the other BYPASS instruction codes (that is, any code from 1000–1100 (\$8–\$C) or 1110 (\$E)) into the instruction register. Then, any other JTAG instruction may be used.</li> </ul>                                                                                                                  |                   |

| ES72          | Description (added 10/30/1997):  During external memory accesses, noise may be generated by the Bus Strobe (\$\overline{BS}\$) signal and placed on the Test Clock (TCK) signal, causing the JTAG Test Access Port (TAP) controller to change states unpredictably. This problem may be more severe at higher speeds or in applications using multiple DSP56300 families.  Note: Applies to PBGA package only.                                                                                                                                                                                                                                                                    | Fixed on<br>1K30A |

|               | Workaround: Bypass the BS line to signal ground with a 10 pF capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                   |

| ES81          | Description: The HI32 may generate a wrong PAR signal.  Workaround:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Fixed on<br>1K30A |

|               | If possible, the system should ignore parity errors generated in such a case.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |

|               | Description: The BL pin may operate improperly when two consecutive manipulation instructions (bset/bclr/bchg) use external memory as the destination.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Fixed on<br>1K30A |

| ES82          | Example of the sequence:  bset #5,x:(r0) ;; r0 is a pointer on an external memory address  bclr #7,x:(r3) ;; r3 is a pointer on an external memory address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                   |

|               | Workaround :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |

|               | Separate the consecutive bit manipulation instructions by any other instruction, as in the following example:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |

|               | <pre>bclr #7,x:(r3) ;; r3 is a pointer on an external memory address nop</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                   |

|               | bset #5,x:(r0) ;; r0 is a pointer on an external memory address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   |

#### a Romoval

| Errata<br>No. | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Status            |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

|               | <ul> <li>Description: When software disables a DMA channel (by clearing the DE bit of the DCR), the DTD status bit of the channel may not be set if any of the following events occur: <ul> <li>Software disables the DMA channel just before a conditional transfer stall (Described by App B-3.5.1,UM).</li> <li>Software disables the DMA channel at the end of the block transfer (that is, after the counter is loaded with its initial value and transfer of the last word of the block is completed).</li> </ul> </li> <li>As a result, the Transfer Done interrupt might not be generated.</li> </ul> | Fixed on<br>1K30A |

|               | Workaround:  Avoid using the instruction sequence causing the conditional transfer stall (See DSP56300 UM, App B-3.5.1 for description) in fast interrupt service routines. Every time the DMA channel needs to be disabled by software, the following sequence must be used:                                                                                                                                                                                                                                                                                                                                 |                   |

| ES84          | bclr #DIE,x:M_DCR ; not needed if DIE is cleared bclr #DE,x:M_DCR ; instead of two instructions above, one 'movep' instruction may be used ; to clear DIE and DE bits                                                                                                                                                                                                                                                                                                                                                                                                                                         |                   |

|               | <pre>movep #DCR_Dummy_Value,x:M_DCR bclr #DE,x:M_DCR nop</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   |

|               | Here, the DCR_Dummy_value is any value of the DCR register that complies with the following requirements:  DE is set;  DIE is set if Transfer Done interrupt request should be generated and cleared otherwise;  DRS[4:0] bits must encode a reserved DMA request source (see the following list of reserved DRS values);                                                                                                                                                                                                                                                                                     |                   |

|               | List of reserved DRS[4:0] values (per device):  • DSP56302, DSP56309, DSP56303, DSP56304, DSP56362 — 10101-11111  • DSP56305 — 11011  • DSP56301 — 10011-11011  • DSP56307 — 10111-11111                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |

| ES86          | Description:  If the HI32 performs a write transaction as a PCI master and the transaction is disconnected by the target, the value of the MTRQ status bit in the DPSR register may be wrong.                                                                                                                                                                                                                                                                                                                                                                                                                 | Fixed on<br>1K30A |

| E30U          | Workaround:  Do not use an MTRQ status bit-related interrupt or polling. (The related DMA functionality is not affected by this issue.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                   |

| ES87          | Description: When the HI32 is an active PCI target, it does not set the DPE bit in the CSTR register if an address parity error occurs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Fixed on<br>1K30A |

|               | Workaround:  The Host can get information about the Address Parity status either by reading the SSE bit (in the CSTR) or by indirectly reading the (e.g. via Host Command) the APER bit in the DPSR register.                                                                                                                                                                                                                                                                                                                                                                                                 |                   |

|               | Description: If the SCI Receiver is programmed to work with a different serial clock than the SCI Transmitter so that either the Receiver or Transmitter is using the external serial clock and the other is using the internally-generated serial clock—RCM and TCM in the SCCR are programmed differently)—then the internal serial clock generator will not operate and the SCI portion (Receiver or Transmitter) clocked by the internal clock will be stuck.                                                                                                                                             | Fixed on<br>1K30A |

| ES89          | Workaround:  Do not use SCI with the two SCI portions (Receiver and Transmitter) clocked by different serial clocks; use either both externally or both internally clocked.  Or:                                                                                                                                                                                                                                                                                                                                                                                                                              |                   |

|               | When using both portions of the SCI (Receiver & Transmitter), do not program different values on RCM and TCM in the SCCR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |

#### Functional Differences Between Masks 3F48S and 1K30A of the DSP56301, Rev. 3

| Errata<br>No. | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Status            |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| ES90          | <ul> <li>Description: A deadlock occurs during DMA transfers if all the following conditions exist: <ul> <li>1. DMA transfers data between internal memory and external memory through port A.</li> <li>2. DMA and the core access the same internal 0.25K memory module.</li> <li>3. The bus arbitration system is implemented in such way that the bus is granted to the DSP (BG is asserted) only after the DSP requests it (BR is asserted).</li> </ul> </li> <li>The symptom is a deadlock on DMA activity, that is, a DMA transfer stops for no apparent reason. BR is not asserted when it should be asserted because of DMA.</li> <li>Workaround: One of the following: <ul> <li>1. Use intermediate internal memory on which there is no contention with the core.</li> <li>2. Do not use bus arbitration (tie BG to the ground), or have an external arbiter that asserts BG even if BR is not asserted by the DSP.</li> <li>3. Set the DSP core priority higher than the DMA (for Port A accesses), and do a periodic external access by</li> </ul> </li> </ul> | Fixed on<br>1K30A |

| ES95          | the core. The core access solves the deadlock.  Description:  If more than a single DMA channel is enabled while the DSP stays in the WAIT processing state, and triggering one of the DMA channels causes an exit from the WAIT state (See A-6.115, UM), triggering another DMA channel might cause improper DMA operation.  Workaround:  Assure that only a single DMA channel can be triggered during DSP WAIT state. If the application cannot guarantee this, other DMA channels should be disabled before the WAIT processing state is entered and then                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Fixed on<br>1K30A |

| ES101         | reenabled after WAIT state is exited.  Description:  If the reset mode is expanded mode (for example, mode 0 or mode 8 on the DSP5630x), A MOVE (not a PROGRAM FETCH) from internal P memory to any destination may not work properly.  Workaround:  After each reset (RESET) negation and before the first move from internal program memory, execute the following sequence:  BSET #M_CE, sr NOP NOP NOP BCLR #M_CE, sr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Fixed on<br>1K30A |

| ES104         | Description: An improper operation may occur when all the following conditions apply: The DMA channel is in a mode that does not automatically clear the DE bit at the end of the block (DTM[2:0] = 1xx in DCR). This channel is disabled by software (by clearing DE in DCR) while it is triggered for a new transfer. The previous operation is not yet completed.  Workaround: The DMA channel should be disabled only when it is not triggered for a new transfer, that is, when the DACT bit in the DSTR register is cleared. To perform this operation most efficiently, all other DMA channels should be disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Fixed on<br>1K30A |

| ES107         | Description: The HDTC status bit (relevant only if the RBLE control bit is set) may not be set properly when both of the following conditions apply:  • a) DSP software clears the HDTC bit while the PCI bus is parked on the HI32.  • b) The PCI master read transaction is initiated by the HI32 while the bus is still parked on the HI32.  Workaround: Use one of the following alternatives:  • Avoid bus parking on the HI32.  • Enter the Personal Software Reset (HM[2:0]=0) in HDTC ISR.  • Poll the MRRQ and SRRQ status bits before the start of each master read transaction (e.g. in MARQ ISR). Start this transaction only when both MRRQ and SRRQ are cleared. The HDTC status bit should be cleared by the DSP software as defined in the specification.                                                                                                                                                                                                                                                                                                  | Fixed on<br>1K30A |

Functional Differences Between Masks 3F48S and 1K30A of the DSP56301, Rev. 3

#### a Removal

| Errata<br>No. |                                                                                                                                                                                                                              | De                                                                                                                                                                                                                                                                                                                            | escription                                                                                                                                                                                                                                                                                         | Status            |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| ES114         | dimensional (D3D=                                                                                                                                                                                                            | ay operate improperly when the and 1) and DAM[5:0] = 1xx 1 10 or                                                                                                                                                                                                                                                              | address mode of this channel is defined as three-DAM[5:0] = 01x1 10 (that is, triple counter mode is E).                                                                                                                                                                                           | Fixed on<br>1K30A |

|               | Description (added When a DMA chans may not get set, an 1. There is anoth cleared by softwarend of the channetransfer - if chans 2. This channel (software at the echannel B line transfer - workaround: Avoid executing a I | d 4/19/99): nel (called channel A) is disabled d the DMA end of the block inter er channel (channel B) executing are at the end of the channel B w el B line transfer - if channel B is nel B is in Block transfer mode. A) is executing EXTERNAL acce nd of the channel B word transfer ansfer - if channel B is in Line tra | DMA channel should be disabled. This can be done as                                                                                                                                                                                                                                                | Fixed on<br>1K30A |