# Freescale Semiconductor Engineering Bulletin

Document Number: EB709

Rev. 1, 04/2009

# Supplementary Information Regarding Brief Pulse Erratum on SG/SH I/O Pins during Power-On-Reset

## 1 Abstract

The 1M07J and 2M84G (and earlier) mask sets of the SG/SH32 and SG/SH8, respectively, have an erratum concerning a brief pulse on I/O pins while the MCU is being powered up. The pulse magnitude and duration are dependent on the power supply rise time. This Engineering Bulletin gives examples of the disturbance and offers suggestions for systems that may be affected by the behavior.

# 2 Description

This engineering bulletin provides additional information regarding the erratum for members of the SG32, SH32, SG8, and SH8 microcontroller (MCU) families. The erratum states "During a power-on-reset, a brief pulse occurs on I/O pins. The brief pulse, which is due to the gating of the integrated pullup resistors, may be able to drive active-high output circuits (for example,

### **Contents**

|   | Abstract    |

|---|-------------|

| 2 | Description |

|   | Summary     |

### Description

relay drivers or NPN transistors) momentarily. Input circuits are not affected."

The integrated pullup resistor on each I/O pin is a weak p-channel MOSFET that is enabled by user software, typically for input pin biasing in an application. During powerup, the pullup is supposed to be disabled, as the port pin is intended to be high impedance. On the mask sets listed above, the pullup is provisionally enabled during the supply ramp until the pin POR logic becomes active. That is, the pullup is not intentionally enabled, and its behavior is dependent on power supply startup characteristics.

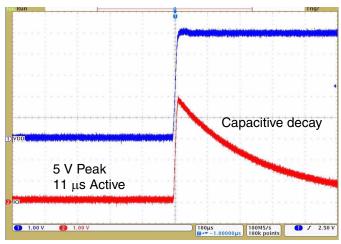

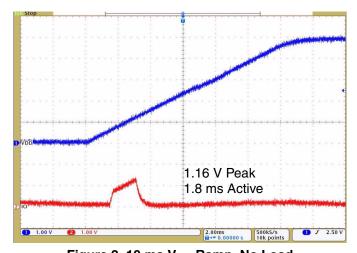

In general, with this erratum faster power supply rise times result in higher pulse amplitudes. Figure 1 shows an I/O pin response during a relatively fast device power-up. Figure 2 shows the response for a much slower power supply ramp. Note that the amplitude of the fast supply is much greater compared to that of the slower supply. Also note the relative duration of the inadvertent pulse – shorter for the fast rise time and longer for the slow rise time.

Figure 1. 10  $\mu$ s  $V_{DD}$  Ramp, No Load

Figure 2. 10 ms  $V_{DD}$  Ramp, No Load

While Freescale cannot provide a mathematical relationship for the responses, we did characterize units to establish the trends. The data shown in Table 1 can be used to determine an appropriate filter to attenuate the pulse(s) in an application if necessary.

Supplementary Information Regarding Brief Pulse Erratum on SG/SH I/O Pins during Power-On-Reset, Rev. 1

| Table 1. Peak Voltage and Pulse Active Time vs V <sub>DD</sub> Ramp Time | eak Voltage | nd Pulse | Active Tir | me vs Vnn | Ramp Tim | ne |

|--------------------------------------------------------------------------|-------------|----------|------------|-----------|----------|----|

|--------------------------------------------------------------------------|-------------|----------|------------|-----------|----------|----|

|                              | No Load                |                         | 100 kΩ                 | 2 Load                  | 10 kΩ Load             |                         |

|------------------------------|------------------------|-------------------------|------------------------|-------------------------|------------------------|-------------------------|

| V <sub>DD</sub> Ramp<br>Time | Peak<br>Voltage<br>(V) | Pulse<br>Active<br>(μs) | Peak<br>Voltage<br>(V) | Pulse<br>Active<br>(μs) | Peak<br>Voltage<br>(V) | Pulse<br>Active<br>(μs) |

| 10 μs                        | 5.00                   | 11                      | 3.79                   | 15                      | 1.23                   | 15                      |

| 50 μs                        | 3.42                   | 28                      | 2.54                   | 27                      | 0.85                   | 27                      |

| 100 μs                       | 2.74                   | 43                      | 2.01                   | 40                      | 0.67                   | 40                      |

| 200 μs                       | 2.26                   | 66                      | 1.64                   | 61                      | 0.56                   | 61                      |

| 500 μs                       | 1.90                   | 128                     | 1.38                   | 114                     | 0.47                   | 114                     |

| 1 ms                         | 1.70                   | 225                     | 1.23                   | 196                     | 0.44                   | 196                     |

| 10 ms                        | 1.16                   | 1800                    | 0.77                   | 1340                    | 0.18                   | 1000                    |

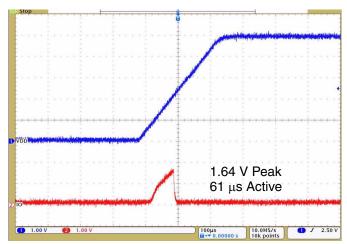

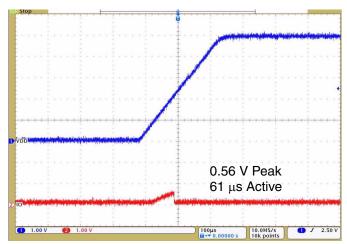

Note the trend with and without loads on the output pins. Figure 3 shows the 200  $\mu s$   $V_{DD}$  ramp time with a 100  $k\Omega$  load, while Figure 4 shows the same ramp time with a 10  $k\Omega$  load. Practically, the no load measurements are not very applicable because most active high outputs will have loads.

Figure 3. 200  $\mu\text{s}$   $\text{V}_{\text{DD}}$  Ramp, 100  $\text{k}\Omega$  Load

Freescale Semiconductor 3

### Summary

Figure 4. 200  $\mu$ s V<sub>DD</sub> Ramp, 10 k $\Omega$  Load

The two main items to consider are output pin usage and power supply ramp time. Critical active high circuits, like relay or TRIAC drivers, that are driven by output pins are the primary concern. In general, these outputs have external pulldown resistors to provide a safe power-up transition. A small capacitor may be the appropriate filter element if the equivalent resistance of the driver network is relatively small ( $<10 \text{ k}\Omega$ ). An additional RC filter may be required if the impedance of the driver network is relatively high ( $>10 \text{ k}\Omega$ ).

Power supply ramp times are dependent on many factors, including input voltage and supply loading. While the scope traces in Figure 1 through Figure 4 show idealized linear rise times (since a pulse generator was used to control the ramps), most system power supplies exhibit traditional capacitive rise times. Power supply rise times are not generally specified in regulator data sheets, so this determination must be made empirically by measuring the ramp in the actual system. A suggestion for a practical range of ramp times would be to allow an order of magnitude above and below the measured time. For instance, a measured rise time of 5 ms would suggest a practical range of 0.5 ms to 50 ms.

What kind of output circuits do not need these precautions? Low frequency indicators like LEDs are not the concern. Likewise, signals that are connected to other logic devices, like serial chips, do not respond to pulses of this duration as the logic chips are powering up as well during this time.

Another aspect that may need consideration is unused pins. Unused or unbonded pins should be terminated by configuring these I/O pins as inputs with pullups enabled, or as outputs driving high or low. Freescale recommends that user software configures the unused and unbonded pins as outputs driving low. In this configuration unused pins are left unconnected on the circuit board.

# 3 Summary

The workaround for the SG/SH erratum is only needed under certain system conditions – critical active-high output pin, fast power supply rise time, and high impedance loading. Otherwise, the erratum workaround will not be a practical system concern.

Freescale Semiconductor 5

### How to Reach Us:

### **Home Page:**

www.freescale.com

### Web Support:

http://www.freescale.com/support

### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405

Denver, Colorado 80217

1-800-441-2447 or +1-303-675-2140

Fax: +1-303-675-2150

LDCForFreescaleSemiconductor@hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale ™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc. 2008-2009. All rights reserved.

EB709 Rev. 1 4/2009