# ES\_LPC11E6x

# **Errata sheet LPC11E6x**

Rev. 1.2 — 19 January 2024

Errata

### **Document information**

| Information | Content                                                                                                                                                                                                                                     |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | LPC11E67JBD48; LPC11E68JBD64; LPC11E68JBD100, LPC11E6x errata                                                                                                                                                                               |

| Abstract    | This errata sheet describes both the known functional problems and any deviations from the electrical specifications known at the release date of this document. Each deviation is assigned a number and its history is tracked in a table. |

# 1 Product identification

The LPC11E6x devices typically have the following top-side marking for LQFP100 packages:

LPC11E6xJBD100

XXXXXX XX

xxxyywwxR[x]

The LPC11E6x devices typically have the following top-side marking for LQFP64 packages:

LPC11E6xJ

XXXXXX XX

xxxyywwxR[x]

The LPC11E6x devices typically have the following top-side marking for LQFP48 packages:

LPC11E6xJ

XX XX

XXXVV

wwxR[x]

Field 'yy' states the year the device was manufactured. Field 'ww' states the week the device was manufactured during that year.

Field 'R' identifies the device revision. This Errata Sheet covers the following revisions of the LPC11E6x:

Table 1. Device revision table

| Revision identifier (R) | Revision description    |

|-------------------------|-------------------------|

| 'A'                     | Initial device revision |

# 2 Errata overview

# Table 2. Errata summary table

| Functional problems | Short description                                                                                                           | Revision identifier | Detailed description |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------|

| UART.1              | The UART controller sets the Idle status bits for receive and transmit before the transmission of the stop bit is complete. | 'A'                 | Section 3.1          |

| ROM.1               | On the LPC11E6x, the ROM inadvertently reports IAP busy status for IAP erase and program operations                         | 'A'                 | Section 3.2          |

#### Table 3. AC/DC deviations table

| AC/DC deviations | Short description | Revision identifier | Detailed description |

|------------------|-------------------|---------------------|----------------------|

| n/a              | n/a               | n/a                 | n/a                  |

#### Table 4. Errata notes table

| Errata notes | Short description | Revision identifier | Detailed description |

|--------------|-------------------|---------------------|----------------------|

| n/a          | n/a               | n/a                 | n/a                  |

ES\_LPC11E6x

All information provided in this document is subject to legal disclaimers.

© 2024 NXP B.V. All rights reserved.

# 3 Functional problems detail

## 3.1 UART.1

#### Introduction:

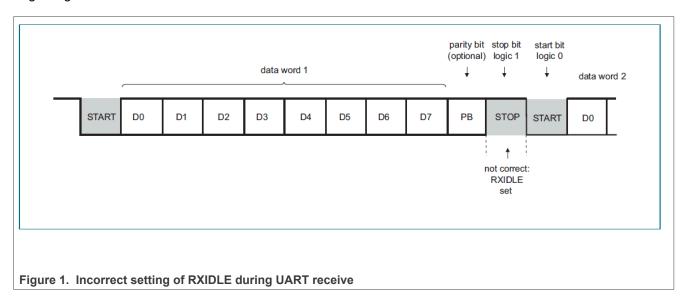

In receive mode, the UART controller provides a status bit (the RXIDLE bit in the UART STAT register) to check whether the receiver is currently receiving data. If RXIDLE is set, the receiver indicates it is idle and does not receive data.

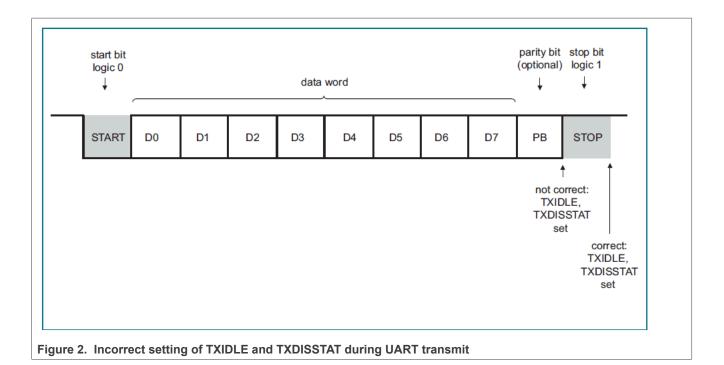

In transmit mode, the UART controller provides two status bits (TXIDLE and TXDISSTAT bits in the UART STAT register) to indicate whether the transmitter is currently transmitting data. The TXIDLE bit is set by the controller after the last stop bit has been transmitted. The TXDISSTAT bit is set by the controller after the transmitter has sent the last stop bit and has become fully idle following a transmit disable executed by setting the TXDIS bit in the UART CTRL register.

The status bits can be used to implement software flow control, but their setting does not affect normal UART operation.

#### Problem:

The RXIDLE bit is incorrectly set for a fraction of the clock cycle between the reception of the last data bit and the reception of the start bit of the next word, that is while the stop bit is received. RXIDLE is cleared at the beginning of the start bit.

Both, TXIDLE and TXDISSTAT are set incorrectly between the last data bit and the stop bit while the transfer is still ongoing.

#### Work-around:

When writing code that checks for the setting of any of the status bits RXIDLE, TXIDLE, TXDISSTAT, check the value of the status bit in the STAT register:

- If status bit = 1, add a delay of one UART bit time (if STOPLEN = 0, one stop bit) or two bit times (if STOPLEN = 1, two stop bits) and check the value of the status bit again:

- If status bit = 1, the receiver is idle.

- If status bit = 0, the receiver is receiving data.

- If the status bit = 0, the receiver is receiving data.

# 3.2 ROM.1: On the LPC11E6x, the ROM inadvertently reports IAP busy status for IAP erase and program operations

## Introduction:

On the LPC11E6x, In-Application Programming (IAP) calls are available to perform erase and write operation on the on-chip flash memory, as directed by the end-user application code. IAP status codes are available for the IAP calls.

### Problem:

For IAP erase (sector and page) calls and IAP copy RAM to flash API calls, the ROM inadvertently reports that the flash programming hardware interface is busy (IAP status code 11).

#### Work-around:

The following software workaround can be implemented in the user application code. The example below is for IAP erase operations and utilizes the interrupt status register of the flash IP to ensure that the IAP erase operation is completed successfully:

```

/* flash controller INT STATUS register address for the workaround */

#define

INT STATUS

((volatile unsigned *)(0x4003CFE0))

END OF BURN

#define

(1 << 1)

END OF ERASE

(1 << 0)

_attribute__((section(".iap_ramfunc")))    uint32_t iap_erase_page(uint8 t

page start, uint8 t page end)

volatile uint32 t dummy = 0;

uint32 t dummy pos = 0;

struct sIAP IAP;

IAP.cmd = IAP ERASE PAGE;

// Erase Page

IAP.par[0] = \overline{page} start;

// Start page

IAP.par[1] = page end;

// End page

IAP.par[2] = SystemCoreClock / 1000; // CCLK in kHz

while (((*INT STATUS) & 0x8) != 0)

dummy = *(volatile uint32 t *)(0x0 + dummy pos);

*INT CLR STATUS = 0x8;

if(((*INT STATUS) & 0x8) != 0x8)

{

break;

/* Find a flash location without ECC error */

dummy_pos += 4;

/* For LPC11E6x, the flash size is 0x10000 */

if (dummy pos \geq 0x10000)

return BUSY;

}

IAP Call(&IAP.cmd, &IAP.stat); // Call IAP Command

if \overline{(IAP.stat} == BUSY)

// If it returns BUSY, wait until program/erase is done

while ((*INT STATUS & (END OF BURN | END OF ERASE)) == 0);

IAP.stat = 0;

return (IAP.stat); // Command Failed

return (0);

}

```

# 4 AC/DC deviations detail

4.1 n/a

# 5 Errata notes detail

5.1 n/a

# 6 Revision history

Table 5. Revision history

| Document ID        | Release date    | Description              |

|--------------------|-----------------|--------------------------|

| ES_LPC11E6x v. 1.2 | 19 January 2024 | Added <u>Section 3.2</u> |

| ES_LPC11E6x v. 1.1 | 22 October 2014 | Added <u>Section 3.1</u> |

| ES_LPC11E6x v. 1   | 1 April 2014    | Initial version.         |

## 7 Note about the source code in the document

Example code shown in this document has the following copyright and BSD-3-Clause license:

Copyright 2024 NXP Redistribution and use in source and binary forms, with or without modification, are permitted provided that the following conditions are met:

- 1. Redistributions of source code must retain the above copyright notice, this list of conditions and the following disclaimer.

- 2. Redistributions in binary form must reproduce the above copyright notice, this list of conditions and the following disclaimer in the documentation and/or other materials must be provided with the distribution.

- 3. Neither the name of the copyright holder nor the names of its contributors may be used to endorse or promote products derived from this software without specific prior written permission.

THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT HOLDER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

# 8 Legal information

## 8.1 Definitions

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

#### 8.2 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at http://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Suitability for use in non-automotive qualified products — Unless this document expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

**Translations** — A non-English (translated) version of a document, including the legal information in that document, is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security — Customer understands that all NXP products may be subject to unidentified vulnerabilities or may support established security standards or specifications with known limitations. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP.

NXP has a Product Security Incident Response Team (PSIRT) (reachable at <a href="mailto:PSIRT@nxp.com">PSIRT@nxp.com</a>) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

**NXP B.V.** — NXP B.V. is not an operating company and it does not distribute or sell products.

### 8.3 Trademarks

Notice: All referenced brands, product names, service names, and trademarks are the property of their respective owners.

NXP — wordmark and logo are trademarks of NXP B.V.

ES\_LPC11E6x

All information provided in this document is subject to legal disclaimers.

© 2024 NXP B.V. All rights reserved.

# **Contents**

| 1   | Product identification                    | 2 |

|-----|-------------------------------------------|---|

| 2   | Errata overview                           |   |

| 3   | Functional problems detail                | 3 |

| 3.1 | UART.1                                    |   |

| 3.2 | ROM.1: On the LPC11E6x, the ROM           |   |

|     | inadvertently reports IAP busy status for |   |

|     | IAP erase and program operations          | 4 |

| 4   | AC/DC deviations detail                   | 6 |

| 4.1 | n/a                                       | 6 |

| 5   | Errata notes detail                       | 6 |

| 5.1 | n/a                                       | 6 |

| 6   | Revision history                          | 6 |

| 7   | Note about the source code in the         |   |

|     | document                                  | 6 |

| 8   | Legal information                         | 7 |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.