## ES\_LPC11U6x Errata sheet LPC11U6x

Rev. 1.5 — 19 January 2024

Errata

#### **Document information**

| Information | Content                                                                                                                                                                                                                                                                |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | LPC11U66JBD48; LPC11U67JBD48; LPC11U67JBD64; LPC11U67JBD100; LPC11U68JBD48; LPC11U68JBD64; LPC11U68JBD100; LPC11U6x errata                                                                                                                                             |

| Abstract    | This errata sheet describes both the known functional problems and any deviations from the electrical specifications known at the release date of this document. Each deviation is assigned a number and its history is tracked in a table at the end of the document. |

## **1 Product identification**

The LPC11U6x devices typically have the following top-side marking for LQFP100 packages:

LPC11U6xJBD100 xxxxxx xx xxxyywwxR[x]

The LPC11U6x devices typically have the following top-side marking for LQFP64 packages:

LPC11U6xJ xxxxxx xx xxxyywwxR[x]

The LPC11U6x devices typically have the following top-side marking for LQFP48 packages:

LPC11U6xJ xx xx xxxyy wwxR[x]

Field 'yy' states the year the device was manufactured. Field 'ww' states the week the device was manufactured during that year.

Field 'R' identifies the device revision. This Errata Sheet covers the following revisions of the LPC11U6x:

| Table 1. | Device | revision | table |

|----------|--------|----------|-------|

|----------|--------|----------|-------|

| Revision identifier (R) | Revision description    |

|-------------------------|-------------------------|

| Ϋ́Α'                    | Initial device revision |

## 2 Errata overview

#### Table 2. Errata summary table

| Functional problems | Short description                                                                                                                                           | Revision identifier | Detailed description |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------|

| USB_ROM.1           | The USB ROM driver routine hwUSB_ResetEP()<br>accidentally corrupts the subsequent word of memory<br>while clearing the STALL bit of the selected endpoint. | ʻA'                 | Section 3.1          |

| USB_ROM.2           | The USBD ROM stack does not split EP0 transfer into multiple packets of 8 bytes (MAXP allowed) in low speed mode.                                           | ʻA'                 | Section 3.2          |

| USB_ROM.3           | FRAME_INT is cleared if new SetConfiguration or USB_RESET are received.                                                                                     | ʻA'                 | Section 3.3          |

| USB_ROM.4           | USB full-speed device fail in the Command/Data/<br>Status Flow after bus reset and bus re-enumeration.                                                      | ʻA'                 | Section 3.4          |

| USB.1               | The USB controller is unable to generate STALL on EP0_OUT.                                                                                                  | 'A'                 | Section 3.5          |

| UART.1              | The UART controller sets the Idle status bits for receive and transmit before the transmission of the stop bit is complete.                                 | ʻA'                 | Section 3.6          |

| ROM.1               | On the LPC11U6x, the ROM inadvertently reports IAP busy status for IAP erase and program operations                                                         | 'A'                 | Section 3.7          |

## ES\_LPC11U6x

| Table 3. AC/DC deviations table |                   |                     |                      |

|---------------------------------|-------------------|---------------------|----------------------|

| AC/DC<br>deviations             | Short description | Revision identifier | Detailed description |

| n/a                             | n/a               | n/a                 | n/a                  |

#### Table 4. Errata notes table

| Errata notes | Short description | Revision identifier | Detailed description |

|--------------|-------------------|---------------------|----------------------|

| n/a          | n/a               | n/a                 | n/a                  |

### 3 Functional problems detail

. . . . . .

#### 3.1 USB\_ROM.1

#### Introduction:

The on-chip USB2.0 full-speed device controller uses the USB endpoint (EP) Command/Status List organized in memory to store the EPs command/status information. Bit 29 indicates the STALL status of the corresponding EP. The USB ROM driver routine hwUSB\_ResetEP(), which is called during SET\_CONFIGURATION and SET\_INTERFACE requests for all EPs present in the corresponding configuration/interface, clears the STALL bit of the selected EPs in Command/Status List as part of EP reset procedure.

#### Problem:

During the EP reset procedure executed by the USB ROM driver routine hwUSB\_ResetEP(), it not only clears the STALL bit of the selected EP but also corrupts the subsequent word of memory. This issue is caused by a software bug in the hwUSB\_ResetEP() routine.

Below is a summary of the runtime errors resulting from this issue:

- Case 1. When reset procedure is invoked on an EP which is at the end of the EP list, this bug will accidentally corrupt the memory area following the EP Command/Status List. In the current version of USB ROM driver this area is used for storing the receiver buffer address for control endpoint (EP0). This corruption causes erratic behavior on control OUT transaction.

- Case 2. When reset procedure is invoked on an EP which is in the beginning or middle of the EP list, this bug will accidentally clear the STALL bit of the subsequent EP in list.

- If hwUSB\_ResetEP() is called during SET\_CONFIGURATION, clearing the STALL bit of the subsequent EP has no consequence since STALL condition is cleared for all EPs during SET\_CONFIGURATION procedure.

- If hwUSB\_ResetEP() is called during SET\_INTERFACE when selecting an ALT interface, this issue could clear STALL condition (if exists) on the subsequent EP. This condition is very rare.

#### Work-around:

The software work-around to address Case 1 is to specify one extra EP in the max\_num\_ep field of the USBD\_API\_INIT\_PARAM\_T structure passed to the ROM driver's hw->init() routine. This extra EP provides a padding buffer to avoid corruption to the subsequent word of memory. This workaround is demonstrated with the line of code highlighted in red in function usb\_init() in the following example.

If your system is affected with Case 2, user should check the "ep\_halt" member of USB\_CORE\_CTRL\_T structure in the SET\_INTERFACE event and set STALL bit for any EP which got cleared due to this bug. This

Errata sheet LPC11U6x

condition is very rare. This workaround is demonstrated with the function StallWorkAround () in the following example. Notice that StallWorkAround is set to be an interface event in the usb\_init() function (highlighted in bold).

```

typedef volatile struct EP LIST {

uint32 t buf ptr;

uint32<sup>t</sup> buf length;

} EP LIST;

ErrorCode t StallWorkAround (USBD HANDLE T hUsb)

{

ErrorCode t ret = LPC OK;

USB CORE CTRL T *pCtrl = (USB CORE CTRL T *) hUsb;

EP LIST *epQueue;

int32 t i;

/*

WORKAROUND for Case 2:

Code clearing STALL bits in endpoint reset routine corrupts memory area

next to the endpoint control data.

* /

if (pCtrl->ep_halt != 0) { /* check if STALL is set for any endpoint */

/* get pointer to HW EP queue */

epQueue = (EP LIST *) LPC USB->EPLISTSTART;

^{\star} check if the HW STALL bit for the endpoint is cleared due to bug. ^{\star/}

for (i = 1; i < pCtrl->max_num_ep; i++) {

/* check OUT EPs */

if ( pCtrl->ep halt & (1 << i)) {

* Check if HW EP queue also has STALL bit = BIT(29) is set */

if (( epQueue[i << 1].buf ptr & BIT(29)) == 0) {

/* bit not set, cleared by BUG. So set it back. */

epQueue[i << 1].buf.ptr |= BIT(29);</pre>

}

}

/* Check IN EPs */

if

( pCtrl->ep halt & (1 << (i + 16))) {

* Check if HW EP queue also has STALL bit = BIT(29) is set */

if (( epQueue[(i << \overline{1}) + 1].buf_ptr & _BIT(29)) == 0) {

/* bit not set, cleared by BUG. So set it back. */

epQueue[(i << 1) + 1].buf ptr |= BIT(29);

}

}

}

}

return ret;

}

/* Initialize USB sub system */

static ErrorCode t usbd init(void)

{

USBD API INIT PARAM T usb param;

USB CORE DESCS T desc;

ADC INIT PARAM T adc param;

ErrorCode t ret = LPC OK;

/* enable clocks and pinmux */

usb pin clk init();

/* initialize USBD ROM API pointer. */

g_pUsbApi = (const USBD_API_T *) LPC_ROM_API->usbdApiBase;

/* initialize call back structures */

memset((void *) &usb_param, 0, sizeof(USBD_API_INIT_PARAM_T));

usb_param.usb_reg_base = LPC_USB0 BASE;

```

© 2024 NXP B.V. All rights reserved.

Errata sheet LPC11U6x

```

/* WORKAROUND for Case 1

For example When EPO, EP1 IN, EP1 OUT and EP2 IN are used we need to

specify usb param.max num ep as \overline{3} here. But as a workaround for this issue

specify usb param.max num ep as 4. So that extra EPs control structure acts

as padding buffer to avoid data corruption. Corruption of padding

memory doesn't affect the stack/program behavior.

*/

usb param.max num ep = 3 + 1;

usb_param.USB_Interface Event = StallWorkAround;

usb_param.mem_base = USB_STACK_MEM_BASE;

usb_param.mem_size = USB_STACK_MEM_SIZE;

/* Set the USB descriptors */

desc.device_desc = (uint8_t *) &USB_DeviceDescriptor[0];

desc.string_desc = (uint8_t *) &USB_StringDescriptor[0];

/* Note, to pass USBCV test full-speed only devices should have both

descriptor arrays point to same location and device qualifier set to 0.

*/

desc.high speed desc = (uint8 t *) &USB FsConfigDescriptor[0];

desc.full speed desc = (uint8 t *) &USB FsConfigDescriptor[0];

desc.device qualifier = 0;

/* USB Initialization */

ret = USBD API->hw->Init(&g hUsb, &desc, &usb param);

if (ret == LPC OK) {

}

```

### 3.2 USB\_ROM.2

#### Introduction:

When USB device operates in low-speed mode the maximum packet length (MAXP) for control transfer and interrupt transfers is restricted to 8 bytes. Hence when more than 8 bytes needs to be transferred, the data should be split into multiple 8 byte packets. But the current ROM stack splits the control transfer into multiples of 64 bytes only.

#### Problem:

Device will not enumerate when used in low-speed mode.

#### Work-around:

The software work-around for this issue is to override the cases where the ROM stack would queue a large transfer and split them into smaller 8 byte packet transfers. Since low speed USB allows only interrupt endpoints, a workaround for HID class implementation is shown below:

```

static ErrorCode_t HID_LowSpeedPatch(USBD_HANDLE_T hUsb, void *data, uint32_t

event)

{

USB_CORE_CTRL_T *pCtrl = (USB_CORE_CTRL_T *) hUsb;

USB_HID_CTRL_T *pHidCtrl = (USB_HID_CTRL_T *) data;

ErrorCode_t ret = ERR_USBD_UNHANDLED;

uint16_t cnt = 0, len = 0;

switch (event) {

case_USB_EVT_SETUP:

if (pCtrl-

>SetupPacket.bmRequestType.BM.Type == REQUEST_STANDARD) {

switch (pCtrl->SetupPacket.bRequest) {

case_USB_REQUEST_GET_DESCRIPTOR:

ES_LPC11U6x

All information provided in this document is subject to legal disclaimers.

0 2024 NXP.B.V.All rights reserved.

```

### Errata sheet LPC11U6x

```

/* handle HID descriptors first */

switch (pCtrl->SetupPacket.wValue.WB.H) {

case HID HID DESCRIPTOR TYPE:

pCtrl->EPOData.pData = pHidCtrl-

>hid desc;

len = ((USB COMMON DESCRIPTOR *)

pHidCtrl->hid desc)->bLength;

ret = LPC OK;

break;

case HID REPORT DESCRIPTOR TYPE:

ret = pHidCtrl-

>HID GetReportDesc(pHidCtrl,

&pCtrl->SetupPacket,

&pCtrl->EPOData.pData, &len);

break;

case HID PHYSICAL DESCRIPTOR TYPE:

if (pHidCtrl->HID GetPhysDesc == 0) {

ret = (ERR USBD STALL); /

* HID Physical Descriptor is not

supported */

else {

ret = pHidCtrl-

>HID GetPhysDesc(pHidCtrl,

&pCtrl-

>SetupPacket,

&pCtrl->EPOData.pData, &len);

break;

default:

ret = pCtrl-

>USB ReqGetDescriptor(pCtrl);

break;

}

break;

case USB REQUEST GET CONFIGURATION:

ret = pCtrl->USB ReqGetConfiguration(pCtrl);

break;

case USB REQUEST GET INTERFACE:

ret = pCtrl->USB ReqGetInterface(pCtrl);

break;

default:

break;

}

}

else if ((pCtrl-

>SetupPacket.bmRequestType.BM.Type == REQUEST CLASS) &&

(pCtrl-

>SetupPacket.bmRequestType.BM.Recipient ==

REQUEST TO INTERFACE) &&

pCtrl-

>SetupPacket.bRequest == HID REQUEST GET REPORT) ) {

pCtrl->EPOData.pData = pCtrl->EPOBuf; /

* point to data to be sent */

* allow user to copy data to EPOBuf or change the pointer to his own

buffer */

ret = pHidCtrl->HID GetReport(pHidCtrl, &pCtrl-

>SetupPacket,

&pCtrl->EPOData.pData, &pCtrl->EPOData.Count);

}

```

Errata sheet LPC11U6x

```

break;

case USB_EVT_IN:

if (pCtrl-

>SetupPacket.bmRequestType.BM.Dir == REQUEST DEVICE TO HOST) {

ret = LPC OK;

}

break;

if (ret == LPC OK) {

if ((len != 0) && (pCtrl->EP0Data.Count > len)) {

pCtrl->EPOData.Count = len;

}

cnt = (pCtrl -

>EPOData.Count > USB MAX PACKET0) ? USB MAX PACKET0 :

pCtrl->EPOData.Count;

cnt = USBD API->hw->WriteEP(pCtrl, 0x80, pCtrl-

>EPOData.pData, cnt);

pCtrl->EPOData.pData += cnt;

pCtrl->EPOData.Count -= cnt;

}

else if (ret == ERR USBD UNHANDLED) {

ret = g defaultHidHdlr(hUsb, data, event);

}

return ret;

}

```

To install this patch handler do the following:

- 1. declare a global variable: static USB\_EP\_HANDLER\_T g\_defaultHidHdlr;

- 2. install the override handler during initialization phase:

```

ret = USBD_API->hid->init(hUsb, &hid_param);

if (ret == LPC_OK) {

g_defaultHidHdlr = pCtrl->ep0_hdlr_cb[pCtrl->num_ep0_hdlrs - 1];

/* store the default CDC handler and replace it with ours */

pCtrl->ep0_hdlr_cb[pCtrl-

>num_ep0_hdlrs - 1] = HID_LowSpeedPatch;

....

}

```

# 3.3 USB\_ROM.3: FRAME\_INT is cleared if new SetConfiguration or USB\_RESET are received.

Introduction:

In the USB ROM API, the function call EnableEvent can be used to enable and disable FRAME\_INT.

Problem:

When the FRAME\_INT is enabled through the USB ROM API call:

```

ErrorCode_t(* USBD_HW_API::EnableEvent)

(USBD_HANDLE_T hUsb, uint32_t EPNum, uint32_t event_type, uint32_t enable),

```

the FRAME\_INT is cleared if new SetConfiguration or USB\_RESET are received.

© 2024 NXP B.V. All rights reserved.

#### Work-around:

Implement the following software work-around in the ISR to ensure that the FRAME\_INT is enabled:

```

void USB_IRQHandler(void)

{

USBD_API->hw->EnableEvent(g_hUsb, 0, USB_EVT_SOF, 1);

USBD_API->hw->ISR(g_hUsb);

}

```

# 3.4 USB\_ROM.4: USB full-speed device fail in the Command/Data/Status Flow after bus reset and bus re-enumeration

#### Introduction:

The LPC11U6x device family includes a USB full-speed interface that can operate in device mode and also, includes USB ROM based drivers. A Bulk-Only Protocol transaction begins with the host sending a CBW to the device and attempting to make the appropriate data transfer (In, Out or none). The device receives the CBW, checks and interprets it, attempts to satisfy the request of the host, and returns status via a CSW.

#### Problem:

When the device fails in the Command/Data/Status Flow, and the host does a bus reset / bus re-enumeration without issuing a Bulk-Only Mass Storage Reset, the USB ROM driver does not re-initialize the MSC variables. This causes the device to fail in the Command/Data/Status Flow after the bus reset / bus re-enumeration.

#### Work-around:

Implement the following software work-around to re-initialize the MSC variables in the USBD stack.

```

*q pMscCtrl;

void

ErrorCode t mwMSC Reset workaround (USBD HANDLE T hUsb)

((USB MSC CTRL T *)g pMscCtrl)->CSW.dSignature = 0;

((USB MSC CTRL T *)g_pMscCtrl)->BulkStage = 0;

return LPC OK;

ErrorCode t mscDisk init(USBD HANDLE T hUsb, USB CORE DESCS T *pDesc,

USBD API INIT PARAM T *pUsbParam)

USBD_MSC_INIT_PARAM_T msc_param;

{

ErrorCode_t ret = LPC_OK;

memset((void *) &msc param, 0, sizeof(USBD MSC INIT PARAM T));

msc param.mem base = pUsbParam->mem base;

msc param.mem size = pUsbParam->mem size;

g pMscCtrl = (void *)msc param.mem base;

ret = USBD API->msc->init(hUsb, &msc param);

/* update memory variables */

pUsbParam->mem_base = msc_param.mem_base;

pUsbParam->mem size = msc param.mem size;

return ret;

}

usb param.USB Reset Event = mwMSC Reset workaround;

ret = USBD API->hw->Init(&g hUsb, &desc, &usb param);

```

Errata sheet LPC11U6x

### 3.5 USB.1: USB controller is unable to generate STALL on EP0\_OUT

#### Introduction:

The LPC11U6x have a full-speed USB device controller with support for 10 physical endpoints.

#### Problem:

The USB device controller is unable to return a STALL handshake on an OUT data packet to endpoint zero. An NAK handshake is returned instead.

#### Work-around:

Endpoint zero is the control endpoint. All requests sent to the control endpoint consist of three stages (SETUP / DATA / STATUS). When an unsupported ControlWrite request (with data phase) is sent by the host to the device, the device is unable to STALL the data phase of this request.

To solve this problem, the device firmware must accept the data transmitted during the data phase of this ControlWrite request and return a STALL handshake when the IN token for the STATUS stage is received.

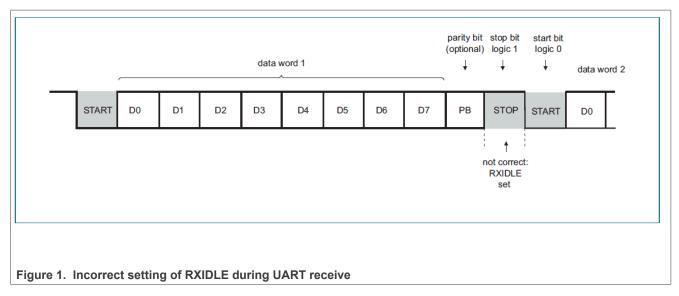

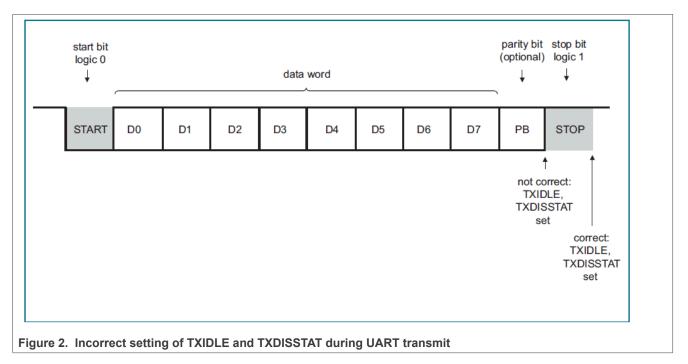

#### 3.6 UART.1

#### Introduction:

In receive mode, the UART controller provides a status bit (the RXIDLE bit in the UART STAT register) to check whether the receiver is currently receiving data. If RXIDLE is set, the receiver indicates it is idle and does not receive data.

In transmit mode, the UART controller provides two status bits (TXIDLE and TXDISSTAT bits in the UART STAT register) to indicate whether the transmitter is currently transmitting data. The TXIDLE bit is set by the controller after the last stop bit has been transmitted. The TXDISSTAT bit is set by the controller after the transmitter has sent the last stop bit and has become fully idle following a transmit disable executed by setting the TXDIS bit in the UART CTRL register.

The status bits can be used to implement software flow control, but their setting does not affect normal UART operation.

#### Problem:

The RXIDLE bit is incorrectly set for a fraction of the clock cycle between the reception of the last data bit and the reception of the start bit of the next word, that is while the stop bit is received. RXIDLE is cleared at the beginning of the start bit.

9/14

#### Errata sheet LPC11U6x

Both, TXIDLE and TXDISSTAT are set incorrectly between the last data bit and the stop bit while the transfer is still ongoing.

#### Work-around:

When writing code that checks for the setting of any of the status bits RXIDLE, TXIDLE, TXDISSTAT, check the value of the status bit in the STAT register:

- If status bit = 1, add a delay of one UART bit time (if STOPLEN = 0, one stop bit) or two bit times (if STOPLEN

- = 1, two stop bits) and check the value of the status bit again:

- If status bit = 1, the receiver is idle.

- If status bit = 0, the receiver is receiving data.

- If the status bit = 0, the receiver is receiving data.

© 2024 NXP B.V. All rights reserved.

# 3.7 ROM.1: On the LPC11U6x, the ROM inadvertently reports IAP busy status for IAP erase and program operations

#### Introduction:

On the LPC111U6x, In-Application Programming (IAP) calls are available to perform erase and write operation on the on-chip flash memory, as directed by the end-user application code. IAP status codes are available for the IAP calls.

#### Problem:

For IAP erase (sector and page) calls and IAP copy RAM to flash API calls, the ROM inadvertently reports that the flash programming hardware interface is busy (IAP status code 11).

#### Work-around:

The following software workaround can be implemented in the user application code. The example below is for IAP erase operations and utilizes the interrupt status register of the flash IP to ensure that the IAP erase operation is completed successfully:

```

/* flash controller INT STATUS register address for the workaround */

#define INT_STATUS ((volatile unsigned *)(0x4003CFE0))

END OF BURN

#define

(1<<1)

END OF ERASE

(1<<0)

#define

_attribute__((section(".iap_ramfunc"))) uint32_t iap_erase_page(uint8_t page_start, uint8_t page_end)

{

volatile uint32 t dummy = 0;

uint32 t dummy pos = 0;

struct sIAP IAP;

IAP.cmd = IAP ERASE PAGE;

// Erase Page

IAP.par[0] = page start;

// Start page

IAP.par[1] = page end;

// End page

IAP.par[2] = SystemCoreClock / 1000; // CCLK in kHz

while (((*INT STATUS) & 0x8) != 0)

{

dummy = *(volatile uint32 t *)(0x0 + dummy pos);

*INT CLR STATUS = 0x8;

if(((*INT STATUS) & 0x8) != 0x8)

{

break;

}

/* Find a flash location without ECC error */

dummy pos += 4;

/* For LPC11U6x, the flash size is 0x10000 */

if (dummy pos >= 0x10000)

{

return BUSY;

}

}

IAP Call(&IAP.cmd, &IAP.stat); // Call IAP Command

if (IAP.stat == BUSY)

{

// If it returns BUSY, wait until program/erase is done

while ((*INT STATUS & (END OF BURN | END OF ERASE)) == 0);

IAP.stat = 0;

```

```

return (IAP.stat); // Command Failed

}

return (0);

}

```

## 4 Revision history

Table 5. Revision history

| Document ID        | Release date    | Description                                                                                                                                                                         |

|--------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ES_LPC11U6x v. 1.5 | 19 January 2024 | Added Section 3.7                                                                                                                                                                   |

| ES_LPC11U6x v. 1.4 | 7 March 2018    | Added Section 3.4                                                                                                                                                                   |

| ES_LPC11U6x v. 1.3 | 4 August 2017   | Added Section 3.3                                                                                                                                                                   |

| ES_LPC11U6x v. 1.2 | 22 October 2015 | <ul> <li>Added <u>Section 3.6</u></li> <li>Added <u>Section 3.1</u></li> </ul>                                                                                                      |

| ES_LPC11U6x v. 1.1 | 28 July 2014    | <ul> <li>Corrected <u>Section 3.1</u> work-around.</li> <li>Corrected part marking information.</li> <li>Parts added: LPC11U67JBD100, LPC11U67JBD64, LPC11U66<br/>JBD48.</li> </ul> |

| ES_LPC11U6x v. 1.0 | 15 January 2014 | Initial version.                                                                                                                                                                    |

## 5 Note about the source code in the document

Example code shown in this document has the following copyright and BSD-3-Clause license:

Copyright 2024 NXP Redistribution and use in source and binary forms, with or without modification, are permitted provided that the following conditions are met:

- 1. Redistributions of source code must retain the above copyright notice, this list of conditions and the following disclaimer.

- 2. Redistributions in binary form must reproduce the above copyright notice, this list of conditions and the following disclaimer in the documentation and/or other materials must be provided with the distribution.

- 3. Neither the name of the copyright holder nor the names of its contributors may be used to endorse or promote products derived from this software without specific prior written permission.

THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT HOLDER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

Errata sheet LPC11U6x

## Legal information

### 6.1 Definitions

Draft - A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

### 6.2 Disclaimers

Limited warranty and liability - Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors

Right to make changes - NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use - NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk

Applications — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Terms and conditions of commercial sale - NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at http://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

Export control - This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Suitability for use in non-automotive qualified products - Unless this document expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

Translations — A non-English (translated) version of a document, including the legal information in that document, is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security - Customer understands that all NXP products may be subject to unidentified vulnerabilities or may support established security standards or specifications with known limitations. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP.

NXP has a Product Security Incident Response Team (PSIRT) (reachable at PSIRT@nxp.com) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

NXP B.V. - NXP B.V. is not an operating company and it does not distribute or sell products.

### 6.3 Trademarks

Notice: All referenced brands, product names, service names, and trademarks are the property of their respective owners.

NXP — wordmark and logo are trademarks of NXP B.V.

## Errata sheet LPC11U6x

### Contents

| 1   | Product identification                    | 2 |

|-----|-------------------------------------------|---|

| 2   | Errata overview                           | 2 |

| 3   | Functional problems detail                | 3 |

| 3.1 | USB ROM.1                                 |   |

| 3.2 | USB_ROM.2                                 | 5 |

| 3.3 | USB_ROM.3: FRAME_INT is cleared if        |   |

|     | new SetConfiguration or USB_RESET are     |   |

|     | received.                                 | 7 |

| 3.4 | USB_ROM.4: USB full-speed device fail in  |   |

|     | the Command/Data/Status Flow after bus    |   |

|     | reset and bus re-enumeration              | 8 |

| 3.5 | USB.1: USB controller is unable to        |   |

|     | generate STALL on EP0_OUT                 | 9 |

| 3.6 | ŬART.1                                    |   |

| 3.7 | ROM.1: On the LPC11U6x, the ROM           |   |

|     | inadvertently reports IAP busy status for |   |

|     | IAP erase and program operations1         | 1 |

| 4   | Revision history1                         |   |

| 5   | Note about the source code in the         |   |

|     | document1                                 | 2 |

| 6   | Legal information1                        | 3 |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

© 2024 NXP B.V.

All rights reserved.

For more information, please visit: http://www.nxp.com

Date of release: 19 January 2024 Document identifier: ES\_LPC11U6x