Enhanced security, memory expansion and flexible I/O capabilities

# Kinetis<sup>®</sup> K8x MCU Family

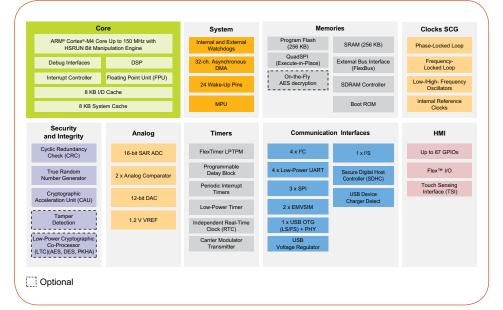

Based on the Arm<sup>®</sup> Cortex<sup>®</sup>-M4 core, the K8x microcontroller (MCU) family offers the security, scalability and flexibility to address the challenges of creating smart devices for the Internet of Tomorrow.

The K8x MCU family extends the Kinetis portfolio with advanced security capabilities including:

- Boot ROM to support encrypted firmware updates

- Automatic AES Decryption and execution from external serial NOR flash memory

- ▶ Hardware AES acceleration

- Support for public key cryptography

Kinetis K8x MCUs offer symmetric cryptographic acceleration as a standard feature along with full-speed USB 2.0 On-The-Go (OTG), including options for crystal-less device functionality. K8x MCUs have 256 KB of embedded flash and 256 KB SRAM. In addition the integrated QuadSPI interface supports connections to non-volatile memory (serial NOR), allowing developers to expand beyond the boundaries of a traditional MCU.

### TARGET APPLICATIONS

- Point-of-sale (POS)

- Building control

- Home automation and security

- IoT data concentrators

- Portable healthcare

- Smart energy gateways

- Wearables

#### **BENEFITS**

- CPU and system cache reduce latency of memory resources, lowering power consumption and improving performance

- Separate I/O power domain for up to 14 pins allow operations without the need for external level translators

- Flex<sup>™</sup> I/O peripheral expands MCU capabilities by emulating serial, parallel, or custom interfaces using software drivers provided by the Kinetis SDK

- $\blacktriangleright$  Low-power operation with state retention stop mode down to 5  $\mu A$  with fast wake-up time and lowest power mode with only 330 nA

# COMPREHENSIVE ENABLEMENT SOLUTIONS

# Kinetis software development kit (SDK) www.nxp.com/ksdk

- Kinetis SDK is a collection of software enablement for NXP Kinetis microcontrollers that includes system startup, peripheral drivers, stacks and middleware, with new support for symmetric and asymmetric cryptographic acceleration

- Pre-integrated real-time operation systems (RTOS) kernels, including FreeRTOS<sup>™</sup>, Micrium<sup>®</sup> µC/OS-II<sup>®</sup> and µC/OS-III<sup>®</sup>

- All software is provided free-of-charge as assembly and C source code under permissive and open-source licensing

- Includes software examples demonstrating the usage of the HAL, peripheral drivers, middleware and RTOSes

# Processor Expert<sup>®</sup> software configuration tool

Complimentary software configuration tool providing I/O allocation and pin initialization and configuration of hardware abstraction and peripheral drivers

### Toolchain

- ► Atollic<sup>®</sup> TrueSTUDIO<sup>®</sup>

- ▶ IAR Embedded Workbench®

- Arm Keil<sup>®</sup> Microcontroller Development Kit

- ▶ SOMNIUM<sup>®</sup> DRT Cortex-M IDE

- Kinetis Design Studio IDE

- No-cost integrated development environment (IDE) for Kinetis MCUs

- Eclipse and GCC-based IDE for C/C++ editing, compiling and debugging

### STANDARD KEY FEATURES

# Bootloader

- Common bootloader for all Kinetis MCUs

- In-system flash programming over a serial connection: erase, program, verify

- ROM-based bootloader with open-source software and host-side programming utilities

#### **Development Hardware**

- FRDM-K28F: Freedom development board

- Low cost

- Arduino<sup>®</sup> R3 compatible

- TWR-K80F150M: Tower<sup>®</sup> System modular development platform

- Rapid prototyping and evaluation

- Interchangeable modules

- TWR-PoS-K81: Point-of-sale (POS) development kit

|                                                                                                                               | CPU                                                                           | Memory                                                                                             | Packages     | Comms             | Security                                |                                                                     |                                                                  |             |

|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--------------|-------------------|-----------------------------------------|---------------------------------------------------------------------|------------------------------------------------------------------|-------------|

| Standard key features<br>UART, I²C, I²S, SPI,<br>16-bit ADC, 12-bit DAC,<br>timers, comparators,<br>True RNG, CRC<br>and GPIO | Arm <sup>®</sup> Cortex <sup>®</sup> -M4<br>with Floating Point<br>Unit (FPU) |                                                                                                    |              | USB<br>Full-speed | Symmetric Crypto<br>Accelerator (mmCAU) | 256-bit AES/192-bit<br>3DES/public key Crypto<br>Co-processor (LTC) | On-the-Fly 128-bit AES<br>decryption from external<br>Serial NOR | Anti-tamper |

| K80                                                                                                                           |                                                                               | 256 KB Flash,<br>256 KB SRAM,<br>8 KB System + 8 KB I/D cache,<br>XIP QuadSPI,<br>SDRAM Controller | MAPBGA, LQFP | x                 | x                                       |                                                                     |                                                                  |             |

| K81                                                                                                                           | 150 MHz                                                                       |                                                                                                    |              | x                 | x                                       | x                                                                   | x                                                                | x           |

| K82                                                                                                                           |                                                                               |                                                                                                    |              | x                 | x                                       | x                                                                   | x                                                                |             |

#### **ADVANCED SECURITY ARCHITECTURE KEY FEATURES\***

| P           | Products    |             | Features                                                                                                                                                                                           | Benefit                                                                                                                                                                                                                                                                                                 | Feature details                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|-------------|-------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|             |             |             | Encrypted firmware updates boot ROM                                                                                                                                                                | Secure firmware update with built in ROM<br>routines to reduce software overhead and<br>complexity                                                                                                                                                                                                      | <ul> <li>Firmware is encrypted by an AES 128-bit key</li> <li>Fully supports internal flash security, including ability to mass erase or unlock security via the backdoor key</li> <li>Multiple options for executing the bootloader either at system start-up or under application control at runtime</li> <li>The ability to configure the QuadSPI interface is based on a configuration block located in the external QuadSPI</li> </ul> |  |  |

| K<br>8<br>0 |             |             | Flash access control (FAC) configurable<br>memory protection scheme designed to<br>allow end users to utilize software libraries<br>while offering programmable restrictions to<br>these libraries | Protection of software IP                                                                                                                                                                                                                                                                               | <ul> <li>Non-volatile control registers to set access<br/>privileges of on-chip flash resources</li> <li>Supervisor or execute-only access can be<br/>set for up to 64 different segments</li> </ul>                                                                                                                                                                                                                                        |  |  |

|             | K<br>8<br>2 | K<br>8<br>1 | Hardware and software mechanisms for<br>acceleration of symmetric cryptography and<br>hashing functions                                                                                            | <ul> <li>Reduces CPU loading for cryptographic functions</li> <li>Simplifies the implementation of higher level security functions nad network security standards</li> <li>For firmware updates, hashing of firmware can be used with encryption keys to ensure that the firmware is trusted</li> </ul> | <ul> <li>Hardware implementation of security operations symmetrical cryptography</li> <li>Supports DES, 3DES, AES, MD5, SHA 1 and SHA 256 algorithms</li> </ul>                                                                                                                                                                                                                                                                             |  |  |

|             |             |             |                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|             |             |             | Cryptographic co-processor for AES, DES and public key cryptography                                                                                                                                | <ul> <li>Offload CPU and reduced software footprint</li> <li>Acceleration for RSA2048, ECDSA and ECDH reduces the latency for authentication</li> </ul>                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|             |             |             | On-the-fly AES decryption from external serial NOR flash                                                                                                                                           | Easily secure off-chip firmware                                                                                                                                                                                                                                                                         | Hardware module supporting AES128<br>counter mode decryptions on external flash<br>data fetched by the QuadSPI                                                                                                                                                                                                                                                                                                                              |  |  |

|             |             |             |                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|             |             |             | Tamper detect module with up to eight tamper pins                                                                                                                                                  | Reduce external circuits needed to support anti-tamper mechanisms                                                                                                                                                                                                                                       | <ul> <li>Secure key storage space with<br/>asynchronous erasure when external tamper<br/>events occur</li> <li>Tamper detection for pin, temperature,<br/>voltage and clock, as well as active tamper</li> </ul>                                                                                                                                                                                                                            |  |  |

|             |             |             | Secure session RAM                                                                                                                                                                                 | Memory scratch pad for secure functions                                                                                                                                                                                                                                                                 | RAM memory block designed for storage<br>of sensitive information (such as encryption<br>session keys) which is automatically cleared in<br>the event of the detection of a tamper event                                                                                                                                                                                                                                                    |  |  |

\*Security features within the Kinetis K8x MCU family are incremental. For a full list of security features offered with Kinetis MCUs, visit: www.nxp.com/security.

#### www.nxp.com/Kinetis/Kseries

NXP and the NXP logo, Kinetis, Processor Expert and Tower are trademarks of NXP Semiconductors. Reg. U.S. Pat. & Tm. Off. All other product or service names are the property of their respective owners. Arm, Cortex and Keil are registered trademarks of Arm Limited (or its subsidiaries) in the EU and/or elsewhere. mbed is a registered trademark of Arm Limited (or its subsidiaries) in the EU and/or elsewhere. MI rights reserved. © 2018 NXP B.V.