Enterprise-class security and packet acceleration in a 1 W typical power microprocessor

# **QorlQ Layerscape® LS1012A Communications Processor**

The Layerscape LS1012A processor provides intelligent integration and extreme power efficiency in a small 9.6  $\times$  9.6 mm package for fanless, small form factor networking and IoT applications.

## TARGET APPLICATIONS

- ▶ Trust-enabled IoT gateways

- Consumer NAS

- Mobile NAS (battery powered)

- Ethernet drives for data center center storage

- Entry-level broadband Ethernet gateways

- Building and factory automation

Incorporating a 64-bit Arm<sup>®</sup> Cortex<sup>®</sup>-A53 core, the LS1012A processor delivers CoreMark<sup>®</sup> performance of over 4,000 as well as hardware acceleration for packet processing and security, and the best overall performance of any 1 W typical power communications processor.

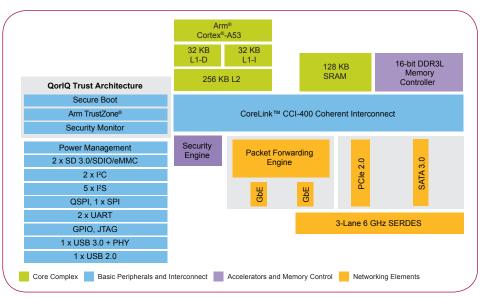

#### **CORE COMPLEX**

The LS1012A processor integrates a single Arm Cortex-A53 core running up to 1 GHz with ECC-protected L1 and L2

caches and incorporates the same trust architecture and software compatibility of higher-tier Layerscape family devices. The LS1012A processor features 32 KB of L1 instruction and data cache and 256 KB of coherent L2 cache. In addition, the Cortex-A53 core features the NEON™ SimD module and dual-precision floating point unit (FPU). The memory controller supports 16-bit DDR3L memory devices at 1 GHz.

## SYSTEM INTERFACES AND NETWORKING

The LS1012A processor features a three-lane, 6 GHz multiprotocol SerDes that provides support for high-speed interfaces, including up to two Gigabit Ethernet ports, DMA-controlled PCI Express<sup>®</sup> generation 2.0 port, and one SATA 3.0 port. The LS1012A processor also features dual USB controllers—one supporting SuperSpeed USB 3.0 with integrated PHY, the other supporting USB 2.0 functions. Additional interfaces include QuadSPI and support for SD/MMC.

The LS1012A includes a hardware packet forwarding engine (PFE) which offloads processing of IP packets from the main CPU, yielding higher performance and lower power than pure software processing can achieve. The PFE is capable of 2 Gbit/s IP forwarding even with the smallest packets, with virtually no CPU load.

# COMPLETE ENABLEMENT, RICH ECOSYSTEM

For customer evaluation, the LS1012A processor is supported by an evaluation board featuring an integrated on-board probe for further cost savings, along with third-party platforms developed by NXP's embedded board solution partners. Evaluation kits include a Linux<sup>®</sup> BSP with optimized drivers to support peripherals and a six-month evaluation license for CodeWarrior development tools. For quick product prototyping, NXP offers the FRYW-LS1012A board with a builtin mikroBUS®Click Module that opens the door to easy expansion through hundreds of powerful click modules supporting sensors, actuators, memories and displays.

All LS series devices are supported by our <u>Product Longevity Program</u> to ensure a stable supply of products, as well as our extensive third-party ecosystem, the largest and most established in the communications market. In conjunction with our expertise and worldwide support infrastructure, the ecosystem helps customers accelerate their migration from both competitive solutions and from legacy NXP devices, preserve investment costs and reduce time-to-market.

## LS1012A BLOCK DIAGRAM

## LS1012A FEATURES

| 64-bit Arm <sup>®</sup> Cortex <sup>®</sup> -A53 core                                                       | Extreme power efficiency, delivering over 4,000 CoreMarks®<br>at 1 W typical power                                                                                |

|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ECC-protected cache memories                                                                                | First 1 W typical power embedded processor featuring Arm<br>Cortex-A53 core with ECC protected caches and coherent<br>256 KB L2 for high reliability applications |

| Rich connectivity and peripheral<br>features including PCI Express® Gen2,<br>USB 3.0, SATA 3, QuadSPI, SDIO | High integration that enables support for 802.11ac modules<br>and high bandwidth connectivity for ASICs, 4G/LTE, SATA,<br>low-cost NOR Flash                      |

| Packet acceleration engine                                                                                  | Delivers hardware acceleration for outstanding IP forwarding and NAS performance                                                                                  |

| Security and trust architecture                                                                             | Support for Arm TrustZone® and secure boot, together with high performance cryptographic processing and manufacturing protection                                  |

| Low-cost board designs                                                                                      | The LS1012A package is engineered to support low-cost,<br>4-layer board designs to minimize system costs                                                          |

#### www.nxp.com/QorlQ

NXP, the NXP logo, Freescale, CodeWarrior, Layerscape, QorlQ and SMARTMOS, are trademarks of NXP B.V. All other product or service names are the property of their respective owners. ARM, Cortex and TrustZone are registered trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. CoreLink and NEON are trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved. © 2018 NXP B.V. Document Number: LS1012AFS REV 0