Enabling secure and connected IoT applications and connected IoT products

## **QorlQ LS2045A and LS2085A Communications Processors**

The QorIQ LS2 family of communications processors delivers performance and integration for the smarter, more capable networks of tomorrow.

### TARGET APPLICATIONS

- ▶ SDN/OpenFlow<sup>™</sup> switching

- NFV solutions

- Enterprise routing

- Wireless access

- Datacenter processing

- Military and aerospace

The QorlQ LS2045A and LS2085A multicore processors combine four and eight ARM® Cortex®-A57 cores respectively with the advanced, high-performance datapath and network peripheral interfaces required for networking, telecom/datacom, wireless infrastructure, military and aerospace applications.

The QorlQ LS2 family includes our second-generation Data Path Acceleration Architecture (DPAA2). DPAA2 provides the infrastructure required to support simplified and secure networking interface and accelerator sharing by multiple general purpose CPU cores, while also providing a range of powerful acceleration engines to off-load software running on the CPUs.

The ARM general purpose processors and DPAA2 are supported by a powerful software toolkit that provides a higher level of hardware abstraction and makes software development quick and simple. This combination balances ease-of-use with high performance processing in a Linux<sup>®</sup> environment that is familiar to any software programmer. Customers can fully exploit the underlying hardware and easily adapt to network changes for real time 'soft' control over the network.

#### **SOFTWARE TOOLKIT**

We have significant and increasing global investment in software for the embedded marketplace. Our software development kit (SDK) delivers foundational technologies (user space, fast path, virtualization) that are continuously 'upstreamed' to support the networking portfolio. With 13+ years experience of commercial ARM software tooling, operating system development and delivery, we continue to be a strong supporter of open source and industry software consortia, including Linaro and the Linux Foundation.

### UNPARALLELED INTEGRATION

QorlQ LS2 family processors integrate up to eight 10 Gbit/s and eight 1 Gbit/s Ethernet interfaces with L2 switching capability for PCIe<sup>®</sup> controllers (supporting SR-IOV) and next-generation SATAIII and USB3 controllers. The next-generation datapath is complemented with high-performance acceleration, including security and trust, pattern matching and data compression.

# NP

## INE I WORKING PERFORMANCE

The QorlQ LS2 processors contain an Advanced I/O Processor that offloads the general purpose ARM Cortex®-A57 cores with in-line or fully autonomous networking functions, involving complex look-ups, header manipulations, and even encapsulations and encryption. A dedicated datapath memory controller is available to support lookup acceleration and packet processing needs.

The next-generation datapath also provides necessary and proven acceleration such as crypto acceleration, Pattern Match/ RegEx and Data Compression Engine. DPAA2 also now integrates L2 switching, allowing the QorIQ LS2 processors eight 10 Gbit/s Ethernet and eight 1 Gbit/s Ethernet ports that can be configured as an 88 Gbit/s L2 switch.

## COMPLETE ENABLEMENT, RICH ECOSYSTEM

The QorlQ LS2 family includes a comprehensive ecosystem to assure that ease-of-use is first priority. The complete offering includes:

- APIs that are compliant with industrystandard consortiums, including Linaro OpenDataPath (ODP).

- Management software that takes care of setup, initialization and teardown of interfaces, accelerators and networking functions

- Functional datapath libraries that are performance optimized

- VortiQa software applications that are bundled for quick networking application deployment

- Tools (e.g., accelerators, debug) to make sure you spend your time creating value added software

- Powerful combination of proptrietary and ARM ecosystems for support

- Open-source software, available upstream for all customers to leverage

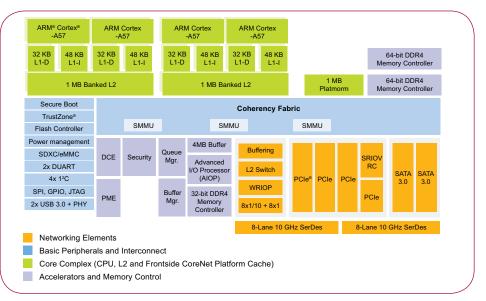

## QorIQ LS2085A PROCESSOR BLOCK DIAGRAM

## QorIQ LS2 FAMILY COMPARISON CHART

|                                       | LS2085A   | LS2045A |

|---------------------------------------|-----------|---------|

| Cores                                 | 8         | 4       |

| Cortex-A57, up to 2 GHz/L2 Cache (MB) | 8/4       | 4/2     |

| Advanced I/O Processor                | 40 Gbit/s |         |

| L2 Switch                             | 88 Gbit/s |         |

### **QorlQ LS2 FAMILY FEATURES**

| Up to Eight Cores Built on<br>ARM Architecture• 8 × Cortex-A57 CPUs, 64-bit, 2 GHz, clusters of two cores sharing<br>1 MB L2 cache<br>• 1 MB L3 cache and 4 MB of cache component memoryHierarchical Interconnect<br>Fabric• Coherency fabric supporting coherent and non-coherent transactions<br>with prioritization and bandwidth allocationDDR Controllers• Two 64-bit DDR4 SDRAM memory controllers with ECC and interleaving<br>support, up to 2.1 GT/s<br>• One secondary 32-bit DDR4 memory controller for the datapath,<br>up to 1.6 GT/sAccelerated Packet<br>Processing• Advanced I/O processor, up to 40 Gbit/s complex packet processing<br>• 20 Gbit/s SEC crypto acceleration<br>• 10 Gbit/s pattern matching engine<br>• 20 Gbit/s data compression engineExpress Packet I/O<br>Network I/O• Supports 1 × 8, 4 × 4, 4 × 2, 4 × 1 PCle Gen 3 controllers<br>• SR-IOV support, root complex<br>• 2 × SATA 3.0, 2 × USB 3.0 with PHYNetwork I/O<br>Network I/O• Wire rate I/O processor, with HW parsing, classification, and<br>policing, featuring:<br>• Eight 1 G<br>• L2 switching on the Ethernet interface<br>• XAU/XFI/KR and SGMII<br>• MACSec on up to four 1/10 GbEVirtualization• Support for HW virtualization and partitioning enforcement |                    |                                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Fabricwith prioritization and bandwidth allocationDDR Controllers• Two 64-bit DDR4 SDRAM memory controllers with ECC and interleaving<br>support, up to 2.1 GT/s<br>• One secondary 32-bit DDR4 memory controller for the datapath,<br>up to 1.6 GT/sAccelerated Packet<br>Processing• Advanced I/O processor, up to 40 Gbit/s complex packet processing<br>• 20 Gbit/s SEC crypto acceleration<br>• 10 Gbit/s pattern matching engine<br>• 20 Gbit/s data compression engineExpress Packet I/O• Supports 1 x 8, 4 x 4, 4 x 2, 4 x 1 PCle Gen 3 controllers<br>• SR-IOV support, root complex<br>• 2 x SATA 3.0, 2 x USB 3.0 with PHYNetwork I/O• Wire rate I/O processor, with HW parsing, classification, and<br>policing, featuring:<br>• Eight 1/10 GbE + eight 1 G<br>• L2 switching on the Ethernet interface<br>• XAUI/XFI/KR and SGMII<br>• MACSec on up to four 1/10 GbE                                                                                                                                                                                                                                                                                                                                                                                    |                    | 1 MB L2 cache                                                                                                               |

| support, up to 2.1 GT/sOne secondary 32-bit DDR4 memory controller for the datapath,<br>up to 1.6 GT/sAccelerated Packet<br>ProcessingProcessing• Advanced I/O processor, up to 40 Gbit/s complex packet processing<br>• 20 Gbit/s SEC crypto acceleration<br>• 10 Gbit/s pattern matching engine<br>• 20 Gbit/s data compression engineExpress Packet I/O• Supports 1 x 8, 4 x 4, 4 x 2, 4 x 1 PCIe Gen 3 controllers<br>• SR-IOV support, root complex<br>• 2 x SATA 3.0, 2 x USB 3.0 with PHYNetwork I/O• Wire rate I/O processor, with HW parsing, classification, and<br>policing, featuring:<br>• Eight 1/10 GbE + eight 1 G<br>• L2 switching on the Ethernet interface<br>• XAUI/XFI/KR and SGMII<br>• MACSec on up to four 1/10 GbE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                    |                                                                                                                             |

| Processing       20 Gbit/s SEC crypto acceleration         10 Gbit/s pattern matching engine         20 Gbit/s data compression engine         Express Packet I/O         Supports 1 x 8, 4 x 4, 4 x 2, 4 x 1 PCIe Gen 3 controllers         SR-IOV support, root complex         2 x SATA 3.0, 2 x USB 3.0 with PHY         Network I/O         Wire rate I/O processor, with HW parsing, classification, and policing, featuring:         Eight 1/10 GbE + eight 1 G         1 L2 switching on the Ethernet interface         XAUI/XFI/KR and SGMII         MACSec on up to four 1/10 GbE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | DDR Controllers    | <ul><li>support, up to 2.1 GT/s</li><li>One secondary 32-bit DDR4 memory controller for the datapath,</li></ul>             |

| <ul> <li>SR-IOV support, root complex</li> <li>2 x SATA 3.0, 2 x USB 3.0 with PHY</li> <li>Wire rate I/O processor, with HW parsing, classification, and policing, featuring:         <ul> <li>Eight 1/10 GbE + eight 1 G</li> <li>L2 switching on the Ethernet interface</li> <li>XAUI/XFI/KR and SGMII</li> <li>MACSec on up to four 1/10 GbE</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                    | <ul><li> 20 Gbit/s SEC crypto acceleration</li><li> 10 Gbit/s pattern matching engine</li></ul>                             |

| policing, featuring:<br>• Eight 1/10 GbE + eight 1 G<br>• L2 switching on the Ethernet interface<br>• XAUI/XFI/KR and SGMII<br>• MACSec on up to four 1/10 GbE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Express Packet I/O | SR-IOV support, root complex                                                                                                |

| Virtualization     Support for HW virtualization and partitioning enforcement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Network I/O        | policing, featuring:<br>• Eight 1/10 GbE + eight 1 G<br>• L2 switching on the Ethernet interface<br>• XAUI/XFI/KR and SGMII |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Virtualization     | Support for HW virtualization and partitioning enforcement                                                                  |

#### www.nxp.com/QorlQ

© 2014–2015 Freescale Semiconductor, Inc.

QorlQ and VortiQa are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. Layerscape is a trademark of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. ARM, Cortex And TrustZone are registered trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved.

Document Number: LS2FAMILYFS REV 5 cc