32-bit Automotive MCUs

# Qorivva MPC5606E

# MPC5606E MCU for automotive video compression and transmission over Ethernet

### **Overview**

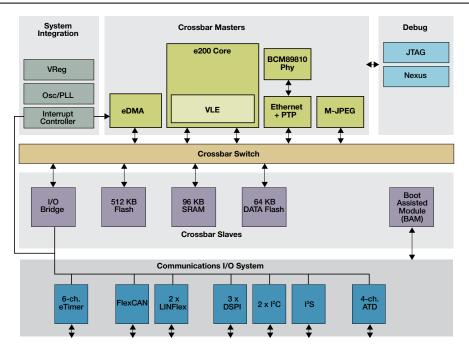

The MPC5606E is part of the Qorivva family of (MCUs) and is built on Power Architecture<sup>®</sup> technology, with variable-length encoding (VLE). This core complies with the Power Architecture embedded category and is 100 percent user mode-compatible with the original PowerPC user instruction set architecture (UISA).

The MPC5606E MCU is a gateway system designed to move data from different sources via Ethernet to a receiving system and vice versa. The supported data sources and sinks are:

- Video data (with 8/10/12 bits per data word)

- Audio data (6 x stereo channels)

- RADAR data (2 x 12-bit with <1 us per sample, digitized externally and read in via DSPI)

- Other serial communication interfaces, including FlexCAN, LINFlex and DSPI

- The MPC5606E also includes a BCM89810 BroadR-Reach compatible physical interface

# Qorivva MPC5606E MCU

Advanced Driver Assistance Systems

- 360-degree Surround View

- Camera-based Park Assist

Ethernet has a bandwidth of 10/100 Mbps supporting precision time stamping (IEEE® 1588). Unshielded twisted pair cables are then used to transfer information via Eithernet throughout the car, resulting in reduced wiring costs achieved through high bandwidth data links.

A comprehensive suite of hardware and software development tools is available to help simplify and speed system design. Development support is available from leading tools vendors providing compilers, debuggers and simulation development environments.

#### **Highlights**

The advanced driver assistance market is growing fast. As historically premium applications such as camera based park assist systems proliferate into the mid range, there is a need to reduce system cost (volumes grow, competition increases, price pressure increases). In order to reduce costs, auto makers are motivated to move away from costly screened cable networks to less expensive two-wire systems.

The Qorivva MPC5606E MCU, with its embedded Motion J-PEG compression engine, precision time stamping hardware (IEEE 1588) and fast Ethernet controller (FEC), enables real-time broadcast of video and audio data over Ethernet.

The MPC5606E MCU includes a fully embedded BCM 89810 BroadR-Reach® compatible physical interface, allowing greater levels of system integration and enabling miniaturization of camera modules.

#### **Development Support Section**

- Development tools

- Compilers

- Freescale CodeWarrior IDE, visit freescale.com/CodeWarrior for more information

- Green Hills Wind River Diab

- Debuggers

- P&E Micro

- Lauterbach

- Green Hills • Runtime software

- Flash and FEE drivers

- Software core self test

- AUTOSAR microcontroller abstraction layer

- AUTOSAR™ Operating System

- · Ethernet streaming software

- Camera application software

#### **Specifications**

- Book E-compliant core built on Power Architecture technology

- Up to 64 MHz PowerPC ISA e200 zen0h core

- Memory

- 512 KB program flash with ECC

- 4 x 16 KB data flash with ECC

- 96 KB SRAM with ECC

#### 1/0

- 1 x MJPEG video encoder with image sensor interface supporting up to 1.2 Mpx

- 1 x 10/100 Ethernet MAC including IEEE 1588 PTP support

- 1 x FlexCAN

- 2 x LinFlex

## **Qorivva MPC5606E Features**

| Feature                     | MPC5606E                                                                                                |

|-----------------------------|---------------------------------------------------------------------------------------------------------|

|                             |                                                                                                         |

| CPU                         | e200z0h, 64 MHz, VLE only, no SPE                                                                       |

| Flash with ECC              | CFlash: 512 KB (LC) DFlash: 64 KB (LC, area optimized)                                                  |

| RAM with ECC                | 96 KB                                                                                                   |

| DMA                         | 16 channels                                                                                             |

| PIT                         | Yes                                                                                                     |

| SWT                         | Yes                                                                                                     |

| FCU                         | Yes                                                                                                     |

| Ethernet                    | 100 MB MII                                                                                              |

| Physical Interface          | Broadcom BroadR-Reach BCM89810                                                                          |

| Video Encoder               | 8/12 BPP                                                                                                |

| Audio Interface             | 6x Stereo (4x synchronous + 2x synchronous/asynchronous)                                                |

| ADC (10-bit)                | 4 channels + VDD_IO + VDDCore + TSens + VGate Current                                                   |

| Timer I/O (eTimer)          | 6 channels                                                                                              |

| SCI (LINFlex)               | 2x                                                                                                      |

| SPI (DSPI)                  | DSPI_0: 2 chip selects                                                                                  |

|                             | DSPI_1: 2 chip selects                                                                                  |

|                             | DSPI_2: 4 chip selects                                                                                  |

| CAN (FlexCAN)               |                                                                                                         |

| I <sup>2</sup> C            | 2x                                                                                                      |

| Supply                      | 3.3V IO                                                                                                 |

|                             | <ul> <li>1.2V core with dedicated ballast source pin in two modes:</li> <li>Internal ballast</li> </ul> |

|                             | External supply (using power on reset pin)                                                              |

| Phase Lock Loop (PLL)       | FMPLL                                                                                                   |

| Internal RC Oscillator      | 16 MHz                                                                                                  |

| External Crystal Oscillator | 4 MHz-40 MHz                                                                                            |

| CRC                         | Yes                                                                                                     |

| Debug                       | JTAG, Nexus2+                                                                                           |

| Ambient Temperature         | -40°C to +105°C                                                                                         |

| Package                     | 121-pin MAPBGA                                                                                          |

|                             |                                                                                                         |

• 2 x I<sup>2</sup>C interface

selects each)

time <1 us

• 16-ch. eDMA

• 3.3V single supply

**System**

• PLL

• 1 x ADC (5V capable)

• 16 MHz internal RC OSC

• 2- or 5-pin JTAG/Nexus Class 1

• 121-pin MAPBGA package, 8x8 mm

1 x I<sup>2</sup>S/I8S/TDM audio interface

• 3 x DSPI (four independent chip

• Channels TBD, 10-bit, conversion

• 1 x eTimer (six general-purpose channels)

### For current information about Kinetis products and documentation, please visit freescale.com/MPC5606E

Freescale, the Freescale logo and CodeWarrior are trademarks or registered trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. Qorivva is a trademark of Freescale Semiconductor, Inc. Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org. All other product or service names are the property of their respective owners. © 2014, Freescale Semiconductor, Inc.

Document Number: MPC5606EFS REV 0