Rev. 3.1 — 24 September 2020 485031

Product short data sheet COMPANY PUBLIC

### 1. Introduction

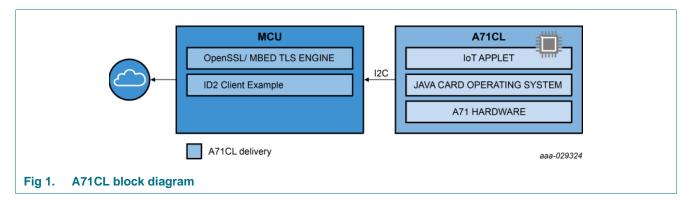

The A71CL is a ready-to-use solution providing a root of trust at the IC level and proven, chip-to-cloud security right out of the box. The product configuration has the provisioned credential to support Alibaba Cloud. It is a platform capable of securely storing and provisioning credentials, securely connecting IoT devices to cloud services and performing cryptographic node authentication.

The A71CL solution provides security measures protecting the IC against physical and logical attacks. The solution is meant to be integrated with a host platform and running operating systems adding a chain of trust for a broad range of applications. The product is delivered with a manual and a set of documents to provide guidance on its integration within a complete system; offering easy design-in with plug & play host application code, development kits, reference designs.

### 2. General description

### 2.1 A71CL naming conventions

The following table explains the naming conventions of the commercial product name of the A71CL products. Every A71CL product gets assigned such a commercial name, which includes also customer and application specific data.

The A71CL basic type names have the following format.

#### A71CLxagpp(p)

The 'A71CL' is a constant, all other letters are variables, which are explained in Table 1.

| Variable | Meaning                                                         | Values | Description                                                                                           |

|----------|-----------------------------------------------------------------|--------|-------------------------------------------------------------------------------------------------------|

| x        | IC hardware specification code                                  | 1      | standard operational ambient temperature:<br>–25 °C to +85 °C<br>I <sup>2</sup> C interface supported |

|          |                                                                 | 2      | standard operational ambient temperature:<br>–40 °C to +90 °C<br>I <sup>2</sup> C interface supported |

| а        | embedded operating<br>system code                               | С      | Java card operating system                                                                            |

| g        | embedded application<br>firmware (applet) code                  | L      | L is a fixed value = IoT security applet pre<br>installed                                             |

| pp(p)    | package type code<br>dd(d)= Delivery Type,<br>TK2= HVSON8 (4x4) |        |                                                                                                       |

#### Table 1. A71CL commercial name format

### 2.2 I<sup>2</sup>C interface

The A71CL has an I<sup>2</sup>C interface in slave mode, supporting data rates up to 400 kbit/s operating in Fast-Mode (FM). The I<sup>2</sup>C interface is using the Smartcard I<sup>2</sup>C protocol as defined in Ref. 3 which is based on SMBus.

Depending on the interface pins state at boot, see <u>Section 7 "Pinning information"</u> for more details; the default I<sup>2</sup>C address after power-on-reset is 0x90 for Write, and 0x91 for Read.

### 2.3 Security licensing

NXP Semiconductors has obtained a patent license for SPA and DPA countermeasures from Cryptography Research Incorporated (CRI). This license covers both hardware and software countermeasures. It is important to customers that countermeasures within the operation system are covered under this license agreement with CRI. Further details can be obtained on request.

#### Features and benefits 3.

#### 3.1 Key benefits

- Secure, zero-touch connectivity

- End-to-end security, from chip to edge to cloud

- Secure credential injection for IC-level root of trust

- Fast design-in with complete product support package

- Easy to integrate with different MCU platforms

#### 3.2 Security features

The A71CL security concepts includes many security measures to protect the chip.

The A71CL operates fully autonomously based on an integrated Javacard operating system and applet. Direct memory access is possible by the fixed functionalities of the applet only. With that, the content from the memory is fully isolated from the host system.

Attack protection by integrated design measures in the chip layout, the logic and the functional blocks.

### 3.3 Cryptography features

- Message digest with SHA1, SHA224, SHA256

- Random number generator

- Asymmetric key storage type: RSA Standard or RSA CRT

- Auto RSA key generator ranges from 512-bit key length to 2048-bit key length. Either RSA Standard or RSA CRT.

- Symmetric encryption/decryption with DES\_CBC\_NOPADDING, DES ECB NOPADDING, AES CBC NOPADDING, AES ECB NOPADDING.

- Symmetric signature/verification with DES CBC ISO9797 M1, DES\_CBC\_ISO9797\_M2, AES\_CBC\_ISO9797\_M1, AES\_CBC\_ISO9797 M2.

- Asymmetric encryption/decryption with RSA\_NOPADDING, RSA\_PKCS1.

- Asymmetric signature/verification with RSA\_SHA1(PKCS1), RSA\_SHA256.

- Service data storage: the storage data read and write is protected by SCP.

- SCP 02 service with option "i" = '55'.

#### 3.4 Functional features

- 400 kbit/s I<sup>2</sup>C Fast-mode interface

- -40 °C to +90 °C operational ambient temperature (A7102)

- On-chip Javacard operating system

- 40 μA typical sleep mode current with I<sup>2</sup>C pads in tristate mode

- 10 μA max deep sleep mode current with I<sup>2</sup>C pads in tristate modeS

- High-performance Public Key Infrastructure (PKI)

- EEPROM with min 500,000 cycles endurance and min 25 years retention time

- HVSON8 package

### 4. Applications

#### 4.1 Use Cases and target applications

- A710xCL EXAMPLE USE CASES

- Secure connection to public/private clouds, edge computing platforms, infrastructure

- Secure commissioning

- Device-to-device authentication

- Proof of origin / anti-counterfeiting

- Key storage and data protection

- A710xCL TARGET APPLICATIONS

- Connected industrial devices

- Sensor networks

- IP cameras

- Home gateways

- Home appliances

### 5. Ordering information

### 5.1 Ordering options

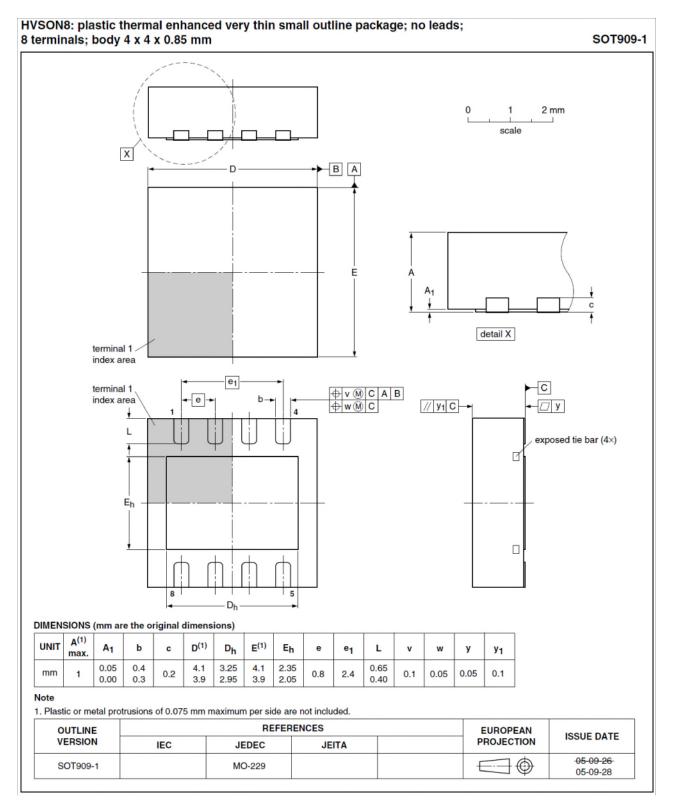

| Table 2. Orderin           | ng information |                                                                       |          |

|----------------------------|----------------|-----------------------------------------------------------------------|----------|

| Type number <sup>[1]</sup> | Package        |                                                                       |          |

|                            | Name           | Description                                                           | Version  |

| A7101agTK2/                | HVSON-8        | plastic thermal enhanced very thin small outline package; no leads; 8 | SOT909-1 |

| A7102agTK2/                |                | terminals; body $4 \times 4 \times 0.85$ mm                           |          |

[1] a = A or C, g = G, C or A, according to the A71CL type classification see Section 2.1 "A71CL naming conventions"

Table 3 gives an overview of available A71CL product types.

| Table 3. A71CL featu       | ire table                          |                 |                                 |                                       |

|----------------------------|------------------------------------|-----------------|---------------------------------|---------------------------------------|

| Orderable type             | Product type number <sup>[1]</sup> | 12NC            | Operational ambient temperature | Commercial name                       |

| A7101CLTK2/T0BC2WJ         | A7101CLTK2/T0BC2WE                 | 935368739118    | –25 °C to +85 °C                | A71CL, provisioned                    |

| A7102CLTK2/T0BC2XJ<br>[2]  | A7102CLTK2/T0BC2XR                 | 935379152118    | –40 °C to +90 °C                | and ready to use for<br>Alibaba Cloud |

| [1] HN1, according the A71 | CL type classification see Sec     | tion 2.1 "A71CL | naming conventions"             |                                       |

[2] product can be made available, please consult our sales for more details and leadtime.

### 5.1.1 Ordering A71CL samples

Samples can be ordered from the NXP Semiconductors e-commerce website.

Note that NXP Semiconductors can provide up to 5 pieces free of charge. Larger quantities have to be ordered separately.

#### 6. **Functional description**

### 6.1 Functional diagram

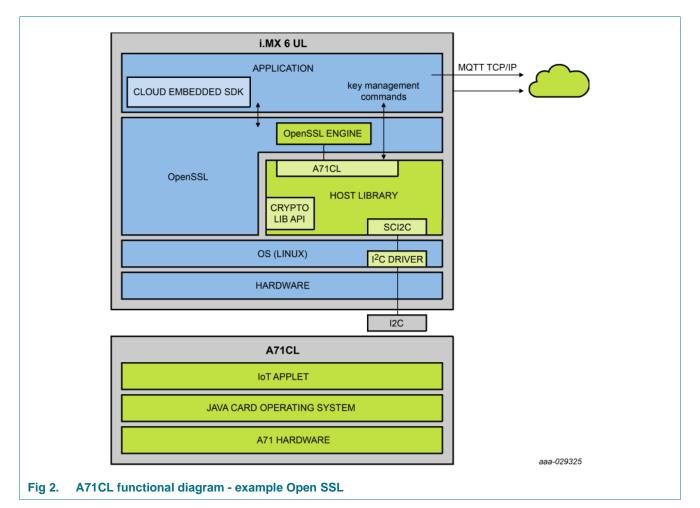

The A71CL uses I<sup>2</sup>C as communication interface as described in the following section. The A71CL commands are wrapped using the Smartcard I<sup>2</sup> protocol (SCI2C). The detailed documentation for the A71CL commands [ref to APDU Spec] and SCI2C encapsulation (Ref. 3) is available in NXP docstore."

In order to simplify the product usage a host library was created which takes care for the A71CL commands and SCI2C protocol encapsulation. The host library is available on the A71CL website. The APDU specification is available for download with complete sources on the A71CL website.

### 6.2 I<sup>2</sup>C Interface

The A71CL has an I<sup>2</sup>C interface in slave mode, supporting data rates up to 400 kbit/s operating in Fast-Mode (FM). The I<sup>2</sup>C interface is using the Smartcard I<sup>2</sup>C protocol as defined in Ref. 3 which is based on SMBus. Depending on the interface pins state at boot, see Section 7 for more details. The default I<sup>2</sup>C address after power-on-reset depends on the bootup condition as shown in Table 4.

| All information provided in this document is subject to legal disclaimers |

|---------------------------------------------------------------------------|

| Rev. 3.1 — 24 September 2020                                              |

| 485031                                                                    |

#### 6.3 Automatic Communication Mode detection at Power on

The IC configures its interface according to the pin state as shown in the table below. The host system must keep the voltage levels stable at these pins for at least 500  $\mu$ s after power-on-reset.

| Table 4. | 12C | address |

|----------|-----|---------|

| Table 4. | 1-C | auuress |

|     | Value at startup |         |         |       | ldress |

|-----|------------------|---------|---------|-------|--------|

| IF0 | IF1              | I2C_SCL | I2C_SDA | Write | Read   |

| 0   | х                | 0       | 0       | n.a.  | n.a.   |

| 1   | 0                | 1       | 1       | 0x90  | 0x91   |

| 1   | 1                | 1       | 1       | 0x92  | 0x93   |

#### 6.4 **Power-saving modes**

The device provides two power-saving operation modes, the SLEEP mode and the DEEP SLEEP mode. These modes are activated via pad RST\_N (DEEP SLEEP mode) or by the device.

#### 6.4.1 SLEEP mode

The SLEEP mode has the following properties:

- all internal clocks are frozen,

- CPU enters power saving mode with program execution being stopped,

- CPU registers keep their contents,

- RAM keeps its contents,

The A71CL enters automatically into SLEEP mode and also wakes up automatically from SLEEP mode. In SLEEP mode, all internal clocks are stopped. The IOs hold the logical states they had at the time IDLE was activated. During SLEEP mode security sensors HVS, LVS, LTS, HTS, Light Sensors, Glitch Sensors and Active Shielding are disabled.

There are two ways to exit from the SLEEP mode:

- A reset signal on RST\_N

- An External Interrupt edge triggered by a falling edge on I2C\_SDA

#### 6.4.2 DEEP SLEEP mode

The A71CLx provides a special sleep mode offering maximum power saving. It is reached by pulling RST\_N to a logic zero level for more than 500  $\mu$ s.

While in deep sleep mode the internal power is completely switched off and only the IO pads stay supplied. All digital pads will stay in high-Z mode.

To leave the DEEP SLEEP mode RST\_N has to be released and set to a logic "1" level.

**A71CL**

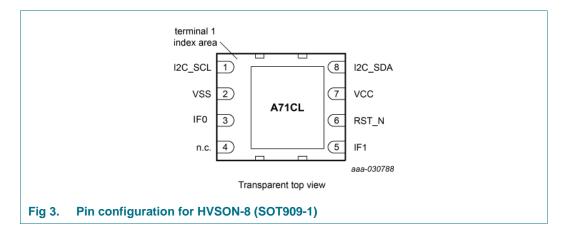

## 7. Pinning information

### 7.1 Pinning

### 7.1.1 Pinning HVSON8

| Symbol  | Pin | Description                                 |

|---------|-----|---------------------------------------------|

| I2C_SCL | 1   | I <sup>2</sup> C clock                      |

| VSS     | 2   | ground                                      |

| IF0     | 3   | interface activation, apply high on startup |

| n.c.    | 4   | not connected                               |

| IF1     | 5   | I <sup>2</sup> C address selection          |

| RST_N   | 6   | reset input, active LOW                     |

| VCC     | 7   | power supply voltage input                  |

| I2C_SDA | 8   | I <sup>2</sup> C data                       |

|         |     |                                             |

#### Table 5. Pin description HVSON8

**A71CL**

### 8. Package outline

#### Fig 4. Package outline SOT909-1

All information provided in this document is subject to legal disclaimers.

### 9. Packing information

### 9.1 Reel packing

The A71CL product is available on 7" tape on reel and 13" tape on reel. Details are provided in <u>Table 6</u>.

| Table 6. Reel | packing options                 |                          |

|---------------|---------------------------------|--------------------------|

| Package type  | Reel type                       | Minimum packing quantity |

| HVSON8        | 7" tape on reel                 | 1500                     |

| HVSON8        | 13" tape on reel <sup>[1]</sup> | 6000                     |

For details about packing method, product orientation, tape dimensions and labeling for A71 parts in HVSON8 package having an ordering code (12NC) ending 118 refer to <u>Ref. 2</u>.

### **10. Electrical and timing characteristics**

The electrical interface characteristics of static (DC) and dynamic (AC) parameters for pads and functions used for  $I^2C$  are in accordance with the NXP  $I^2C$  specification (see Ref. 1).

### **11. Limiting values**

#### Table 7. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to VSS (ground = 0 V).

| Symbol               | Parameter                                                   | Conditions                                   |     | Min  | Max   | Unit |

|----------------------|-------------------------------------------------------------|----------------------------------------------|-----|------|-------|------|

| V <sub>DD</sub>      | supply voltage                                              |                                              |     | -0.3 | +4.6  | V    |

| VI                   | input voltage                                               | any signal pad                               |     | -0.3 | +4.6  | V    |

| I                    | input current                                               | pad I2C_SDA,<br>I2C_SCL                      |     | -    | 10    | mA   |

| I <sub>O</sub>       | output current                                              | pad I2C_SDA,<br>I2C_SCL                      |     | -    | 10    | mA   |

| l <sub>lu</sub>      | latch-up current                                            | $V_I < 0 V \text{ or } V_I > V_{DD}$         |     | -    | 100   | mA   |

| V <sub>esd_hbm</sub> | electrostatic discharge<br>voltage (Human Body<br>Model)    | pads VCC, VSS,<br>RST_N, I2C_SDA,<br>I2C_SCL | [1] |      | ± 2.0 | kV   |

| V <sub>esd_cdm</sub> | electrostatic discharge<br>voltage (Charge Device<br>Model) | pads VCC, VSS,<br>RST_N, I2C_SDA,<br>I2C_SCL | [3] |      | ± 500 | V    |

| P <sub>tot</sub>     | Total power dissipation                                     |                                              | [2] | -    | 1     | W    |

| T <sub>stg</sub>     | Storage temperature                                         |                                              |     | -55  | +125  | °C   |

[1] MIL Standard 883-D method 3015; human body model; C = 100 pF, R =  $1.5 \text{ k}\Omega$ ; T<sub>amb</sub> = -25 °C to +85 °C.

[2] Depending on appropriate thermal resistance of the package.

[3] JESD22-C101, JEDEC Standard Field induced charge device model test method.

## 12. Recommended operating conditions

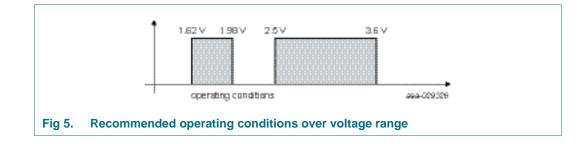

The A71CL offers two operation modes, the so-called 1V8 mode and the 3V3 mode targeted for battery supplied applications.

| Table 8.         | Recommended operating cor       | nditions                                     |      |     |      |      |

|------------------|---------------------------------|----------------------------------------------|------|-----|------|------|

| Symbol           | Parameter                       | Conditions                                   | Min  | Тур | Max  | Unit |

| V <sub>DD</sub>  | supply voltage range            | 3V3 mode range<br>CPU in free<br>runing mode | 2.50 | 3.3 | 3.6  | V    |

|                  |                                 | 1V8 mode                                     | 1.62 | 1.8 | 1.98 | V    |

| VI               | DC input voltage on digital I/O | 3V3 mode                                     | 0    |     | 3.6  | V    |

|                  | pads I2C_SCL, I2C_SDA           | 1V8 mode                                     | 0    |     | 3.6  | V    |

| VI               | DC input voltage on digital     | 3V3 mode                                     | 0    |     | 3.6  | V    |

|                  | input pad RST_N                 | 1V8 mode                                     | 0    |     | 3.6  | V    |

| T <sub>amb</sub> | Operating ambient               | A7101                                        | -25  |     | +85  | °C   |

|                  | temperature                     | A7102                                        | -40  |     | +90  | °C   |

### **13. Characteristics**

### 13.1 DC characteristics

#### **Measurement conventions**

Testing measurements are performed at the contact pads of the device under test. All voltages are defined with respect to the ground contact pad VSS. All currents flowing into the device are considered positive.

#### 13.1.1 General and I<sup>2</sup>C I/O interface

### Table 9. Electrical DC characteristics of I2C\_SCL, I2C\_SDA and RST\_N

| Symbol          | Parameter                              | Conditions                             |     | Min                 | Тур | Max                   | Unit |

|-----------------|----------------------------------------|----------------------------------------|-----|---------------------|-----|-----------------------|------|

| Input/Out       | put: I2C_SCL, I2C_SDA in push-p        | oull mode                              |     |                     |     |                       |      |

| V <sub>IH</sub> | HIGH level input voltage               |                                        |     | $0.7 V_{DD}$        |     | V <sub>Imax</sub> [1] | V    |

| V <sub>IL</sub> | LOW level input voltage                |                                        |     | -0.5                |     | 0.3 V <sub>DD</sub>   | V    |

| IIH             | HIGH level input current in input mode | $V_{IHmin} < V_I < V_{IHmax}$          |     |                     |     | ± 10                  | μA   |

| IIL             | LOW level input current                | $V_{ILmin} < V_I < V_{ILmax}$          |     |                     |     | ± 10                  | μA   |

| V <sub>OH</sub> | HIGH level output voltage              | I <sub>OH</sub> = -3.0 mA;<br>3V3 mode | [2] | 0.7 V <sub>DD</sub> |     |                       | V    |

|                 |                                        | I <sub>OH</sub> = -3.0 mA;<br>1V8 mode | [2] | 0.7 V <sub>DD</sub> |     |                       | V    |

| V <sub>OL</sub> | LOW level output voltage               | I <sub>OL</sub> = 3.0 mA<br>3V3 mode   |     |                     |     | 0.4                   | V    |

|                 |                                        | I <sub>OL</sub> = 2.0 mA<br>1V8 mode   |     |                     |     | $0.2 V_{DD}$          | V    |

#### Input/Output: I2C\_SCL, I2C\_SDA in open-drain mode

| VIH             | HIGH level input voltage               |                                                          | 0.7 V <sub>DD</sub> | V <sub>Imax</sub> [1] | V  |

|-----------------|----------------------------------------|----------------------------------------------------------|---------------------|-----------------------|----|

| V <sub>IL</sub> | LOW level input voltage                |                                                          | -0.5                | 0.3 V <sub>DD</sub>   | V  |

| I <sub>IH</sub> | HIGH level input current in input mode | V <sub>IHmin</sub> < V <sub>I</sub> < V <sub>IHmax</sub> |                     | ± 10                  | μA |

| IIL             | LOW level input current                | $V_{ILmin} < V_I < V_{ILmax}$                            |                     | ± 10                  | μA |

| V <sub>OL</sub> | LOW level output voltage               | I <sub>OL</sub> = 3.0 mA<br>3V3 mode                     |                     | 0.4                   | V  |

|                 |                                        | I <sub>OL</sub> = 2.0 mA<br>1V8 mode                     |                     | 0.2 V <sub>DD</sub>   | V  |

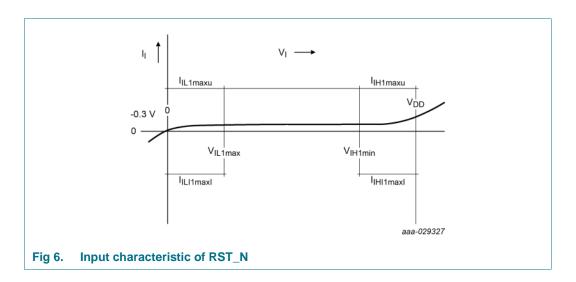

#### Input: RST\_N

| V <sub>IH1</sub> | HIGH level input voltage       |                                   |     | 0.7 V <sub>DD</sub> | V <sub>Imax</sub> [1] | V  |

|------------------|--------------------------------|-----------------------------------|-----|---------------------|-----------------------|----|

| V <sub>IL1</sub> | LOW level input voltage        |                                   |     | -0.3                | $0.3  V_{DD}$         | V  |

| I <sub>IH1</sub> | HIGH level RST_N input current | $V_{IH1min} \leq V_I \leq V_{DD}$ | [3] |                     | ± 20                  | μA |

| $I_{IL1}$        | LOW level RST_N input current  | $0 V \le V_I \le V_{IL1max};$     | [3] |                     | ± 20                  | μA |

[1] Maximum value according to Table 8 "Recommended operating conditions"

Product short data sheet COMPANY PUBLIC

- [2] : External pull-up resistor 20 k $\Omega$  to VDD. The worst case test condition for parameter V<sub>OH</sub> is present at minimum V<sub>DD</sub>. For class A supply voltage conditions V<sub>DD</sub> = 4.5 V is the worst case with respect to the fix specification limit V<sub>OHmin</sub> = 3.8 V (0.844 V<sub>DD</sub>). The supply voltage related limit "0.7 V<sub>DD</sub>" is a stricter requirement than the fix value 3.8 V at high V<sub>DD</sub> (0.7 V<sub>DD</sub> = 3.85 V at V<sub>DD</sub> = 5.5 V). So, in the V<sub>DD</sub> range 4.5 V to 5.5 V, V<sub>OHmin</sub> is specified as "the larger value of 0.7 V<sub>DD</sub> and 3.8 V, respectively".

- [3] The active low RST\_N input internally has a resistive pull-down device to VSS. Accordingly a current is flowing into the pad voltages above 0 V. Figure 6 shows the RST\_N input characteristic.

### 13.1.2 I<sup>2</sup>C interface at 3V3 mode operation<sup>[1]</sup>

#### Table 10. Electrical characteristics of IC supply voltage $V_{DD}$ ; $V_{SS} = 0 V$ ; $T_{amb} = -40$ to +90 °C

| Symbol                | Parameter                      | Conditions                                  | Min  | Тур  | Max  | Unit |

|-----------------------|--------------------------------|---------------------------------------------|------|------|------|------|

| Supply                |                                | 1                                           |      |      |      |      |

| V <sub>DD</sub>       | supply voltage range           | 3V3 mode range<br>CPU in free running mode  | 2.50 | 3.3  | 3.6  | V    |

| I <sub>DD</sub>       | no coprocessor active          | CPU in free running mode                    |      | 6.3  | 7.0  | mA   |

|                       | EPROM programming in progress  | CPU in free running mode                    |      | 7.3  | 8.0  | mA   |

|                       | AES coprocessor active         | CPU in free running mode                    |      | 9.3  | 10.3 | mA   |

|                       | ECC coprocessor active         | CPU in free running mode                    |      | 13.7 | 15.1 | mA   |

| I <sub>DD(SLP)</sub>  | supply current SLEEP mode      | T <sub>amb</sub> = 25 °C                    |      | 45   | 150  | μA   |

| I <sub>DD(DSLP)</sub> | supply current deep sleep mode | RST_N at 0V, $T_{amb} = 25 \ ^{\circ}C$     |      |      | 10   | μA   |

|                       |                                | RST_N at 0V, <i>T<sub>amb</sub></i> = 90 °C |      |      | 10   | μA   |

[1] All appropriately marked values are typical values and only referenced for information. They are subject to change without notice.

### 13.1.3 I<sup>2</sup>C interface at 1V8 mode operation<sup>[1]</sup>

#### Table 11. Electrical characteristics of IC supply voltage $V_{DD}$ ; $V_{SS} = 0 V$ ; $T_{amb} = -40$ to +90 °C

| Symbol                | Parameter                      | Conditions                              | Min  | Тур  | Max  | Unit |

|-----------------------|--------------------------------|-----------------------------------------|------|------|------|------|

| Supply                | 1                              |                                         |      |      |      |      |

| V <sub>DD</sub>       | supply voltage range           | 1V8 mode range                          | 1.62 | 1.8  | 1.98 | V    |

| I <sub>DD</sub>       | no coprocessor active          | CPU in free running mode                |      | 2.45 |      | mA   |

|                       | AES coprocessor active         | CPU in free running mode                |      | 2.7  |      | mA   |

|                       | ECC coprocessor active         | CPU in free running mode                |      | 7.5  |      | mA   |

| I <sub>DD(SLP)</sub>  | supply current SLEEP mode      | T <sub>amb</sub> = 25 °C                |      | 40   | 80   | μA   |

| I <sub>DD(DSLP)</sub> | supply current deep sleep mode | RST_N at 0V, $T_{amb} = 25 \ ^{\circ}C$ |      |      | 10   | μA   |

| . ,                   |                                | RST_N at 0V, $T_{amb} = 90 \ ^{\circ}C$ |      |      | 10   | μA   |

[1] All appropriately marked values are typical values and only referenced for information. They are subject to change without notice.

### **13.2 AC characteristics**

# Table 12. Non-volatile memory timing characteristics; $V_{DD} = 1.8 \text{ V} \pm 10\%$ or $3 \text{ V} \pm 10\%$ V; $V_{SS} = 0 \text{ V}$ ; $T_{amb} = -40$ to 90 °C

| Symbol           | Parameter                                          | Conditions                | Min                 | Тур | Max | Unit   |

|------------------|----------------------------------------------------|---------------------------|---------------------|-----|-----|--------|

| t <sub>EEP</sub> | EEPROM erase + program time                        |                           |                     | 2.7 |     | ms     |

| t <sub>EEE</sub> | EEPROM erase time                                  |                           |                     | 1.7 |     | ms     |

| t <sub>EEW</sub> | EEPROM program time                                |                           |                     | 1.0 |     | ms     |

| t <sub>EER</sub> | EEPROM data retention time                         | T <sub>amb</sub> = +55 °C | 25                  |     |     | years  |

| N <sub>EEC</sub> | EEPROM endurance<br>(number of programming cycles) |                           | 5 × 10 <sup>5</sup> |     |     | cycles |

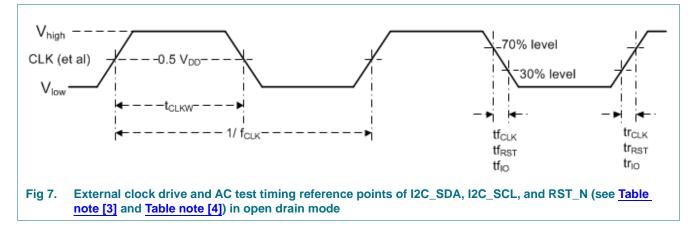

# Table 13. Electrical AC characteristics of I2C\_SDA, I2C\_SCL, and RST\_N<sup>[1]</sup>; $V_{DD} = 1.8 V \pm 10\%$ or $3 V \pm 10\% V$ ; $V_{SS} = 0 V$ ; $T_{amb} = -40$ to $90 \text{ }^{\circ}\text{C}$

| Symbol             | Parameter                                                                      | Conditions                                                                  |            | Min | Тур | Max | Unit |

|--------------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------|------------|-----|-----|-----|------|

| Input/Ou           | utput: I2C_SDA, I2C_SCL in op                                                  | en-drain mode                                                               |            |     |     |     |      |

| tr <sub>IO</sub>   | I/O Input rise time                                                            | Input/reception mode                                                        | <u>[4]</u> |     |     | 1   | μS   |

| tf <sub>IO</sub>   | I/O Input fall time                                                            | Input/reception mode                                                        | <u>[4]</u> |     |     | 1   | μS   |

| tf <sub>OIO</sub>  | I/O Output fall time                                                           | Output/transmission mode;<br>$C_L = 30 \text{ pF}$                          | <u>[4]</u> |     |     | 0.3 | μS   |

| f <sub>CLK</sub>   | External clock frequency in I <sup>2</sup> C applications                      | $t_{\text{CLKW}},T_{\text{amb}}$ and $V_{\text{DD}}$ in their spec'd limits |            | -   |     | 400 | kHz  |

| t <sub>CLKW</sub>  | Clock pulse width i.r.t. clock<br>period (positive pulse duty<br>cycle of CLK) |                                                                             | [3]        | 40  |     | 60  | %    |

| Inputs:            | RST_N                                                                          |                                                                             |            |     | I   | I   | I    |

| t <sub>RW</sub>    | Reset pulse width (RST_N low) without entering deep sleep mode                 |                                                                             |            | 40  |     | 400 | μS   |

| t <sub>RDSLP</sub> | Reset pulse width (RST_N low) to enter deep sleep mode                         |                                                                             |            | 500 |     |     | μS   |

| t <sub>WKP</sub>   | Wake-up time from SLEEP mode                                                   | $f_{CLKmin} < f_{CLK} < f_{CLKmax}$                                         |            | -   | 8   | 10  | μS   |

All information provided in this document is subject to legal disclaimers.

|                     | $v_{\rm DD} = 1.0 v \pm 10\% \text{ or } 3 v \pm 10\% \text{ v}, v_{\rm SS} = 0 v, r_{\rm amb} = -40.030 \text{ C}$ |                                                     |     |     |     |      |

|---------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----|-----|-----|------|

| Symbol              | Parameter                                                                                                           | Conditions                                          | Min | Тур | Max | Unit |

|                     | Pad LOW time for wake-up<br>from SLEEP mode                                                                         | level triggered ext.int.                            | -   | 8   | 10  | μs   |

|                     |                                                                                                                     | edge triggered ext.int.                             | -   | 8   | 10  | μs   |

| t <sub>WKPRST</sub> | RST_N LOW time for wake-up<br>from SLEEP mode                                                                       |                                                     | 40  |     | -   | μs   |

| t <sub>WKWT</sub>   | Time from SLEEP mode<br>wake/up event to I2C_SDA<br>valid                                                           |                                                     |     | 50  | 100 | ns   |

| C <sub>PIN</sub>    | Pin capacitances RST_N,<br>I2C_SDA, /I2C_SCL                                                                        | Test frequency = 1 MHz;<br>T <sub>amb</sub> = 25 °C | -   |     | 10  | pF   |

#### Table 13. Electrical AC characteristics of I2C\_SDA, I2C\_SCL, and RST\_N<sup>[1]</sup>; Vpp = 1.8 V + 10% or 3 V + 10% V; Vss = 0 V; Tamb = -40 to 90 °C

[1] All appropriately marked values are typical values and only referenced for information. They are subject to change without notice.

- [3] During AC testing the inputs RST\_N, I2C\_SDA, I2C\_SCL are driven at 0 V to +0.3 V for a LOW input level and at V<sub>DD</sub> -0.3 V to V<sub>DD</sub> for a HIGH input level. Clock period and signal pulse (duty cycle) timing is measured at 50% of V<sub>DD</sub>.

### 13.3 EMC/EMI

EMC and EMI resistance according to IEC 61967-4.

### 14. Abbreviations

| Table 14. | Abbreviations                                       |

|-----------|-----------------------------------------------------|

| Acronym   | Description                                         |

| AES       | Advanced Encryption Standard                        |

| CRC       | Cyclic Redundancy Check                             |

| DES       | Digital Encryption Standard                         |

| DPA       | Differential Power Analysis                         |

| DSS       | Digital Signature Standard                          |

| ECC       | Elliptic Curve Cryptography                         |

| EEPROM    | Electrically Erasable Programmable Read-Only Memory |

| I/O       | Input/Output                                        |

| MAC       | Message Authentication Code                         |

| OS        | Operating System                                    |

| PKI       | Public Key Infrastructure                           |

| SFI       | Single Fault Injection                              |

| SHA       | Secure Hash Algorithm                               |

**A71CL**

## **15. References**

- I<sup>2</sup>C-bus specification and user manual, Rev. 3.0 June-19-2007, NXP Semiconductors

- [2] SOT909-1; HVSON8; Reel pack; Ordering code (12NC) ending 118; Packing Information; Rev. 2 — 19 April 2013

- [3] Application note SCIIC Protocol Specification, Application note, Rev 1.5, an195015

31 January 2017

- [4] Application Note A71CL Secure Module Alibaba Cloud Ready APDU Application Note, Rev. 1.1, AN12297

### 16. Revision history

#### Table 15.Revision history

| Document ID    | Release date                                                                                     | Data sheet status                     | Change notice                        | Supersedes |  |  |

|----------------|--------------------------------------------------------------------------------------------------|---------------------------------------|--------------------------------------|------------|--|--|

| 485030         | 2018-11-27                                                                                       | Short data sheet                      |                                      |            |  |  |

| Modifications: | Figure 1 "A7                                                                                     | 1CL block diagram" updated            |                                      |            |  |  |

|                | • <u>Table 1 "A71</u>                                                                            | CL commercial name format"            | updated                              |            |  |  |

|                | Section 3.3 <sup>c</sup>                                                                         | <u>'Cryptography features"</u> update | ed                                   |            |  |  |

|                | <ul> <li>Table 3 "A71CL feature table" updated</li> </ul>                                        |                                       |                                      |            |  |  |

|                | <ul> <li>Section 5 "Ordering information" updated</li> </ul>                                     |                                       |                                      |            |  |  |

|                | <ul> <li>Figure 2 "A7</li> </ul>                                                                 | 1CL functional diagram - exam         | ple Open SSL" updated                | Ł          |  |  |

|                | Section 6.1 <sup>6</sup>                                                                         | 'Functional diagram" updated          |                                      |            |  |  |

|                | <ul> <li><u>Section 15 "References"</u> updated</li> </ul>                                       |                                       |                                      |            |  |  |

|                | <ul> <li>Section 13.1.2 "I2C interface at 3V3 mode operation<sup>[1]</sup>" updated</li> </ul>   |                                       |                                      |            |  |  |

|                | <ul> <li>Section 13.1.3 "I2C interface at 1V8 mode operation<sup>[1]</sup>" updated</li> </ul>   |                                       |                                      |            |  |  |

|                | Section 13.2 "AC characteristics" updated                                                        |                                       |                                      |            |  |  |

|                | <ul> <li>Changed status from Preliminary short data sheet to Product short data sheet</li> </ul> |                                       |                                      |            |  |  |

|                | <ul> <li>Title updated</li> </ul>                                                                | ł                                     |                                      |            |  |  |

|                | <ul> <li>Section 1 "Introduction" updated</li> </ul>                                             |                                       |                                      |            |  |  |

|                | • Table 3 "A71                                                                                   | CL feature table" updated             |                                      |            |  |  |

|                | • Figure 2 "A7                                                                                   | 1CL functional diagram - exam         | n <mark>ple Open SSL"</mark> updated | Ł          |  |  |

| 485010         | 2018-07-10                                                                                       | Short data sheet                      |                                      |            |  |  |

| Modifications: | <ul> <li>Initial version</li> </ul>                                                              | า                                     |                                      |            |  |  |

## 17. Legal information

### 17.1 Data sheet status

| Document status[1][2]          | Product status <sup>[3]</sup> | Definition                                                                            |

|--------------------------------|-------------------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet   | Development                   | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet | Qualification                 | This document contains data from the preliminary specification.                       |

| Product [short] data sheet     | Production                    | This document contains the product specification.                                     |

[1] Please consult the most recently issued document before initiating or completing a design.

[2] The term 'short data sheet' is explained in section "Definitions".

[3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL http://www.nxp.com.

### 17.2 Definitions

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with

the short data sheet, the full data sheet shall prevail.

**Product specification** — The information and data provided in a Product data sheet shall define the specification of the product as agreed between NXP Semiconductors and its customer, unless NXP Semiconductors and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the NXP Semiconductors product is deemed to offer functions and qualities beyond those described in the Product data sheet.

### 17.3 Disclaimers

Limited warranty and liability - Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors. In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory. Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors

Right to make changes - NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication here. - Suitability for use - NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk. - Applications - Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification. Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products. NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect. - Limiting values - Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device. - Terms and conditions of commercial sale - NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at http://www.nxp.com/profile/terms. unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP

485030

Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer. - No offer to sell or license - Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights. - Export control - This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities - Non-automotive qualified products — Unless this data sheet expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications. In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications. - Translations - A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions. - Security - While NXP Semiconductors has implemented advanced security features, all products may be subject to unidentified vulnerabilities. Customers are responsible for the design and operation of their applications and products to reduce the effect of these vulnerabilities on customer's applications and products, and NXP Semiconductors accepts no liability for any vulnerability

## **18. Contact information**

that is discovered. Customers should implement appropriate design and operating safeguards to minimize the risks associated with their applications and products. -17.4 Licenses

#### ICs with DPA Countermeasures functionality

NXP ICs containing functionality implementing countermeasures to Differential Power Analysis and Simple Power Analysis are produced and sold under applicable license from Cryptography Research, Inc.

### 17.5 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

FabKey — is a trademark of NXP B.V.

I<sup>2</sup>C-bus — logo is a trademark of NXP B.V.

For more information, please visit: <u>http://www.nxp.com</u>

For sales office addresses, please send an email to: salesaddresses@nxp.com

#### **NXP Semiconductors**

#### **Plug & Trust Secure Element for Alibaba Cloud**

A71CL

### 19. Tables

| Table 1.  | A71CL commercial name format2                                           |

|-----------|-------------------------------------------------------------------------|

| Table 2.  | Ordering information                                                    |

| Table 3.  | A71CL feature table                                                     |

| Table 4.  | I <sup>2</sup> C address                                                |

| Table 5.  | Pin description HVSON89                                                 |

| Table 6.  | Reel packing options11                                                  |

| Table 7.  | Limiting values                                                         |

| Table 8.  | Recommended operating conditions12                                      |

| Table 9.  | Electrical DC characteristics of I2C_SCL,                               |

|           | I2C_SDA and RST_N13                                                     |

| Table 10. | Electrical characteristics of IC supply voltage V <sub>DD</sub> ;       |

|           | $V_{SS} = 0 V; T_{amb} = -40 \text{ to } +90 \text{ °C} \dots \dots 15$ |

### **20. Figures**

| Fig 2.<br>Fig 3.<br>Fig 4. | A71CL block diagram |

|----------------------------|---------------------|

|                            | range               |

21. Contents

| 1     | Introduction 1                            |

|-------|-------------------------------------------|

| 2     | General description 2                     |

| 2.1   | A71CL naming conventions 2                |

| 2.2   | I <sup>2</sup> C interface 2              |

| 2.3   | Security licensing 2                      |

| 3     | Features and benefits 3                   |

| 3.1   | Key benefits 3                            |

| 3.2   | Security features                         |

| 3.3   | Cryptography features 3                   |

| 3.4   | Functional features                       |

| 4     | Applications 5                            |

| 4.1   | Use Cases and target applications 5       |

| 5     | Ordering information 6                    |

| 5.1   | Ordering options6                         |

| 5.1.1 | Ordering A71CL samples 6                  |

| 6     | Functional description 7                  |

| 6.1   | Functional diagram                        |

| 6.2   | I <sup>2</sup> C Interface 7              |

| 6.3   | Automatic Communication Mode detection at |

|       | Power on                                  |

| 6.4   | Power-saving modes 8                      |

| Table 11. | Electrical characteristics of IC supply voltage $V_{DD}$ ;                                                  |

|-----------|-------------------------------------------------------------------------------------------------------------|

|           | $V_{SS} = 0 V; T_{amb} = -40 \text{ to } +90 \text{ °C} \dots \dots 16$                                     |

| Table 12. | Non-volatile memory timing characteristics;                                                                 |

|           | $V_{DD} = 1.8 \text{ V} \pm 10\% \text{ or } 3 \text{ V} \pm 10\% \text{ V}; \text{ V}_{SS} = 0 \text{ V};$ |

|           | $T_{amb} = -40$ to 90 °C                                                                                    |

| Table 13. | Electrical AC characteristics of I2C_SDA,                                                                   |

|           | I2C_SCL, and RST_N <sup>[1]</sup> ;                                                                         |

|           | $V_{DD} = 1.8 \text{ V} \pm 10\% \text{ or } 3 \text{ V} \pm 10\% \text{ V}; \text{ V}_{SS} = 0 \text{ V};$ |

|           | $T_{amb} = -40$ to 90 °C                                                                                    |

| Table 14. | Abbreviations                                                                                               |

| Table 15. | Revision history                                                                                            |

|           |                                                                                                             |

| Fig 6. | Input characteristic of RST_N 14                  |

|--------|---------------------------------------------------|

| Fig 7. | External clock drive and AC test timing reference |

| C      | points of I2C_SDA, I2C_SCL, and RST_N (see        |

|        | Table note [3] and Table note [4]) in open drain  |

|        | mode                                              |

|        |                                                   |

#### 6.4.1 SLEEP mode ..... 8 6.4.2 7.1 Pinning HVSON8 ..... 9 7.1.1 8 Package outline..... 10 9 Packing information ..... 11 9.1 Reel packing ..... 11 Electrical and timing characteristics......11 10 11 Limiting values ..... 11 Recommended operating conditions ..... 12 12 Characteristics ..... 13 13 13.1 DC characteristics ..... 13 General and I2C I/O interface ..... 13 13.1.1 I2C interface at 3V3 mode operation<sup>[1]</sup> ..... 15 13.1.2 I2C interface at 1V8 mode operation<sup>[1]</sup> ..... 16 13.1.3 AC characteristics ..... 16 13.2 13.3 EMC/EMI ..... 17 14 Abbreviations ..... 18 15 References..... 19

#### continued >>

485030

485031

### **NXP Semiconductors**

# A71CL

### Plug & Trust Secure Element for Alibaba Cloud

| 16   | Revision history 20    |

|------|------------------------|

| 17   | Legal information 21   |

| 17.1 | Data sheet status 21   |

| 17.2 | Definitions 21         |

| 17.3 | Disclaimers            |

| 17.4 | Licenses               |

| 17.5 | Trademarks 22          |

| 18   | Contact information 22 |

| 19   | Tables                 |

| 20   | Figures 23             |

| 21   | Contents 23            |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

© NXP B.V. 2020.

All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 24 September 2020 485031