# ES\_QN908x

# Errata sheet QN908x

Rev. 1.1 — 23 February 2018

**Errata sheet**

### **Document information**

| Info     | Content        |

|----------|----------------|

| Keywords | QN908x, errata |

| Abstract | QN908x errata  |

**Errata sheet QN908x**

### **Revision history**

| Rev   | Date     | Description                                                    |

|-------|----------|----------------------------------------------------------------|

| 00.01 | 20160809 | Initial draft                                                  |

| 00.02 | 20160901 | Reviewed internally and updated                                |

| 00.03 | 20161125 | Removed some issue after Metal fix                             |

| 00.04 | 20170307 | Change document name and version                               |

| 00.06 | 20170427 | Update from v00.04, add RTC in errata, change TSC name into CS |

| 1.0   | 20170601 | Change document revision number to 1.0                         |

| 1.1   | 20180223 | ESD issue fixed                                                |

# **Contact information**

For more information, please visit: <a href="http://www.nxp.com">http://www.nxp.com</a>

For sales office addresses, please send an email to: <a href="mailto:salesaddresses@nxp.com">salesaddresses@nxp.com</a>

Introduction

1.

This document describes QN908x errata which should be referred by customer while application development.

# 2. Product Identification

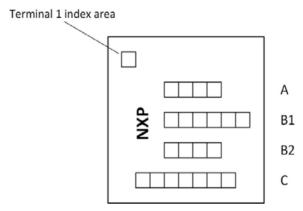

Figure 1 HVQFN48 package marking

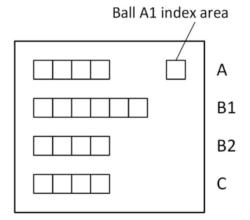

Figure 2 WLCSP47 package marking

The QN9080 HVQFN package has the following top-side marking:

- Line A: "9080" for QN9080

- Line B1: xxxxxx

- Line B2: xxxx

- Line C: xxYYWW[R]

- YY: year code, 16 for 2016.

- WW: week code.

- R = Chip revision.

The QN9083 WLCSP package has the following top-side marking:

- Line A: "9083" for QN9083

- Line B1: xxxxxx

• Line B2: xxWW

- WW: week code.

• Line C: YY[R]x

- YY: year code, 16 for 2016.

- R = Chip revision.

Table 1. Revision overview table

| Revision identifier | Revision description      |

|---------------------|---------------------------|

| 'A'                 | Initial device revision   |

| 'B'                 | First metal fix revision  |

| 'C'                 | Second metal fix revision |

| 'D'                 | ESD problem fixed         |

## 3. Errata Overview

Table 2. Errata summary table

| Erratum ID   | Short description                                                                                             | Product version(s)     | <b>Detailed description</b> |

|--------------|---------------------------------------------------------------------------------------------------------------|------------------------|-----------------------------|

| FSP.1        | FIR coefficient can only be saved in low 64K SRAM                                                             | 'A', 'B', 'C', and 'D' | Section 4.1                 |

| FC.1         | Flexcomm (0~3) interrupt can't be wakeup source in sleep mode if SLEEPDEEP bit of Cortex-M4 SCR register is 1 | 'A', 'B', 'C', and 'D' | Section 4.2                 |

| FC.2         | TXIDLE bit error in USART synchronous slave mode                                                              | 'A', 'B', 'C', and 'D' | Section 4.3                 |

| COMPARATOR.1 | Comparator can't work correctly under some condition                                                          | 'A', 'B', 'C', and 'D' | Section 4.4                 |

| COMPARATOR.2 | Comparator can't work correctly under some condition                                                          | 'A', 'B', 'C', and 'D' | Section 4.5                 |

| CS.1         | SCAN_INTEN register cannot be read                                                                            | 'A', 'B', 'C', and 'D' | Section 4.6                 |

| RTC.1        | SEC, CNT_VAL and CNT2 register reading may return invalid values when happens at 32k clock positive edge      | 'A', 'B', 'C', and 'D' | Section 4.7                 |

| ESD.1        | DCDC does not meet the required 2 kV ESD HBM specification                                                    | 'A', 'B', and 'C'      | Section 4.8                 |

### 4. Errata Details

### 4.1 FSP.1: FIR coefficients can only be stored in low 64K SRAM

#### Introduction:

FIR coefficients can be stored anywhere in the 128K SRAM, and FIR engine will read it for computation.

#### **Problem:**

The FIR coefficient base address register (FIR\_CH<x>\_COEF\_BASE, x = 0-8) is only 16 bit, which means only 64K SRAM is accessible. If the FIR coefficient is saved in high 64K, FIR can't fetch it.

#### Work-arounds:

Coefficient can only be stored in low 64K SRAM.

# 4.2 FC.1: Flexcomm (0~3) interrupt can't be wakeup source in sleep mode if SLEEPDEEP bit of Cortex-M4 SCR register is 1

#### Introduction:

Flexcomm (0~3) interrupt should be a wakeup source in sleep mode, no matter what value the SLEEPDEEP bit of Cortex-M4 System Control Register (SCR) is.

#### **Problem:**

Flexcomm (0-3) can't wake up MCU from sleep mode if the SLEEPDEEP bit in SCR is 1.

#### Work-arounds:

If Flexcomm are used as wakeup source, set SLEEPDEEP bit as 0 in sleep mode. The power saving from SLEEPDEEP=1 is negligible.

# 4.3 FC.2: TXIDLE bit error in USART synchronous slave mode

#### Introduction:

TXIDLE bit in USART Status register (STAT) should be 1 after transmit is finished in synchronous slave mode.

#### **Problem:**

When USART works in synchronous slave mode, TXIDLE bit in USART Status register (STAT) is set one cycle after transmit completes. The TXIDLE signal is not asserted correctly if the synchronous CLK from USART master doesn't provide that extra clock cycle.

#### Work-arounds:

Ignore the TXIDLE bit in synchronous slave mode. Use the buffer status as the indication of transmit completion.

# 4.4 COMPARATOR.1: Comparator cannot work correctly under some condition

#### Introduction:

Comparator should work well when internal reference is VCC\*(15/16).

#### **Problem:**

When VCC<=1.8V and one of the analog comparator input is selected as internal reference=VCC\*(15/16), the analog comparator does not function correctly. The analog comparator result does not change to logic "1" even if another input is >VCC\*(15/16).

### Work-arounds:

No work-arounds.

# 4.5 COMPARATOR.2: Comparator cannot work correctly under some condition

#### Introduction:

Comparator should work well when internal reference is (1/16)\*VCC.

#### **Problem:**

When VCC<=1.8V and one of the analog comparator input is selected as internal reference=VCC\*(1/16), the analog comparator does not function correctly. The analog comparator result does not change to logic "1" even if another input is >VCC\*(1/16).

#### Work-arounds:

No work-arounds.

### 4.6 CS.1: SCAN\_INTEN register cannot be read back correctly

### Introduction:

SCAN\_INTEN register, bit 3 in address 0x4000780C should be RMW correctly.

#### **Problem:**

SCAN INTEN register, bit 3 in address 0x4000780C can't be read by MCU.

This bit will always read back 0. If read-modify-write is used to modify this register, this bit will be written as 0.

#### Work-arounds:

Software should keep track of this register value. Always modify on the software saved value rather than read-back value when changing this register.

# 4.7 RTC.1: SEC, CNT\_VAL, CNT2 register read return invalid value

#### Introduction:

Reading SEC, CNT\_VAL and CNT2 registers, may return invalid values when it happens at the edge of 32K clock.

#### **Problem:**

These registers are 32k domain register, and they are mapping to APB clock domain. There is only a stage of synchronization of these registers. So when the reading operation happens at the edge of the 32K clock, the reading back value may be invalid.

### Work-arounds:

Software need to read more times, when get 2 same value. It should be the correct one.

ES\_QN908x

# 4.8 ESD.1: DCDC does not meet the required 2 kV ESD HBM specification

#### Introduction:

The chip is rated for 2 kV ESD HBM. ESD HBM stressed as highlighted a weakness in the DCDC IP.

#### **Problem:**

DCDC IP is passing ESD-HBM stress at 500V and failing above. When stressing the device with a level above 500V, DCDC IP will be damaged but the device is fully functional when the DCDC is using external power supplies.

### Work-arounds:

This problem is fixed in Rev. D.

For the earlier reversions, it is not recommended to enable the DCDC. In such case, make sure to connect the VCC/VVD1/VDD2/VDD3 pins all together.

# 5. Legal Information

### 5.1 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or

customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

#### 5.2 Licenses

#### Purchase of NXP <xxx> components

<License statement text>

#### 5.3 Patents

Notice is herewith given that the subject device uses one or more of the following patents and that each of these patents may have corresponding patents in other jurisdictions.

<Patent ID> — owned by <Company name>

#### 5.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are property of their respective owners.

<Name> — is a trademark of NXP B.V.

# 6. Contents

| 1.  | Introduction                                                                           | 3 |

|-----|----------------------------------------------------------------------------------------|---|

| 2.  | Product Identification                                                                 | 3 |

| 3.  | Errata Overview                                                                        | 4 |

| 4.  | Errata Details                                                                         | 5 |

| 4.1 | FSP.1: FIR coefficients can only be stored in lo                                       |   |

| 4.2 | FC.1: Flexcomm (0~3) interrupt can't be waked source in sleep mode if SLEEPDEEP bit of |   |

| 4.3 | Cortex-M4 SCR register is 1FC.2: TXIDLE bit error in USART synchronous slave mode      |   |

| 4.4 | COMPARATOR.1: Comparator cannot work correctly under some condition                    |   |

| 4.5 | COMPARATOR.2: Comparator cannot work correctly under some condition                    |   |

| 4.6 | CS.1: SCAN_INTEN register cannot be read back correctly                                |   |

| 4.7 | RTC.1: SEC, CNT_VAL, CNT2 register read return invalid value                           | 6 |

| 4.8 | ESD.1: DCDC does not meet the required 2 kV ESD HBM specification                      |   |

| 5.  | Legal Information                                                                      | 8 |

| 5.1 | Disclaimers                                                                            | 8 |

| 5.2 | Licenses                                                                               | 8 |

| 5.3 | Patents                                                                                | 8 |

| 5.4 | Trademarks                                                                             | 8 |

| 6   | Contents                                                                               | a |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in the section 'Legal information'.