Freescale Semiconductor Product Brief

Document Number: DSP56725PB Rev. 0, 06/2008

# Symphony<sup>TM</sup> DSP56725 Multi-Core Audio Processor Product Brief

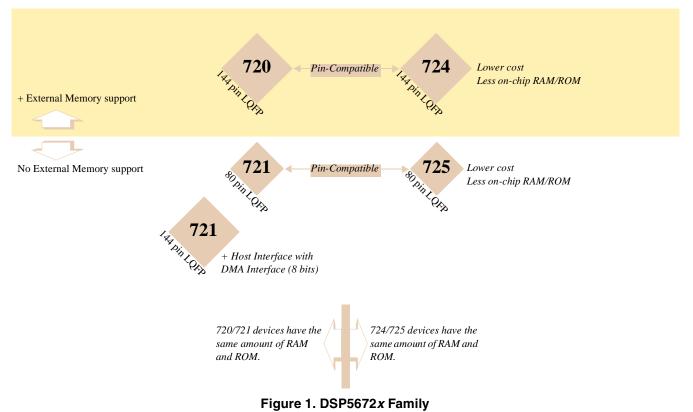

The Symphony DSP56725 Multi-Core Audio Processor is part of the DSP5672x family of programmable CMOS DSPs, designed using multiple DSP56300 24-bit cores. The DSP56725 offers customers flexibility in their designs by providing a more cost-effective alternative to the DSP56721 while maintaining pin and peripheral compatibility.

The DSP56725 is intended for automotive and audio applications that require high performance for audio processing. Potential applications include A/V receivers, DVD Receivers, Home Theater in a Box (HTIB), and automotive amplifiers and entertainment systems.

The DSP56725 provides a wealth of on-chip audio processing functions, via a plug and play software architecture system which has the ability to support audio decoding algorithms, various equalization algorithms, compression, signal generator, tone control, fade/balance, level meter/spectrum analyzer, among others. The DSP56725 also supports various matrix decoders and sound field processing algorithms.

#### Contents

| 1 | Bloc | k Diagram2            |

|---|------|-----------------------|

| 2 | Feat | ures                  |

|   | 2.1  | Dual DSP56300 Cores 4 |

|   | 2.2  | Core Modules 4        |

|   | 2.3  | Shared Modules7       |

| 3 | Docu | ment Revision History |

With two DSP56300 cores, a single DSP56725 device can replace dual-DSP designs, saving costs while meeting high MIPs requirements. Legacy peripherals from the previous DSP5636x/37x families are included, as well as a variety of new modules available in the DSP5672x family. Modules from the DSP56720 which are included on the DSP56725 are an Asynchronous Sample Rate Converter (ASRC), Inter-Core Communication (ICC), and a Sony/Philips Digital Interface (S/PDIF) transceiver.

Table 1 shows the DSP5672x family of devices.

Symphony<sup>™</sup> DSP56725 Multi-Core Audio Processor Product Brief, Rev. 0

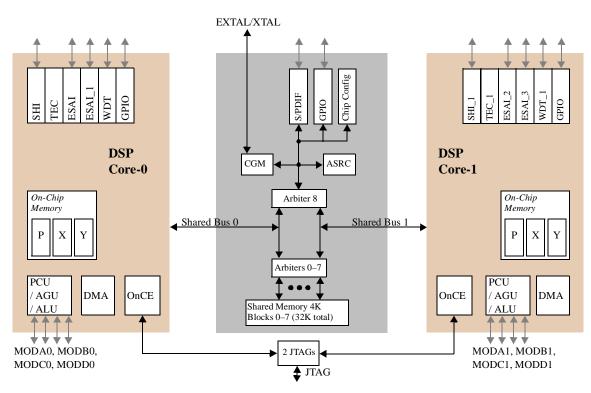

# 1 Block Diagram

The following figure shows the block diagram for the DSP56725 device.

Figure 2. DSP56725 Block Diagram

# 2 Features

The DSP56725 processor includes the following features:

- Two enhanced DSP56300 cores that are integrated, replacing two DSPs in designs, lowering costs and meeting high MIPs requirements: up to 500 million instructions per second in total (250 MIPs/core) using a 250-MHz clock with 1.2-V internal logic supply. Each core in the DSP56725 has the following features:

- Highly parallel instruction set

- Hardware debugging support (JTAG TAP, OnCE<sup>TM</sup> module)

- Eight-channel DMA (Direct Memory Access) controller

- Wait and Stop low-power standby modes

- Configurable and flexible arbitration methods for shared peripherals and shared memory blocks.

- Powerful audio data communication abilities:

- Four Enhanced Serial Audio Interface (ESAI) modules to transmit and receive audio data., with two ESAI modules per core. Each ESAI module includes up to 4 receivers and 6 transmitters, master or slave. I<sup>2</sup>S, Left-justified, Right-justified, Sony, AC97, network and other programmable protocols are supported.

#### Symphony<sup>™</sup> DSP56725 Multi-Core Audio Processor Product Brief, Rev. 0

Features

One S/PDIF module that is shared by the cores to transmit and receive audio data in IEC958 format.

- Powerful host communication port:

- Two Serial Host Interface (SHI) modules, with one SHI per core. The SHI modules support SPI and I<sup>2</sup>C protocols, multi-master capability in I<sup>2</sup>C mode, 10-word receive FIFO, and support for 8, 16 and 24-bit words.

- Two triple-timer modules (TEC), with one TEC per core

- Two watchdog timer modules (WDT) to prevent software runaway conditions, with one WDT per core

- Seamless hardware Asynchronous Sampling Rate Converter (ASRC) module, to support different sample rate audio data transmission and reception. The ASRC can be accessed by both DSP cores.

- Supports three data sampling rate convert pairs at the same time

- Different data sampling rate convert pairs can be used by different cores at the same time

- Inter-Core Communication (ICC) module:

- 32K shared memory between two DSP cores

- Supports a flexible arbitration system which allows multiple methods of arbitration

- Non-maskable and maskable interrupts between the two cores

- Poll data registers for simple data transfer

- As many as 33 GPIO pins, shared with other peripherals function pins.

# 2.1 Dual DSP56300 Cores

The DSP56725 contains two enhanced DSP56300 cores. Together, the two cores provide over twice the performance of Freescale's popular DSP56371 processor, while retaining code compatibility.

The DSP56300 core offers a high level of performance in speed and power, provided by its rich instruction set and low power dissipation. (Core features are fully described in the *DSP56300 Family Manual*.)

Each DSP56725 core contains its own set of peripherals: PIC, DMA, ESAI, SHI, triple timer, watchdog timer, patch module, and internal memory, which are described in the following sections.

### 2.2 Core Modules

The following sections describe the various modules that are present with each DSP56725 core. These modules are similar or identical to the modules present in DSP5636x/37x devices.

### 2.2.1 Internal Core Memory

The memory space of each DSP56725 core is partitioned into three memory spaces: program memory space, X data memory space, and Y data memory space.

| Bi   | it Settings |    | Memory Sizes (24-Bit Words)<br>RAM |        |        |

|------|-------------|----|------------------------------------|--------|--------|

| D    | it Settings |    |                                    |        |        |

| MSW1 | MSW0        | MS | Program                            | X Data | Y Data |

| Х    | Х           | 0  | 4K                                 | 28K    | 24K    |

| 0    | 0           | 1  | 40K                                | 8K     | 8K     |

| 0    | 1           | 1  | 24K                                | 16K    | 16K    |

| 1    | 0           | 1  | 16K                                | 24K    | 16K    |

| 1    | 1           | 1  | 8K                                 | 24K    | 24K    |

#### Table 1. Memory Map Options for Core-0

#### Table 2. Memory Map Options for Core-1

| В    | it Cottingo |    | Memory Sizes (24-Bit Words) |        |        |

|------|-------------|----|-----------------------------|--------|--------|

|      | it Settings |    |                             | RAM    |        |

| MSW1 | MSW0        | MS | Prog                        | X Data | Y Data |

| Х    | Х           | 0  | 2K                          | 12K    | 10K    |

| 0    | 0           | 1  | 16K                         | 4K     | 4K     |

| 0    | 1           | 1  | 12K                         | 8K     | 4K     |

| 1    | 0           | 1  | 8K                          | 8K     | 8K     |

| 1    | 1           | 1  | 4K                          | 12K    | 8K     |

#### 2.2.2 Direct Memory Access (DMA) Controller

The DMA module permits data transfers without the interaction of a core, and supports any combination of internal memory, internal peripheral I/O and external memory as source and destination during accesses. However, the DSP56725 DMA has been enhanced to support up to 8 DMA channels per core. Additionally, each DMA channel receives its own 32 request lines, allowing more flexibility in the DMA request sources for different channels, and potential support for a greater number of DMA request sources. The DMA module features:

- Eight DMA channels that support internal and external accesses

- One-, two-, and three-dimensional transfers (including circular buffering)

- End-of-block-transfer interrupts

- Triggering from interrupt lines and all peripherals

The DMA module is fully described in the DSP56300 Family Manual.

Features

### 2.2.3 **Programmable Interrupt Controller (PIC)**

The Program Interrupt Controller arbitrates among all interrupt requests (internal interrupts and the five external requests IRQA, IRQB, IRQC, IRQD, and NMI), and generates the appropriate interrupt vector address. PIC features include:

- Supports both maskable and non-maskable interrupts

- Supports additional DMA and peripheral interrupts. Allows up to 18 DMA and 24 peripheral interrupts

- Supports nine non-maskable interrupts

Refer to the DSP56300 Family Manual for more information about the PIC module.

### 2.2.4 Enhanced Serial Audio Interface (ESAI)

The ESAI module provides a full-duplex serial port for serial communications with a variety of serial devices, including industry-standard codecs, S/PDIF transceivers, and other DSPs. The ESAI consists of independent transmitter and receiver sections, with each section having its own clock generator. There are two ESAI modules per DSP core.

### 2.2.5 Serial Host Interface (SHI)

The SHI module is a serial I/O interface that provides a path for communication and program/coefficient data transfers between each DSP core and an external host processor. The SHI can also communicate with other serial peripheral devices.

The SHI supports two well-known and widely used synchronous serial buses: Serial Peripheral Interface (SPI) bus, and Inter-Integrated-circuit Control ( $I^2C$ ) bus. The SHI supports either SPI or  $I^2C$  bus protocol as required from a slave or a single-master device.

To minimize DSP core overhead, the SHI supports 8-bit, 16-bit, and 24-bit data transfers. The SHI has a 10-word receive FIFO that permits receiving up to 30 bytes before generating a receive interrupt, thereby reducing the overhead for data reception.

# 2.2.6 Triple Timer Module- Timer/Event Counters (TEC)

The Triple Timer module is composed of a common 21-bit prescaler and three independent and identical general purpose 24-bit timer/event counters, with each counter having its own register set. A timer can use internal clocking, and can interrupt the DSP core after a specified number of events (clocks). A timer can also be used to trigger DMA transfers after a specified number of events (clocks) occurred.

### 2.2.7 Watchdog Timer (WDT)

The Watchdog timer is a 16-bit timer that can help software recover from a runaway code condition. The timer is a free-running down-counter used to generate a reset (by asserting the WDT pin) on underflow. Software must periodically service the watchdog timer in order to restart the countdown and prevent assertion of the WDT pin.

#### 2.2.8 GPIO

The DSP56725 device provides up to 33 bidirectional signals that can be configured as GPIO function signals, or as peripheral function signals. Most of these signals are GPIO by default after resets.

### 2.2.9 Core Integration Module (CIM)

The CIM includes a chip ID register, a OnCE GDB register, and a DMA stall monitor function. When enabled, the DMA stall monitor can assert a non-maskable interrupt to the DSP core when the DMA has been stalled for longer than a configurable number of cycles due to internal memory contention.

#### 2.2.10 JTAG/OnCE Module

Each DSP core contains its own independent JTAG/OnCE module, which can obtain the working status and data for each DSP core. This is helpful for software or hardware debugging. Note that there is only a single set of JTAG/OnCE output signals on the DSP56725 device.

### 2.3 Shared Modules

The following sections describes the peripheral modules that are shared between the two DSP56725 cores.

#### 2.3.1 Shared Memory

The DSP56725 shared memory space can be accessed by either DSP Core-0 or DSP Core-1. Shared memory has eight 4K x 24-bit word memory blocks, resulting in a total of 32K shared words (located at \$030000). Shared memory can be accessed as X, Y or P memory. The 4K x 24-bit word blocks are single port SRAMs, with arbiters to perform arbitration when two DSP cores try to simultaneously access the same 4K x 24-bit word SRAM block. However, no shared memory contentions occur when the two DSP cores simultaneously access *different* 4K x 24-bit word SRAM blocks.

#### 2.3.2 Inter-Core Communication (ICC) Module

Using the Inter-Core Communication module (ICC), each DSP core can issue maskable or non-maskable interrupts to the other DSP core. Each DSP core has its own write data register, which passes data to the other DSP core when an interrupt is generated. There are also poll data registers for inter-core data exchanges in the ICC. The ICC module interfaces with the dedicated peripheral buses of both DSP cores.

#### 2.3.3 Shared Bus Arbiter

As shown in Figure 1, the following modules are shared by the two DSP cores: SPDIF, ASRC and Chip Configuration modules and Shared Memory. Each DSP core can access these shared modules without contention as long as neither DMA nor the other core is accessing the same shared blocks. An Arbiter

#### Features

determines the core access delays when contention occurs. The arbitration method can be chosen using the chip configuration registers. The following arbitration methods are supported:

- Always Round-Robin

- Core-0 always has high priority

- Core-1 always has high priority

# 2.3.4 Sony/Phillips Digital Interface (S/PDIF) Module

The S/PDIF audio module is a stereo transceiver that allows the DSP56725 to receive and transmit digital audio. The DSP56725 provides a single S/PDIF receiver, with one input and one S/PDIF transmitter with one output. The S/PDIF module can also transmit and receive S/PDIF channel status (CS) and user (U) data. Note that there is only one S/PDIF module in the DSP56725 device, and it is shared by the two DSP cores.

An internal Digital Phase-Locked Loop (DPLL) derives the receiving clock from the bi-phase incoming audio-data; the transmitting clock can be derived from an external source or the main oscillator. A frequency measurement circuit is included to allow precise measurement of the receiving clock or the transmitting clock.

# 2.3.5 Asynchronous Sample Rate Converter (ASRC)

The incoming audio data to the DSP56725 can come from various sources at different sampling rates. Additionally, the outgoing audio data from the DSP56725 may have different sampling rates and it can also be associated with output clocks that are asynchronous to the input clocks.

The Asynchronous Sample Rate Converter (ASRC) converts the sampling rate of a signal associated with an input clock into a signal associated to a different output clock. The ASRC supports concurrent sample rate conversions of up to 10 channels, at -120 dB THD+N. The sample rate conversion of each channel is associated to a pair of incoming and outgoing sampling rates. The ASRC supports up to three sampling rate pairs. Note that there is only one ASRC module in the DSP56725 device, and the ASRC is shared by the two DSP cores. The three sample rate convert pairs can be used by both DSP cores at the same time.

The ASRC is hard-coded and acts like a co-processor, with minimal CPU or DSP core intervention.

# 2.3.6 Clock Generation Module (CGM)

The CGM is responsible for generating all clocks in the DSP56725. In functional mode, the output is a series of gated clocks. CGM has a low-jitter PLL inside. The PLL has a wide range of frequency multiplications (1 to 256), predivider factors (1 to 32) and output dividers (1 to 8). The CGM also has a power-saving clock divider (2<sup>i</sup>: i=0 to 7). In functional mode, the PLL control register (PCTL) sits on the bus; both DSP cores can read and write these registers to change the chip's working frequency. Furthermore, each DSP core can independently enter stop or wait mode to save power. Note that the shared peripherals enter power-saving mode only when both DSP cores enter stop mode.

# 3 Document Revision History

Table 3 provides a revision history for this document.

| Revision | Substantive Change(s)                                                                         |

|----------|-----------------------------------------------------------------------------------------------|

| 0.4      | Document updates and template conformance edits.                                              |

| 0.3      | Moved 723 package in DSP5672x family diagram (Figure 1) to "No external memory support" area. |

| 0.2      | Removed 208 MAP BGA package from DSP5672x family diagram.                                     |

| 0.1      | Added DSP5672x family diagram.                                                                |

| 0        | Initial release of document to NDA customers.                                                 |

#### Table 3. DSP56725PB Document Revision History

Symphony<sup>TM</sup> DSP56725 Multi-Core Audio Processor Product Brief, Rev. 0

**Document Revision History**

THIS PAGE INTENTIONALLY BLANK

Symphony<sup>TM</sup> DSP56725 Multi-Core Audio Processor Product Brief, Rev. 0

**Document Revision History**

THIS PAGE INTENTIONALLY BLANK

Symphony<sup>TM</sup> DSP56725 Multi-Core Audio Processor Product Brief, Rev. 0

#### How to Reach Us:

Home Page: www.freescale.com

#### Web Support:

http://www.freescale.com/support

#### USA/Europe or Locations Not Listed:

Freescale Semiconductor Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 +1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com

Document Number: DSP56725PB Rev. 0 06/2008 Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc. 2008. All rights reserved.