# Symphony DSP56720/DSP56721 Multi-Core Audio Processors Reference Manual

Document Number: DSP56720RM

Rev. 1.1 2/2008

#### How to Reach Us:

#### Home Page:

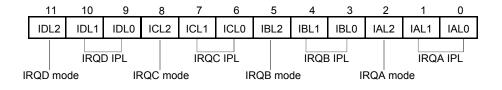

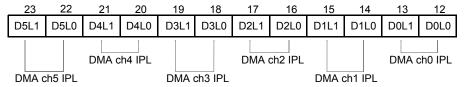

www.freescale.com

#### E-mail:

support@freescale.com

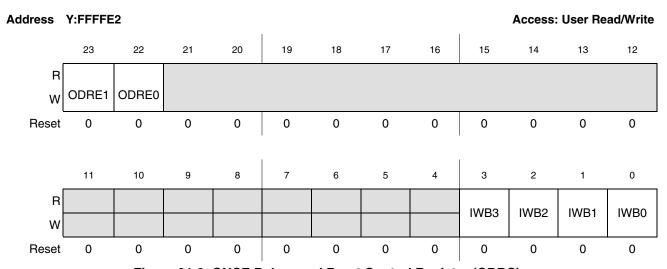

#### USA/Europe or Locations Not Listed:

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064, Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405

Denver, Colorado 80217

1-800-521-6274 or 303-675-2140

Fax: 303-675-2150

LDCForFreescaleSemiconductor@hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc. 2006–2008. All rights reserved.

# **Contents**

# Chapter 1 Introduction

| 1.1    | Overview                                                               | 1-1  |

|--------|------------------------------------------------------------------------|------|

| 1.2    | Block Diagram                                                          | 1-3  |

| 1.3    | Benefits and Features                                                  | 1-4  |

| 1.4    | Overview of Peripherals                                                | 1-5  |

| 1.4.1  | Direct Memory Access Controller (DMA, DMA_1)                           | 1-5  |

| 1.4.2  | Program Interrupt Controller (PIC, PIC_1)                              | 1-5  |

| 1.4.3  | Enhanced Serial Audio Interfaces (ESAI, ESAI_1, ESAI_2, ESAI_3)        |      |

| 1.4.4  | Serial Host Interfaces (SHI, SHI_1)                                    |      |

| 1.4.5  | Host Interfaces (HDI24, HDI24_1)                                       |      |

| 1.4.6  | Triple Timers (TEC, TEC_1)                                             |      |

| 1.4.7  | Watch Dog Timers (WDT, WDT_1)                                          |      |

| 1.4.8  | Core Integration Modules (CIM, CIM_1)                                  |      |

| 1.4.9  | Sony/Philips Digital Interface (S/PDIF)                                |      |

| 1.4.10 | Asynchronous Sample Rate Converter (ASRC)                              |      |

| 1.4.11 | External Memory Controller (EMC)                                       |      |

| 1.4.12 | Clock Generation Module (CGM)                                          |      |

| 1.4.13 | Shared Memory                                                          |      |

| 1.4.14 | Inter-Core Communication (ICC).                                        |      |

| 1.4.15 | Shared Bus Arbiters                                                    |      |

| 1.4.16 | Chip Configuration Module                                              |      |

| 1.4.17 | JTAG Controller                                                        | 1-9  |

|        | al Descriptions                                                        |      |

| 2.1    | Signal Groupings                                                       |      |

| 2.2    | Signals in Each Functional Group                                       |      |

| 2.2.1  | Power                                                                  |      |

| 2.2.2  | Ground                                                                 |      |

| 2.2.3  | SCAN                                                                   |      |

| 2.2.4  | Clock and PLL                                                          |      |

| 2.2.5  | Reset Pin                                                              |      |

| 2.2.6  | Interrupt and Mode Control                                             |      |

| 2.2.7  | DSP Core-1 Non-Maskable Interrupt (NMI1)                               |      |

| 2.2.8  | Serial Host Interface (SHI and SHI_1)                                  |      |

| 2.2.9  | Enhanced Serial Audio Interface Signals (ESAI, ESAI_1, ESAI_2, ESAI_3) |      |

| 2.2.10 | Watch Dog Timer (WDT)                                                  |      |

| 2.2.11 | Timer Event Counters (TEC, TEC_1)                                      |      |

| 2.2.12 | Host Interface Signals (HDI24 & HDI24_1)                               |      |

| 2.2.13 | External Memory Controller (EMC)                                       |      |

| 2.2.14 | S/PDIF Audio Interface Signals                                         |      |

| 2.2.15 | Dedicated Port G GPIOs                                                 | 2-45 |

|        |                                                                        |      |

Symphony DSP56720/DSP56721 Multi-Core Audio Processors Reference Manual, Rev. 1.1

Freescale Semiconductor

iii

| 2.2.16                                                         | JTAG/OnCE Interface Signals                                                                                                                                                                                                                                                                        |

|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chap<br>Mem                                                    | eter 3<br>ory Map                                                                                                                                                                                                                                                                                  |

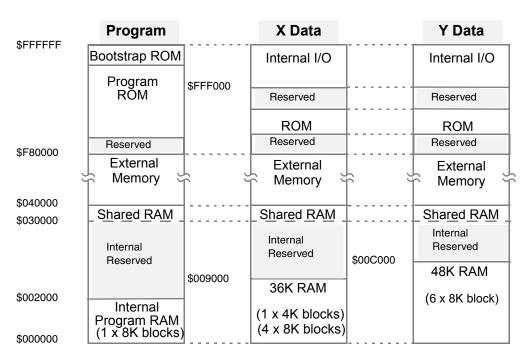

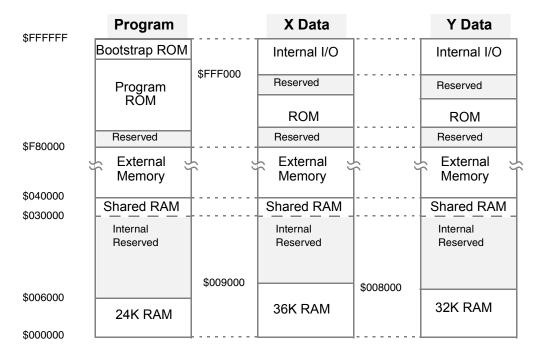

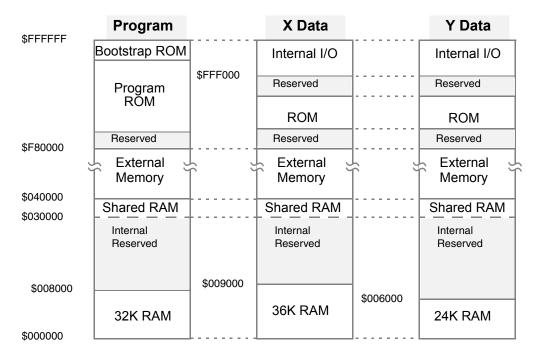

| 3.1<br>3.2<br>3.3                                              | Overview.3-1Data and Program Memory Maps.3-2Peripheral Register Memory Map.3-6                                                                                                                                                                                                                     |

| Chap<br>DSP5                                                   | iter 4<br>66300 Platform                                                                                                                                                                                                                                                                           |

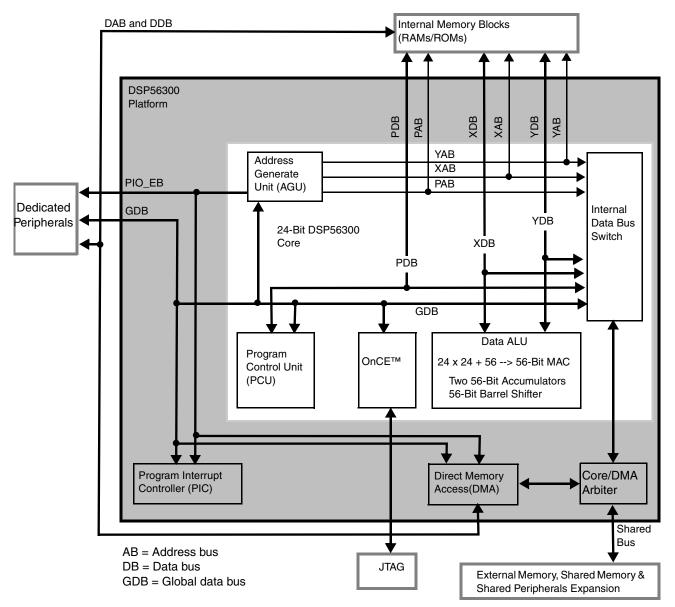

| 4.1<br>4.2<br>4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5 | Overview.       4-1         DSP56300 Core Features       4-3         DSP56300 Block Descriptions       4-3         Data ALU.       4-3         Address Generation Unit (AGU)       4-4         Program Control Unit (PCU)       4-5         Internal Buses       4-6         OnCE Module       4-6 |

| Chap<br>Core                                                   | ter 5<br>Configuration                                                                                                                                                                                                                                                                             |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7                  | Introduction.5-1Operating Mode Register (OMR)5-1Status Register (SR)5-3DSP Cores Operating Modes5-6Interrupt Priority Registers5-10DMA Request Sources5-21Chip ID Register5-23                                                                                                                     |

| Chap<br>Core                                                   | ter 6 Integration Module (CIM, CIM_1)                                                                                                                                                                                                                                                              |

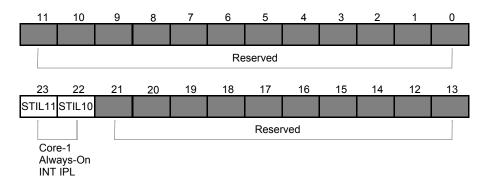

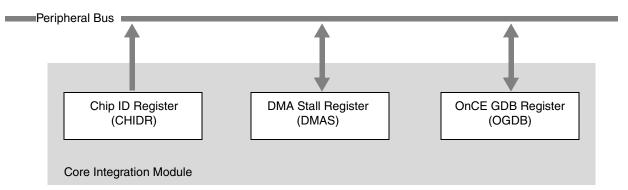

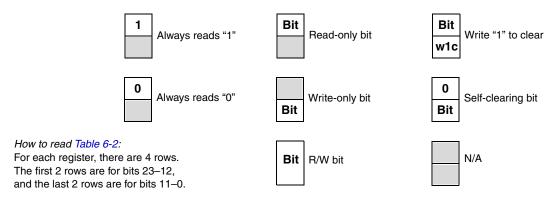

| 6.1<br>6.1.1<br>6.1.2<br>6.2<br>6.2.1<br>6.2.2<br>6.2.3        | Overview.       6-1         Memory Map       6-2         Register Summary.       6-2         Register Descriptions       6-3         Chip ID Register (CHIDR)       6-3         DMA Stall Register (DMAS)       6-4         OnCE Global Data Bus Register (OGDB)       6-5                         |

# Chapter 7 Clock Generation Module (CGM)

| 7.1    | Introduction                                               | 7-1 |

|--------|------------------------------------------------------------|-----|

| 7.1.1  | Overview of Modes                                          | 7-1 |

| 7.1.2  | Features                                                   | 7-2 |

| 7.1.3  | Modes of Operation                                         | 7-2 |

| 7.1.4  | External Signal Description                                | 7-3 |

| 7.2    | Functional Description                                     |     |

| 7.2.1  | Clocks                                                     | 7-4 |

| 7.2.2  | Reset                                                      |     |

| 7.2.3  | Interrupts                                                 |     |

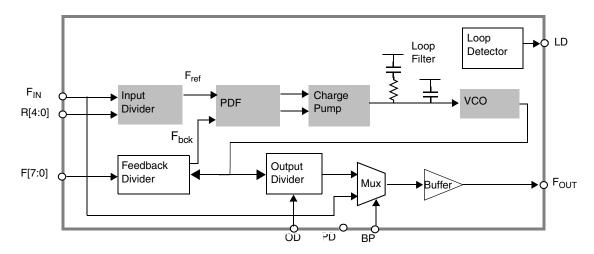

| 7.2.4  | Internal PLL Block                                         |     |

| 7.2.5  | Low Power Divider.                                         |     |

| 7.3    | Memory Map and Register Definition                         |     |

| 7.3.1  | Memory Map                                                 |     |

| 7.3.2  | Register Summary                                           |     |

| 7.3.3  | Register Descriptions                                      |     |

| 7.3.5  | register bescriptions                                      | , , |

| Chap   | ter 8                                                      |     |

| Gene   | ral Purpose Input/Output (GPIO)                            |     |

|        | , , , , , , , , , , , , , , , , , , ,                      |     |

| 8.1    | Introduction                                               | 8-1 |

| 8.2    | Programming Model                                          | 8-1 |

| 8.2.1  | Port C, Port E, Port C1, Port E1 Signals and Registers     | 8-2 |

| 8.2.2  | Port H Signals and Registers                               | 8-2 |

| 8.2.3  | Port H1 Signals and Registers                              | 8-4 |

| 8.2.4  | Port A Signals and Registers                               | 8-7 |

| 8.2.5  | Port G Signals and Registers                               |     |

| 8.2.6  | Timer Event Counter Signals                                |     |

|        | 8                                                          |     |

| Chap   | ter 9                                                      |     |

|        | nced Serial Audio Interface (ESAI, ESAI_1, ESAI_2, ESAI_3) |     |

|        |                                                            |     |

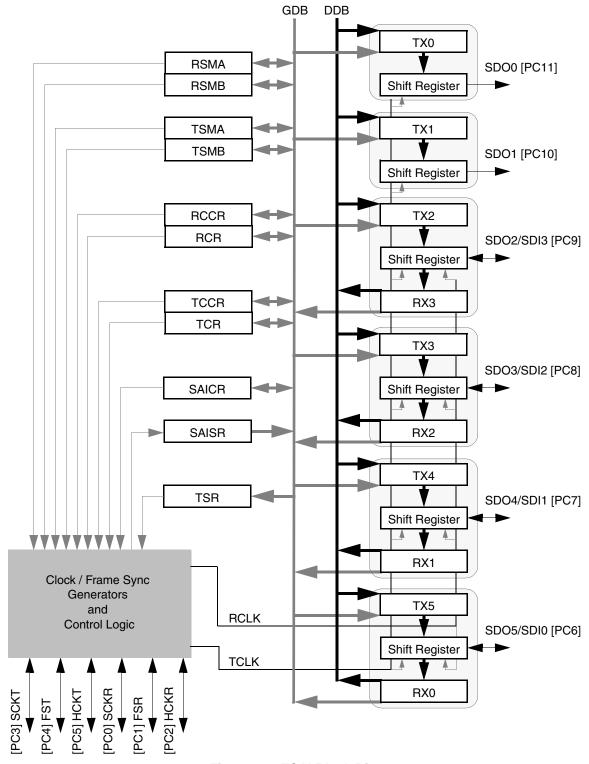

| 9.1    | ESAI Data and Control Pins                                 |     |

| 9.1.1  | Serial Transmit 0 Data Pin (SDO0)                          |     |

| 9.1.2  | Serial Transmit 1 Data Pin (SDO1)                          |     |

| 9.1.3  | Serial Transmit 2/Receive 3 Data Pin (SDO2/SDI3)           |     |

| 9.1.4  | Serial Transmit 3/Receive 2 Data Pin (SDO3/SDI2)           | 9-4 |

| 9.1.5  | Serial Transmit 4/Receive 1 Data Pin (SDO4/SDI1)           | 9-4 |

| 9.1.6  | Serial Transmit 5/Receive 0 Data Pin (SDO5/SDI0)           | 9-4 |

| 9.1.7  | Receiver Serial Clock (SCKR)                               |     |

| 9.1.8  | Transmitter Serial Clock (SCKT)                            |     |

| 9.1.9  | Frame Sync for Receiver (FSR)                              |     |

| 9.1.10 | ·                                                          |     |

| 9.1.11 | High Frequency Clock for Transmitter (HCKT)                |     |

|        | 0 15000) 02000 201 22000000000 (220112)                    | , 0 |

|        |                                                            |     |

Freescale Semiconductor

Symphony DSP56720/DSP56721 Multi-Core Audio Processors Reference Manual, Rev. 1.1

| 9.1.12 | High Frequency Clock for Receiver (HCKR)                              |       |

|--------|-----------------------------------------------------------------------|-------|

| 9.2    | ESAI Programming Model                                                |       |

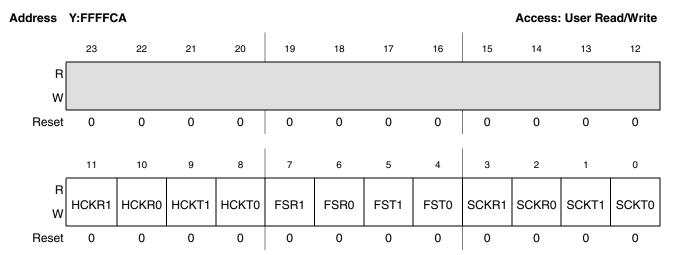

| 9.2.1  | ESAI Transmitter Clock Control Register (TCCR)                        | . 9-9 |

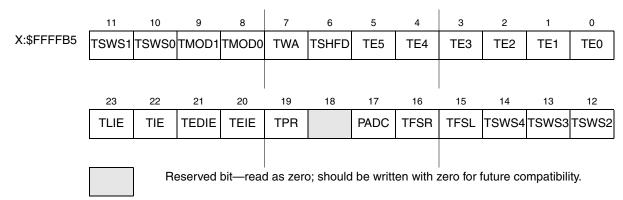

| 9.2.2  | ESAI Transmit Control Register (TCR)                                  | 9-13  |

| 9.2.3  | ESAI Receive Clock Control Register (RCCR)                            | 9-23  |

| 9.2.4  | ESAI Receive Control Register (RCR)                                   | 9-27  |

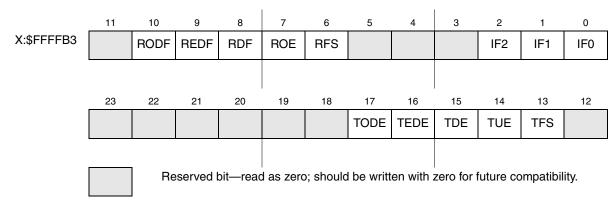

| 9.2.5  | ESAI Common Control Register (SAICR)                                  | 9-32  |

| 9.2.6  | ESAI Status Register (SAISR)                                          | 9-34  |

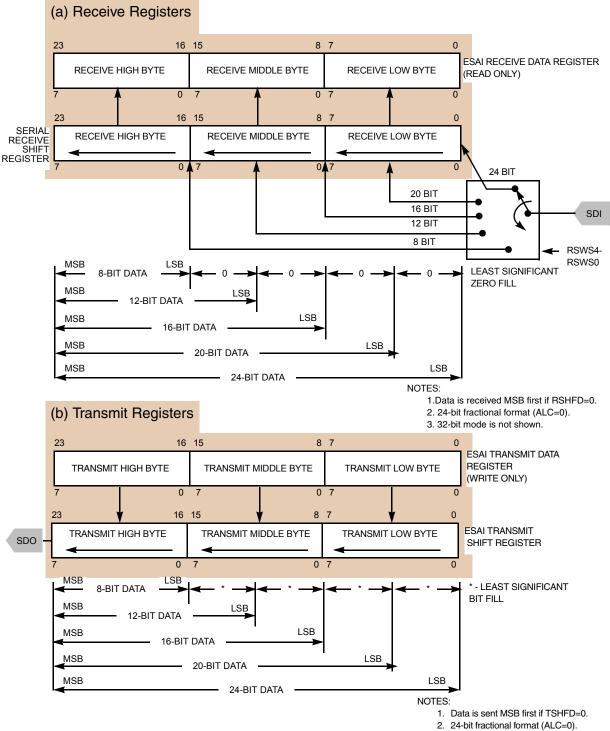

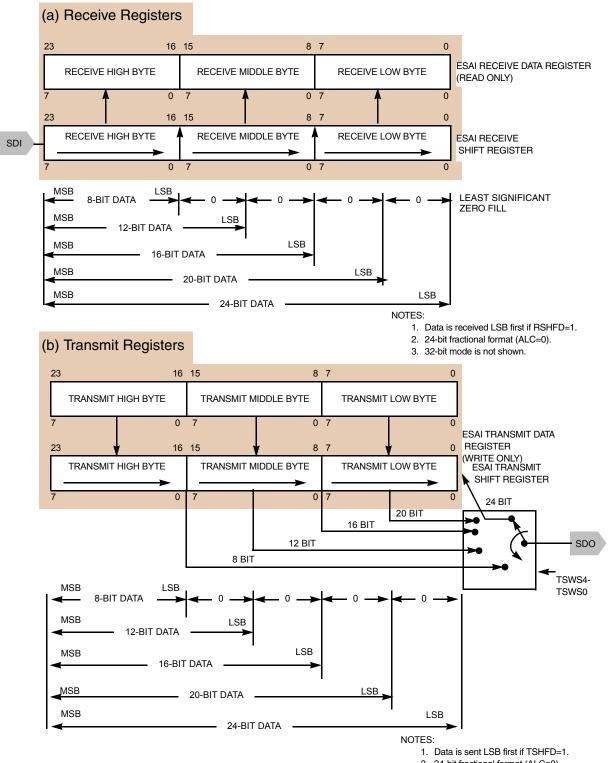

| 9.2.7  | ESAI Receive Shift Registers                                          | 9-41  |

| 9.2.8  | ESAI Receive Data Registers (RX3, RX2, RX1, RX0)                      | 9-41  |

| 9.2.9  | ESAI Transmit Shift Registers                                         |       |

| 9.2.10 | ESAI Transmit Data Registers (TX5, TX4, TX3, TX2,TX1,TX0)             | 9-41  |

| 9.2.11 | ESAI Time Slot Register (TSR)                                         |       |

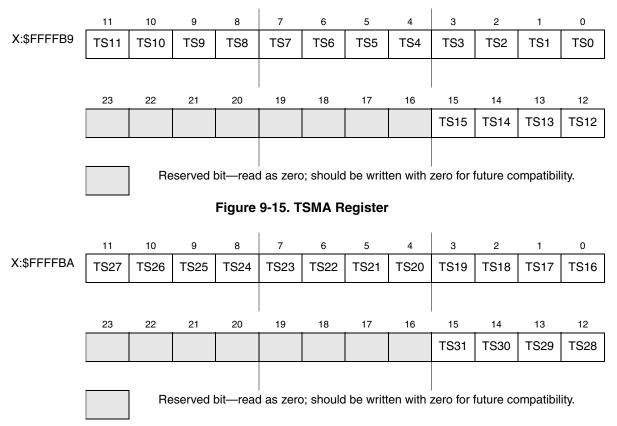

| 9.2.12 | Transmit Slot Mask Registers (TSMA, TSMB)                             | 9-41  |

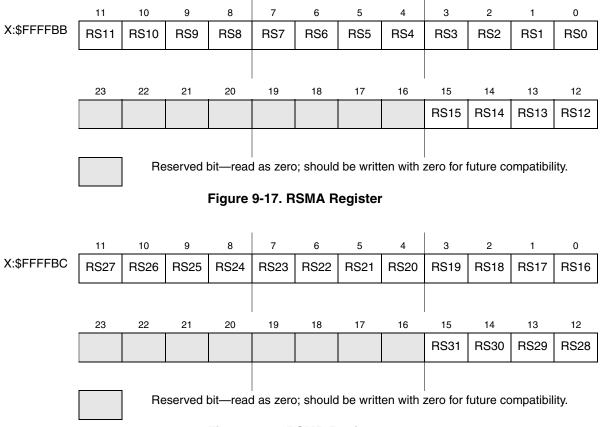

| 9.2.13 | Receive Slot Mask Registers (RSMA, RSMB)                              | 9-43  |

| 9.3    | Operating Modes                                                       | 9-44  |

| 9.3.1  | ESAI After Reset                                                      | 9-44  |

| 9.3.2  | ESAI Initialization                                                   | 9-44  |

| 9.3.3  | ESAI Interrupt Requests                                               | 9-45  |

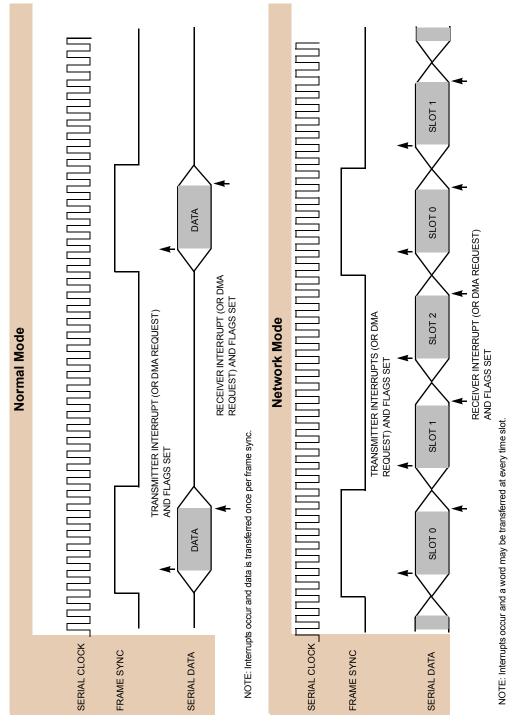

| 9.3.4  | Operating Modes—Normal, Network and On-Demand                         | 9-46  |

| 9.3.5  | Serial I/O Flags                                                      | 9-47  |

| 9.4    | GPIO—Pins and Registers                                               | 9-48  |

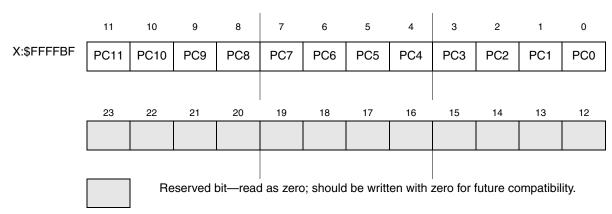

| 9.4.1  | Port C Control Register (PCRC)                                        | 9-48  |

| 9.4.2  | Port C Direction Register (PRRC)                                      | 9-48  |

| 9.4.3  | Port C Data Register (PDRC)                                           | 9-49  |

| 9.5    | ESAI Initialization Examples                                          | 9-50  |

| 9.5.1  | Initializing the ESAI Using Individual Reset                          | 9-50  |

| 9.5.2  | Initializing Only the ESAI Transmitter Section                        | 9-50  |

| 9.5.3  | Initializing Only the ESAI Receiver Section                           | 9-51  |

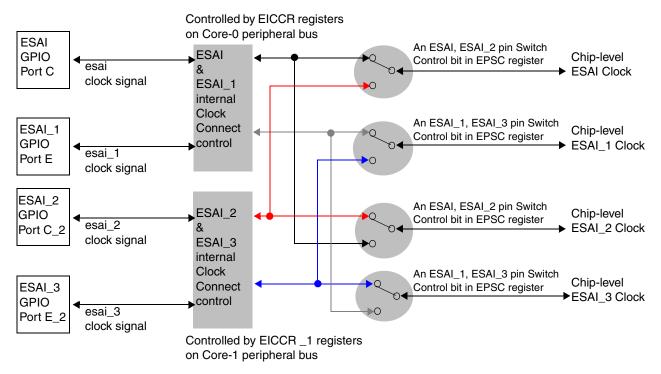

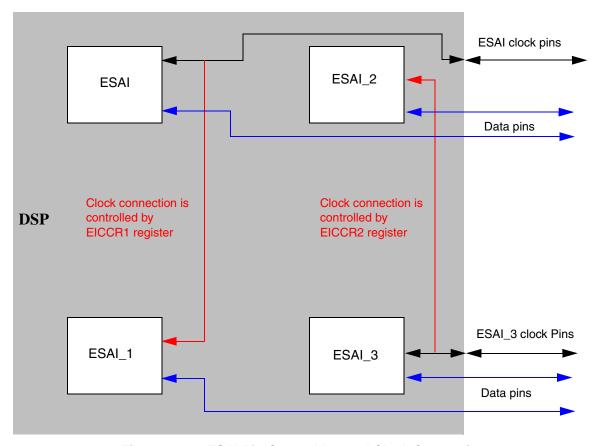

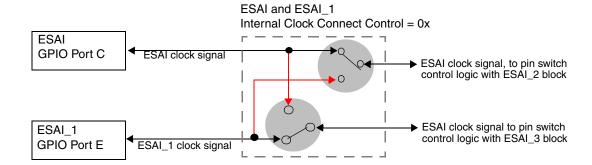

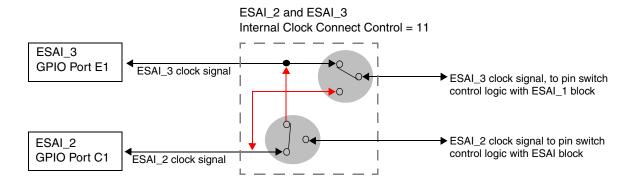

| 9.6    | ESAI/ESAI_2 and ESAI_1/ESAI_3 Pin Switch                              | 9-51  |

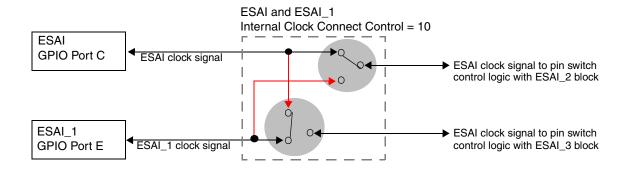

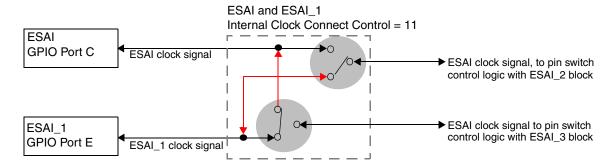

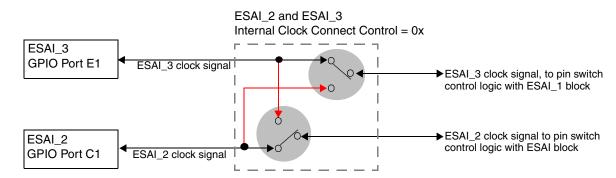

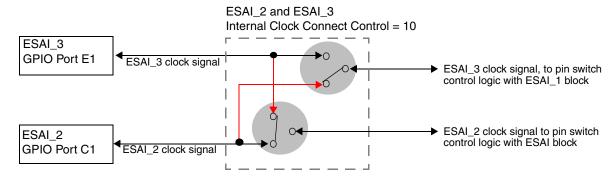

| 9.7    | Internal Clock Connections Between ESAI and ESAI_1, ESAI_2 and ESAI_3 | 9-52  |

| Chan   | ter 10                                                                |       |

| Serial | l Host Interface (SHI, SHI_1)                                         |       |

| 10.1   | Introduction                                                          | 10-1  |

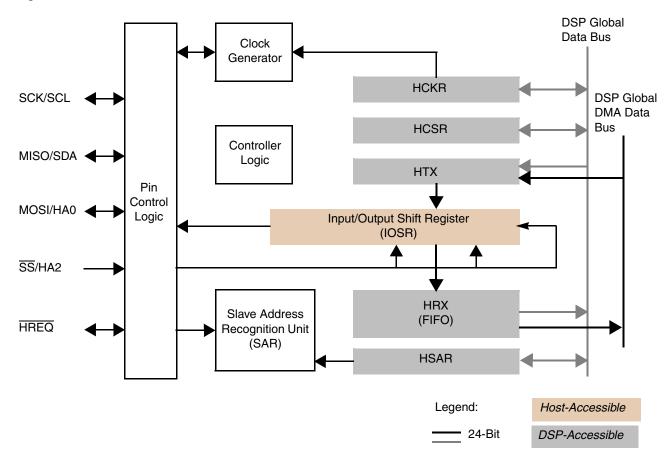

| 10.2   | Serial Host Interface Internal Architecture                           | 10-2  |

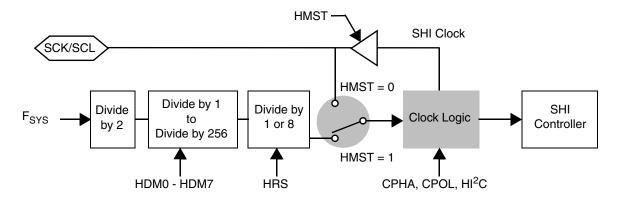

| 10.3   | SHI Clock Generator                                                   | 10-3  |

| 10.3.1 | Serial Host Interface Programming Model                               | 10-3  |

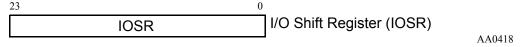

| 10.3.2 | SHI Input/Output Shift Register (IOSR)—Host Side                      |       |

| 10.3.3 | SHI Host Transmit Data Register (HTX)—DSP Side                        | 10-6  |

| 10.3.4 | SHI Host Receive Data FIFO (HRX)—DSP Side                             |       |

| 10.3.5 | SHI Slave Address Register (HSAR)—DSP Side                            |       |

| 10.3.6 | HSAR I <sup>2</sup> C Slave Address (HA[6:3], HA1)—Bits 23–20,18      |       |

| 10.3.7 | SHI Clock Control Register (HCKR)—DSP Side                            |       |

|        |                                                                       |       |

Symphony DSP56720/DSP56721 Multi-Core Audio Processors Reference Manual, Rev. 1.1

vi

| 10.3.8 | SHI Control/Status Register (HCSR)—DSP Side | 10-10  |

|--------|---------------------------------------------|--------|

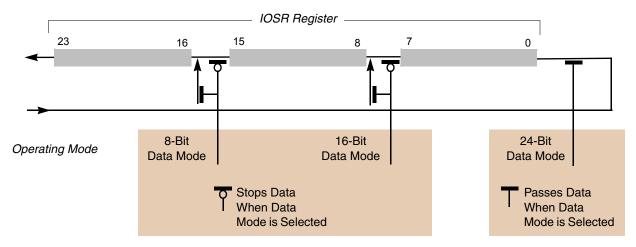

| 10.4   | Characteristics Of The SPI Bus              | 10-17  |

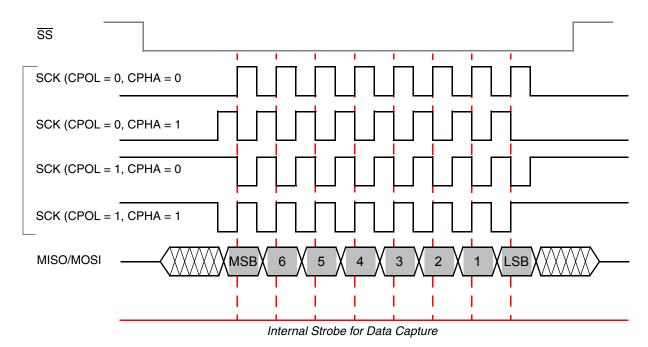

| 10.5   | Characteristics Of The I <sup>2</sup> C Bus | 10-18  |

| 10.5.1 | Overview                                    | 10-18  |

| 10.5.2 | I <sup>2</sup> C Data Transfer Formats      | 10-20  |

| 10.6   | SHI Programming Considerations              | 10-20  |

| 10.6.1 | SPI Slave Mode                              | 10-21  |

| 10.6.2 | SPI Master Mode                             | 10-22  |

| 10.6.3 | I <sup>2</sup> C Slave Mode                 |        |

| 10.6.4 | I <sup>2</sup> C Master Mode                |        |

| 10.6.5 | SHI Operation During DSP Stop               |        |

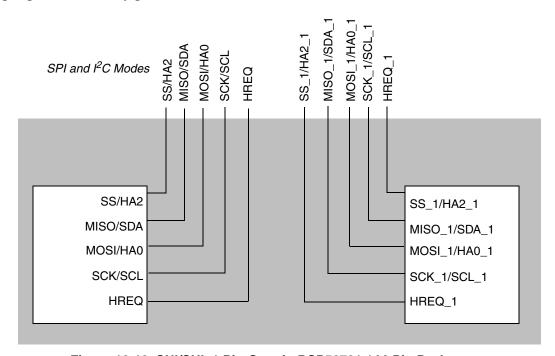

| 10.7   | SHI Pin-Outs for Device Packages            |        |

| 10.7.1 | SHI Pin-Outs for Small Pin Count Packages   |        |

| 10.7.2 | SHI Pin-Out in DSP56721 144-Pin Packages    | 10-29  |

|        |                                             |        |

|        | ter 11                                      |        |

| ripie  | e Timer Module (TEC, TEC_1)                 |        |

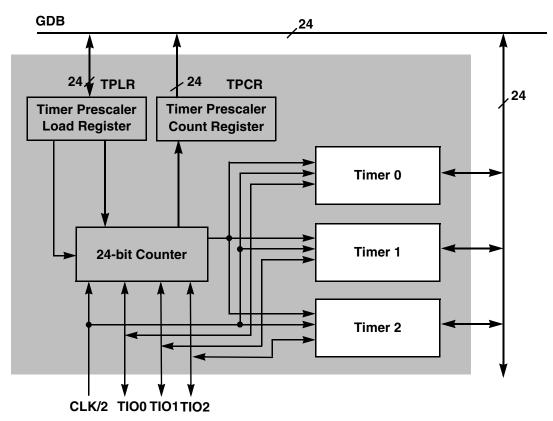

| 11.1   | Introduction                                | . 11-1 |

| 11.1.1 | Overview                                    | . 11-1 |

| 11.1.2 | Triple Timer Module Block Diagram           | . 11-1 |

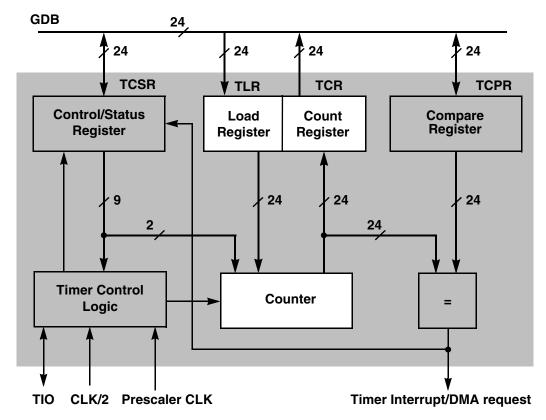

| 11.2   | Individual Timer Block Diagram              |        |

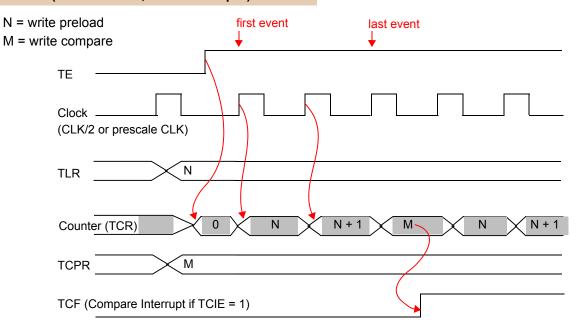

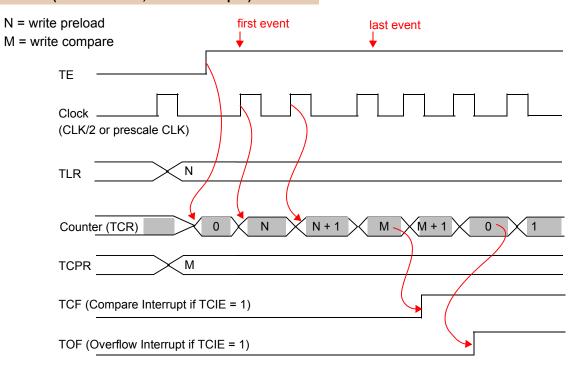

| 11.3   | Operation                                   | . 11-3 |

| 11.3.1 | Timer After Reset                           | . 11-3 |

| 11.3.2 | Timer Initialization                        | . 11-3 |

| 11.3.3 | Timer Exceptions                            | . 11-4 |

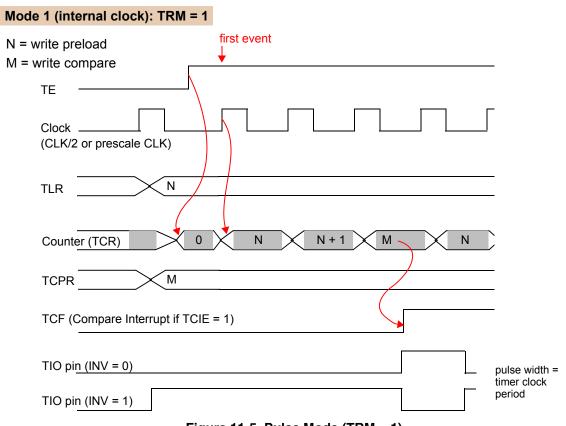

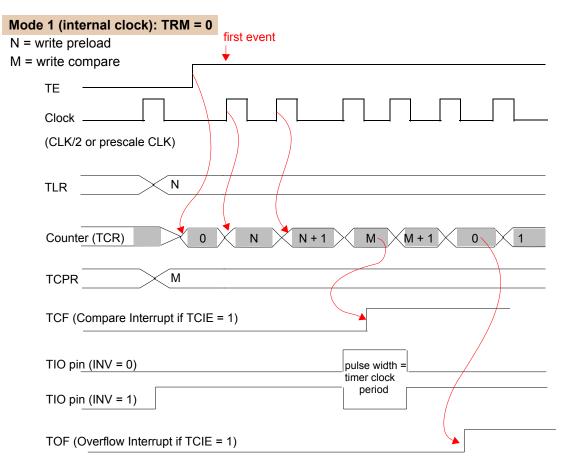

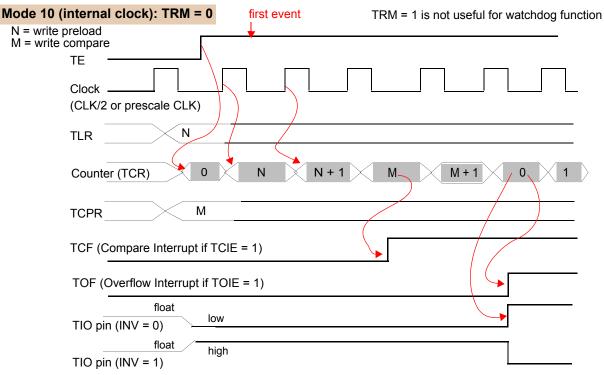

| 11.4   | Operating Modes                             | . 11-4 |

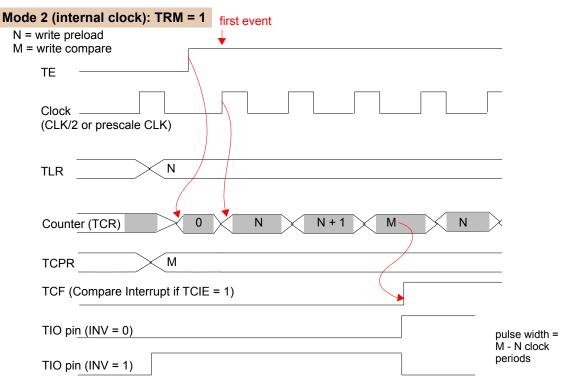

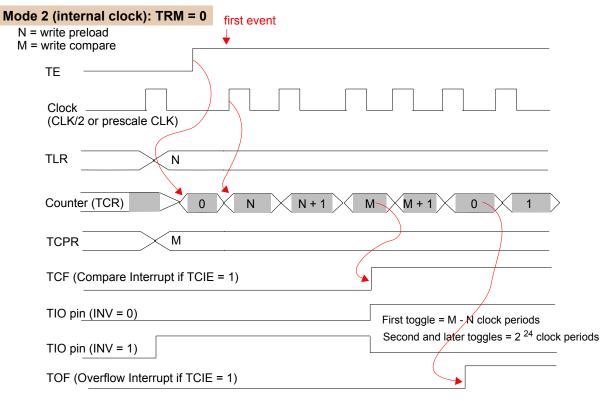

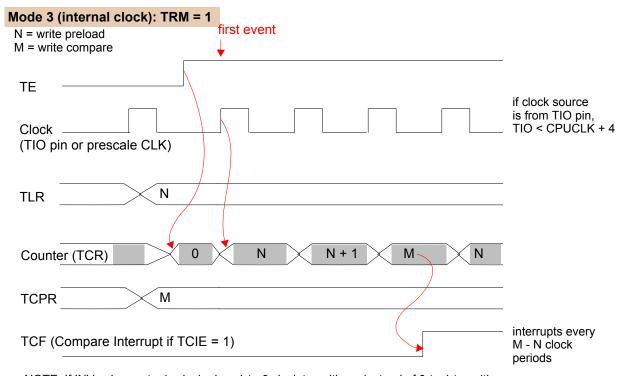

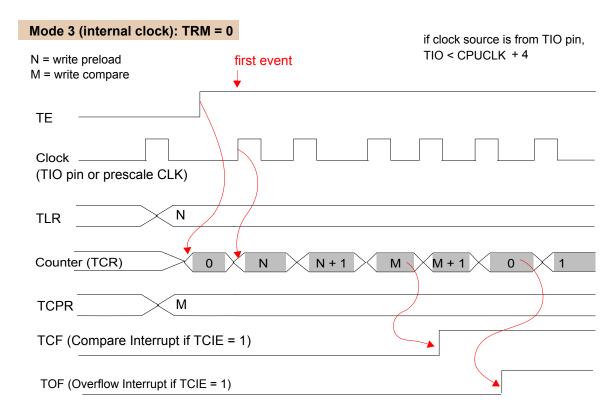

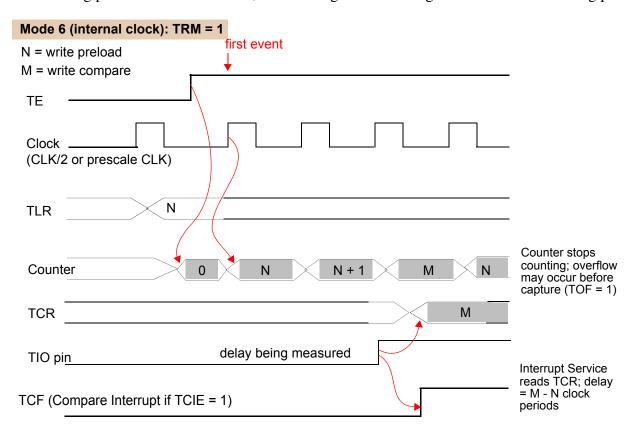

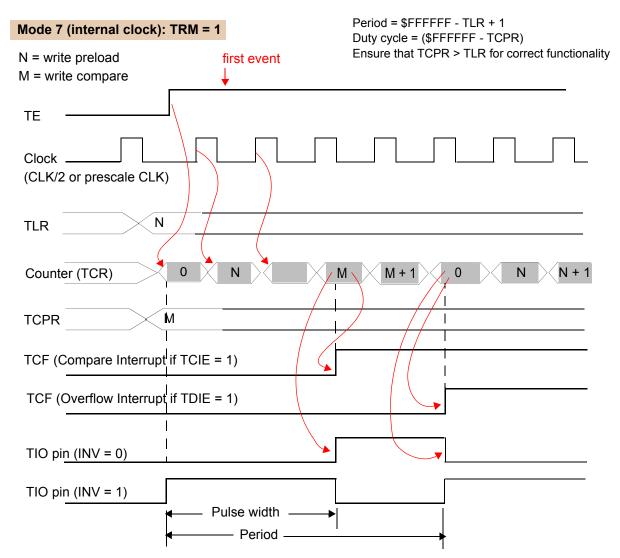

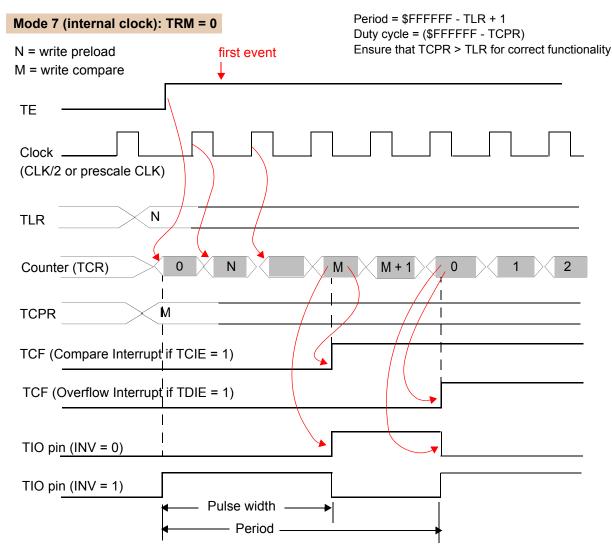

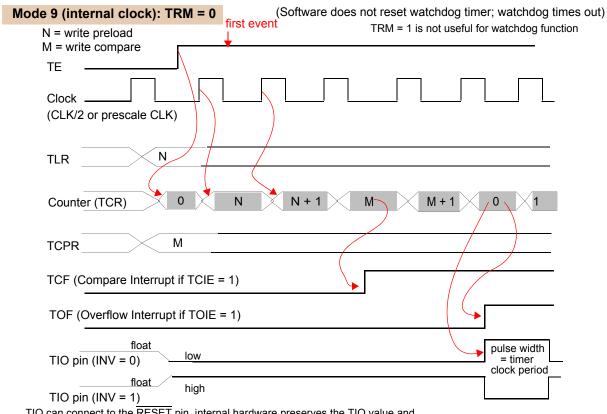

| 11.4.1 | Triple Timer Modes                          | . 11-5 |

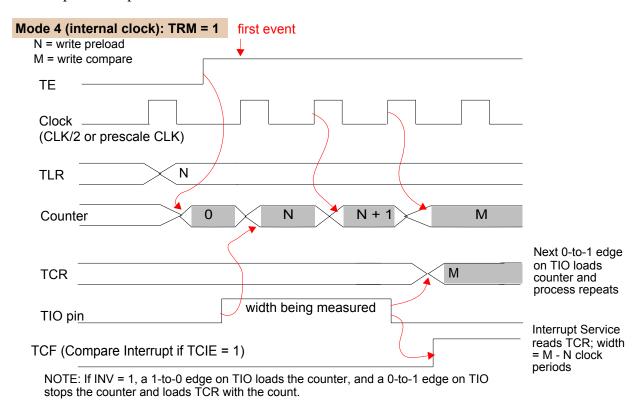

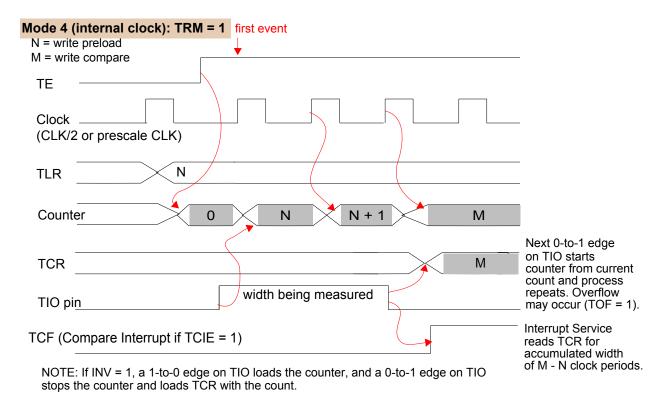

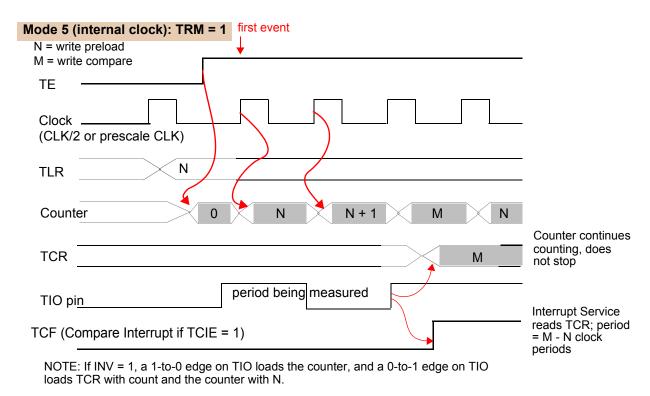

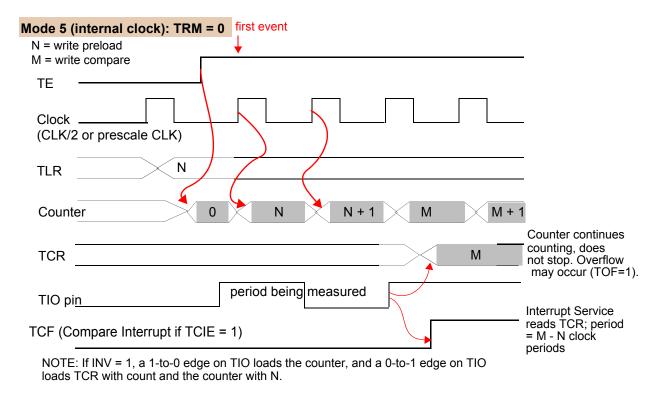

| 11.4.2 | Signal Measurement Modes                    |        |

| 11.4.3 | Watchdog Modes                              | 11-18  |

| 11.4.4 | Reserved Modes                              | 11-21  |

| 11.4.5 | Special Cases                               |        |

| 11.4.6 | DMA Trigger                                 |        |

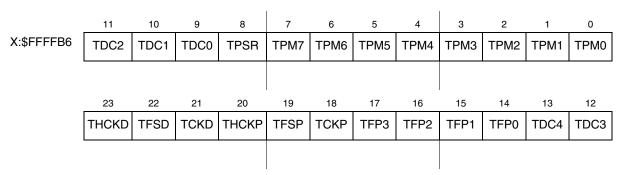

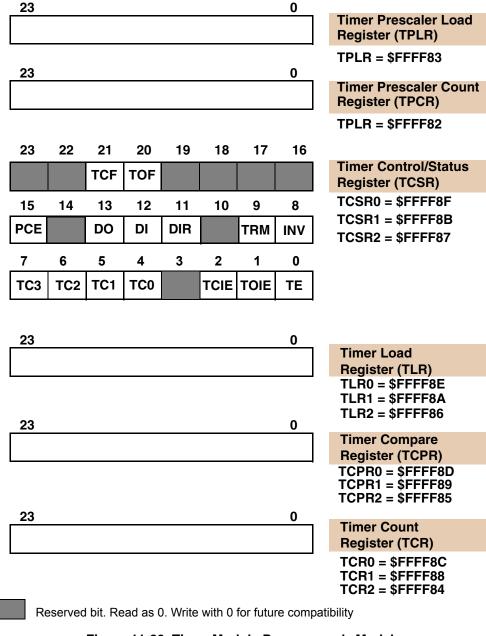

| 11.5   | Triple Timer Module Programming Model       | 11-22  |

| 11.5.1 | Prescaler Counter                           | 11-22  |

| 11.5.2 | Timer Prescaler Load Register (TPLR)        |        |

| 11.5.3 | Timer Prescaler Count Register (TPCR)       |        |

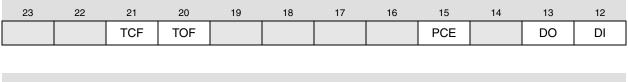

| 11.5.4 | Timer Control/Status Register (TCSR)        |        |

| 11.5.5 | Timer Load Register (TLR)                   |        |

| 11.5.6 | Timer Compare Register (TCPR)               |        |

| 11.5.7 | Timer Count Register (TCR)                  | 11-29  |

# Chapter 12 Host Data Interface (HDI24, HDI24\_1)

| 12.1   | Introduction                                | 12-1  |

|--------|---------------------------------------------|-------|

| 12.1.1 | Features                                    | 12-3  |

| 12.2   | Signal Descriptions                         | 12-5  |

| 12.3   | Memory Map and Register Definitions         |       |

| 12.3.1 | Memory Map                                  |       |

| 12.3.2 | Register Summaries                          | 12-7  |

| 12.4   | HDI24 DSP-Side Programmer's Model           |       |

| 12.4.1 | Host Receive Data Register (HORX)           | 12-9  |

| 12.4.2 | Host Transmit Data Register (HOTX)          |       |

| 12.4.3 | Host Control Register (HCR)                 |       |

| 12.4.4 | Host Status Register (HSR)                  | 12-13 |

| 12.4.5 | Host Base Address Register (HBAR)           | 12-14 |

| 12.4.6 | Host Port Control Register (HPCR)           |       |

| 12.4.7 | DSP-Side Registers After Reset              | 12-19 |

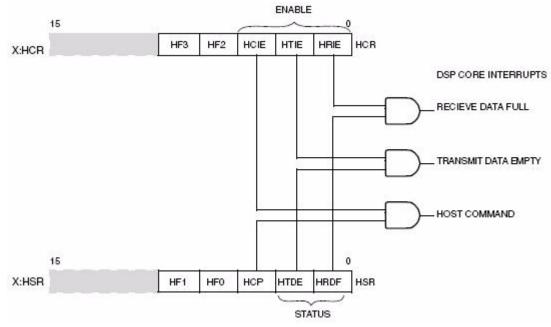

| 12.4.8 | HOST Interface DSP Core Interrupts          |       |

| 12.5   | HDI24 External Programmer's Model           |       |

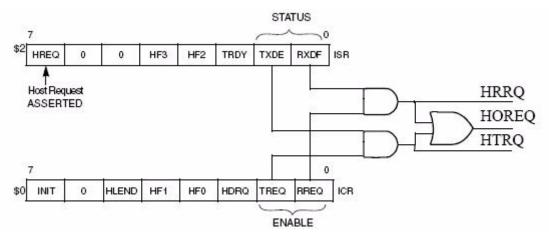

| 12.5.1 | Interface Control Register (ICR)            | 12-22 |

| 12.5.2 | Command Vector Register (CVR)               | 12-25 |

| 12.5.3 | Interface Status Register (ISR)             |       |

| 12.5.4 | Interrupt Vector Register (IVR)             | 12-28 |

| 12.5.5 | Receive Byte Registers (RXH:RXM:RXL)        | 12-28 |

| 12.5.6 | Transmit Byte Registers (TXH:TXM:TXL)       |       |

| 12.5.7 | Host-Side Registers After Reset             | 12-29 |

| 12.5.8 | General Purpose Input/Output (GPIO)         | 12-30 |

| 12.6   | Servicing the Host Interface                |       |

| 12.6.1 | HDI24 Host Processor Data Transfers         | 12-30 |

| 12.6.2 | Polling                                     | 12-30 |

| 12.6.3 | Servicing Interrupts                        |       |

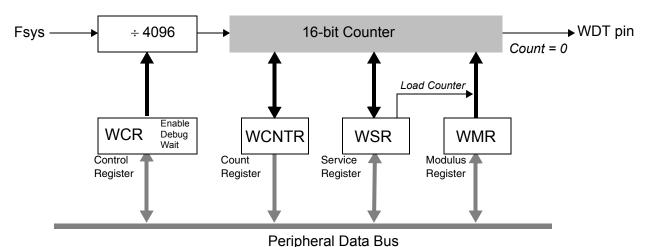

| Watc   | ter 13<br>hdog Timer (WDT, WDT_1)           |       |

|        | Introduction                                |       |

| 13.2   | WDT Pin-Outs for Different Device Packages. |       |

| 13.3   | WDT Registers                               |       |

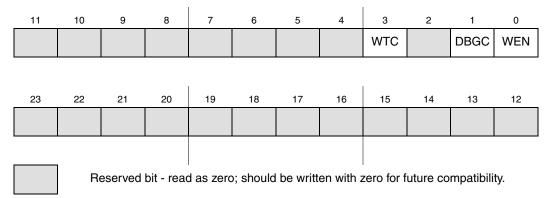

| 13.3.1 | Watchdog Control Register (WCR)             |       |

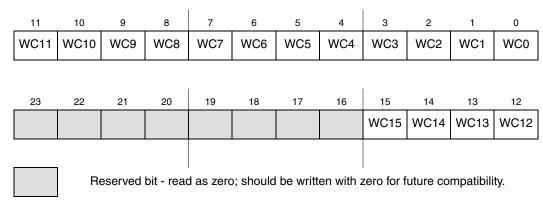

| 13.3.2 | Watchdog Counter and WCNTR Register         |       |

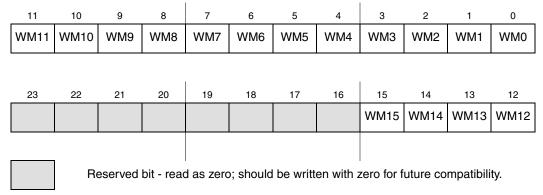

| 13.3.3 | Watchdog Modulus Register (WMR)             | 13-4  |

| 13.3.4 | Watchdog Service Register (WSR)             | 13-5  |

| 13.4   | Watchdog Operating Modes                    |       |

| 13.4.1 | Wait Mode                                   | 13-6  |

| 13.4.2 | Debug Mode                                  | 13-6  |

| 13.4.3 | Stop Mode                                   | 13-6  |

|        |                                             |       |

Symphony DSP56720/DSP56721 Multi-Core Audio Processors Reference Manual, Rev. 1.1

viii Freescale Semiconductor

# Chapter 14 Inter-Core Communication (ICC)

| 14.1        | Introduction                                                                      |

|-------------|-----------------------------------------------------------------------------------|

| 14.1.1      | Overview                                                                          |

| 14.1.2      | Features                                                                          |

| 14.2        | Memory Map and Register Definition                                                |

| 14.2.1      | Memory Map                                                                        |

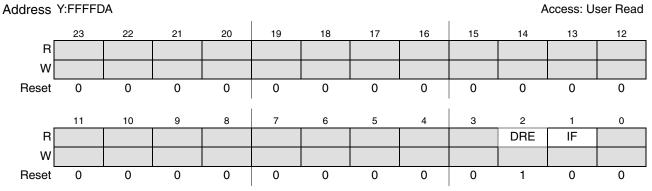

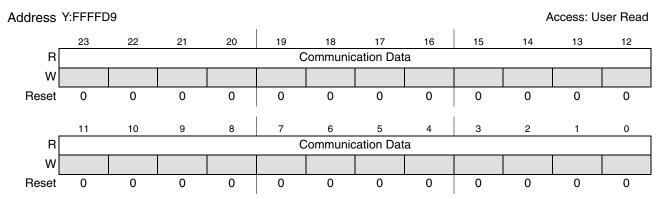

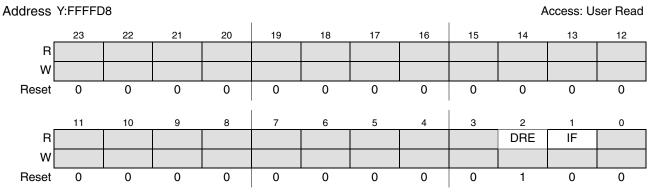

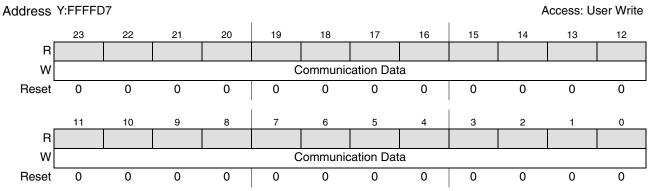

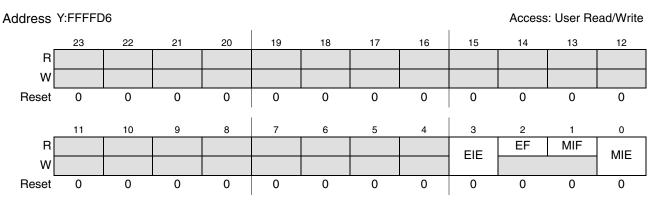

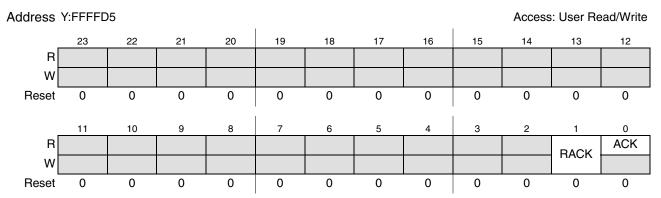

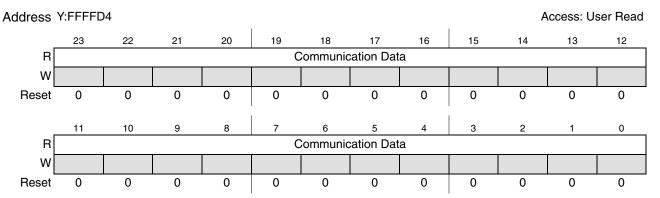

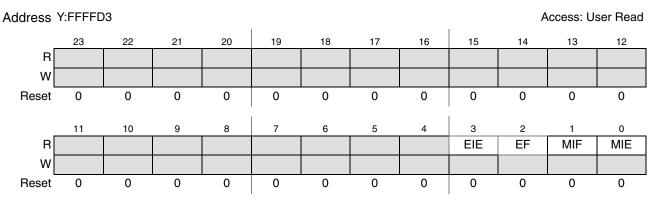

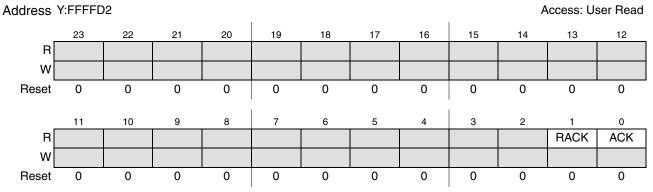

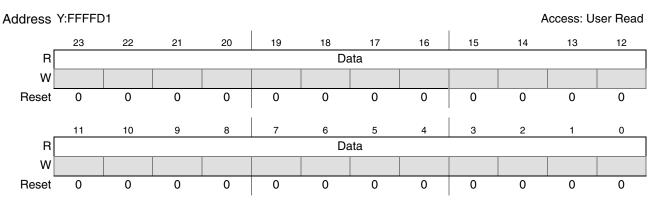

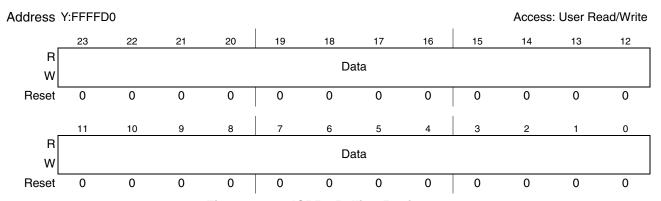

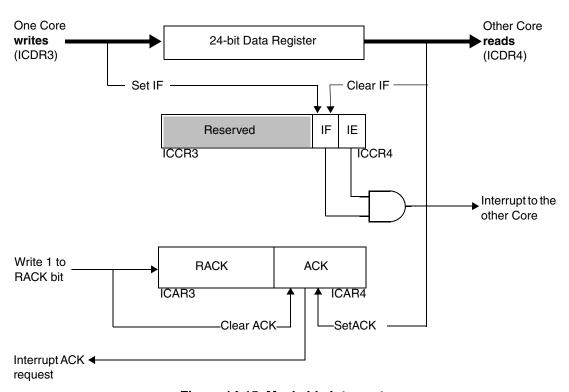

| 14.2.2      | Register Descriptions                                                             |

| 14.3        | Programming Model                                                                 |

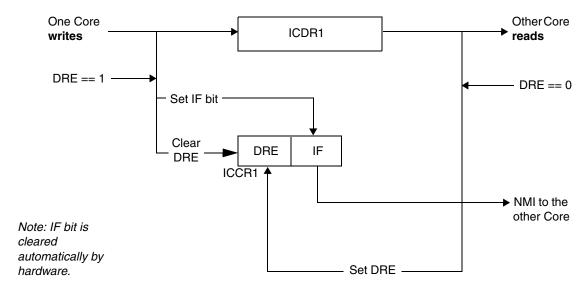

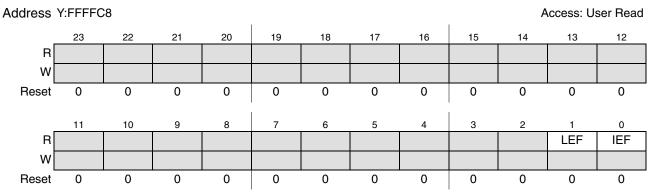

| 14.3.1      | Inter-Core Maskable Interrupts                                                    |

| 14.3.2      | Inter-Core Non-Maskable Interrupts 14-14                                          |

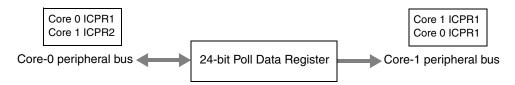

| 14.3.3      | Polling                                                                           |

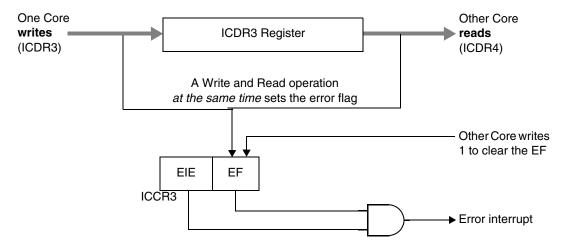

| 14.3.4      | Error Interrupts                                                                  |

| 14.3.5      | Reset                                                                             |

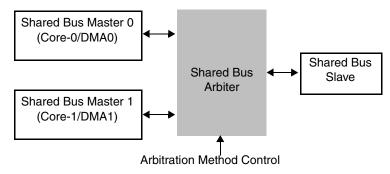

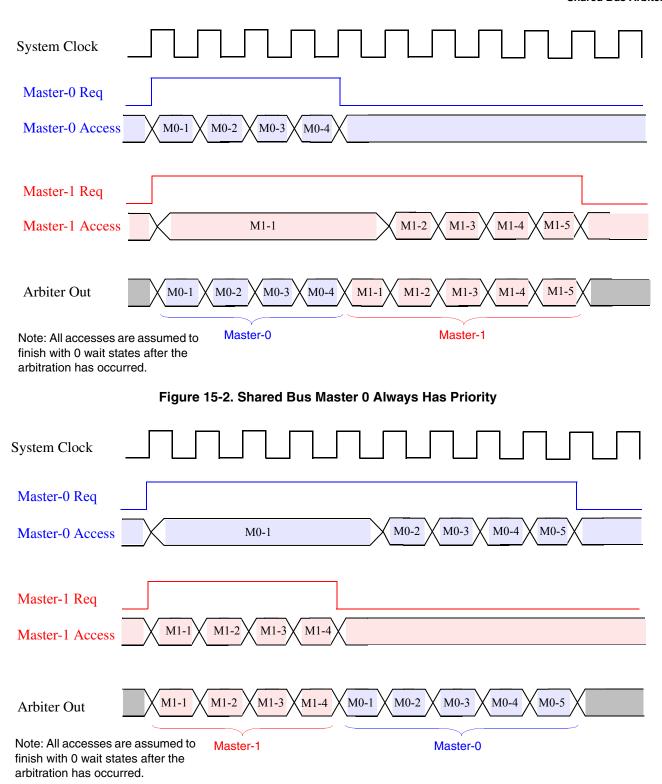

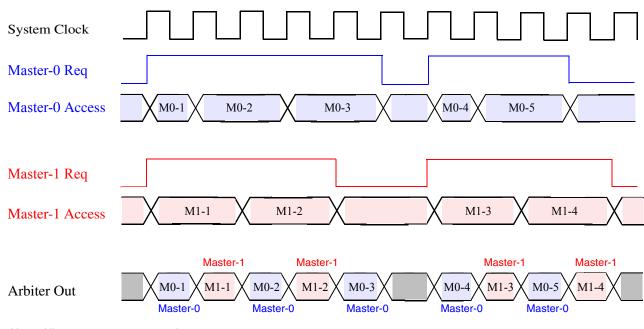

|             | ter 15<br>ed Bus Arbiter                                                          |

| 15.1        | Introduction                                                                      |

| 15.1.1      | Overview                                                                          |

| 15.1.2      | Features                                                                          |

| 15.2        | Memory Map and Register Definition                                                |

| 15.3        | Functional Description                                                            |

| 15.3.1      | Shared Bus Arbitration                                                            |

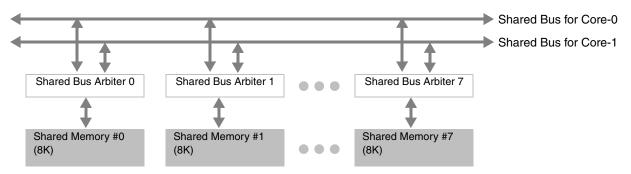

|             | ter 16<br>ed Memory (Shared Memory)                                               |

| 16.1        | Overview                                                                          |

| 16.2        | Block Diagram                                                                     |

|             | ter 17<br>ed Peripheral Bus                                                       |

| 17.1        | Introduction. 17-1                                                                |

| 17.1.1      | Features                                                                          |

| 17.2        | Memory Map and Register Definition                                                |

| 17.3        | Functional Description                                                            |

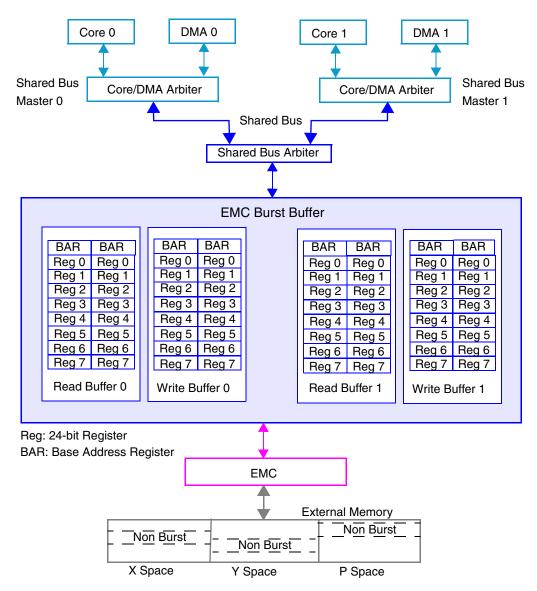

| Chap<br>EMC | ter 18<br>Burst Buffer                                                            |

| 18.1        | Introduction                                                                      |

| 18.1.1      | Overview                                                                          |

| 18.1.2      | Features                                                                          |

| 18.2        | Memory Map and Register Definition                                                |

|             | Symphony DSP56720/DSP56721 Multi-Core Audio Processors Reference Manual, Rev. 1.1 |

|         | Functional Description                                                            | 18-3    |

|---------|-----------------------------------------------------------------------------------|---------|

| 18.3.1  | Burst Control                                                                     | 18-3    |

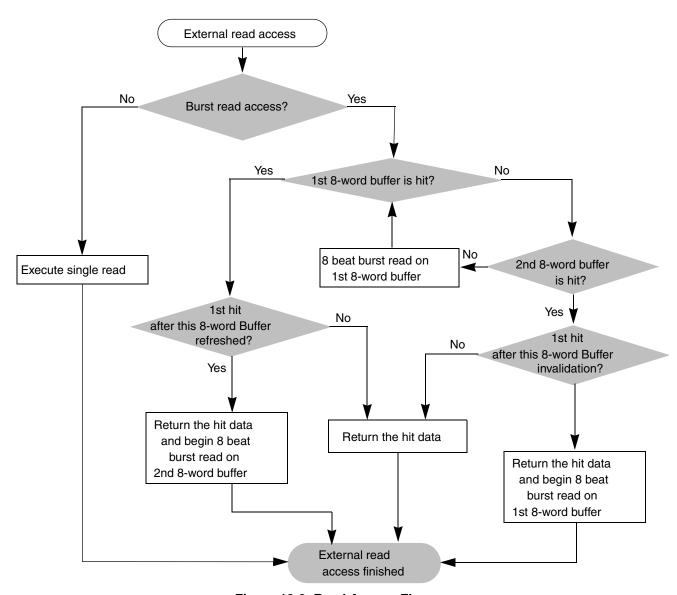

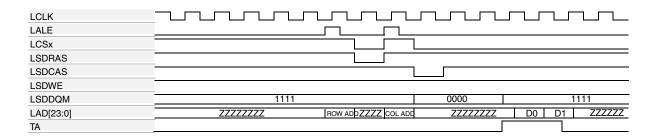

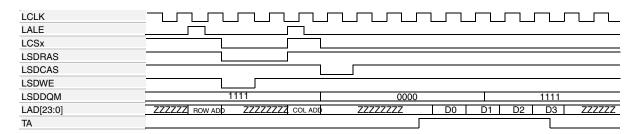

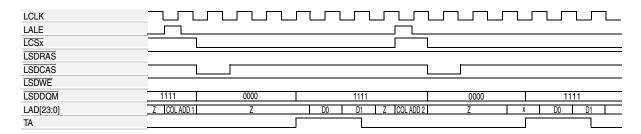

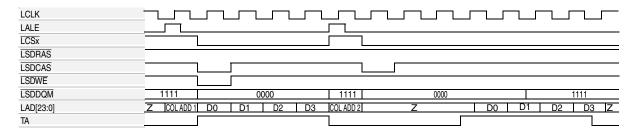

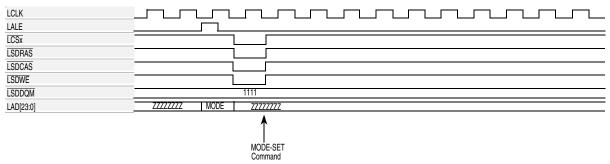

| 18.3.2  | Read Access                                                                       | 18-5    |

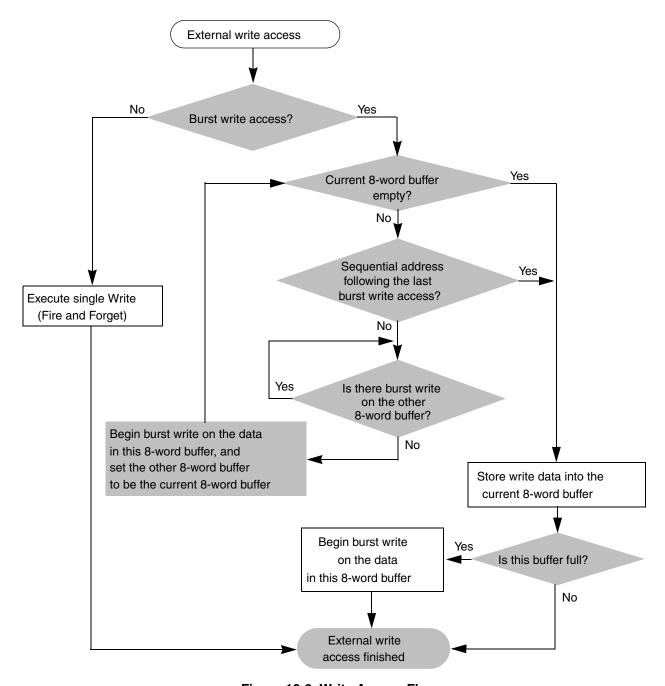

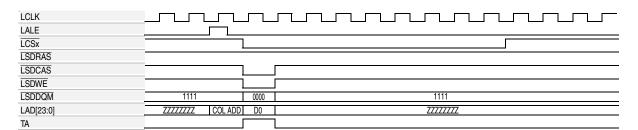

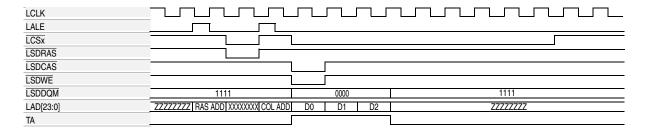

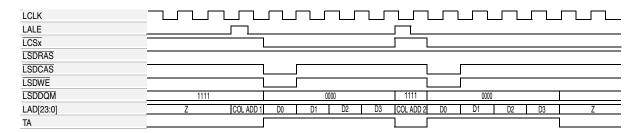

| 18.3.3  | Write Access                                                                      | 18-6    |

| Chap    | ter 19                                                                            |         |

| S/PDI   | IF—Sony/Philips Digital Interface                                                 |         |

| 19.1    | Introduction                                                                      | 19-1    |

| 19.1.1  | Features                                                                          | 19-3    |

| 19.1.2  | External Signal Description                                                       | 19-3    |

| 19.1.3  | Memory Map                                                                        |         |

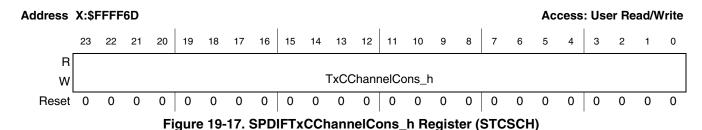

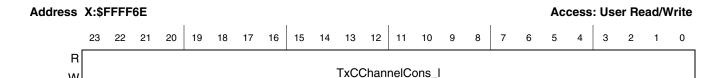

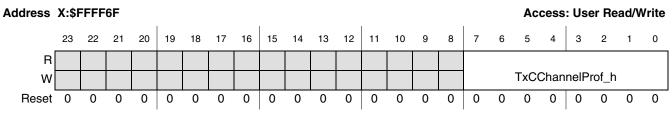

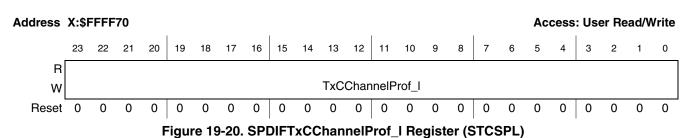

| 19.2    | Register Descriptions                                                             |         |

| 19.2.1  | S/PDIF Configuration Register (SCR)                                               |         |

| 19.2.2  | CDText Control Register (SRCD)                                                    |         |

| 19.2.3  | PhaseConfig Register (SRPC)                                                       |         |

| 19.2.4  | Interrupt Registers (SIE, SIS, SIC)                                               |         |

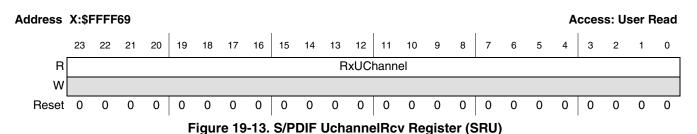

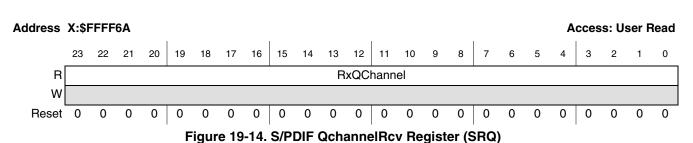

| 19.2.5  | S/PDIF Reception Registers                                                        |         |

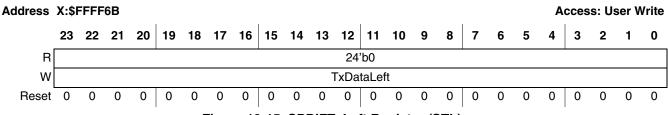

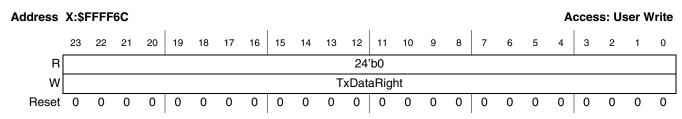

| 19.2.6  | S/PDIF Transmission Registers                                                     |         |

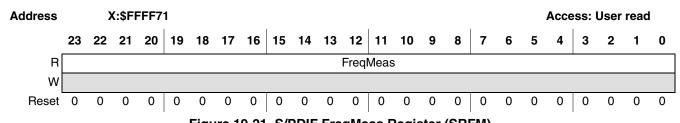

| 19.2.7  | S/PDIF FreqMeas Register (SRFM)                                                   |         |

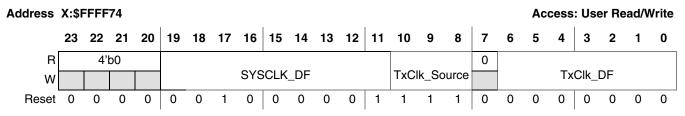

| 19.2.8  | SPDIFTxClk Register (STC)                                                         |         |

| 19.3    | S/PDIF Receiver                                                                   |         |

| 19.3.1  | Audio Data Reception                                                              |         |

| 19.3.2  | Channel Status Reception                                                          |         |

| 19.3.3  | User Bit Reception                                                                |         |

| 19.3.4  | Validity Flag Reception                                                           |         |

| 19.3.5  | S/PDIF Receiver Interrupt Exception Definition                                    |         |

| 19.3.6  | Standards Compliance                                                              |         |

| 19.3.7  | S/PDIF PLOCK Detection and Rxclk Output                                           |         |

| 19.3.8  | Measuring the Frequency of SPDIF_RcvClk                                           |         |

| 19.4    | S/PDIF Transmitter                                                                |         |

| 19.4.1  | Audio Data Transmission                                                           |         |

| 19.4.2  | Channel Status Transmission                                                       |         |

| 19.4.3  | Validity Flag Transmission.                                                       | ,       |

| 17.11.5 | variately 1 mg 17miomiositom                                                      | . 1, 2. |

|         | ter 20                                                                            |         |

| Asyn    | chronous Sample Rate Converter                                                    |         |

| 20.1    | Introduction                                                                      | 20-1    |

| 20.1.1  | Overview                                                                          | 20-2    |

| 20.1.2  | Features                                                                          | 20-3    |

| 20.1.3  | Modes of Operation                                                                | 20-3    |

| 20.2    | Memory Map and Register Definitions                                               |         |

| 20.2.1  | Memory Map                                                                        |         |

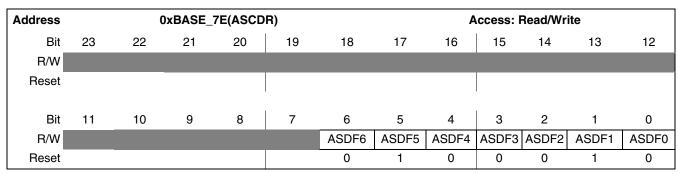

| 20.2.2  | Register Descriptions                                                             |         |

| 20.3    | Interrupts                                                                        |         |

|         |                                                                                   |         |

|         | Symphony DSP56720/DSP56721 Multi-Core Audio Processors Reference Manual, Rev. 1.1 |         |

| 20.4           | DMA Requests                                                                      |        |

|----------------|-----------------------------------------------------------------------------------|--------|

| 20.5           | Functional Description                                                            |        |

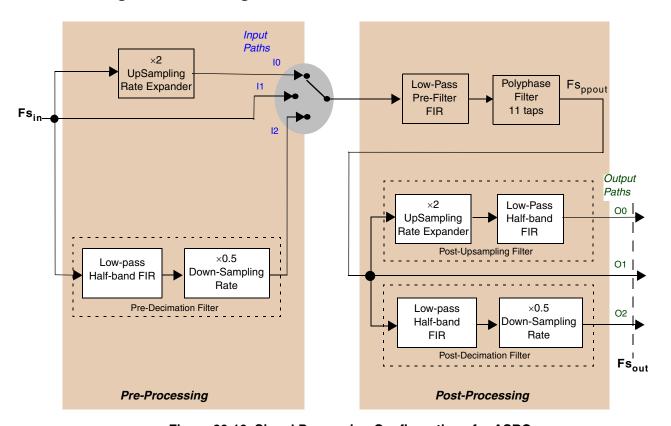

| 20.5.1         | Algorithm Description                                                             | 20-27  |

| Chap           | ter 21                                                                            |        |

| Chip           | Configuration Module                                                              |        |

| 21.1           | Introduction                                                                      | . 21-1 |

| 21.1.1         | Modes of Operation                                                                |        |

| 21.2           | Memory Map and Register Definition                                                |        |

| 21.2.1         | Memory Map                                                                        |        |

| 21.2.2         | Register Descriptions                                                             | . 21-3 |

| 21.3           | Programming Model                                                                 |        |

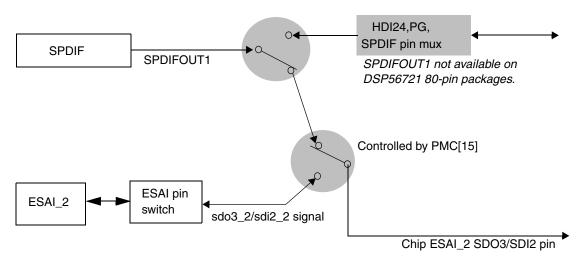

| 21.3.1         | ESAI/ESAI_1/ESAI_2/ESAI_3 Pin-Switching and Internal Connections                  |        |

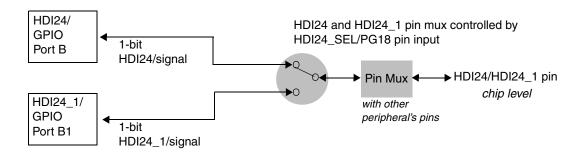

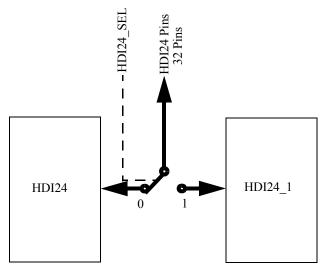

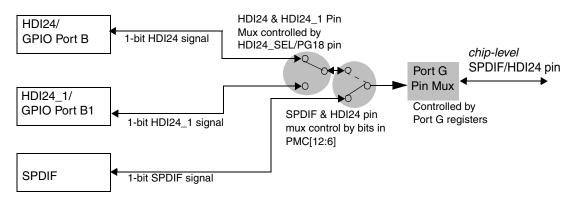

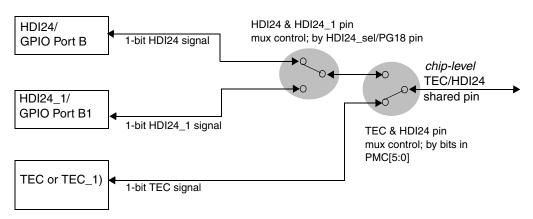

| 21.3.2         | SPDIF, TEC, HDI24, HDI24_1 Pin Mux                                                |        |

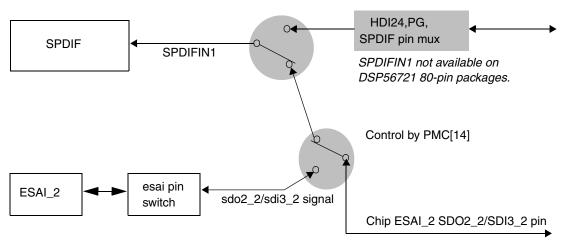

| 21.3.3         | ESAI_2 Data and SPDIF Data Pin Mux                                                |        |

| 21.3.4         | Soft Reset                                                                        |        |

| 21.3.5         | Reset                                                                             |        |

| 21.3.6         | ESAI Pin Switch and Internal Clock Connections                                    | 21-20  |

| Chan           | ter 22                                                                            |        |

|                | nal Memory Controller (EMC)                                                       |        |

|                | ·                                                                                 |        |

| 22.1           | Introduction                                                                      |        |

| 22.1.1         | Features                                                                          |        |

| 22.2           | External Signal Descriptions                                                      |        |

| 22.2.1<br>22.3 | Detailed Signal Descriptions                                                      |        |

| 22.3.1         | Memory Map                                                                        |        |

| 22.3.1         | Register Descriptions                                                             |        |

| 22.4           | Functional Description                                                            |        |

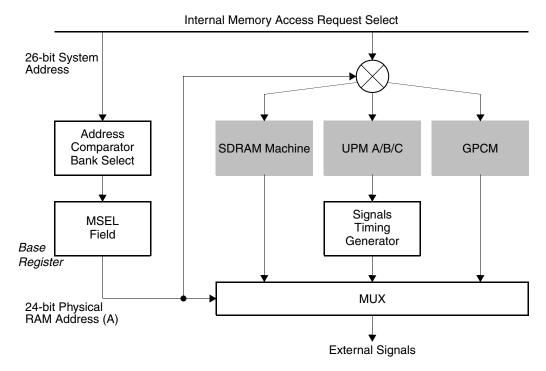

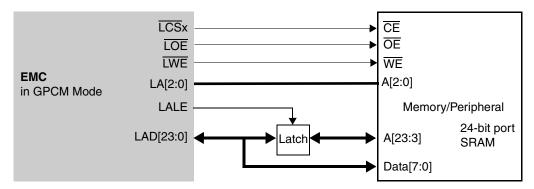

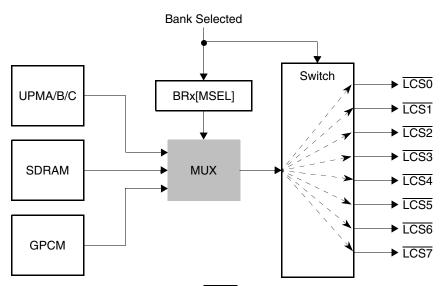

| 22.4.1         | Basic Architecture.                                                               |        |

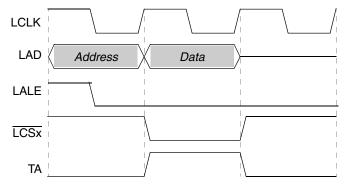

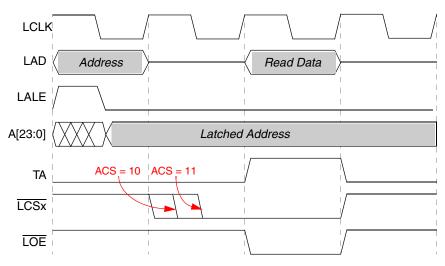

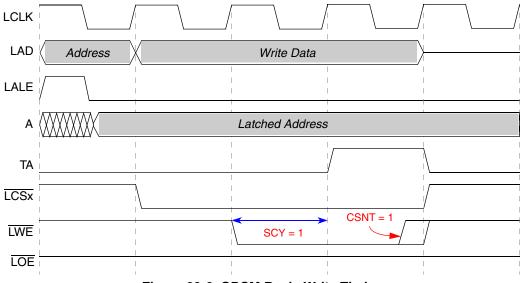

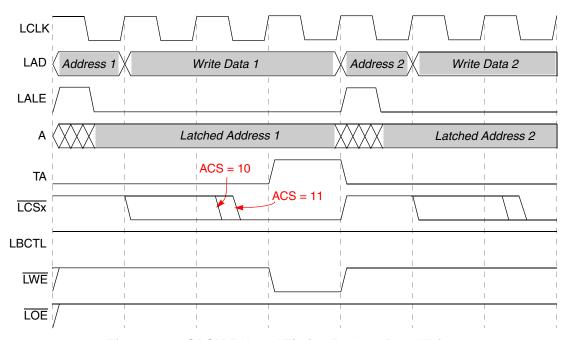

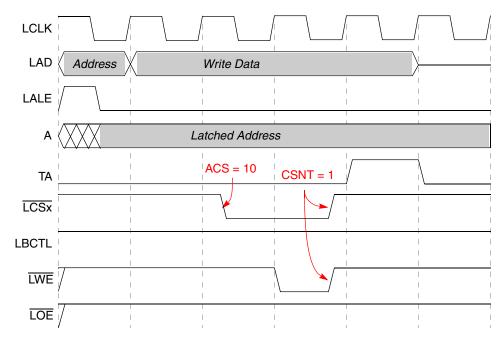

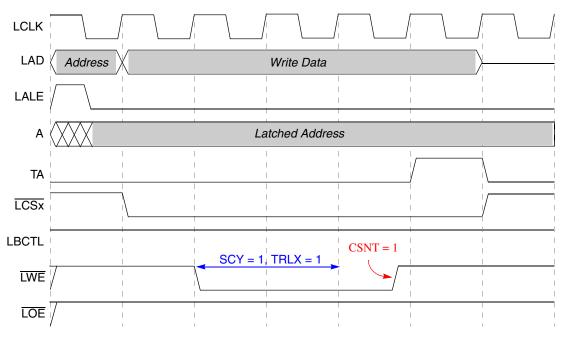

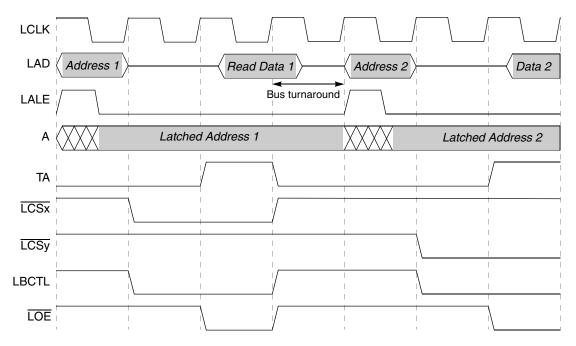

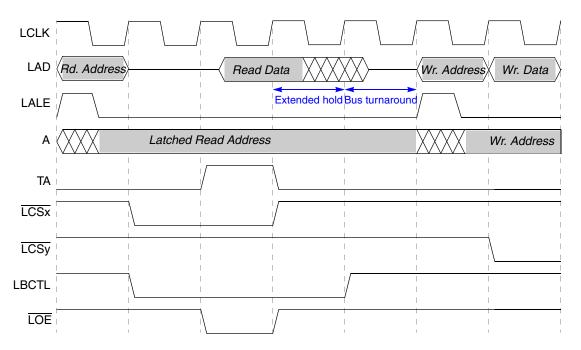

| 22.4.2         | General-Purpose Chip-Select Machine (GPCM)                                        |        |

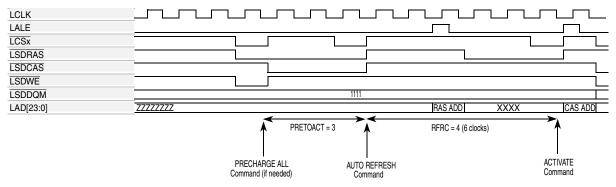

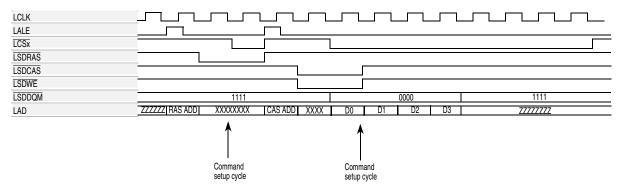

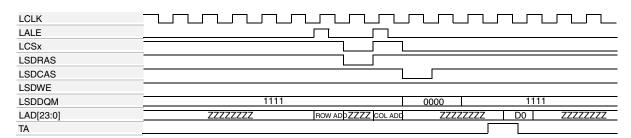

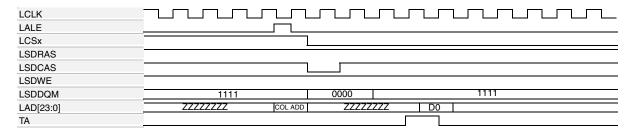

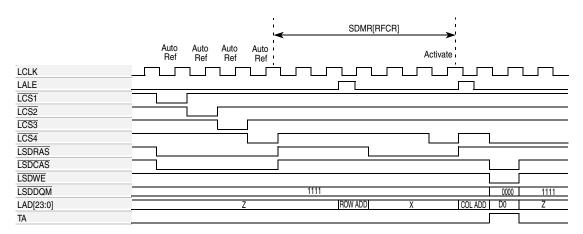

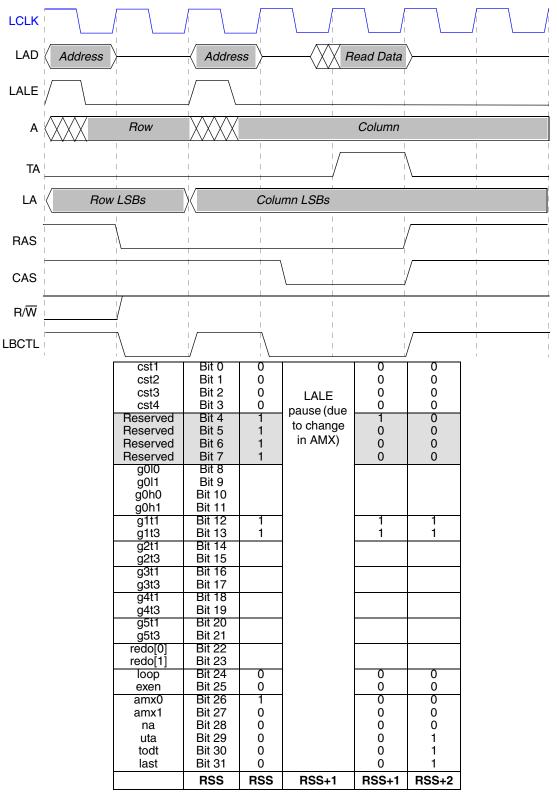

| 22.4.3         | SDRAM Machine                                                                     |        |

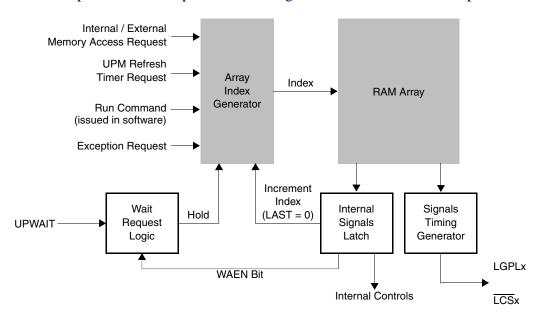

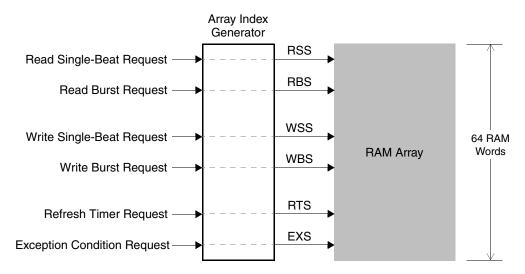

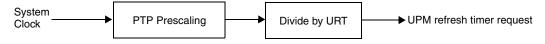

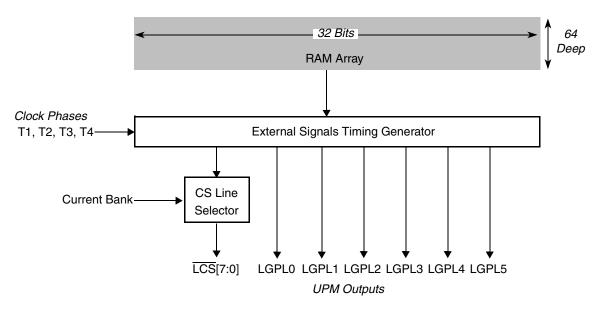

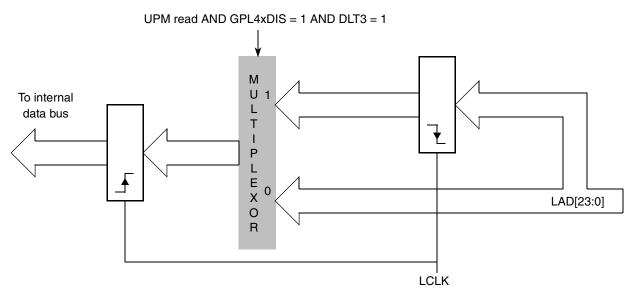

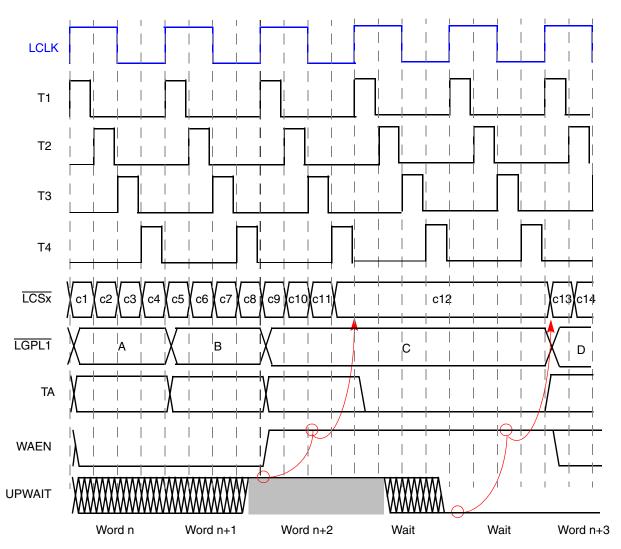

| 22.4.4         | User-Programmable Machines (UPMs)                                                 |        |

| 22.5           | Application Information                                                           |        |

| 22.5.1         | Interfacing to Peripherals                                                        | 22-87  |

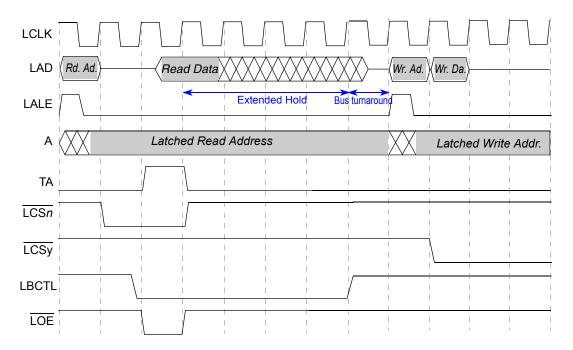

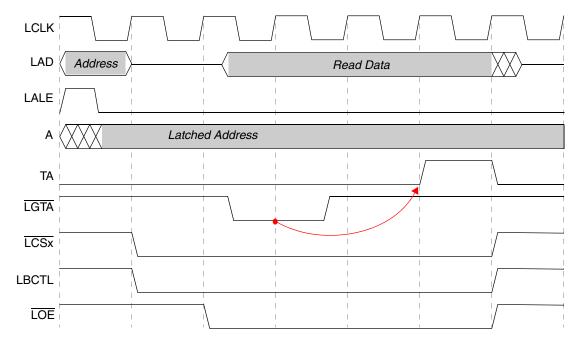

| 22.5.2         | Bus Turnaround                                                                    |        |

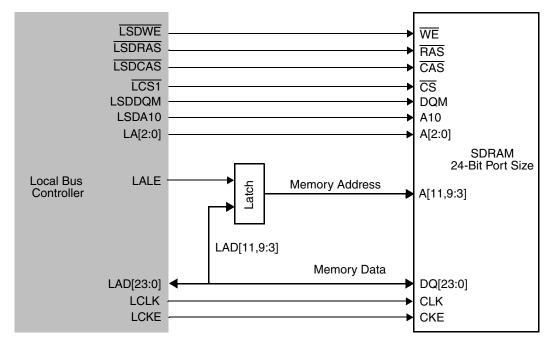

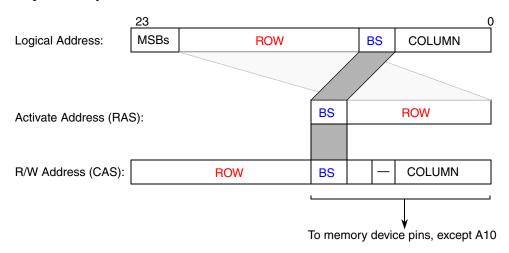

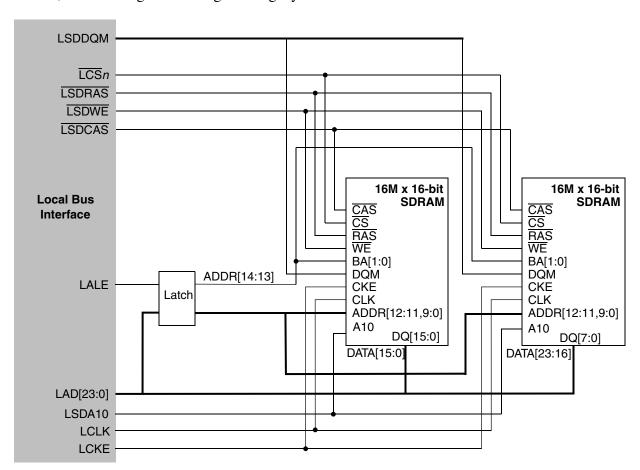

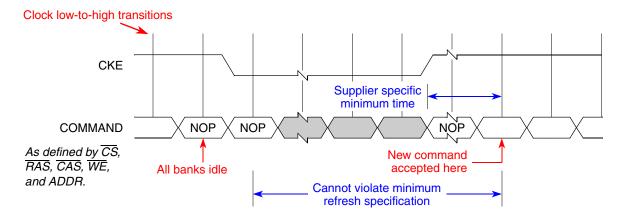

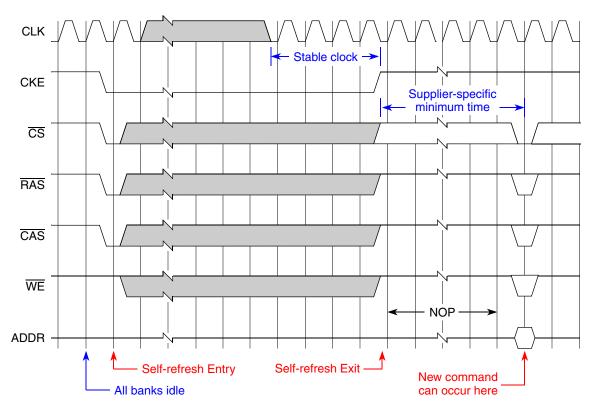

| 22.5.3         | Interfacing to SDRAM                                                              | 22-91  |

| <b>O</b> I     | 1 00                                                                              |        |

|                | ter 23<br>6 Controller                                                            |        |

| JIAC           |                                                                                   |        |

| 23.1           | Overview                                                                          | . 23-1 |

| 23.2           | Features                                                                          |        |

| 23.3           | External Signal Descriptions                                                      |        |

|                |                                                                                   |        |

|                | Symphony DSP56720/DSP56721 Multi-Core Audio Processors Reference Manual, Rev. 1.1 |        |

|                | -,p,                                                                              |        |

#### **About This Book**

The *Symphony DSP56720/DSP56721 Multi-Core Audio Processors Reference Manual* describes the features and operation of the Symphony<sup>TM</sup> DSP56720/DSP56721 Multi-Core Audio Processors, including, for example, their main features, architecture, function blocks, operation modes, pin signals, clocks, interrupts, DMA operations, and memory maps.

The DSP56720/DSP56721 Multi-Core Audio Processors are the first devices of the DSP5672x family of programmable CMOS DSPs, designed using dual DSP56300 24-bit cores. The DSP56720/DSP56721 are intended for automotive, consumer, and professional audio applications that require high performance for audio processing. Potential applications include A/V receivers, HD-DVD and Blu-Ray players, car audio/amplifiers, and professional audio equipment.

# **Revision History**

The following table summarizes revisions to this document.

Revision

1 • Initial release

1.1 Changed the following registers from low to high:

• TEIR

• TEDR

• TESR

• SRT

• URT

• MRTPR

**Table 1. Revision History**

#### **Audience**

The Symphony DSP56720/DSP56721 Multi-Core Audio Processors Reference Manual provides to the design engineer the necessary data to successfully integrate the processors into a wide variety of applications.

The intended audience for this document includes system architects, system modeling teams, IC designers, software architects/designers, and the platform integration and testing teams. The level of detail in this document is intended to provide the reader with sufficient information to validate the capabilities of the processes in the targeted applications.

# Organization

This reference manual is organized into chapters that describe the operation and programming of the processors. It includes brief summaries of the major components, as well as listings of the memory maps for the processors and shared memories.

This manual also contains chapters that describe the operations and configuration of the peripherals, including the modules that provide bootmodes, memory, and connectivity.

# Suggested Reading

The *DSP56300 Family Manual* (DSP56300FM) document is suggested for a complete description of the Symphony DSP56720/DSP56721 Multi-Core Audio Processors, and is necessary to design with the devices. This document is helpful when used in conjunction with this reference manual.

#### Conventions

This reference manual uses the following conventions:

- OVERBAR is used to indicate a signal that is active when pulled low: for example, RESET.

- Logic level one is a voltage that corresponds to Boolean true (1) state.

- Logic level zero is a voltage that corresponds to Boolean false (0) state.

- To set a bit or bits means to establish logic level one.

- To *clear* a bit or bits means to establish logic level zero.

- A *signal* is an electronic construct whose state conveys or changes in state convey information.

- A pin is an external physical connection. The same pin can be used to connect a number of signals.

- Asserted means that a discrete signal is in active logic state.

- Active low signals change from logic level one to logic level zero.

- Active high signals change from logic level zero to logic level one.

- Negated means that an asserted discrete signal changes logic state.

- Active low signals change from logic level zero to logic level one.

- Active high signals change from logic level one to logic level zero.

- LSB means *least significant bit* or *bits*, and MSB means *most significant bit* or *bits*. References to low and high bytes or words are spelled out.

- Numbers preceded by a percent sign (%) are binary. Numbers preceded by a 0x are hexadecimal.

- Courier monospaced type indicate commands, command parameters, code examples, expressions, data types, and directives.

- Italic type indicates replaceable command parameters.

# Chapter 1 Introduction

#### 1.1 Overview

The Symphony<sup>TM</sup> DSP56720 and DSP56721 Multi-Core Audio Processors are the first devices of the DSP5672x family of programmable CMOS DSPs, designed using multiple DSP56300 24-bit cores. The DSP56720 and DSP56721 are intended for automotive, consumer, and professional audio applications that require high performance for audio processing. These processors also support professional audio applications, including audio recording, signal processing and digital audio synthesis. Potential applications include A/V receivers, HD-DVD and Blu-Ray players, car audio/amplifiers, and professional audio equipment. Additional device features include support for digital audio compression/decompression, sound field processing, acoustic equalization and other digital audio algorithms. With two DSP56300 cores, the DSP56720 (or DSP56721) device can replace two DSP devices in designs, providing high MIPs and lower cost.

#### DSP56720/DSP56721 features include:

- Two DSP56300 enhanced cores: 400 MIPs (200 MIPs/core) with a 200 MHz clock; each core includes:

- Highly parallel instruction set

- Hardware debugging support (JTAG TAP, OnCE<sup>TM</sup> module)

- Eight-channel DMA controller

- Wait and Stop low-power standby modes

- Configurable and flexible arbitration method for the shared peripherals and shared memory blocks

- Powerful audio data communication ability:

- Four Enhanced Serial Audio Interface (ESAI) modules to transmit and receive audio data. Two ESAI modules are provided for each core. For each ESAI, up to 4 receivers and up to 6 transmitters, master or slave. Protocols include I<sup>2</sup>S, Left-Justified, Right-Justified, Sony, AC97, network and other programmable protocols.

- One S/PDIF module is shared by the two cores to transmit and receive audio data in IEC958 format.

- Powerful host communication ports:

- Two Serial Host Interface (SHI, SHI\_1) modules, with one module for each core. SHIs support SPI and I<sup>2</sup>C protocols, multi-master capability in I<sup>2</sup>C mode, 10-word receive FIFO, and support for 8, 16 and 24-bit words.

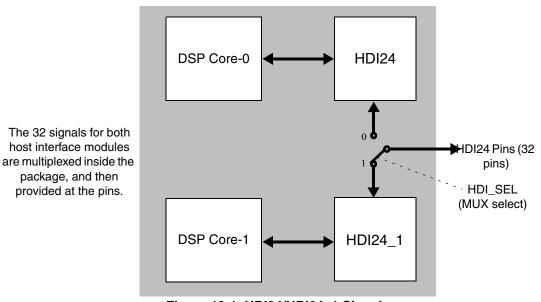

- Two parallel Host Interface (HDI24, HDI24\_1) modules with DMA support, with one module for each core, supporting 8-bit, 16-bit, or 24-bit host interface. The HDI24/HDI24\_1 is a word or byte-wide, full-duplex, double-buffered parallel port that can connect directly to the data bus

Symphony DSP56720/DSP56721 Multi-Core Audio Processors Reference Manual, Rev. 1.1

#### Introduction

of a host processor. The HDI24 is only available on the DSP56721 (144-pin package) and is not available on the DSP56720 or the DSP56721 (80-pin package).

- Two triple-timer modules (TEC, TEC\_1), with one timer module for each core.

- Two watchdog timer modules (WDT, WDT\_1), with one watchdog timer module for each core, to prevent code runaway problems.

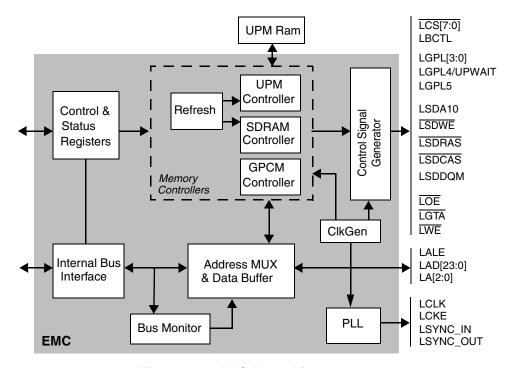

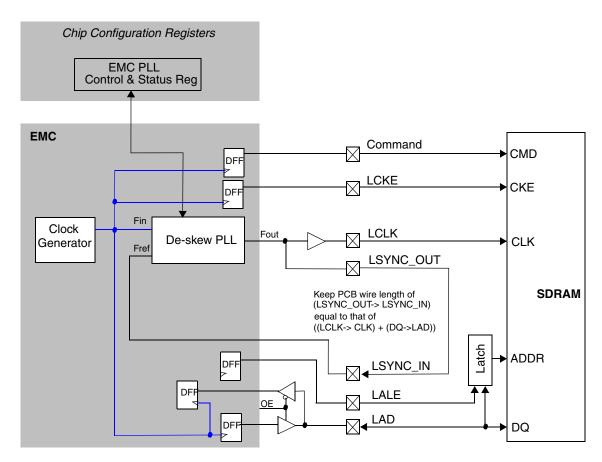

- An External Memory Controller (EMC) that can be accessed by both DSP cores, which supports SDRAM, SRAM, EPROM, flash EPROM, burstable RAM, regular DRAM devices, and extended data output DRAM devices. Note that the EMC is only available on DSP56720 devices, and is not available on DSP56721 devices. The EMC includes:

- High performance SDRAM machine

- A general-purpose chip-select machine (GPCM)

- Up to three user-programmable machines (UPMs)

- A seamless hardware Asynchronous Sampling Rate Converter (ASRC) that is accessible to both

cores, to support different sample rate audio data transmission reception. Three data sampling rate

convert pairs can be supported at the same time. Different pairs can be used by different cores at

the same time.

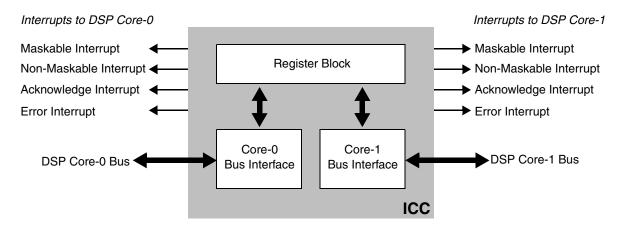

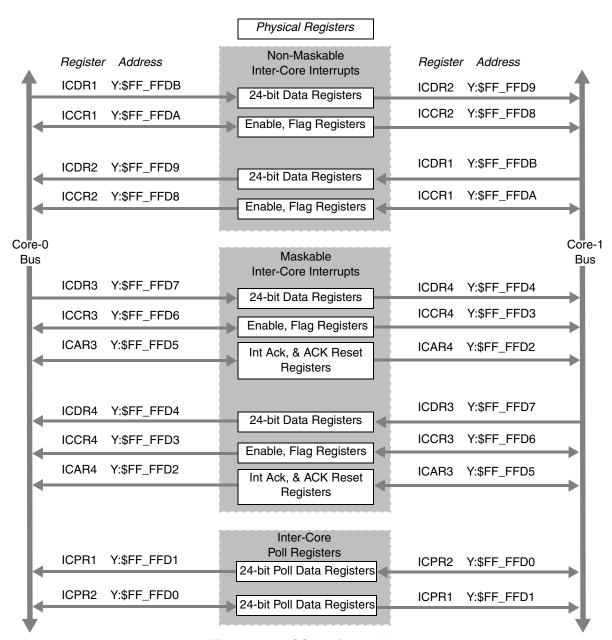

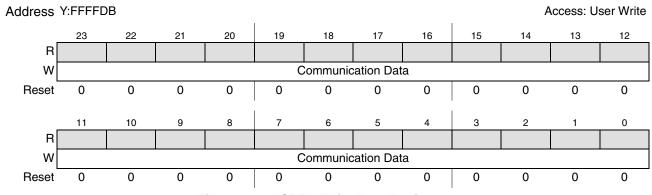

- Inter-Core Communication (ICC) module:

- 64K shared memory between the two DSP56300 cores

- Supports a flexible arbitration system which allows multiple methods of arbitration

- Non-maskable and maskable interrupts between the two cores

- Poll data registers for simple data transfers

- Includes as many as 79 GPIO pins, shared with other peripherals function pins; the actual number is different for different device packages.

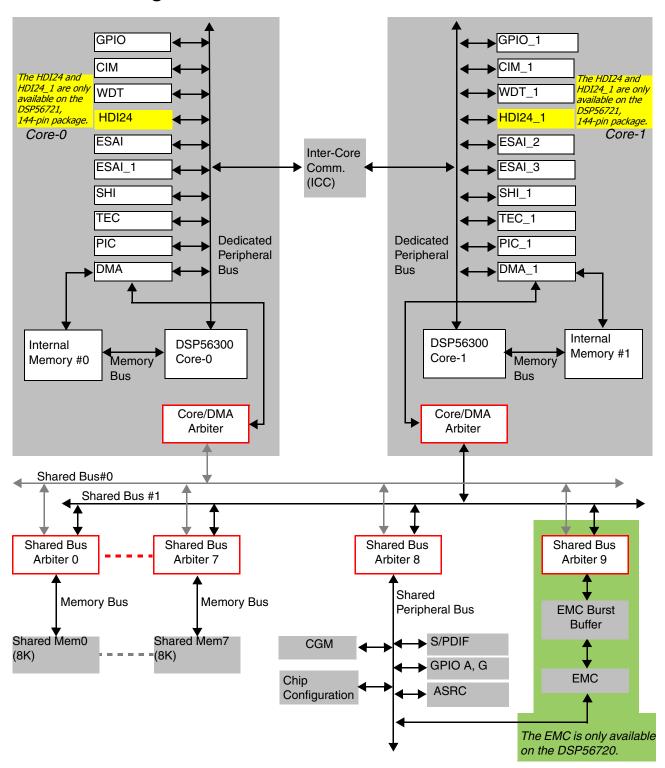

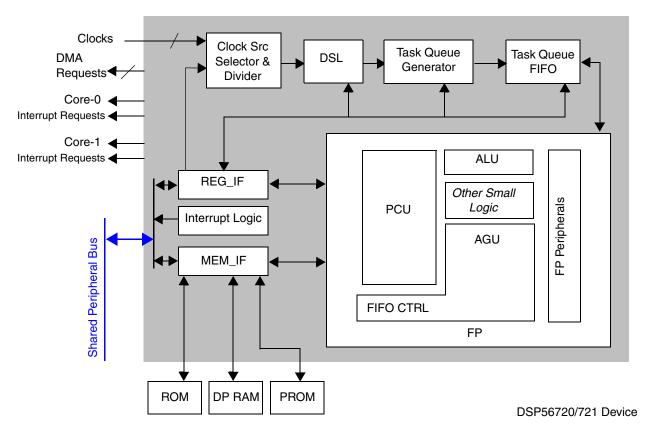

# 1.2 Block Diagram

Figure 1-1. DSP56720/DSP56721 Block Diagram

Introduction

#### 1.3 Benefits and Features

In addition to high MIPS, the DSP56720/DSP56721 provides powerful and flexible audio data communications and supports a wide variety of audio applications. This section provides a brief description of the DSP56720/DSP56721 processor features.

The DSP56720/DSP56721 has two DSP56300 DSP cores. The high throughput of the DSP56300 family of processors makes them well-suited for high-speed control, efficient signal processing, numeric processing, and audio applications. Benefits of using DSP56300 cores include:

- Speed: The DSP56300 family supports most high-performance DSP applications.

- *Precision:* The data paths are 24 bits wide, providing 144 dB of dynamic range. Intermediate results held in the 56-bit accumulators can range over 336 dB.

- *Parallelism:* Each on-chip execution unit, memory, and peripheral operates independently and in parallel with the other units through a sophisticated bus system. The Data ALU, AGU, and program controller operate in parallel so that the following operations can execute in a single instruction:

- An instruction pre-fetch

- A 24-bit  $\times$  24-bit multiplication

- A 54-bit addition

- Two data moves

- Two address-pointer updates using either linear or modulo arithmetic

- *Flexibility:* While many other DSPs require external communication devices to interface with peripheral circuits (such as A/D converters, D/A converters, or processors), the DSP56300 family provides on-chip serial and parallel interfaces that support various configurations of memory and peripheral modules. The peripherals are interfaced to the DSP56300 family core through a peripheral interface bus that provides a common interface to many different peripherals.

- Sophisticated Debugging: Freescale's On-Chip Emulation (OnCE) technology allows simple, inexpensive, and speed-independent access to the internal registers for debugging. With the OnCE module, you can easily determine the exact status of the registers and memory locations, plus identify which instructions were executed last.

- Phase Locked Loop (PLL)-Based Clocking: The PLL allows the chip to use almost any available external system clock for full-speed operation, while also supplying an output clock synchronized to a synthesized internal core clock. It improves the synchronous timing of the external memory port, eliminating the timing skew common on other processors.

- *Invisible Pipeline:* The seven-stage instruction pipeline is essentially invisible to the programmer, allowing straightforward program development in either assembly language or high-level languages such as C or C++.

- Similar Instruction Set: The instruction mnemonics are similar to those used for microcontroller units, making an easy transition from programming microprocessors to programming the device. New microcontroller instructions, addressing modes, and bit field instructions allow for significant decreases in program code size. The orthogonal syntax controls the parallel execution units. The hardware DO loop and the repeat (REP) instructions make writing straight-line code obsolete.

- Low Power: Designed in CMOS, the DSP56300 family consumes very little power. Two additional low-power modes, Stop and Wait, further reduce power requirements. Wait is a low-power mode

in which the DSP56300 core shuts down, but the peripherals and interrupt controller continue to operate, so that an interrupt can bring the chip out of Wait mode. In Stop mode, even more of circuitry is shut down for the lowest power consumption. Several different methods are available to bring the chip out of Stop mode: hardware RESET, IRQA, and DE.

# 1.4 Overview of Peripherals

#### 1.4.1 Direct Memory Access Controller (DMA, DMA\_1)

The DMA controller enables data transfers without any interactions with the DSP cores. During DMA accesses, it supports any combination of source and destination between internal memory, internal peripheral I/O, and external memory. DMA features include:

- Eight DMA channels supporting internal and external accesses

- One-, two-, and three-dimensional transfers (including circular buffering)

- End-of-block-transfer interrupts

- Triggering from interrupt lines and all peripherals

# 1.4.2 Program Interrupt Controller (PIC, PIC\_1)

The Program Interrupt Controller arbitrates among all interrupt requests (internal interrupts and the five external requests IRQA, IRQB, IRQC, IRQD, and NMI), and generates the appropriate interrupt vector address.

The Program Interrupt Controller supports:

- Both non-maskable and maskable interrupts

- Up to 18 DMA interrupts and 24 Peripheral interrupts

- Up to 9 non-maskable interrupts

# 1.4.3 Enhanced Serial Audio Interfaces (ESAI, ESAI\_1, ESAI\_2, ESAI\_3)

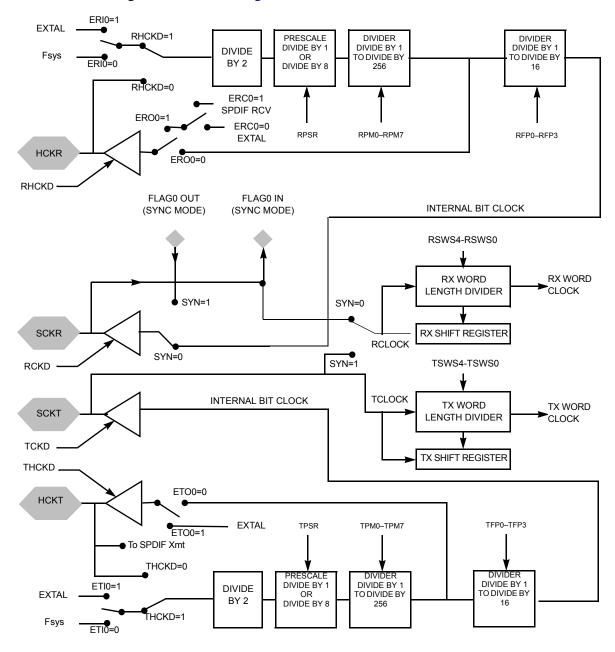

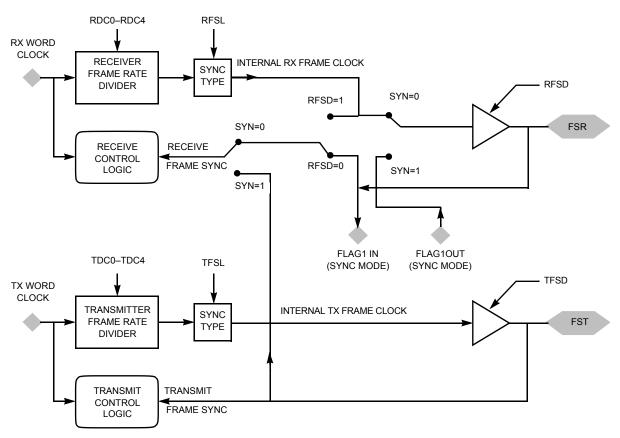

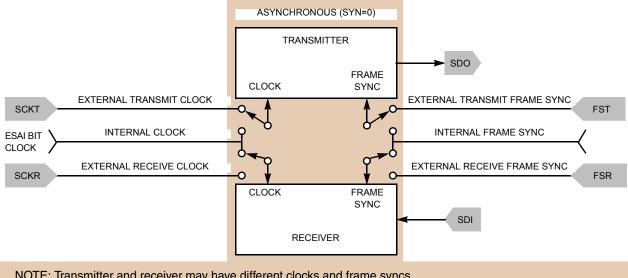

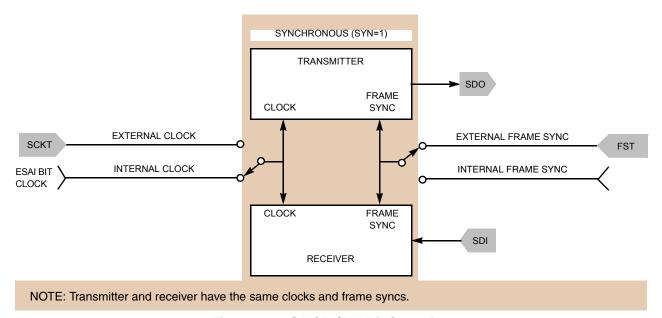

The enhanced serial audio interfaces provide full-duplex serial GPIO pins or serial communications with a variety of serial devices, including one or more industry-standard codecs, other DSPs, microprocessors and other peripherals that implement the serial peripheral interface (SPI) serial protocol. Each ESAI consists of independent transmitter and receiver sections, each with its own clock generator, and is a superset of the DSP56300 family ESSI peripherals and the DSP56000 family SAI peripherals.

# 1.4.4 Serial Host Interfaces (SHI, SHI\_1)

Each serial host interface provides a path for communications and program/coefficient data transfers between the DSP core and an external host processor. The SHI can interface directly to either of two well-known and widely used synchronous serial buses: the SPI bus and the Phillips inter-integrated-circuit control (I2C) bus. The SHI supports either the SPI or I2C bus protocol, as required, from a slave or a single-master device. To minimize DSP overhead, the SHI supports single-, double- and triple-byte data

#### Introduction

transfers. The SHI has a 10-word receive FIFO that permits receiving up to 30 bytes before generating a receive interrupt, reducing the overhead for data reception.

#### 1.4.5 Host Interfaces (HDI24, HDI24\_1)

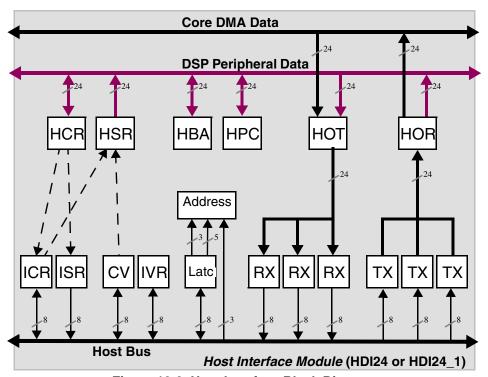

The host interfaces (HDI24/HDI24\_1) support a byte-wide, 16-bit wide, or 24-bit wide, full-duplex, double-buffered parallel port that can connect directly to the data bus of a host processor.

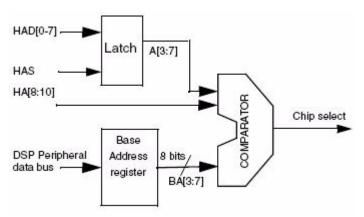

The host interface supports a variety of buses and provides connection with a number of industry-standard DSPs, microcontrollers, and microprocessors, without requiring any additional logic. The DSP core treats the host interface as a memory-mapped peripheral, occupying eight 24-bit words in data memory space.

The DSP can use the host data interface as a memory-mapped peripheral, using either standard polled or interrupt programming techniques. Separate double-buffered transmit and receive data registers allow the DSP and host processor to transfer data efficiently at high speeds. Memory mapping allows you to program DSP core communications with the host interface registers, using standard instructions and addressing modes.

#### NOTE

The HDI24/HDI24\_1 are only present on the DSP56721, 144-pin package.

### 1.4.6 Triple Timers (TEC, TEC\_1)

Each Triple Timer is composed of a common 21-bit prescaler and three independent and identical general purpose 24-bit timer event counters, with each timer having its own register set. Each timer can use internal or external clocking, and can also interrupt the DSP after a specified number of events (clocks). Each of the three timers can signal an external device after counting internal events. Each timer can also be used to trigger DMA transfers after a specified number of events (clocks) have occurred.

Each of the three timers connects to the external world through bidirectional pins (TIO0, TIO1 and TIO2). When a TIO pin is configured as input, the timer functions as an external event counter or can measure external pulse width/signal period. When a TIO pin is used as output, the timer is functioning as either a timer, a watchdog or a Pulse Width Modulator. When a TIO pin is not used by the timer, it can be used as a General Purpose Input/Output Pin. Not all timer pins are available on all packages.

# 1.4.7 Watch Dog Timers (WDT, WDT\_1)

Each watchdog timer is a 16-bit timer used to help software recover from runaway code. The timer is a free-running down-counter used to generate a reset on underflow. Software must periodically service the watchdog timer to restart the count down.

# 1.4.8 Core Integration Modules (CIM, CIM\_1)

Each DSP core has a Core Integration Module. Each core integration module includes a chip ID register, DMA stall monitor function, and OnCE global data bus (GDB) register.

## 1.4.9 Sony/Philips Digital Interface (S/PDIF)

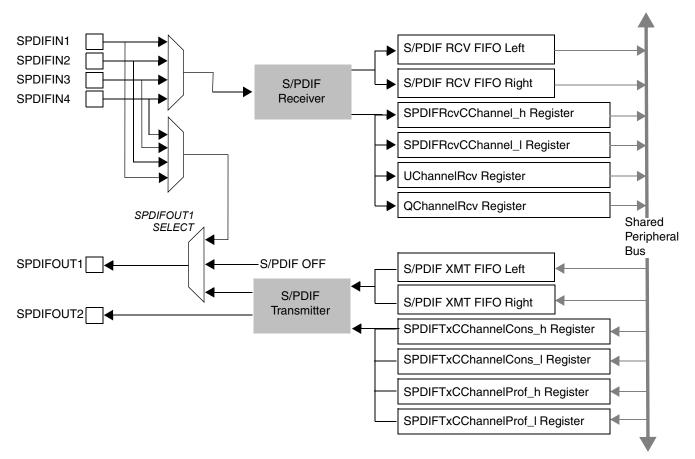

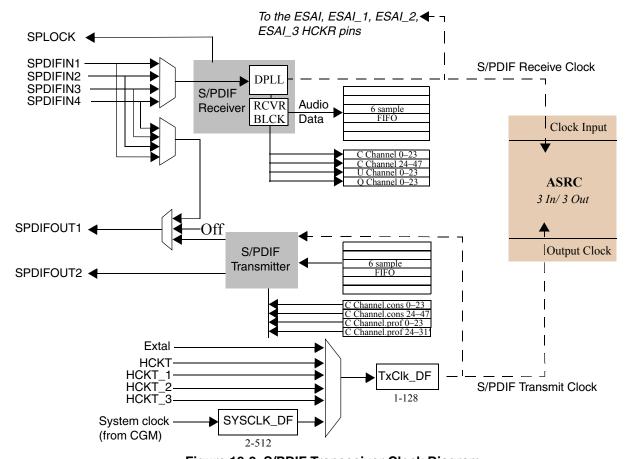

The Sony/Philips Digital Interface (S/PDIF) audio module is a transceiver that allows the DSP to receive and transmit digital audio via this module. The DSP provides a single S/PDIF receiver with four multiplexed inputs, and one S/PDIF transmitter with two outputs. The S/PDIF module can also transmit and receive the S/PDIF channel status (CS) and user (U) data. Not all S/PDIF pins are available on all packages.

Note that there is only one S/PDIF in each DSP56720/DSP56721 device, shared by the two DSP cores.

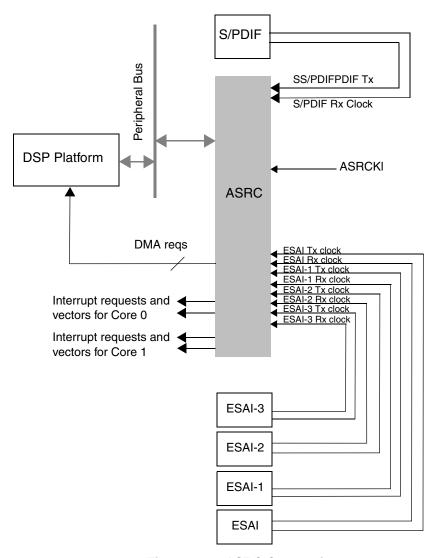

# 1.4.10 Asynchronous Sample Rate Converter (ASRC)

Incoming audio data to the DSP can be received from various sources at different sampling rates. Outgoing audio data from the DSP can have different sampling rates, and additionally, it can be associated with output clocks that are asynchronous to the input clocks. The Asynchronous Sample Rate Converter (ASRC) converts the sampling rate of a signal associated to an input clock into a signal associated to a different output clock.

The ASRC supports concurrent sample rate conversion of up to 10 channels of about 120 dB THD+N. The sample rate conversion of each channel is associated to a pair of incoming and outgoing sampling rates.

The ASRC supports up to three sampling rate pairs. Although there is only one ASRC in the DSP56720/DSP56721 device (shared by the two DSP cores), the three sample rate pairs can be used by both DSP cores at the same time. The ASRC is hard-coded and implemented as a co-processor, requiring minimal CPU or DSP controller intervention.

# 1.4.11 External Memory Controller (EMC)

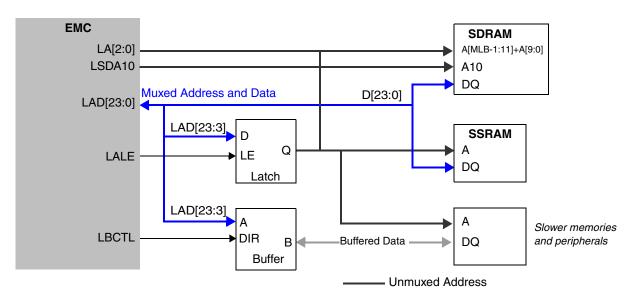

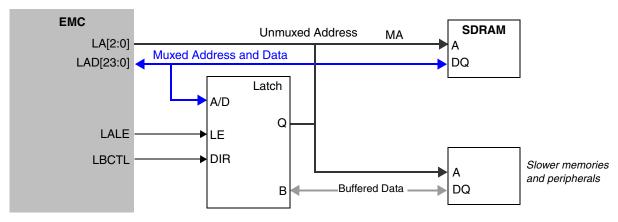

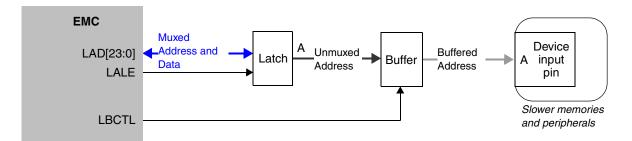

The EMC provides a seamless interface to many types of memory devices and peripherals over a shared address and data bus and dedicated control signals. The memory controller in the EMC controls a parameterized number of memory banks shared by a high performance SDRAM machine, a general-purpose chip-select machine (GPCM), and up to three user-programmable machines (UPMs).

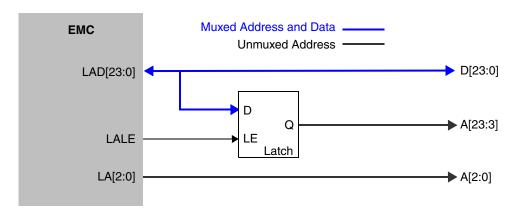

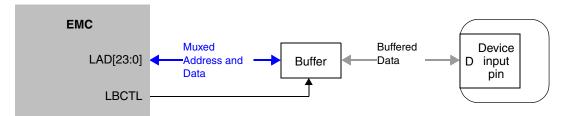

With external latching, it supports connections to synchronous DRAM (SDRAM), SRAM, EPROM, flash EPROM, burstable RAM, regular DRAM devices, extended data output DRAM devices, and other peripherals. Support signals for external address latch (LALE) allows multiplexing of address with data lines in devices with strict pin count limitations.

Note that there is one EMC in each DSP56720 device, shared by the two DSP cores. Both cores can access external memory using the EMC. (DSP56721 devices do not have an EMC.)

Introduction

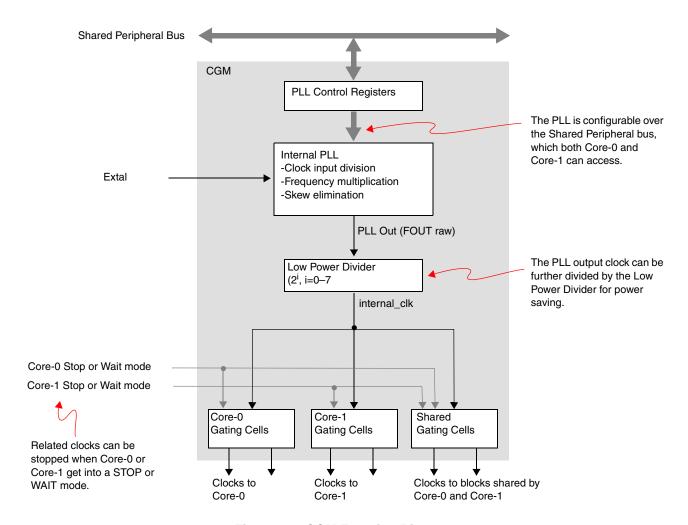

#### 1.4.12 Clock Generation Module (CGM)

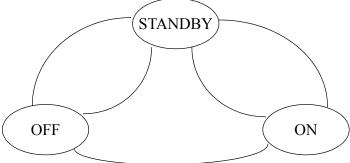

The Clock Generation Module generates all clocks in the DSP56720/DSP56721 device; the output is a series of gated clocks. The CGM uses a low jitter phase-locked loop (PLL). The PLL has a wide range of frequency multiplications (1 to 256), predivider factors (1 to 32) and output divider (1 to 8). The CGM also has a power saving clock divider ( $2^i$ : i = 0 to 7).

In functional mode, the PLL control register (PCTL) sits on the Shared Peripheral bus; both DSP cores can read and write these registers to change the chip's working frequency. Additionally, each core can independently enter stop or wait mode to save power. The shared peripherals enter power-saving mode only when both DSP cores enter the stop mode.

#### 1.4.13 Shared Memory

The shared memory is a shared memory space accessible by either DSP Core-0 or DSP Core-1. The DSP56720/DSP56721 shared memory has eight 8K x 24 words memory blocks for a total of 64K shared words and is located starting from \$030000. It can be accessed as X or Y memory (with zero wait states) or as P memory (with 1 wait state).

The 8K x 24 words blocks are single port SRAMs; the Shared Bus Arbiter perform arbitration when the two DSP cores try to access the same 8K x 24 SRAM block at the same time. No bus contentions occur when the two DSP cores access different 8K x 24 SRAM blocks simultaneously.

#### 1.4.14 Inter-Core Communication (ICC)

Using the inter-core communication module, each DSP core can issue a maskable interrupt or non-maskable interrupt to the other core, and each core has its own write data register (which passes data to the other core when the interrupt is generated). There are also poll data registers for inter-core data exchange in the ICC. The ICC module interfaces with both cores' dedicated peripheral buses.

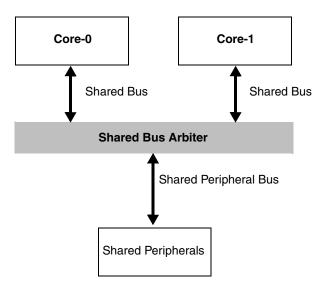

#### 1.4.15 Shared Bus Arbiters

The Shared Bus Arbiter provides arbitration between the two DSP cores for the shared peripherals, shared memory and shared external memory interface (if available). It is a configurable arbiter, so users can choose the arbitration method via the appropriate chip configuration registers. The Shared Bus Arbiter supports using one of three arbitration schemes:

- Always round-robin method

- DSP Core-0 always has high priority

- DSP Core-1 always has high priority

## 1.4.16 Chip Configuration Module

The Chip Configuration module contains several registers which establish the mode of operation for various internal blocks, modules, and some of the peripherals. These registers include:

- Control bits of Shared Bus Arbiters

- EMC Burst Mode control bits

- Pin mux/switch control of ESAI, S/PDIF, S/PDIF Rx Clock output mux on ESAI HCKR pins

- Shared peripherals Soft Reset triggering and auto-release

- EMC PLL control and status

#### 1.4.17 JTAG Controller

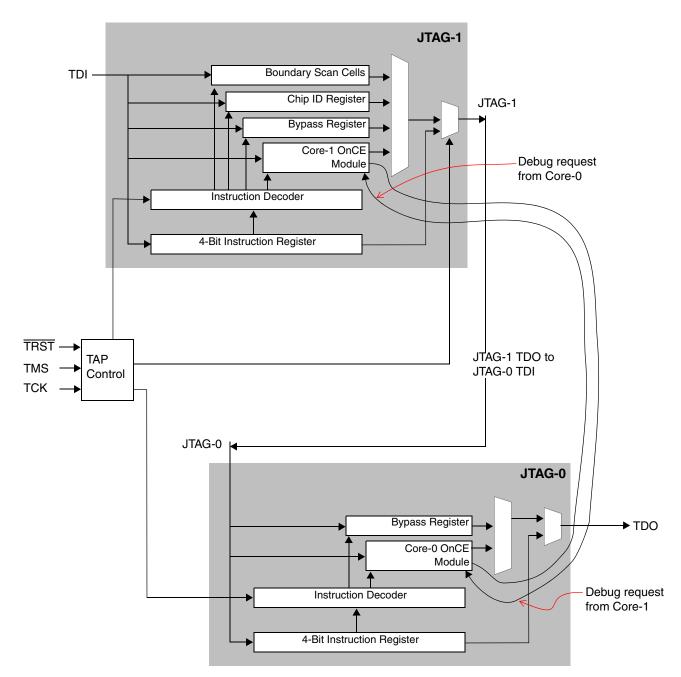

In the DSP56720/DSP56721 devices, two separate DSP cores are supported, each with their own OnCE and JTAG TAP controller. The two JTAG TAPs are daisy-chained, and appear to be two separate single core devices to the outside world.

Introduction

Symphony DSP56720/DSP56721 Multi-Core Audio Processors Reference Manual, Rev. 1.1

# **Chapter 2 Signal Descriptions**

# 2.1 Signal Groupings

Each product (DSP56720, DSP56721) is available in a variety of packages, which affects whether some modules use dedicated or shared external pins. See Table 2-1.

Table 2-1. DSP56720/DSP56721 Shared/Dedicated Pins

|                                              |         | DSP56720                                                     | DSP56721                                                           |                            |  |  |

|----------------------------------------------|---------|--------------------------------------------------------------|--------------------------------------------------------------------|----------------------------|--|--|

| Function                                     | Module  | 144-pin                                                      | 80-pin                                                             | 144-pin                    |  |  |

| Timers                                       | TEC     | None                                                         | None None                                                          |                            |  |  |

|                                              | TEC_1   | None                                                         | None                                                               | TIO0 Only                  |  |  |

| Enhanced Serial Audio                        | ESAI    | No SDO0, SDO1                                                | No SDO0, SDO1                                                      | All                        |  |  |

| Interface                                    | ESAI_1  | No SDO0, SDO1, FST, FSR, SCKT, SCKR, HCKT, HCKR <sup>1</sup> | No SDO0, SDO1, FST,<br>FSR, SCKT, SCKR, HCKT,<br>HCKR <sup>1</sup> | No HCKR, HCKT <sup>2</sup> |  |  |

|                                              | ESAI_2  | No SDO0, SDO1, FST, FSR, SCKT, SCKR, HCKT, HCKR <sup>3</sup> | No SDO0, SDO1, FST,<br>FSR, SCKT, SCKR, HCKT,<br>HCKR <sup>3</sup> | No HCKR, HCKT <sup>4</sup> |  |  |

|                                              | ESAI_3  | No SDO0, SDO1                                                | No SDO0, SDO1, HCKR                                                | All                        |  |  |

| Serial Host Interface                        | SHI     | All                                                          | All                                                                | All                        |  |  |

|                                              | SHI_1   | Only SS, others muxed with SHI                               | Only SS; others muxed with SHI                                     | All                        |  |  |

| Watchdog Timer                               | WDT     | All                                                          | All                                                                | All                        |  |  |

|                                              | WDT_1   | Muxed with WDT                                               | Muxed with WDT                                                     | Muxed with WDT             |  |  |

| Host Interface                               | HDI24   | N/A                                                          | N/A                                                                | All <sup>5</sup>           |  |  |

|                                              | HDI24_1 | N/A                                                          | N/A                                                                | Muxed with HDI24           |  |  |

| General Purpose I/O                          | GPIO    | Only PG1, PG2                                                | None                                                               | Only PG1, PG2, PG18        |  |  |

| Sony/Philips Digital S/PDIF Interface Format |         | Only SPDIFIN and SPDIFOUT1                                   | None;muxed with ESAI_2's SDO2, SDO3                                | All                        |  |  |

| External Memory<br>Controller                |         |                                                              |                                                                    |                            |  |  |

<sup>1</sup> Clock and Frame Sync signals can be shared with ESAI.

<sup>&</sup>lt;sup>2</sup> Clock signals can be shared with ESAI.

<sup>&</sup>lt;sup>3</sup> Clock and Frame Sync signals can be shared with ESAI\_3.

#### **Signal Descriptions**

- <sup>4</sup> Clock signals can be shared with ESAI\_3.

- <sup>5</sup> Lack of PG19, PG20, PG21 and TIO1, TIO2, TIO1\_1, TIO2\_1 prevent HDI24 from interfacing to a 24-bit host interface. Can only support 8-bit or 16-bit host interface.

The input and output signals of the DSP56720/DSP56721 are organized into functional groups, as listed in Table 2-2. The DSP56720/DSP56721 devices are operated from a 1.0 V core voltage and 3.3 V power IO voltage supply. However, all of the device functional inputs can tolerate 5.0 V.

Table 2-2. DSP56720/DSP56721 Signal Groups

|                            |                                                     |                      | Number of Signals |        |         |                        |

|----------------------------|-----------------------------------------------------|----------------------|-------------------|--------|---------|------------------------|

| Signal Group               | Signal                                              |                      | DSP56720          | DSP    | 56721   | Detailed Description   |

|                            |                                                     |                      | 144-Pin           | 80-Pin | 144-pin | 1                      |

| Power, Ground, Scan,       | Power (V <sub>DD</sub> )                            |                      | 21                | 13     | 20      | Table 2-3              |

| Clock, Interrupts          | Ground (GND)                                        |                      | 21                | 18     | 26      | Table 2-4              |

|                            | Scan Pins                                           |                      | 1                 | 1      | 1       | Table 2-5              |

|                            | Reset Pin                                           |                      | 1                 | 1      | 1       | Table 2-7              |

|                            | Clock and PLL                                       | Port G <sup>8</sup>  | 4                 | 4      | 4       | Table 2-6              |

|                            | Shared External<br>Interrupt Pins / Mode<br>Control | Port G <sup>8</sup>  | 5                 | 5      | 5       | Table 2-8<br>Table 2-9 |

| DSP Core-0 Peripheral Pins | SHI                                                 | Port H <sup>1</sup>  | 5                 | 5      | 5       | Table 2-11             |

|                            | HDI24                                               | Port G <sup>8</sup>  | 0                 | 0      | 16      | Table 2-20             |

|                            | ESAI                                                | Port C <sup>2</sup>  | 10                | 10     | 12      | Table 2-13             |

|                            | ESAI_1                                              | Port E <sup>3</sup>  | 4                 | 4      | 10      | Table 2-14             |

|                            | TEC                                                 | _                    | 0                 | 0      | 1       | Table 2-18             |

|                            | WDT                                                 | No GPIO<br>Function  | 1                 | 1      | 1       | Table 2-17             |

| DSP Core-1 Peripheral Pins | SHI_1                                               | Port H1 <sup>4</sup> | 1                 | 1      | 5       | Table 2-12             |

|                            | HDI24_1                                             | Port G <sup>8</sup>  | 0                 | 0      | 0       | Table 2-20             |

|                            | ESAI_2                                              | Port C1 <sup>5</sup> | 4                 | 4      | 10      | Table 2-15             |

|                            | ESAI_3                                              | Port E1 <sup>6</sup> | 10                | 9      | 12      | Table 2-16             |

|                            | TEC_1                                               | _                    | 0                 | 0      | 1       | Table 2-19             |

|                            | WDT_1                                               | No GPIO<br>Function  | 0                 | 0      | 0       | _                      |

#### Table 2-2. DSP56720/DSP56721 Signal Groups (continued)

|                            |                                     |                     | Number of Signals |        |         |                         |

|----------------------------|-------------------------------------|---------------------|-------------------|--------|---------|-------------------------|

| Signal Group               | Signal                              |                     | DSP56720          | DSP    | 56721   | Detailed<br>Description |

|                            |                                     |                     | 144-Pin 80-Pin    | 80-Pin | 144-pin |                         |

| Pins of Shared Peripherals | SPDIF                               | Port G <sup>8</sup> | 2                 | 0      | 7       | Table 2-22              |

|                            | EMC <sup>9</sup>                    | Port A <sup>7</sup> | 48                | 0      | 0       | Table 2-21              |

|                            | GPIO PORT G and<br>Mode Pins        | Port G <sup>8</sup> | 2                 | 0      | 3       | Table 2-23              |

|                            | JTAG/OnCE Por<br>for the two DSP Co |                     | 4                 | 4      | 4       | Table 2-24              |

Note:

- 1. Port H signals are the GPIO port signals that are multiplexed with the SHI HREQ signal.

- 2. Port C signals are the GPIO port signals that are multiplexed with the ESAI signals.

- 3. Port E signals are the GPIO port signals that are multiplexed with the ESAI\_1 signals.

- 4. Port H1 signals are the GPIO port signals that are multiplexed with the SHI\_1 HREQ\_1 signals.

- 5. Port C1 signals are the GPIO port signals that are multiplexed with the ESAI\_2 signals.

- 6. Port E1 signals are the GPIO port signals that are multiplexed with the ESAI\_3 signals.

- 7. Port A signals are the GPIO port signals that are multiplexed with the EMC.

- 8. Port G signals are the GPIO port signals that are multiplexed with S/PDIF, shared external maskable interrupts, PLL lock output signals, and HDI24/HDI24\_1 shared pins.

- 9. DSP56720 products have an EMC; DSP56721 products do not have an EMC.

#### **Signal Descriptions**

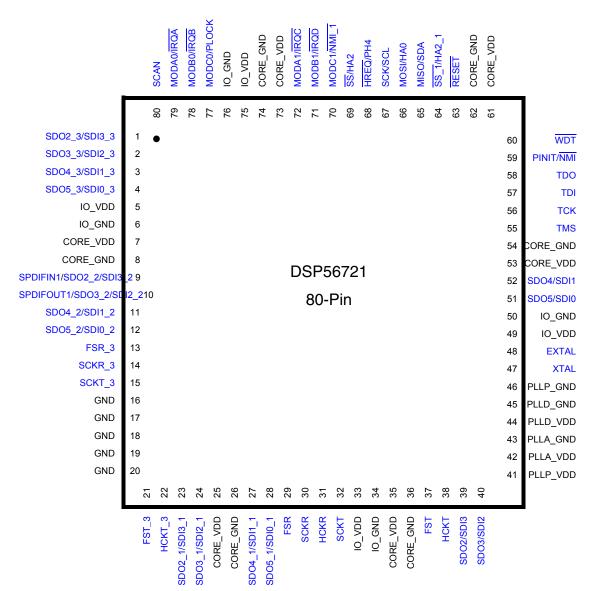

Figure 2-1. DSP56721 80-Pin Package Pin-Out

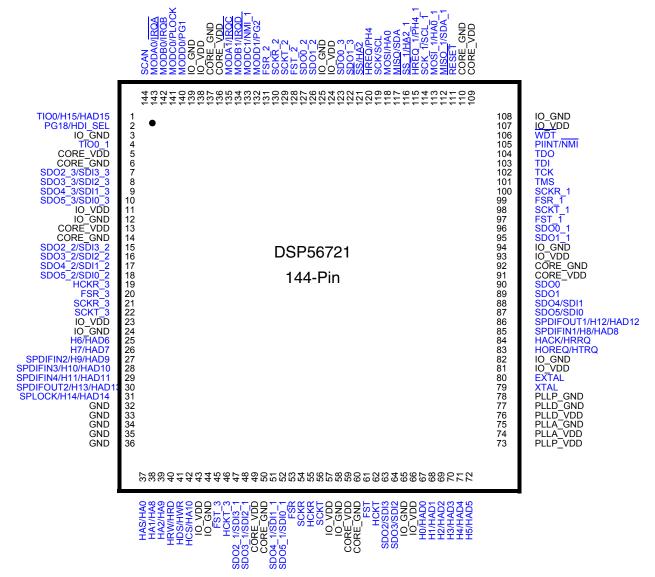

Figure 2-2. DSP56721 144-Pin Package Pin-Out

#### **Signal Descriptions**

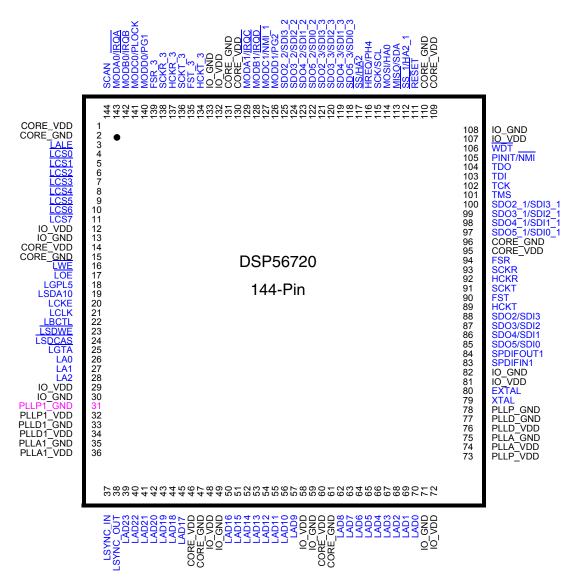

Figure 2-3. DSP56720 144-Pin Package Pin-Out

Symphony DSP56720/DSP56721 Multi-Core Audio Processors Reference Manual, Rev. 1.1 6 Freescale Semiconductor

# 2.2 Signals in Each Functional Group

#### 2.2.1 **Power**

**Table 2-3. Power Pins**

| Power Name                                     | Description                                                                                                                                                                                                                                                                                                                                           |

|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLLA_VDD<br>PLLP_VDD<br>PLLA1_VDD<br>PLLP1_VDD | PLL Power The voltage (3.3 V) should be well-regulated and the input should be provided with an extremely low impedance path to the 3.3 VDD power rail. The user must provide adequate external decoupling capacitors.                                                                                                                                |

| PLLD_VDD<br>PLLD1_VDD                          | PLL Power The voltage (1.0 V) should be well-regulated and the input should be provided with an extremely low impedance path to the 1.0 VDD power rail. The user must provide adequate external decoupling capacitors.                                                                                                                                |

| CORE_VDD                                       | Core Power  The voltage (1.0 V) should be well-regulated and the input should be provided with an extremely low impedance path to the 1.0 VDD power rail. The user must provide adequate decoupling capacitors.                                                                                                                                       |

| IO_VDD                                         | I/O Power The voltage (3.3 V) should be well-regulated and the input should be provided with an extremely low impedance path to the 3.3 V <sub>DD</sub> power rail. This is an isolated power for the SHI, SHI_1, ESAI, ESAI_1, ESAI_2, ESAI_3, Timer I/O, HDI24 and other IO signals. The user must provide adequate external decoupling capacitors. |

## **2.2.2** Ground

**Table 2-4. Ground Pins**

| <b>Ground Name</b>                             | Description                                                                                                                                                                                                                                 |

|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLLA_GND<br>PLLP_GND<br>PLLA1_GND<br>PLLP1_GND | PLL Ground The PLL ground should be provided with an extremely low-impedance path to ground. The user must provide adequate external decoupling capacitors.                                                                                 |

| PLLD_GND<br>PLLD1_GND                          | PLL Ground The PLL ground should be provided with an extremely low-impedance path to ground. The user must provide adequate external decoupling capacitors.                                                                                 |

| CORE_GND                                       | Core Ground The Core ground should be provided with an extremely low-impedance path to ground. This connection must be tied externally to all other chip ground connections. The user must provide adequate external decoupling capacitors. |

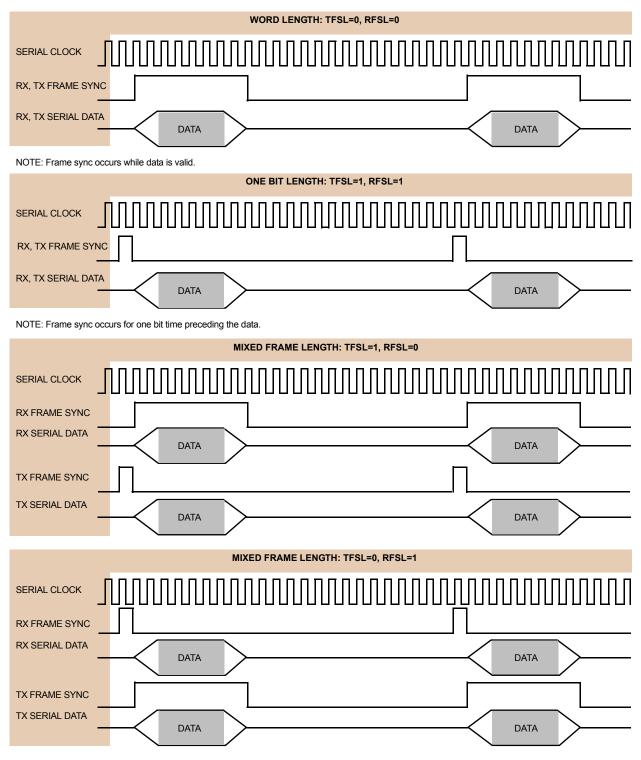

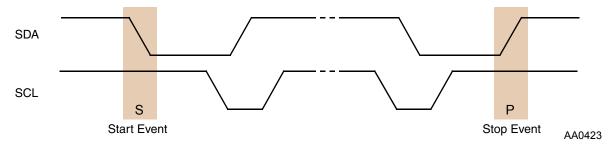

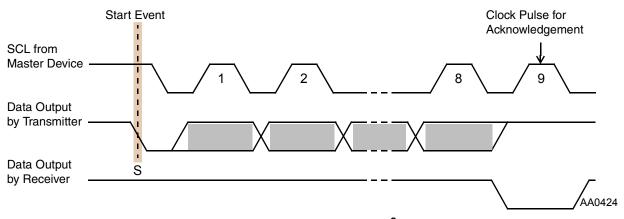

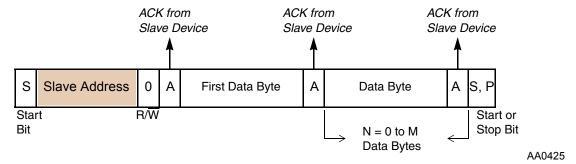

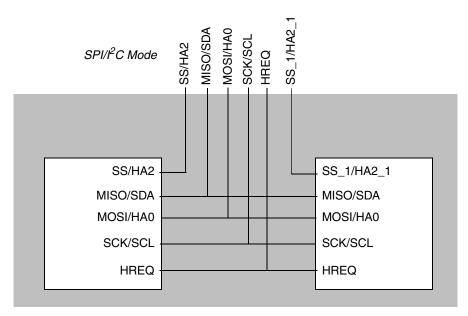

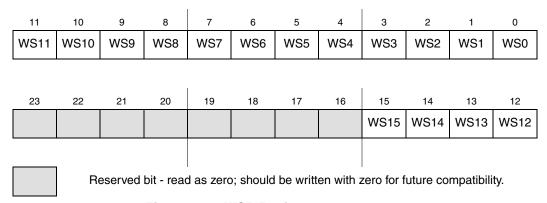

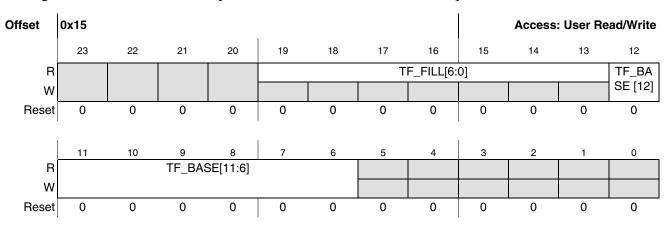

| IO_GND                                         | I/O Ground IO_GND is an isolated ground for the SHIs, ESAIs, HDI24s, Timer I/O and LIBU IO. This connection must be tied externally to all other chip ground connections. The user must provide adequate external decoupling capacitors.    |