## MC9S08PA60 Reference Manual

Supports: MC9S08PA60 and MC9S08PA32

Document Number: MC9S08PA60RM

Rev. 3, 04/2020

#### **Contents**

| Sed | ction n | umber Title                                                              | Page |

|-----|---------|--------------------------------------------------------------------------|------|

|     |         | Chapter 1 Device Overview                                                |      |

| 1.1 | Introdu | ction                                                                    | 33   |

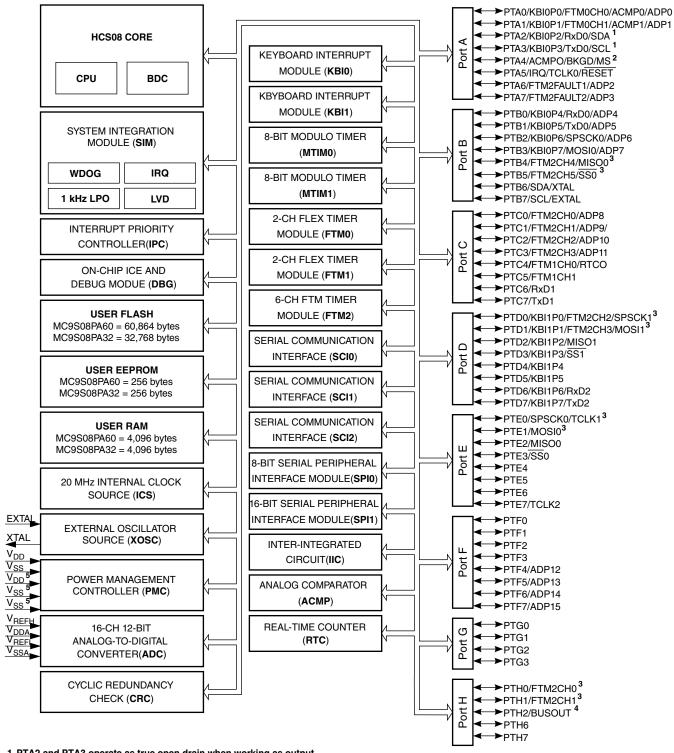

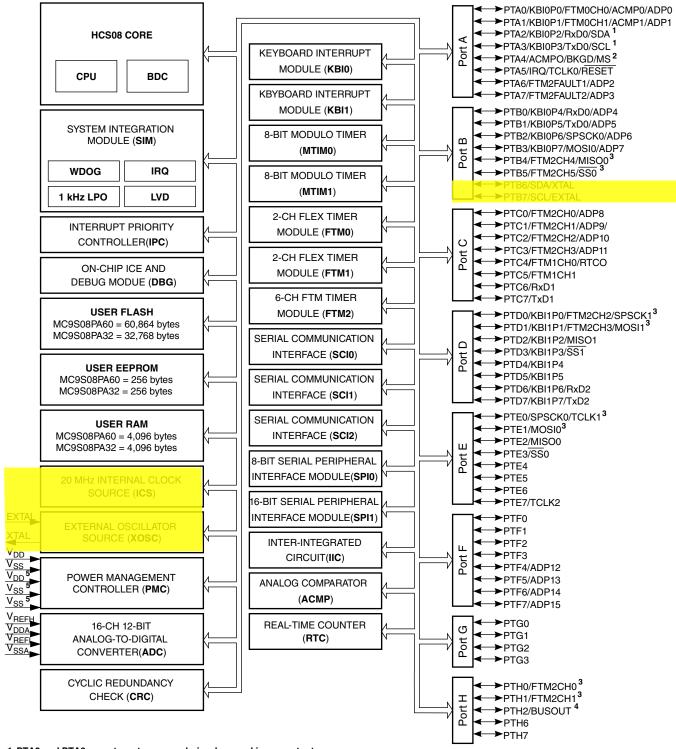

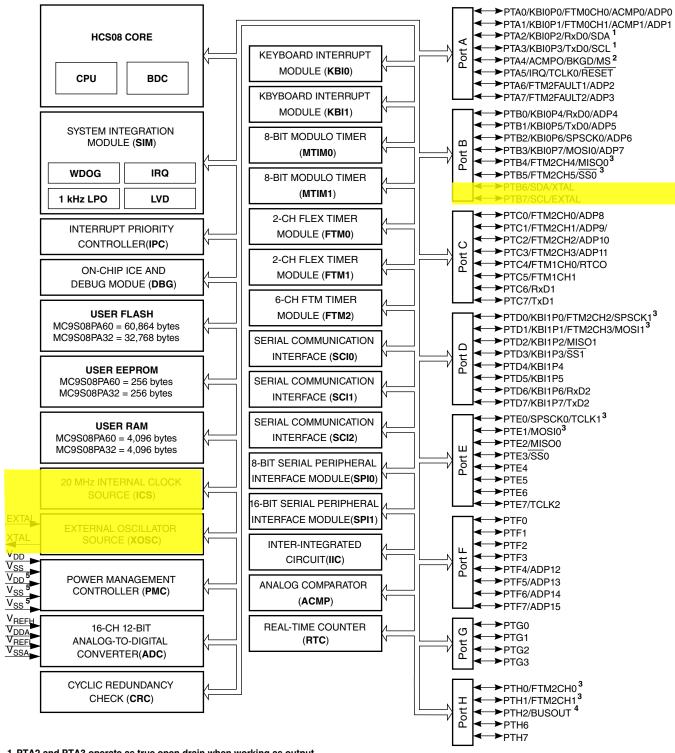

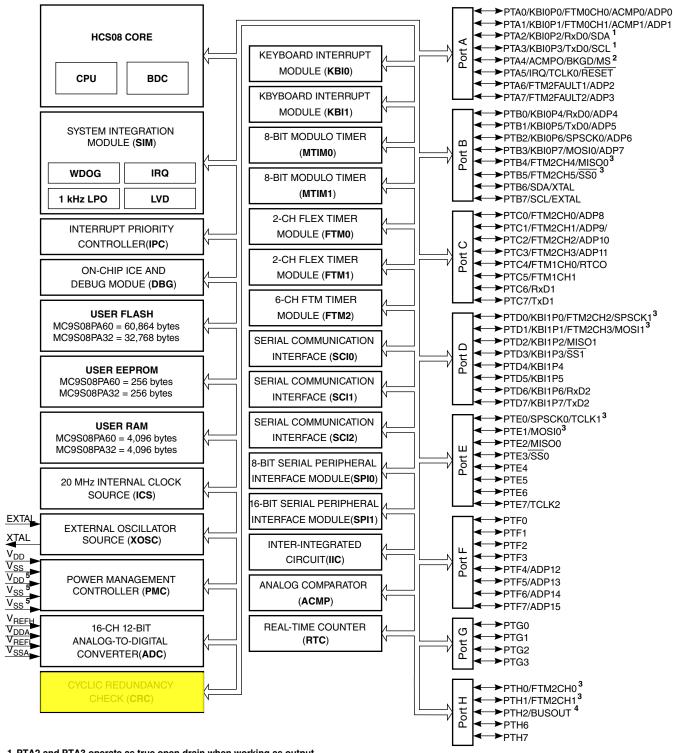

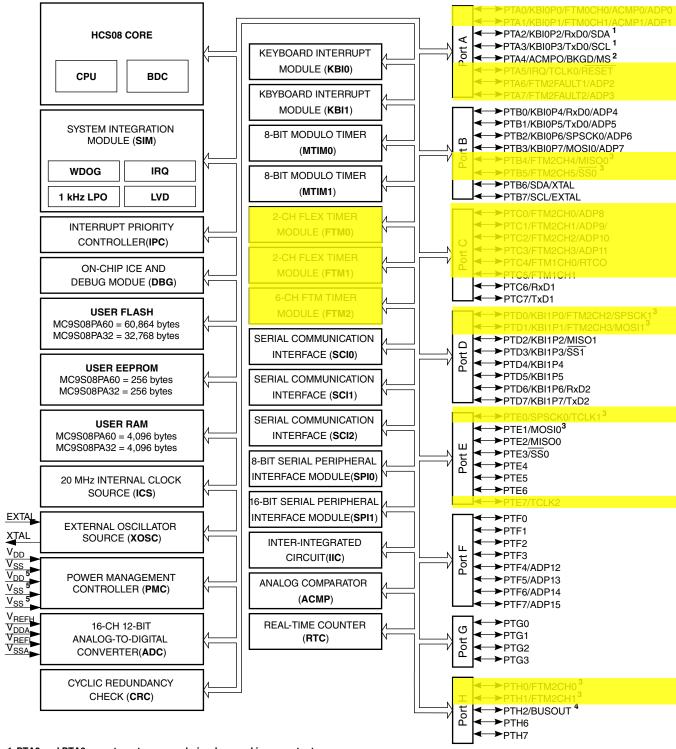

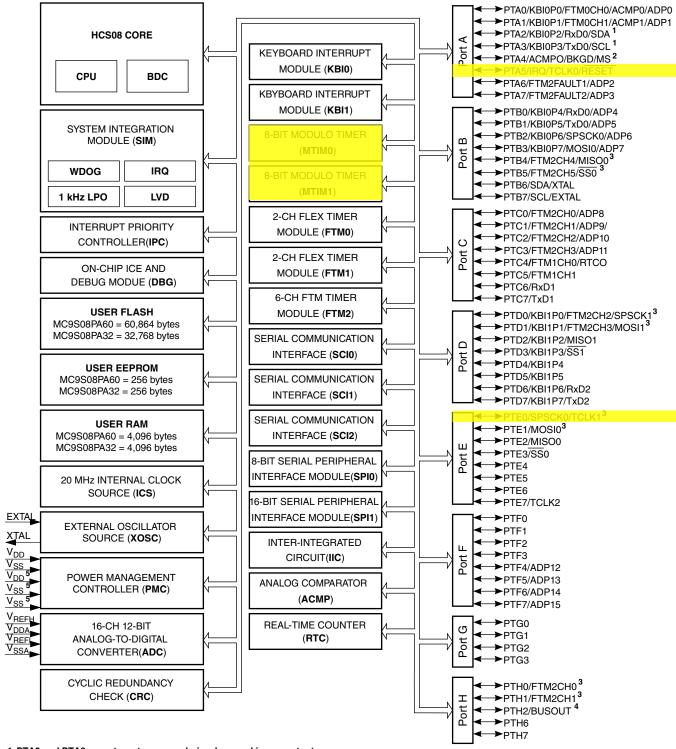

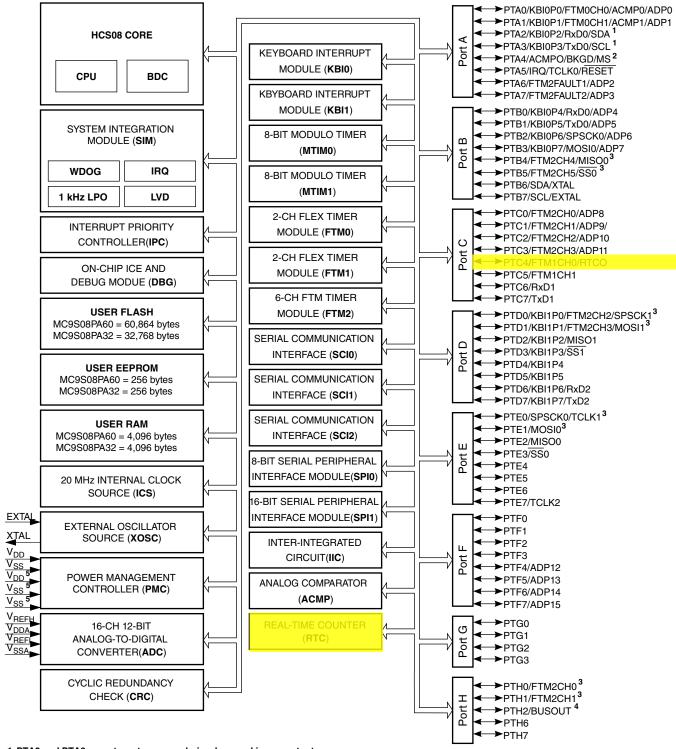

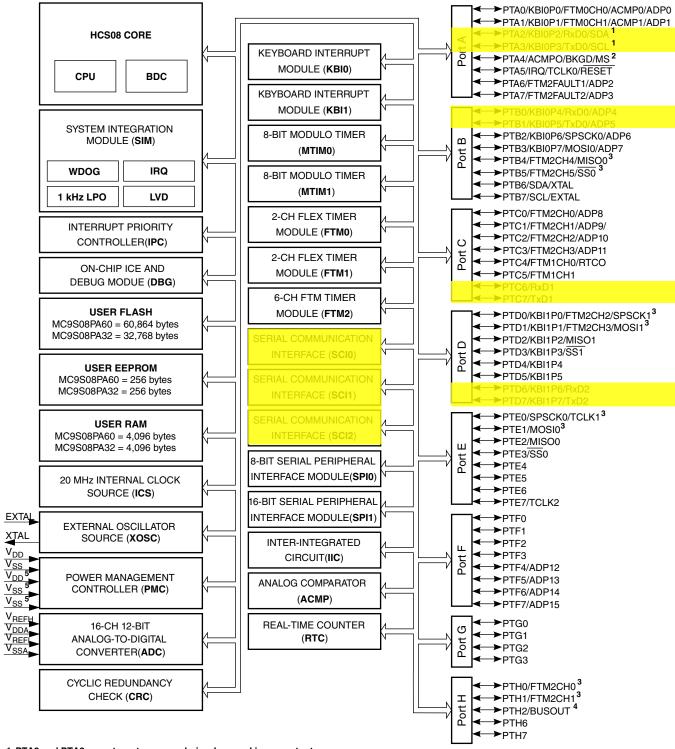

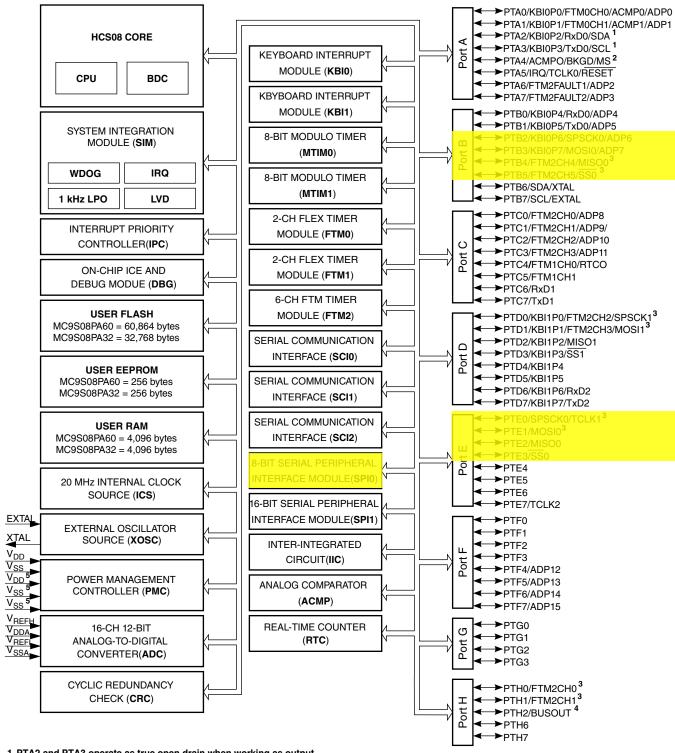

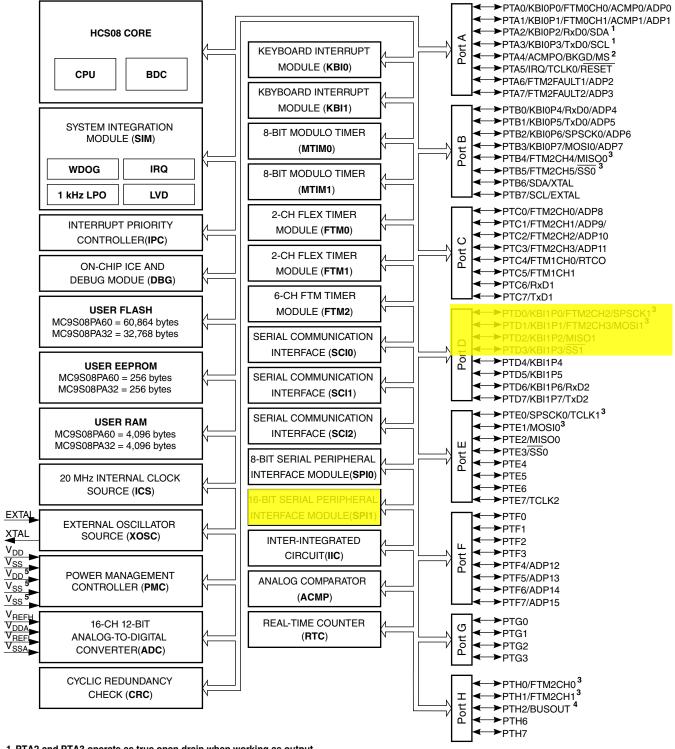

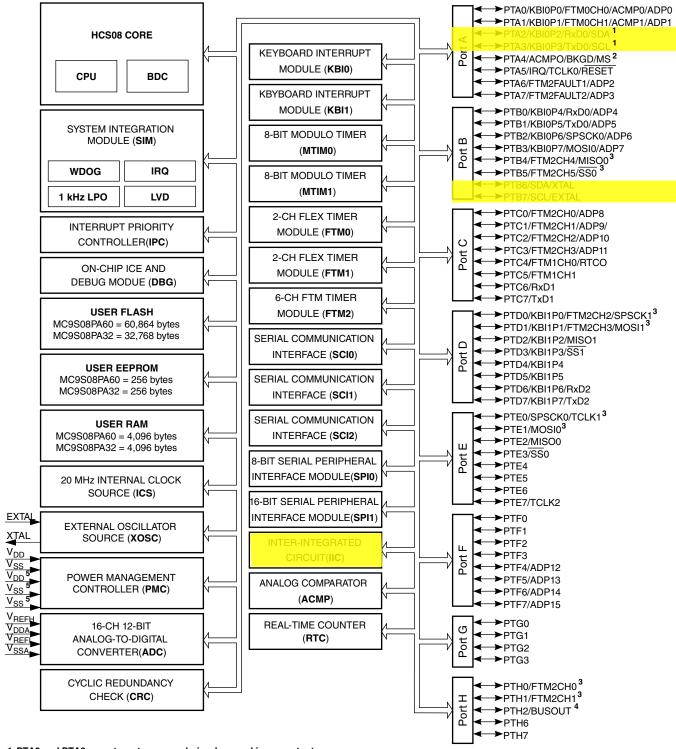

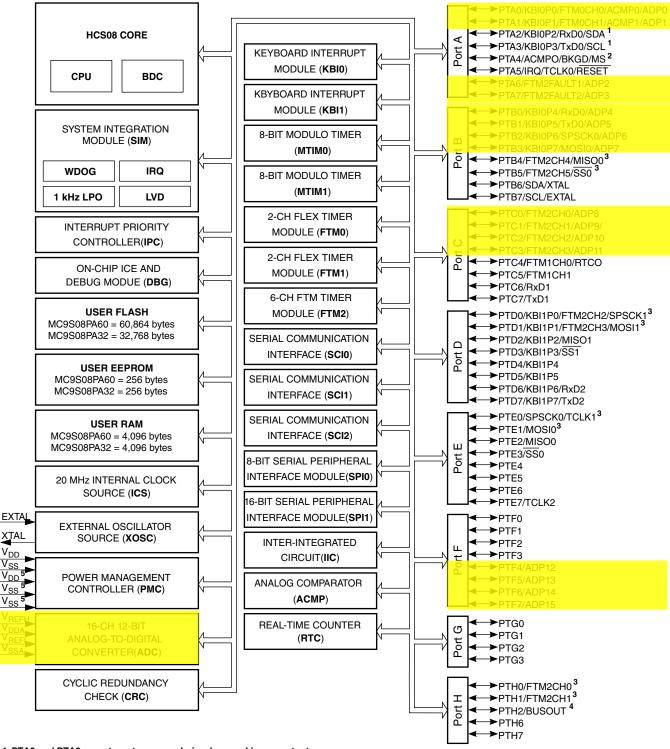

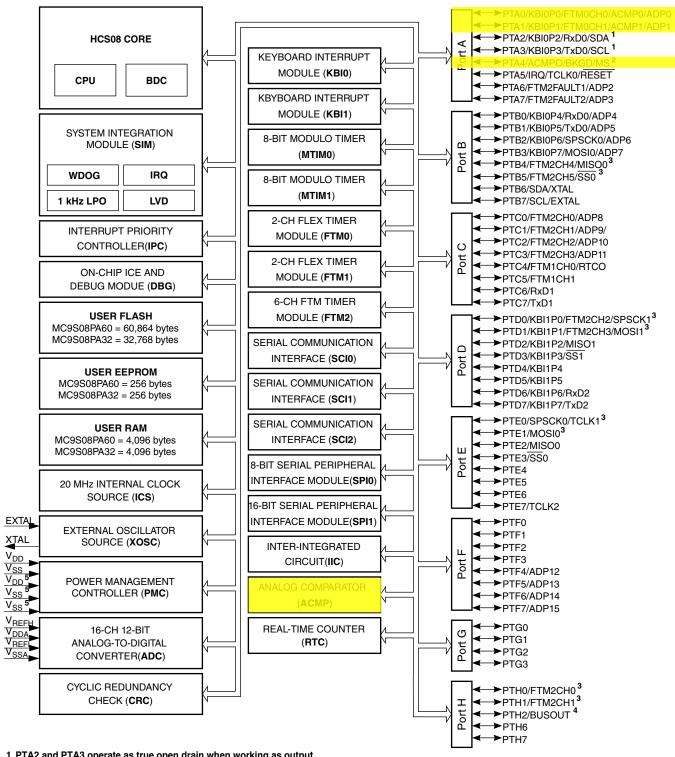

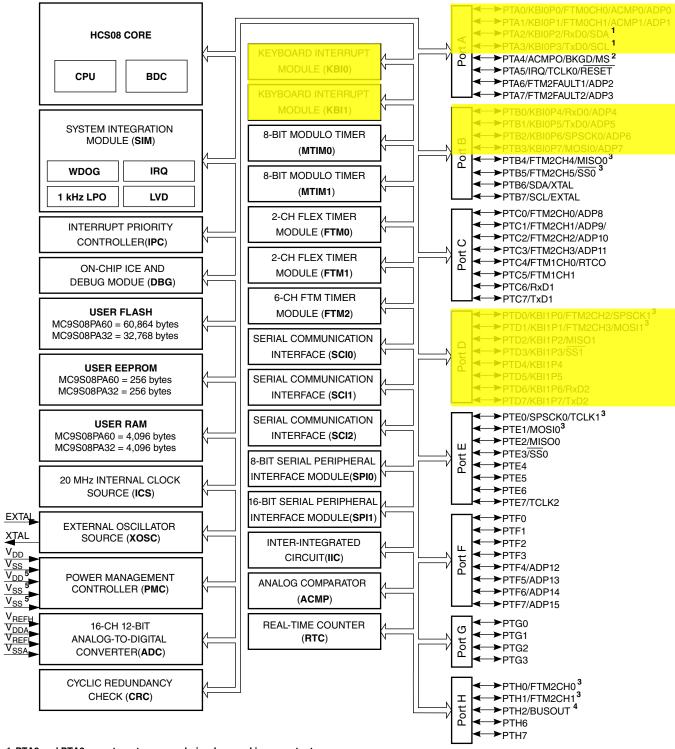

| 1.2 | MCU b   | lock diagram                                                             | 34   |

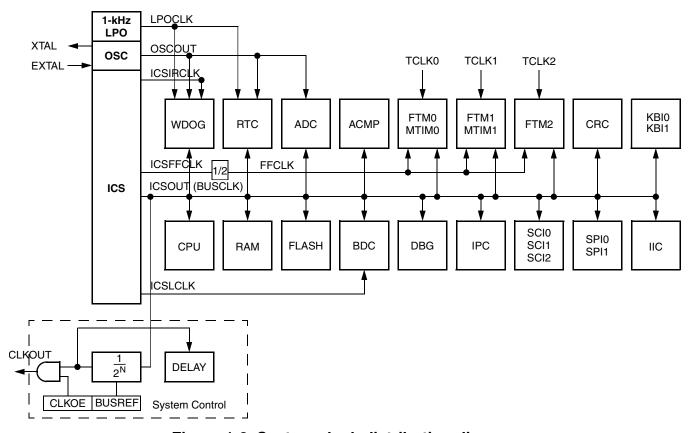

| 1.3 | System  | clock distribution                                                       | 36   |

|     |         | Chapter 2 Pins and connections                                           |      |

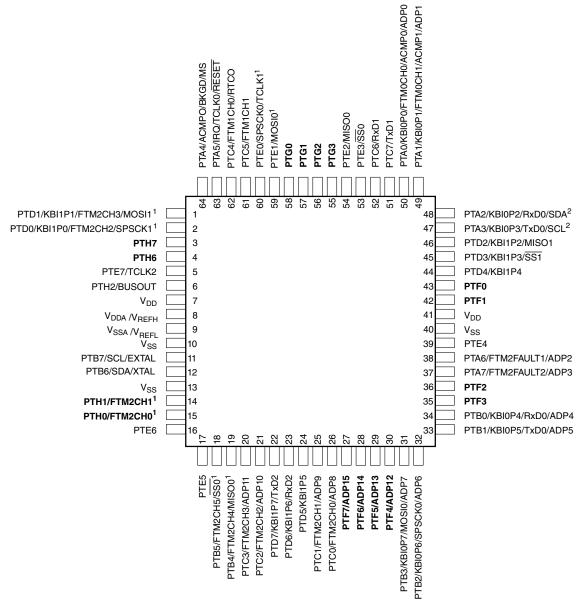

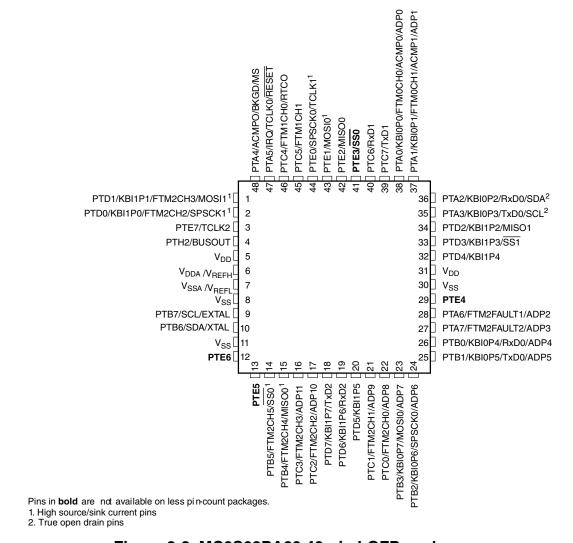

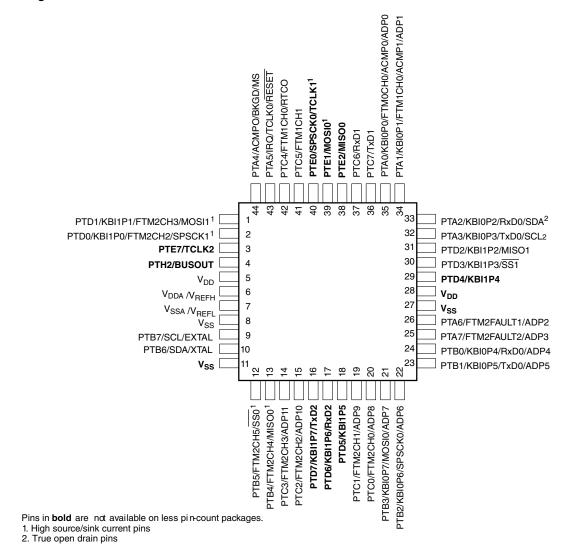

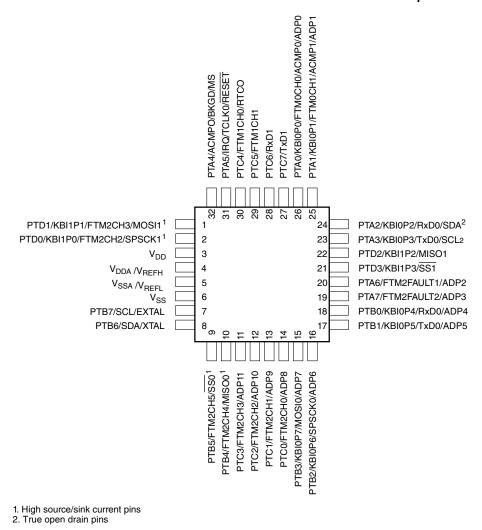

| 2.1 | Device  | pin assignment.                                                          | 39   |

| 2.2 | Pin fun | 43                                                                       |      |

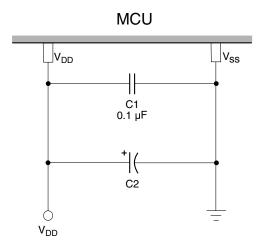

|     | 2.2.1   | Power (VDD, VSS)                                                         | 43   |

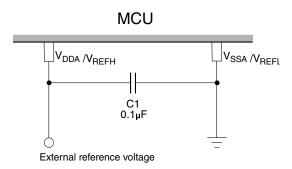

|     | 2.2.2   | Analog power supply and reference pins (VDDA/VREFH and VSSA/VREFL)       | 44   |

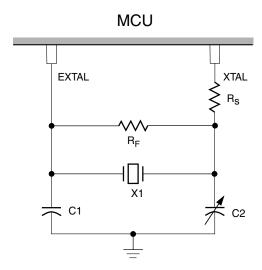

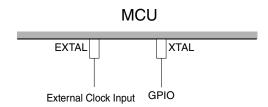

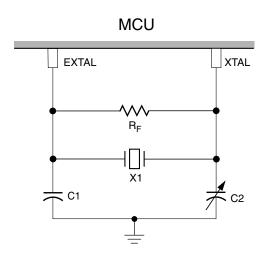

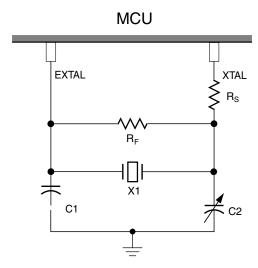

|     | 2.2.3   | Oscillator (XTAL, EXTAL)                                                 | 45   |

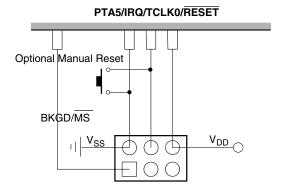

|     | 2.2.4   | External reset pin (RESET)                                               | 46   |

|     | 2.2.5   | Background/mode select (BKGD/MS)                                         | 46   |

|     | 2.2.6   | Port A input/output (I/O) pins (PTA–PTA0)                                | 47   |

|     | 2.2.7   | Port B input/output (I/O) pins (PTB7–PTB0)                               | 47   |

|     | 2.2.8   | Port C input/output (I/O) pins (PTC–PTC0)                                | 47   |

|     | 2.2.9   | Port D input/output (I/O) pins (PTD7–PTD0)                               | 48   |

|     | 2.2.10  | Port E input/Output (I/O) pins (PTE7-PTE0)                               | 48   |

|     | 2.2.11  | Port F input/output (I/O) pins (PTF7–PTF0)                               | 48   |

|     | 2.2.12  | Port G input/output (I/O) pins (PTG3–PTG0)                               | 48   |

|     | 2.2.13  | Port H input/output (I/O) pins (PTH7–PTH6, PTH2–PTH0)                    | 48   |

|     | 2.2.14  | True open drain pins (PTA3–PTA2)                                         | 49   |

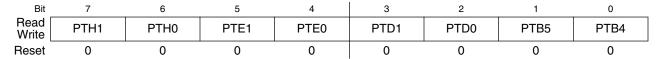

|     | 2.2.15  | High current drive pins (PTB4, PTB5, PTD0, PTD1, PTE0, PTE1, PTH0, PTH1) | 49   |

| 2.3 | Periphe | ral pinouts.                                                             | 49   |

|     |         | Chapter 3 Power management                                               |      |

| 3.1 | Introdu | ction                                                                    | 53   |

| Sec | Section number Title |                                                                    |    |

|-----|----------------------|--------------------------------------------------------------------|----|

| 3.2 | Feature              | es                                                                 | 53 |

|     | 3.2.1                | Run mode                                                           | 53 |

|     | 3.2.2                | Wait mode                                                          | 54 |

|     | 3.2.3                | Stop3 mode                                                         | 54 |

|     | 3.2.4                | Active BDM enabled in stop3 mode                                   | 54 |

|     | 3.2.5                | LVD enabled in stop mode                                           | 55 |

|     | 3.2.6                | Power modes behaviors                                              | 55 |

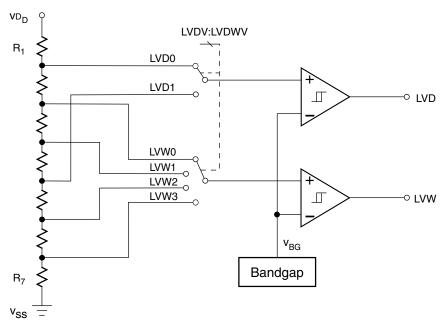

| 3.3 | Low ve               | oltage detect (LVD) system                                         | 56 |

|     | 3.3.1                | Power-on reset (POR) operation                                     | 57 |

|     | 3.3.2                | LVD reset operation                                                | 57 |

|     | 3.3.3                | Low-voltage warning (LVW)                                          | 57 |

| 3.4 | Bandg                | ap reference                                                       | 58 |

| 3.5 | Power                | 58                                                                 |    |

|     | 3.5.1                | System Power Management Status and Control 1 Register (PMC_SPMSC1) | 58 |

|     | 3.5.2                | System Power Management Status and Control 2 Register (PMC_SPMSC2) | 60 |

|     |                      | Chapter 4<br>Memory map                                            |    |

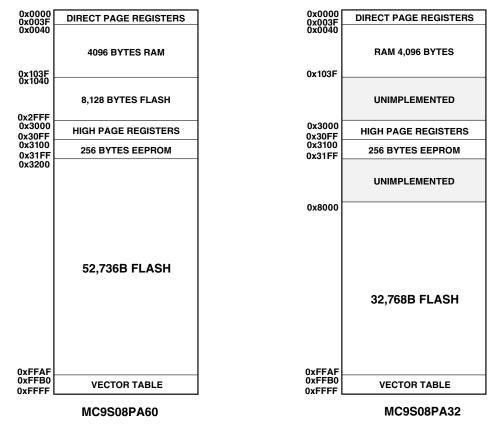

| 4.1 | Memo                 | ry map                                                             | 61 |

| 4.2 | Reset a              | and interrupt vector assignments                                   | 62 |

| 4.3 | Registe              | er addresses and bit assignments                                   | 63 |

| 4.4 | Rando                | m-access memory (RAM)                                              | 75 |

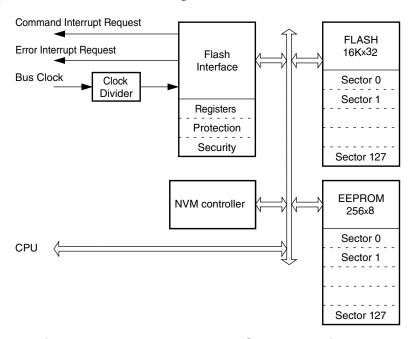

| 4.5 | Flash a              | and EEPROM                                                         | 75 |

|     | 4.5.1                | Overview                                                           | 75 |

|     | 4.5.2                | Function descriptions.                                             | 77 |

|     |                      | 4.5.2.1 Modes of operation                                         | 77 |

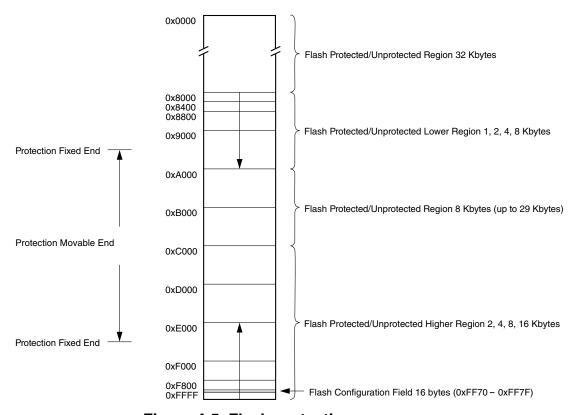

|     |                      | 4.5.2.2 Flash and EEPROM memory map                                | 78 |

|     |                      | 4.5.2.3 Flash and EEPROM initialization after system reset         | 78 |

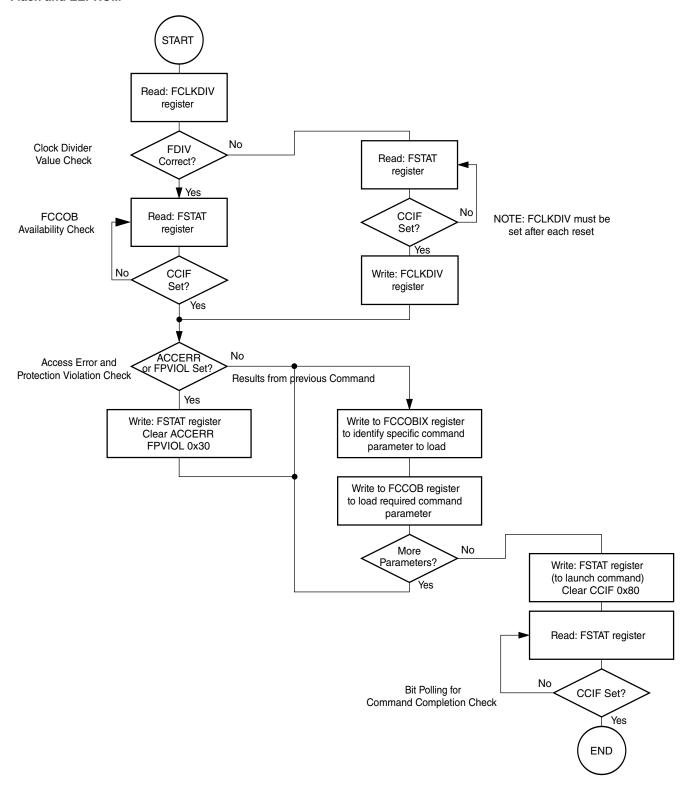

|     |                      | 4.5.2.4 Flash and EEPROM command operations                        | 79 |

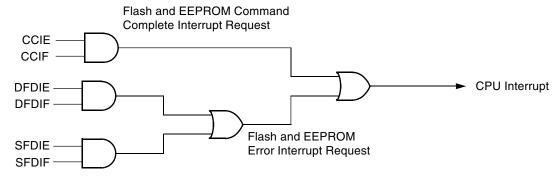

|     |                      | 4.5.2.5 Flash and EEPROM interrupts                                | 84 |

| Section number |          | umber       | Title                                                | Page |

|----------------|----------|-------------|------------------------------------------------------|------|

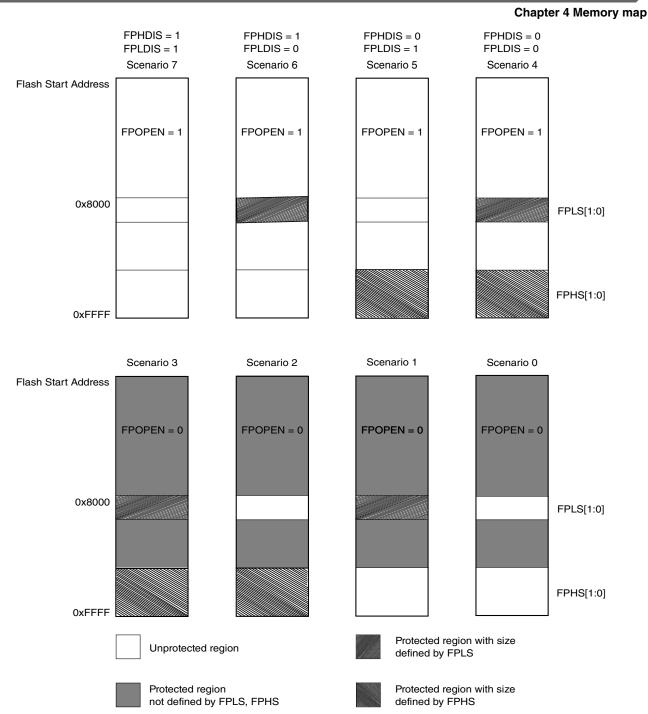

|                |          | 4.5.2.6     | Protection                                           | 85   |

|                |          | 4.5.2.7     | Security                                             |      |

|                |          | 4.5.2.8     | Flash and EEPROM commands                            | 91   |

|                |          | 4.5.2.9     | Flash and EEPROM command summary                     | 93   |

| 4.6            | Flash a  | nd EEPRO    | OM registers descriptions.                           | 107  |

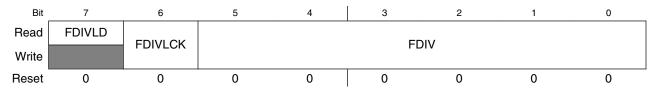

|                | 4.6.1    | Flash Clo   | ock Divider Register (NVM_FCLKDIV)                   | 107  |

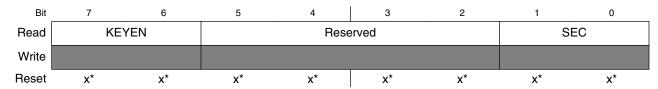

|                | 4.6.2    | Flash Sec   | curity Register (NVM_FSEC)                           | 108  |

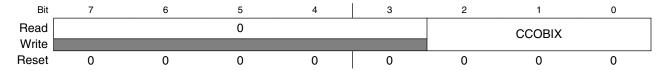

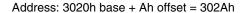

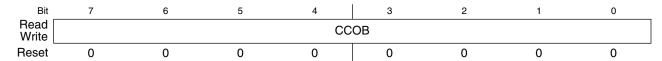

|                | 4.6.3    | Flash CC    | COB Index Register (NVM_FCCOBIX)                     |      |

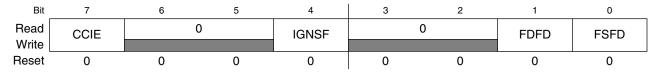

|                | 4.6.4    | Flash Co    | onfiguration Register (NVM_FCNFG)                    |      |

|                | 4.6.5    | Flash Em    | ror Configuration Register (NVM_FERCNFG)             | 110  |

|                | 4.6.6    | Flash Sta   | atus Register (NVM_FSTAT)                            | 111  |

|                | 4.6.7    | Flash Em    | ror Status Register (NVM_FERSTAT)                    | 112  |

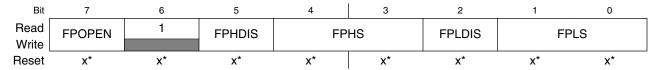

|                | 4.6.8    | Flash Pro   | otection Register (NVM_FPROT)                        | 113  |

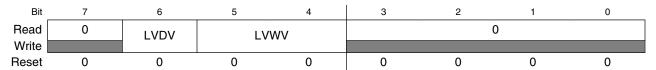

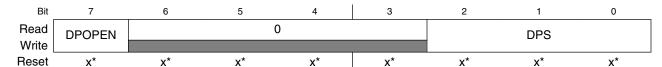

|                | 4.6.9    | EEPRON      | M Protection Register (NVM_EEPROT)                   | 114  |

|                | 4.6.10   | Flash Co    | ommon Command Object Register:High (NVM_FCCOBHI)     | 116  |

|                | 4.6.11   | Flash Co    | ommon Command Object Register: Low (NVM_FCCOBLO)     | 116  |

|                | 4.6.12   | Flash Op    | otion Register (NVM_FOPT)                            | 116  |

|                |          |             | Chapter 5<br>Interrupts                              |      |

| 5.1            | Interrup | ots         |                                                      | 119  |

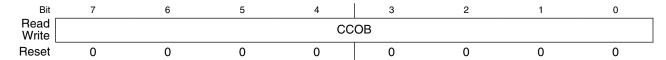

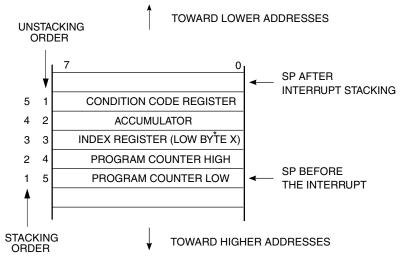

|                | 5.1.1    | Interrupt   | stack frame                                          | 120  |

|                | 5.1.2    | Interrupt   | t vectors, sources, and local masks                  | 121  |

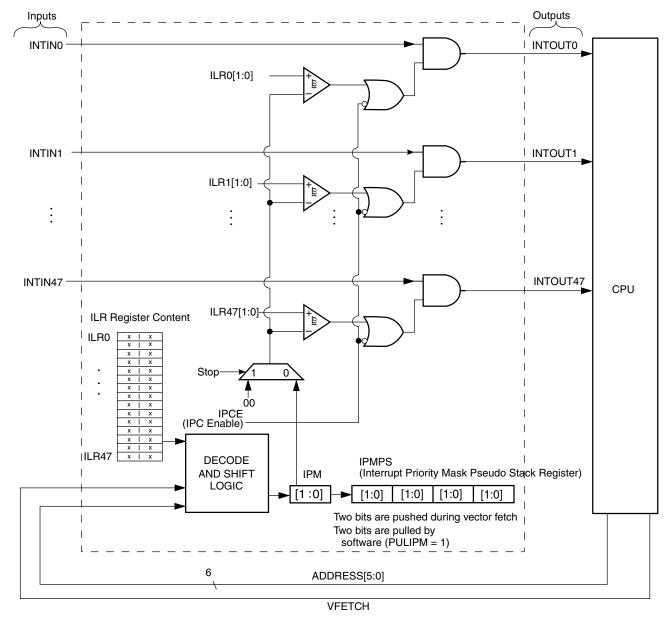

|                | 5.1.3    | Interrupt   | priority controller (IPC)                            | 124  |

|                |          | 5.1.3.1     | Interrupt priority level register                    | 125  |

|                |          | 5.1.3.2     | Interrupt priority level comparator set              | 126  |

|                |          | 5.1.3.3     | Interrupt priority mask update and restore mechanism | 126  |

|                |          | 5.1.3.4     | Integration and application of the IPC               | 127  |

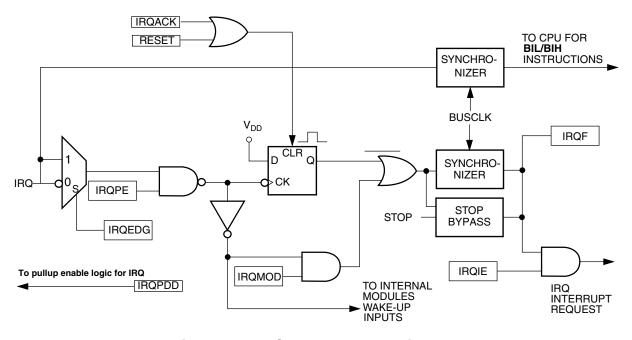

| 5.2            | Externa  | l interrupt | request (IRQ)                                        | 127  |

|                | 5.2.1    | Features.   |                                                      | 128  |

|                |          |             |                                                      |      |

| Section number |                 | mber       | Title                                               | Page |

|----------------|-----------------|------------|-----------------------------------------------------|------|

|                | :               | 5.2.1.1    | Pin configuration options                           | 128  |

|                | :               | 5.2.1.2    | Edge and level sensitivity                          |      |

| 5.3            | IRQ mem         | nory map   | and register definition                             | 129  |

|                | 5.3.1           | Interrupt  | Pin Request Status and Control Register (IRQ_SC)    | 129  |

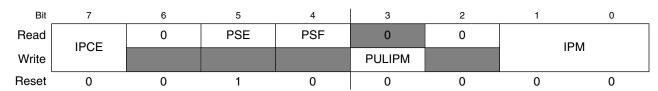

| 5.4            | Interrupt       | priority o | controller (IPC) memory map and register definition | 131  |

|                | 5.4.1           | IPC Statu  | us and Control Register (IPC_SC)                    | 131  |

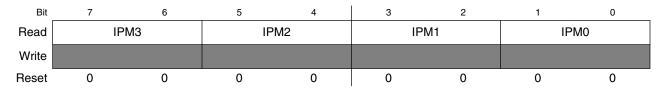

|                | 5.4.2           | Interrupt  | Priority Mask Pseudo Stack Register (IPC_IPMPS)     |      |

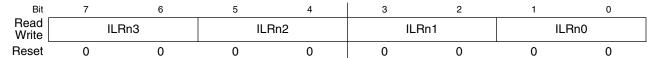

|                | 5.4.3           | Interrupt  | t Level Setting Registers n (IPC_ILRSn)             | 133  |

|                |                 |            | Chapter 6 System control                            |      |

| 6.1            | System de       | evice ide  | entification (SDID)                                 | 135  |

| 6.2            | Universal       | lly uniqu  | e identification (UUID)                             | 135  |

| 6.3            | Reset and       | l system   | initialization                                      | 135  |

| 6.4            | System options. |            |                                                     |      |

|                | 6.4.1           | BKGD p     | oin enable                                          | 136  |

|                | 6.4.2           | RESET p    | pin enable                                          | 136  |

|                | 6.4.3           | SCI0 pin   | n reassignment                                      |      |

|                | 6.4.4           | SPI0 pin   | reassignment.                                       | 137  |

|                | 6.4.5           | IIC pins   | reassignments                                       | 137  |

|                | 6.4.6           | FTM2 ch    | hannels pin reassignment                            |      |

|                | 6.4.7           | Bus cloc   | k output pin enable                                 | 137  |

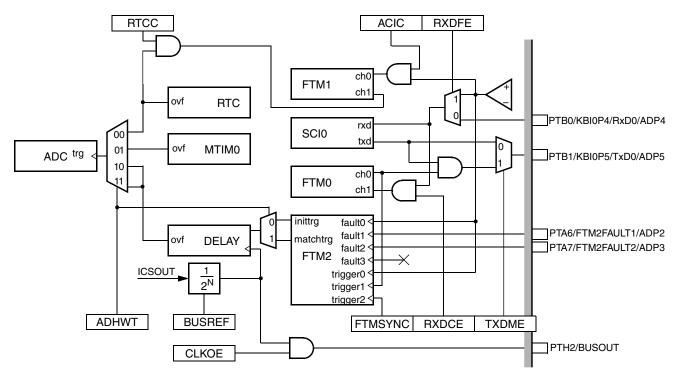

| 6.5            | System in       | nterconne  | ection                                              | 138  |

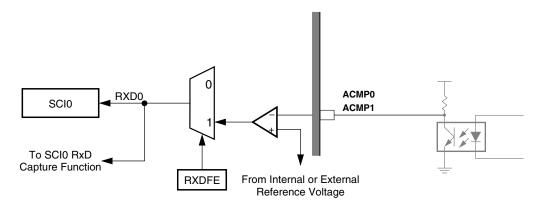

|                | 6.5.1           | ACMP o     | output selection                                    | 138  |

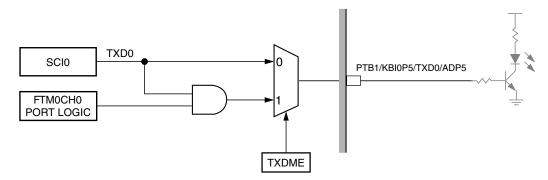

|                | 6.5.2           | SCI0 Txl   | D modulation                                        | 138  |

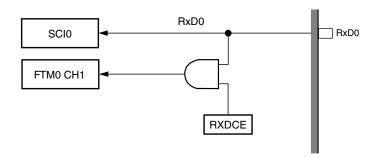

|                | 6.5.3           | SCI0 Rx    | D capture                                           | 139  |

|                | 6.5.4           | SCI0 Rx    | D filter                                            | 139  |

|                | 6.5.5           | RTC cap    | oture                                               | 140  |

|                | 6.5.6           | FTM2 so    | oftware synchronization                             | 140  |

|                | 6.5.7           | ADC har    | rdware trigger                                      | 140  |

| Sec | ction n  | Page                                     |                                 |     |

|-----|----------|------------------------------------------|---------------------------------|-----|

| 5.6 | System   | Control Registers                        |                                 | 141 |

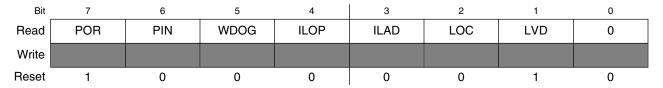

|     | 6.6.1    | System Reset Status Register (SYS_SR     | S)                              | 141 |

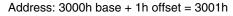

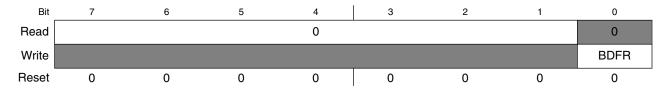

|     | 6.6.2    | System Background Debug Force Reset      | t Register (SYS_SBDFR)          | 143 |

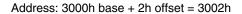

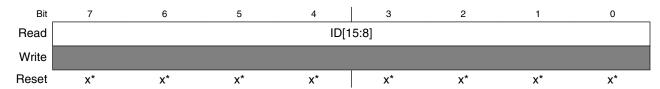

|     | 6.6.3    | System Device Identification Register:   | High (SYS_SDIDH)                | 144 |

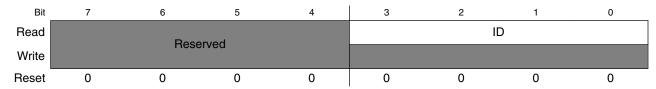

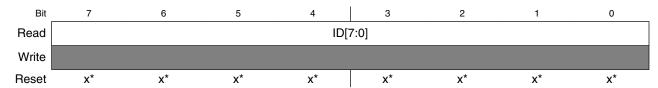

|     | 6.6.4    | System Device Identification Register:   | Low (SYS_SDIDL)                 | 144 |

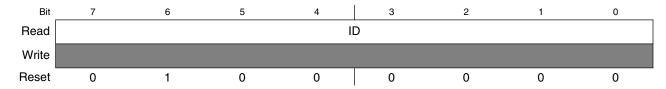

|     | 6.6.5    | System Options Register 1 (SYS_SOPT      | Γ1)                             | 145 |

|     | 6.6.6    | System Options Register 2 (SYS_SOPT      | Γ2)                             | 146 |

|     | 6.6.7    | System Options Register 3 (SYS_SOPT      | T3)                             | 147 |

|     | 6.6.8    | System Options Register 4 (SYS_SOPT      | Γ4)                             | 148 |

|     | 6.6.9    | Illegal Address Register: High (SYS_IL   | LAH)                            | 149 |

|     | 6.6.10   | Illegal Address Register: Low (SYS_IL    | LAL)                            | 149 |

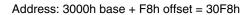

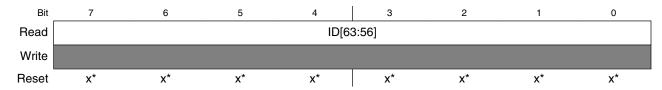

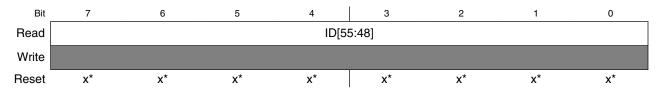

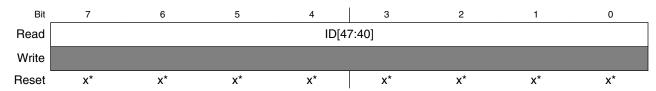

|     | 6.6.11   | Universally Unique Identifier Register   | 1 (SYS_UUID1)                   | 150 |

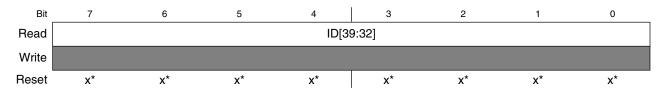

|     | 6.6.12   | Universally Unique Identifier Register 2 | 2 (SYS_UUID2)                   | 150 |

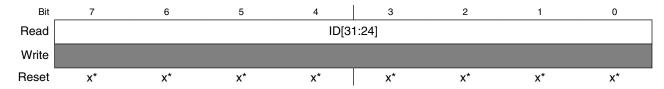

|     | 6.6.13   | Universally Unique Identifier Register   | 3 (SYS_UUID3)                   | 151 |

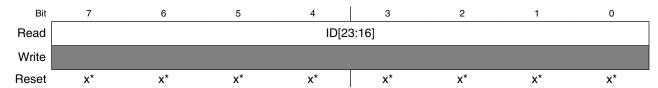

|     | 6.6.14   | Universally Unique Identifier Register   | 4 (SYS_UUID4)                   | 151 |

|     | 6.6.15   | Universally Unique Identifier Register   | 5 (SYS_UUID5)                   | 152 |

|     | 6.6.16   | Universally Unique Identifier Register ( | 6 (SYS_UUID6)                   | 152 |

|     | 6.6.17   | Universally Unique Identifier Register   | 7 (SYS_UUID7)                   | 153 |

|     | 6.6.18   | Universally Unique Identifier Register   | 8 (SYS_UUID8)                   | 153 |

|     |          | Para                                     | Chapter 7<br>Illel input/output |     |

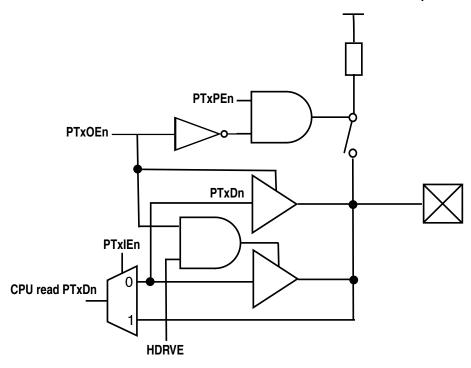

| 7.1 | Introdu  | ction                                    |                                 | 155 |

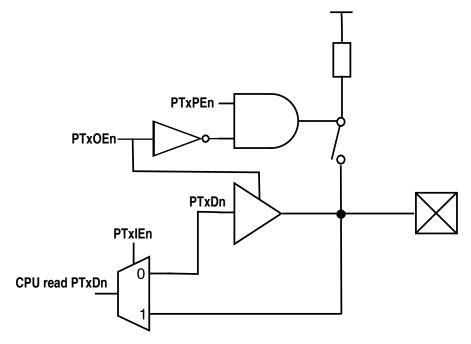

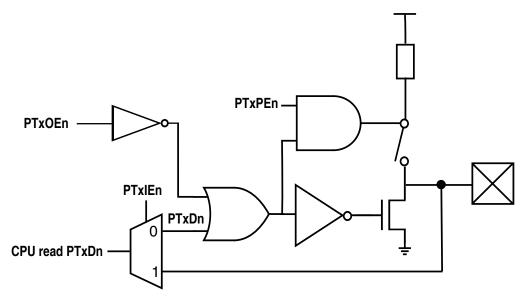

| 7.2 | Port dat | ta and data direction                    |                                 | 157 |

| 7.3 | Internal | pullup enable                            |                                 |     |

| 7.4 | Input g  | litch filter setting                     |                                 | 158 |

| 7.5 | High cu  | rrent drive                              |                                 | 159 |

| 7.6 | Pin beh  | avior in stop mode                       |                                 | 159 |

| 7.7 | Port dat | ta registers                             |                                 | 159 |

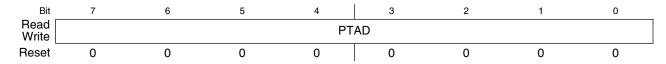

|     | 7.7.1    | Port A Data Register (PORT_PTAD)         |                                 | 160 |

|     |          |                                          |                                 |     |

| Section n | umber Title                                  | Page |

|-----------|----------------------------------------------|------|

| 7.7.2     | Port B Data Register (PORT_PTBD)             | 161  |

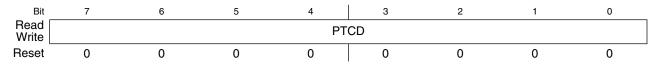

| 7.7.3     | Port C Data Register (PORT_PTCD)             |      |

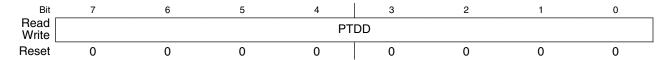

| 7.7.4     | Port D Data Register (PORT_PTDD)             | 162  |

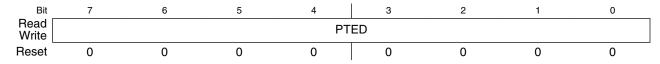

| 7.7.5     | Port E Data Register (PORT_PTED)             | 162  |

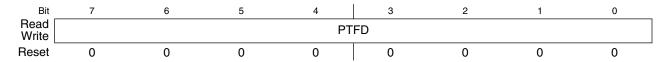

| 7.7.6     | Port F Data Register (PORT_PTFD)             |      |

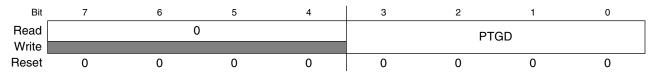

| 7.7.7     | Port G Data Register (PORT_PTGD)             | 163  |

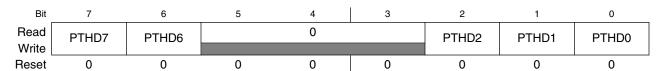

| 7.7.8     | Port H Data Register (PORT_PTHD)             | 164  |

| 7.7.9     | Port High Drive Enable Register (PORT_HDRVE) | 165  |

| 7.7.10    | Port A Output Enable Register (PORT_PTAOE)   | 166  |

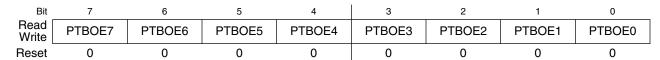

| 7.7.11    | Port B Output Enable Register (PORT_PTBOE)   |      |

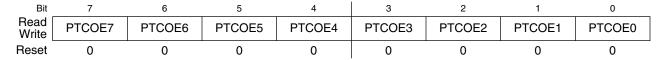

| 7.7.12    | Port C Output Enable Register (PORT_PTCOE)   |      |

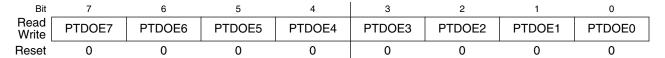

| 7.7.13    | Port D Output Enable Register (PORT_PTDOE)   | 170  |

| 7.7.14    | Port E Output Enable Register (PORT_PTEOE)   | 171  |

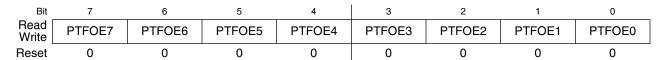

| 7.7.15    | Port F Output Enable Register (PORT_PTFOE)   |      |

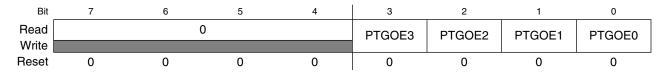

| 7.7.16    | Port G Output Enable Register (PORT_PTGOE)   | 173  |

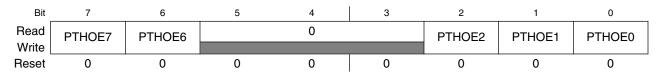

| 7.7.17    | Port H Output Enable Register (PORT_PTHOE)   | 174  |

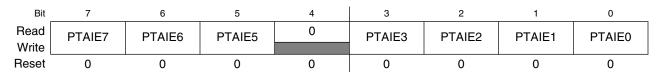

| 7.7.18    | Port A Input Enable Register (PORT_PTAIE)    | 175  |

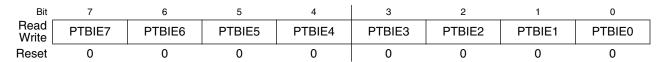

| 7.7.19    | Port B Input Enable Register (PORT_PTBIE)    |      |

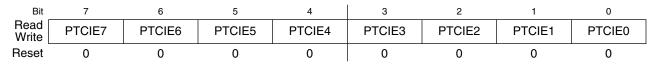

| 7.7.20    | Port C Input Enable Register (PORT_PTCIE)    |      |

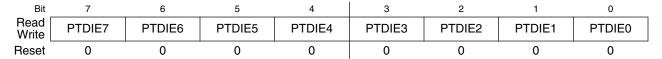

| 7.7.21    | Port D Input Enable Register (PORT_PTDIE)    | 179  |

| 7.7.22    | Port E Input Enable Register (PORT_PTEIE)    | 180  |

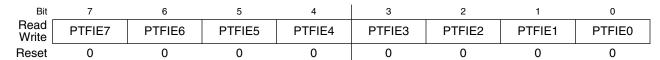

| 7.7.23    | Port F Input Enable Register (PORT_PTFIE)    |      |

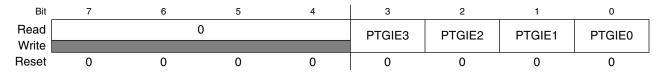

| 7.7.24    | Port G Input Enable Register (PORT_PTGIE)    | 182  |

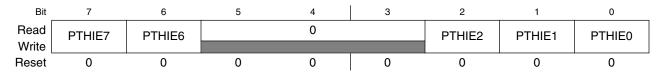

| 7.7.25    | Port H Input Enable Register (PORT_PTHIE)    | 183  |

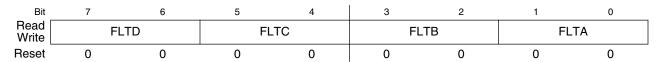

| 7.7.26    | Port Filter Register 0 (PORT_IOFLT0)         | 184  |

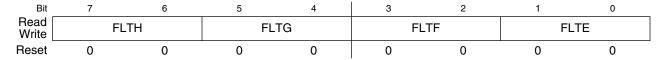

| 7.7.27    | Port Filter Register 1 (PORT_IOFLT1)         | 185  |

| 7.7.28    | Port Filter Register 2 (PORT_IOFLT2)         | 186  |

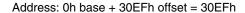

| 7.7.29    | Port Clock Division Register (PORT_FCLKDIV)  |      |

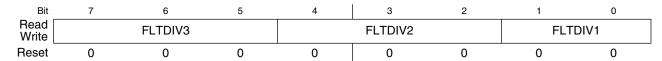

| 7.7.30    | Port A Pullup Enable Register (PORT_PTAPE)   |      |

| Sec | ction n                                  | umber       | Title                                   | Page |

|-----|------------------------------------------|-------------|-----------------------------------------|------|

|     | 7.7.31                                   | Port B P    | ullup Enable Register (PORT_PTBPE)      | 189  |

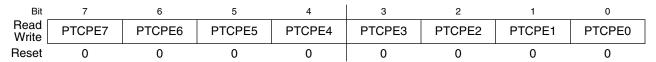

|     | 7.7.32                                   | Port C P    | tullup Enable Register (PORT_PTCPE)     | 190  |

|     | 7.7.33                                   | Port D P    | Pullup Enable Register (PORT_PTDPE)     | 192  |

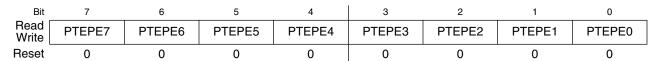

|     | 7.7.34                                   | Port E Pu   | ullup Enable Register (PORT_PTEPE)      | 193  |

|     | 7.7.35                                   | Port F Pu   | ullup Enable Register (PORT_PTFPE)      |      |

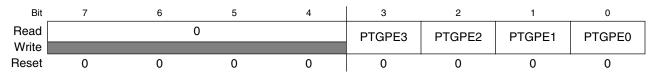

|     | 7.7.36                                   | Port G P    | Pullup Enable Register (PORT_PTGPE)     | 196  |

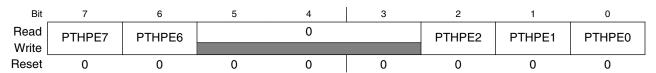

|     | 7.7.37                                   | Port H P    | Pullup Enable Register (PORT_PTHPE)     | 197  |

|     |                                          |             | Chapter 8 Clock management              |      |

| 8.1 | Clock 1                                  | module      |                                         | 199  |

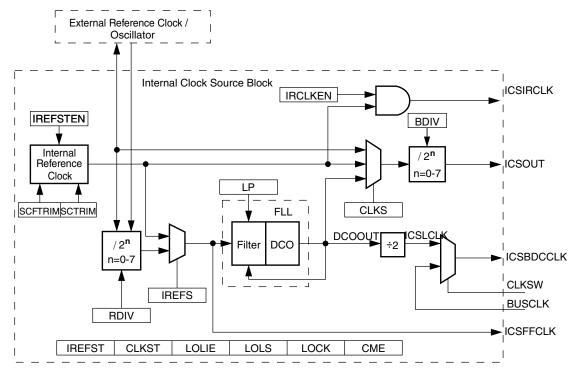

| 8.2 | Interna                                  | l clock sou | rrce (ICS)                              | 201  |

|     | 8.2.1                                    | Function    | n description                           | 201  |

|     |                                          | 8.2.1.1     | Bus frequency divider                   | 202  |

|     |                                          | 8.2.1.2     | Low power bit usage                     | 202  |

|     |                                          | 8.2.1.3     | Internal reference clock (ICSIRCLK)     | 202  |

|     |                                          | 8.2.1.4     | Fixed frequency clock (ICSFFCLK)        | 203  |

|     |                                          | 8.2.1.5     | BDC clock                               | 204  |

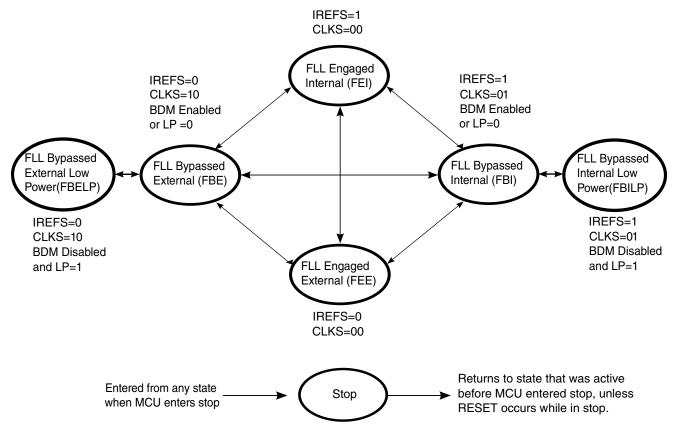

|     | 8.2.2                                    | Modes o     | of operation                            |      |

|     |                                          | 8.2.2.1     | FLL engaged internal (FEI)              |      |

|     |                                          | 8.2.2.2     | FLL engaged external (FEE)              | 206  |

|     |                                          | 8.2.2.3     | FLL bypassed internal (FBI)             | 206  |

|     |                                          | 8.2.2.4     | FLL bypassed internal low power (FBILP) | 206  |

|     |                                          | 8.2.2.5     | FLL bypassed external (FBE)             | 207  |

|     |                                          | 8.2.2.6     | FLL bypassed external low power (FBELP) |      |

|     |                                          | 8.2.2.7     | Stop (STOP)                             | 208  |

|     | 8.2.3                                    | FLL lock    | k and clock monitor                     | 209  |

|     |                                          | 8.2.3.1     | FLL clock lock                          | 209  |

|     |                                          | 8.2.3.2     | External reference clock monitor        |      |

| 8.3 | Initialization / application information |             |                                         |      |

| Sec | Section number                         |                                                 | Title                                            | Page |

|-----|----------------------------------------|-------------------------------------------------|--------------------------------------------------|------|

|     | 8.3.1                                  | Initializi                                      | ng FEI mode                                      | 210  |

|     | 8.3.2                                  | Initializi                                      | ng FBI mode                                      | 210  |

|     | 8.3.3                                  | Initializi                                      | ng FEE mode                                      | 210  |

|     | 8.3.4                                  | Initializi                                      | ng FBE mode                                      | 211  |

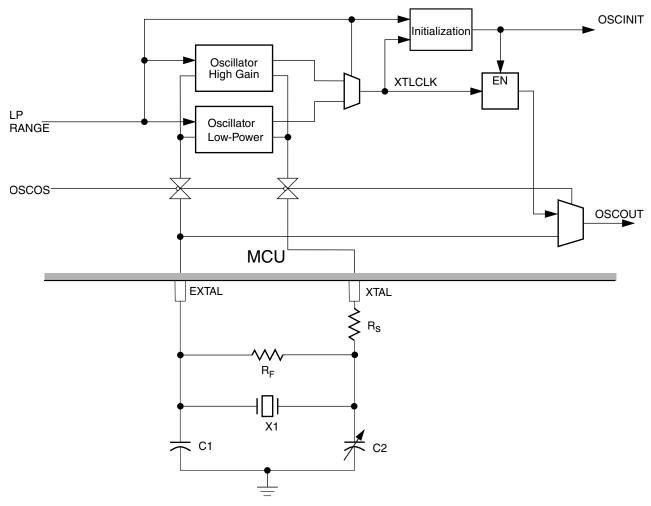

|     | 8.3.5                                  | External                                        | oscillator (XOSC)                                | 211  |

|     |                                        | 8.3.5.1                                         | Bypass mode                                      | 212  |

|     |                                        | 8.3.5.2                                         | Low-power configuration                          |      |

|     |                                        | 8.3.5.3                                         | High-gain configuration                          | 213  |

|     |                                        | 8.3.5.4                                         | Initializing external oscillator for peripherals | 214  |

| 8.4 | 1 kHz                                  | low-power                                       | oscillator (LPO)                                 |      |

| 8.5 | Periphe                                | eral clock g                                    | gating                                           |      |

| 8.6 | ICS co                                 |                                                 |                                                  |      |

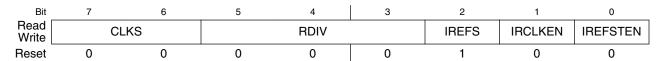

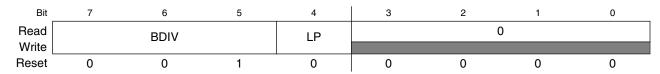

|     | 8.6.1                                  | ICS Con                                         | trol Register 1 (ICS_C1)                         |      |

|     | 8.6.2                                  | ICS Con                                         | trol Register 2 (ICS_C2)                         | 217  |

|     | 8.6.3                                  | ICS Con                                         | trol Register 3 (ICS_C3)                         |      |

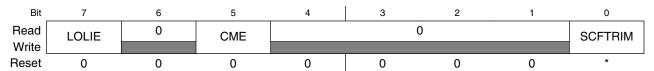

|     | 8.6.4                                  | ICS Con                                         | trol Register 4 (ICS_C4)                         |      |

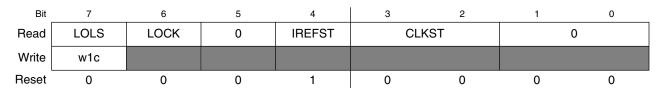

|     | 8.6.5                                  | ICS Stati                                       | us Register (ICS_S)                              | 219  |

|     | 8.6.6                                  | OSC Sta                                         | tus and Control Register (ICS_OSCSC)             |      |

| 8.7 | System clock gating control registers. |                                                 |                                                  |      |

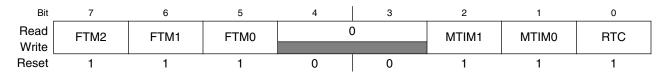

|     | 8.7.1                                  | System (                                        | Clock Gating Control 1 Register (SCG_C1)         | 222  |

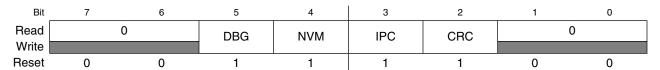

|     | 8.7.2                                  | System (                                        | Clock Gating Control 2 Register (SCG_C2)         | 223  |

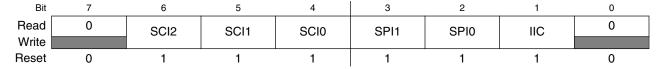

|     | 8.7.3                                  | System Clock Gating Control 3 Register (SCG_C3) |                                                  | 224  |

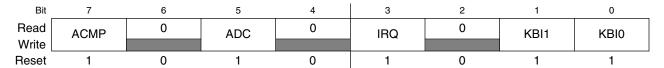

|     | 8.7.4                                  | System (                                        | Clock Gating Control 4 Register (SCG_C4)         |      |

|     |                                        |                                                 | Chapter 9 Chip configurations                    |      |

| 9.1 | Introdu                                | iction                                          |                                                  | 227  |

| 9.2 | Core m                                 | nodules                                         |                                                  | 227  |

|     | 9.2.1                                  | Central p                                       | processor unit (CPU)                             | 227  |

|     | 9.2.2                                  | Debug m                                         | nodule (DBG)                                     | 227  |

| Sec  | tion n                                                | umber      | Title                         | Page |

|------|-------------------------------------------------------|------------|-------------------------------|------|

| 9.3  | System                                                | modules    |                               | 228  |

|      | 9.3.1                                                 | Watchdo    | g (WDOG)                      |      |

| 9.4  | Clock m                                               | odule      |                               |      |

| 9.5  | Memory                                                | <i>7</i>   |                               | 230  |

|      | 9.5.1                                                 | Random-    | -access-memory (RAM)          | 230  |

|      | 9.5.2                                                 | Non-vola   | atile memory (NVM)            | 230  |

| 9.6  | Power n                                               | nodules    |                               | 230  |

| 9.7  | Security                                              | ·          |                               | 231  |

|      | 9.7.1                                                 | Cyclic re  | edundancy check (CRC)         | 231  |

| 9.8  | Timers                                                |            |                               | 233  |

|      | 9.8.1                                                 | FlexTime   | er module (FTM)               | 233  |

|      |                                                       | 9.8.1.1    | FTM0 interconnection          | 235  |

|      |                                                       | 9.8.1.2    | FTM1 interconnection          | 235  |

|      |                                                       | 9.8.1.3    | FTM2 interconnection          | 235  |

|      |                                                       | 9.8.1.4    | FTM registers                 | 235  |

|      | 9.8.2                                                 | 8-bit mod  | dulo timer (MTIM)             | 237  |

|      |                                                       | 9.8.2.1    | MTIM0 as ADC hardware trigger |      |

|      | 9.8.3 Real-time counter (RTC)                         |            |                               |      |

| 9.9  | Communication interfaces.                             |            | 241                           |      |

|      | 9.9.1                                                 | Serial con | mmunications interface (SCI)  | 241  |

|      |                                                       | 9.9.1.1    | SCI0 infrared functions       | 243  |

|      | 9.9.2 8-Bit Serial Peripheral Interface (8-bit SPI)   |            |                               |      |

|      | 9.9.3 16-bit serial peripheral interface (16-bit SPI) |            | 245                           |      |

|      | 9.9.4                                                 | Inter-Inte | egrated Circuit (I2C)         | 247  |

| 9.10 | Analog.                                               |            |                               | 249  |

|      | 9.10.1                                                | Analog-to  | o-digital converter (ADC)     | 249  |

|      |                                                       | 9.10.1.1   | ADC channel assignments       |      |

|      |                                                       | 9.10.1.2   | Alternate clock               |      |

|      |                                                       | 9.10.1.3   | Hardware trigger              |      |

|      |                                                       |            |                               |      |

| Section number |         | umber       | Title                                            | Page |

|----------------|---------|-------------|--------------------------------------------------|------|

|                |         | 9.10.1.4    | Temperature sensor                               | 252  |

|                | 9.10.2  | Analog co   | comparator (ACMP)                                | 253  |

|                |         | 9.10.2.1    | ACMP configuration information.                  | 256  |

|                |         | 9.10.2.2    | ACMP in stop3 mode                               | 256  |

|                |         | 9.10.2.3    | ACMP to FTM configuration information            | 256  |

|                |         | 9.10.2.4    | ACMP for SCI0 RXD filter                         | 256  |

| 9.11           | Human   | -machine ir | nterfaces HMI                                    | 257  |

|                | 9.11.1  | Keyboard    | d interrupts (KBI)                               | 257  |

|                |         |             | Chapter 10<br>Central processor unit             |      |

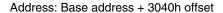

| 10.1           | Introdu | ction       |                                                  | 259  |

|                | 10.1.1  | Features    |                                                  | 259  |

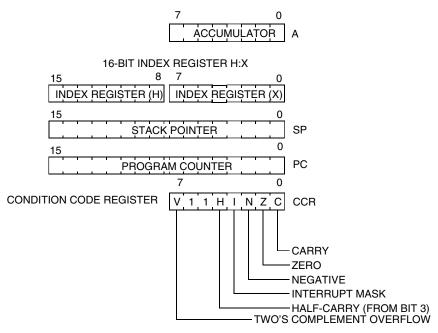

| 10.2           | Program | nmer's Mod  | del and CPU Registers                            |      |

|                | 10.2.1  | Accumula    | lator (A)                                        |      |

|                | 10.2.2  | Index Re    | gister (H:X)                                     | 261  |

|                | 10.2.3  | Stack Poi   | inter (SP)                                       | 261  |

|                | 10.2.4  | Program     | Counter (PC)                                     |      |

|                | 10.2.5  | Condition   | n Code Register (CCR)                            |      |

| 10.3           | Address | sing Modes  | s                                                |      |

|                | 10.3.1  | Inherent A  | Addressing Mode (INH)                            | 264  |

|                | 10.3.2  | Relative A  | Addressing Mode (REL)                            | 264  |

|                | 10.3.3  | Immediat    | te Addressing Mode (IMM)                         | 264  |

|                | 10.3.4  | Direct Ad   | ddressing Mode (DIR)                             | 265  |

|                | 10.3.5  | Extended    | d Addressing Mode (EXT)                          | 265  |

|                | 10.3.6  | Indexed A   | Addressing Mode                                  |      |

|                |         | 10.3.6.1    | Indexed, No Offset (IX)                          | 266  |

|                |         | 10.3.6.2    | Indexed, No Offset with Post Increment (IX+)     | 266  |

|                |         | 10.3.6.3    | Indexed, 8-Bit Offset (IX1)                      | 266  |

|                |         | 10.3.6.4    | Indexed, 8-Bit Offset with Post Increment (IX1+) |      |

| Section number |           | ımber      | Title                                   | Page |

|----------------|-----------|------------|-----------------------------------------|------|

|                |           | 10.3.6.5   | Indexed, 16-Bit Offset (IX2)            | 267  |

|                |           | 10.3.6.6   | SP-Relative, 8-Bit Offset (SP1)         | 267  |

|                |           | 10.3.6.7   | SP-Relative, 16-Bit Offset (SP2)        |      |

|                | 10.3.7    | Memory     | to memory Addressing Mode               | 268  |

|                |           | 10.3.7.1   | Direct to Direct                        | 268  |

|                |           | 10.3.7.2   | Immediate to Direct                     |      |

|                |           | 10.3.7.3   | Indexed to Direct, Post Increment       | 268  |

|                |           | 10.3.7.4   | Direct to Indexed, Post-Increment       | 269  |

| 10.4           | Operation | on modes   |                                         | 269  |

|                | 10.4.1    | Stop mod   | le                                      |      |

|                | 10.4.2    | Wait mod   | le                                      | 269  |

|                | 10.4.3    | Backgrou   | and mode                                | 270  |

|                | 10.4.4    | Security 1 | mode                                    | 271  |

| 10.5           | HCS08     | V6 Opcode  | es                                      | 273  |

| 10.6           | Special   | Operations | S                                       | 273  |

|                | 10.6.1    | Reset Sec  | quence                                  |      |

|                | 10.6.2    | Interrupt  | Sequence                                | 273  |

| 10.7           | Instructi | on Set Sur | mmary                                   | 274  |

|                |           |            | Chapter 11<br>Keyboard Interrupts (KBI) |      |

| 11.1           | Introduc  | tion       |                                         | 287  |

|                | 11.1.1    | Features   |                                         | 287  |

|                | 11.1.2    | Modes of   | f Operation                             |      |

|                |           | 11.1.2.1   | KBI in Wait mode                        | 287  |

|                |           | 11.1.2.2   | KBI in Stop modes                       | 288  |

|                |           | 11.1.2.3   | KBI in Active Background mode           |      |

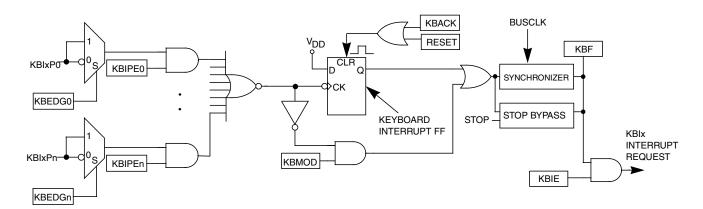

|                | 11.1.3    | Block Dia  | agram                                   | 288  |

| 11.2           | External  | signals de | escription                              | 289  |

| 11.3           | Register  | definition |                                         | 289  |

|                |           |            |                                         |      |

| Sec  | tion n  | umber Title                               | Page |

|------|---------|-------------------------------------------|------|

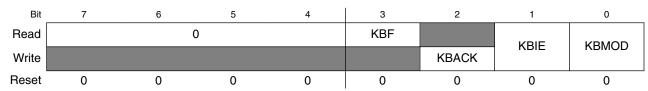

| 11.4 | Memor   | y Map and Registers                       | 289  |

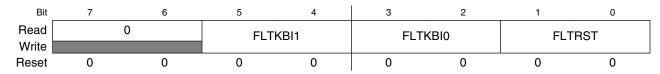

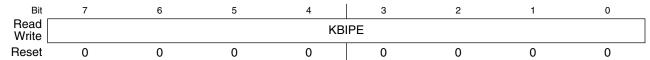

|      | 11.4.1  | KBI Status and Control Register (KBIx_SC) | 290  |

|      | 11.4.2  | KBI Pin Enable Register (KBIx_PE)         | 291  |

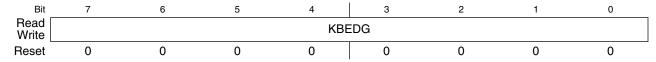

|      | 11.4.3  | KBI Edge Select Register (KBIx_ES)        |      |

| 11.5 | Functio | onal Description                          |      |

|      | 11.5.1  | Edge-only sensitivity                     |      |

|      | 11.5.2  | Edge and level sensitivity                |      |

|      | 11.5.3  | KBI Pullup Resistor                       |      |

|      | 11.5.4  | KBI initialization                        |      |

|      |         | Chapter 12<br>FlexTimer Module (FTM)      |      |

| 12.1 | Introdu | ction                                     |      |

|      | 12.1.1  | FlexTimer philosophy                      |      |

|      | 12.1.2  | Features                                  | 296  |

|      | 12.1.3  | Modes of operation                        |      |

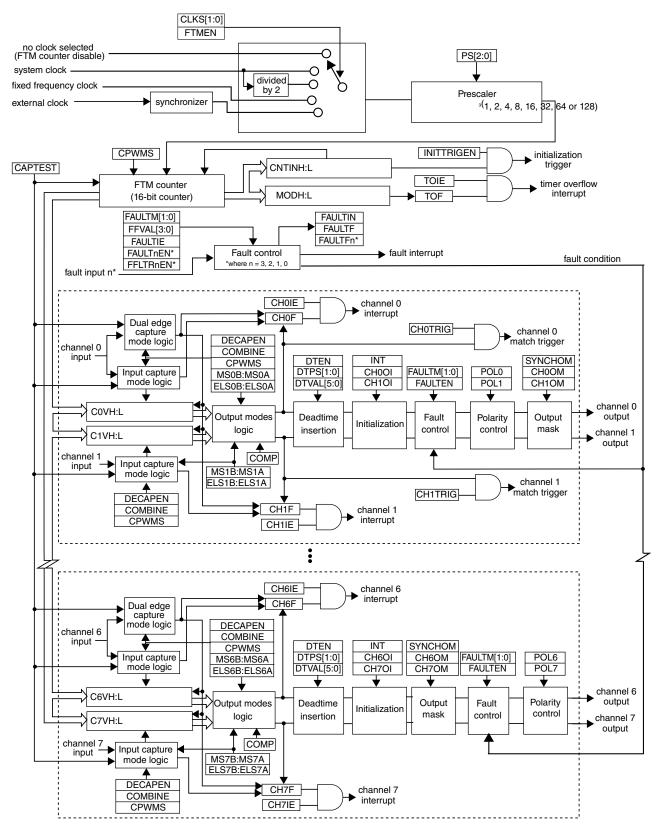

|      | 12.1.4  | Block diagram                             | 297  |

| 12.2 | Signal  | description                               | 300  |

|      | 12.2.1  | EXTCLK — FTM external clock               | 300  |

|      | 12.2.2  | CHn — FTM channel (n) I/O pin             |      |

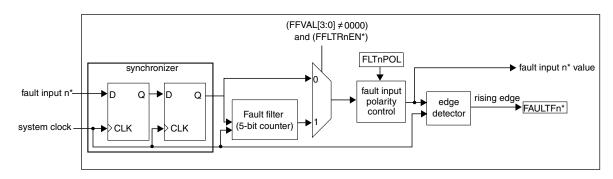

|      | 12.2.3  | FAULTj — FTM fault input                  | 300  |

| 12.3 | Memor   | y map and register definition             | 301  |

|      | 12.3.1  | Module memory map                         | 301  |

|      | 12.3.2  | Register descriptions.                    | 301  |

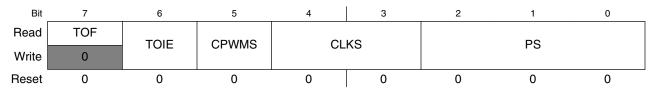

|      | 12.3.3  | Status and Control (FTMx_SC)              |      |

|      | 12.3.4  | Counter High (FTMx_CNTH)                  | 306  |

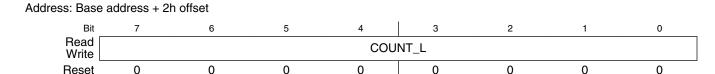

|      | 12.3.5  | Counter Low (FTMx_CNTL)                   |      |

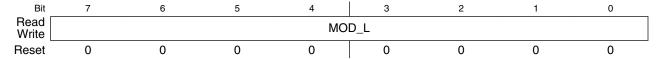

|      | 12.3.6  | Modulo High (FTMx_MODH)                   |      |

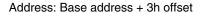

|      | 12.3.7  | Modulo Low (FTMx_MODL)                    |      |

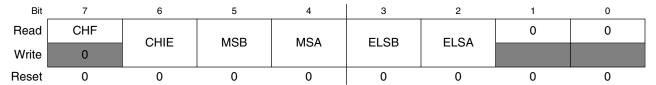

|      | 12.3.8  | Channel Status and Control (FTMx_CnSC)    |      |

| Section r     | number Title                                      | Page |

|---------------|---------------------------------------------------|------|

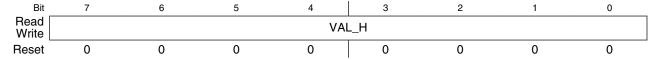

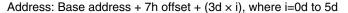

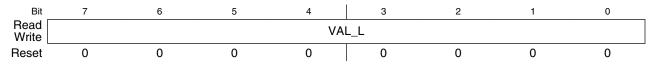

| 12.3.9        | Channel Value High (FTMx_CnVH)                    | 311  |

| 12.3.10       | O Channel Value Low (FTMx_CnVL)                   | 312  |

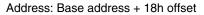

| 12.3.11       | 1 Counter Initial Value High (FTMx_CNTINH)        | 312  |

| 12.3.12       | 2 Counter Initial Value Low (FTMx_CNTINL)         | 313  |

| 12.3.13       | 3 Capture and Compare Status (FTMx_STATUS)        | 313  |

| 12.3.14       | 4 Features Mode Selection (FTMx_MODE)             |      |

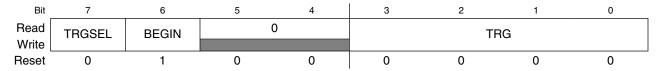

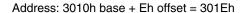

| 12.3.15       | 5 Synchronization (FTMx_SYNC)                     | 316  |

| 12.3.16       | 6 Initial State for Channel Output (FTMx_OUTINIT) | 318  |

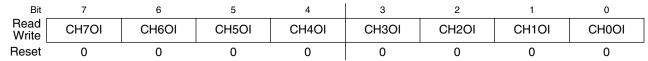

| 12.3.17       | 7 Output Mask (FTMx_OUTMASK)                      | 320  |

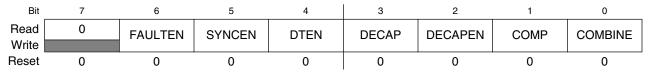

| 12.3.18       | 8 Function for Linked Channels (FTMx_COMBINEn)    |      |

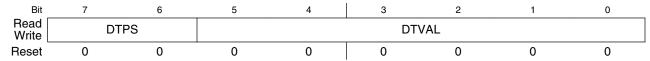

| 12.3.19       | 9 Deadtime Insertion Control (FTMx_DEADTIME)      | 323  |

| 12.3.20       | 0 External Trigger (FTMx_EXTTRIG)                 |      |

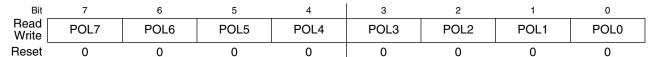

| 12.3.2        | 1 Channels Polarity (FTMx_POL)                    | 325  |

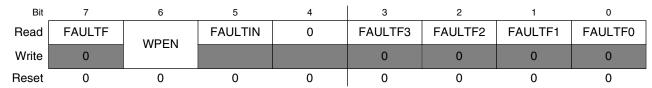

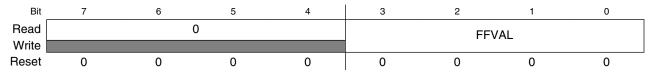

| 12.3.22       | 2 Fault Mode Status (FTMx_FMS)                    | 327  |

| 12.3.23       | 3 Input Capture Filter Control (FTMx_FILTERn)     |      |

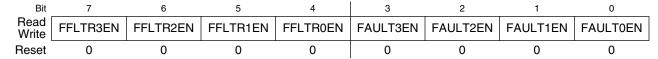

| 12.3.24       | 4 Fault Input Filter Control (FTMx_FLTFILTER)     | 329  |

| 12.3.25       | 5 Fault Input Control (FTMx_FLTCTRL)              | 330  |

| 12.4 Function | onal Description                                  | 331  |

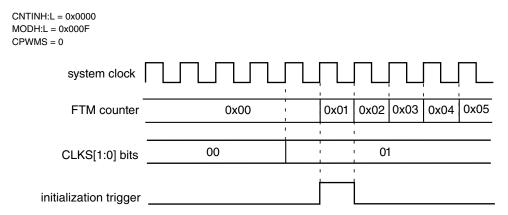

| 12.4.1        | Clock Source                                      | 332  |

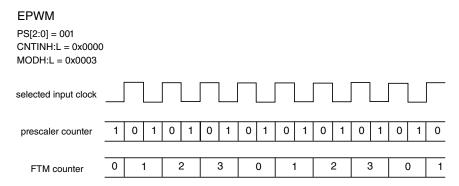

|               | 12.4.1.1 Counter Clock Source                     | 332  |

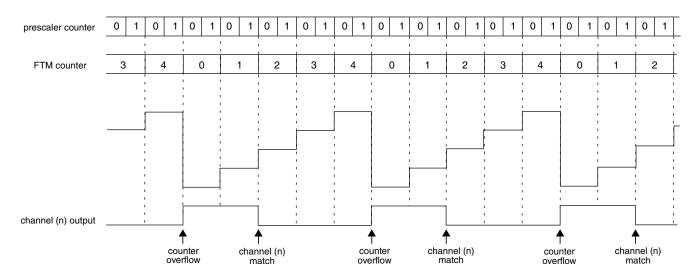

| 12.4.2        | Prescaler                                         | 333  |

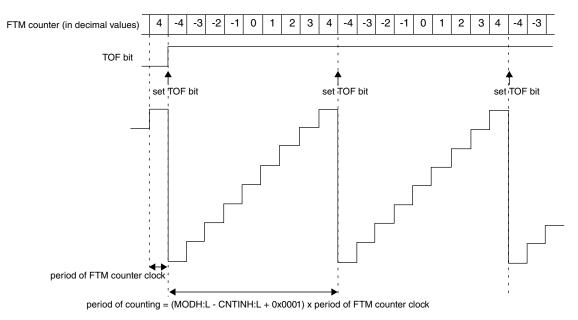

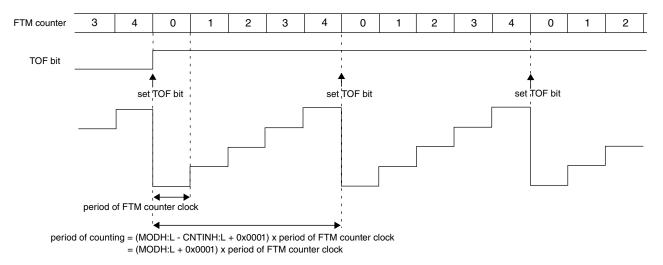

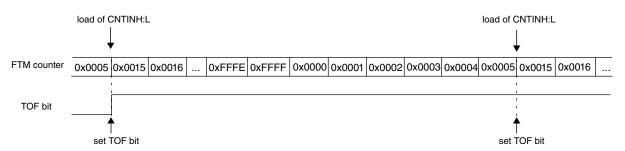

| 12.4.3        | Counter                                           | 333  |

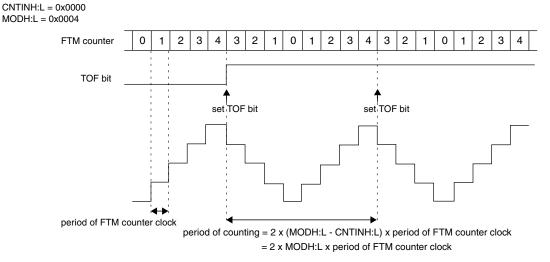

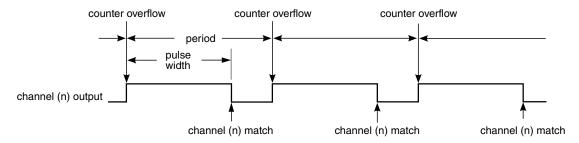

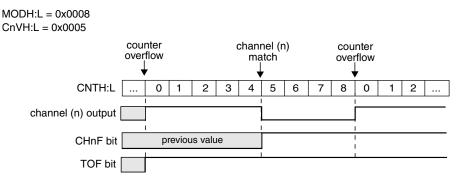

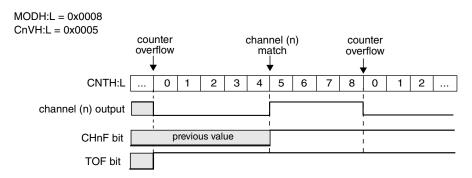

|               | 12.4.3.1 Up counting                              | 333  |

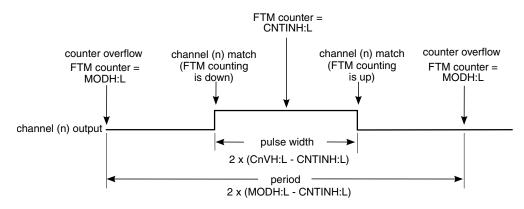

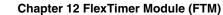

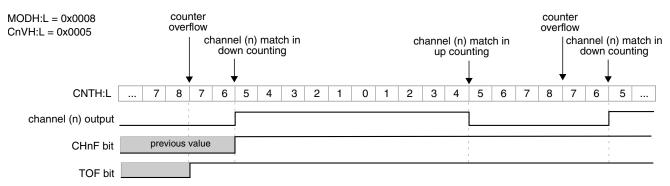

|               | 12.4.3.2 Up-down counting                         | 336  |

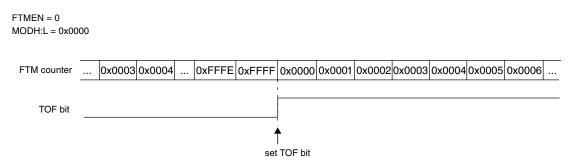

|               | 12.4.3.3 Free running counter                     | 337  |

|               | 12.4.3.4 Counter reset                            | 338  |

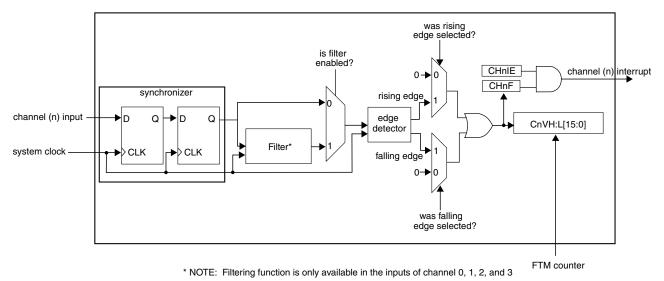

| 12.4.4        | Input capture mode                                | 338  |

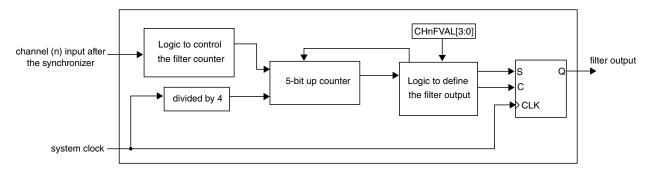

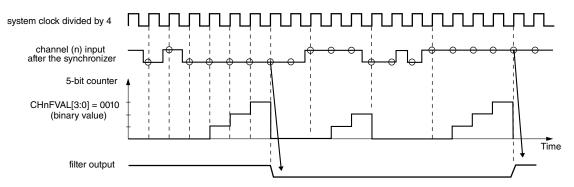

|               | 12.4.4.1 Filter for input capture mode            | 339  |

| 12.4.5        | Output compare mode                               | 340  |

|               |                                                   |      |

| Section nu | umber Title                                | Page |

|------------|--------------------------------------------|------|

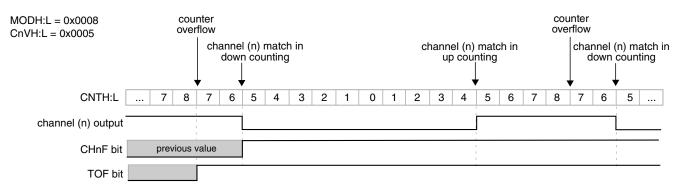

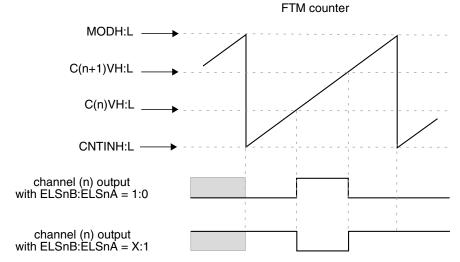

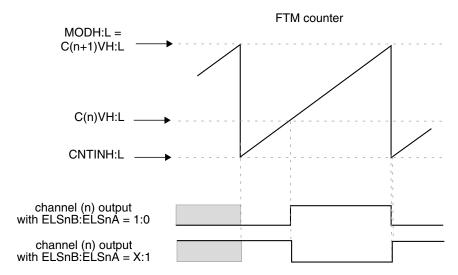

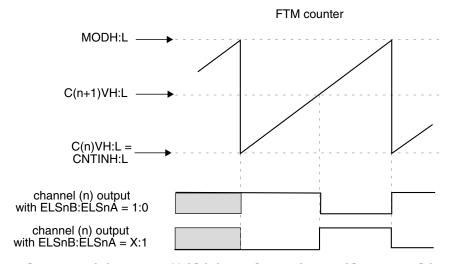

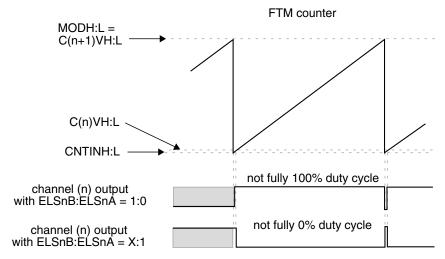

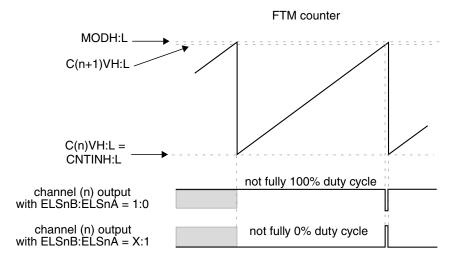

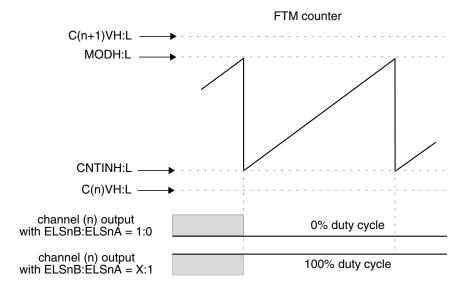

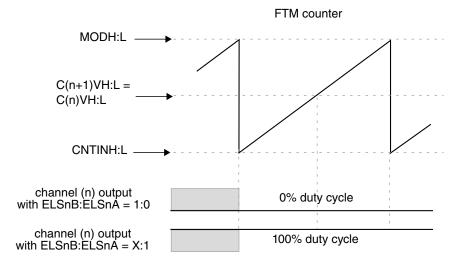

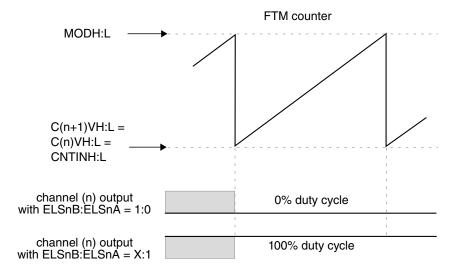

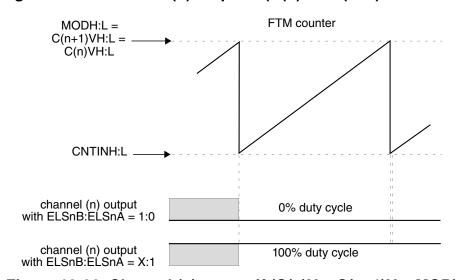

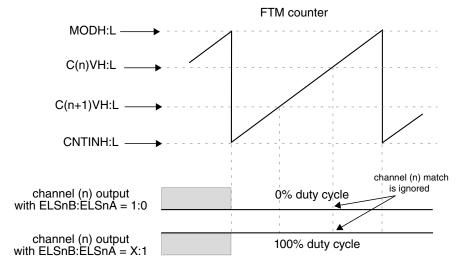

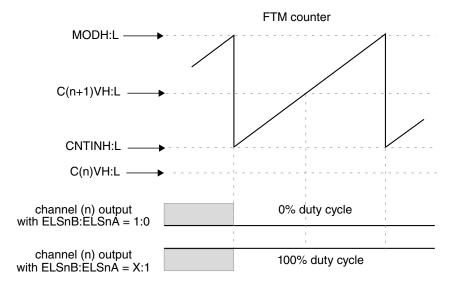

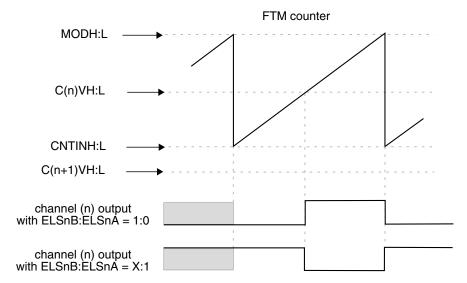

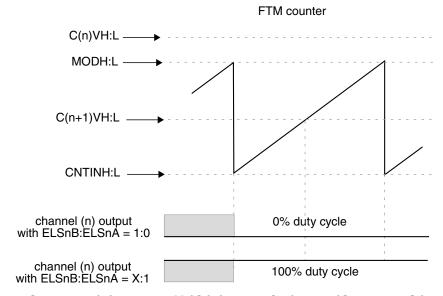

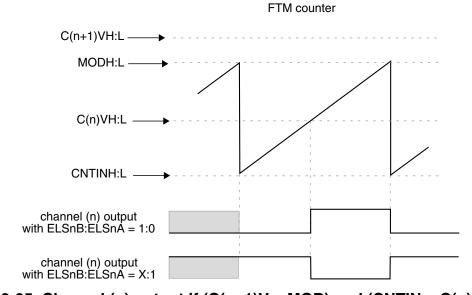

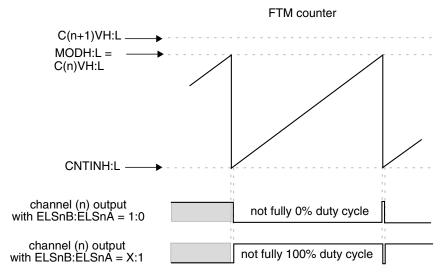

| 12.4.6     | Edge-aligned PWM (EPWM) mode               | 342  |

| 12.4.7     | Center-aligned PWM (CPWM) mode             | 344  |

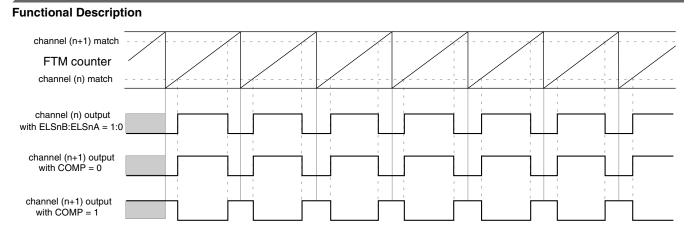

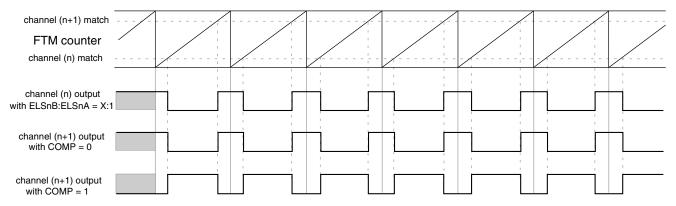

| 12.4.8     | Combine mode                               | 346  |

|            | 12.4.8.1 Asymmetrical PWM                  |      |

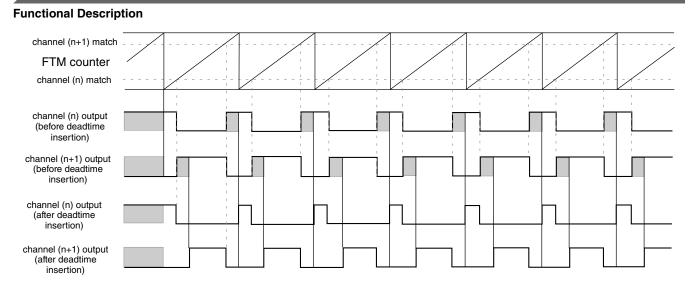

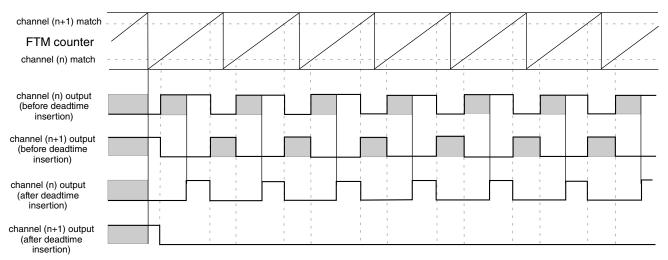

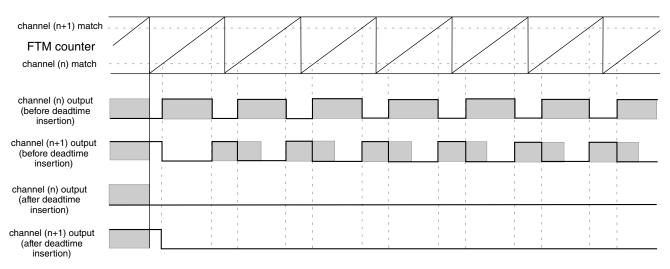

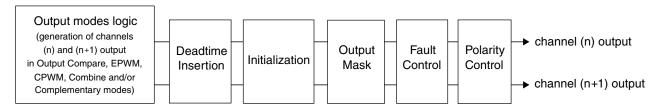

| 12.4.9     | Complementary mode                         | 353  |

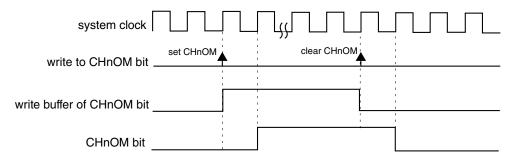

| 12.4.10    | Update of the registers with write buffers | 354  |

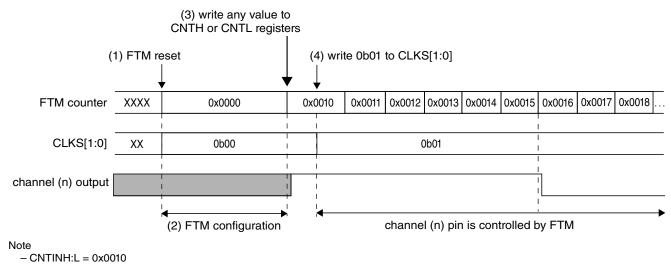

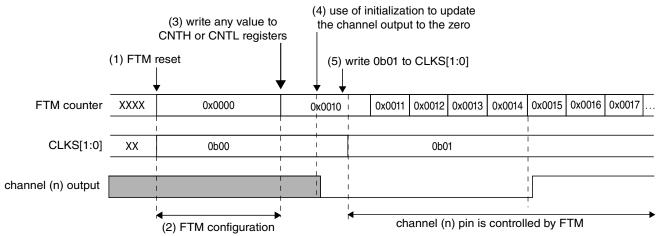

|            | 12.4.10.1 CNTINH:L registers               |      |

|            | 12.4.10.2 MODH:L registers                 | 354  |

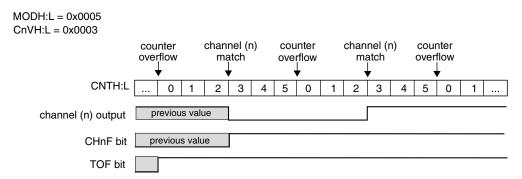

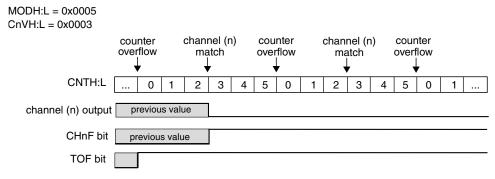

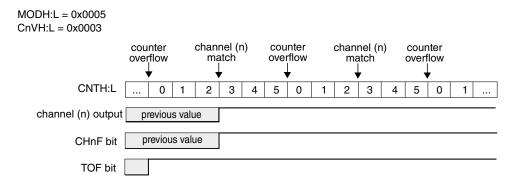

|            | 12.4.10.3 CnVH:L registers                 | 355  |

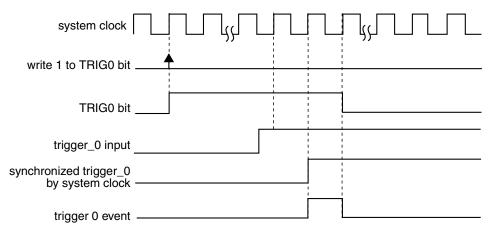

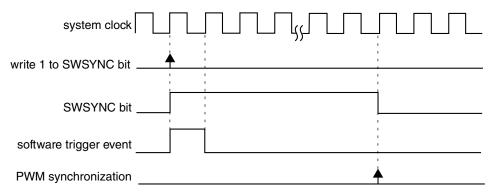

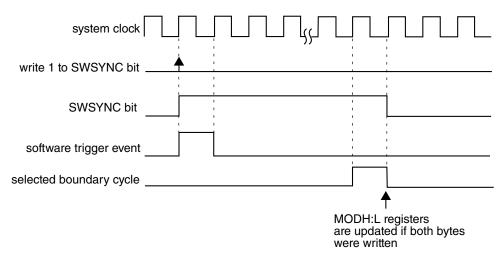

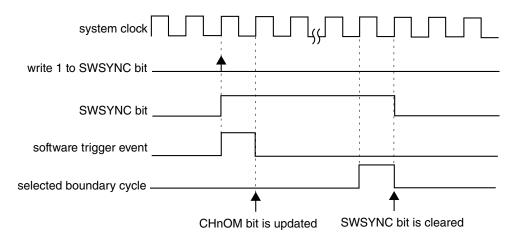

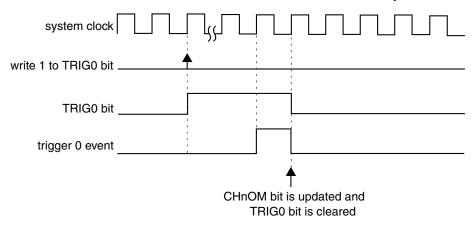

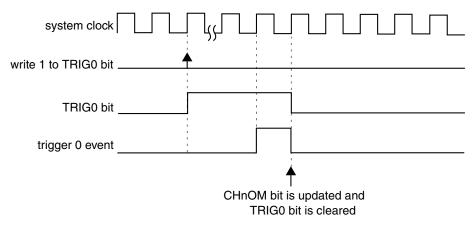

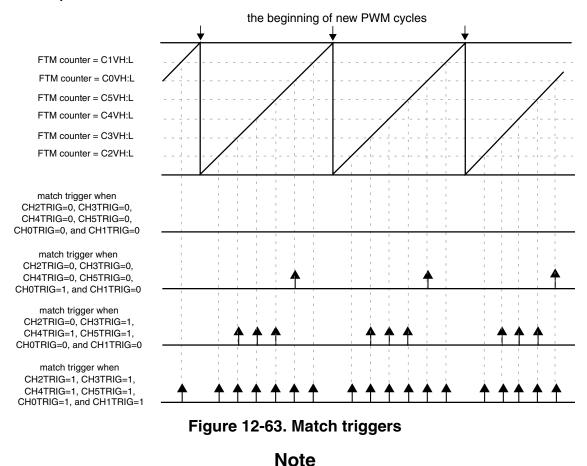

| 12.4.11    | PWM synchronization                        | 356  |

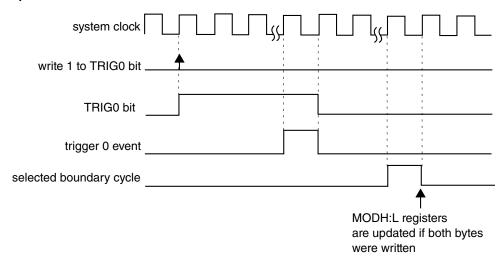

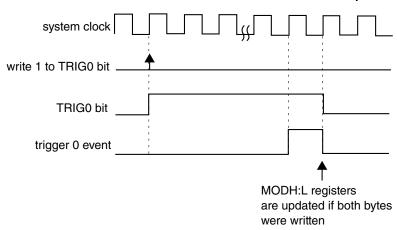

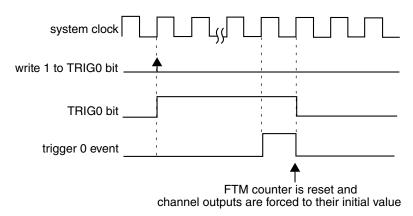

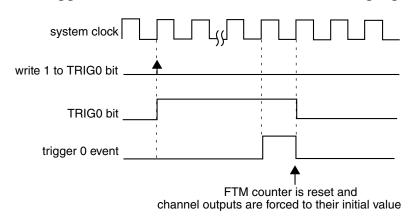

|            | 12.4.11.1 Hardware trigger                 | 356  |

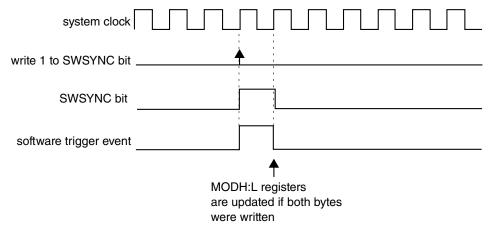

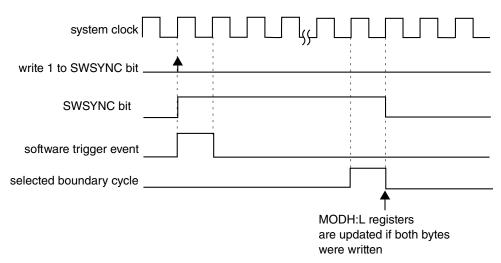

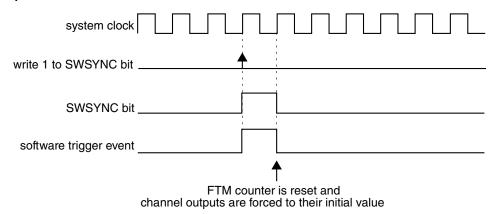

|            | 12.4.11.2 Software trigger                 | 357  |

|            | 12.4.11.3 Boundary cycle                   | 358  |

|            | 12.4.11.4 MODH:L registers synchronization | 359  |

|            | 12.4.11.5 CnVH:L registers synchronization | 361  |

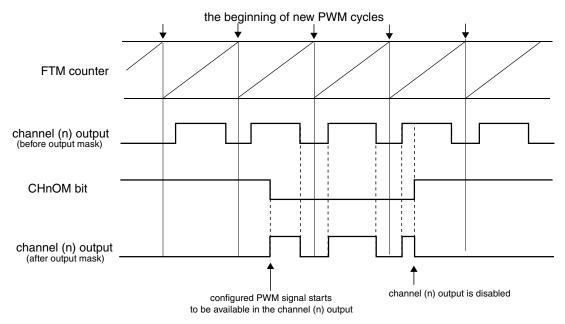

|            | 12.4.11.6 OUTMASK register synchronization | 361  |

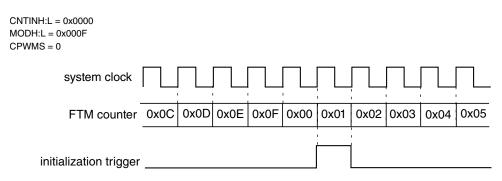

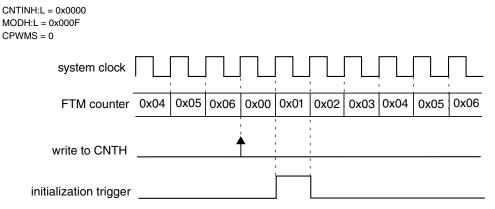

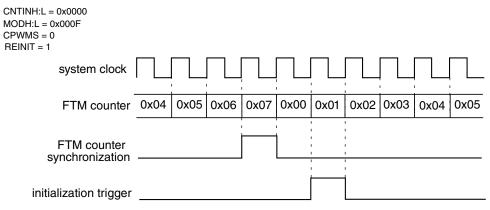

|            | 12.4.11.7 FTM counter synchronization      | 363  |

|            | 12.4.11.8 Summary of PWM synchronization   | 365  |

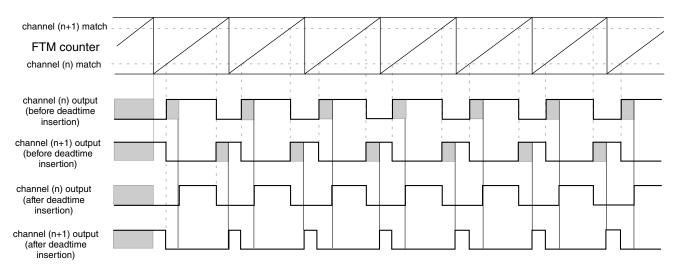

| 12.4.12    | Deadtime insertion                         | 367  |

|            | 12.4.12.1 Deadtime insertion corner cases  |      |

| 12.4.13    | Output mask                                | 369  |

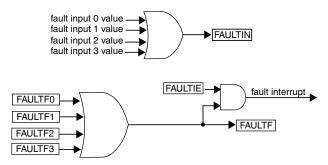

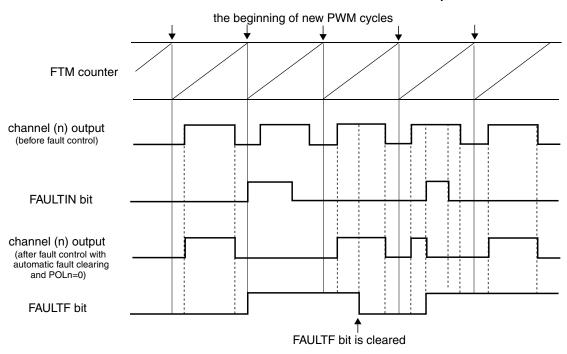

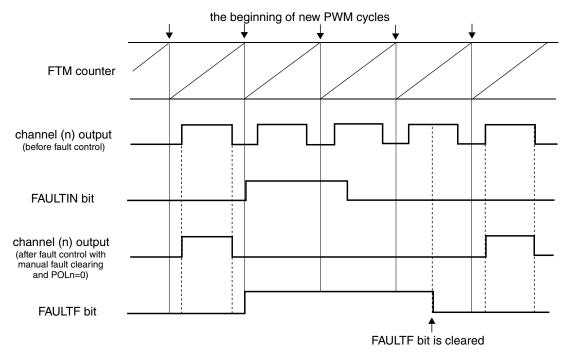

| 12.4.14    | Fault control.                             | 370  |

|            | 12.4.14.1 Automatic fault clearing         | 372  |

|            | 12.4.14.2 Manual fault clearing.           | 373  |

| 12.4.15    | Polarity control                           | 374  |

| 12.4.16    | Initialization                             | 374  |

| 12.4.17    | Features priority                          | 375  |

| 12.4.18    | Channel trigger output.                    |      |

| 12.4.19    | Initialization trigger                     | 376  |

| Sec  | tion nu  | umber Title                                 | Page |

|------|----------|---------------------------------------------|------|

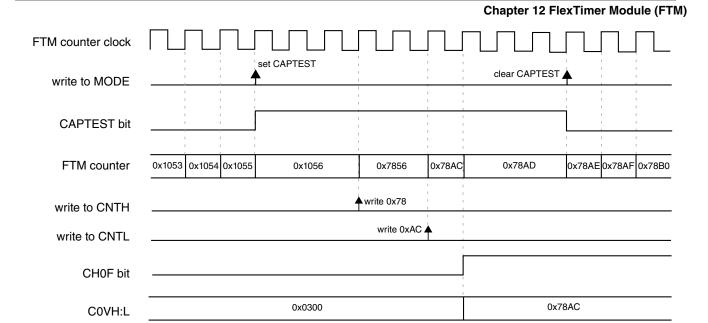

|      | 12.4.20  | Capture test mode                           | 378  |

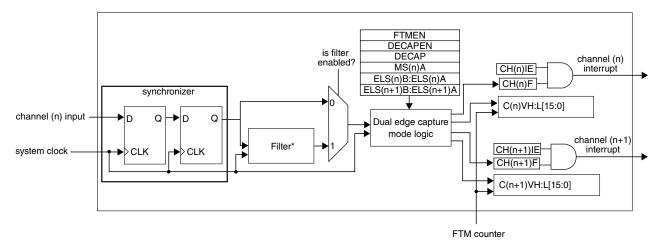

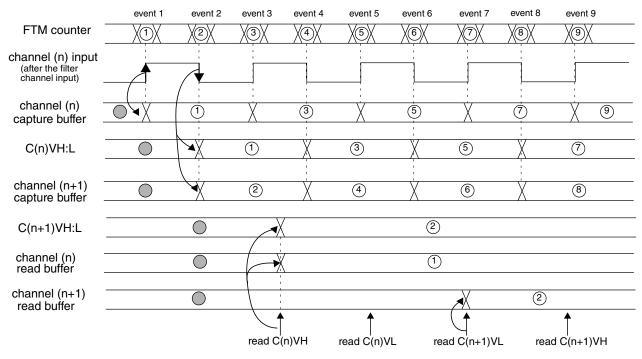

|      | 12.4.21  | Dual edge capture mode                      | 379  |

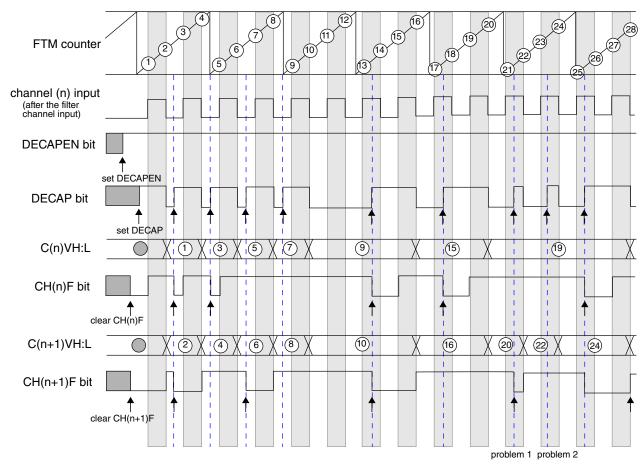

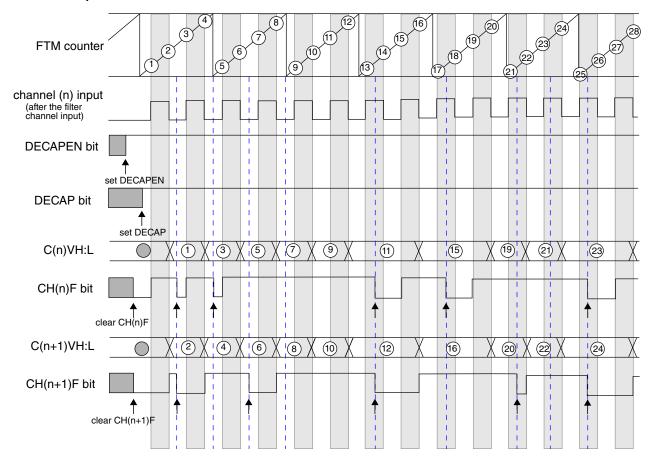

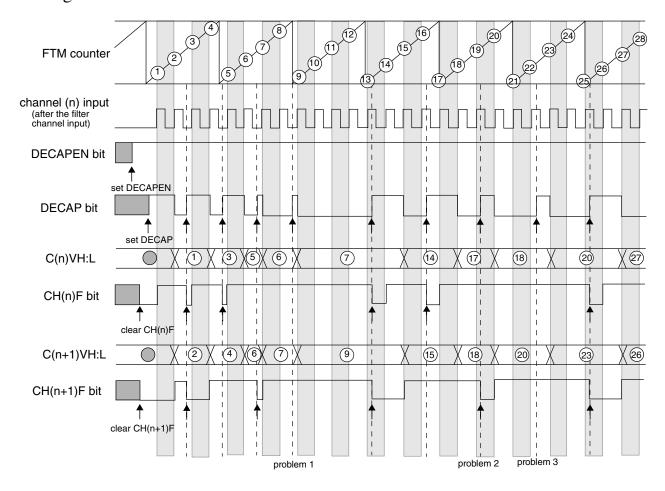

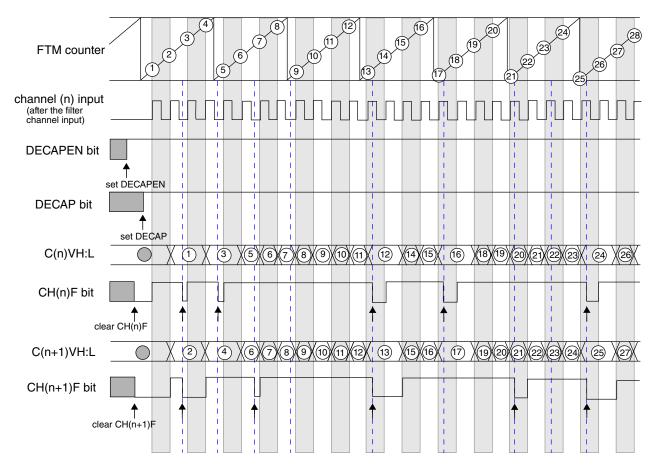

|      |          | 12.4.21.1 One-shot capture mode             | 381  |

|      |          | 12.4.21.2 Continuous capture mode           | 381  |

|      |          | 12.4.21.3 Pulse width measurement           | 382  |

|      |          | 12.4.21.4 Period measurement.               | 384  |

|      |          | 12.4.21.5 Read coherency mechanism.         | 386  |

|      | 12.4.22  | TPM emulation                               | 388  |

|      |          | 12.4.22.1 MODH:L and CnVH:L synchronization | 388  |

|      |          | 12.4.22.2 Free running counter              | 388  |

|      |          | 12.4.22.3 Write to SC                       | 388  |

|      |          | 12.4.22.4 Write to CnSC                     | 388  |

|      | 12.4.23  | BDM mode                                    | 388  |

| 12.5 | Reset ov | verview                                     | 389  |

| 12.6 | FTM Int  | terrupts                                    | 391  |

|      | 12.6.1   | Timer overflow interrupt                    | 391  |

|      | 12.6.2   | Channel (n) interrupt                       | 391  |

|      | 12.6.3   | Fault interrupt.                            | 391  |

|      |          | Chapter 13                                  |      |

|      |          | 8-bit modulo timer (MTIM)                   |      |

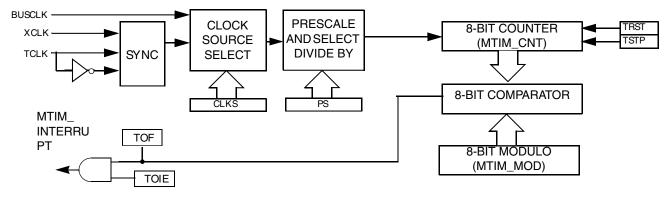

| 13.1 | Introduc | tion                                        | 393  |

|      |          |                                             |      |

| 13.3 | Modes o  | of operation                                | 393  |

|      | 13.3.1   | MTIM in wait mode                           | 394  |

|      | 13.3.2   | MTIM in stop mode                           | 394  |

|      | 13.3.3   | MTIM in active background mode              | 394  |

| 13.4 | Block di | agram                                       | 394  |

|      |          | signal description.                         |      |

| 13.6 | Register | definition                                  | 395  |

| Sec  | tion n    | umber Title                                      | Page |

|------|-----------|--------------------------------------------------|------|

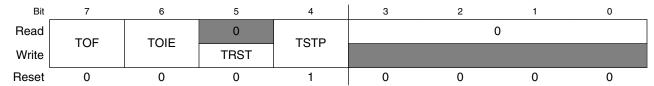

|      | 13.6.1    | MTIM Status and Control Register (MTIMx_SC)      |      |

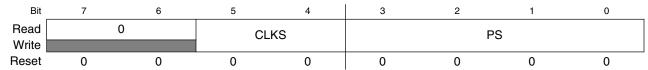

|      | 13.6.2    | MTIM Clock Configuration Register (MTIMx_CLK)    | 397  |

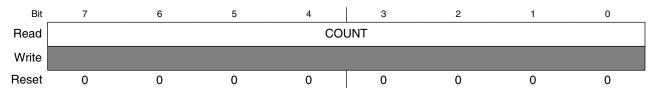

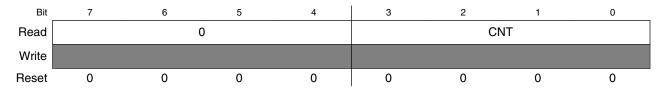

|      | 13.6.3    | MTIM Counter Register (MTIMx_CNT)                | 398  |

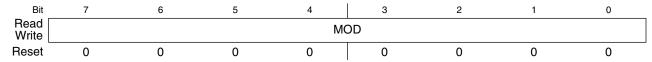

|      | 13.6.4    | MTIM Modulo Register (MTIMx_MOD)                 | 398  |

| 13.7 | Function  | nal description                                  | 398  |

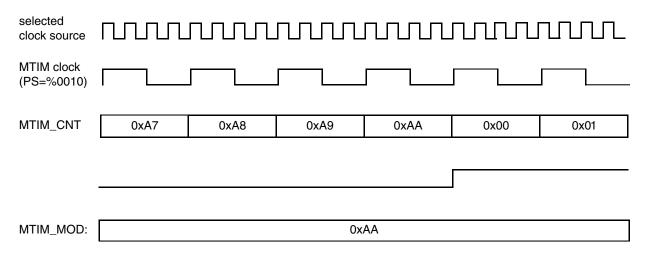

|      | 13.7.1    | MTIM operation example                           | 400  |

|      |           | Chapter 14<br>Real-time counter (RTC)            |      |

| 14.1 | Introduc  | ction                                            | 401  |

| 14.2 | Feature   | S                                                | 401  |

|      | 14.2.1    | Modes of operation                               | 401  |

|      |           | 14.2.1.1 Wait mode                               | 401  |

|      |           | 14.2.1.2 Stop modes                              | 402  |

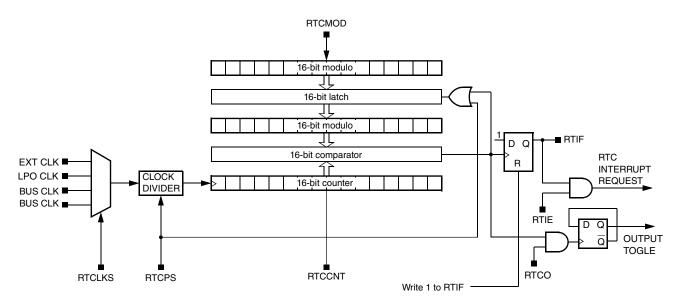

|      | 14.2.2    | Block diagram                                    | 402  |

| 14.3 | Externa   | l signal description                             | 402  |

| 14.4 | Register  | definition                                       | 403  |

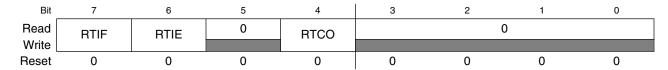

|      | 14.4.1    | RTC Status and Control Register 1 (RTC_SC1)      | 403  |

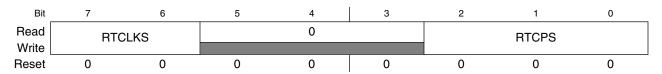

|      | 14.4.2    | RTC Status and Control Register 2 (RTC_SC2)      | 404  |

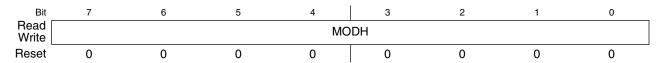

|      | 14.4.3    | RTC Modulo Register: High (RTC_MODH)             | 405  |

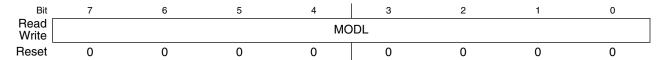

|      | 14.4.4    | RTC Modulo Register: Low (RTC_MODL)              | 405  |

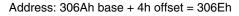

|      | 14.4.5    | RTC Counter Register: High (RTC_CNTH)            | 406  |

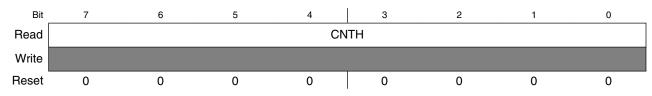

|      | 14.4.6    | RTC Counter Register: Low (RTC_CNTL)             | 406  |

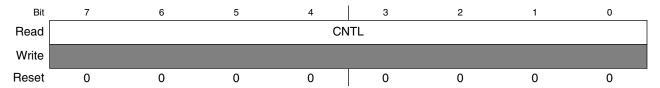

| 14.5 | Function  | nal description                                  | 407  |

|      | 14.5.1    | RTC operation example                            | 408  |

| 14.6 | Initializ | ation/application information                    | 409  |

|      |           | Chapter 15 Serial communications interface (SCI) |      |

| 15.1 | Introduc  | ction                                            | 411  |

|      | 15.1.1    | Features                                         | 411  |

| Sec  | tion n   | umber        | Title                          | Page |

|------|----------|--------------|--------------------------------|------|

|      | 15.1.2   | Modes of     | operation                      | 411  |

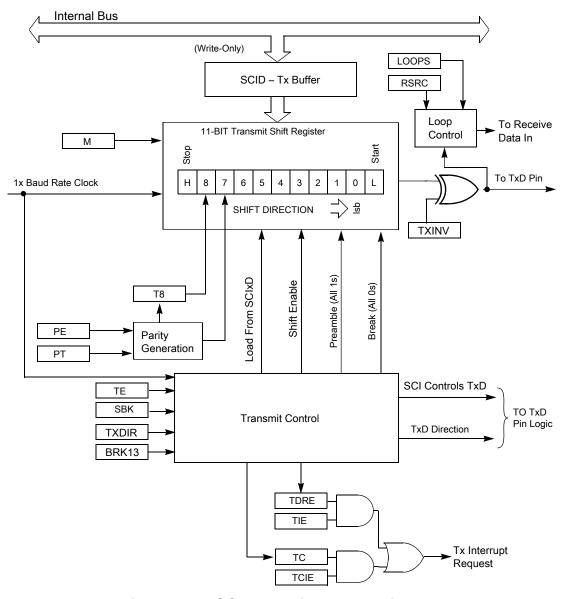

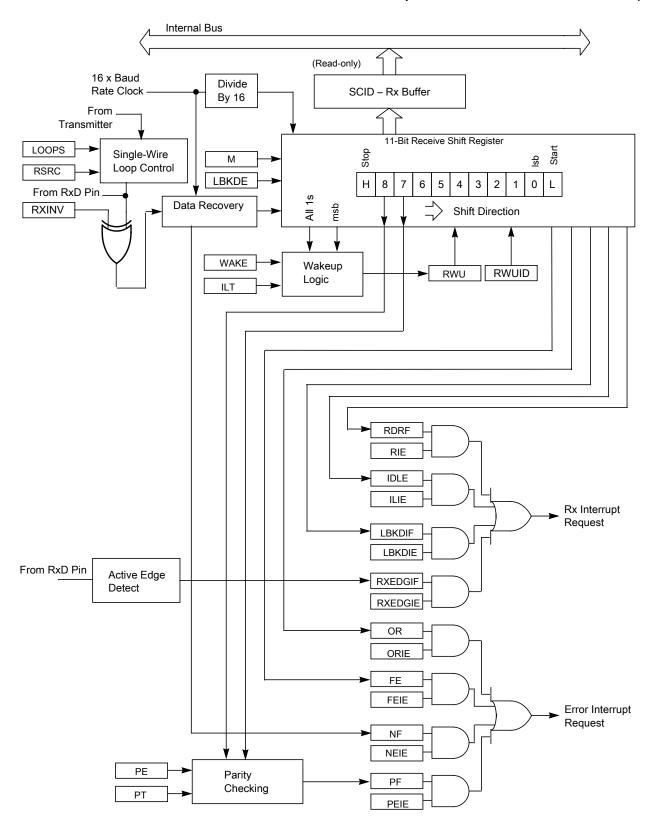

|      | 15.1.3   | Block dia    | gramgram                       | 412  |

| 15.2 | SCI sign | nal descript | ions                           | 414  |

|      | 15.2.1   | Detailed s   | signal descriptions            | 414  |

| 15.3 | Register | definition   |                                | 414  |

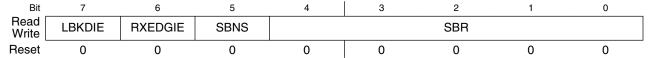

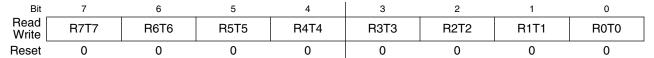

|      | 15.3.1   | SCI Baud     | Rate Register: High (SCIx_BDH) | 415  |

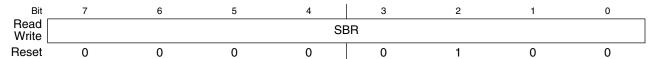

|      | 15.3.2   | SCI Baud     | Rate Register: Low (SCIx_BDL)  | 416  |

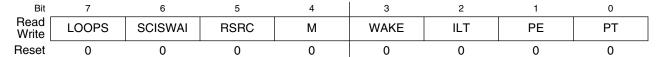

|      | 15.3.3   | SCI Contr    | rol Register 1 (SCIx_C1)       | 417  |

|      | 15.3.4   | SCI Contr    | rol Register 2 (SCIx_C2)       | 418  |

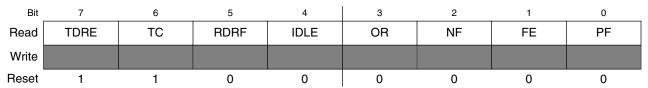

|      | 15.3.5   | SCI Statu    | s Register 1 (SCIx_S1)         | 419  |

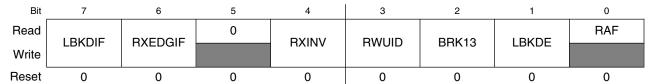

|      | 15.3.6   | SCI Statu    | s Register 2 (SCIx_S2)         |      |

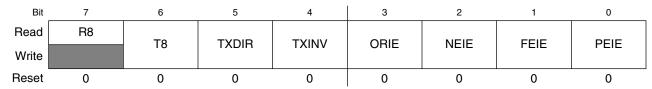

|      | 15.3.7   | SCI Contr    | rol Register 3 (SCIx_C3)       | 423  |

|      | 15.3.8   | SCI Data     | Register (SCIx_D)              | 424  |

| 15.4 | Function | nal descript | tion                           | 425  |

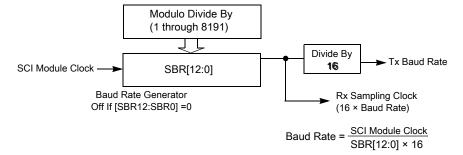

|      | 15.4.1   | Baud rate    | generation                     |      |

|      | 15.4.2   | Transmitt    | er functional description      | 426  |

|      |          | 15.4.2.1     | Send break and queued idle     |      |

|      | 15.4.3   | Receiver     | functional description         |      |

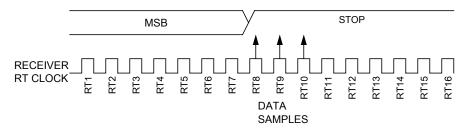

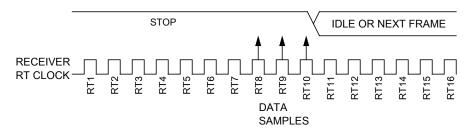

|      |          | 15.4.3.1     | Data sampling technique.       | 428  |

|      |          | 15.4.3.2     | Receiver wake-up operation     | 429  |

|      | 15.4.4   | Interrupts   | and status flags               |      |

|      | 15.4.5   | Baud rate    | tolerance                      | 431  |

|      |          | 15.4.5.1     | Slow data tolerance            | 432  |

|      |          | 15.4.5.2     | Fast data tolerance            | 433  |

|      | 15.4.6   | Additiona    | al SCI functions               | 434  |

|      |          | 15.4.6.1     | 8- and 9-bit data modes        | 434  |

|      |          | 15.4.6.2     | Stop mode operation            | 434  |

|      |          | 15.4.6.3     | Loop mode                      |      |

|      |          | 15.4.6.4     | Single-wire operation          | 435  |

|      |          |              |                                |      |

### Chapter 16

| 8-Bit Serial | <b>Peripheral</b> | Interface | (8-bit | SPI) |

|--------------|-------------------|-----------|--------|------|

| 16.1 | Introduction. |                                            | 437 |

|------|---------------|--------------------------------------------|-----|

|      | 16.1.1        | Features                                   | 437 |

|      | 16.1.2        | Modes of Operation                         | 438 |

|      | 16.1.3        | Block Diagrams                             | 438 |

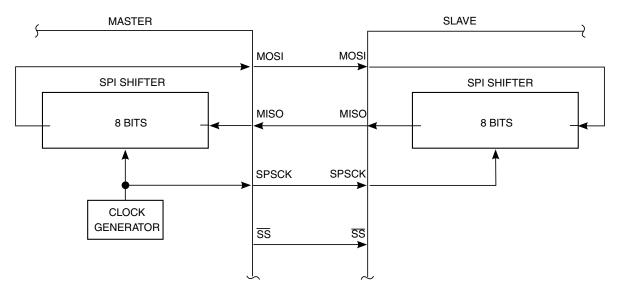

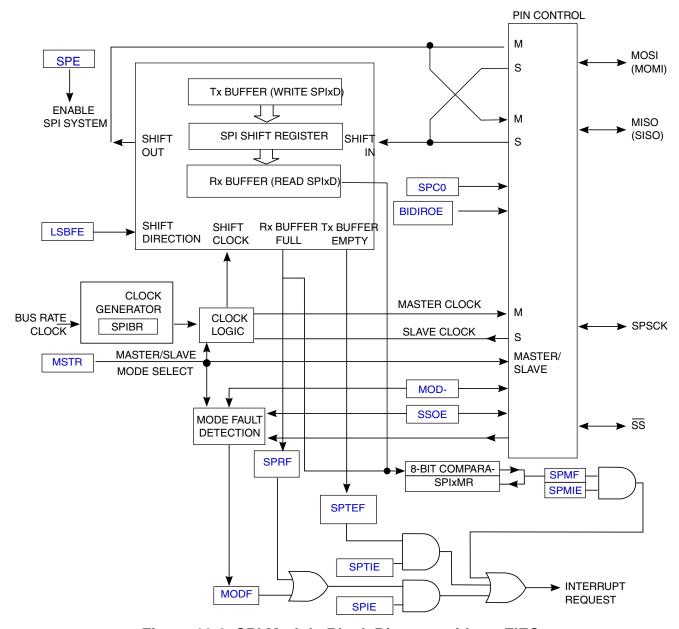

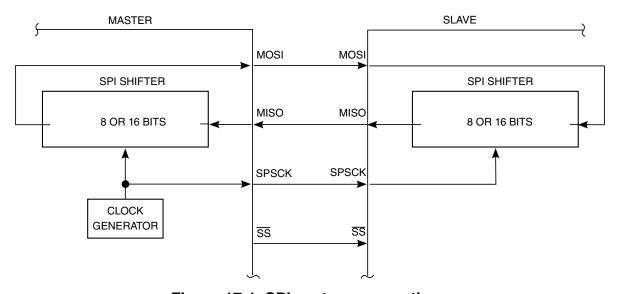

|      |               | 16.1.3.1 SPI System Block Diagram          | 439 |

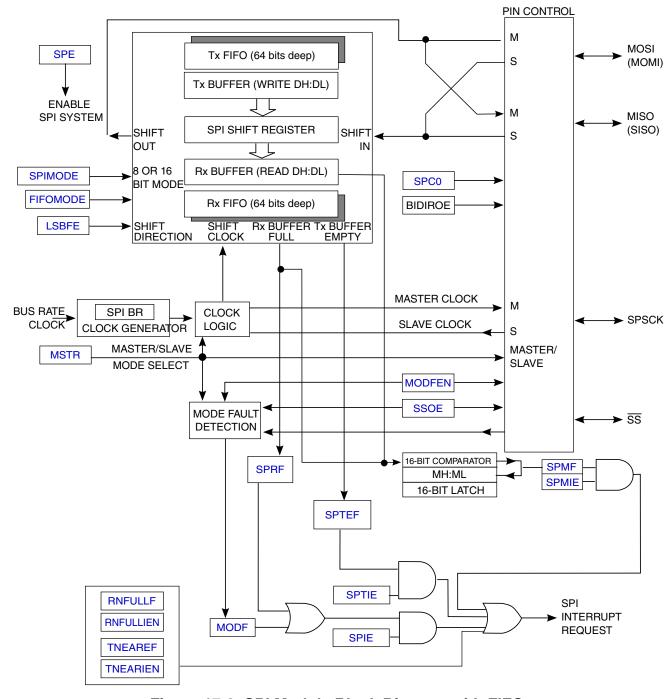

|      |               | 16.1.3.2 SPI Module Block Diagram          | 439 |

| 16.2 | Externa       | l Signal Description                       | 440 |

|      | 16.2.1        | SPSCK — SPI Serial Clock                   | 441 |

|      | 16.2.2        | MOSI — Master Data Out, Slave Data In      | 441 |

|      | 16.2.3        | MISO — Master Data In, Slave Data Out      | 441 |

|      | 16.2.4        | SS — Slave Select                          | 441 |

| 16.3 | Register      | r Definition                               | 442 |

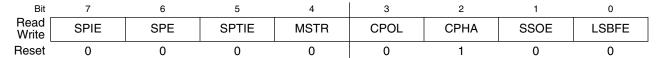

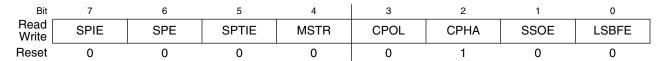

|      | 16.3.1        | SPI control register 1 (SPLx_C1)           | 442 |

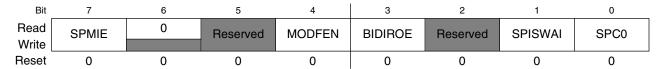

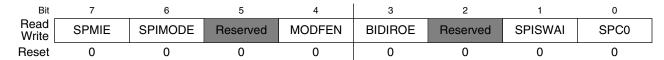

|      | 16.3.2        | SPI control register 2 (SPIx_C2)           | 444 |

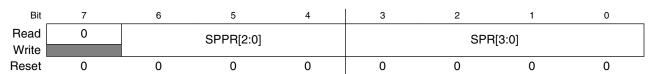

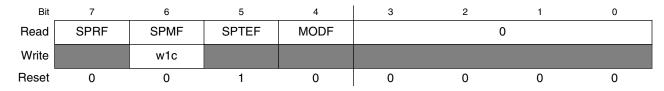

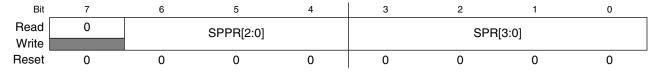

|      | 16.3.3        | SPI baud rate register (SPIx_BR)           | 445 |

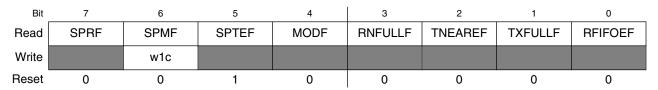

|      | 16.3.4        | SPI status register (SPIx_S)               | 446 |

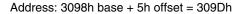

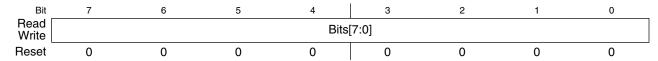

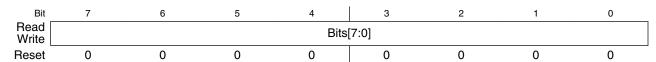

|      | 16.3.5        | SPI data register (SPIx_D)                 | 447 |

|      | 16.3.6        | SPI match register (SPIx_M)                | 448 |

| 16.4 | Function      | nal Description                            | 448 |

|      | 16.4.1        | General                                    | 448 |

|      | 16.4.2        | Master Mode                                | 449 |

|      | 16.4.3        | Slave Mode                                 | 450 |

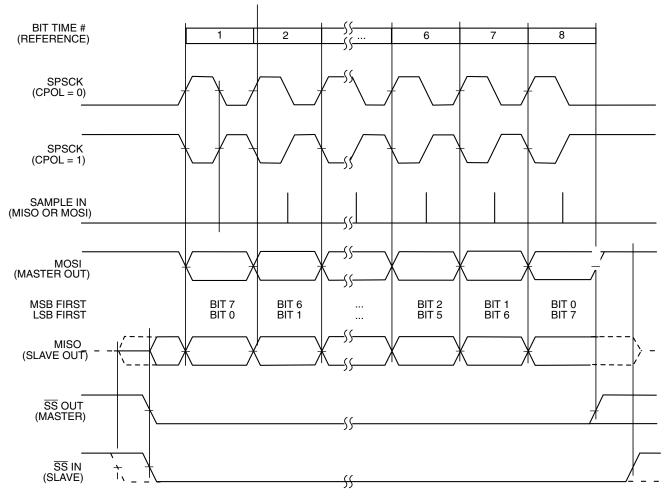

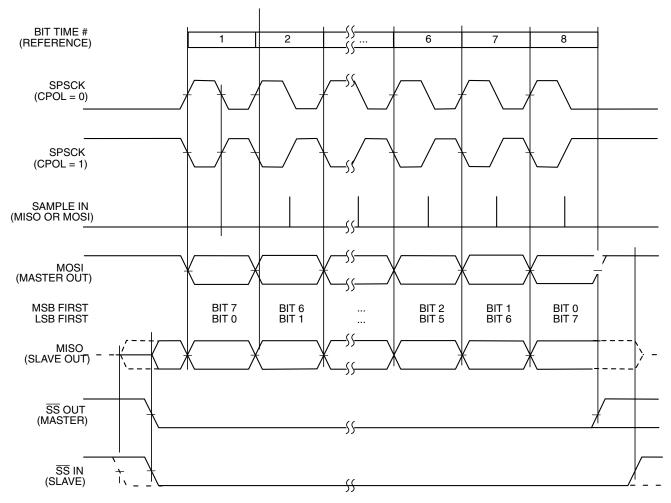

|      | 16.4.4        | SPI Clock Formats                          | 452 |

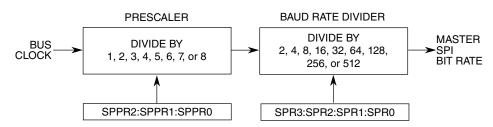

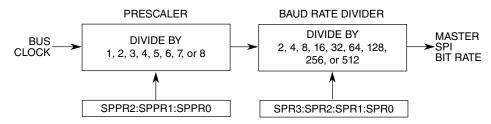

|      | 16.4.5        | SPI Baud Rate Generation.                  | 455 |

|      | 16.4.6        | Special Features                           | 455 |

|      |               | 16.4.6.1 SS Output                         | 455 |

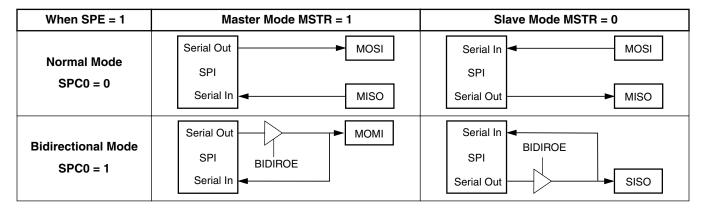

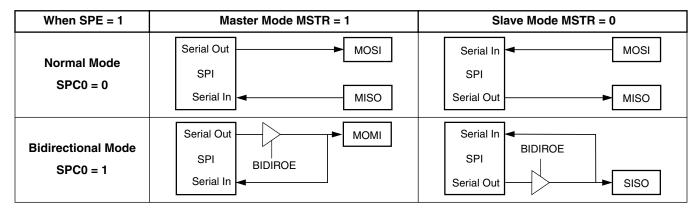

|      |               | 16.4.6.2 Bidirectional Mode (MOMI or SISO) | 456 |

| Sec  | tion nu    | umber Title                                                   | Page |

|------|------------|---------------------------------------------------------------|------|

|      | 16.4.7     | Error Conditions.                                             | 457  |

|      |            | 16.4.7.1 Mode Fault Error                                     | 457  |

|      | 16.4.8     | Low Power Mode Options                                        | 458  |

|      |            | 16.4.8.1 SPI in Run Mode                                      | 458  |

|      |            | 16.4.8.2 SPI in Wait Mode                                     | 458  |

|      |            | 16.4.8.3 SPI in Stop Mode                                     | 459  |

|      | 16.4.9     | Reset                                                         | 459  |

|      | 16.4.10    | Interrupts.                                                   | 460  |

|      |            | 16.4.10.1 MODF                                                | 460  |

|      |            | 16.4.10.2 SPRF                                                | 460  |

|      |            | 16.4.10.3 SPTEF                                               | 461  |

|      |            | 16.4.10.4 SPMF                                                | 461  |

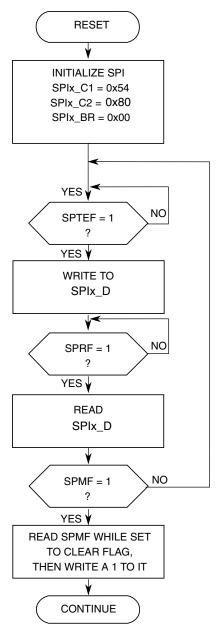

| 16.5 | Initializa | ation/Application Information                                 | 461  |

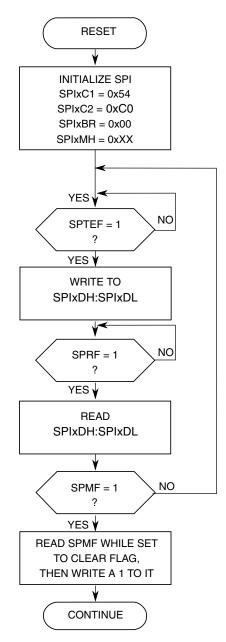

|      | 16.5.1     | Initialization Sequence.                                      | 461  |

|      | 16.5.2     | Pseudo-Code Example                                           | 462  |

|      |            | Chapter 17<br>16-Bit Serial Peripheral Interface (16-Bit SPI) |      |

| 17.1 | Introduc   | tion                                                          | 465  |

|      | 17.1.1     | Features.                                                     | 465  |

|      | 17.1.2     | Modes of operation.                                           | 466  |

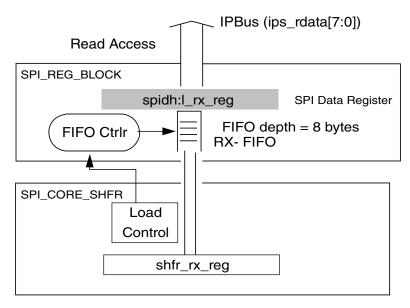

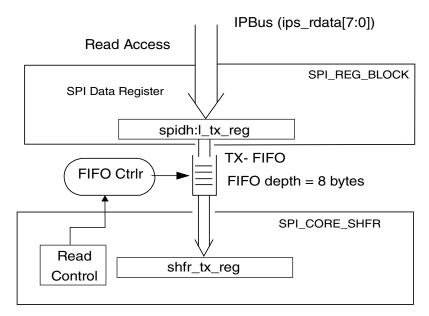

|      | 17.1.3     | Block diagrams                                                | 467  |

|      |            | 17.1.3.1 SPI system block diagram.                            | 467  |

|      |            | 17.1.3.2 SPI module block diagram                             | 467  |

| 17.2 | External   | signal description.                                           | 469  |

|      | 17.2.1     | SPSCK — SPI Serial Clock                                      | 470  |

|      | 17.2.2     | MOSI — Master Data Out, Slave Data In                         | 470  |

|      | 17.2.3     | MISO — Master Data In, Slave Data Out                         | 470  |

|      | 17.2.4     | SS — Slave Select                                             | 470  |

| 17.3 | Memory     | map/register definition.                                      | 471  |

|      |            |                                                               |      |

| Section n    | umber Title                                | Page |

|--------------|--------------------------------------------|------|

| 17.3.1       | SPI Control Register 1 (SPIx_C1)           | 471  |

| 17.3.2       | SPI Control Register 2 (SPIx_C2)           |      |

| 17.3.3       | SPI Baud Rate Register (SPIx_BR)           |      |

| 17.3.4       | SPI Status Register (SPIx_S)               |      |

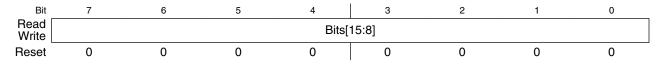

| 17.3.5       | SPI data register high (SPIx_DH)           | 479  |

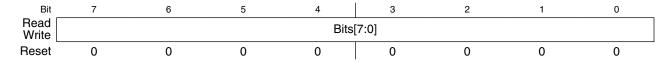

| 17.3.6       | SPI Data Register low (SPIx_DL)            |      |

| 17.3.7       | SPI match register high (SPIx_MH)          |      |

| 17.3.8       | SPI Match Register low (SPIx_ML)           | 480  |

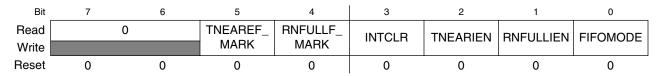

| 17.3.9       | SPI control register 3 (SPIx_C3)           | 481  |

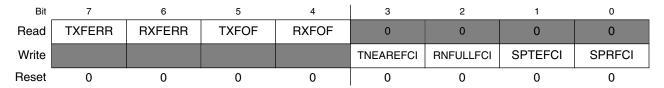

| 17.3.10      | SPI clear interrupt register (SPIx_CI)     | 482  |

| 17.4 Functio | onal description                           | 484  |

| 17.4.1       | General                                    | 484  |

| 17.4.2       | Master mode                                | 485  |

| 17.4.3       | Slave mode                                 | 486  |

| 17.4.4       | SPI FIFO Mode                              | 487  |

| 17.4.5       | Data Transmission Length                   | 488  |

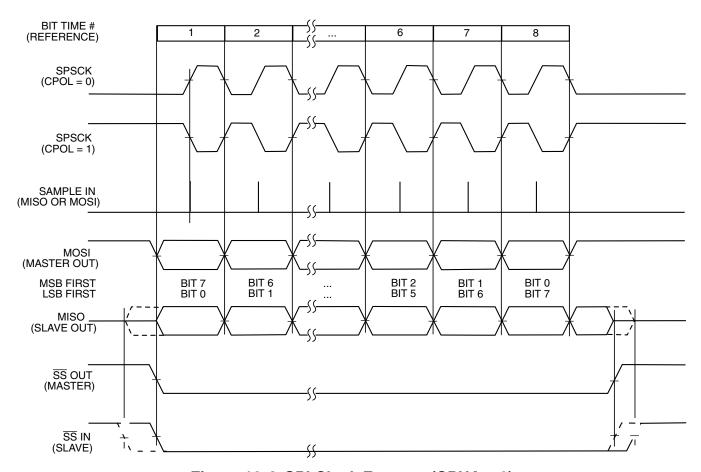

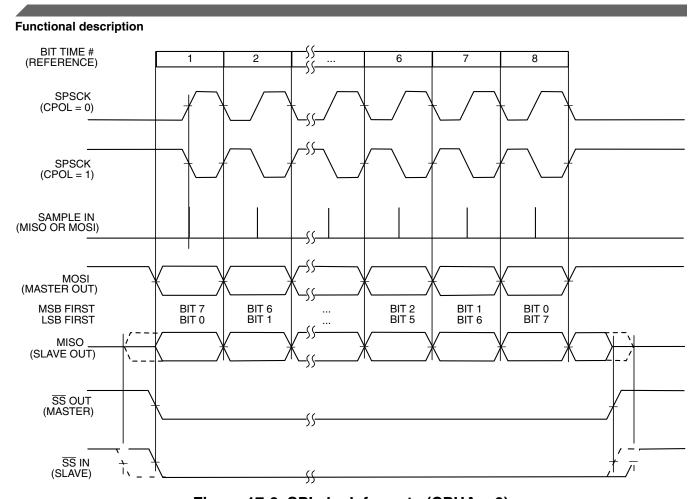

| 17.4.6       | SPI clock formats                          | 489  |

| 17.4.7       | SPI baud rate generation.                  | 492  |

| 17.4.8       | Special features                           | 493  |

|              | 17.4.8.1 SS Output                         | 493  |

|              | 17.4.8.2 Bidirectional mode (MOMI or SISO) | 493  |

| 17.4.9       | Error conditions.                          | 494  |

|              | 17.4.9.1 Mode fault error                  | 495  |

| 17.4.10      | Low-power mode options                     |      |

|              | 17.4.10.1 SPI in Run mode                  | 495  |

|              | 17.4.10.2 SPI in Wait mode                 | 495  |

|              | 17.4.10.3 SPI in Stop mode                 | 496  |

| 17.4.11      | Reset                                      | 497  |

| 17.4.12      | Interrupts                                 | 497  |

| Sec  | tion n    | umber Title                                             | Page |

|------|-----------|---------------------------------------------------------|------|

|      |           | 17.4.12.1 MODF                                          | 498  |

|      |           | 17.4.12.2 SPRF                                          | 498  |

|      |           | 17.4.12.3 SPTEF                                         | 498  |

|      |           | 17.4.12.4 SPMF                                          | 498  |

|      |           | 17.4.12.5 TNEAREF                                       | 499  |

|      |           | 17.4.12.6 RNFULLF                                       | 499  |

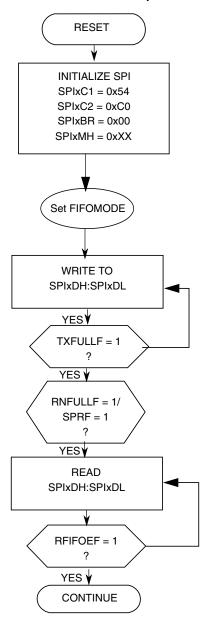

| 17.5 | Initializ | zation/application information                          | 499  |

|      | 17.5.1    | Initialization sequence                                 | 499  |

|      | 17.5.2    | Pseudo-Code Example                                     | 500  |

|      |           | Chapter 18<br>Inter-Integrated Circuit (I2C)            |      |

| 18.1 | Introduc  | ction                                                   | 505  |

|      | 18.1.1    | Features                                                | 505  |

|      | 18.1.2    | Modes of operation                                      | 506  |

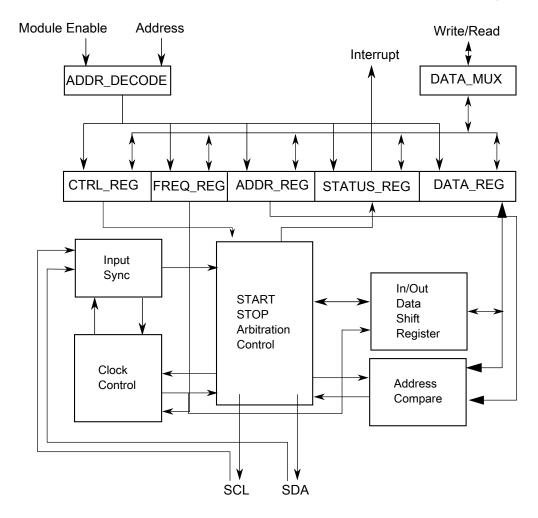

|      | 18.1.3    | Block diagram                                           | 506  |

| 18.2 | I2C sign  | nal descriptions                                        | 507  |

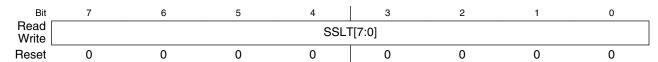

| 18.3 | Memor     | y map/register definition                               | 508  |

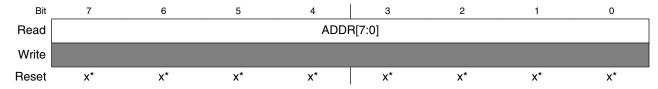

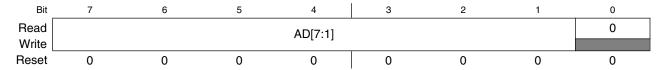

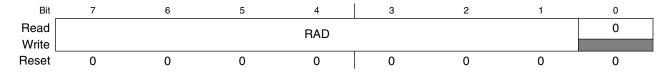

|      | 18.3.1    | I2C Address Register 1 (I2C_A1)                         | 508  |

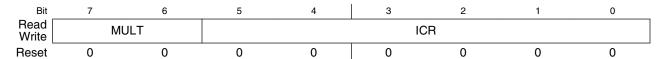

|      | 18.3.2    | I2C Frequency Divider register (I2C_F)                  | 509  |

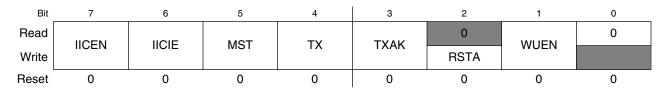

|      | 18.3.3    | I2C Control Register 1 (I2C_C1)                         | 510  |

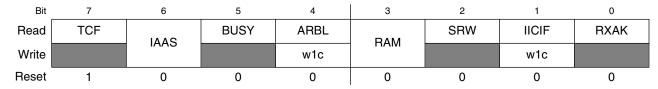

|      | 18.3.4    | I2C Status register (I2C_S)                             | 511  |

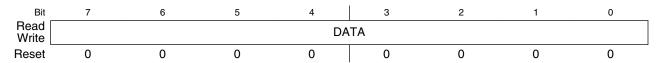

|      | 18.3.5    | I2C Data I/O register (I2C_D)                           | 513  |

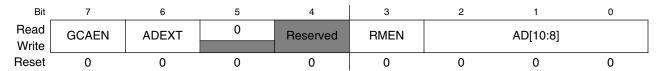

|      | 18.3.6    | I2C Control Register 2 (I2C_C2)                         | 514  |

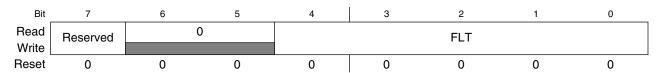

|      | 18.3.7    | I2C Programmable Input Glitch Filter Register (I2C_FLT) | 515  |

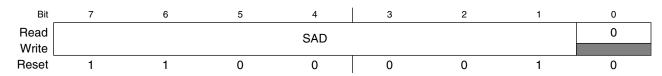

|      | 18.3.8    | I2C Range Address register (I2C_RA)                     | 515  |

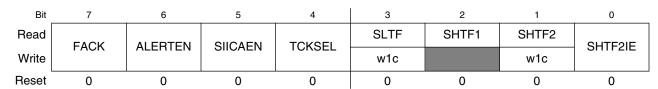

|      | 18.3.9    | I2C SMBus Control and Status register (I2C_SMB)         | 516  |

|      | 18.3.10   | I2C Address Register 2 (I2C_A2)                         | 517  |

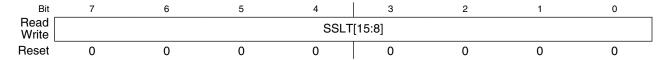

|      | 18.3.11   | I2C SCL Low Timeout Register High (I2C_SLTH)            | 518  |

|      | 18.3.12   | I2C SCL Low Timeout Register Low (I2C_SLTL)             | 518  |

| Sect | tion n    | umber       | Title                                         | Page |

|------|-----------|-------------|-----------------------------------------------|------|

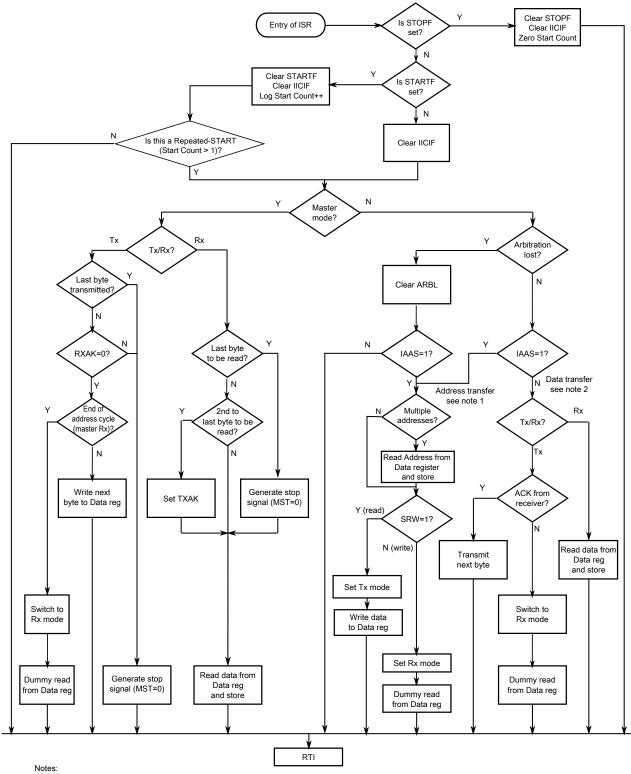

| 18.4 | Functio   | nal descrip | tion                                          | 518  |

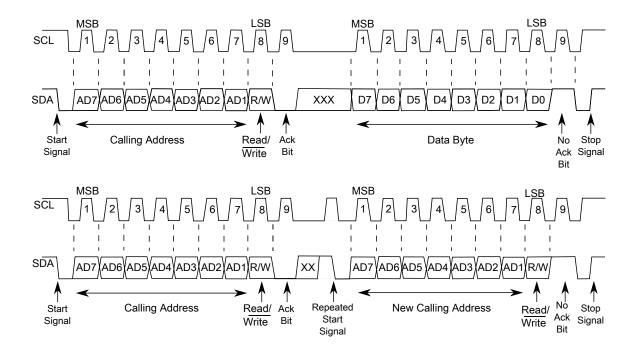

|      | 18.4.1    | I2C proto   | ocol                                          | 518  |

|      |           | 18.4.1.1    | START signal                                  | 519  |

|      |           | 18.4.1.2    | Slave address transmission.                   | 520  |

|      |           | 18.4.1.3    | Data transfers.                               |      |

|      |           | 18.4.1.4    | STOP signal.                                  |      |

|      |           | 18.4.1.5    | Repeated START signal                         | 521  |

|      |           | 18.4.1.6    | Arbitration procedure                         | 521  |

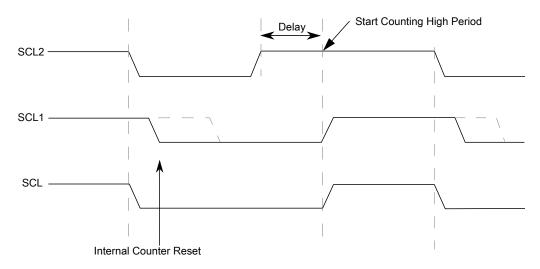

|      |           | 18.4.1.7    | Clock synchronization                         | 522  |

|      |           | 18.4.1.8    | Handshaking                                   | 522  |

|      |           | 18.4.1.9    | Clock stretching.                             |      |

|      |           | 18.4.1.10   | I2C divider and hold values                   |      |

|      | 18.4.2    | 10-bit add  | dress                                         | 524  |

|      |           | 18.4.2.1    | Master-transmitter addresses a slave-receiver |      |

|      |           | 18.4.2.2    | Master-receiver addresses a slave-transmitter | 525  |

|      | 18.4.3    | Address r   | matching                                      | 525  |

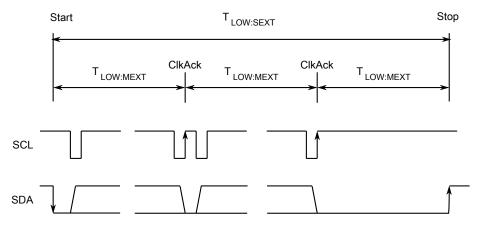

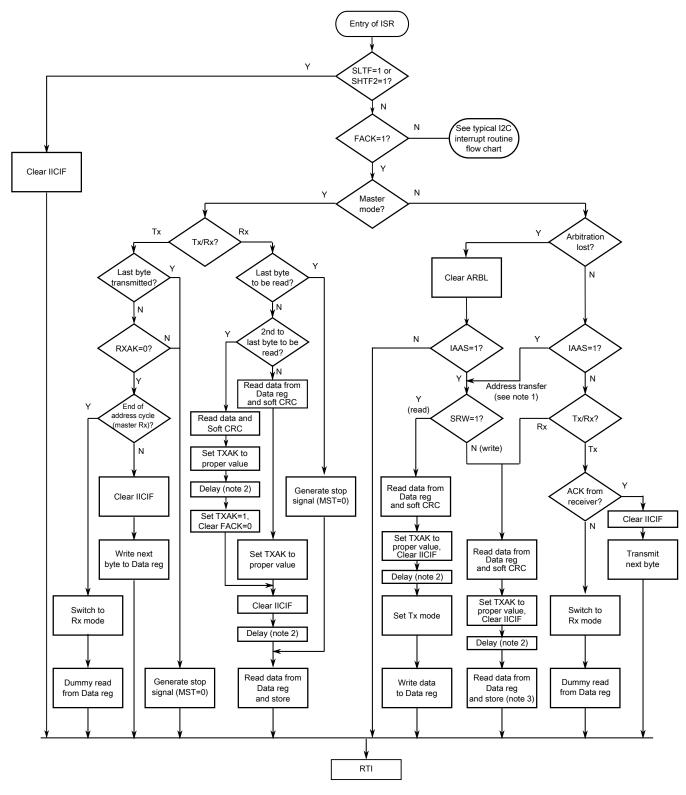

|      | 18.4.4    | System m    | nanagement bus specification                  | 526  |

|      |           | 18.4.4.1    | Timeouts                                      | 526  |

|      |           | 18.4.4.2    | FAST ACK and NACK                             | 528  |

|      | 18.4.5    | Resets      |                                               | 529  |

|      | 18.4.6    | Interrupts  | S                                             | 529  |

|      |           | 18.4.6.1    | Byte transfer interrupt                       | 530  |

|      |           | 18.4.6.2    | Address detect interrupt                      | 530  |

|      |           | 18.4.6.3    | Exit from low-power/stop modes                | 530  |

|      |           | 18.4.6.4    | Arbitration lost interrupt                    | 530  |

|      |           | 18.4.6.5    | Timeout interrupt in SMBus                    | 531  |

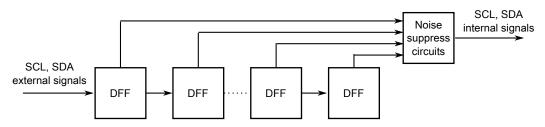

|      | 18.4.7    | Programn    | mable input glitch filter                     | 531  |

|      | 18.4.8    | Address r   | matching wake-up                              | 531  |

| 18.5 | Initializ | ation/appli | cation information                            | 532  |

## Chapter 19 Analog-to-digital converter (ADC)

| 19.1 | Introduc | ction                                    | 537 |

|------|----------|------------------------------------------|-----|

|      | 19.1.1   | Features                                 | 537 |

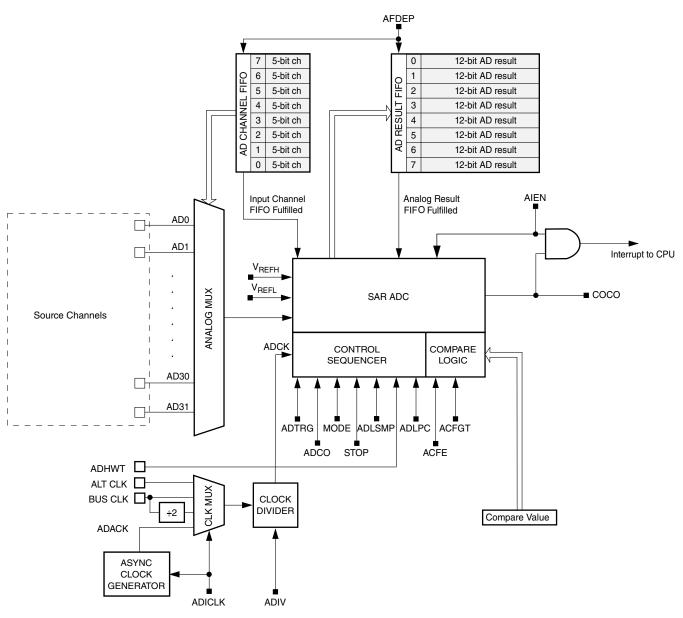

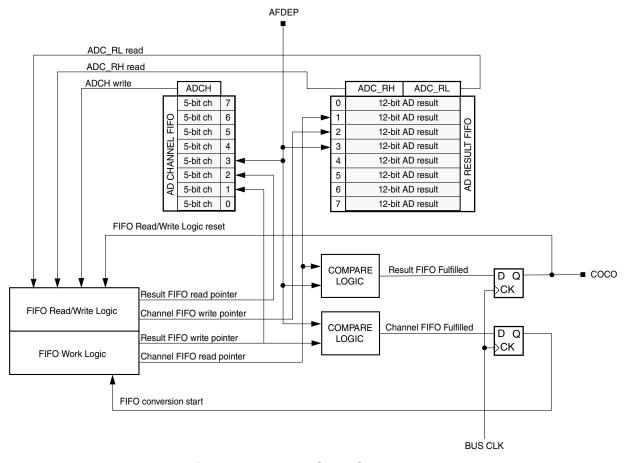

|      | 19.1.2   | Block Diagram                            | 538 |

| 19.2 | External | l Signal Description                     | 539 |

|      | 19.2.1   | Analog Power (VDDA)                      | 539 |

|      | 19.2.2   | Analog Ground (VSSA)                     | 539 |

|      | 19.2.3   | Voltage Reference High (VREFH)           | 539 |

|      | 19.2.4   | Voltage Reference Low (VREFL)            | 539 |

|      | 19.2.5   | Analog Channel Inputs (ADx)              | 540 |

| 19.3 | ADC Co   | ontrol Registers                         | 540 |

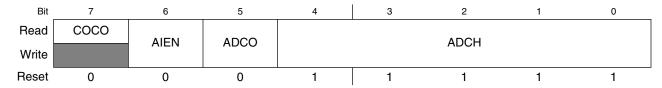

|      | 19.3.1   | Status and Control Register 1 (ADC_SC1)  | 540 |

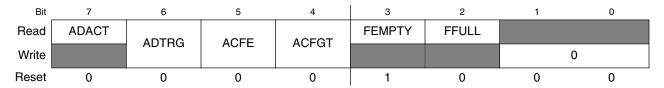

|      | 19.3.2   | Status and Control Register 2 (ADC_SC2)  | 542 |

|      | 19.3.3   | Status and Control Register 3 (ADC_SC3)  | 543 |

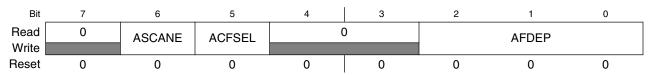

|      | 19.3.4   | Status and Control Register 4 (ADC_SC4)  | 544 |

|      | 19.3.5   | Conversion Result High Register (ADC_RH) | 545 |

|      | 19.3.6   | Conversion Result Low Register (ADC_RL)  | 546 |

|      | 19.3.7   | Compare Value High Register (ADC_CVH)    | 547 |

|      | 19.3.8   | Compare Value Low Register (ADC_CVL)     | 547 |

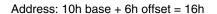

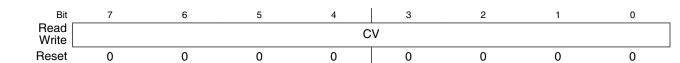

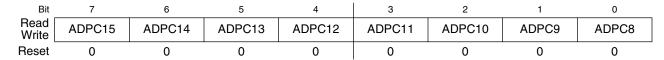

|      | 19.3.9   | Pin Control 1 Register (ADC_APCTL1)      | 548 |

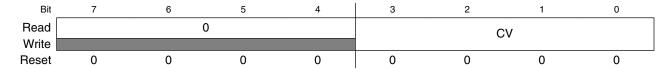

|      | 19.3.10  | Pin Control 2 Register (ADC_APCTL2)      | 549 |

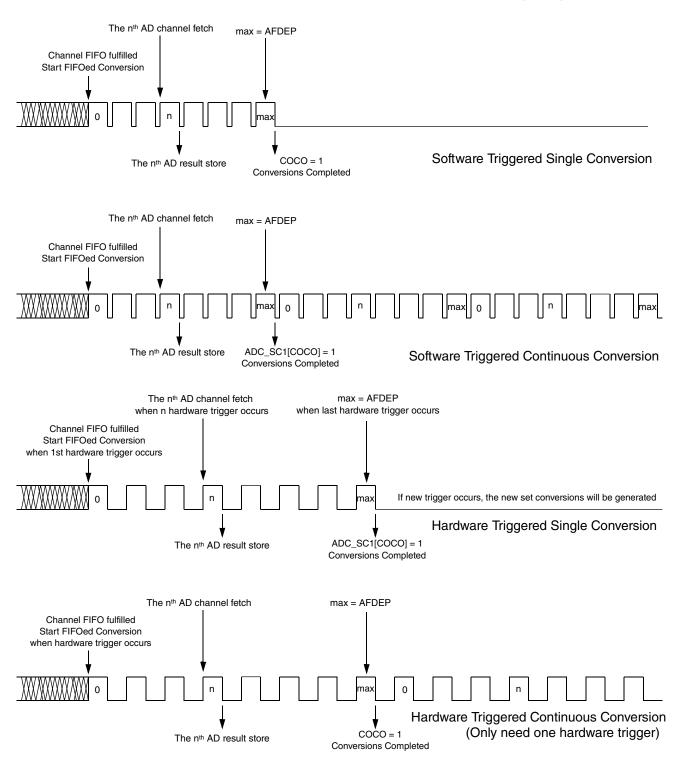

| 19.4 | Function | nal description                          | 550 |

|      | 19.4.1   | Clock select and divide control          | 551 |

|      | 19.4.2   | Input select and pin control             | 551 |

|      | 19.4.3   | Hardware trigger                         | 552 |

|      | 19.4.4   | Conversion control                       | 552 |

|      |          | 19.4.4.1 Initiating conversions          | 552 |

|      |          | 19.4.4.2 Completing conversions          | 553 |

|      |          |                                          |     |

| Section number  |             | Title                                            | Page |

|-----------------|-------------|--------------------------------------------------|------|

|                 | 19.4.4.3    | Aborting conversions                             | 553  |

|                 | 19.4.4.4    | Power control                                    | 554  |

|                 | 19.4.4.5    | Sample time and total conversion time            | 554  |

| 19.4.5          | Automati    | ic compare function                              | 555  |

| 19.4.6          | FIFO ope    | eration                                          | 556  |

| 19.4.7          | MCU wa      | it mode operation                                | 559  |

| 19.4.8          | MCU Sto     | op3 mode operation                               | 560  |

|                 | 19.4.8.1    | Stop3 mode with ADACK disabled                   | 560  |

|                 | 19.4.8.2    | Stop3 mode with ADACK enabled                    | 560  |

| 19.5 Initializa | ation infor | mation                                           | 561  |

| 19.5.1          | ADC mo      | dule initialization example                      | 561  |

|                 | 19.5.1.1    | Initialization sequence                          | 561  |

|                 | 19.5.1.2    | Pseudo-code example                              | 562  |

| 19.5.2          | ADC FIF     | FO module initialization example                 | 562  |

|                 | 19.5.2.1    | Pseudo-code example                              | 563  |

| 19.6 Applicat   | tion inform | nation                                           | 564  |

| 19.6.1          | External    | pins and routing                                 | 564  |

|                 | 19.6.1.1    | Analog supply pins                               | 564  |

|                 | 19.6.1.2    | Analog reference pins                            |      |

|                 | 19.6.1.3    | Analog input pins                                | 565  |

| 19.6.2          | Sources of  | of error                                         | 566  |

|                 | 19.6.2.1    | Sampling error                                   | 566  |

|                 | 19.6.2.2    | Pin leakage error                                | 566  |

|                 | 19.6.2.3    | Noise-induced errors                             | 566  |

|                 | 19.6.2.4    | Code width and quantization error                | 567  |

|                 | 19.6.2.5    | Linearity errors                                 | 568  |

|                 | 19.6.2.6    | Code jitter, non-monotonicity, and missing codes | 569  |

Chapter 20 Analog comparator (ACMP)

| Section number |          | umber        | Title                                    | Page |

|----------------|----------|--------------|------------------------------------------|------|

| 20.1           | Introduc | ction        |                                          | 571  |

|                | 20.1.1   | Features.    |                                          | 571  |

|                | 20.1.2   | Modes of     | f operation                              |      |

|                |          | 20.1.2.1     | Operation in Wait mode                   | 572  |

|                |          | 20.1.2.2     | Operation in Stop3 mode                  |      |

|                |          | 20.1.2.3     | Operation in Debug mode                  | 572  |

|                | 20.1.3   | Block dia    | ngram                                    | 572  |

| 20.2           | Externa  | l signal des | scription                                | 572  |

| 20.3           | Memor    | y map and    | register definition                      | 573  |

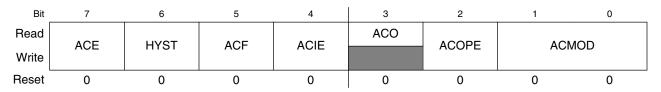

|                | 20.3.1   | ACMP C       | Control and Status Register (ACMP_CS)    |      |

|                | 20.3.2   | ACMP C       | Control Register 0 (ACMP_C0)             | 574  |

|                | 20.3.3   | ACMP C       | Control Register 1 (ACMP_C1)             | 575  |

|                | 20.3.4   | ACMP C       | Control Register 2 (ACMP_C2)             | 575  |

| 20.4           | Functio  | nal descrip  | tion                                     | 576  |

| 20.5           | Setup an | nd operation | on of ACMP                               | 577  |

| 20.6           | Resets   |              |                                          | 577  |

| 20.7           | Interrup | ots          |                                          | 577  |

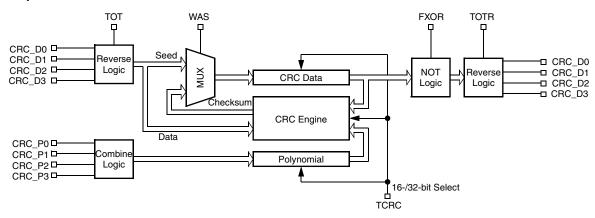

|                |          |              | Chapter 21 Cyclic redundancy check (CRC) |      |

| 21.1           | Introduc | ction        |                                          | 579  |

|                |          |              |                                          |      |

|                |          |              |                                          |      |

|                |          |              | n                                        |      |

|                |          | _            | L                                        |      |

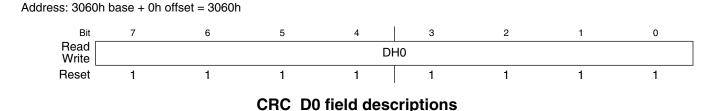

|                | 21.5.1   | CRC Dat      | a 0 Register (CRC_D0)                    | 581  |

|                | 21.5.2   |              | a 1 Register (CRC_D1)                    |      |

|                | 21.5.3   |              | a 2 Register (CRC_D2)                    |      |

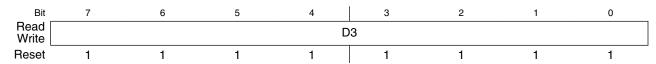

|                | 21.5.4   |              | a 3 Register (CRC_D3)                    |      |

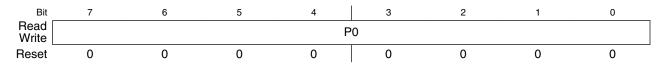

|                | 21.5.5   | CRC Pol      | ynomial 0 Register (CRC_P0)              | 583  |

|                |          |              |                                          |      |

| 360  | tion n   | umber Title                                         | Page |

|------|----------|-----------------------------------------------------|------|

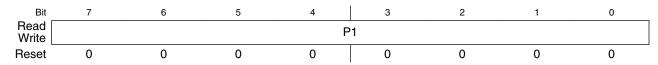

|      | 21.5.6   | CRC Polynomial 1 Register (CRC_P1)                  | 584  |

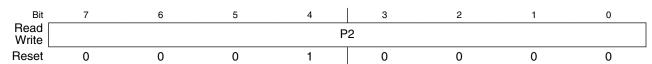

|      | 21.5.7   | CRC Polynomial 2 Register (CRC_P2)                  | 584  |

|      | 21.5.8   | CRC Polynomial 3 Register (CRC_P3)                  | 585  |

|      | 21.5.9   | CRC Control Register (CRC_CTRL)                     | 585  |

| 21.6 | Function | nal description                                     | 586  |

|      | 21.6.1   | 16-bit CRC calculation.                             | 586  |

|      | 21.6.2   | 32-bit CRC calculation.                             | 586  |

|      | 21.6.3   | Bit reverse                                         | 587  |

|      | 21.6.4   | Result complement                                   | 587  |

|      | 21.6.5   | CCITT compliant CRC example                         | 587  |

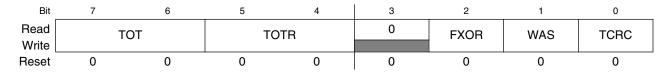

|      |          | Chapter 22<br>Watchdog (WDOG)                       |      |

| 22.1 | Introduc | ction                                               | 589  |

| 22.1 | 22.1.1   | Features                                            |      |

|      | 22.1.2   | Block diagram                                       |      |

| 22.2 |          | y map and register definition                       |      |

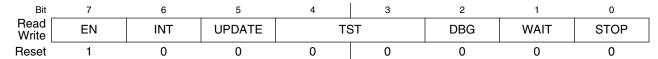

|      | 22.2.1   | Watchdog Control and Status Register 1 (WDOG_CS1)   |      |

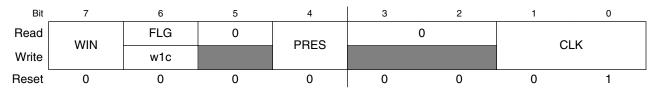

|      | 22.2.2   | Watchdog Control and Status Register 2 (WDOG_CS2)   |      |

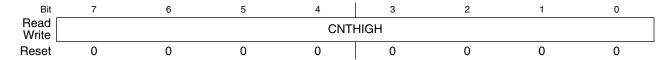

|      | 22.2.3   | Watchdog Counter Register: High (WDOG_CNTH)         |      |

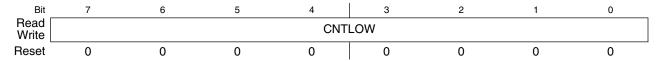

|      | 22.2.4   | Watchdog Counter Register: Low (WDOG_CNTL)          | 594  |

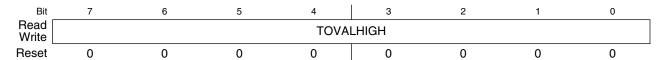

|      | 22.2.5   | Watchdog Timeout Value Register: High (WDOG_TOVALH) | 595  |

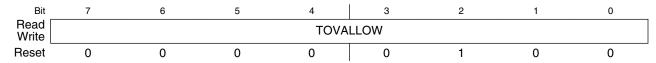

|      | 22.2.6   | Watchdog Timeout Value Register: Low (WDOG_TOVALL)  | 595  |

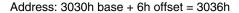

|      | 22.2.7   | Watchdog Window Register: High (WDOG_WINH)          | 596  |

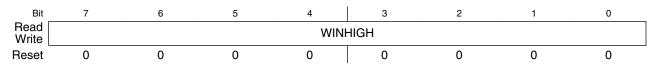

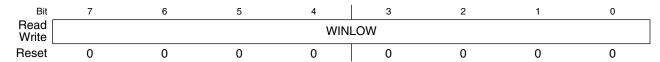

|      | 22.2.8   | Watchdog Window Register: Low (WDOG_WINL)           | 596  |

| 22.3 | Function | nal description                                     | 597  |

|      | 22.3.1   | Watchdog refresh mechanism.                         | 597  |

|      |          | 22.3.1.1 Window mode                                | 598  |

|      |          | 22.3.1.2 Refreshing the Watchdog                    | 598  |

|      |          | 22.3.1.3 Example code: Refreshing the Watchdog      | 599  |

| Section number |          | umber       | Title                                    | Page |

|----------------|----------|-------------|------------------------------------------|------|

|                | 22.3.2   | Configuri   | ing the Watchdog                         | 599  |

|                |          | 22.3.2.1    | Reconfiguring the Watchdog               | 599  |

|                |          | 22.3.2.2    | Unlocking the Watchdog                   | 600  |

|                |          | 22.3.2.3    | Example code: Reconfiguring the Watchdog | 600  |

|                | 22.3.3   | Clock sou   | ırce                                     | 600  |

|                | 22.3.4   | Using into  | errupts to delay resets                  | 602  |

|                | 22.3.5   | Backup re   | eset                                     | 602  |

|                | 22.3.6   | Functiona   | ality in debug and low-power modes       | 602  |

|                | 22.3.7   | Fast testin | ng of the watchdog                       | 603  |

|                |          | 22.3.7.1    | Testing each byte of the counter         | 603  |

|                |          | 22.3.7.2    | Entering user mode                       | 604  |

|                |          |             | Chapter 23<br>Development support        |      |

| 23.1           | Introduc | ction       |                                          | 605  |

|                | 23.1.1   | Forcing a   | ctive background                         | 605  |

|                | 23.1.2   | Features    |                                          | 605  |

| 23.2           | Backgro  | ound debug  | controller (BDC)                         | 606  |

|                | 23.2.1   | BKGD pi     | n description                            | 607  |

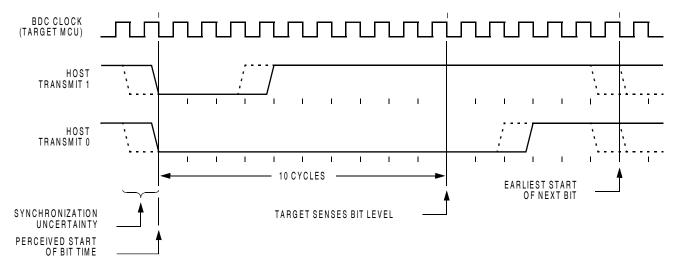

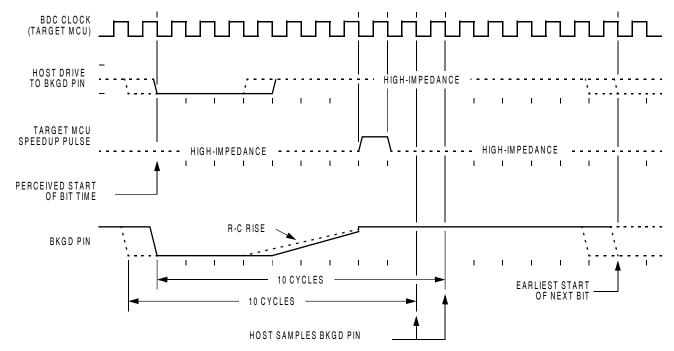

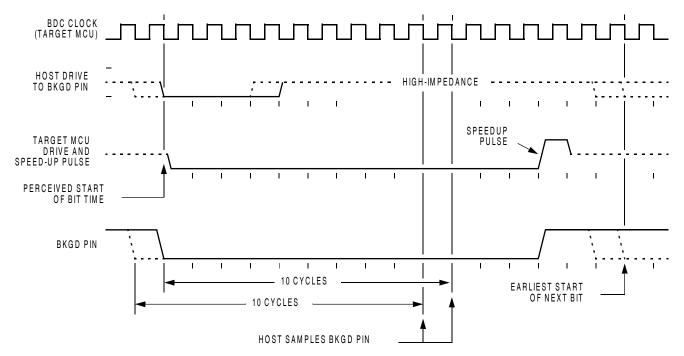

|                | 23.2.2   | Communi     | ication details                          | 608  |

|                | 23.2.3   | BDC com     | nmands                                   | 610  |

|                | 23.2.4   | BDC hard    | dware breakpoint                         | 613  |

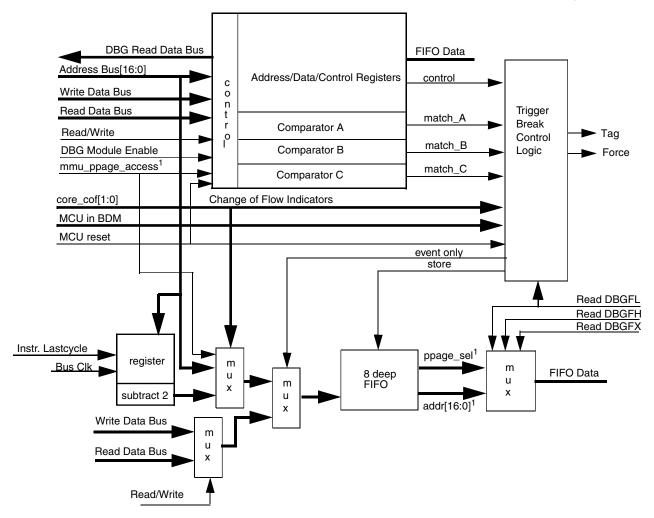

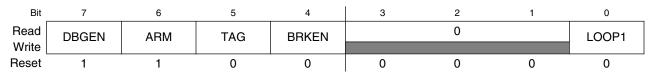

| 23.3           | On-chip  | debug sys   | tem (DBG)                                | 613  |

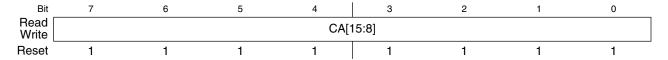

|                | 23.3.1   | Comparat    | tors A and B                             | 614  |

|                | 23.3.2   | Bus captu   | are information and FIFO operation       | 614  |

|                | 23.3.3   | Change-o    | of-flow information                      | 615  |

|                | 23.3.4   | Tag vs. fo  | orce breakpoints and triggers            | 616  |

|                | 23.3.5   | Trigger m   | nodes                                    | 617  |

|                | 23.3.6   | Hardware    | breakpoints                              | 618  |

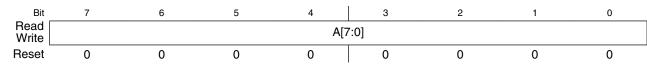

| 23.4           | Memory   | map and i   | register description                     | 619  |

|                |          |             |                                          |      |

| Section number |          | umber Title                                              | Page |