# MCF5102 (ColdFire) Integrated Processor User's Manual Revision 1.0

© MOTOROLA, 1995. All Rights Reserved.

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document. Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

For More Information On This Product, Go to: www.freescale.com

### **Documentation Comments**

#### FAX 512-891-8593—Documentation Comments Only

The Motorola High-Performance Embedded Systems Technical Communications Department provides you with several ways to submit any questions or comments about this document or to order other documents. We welcome your suggestions for improving our documentation. Please do not fax technical questions.

Please provide the part number and revision number (located in upper right-hand corner of the cover) and the title of the document. When referring to items in the manual, please reference by the page number, paragraph number, figure number, table number, and line number, if needed.

When sending a fax, please provide your name, company, fax number, and phone number including area code.

#### For Internet Access:

Telnet: pirs.aus.sps.mot.com (Login: pirs) WWW: http://pirs.aus.sps.mot.com/aesop/hmpg.html Query By Email: aesop\_query@pirs.aus.sps.mot.com (Type "HELP" in text body.)

#### For Dial-Up:

Phone: +1-512-891-3650 Phone (US or Canada): 1-800-843-3451 Connection Settings: N/8/1/F Data Rate: < 14,400 bps Terminal Emulation: VT100 Login: pirs

#### For AESOP Questions:

FAX: +1-512-891-8775 EMAIL: aesop\_sysop@pirs.aus.sps.mot.com

#### For Hotline Questions:

FAX (US or Canada): 1-800-248-8567 EMAIL: aesop\_support@pirs.aus.sps.mot.com

MOTOROLA

MCF5102 USER'S MANUAL REV. 1.0

iii

### MOTOROLA WORLDWIDE SALES OFFICES

| P | FN | NS | VI 1 | ۷A | NI. |

|---|----|----|------|----|-----|

| UNITED STATES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| ALABAMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                               |

| Huntsville                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                               |

| ALASKA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                               |

| Tempe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                               |

| CALIFORNIA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                               |

| Calabasas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                               |

| Irvine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                               |

| Los Angeles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                               |

| San Diego                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                               |

| Sunnyvale                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                               |

| COLORADO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                               |

| Denver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                               |

| CONNECTICUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                               |

| Wallingford                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                               |

| FLORIDA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                               |

| Clearwater                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                               |

| Maitland                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                               |

| Pompano Beach/Ft. Lauderdale (305)351-6040                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                               |

| GEORGIA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                               |

| Atlanta                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _                             |

| IDAHO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | C                             |

| Boise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                               |

| ILLINOIS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                               |

| Chicago/Schaumburg (708)413-2500                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                               |

| INDIANA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                               |

| Indianapolis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                               |

| Kokomo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                               |

| IOWA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                               |

| Cedar Rapids                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                               |

| KANSAS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                               |

| Kansas City/Mission                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | IN                            |

| MARYLAND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | IN                            |

| Columbia (410)381-1570                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | IN                            |

| Columbia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | IN                            |

| Columbia (410)381-1570                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | IN                            |

| Columbia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | IN<br>I                       |

| Columbia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | או<br> <br>                   |

| Columbia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | אנ<br> <br>                   |

| Columbia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | л<br>,<br>,<br>,              |

| Columbia         (410)381–1570           MASSACHUSETTS         Marborough           Marborough         (508)481–8100           Woburn         (617)932–9700           MICHIGAN         (810)347–6800           Literature         (800)392–2016           MINNESOTA         (800)392–2016                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | л<br>,<br>,<br>,              |

| Columbia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | אנ<br>ו<br>ו                  |

| Columbia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | אנ<br> <br> <br>              |

| Columbia         (410)381–1570           MASSACHUSETTS         Marborough         (508)481–8100           Woburn         (617)932–9700           MICHIGAN         (810)347–6800           Literature         (800)392–2016           MINNESOTA         (612)932–1500           MISOURI         (314)275–7380                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                             |

| Columbia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1                             |

| Columbia         (410)381–1570           MASSACHUSETTS         Marborough         (508)481–8100           Woburn         (517)932–9700         MiCHIGAN           Detroit         (810)347–6800         Literature           MiNNESOTA         (810)392–2016         Minnetorika           MissOURI         (612)932–1500         MissOURI           St. Louis         (314)275–7380           NEW JERSEY         Fairfield         (201)808–2400                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1                             |

| Columbia         (410)381–1570           MASSACHUSETTS         Marborough         (508)481–8100           Woburn         (617)932–9700           MICHIGAN         (810)347–6800           Detroit         (800)392–2016           MinNESOTA         (612)932–1500           MISOURI         (314)275–7360           NEW JERSEY         Fairfield           Fairfield         (201)808–2400                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1                             |

| Columbia (410)381–1570<br>MASSACHUSETTS<br>Marborough (508)481–8100<br>Woburn (617)932–9700<br>MICHIGAN<br>Detroit (810)347–6800<br>Literature (800)392–2016<br>MINNESOTA<br>Minnetorka (612)932–1500<br>MISSOURI<br>St. Louis (314)275–7380<br>NEW JERSEY<br>Fairfield (201)808–2400<br>NEW YORK<br>Fairport (716)425–4000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1                             |

| Columbia         (410)381–1570           MASSACHUSETTS         Marborough         (508)481–8100           Woburn         (617)932–9700           MICHIGAN         (610)347–6800           Detroit         (810)347–6800           Literature         (800)392–2016           MiNNESOTA         (612)932–1500           MISSOURI         (314)275–7380           NEW JERSEY         Fairfield           Fairfield         (201)808–2400           NEW YORK         (716)425–4000           Fishkill         (914)898–0511                                                                                                                                                                                                                                                                                                                                                            | ,<br>(<br>]<br>]              |

| Columbia         (410)381–1570           MASSACHUSETTS         Marborough         (508)481–8100           Woburn         (617)932–9700           MICHIGAN         (810)347–6800           Literature         (800)392–2016           Minnetorika         (612)932–1500           MISOURI         (314)275–7380           NEW JERSEY         Fairfield           Fairport         (716)425–4000           Fishkill         (914)996–0511           Hauppauge         (516)361–7000                                                                                                                                                                                                                                                                                                                                                                                                   | ,<br>(<br>]<br>]              |

| Columbia         (410)381–1570           MASSACHUSETTS         Marborough         (508)481–8100           Woburn         (510)347–6800         Literature           Detroit         (810)347–6800         Literature           MinnetorKa         (810)347–6800         Literature           MinnetorKa         (612)932–2016         MinnetorKa           MissOURI         (512)932–1500         MissOURI           St. Louis         (314)275–7380           NEW JERSEY         Fairfield         (201)808–2400           Fairfield         (211)808–2400         Fishkill           Fairport         (716)425–4000         Fishkill           NORTH CAROLINA         (515)361–7000         NORTH CAROLINA                                                                                                                                                                        | ,<br>(<br>]<br>]              |

| Columbia         (410)381–1570           MASSACHUSETTS         Marborough         (508)481–8100           Woburn         (617)932–9700           MICHIGAN         (810)347–6800           Literature         (800)392–2016           MINNESOTA         (812)932–1500           MISSOURI         (314)275–7380           St. Louis         (314)275–7380           NEW JERSEY         Fairfield           Fairfield         (201)808–2400           Fishkill         (914)898–0511           Hauppauge         (516)361–7000           NORTH CAROLINA         (919)870–4355                                                                                                                                                                                                                                                                                                          | ,<br>(<br>]<br>]              |

| Columbia         (410)381–1570           MASSACHUSETTS         Marborough         (508)481–8100           Woburn         (617)932–9700           MICHIGAN         (810)347–6800           Literature         (800)392–2016           MINNESOTA         (612)932–1500           MISCOURI         (314)275–7380           St. Louis         (211)808–2400           Fairfield         (201)808–2400           Fishkill         (914)986–0511           Hauppauge         (516)361–7000           NORTH CAROLINA         (919)870–4355           OHIO         OHIO                                                                                                                                                                                                                                                                                                                     | <br> <br> <br> <br>           |

| Columbia         (410)381–1570           MASSACHUSETTS         Marborough         (508)481–8100           Woburn         (617)932–9700           MICHIGAN         (810)347–6800           Literature         (800)392–2016           MINNESOTA         (810)347–6800           MISSOURI         (314)275–7380           NEW JERSEY         (314)275–7380           Fairfield         (201)808–2400           Fishkill         (914)896–0511           Hauppauge         (516)361–7000           NORTH CAROLINA         (919)870–4355           OHIO         Clevaliand         (216)349–3100                                                                                                                                                                                                                                                                                        | ,<br>(<br>]<br>]              |

| Columbia         (410)381–1570           MASSACHUSETTS         Marborough         (508)481–8100           Woburn         (617)932–9700           MICHIGAN         (810)347–6800           Literature         (800)392–2016           MINNESOTA         (812)932–1500           MISCOURI         (814)275–7380           St. Louis         (314)275–7380           NEW JERSEY         Fairfield           Fairfield         (201)808–2400           NEW JORK         Fishkill           Fishkill         (919)870–4355           OHIO         (216)349–3100           Cieveland         (216)349–3100           ColumbusuWorthington         (814)431–8429                                                                                                                                                                                                                           | <br> <br> <br> <br>           |

| Columbia         (410)381–1570           MASSACHUSETTS         Marborough         (508)481–8100           Woburn         (617)932–9700           MICHIGAN         (810)347–6800           Detroit         (810)347–6800           Literature         (800)392–2016           MINNESOTA         (812)932–1500           MISSOURI         (314)275–7380           St. Louis         (314)275–7380           NEW JERSEY         Fairfield           Fairport         (716)425–4000           Fishkill         (914)996–0511           Hauppauge         (516)361–7000           NORTH CAROLINA         (919)870–4355           Raleigh         (919)870–4355           OHIO         Clevaland         (216)349–3100           Clevaland         (216)343–1492           Dayton         (513)438–8800                                                                                   | <br> <br> <br> <br> <br> <br> |

| Columbia         (410)381–1570           MASSACHUSETTS         Marborough         (508)481–8100           Woburn         (617)932–9700           MICHIGAN         (610)347–6800           Detroit         (810)347–6800           Literature         (800)392–2016           MiNNESOTA         (612)932–1500           MISSOURI         (314)275–7380           St. Louis         (314)275–7380           NEW JERSEY         Fairfield           Fairfield         (201)808–2400           NEW YORK         (716)425–4000           Fishkill         (919)870–4355           OHIO         (216)349–3100           Cleveland         (216)349–3100           Columbus/Worthington         (614)431–8492           Dayton         (513)438–6800                                                                                                                                       | <br> <br> <br> <br>           |

| Columbia         (410)381–1570           MASSACHUSETTS         Marborough           Marborough         (508)481–8100           Woburn         (617)932–9700           MICHIGAN         (810)347–6800           Detroit         (810)347–6800           Literature         (800)392–2016           MINNESOTA         (612)932–1500           MISSOURI         (314)275–7380           St. Louis         (314)275–7380           NEW JERSEY         Fairfield           Fairfield         (201)808–2400           Fishkill         (914)896–0511           Hauppauge         (516)361–7000           Fishkill         (919)870–4365           OHIO         (216)349–3100           Celweland         (216)349–3100           ColumbusuWorthington         (614)431–8492           Dayton         (513)438–6800           OKLAHOMA         Tuisa           Tuisa         (918)459–4565 | <br> <br> <br> <br> <br> <br> |

| Columbia         (410)381–1570           MASSACHUSETTS         Marborough         (508)481–8100           Warborough         (508)481–8100           Woburn         (617)932–9700           MICHIGAN         (810)347–6800           Detroit         (810)347–6800           Literature         (800)392–2016           MINNESOTA         (812)932–1500           MISSOURI         (314)275–7380           NEW JERSEY         (314)275–7380           Fairfield         (201)808–2400           Fishkill         (914)898–0511           Hauppauge         (516)361–7000           NORTH CAROLINA         (919)870–4365           OHIO         Cleveland         (216)349–3100           Cleveland         (216)3438–6800           OKLAHOMA         (918)459–4565           OREGON         (918)459–4565                                                                           | <br> <br> <br> <br> <br> <br> |

| Columbia         (410)381–1570           MASSACHUSETTS         Marborough           Marborough         (508)481–8100           Woburn         (617)932–9700           MICHIGAN         (810)347–6800           Detroit         (810)347–6800           Literature         (800)392–2016           MINNESOTA         (612)932–1500           MISSOURI         (314)275–7380           St. Louis         (314)275–7380           NEW JERSEY         Fairfield           Fairfield         (201)808–2400           Fishkill         (914)896–0511           Hauppauge         (516)361–7000           Fishkill         (919)870–4365           OHIO         (216)349–3100           Celweland         (216)349–3100           ColumbusuWorthington         (614)431–8492           Dayton         (513)438–6800           OKLAHOMA         Tuisa           Tuisa         (918)459–4565 | <br> <br> <br> <br> <br> <br> |

| LA WORLDWIDE SALE                        | SC  |

|------------------------------------------|-----|

| PENNSYLVANIA                             |     |

| Colmar                                   |     |

| Philadelphia/Horsham (215)957-4          | 100 |

| TENNESSEE                                |     |

| Knoxville                                | 841 |

| TEXAS                                    |     |

| Austin (512)502-2                        |     |

| Houston                                  |     |

| Plano                                    | 100 |

| VIRGINIA                                 |     |

| Richmond                                 | 100 |

| UTAH                                     |     |

| CSI Inc                                  | 010 |

| Bellevue                                 | 160 |

| Seattle Access                           |     |

| WISCONSIN                                | 100 |

| Milwaukee/Brookfield                     | 100 |

|                                          | 22  |

| Field Applications Engineering Available |     |

| Through All Sales Offices                |     |

| CANADA                                   |     |

| BRITISH COLUMBIA                         |     |

| Vancouver                                | 350 |

| ONTARIO                                  |     |

| Ottawa (613)226-34                       | 91  |

| Toronto                                  |     |

| QUEBEC                                   |     |

| Montreal                                 | 00  |

|                                          |     |

| NTERNATIONAL                             |     |

| AUSTRALIA                                |     |

| AUSTRALIA           |                 |

|---------------------|-----------------|

| Melbourne           | (61–3)98870711  |

| Sydney              |                 |

| BRAZIL              |                 |

| Sao Paulo           | 55(11)815-4200  |

| CHINA               | • •             |

| Beijing             | 86-10-8437222   |

| Guangzhou           | 86-20-7537888   |

| Shanghai            | 86-21-3747668   |

| Tianjin             | 86-22-5325072   |

| FINLAND             |                 |

| Helsinki            | 358-0-351 61191 |

| car phone           | 358(49)211501   |

| FRANCE              |                 |

| Paris               | 33134 635900    |

| GERMANY             |                 |

| Langenhagen/Hanover |                 |

| Munich              |                 |

| Nuremberg           | 49 911 96-3190  |

| Sindelfingen        | 49 7031 79 710  |

| Wiesbaden           | 49 611 973050   |

| HONG KONG           |                 |

| KwaiFong            | 852-2-610-6888  |

| Tai Po              | 852-2-666-8333  |

| INDIA               |                 |

| Bangalore           | 91-80-5598615   |

| ISRAEL              |                 |

| Herzlia             | 972–9–590222    |

|                     |                 |

| UFFICES                     |

|-----------------------------|

| ITALY                       |

| Milan                       |

| JAPAN                       |

| Fukuoka                     |

| Gotanda 81-3-5487-8311      |

| Nagoya                      |

| Osaka 81-6-305-1802         |

| Sendai 81-22-268-4333       |

| Takamatsu                   |

| Tokyo                       |

| KOREA                       |

| Pusan                       |

| Seoul                       |

| Penang 60(4)228-2514        |

| MEXICO                      |

| Mexico City                 |

| Guadalajara                 |

| Marketing                   |

| Customer Service            |

| NETHERLANDS                 |

| Best (31)4998 612 11        |

| PHILIPPINES                 |

| Manila                      |

| PUERTO RICO                 |

| San Juan                    |

| SINGAPORE                   |

| Madrid                      |

| or                          |

| SWEDEN                      |

| Solna                       |

| SWITZERLAND                 |

| Geneva                      |

| Zurich                      |

| TAIWAN                      |

| Taipei                      |

| THAILAND                    |

| Bangkok                     |

| UNITED KINGDOM<br>Aylesbury |

| Aylesbury                   |

|                             |

| FULL LINE REPRESENTATIVES   |

| CALIFORNIA, Loomis          |

|                             |

| GALIFURNIA, LOOMIS                    |

|---------------------------------------|

| Galena Technology Group (916)652-0268 |

| NEVADA, Reno                          |

| Galena Tech. Group (702)746-0642      |

| NEW MEXICO, Albuquerque               |

| S&S Technologies, Inc (602)414-1100   |

| UTAH, Salt Lake City                  |

| Utah Comp. Sales, Inc (801)561-5099   |

| WASHINGTON, Spokane                   |

| Doug Kenley (509)924-2322             |

| •••                                   |

|                                       |

|                                       |

### HYBRID/MCM COMPONENT SUPPLIERS

| Chip Supply                | (407)298-7100 |

|----------------------------|---------------|

| Elmo Semiconductor         | (818)768-7400 |

| Minco Technology Labs Inc. | (512)834-2022 |

| Semi Dice Inc              | (310)594-4631 |

|                            |               |

For changes to this information contact Technical Publications at FAX (602) 244-6561

### PREFACE

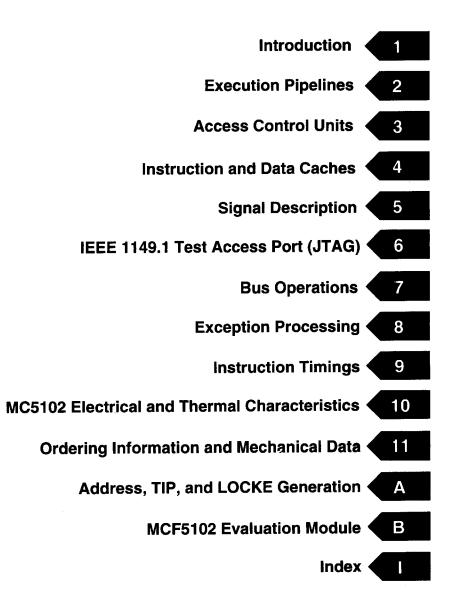

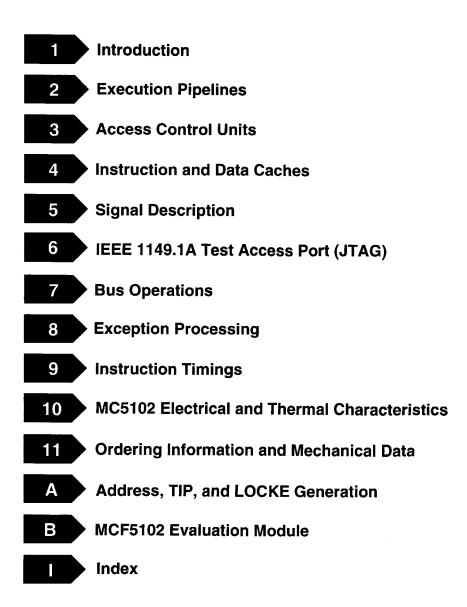

The MCF5102 Integrated Processor User's Manual describes the programming, capabilities, and operation of the MCF5102; the MCF5200 Programmer's Reference Manual provides instruction details for the processor core; and the MCF5102 Integrated Processor Product Brief provides an overview of the MCF5102.

The organization of this manual is as follows:

| Section 1:  | Introduction                             |

|-------------|------------------------------------------|

| Section 2:  | Execution Pipeline                       |

| Section 3:  | Access Control Units                     |

| Section 4:  | Instruction and Data Caches              |

| Section 5:  | Signal Description                       |

| Section 6:  | IEEE 1149.1A Test Access Port (JTAG)     |

| Section 7:  | Bus Operations                           |

| Section 8:  | Exception Processing                     |

| Section 9:  | Instruction Timing                       |

| Section 10: | Electrical and Thermal Characteristics   |

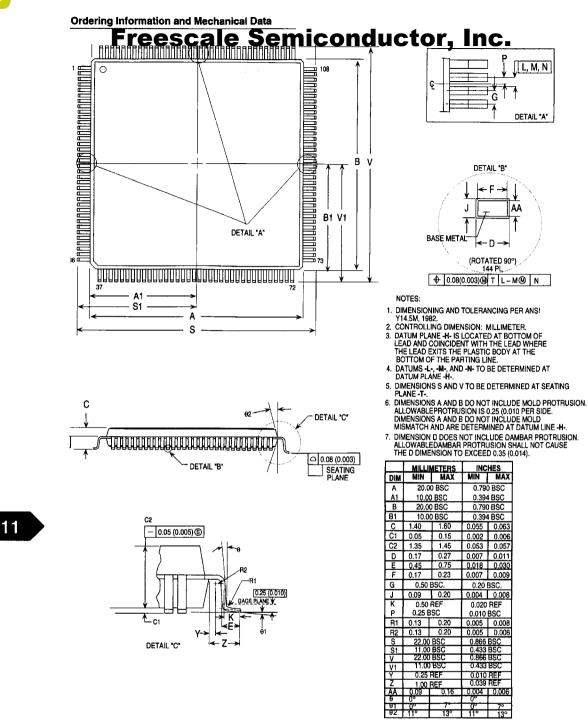

| Section 11: | Ordering Information and Mechanical Data |

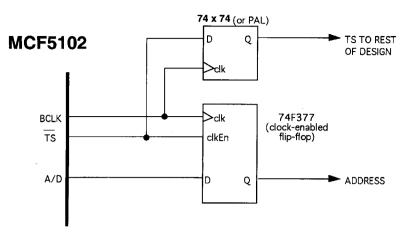

| Appendix A: | Address, TIP, and LOCKE Generation       |

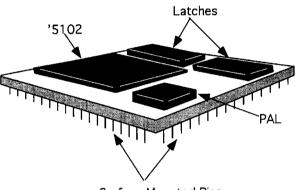

| Appendix B: | MCF5102 Evaluation Module                |

| Index       |                                          |

#### TRADEMARKS

All trademarks reside with their respective owners.

MOTOROLA

MCF5102 USER'S MANUAL REV. 1.0

۷

For More Information On This Product, Go to: www.freescale.com

## **Freescale Semiconductor, Inc.**

vi

MCF5102 USER'S MANUAL REV. 1.0

2.1

2.2

### **Freescale Semiconductor, Inc.**

### **Freescale Semiconductor, Inc.**

### **TABLE OF CONTENTS**

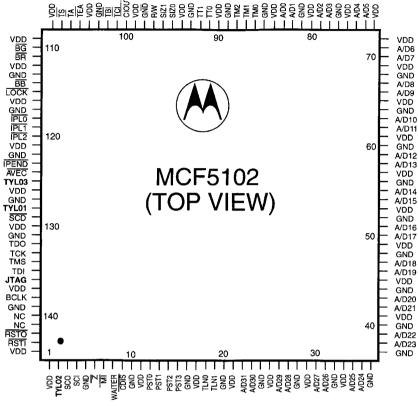

| Section<br>Number | Section 1<br>Introduction       | Page<br>Number |

|-------------------|---------------------------------|----------------|

| 1.1               | Features                        |                |

| 1.2               | Functional Blocks               |                |

| 1.3               | Processing States               | 1-4            |

| 1.4               | Programming Model               | 1-4            |

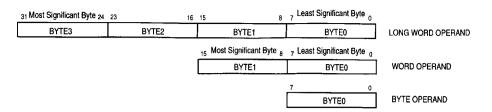

| 1.5               | Data Format Summary             | 1-7            |

| 1.6               | Addressing Capabilities Summary | 1-7            |

| 1.7               | Notational Conventions          | 1-9            |

| 1.8               | Instruction Set Overview        | 1-12           |

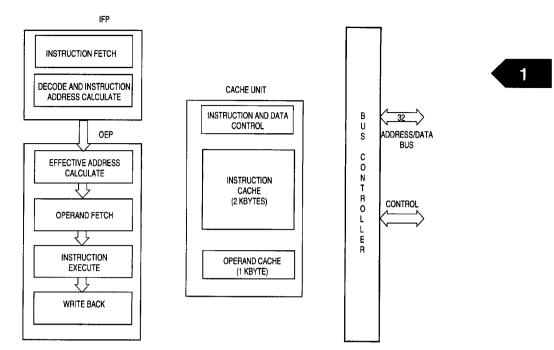

#### Section 2

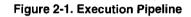

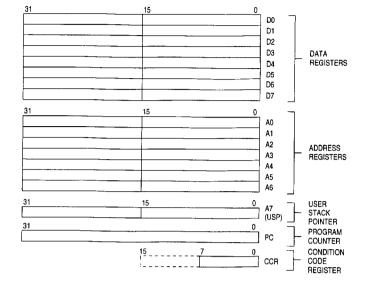

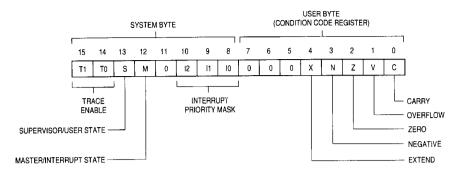

#### **Execution Pipelines** Pipelines ......2-1 Programming Model Registers ......2-3 User Programming Model......2-3 2.2.1 Data Registers (D7-D0). ......2-3 2.2.1.1 Address Registers (A6-A0). .....2-3 2.2.1.2 System Stack Pointer (A7). .....2-4 2.2.1.3 Program Counter......2-4 2.2.1.4 Condition Code Register ......2-5 2.2.1.5 Supervisor Programming Model ......2-5 2.2.2 2.2.2.1 2.2.2.2 Vector Base Register......2-7 2.2.2.3 2.2.2.4 Alternate Function Code Registers......2-7 Cache Control Register. ......2-7 2.2.2.5

### Section 3

#### **Access Control Units**

| 3.1 | Access Control Registers  |  |

|-----|---------------------------|--|

| 3.2 | Address Comparison        |  |

| 3.3 | Effect of RSTI On the ACU |  |

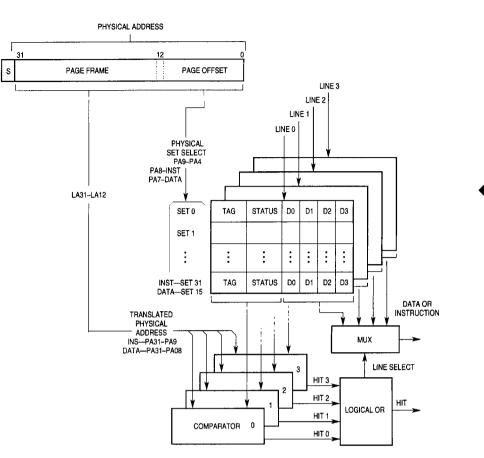

#### Section 4 Instruction and Data Caches

| 4.1     | Cache Operation   |  |

|---------|-------------------|--|

| 4.2     | Cache Management  |  |

| 4.3     | Caching Modes     |  |

| 4.3.1   | Cachable Accesses |  |

| 4.3.1.1 | Writethrough Mode |  |

|         |                   |  |

MOTOROLA

MCF5102 USER'S MANUAL REV. 1.0

For More Information On This Product, Go to: www.freescale.com

vii

### Table of Contents Freescale Semiconductor, Inc.

| 4.3.1.2 | Copyback Mode                         |      |

|---------|---------------------------------------|------|

| 4.3.2   | Cache-Inhibited Accesses              |      |

| 4.3.3   | Special Accesses                      | 4-6  |

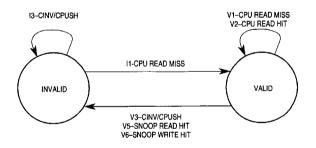

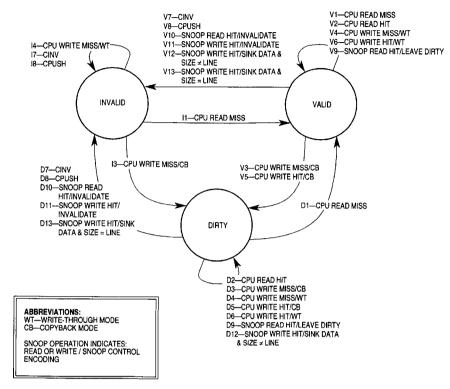

| 4.4     | Cache Protocol                        |      |

| 4.4.1   | Read Miss                             |      |

| 4.4.2   | Write Miss                            | 4-6  |

| 4.4.3   | Read Hit                              | 4-7  |

| 4.4.4   | Write Hit                             |      |

| 4.5     | Cache Coherency                       |      |

| 4.6     | Memory Accesses for Cache Maintenance | 4-9  |

| 4.6.1   | Cache Filling                         | 4-9  |

| 4.6.2   | Cache Pushes                          | 4-11 |

| 4.7     | Cache Operation Summary               |      |

| 4.7.1   | Instruction Cache                     | 4-12 |

| 4.7.2   | Data Cache                            | 4-13 |

#### Section 5

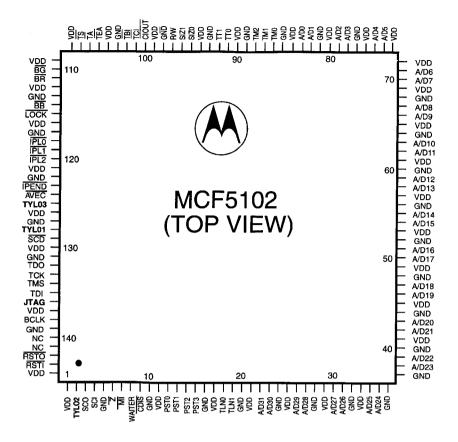

#### Signal Description 5.1 5.2 5.2.1 5.2.2 5.2.3 5.2.4 5.2.5 5.2.6 5.2.7 Bus Transfer Control Signals...... 5-6 5.3 5.3.1 5.3.2 5.3.3 Transfer Cache Inhibit (TCI) 5.3.4 5.3.5 5.4 5.4.1 5.4.2 5.5 5.5.1 5.5.2 5.5.3 5.6 5.6.1 5.6.2 5.6.3 5.7

viii

MCF5102 USER'S MANUAL REV. 1.0

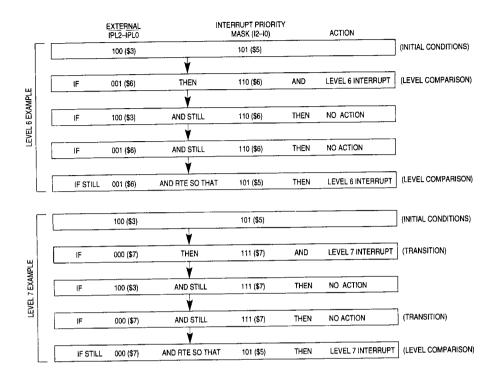

| 5.7.1 | Interrupt Priority Level (IPL[2:0]) |      |

|-------|-------------------------------------|------|

|       | Interrupt Pending Status (IPEND)    | 5-9  |

| 5.7.2 | Interrupt Pending Status (IPEND)    | E 0  |

| 5.7.3 | Autovector (AVEC)                   |      |

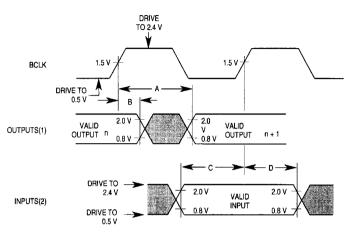

| 5.8   | Status and Clock Signals            |      |

| 5.8.1 | Processor Status (PST[3:0])         |      |

| 5.8.2 | Bus Clock (BCLK)                    |      |

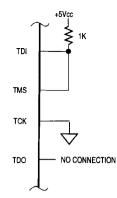

| 5.9   | Test Signals                        | 5-11 |

| 5.9.1 | Test Clock (TCK)                    |      |

| 5.9.2 | Test Mode Select (TMS)              | 5-12 |

| 5.9.3 | Test Data in (TDI)                  | 5-12 |

| 5.9.4 | Test Data Out (TDO)                 |      |

| 5.9.5 | Wait State Pin (WAITER)             | 5-12 |

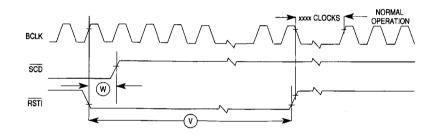

| 5.9.6 | System Clock Disable (SCD) Signal   |      |

| 5.9.7 | Z Signal                            | 5-12 |

| 5.10  | Power Supply Connections            |      |

| 5.11  | Signal Summary                      | 5-12 |

|       |                                     |      |

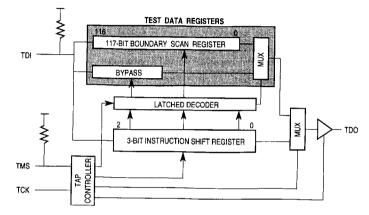

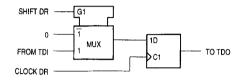

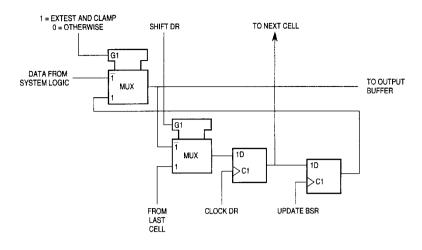

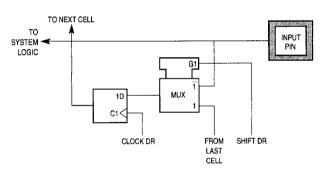

#### Section 6

#### IEEE 1149.1A Test Access Port (JTAG)

| Instruction Shift Register              | 6-2                                                                                                                                                                                                                                                         |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXTEST                                  | 6-3                                                                                                                                                                                                                                                         |

| HIGHZ                                   | 6-3                                                                                                                                                                                                                                                         |

| Sample/Preload                          | 6-3                                                                                                                                                                                                                                                         |

| CLAMP                                   | 6-4                                                                                                                                                                                                                                                         |

| BYPASS                                  | 6-4                                                                                                                                                                                                                                                         |

| Boundary-Scan Register                  | 6-4                                                                                                                                                                                                                                                         |

| Restrictions                            | 6-6                                                                                                                                                                                                                                                         |

|                                         |                                                                                                                                                                                                                                                             |

| MCF5102 JTAG Electrical Characteristics |                                                                                                                                                                                                                                                             |

| JTAG Pinout                             | 6-10                                                                                                                                                                                                                                                        |

| BSDL Description                        | 6-10                                                                                                                                                                                                                                                        |

|                                         | Instruction Shift Register<br>EXTEST<br>HIGHZ<br>Sample/Preload<br>CLAMP<br>BYPASS<br>Boundary-Scan Register<br>Restrictions<br>Disabling the IEEE Standard 1149.1a Operation<br>MCF5102 JTAG Electrical Characteristics<br>JTAG Pinout<br>BSDL Description |

### Section 7

#### **Bus Operation**

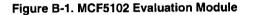

| 7.1     | Bus Characteristics                                   | 7-1  |

|---------|-------------------------------------------------------|------|

| 7.2     | Data Transfer Mechanism                               | 7-1  |

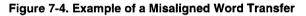

| 7.3     | Misaligned Operands                                   | 7-4  |

| 7.4     | Processor Data Transfers                              | 7-6  |

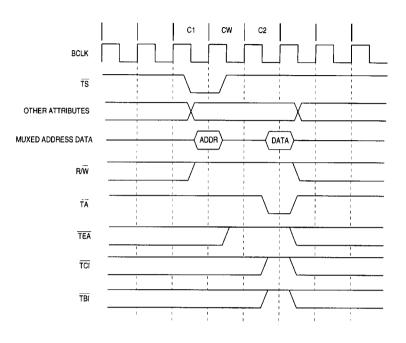

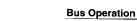

| 7.4.1   | Byte, Word, and Long-Word Read Transfers              | 7-6  |

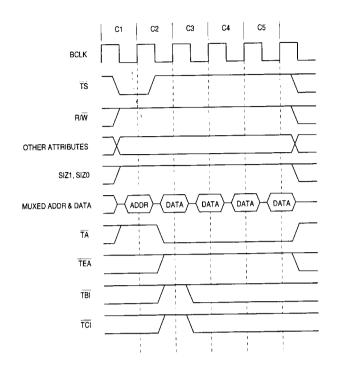

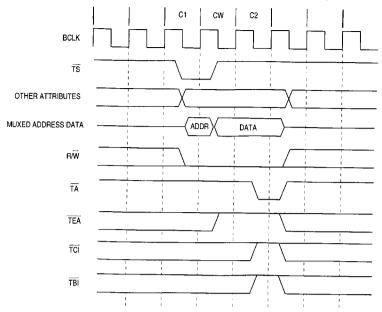

| 7.4.2   | Line Read Transfer                                    | 7-8  |

| 7.4.3   | Byte, Word, and Long-Word Write Transfers             |      |

| 7.4.4   | Line Write Transfers                                  | 7-13 |

| 7.4.5   | Read-Modify-Write Transfers (Locked Transfers)        |      |

| 7.5     | Acknowledge Bus Cycles                                | 7-15 |

| 7.5.1   | Interrupt-Acknowledge Bus Cycles                      | 7-15 |

| 7.5.1.1 | Interrupt Acknowledge Bus Cycle (Terminated Normally) | 7-15 |

MOTOROLA

#### MCF5102 USER'S MANUAL REV. 1.0

ix

## Table o Freescale Semiconductor, Inc.

| 7.5.1.2 | Autovector Interrupt-Acknowledge Bus Cycle     |      |

|---------|------------------------------------------------|------|

| 7.5.1.3 | Spurious Interrupt-Acknowledge Bus Cycle.      |      |

| 7.5.2   | Breakpoint Interrupt Acknowledge Bus Cycle     |      |

| 7.6     | Bus Exception Control Cycles                   |      |

| 7.6.1   | Bus Errors                                     |      |

| 7.6.2   | Retry Operation                                |      |

| 7.6.3   | Double Bus Fault                               |      |

| 7.7     | Bus Synchronization                            |      |

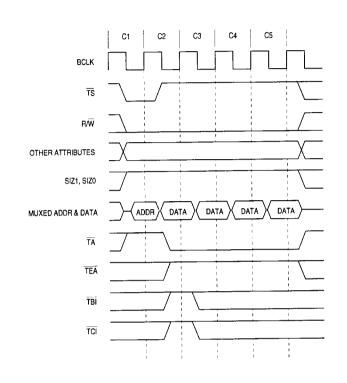

| 7.8     | Bus Arbitration                                |      |

| 7.9     | Bus Snooping Operation                         |      |

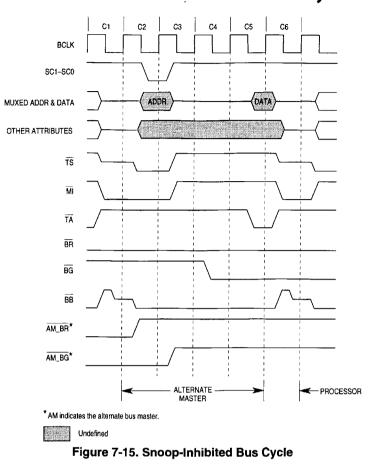

| 7.9.1   | Snoop-Inhibited Cycle                          |      |

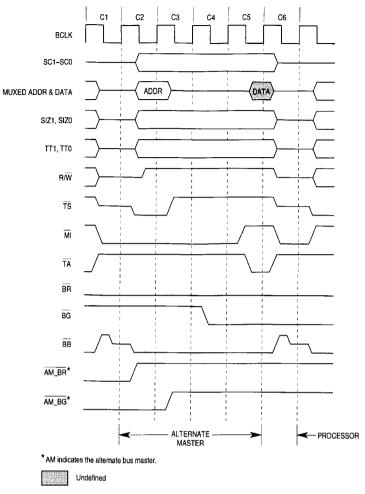

| 7.9.2   | Snoop-Enabled Cycle (No Intervention Required) |      |

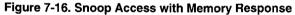

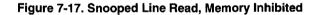

| 7.9.3   | Snoop Read Cycle (Intervention Required)       | 7-32 |

| 7.9.4   | Snoop Write Cycle (Intervention Required)      | 7-33 |

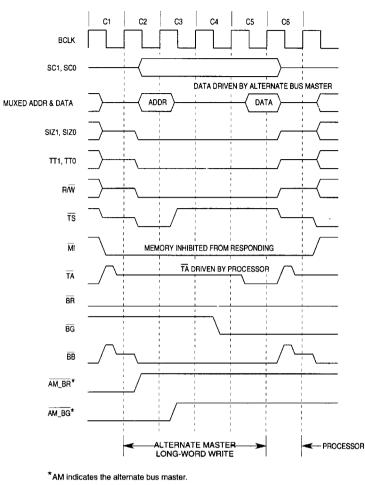

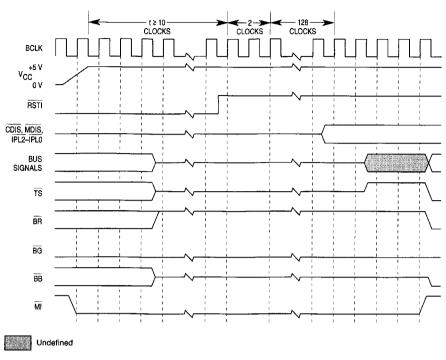

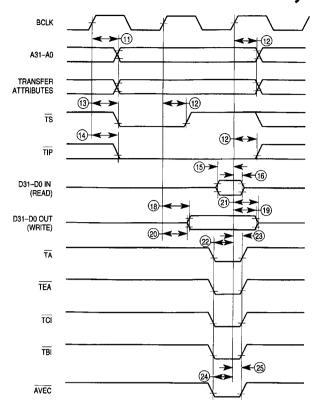

| 7.10    | Reset Operation                                |      |

|         |                                                |      |

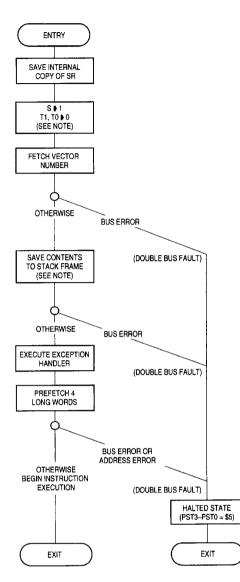

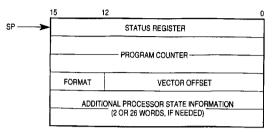

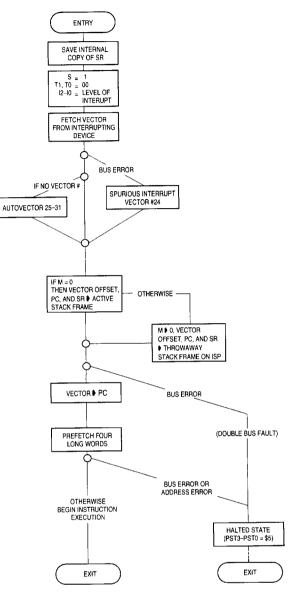

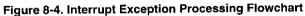

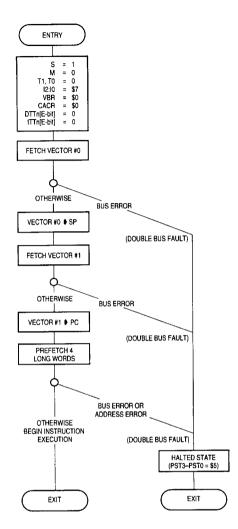

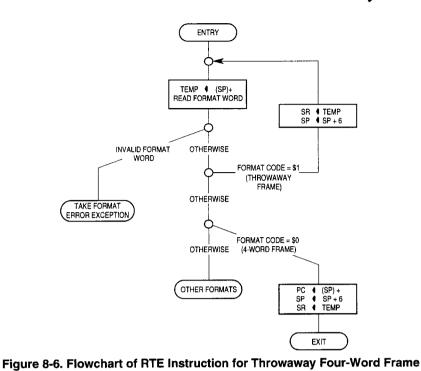

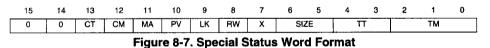

#### Section 8 Exception Processing

|         | Exception Trocessing                              |      |

|---------|---------------------------------------------------|------|

| 8.1     | Exception Processing Overview                     |      |

| 8.2     | Integer Unit Exceptions                           |      |

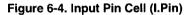

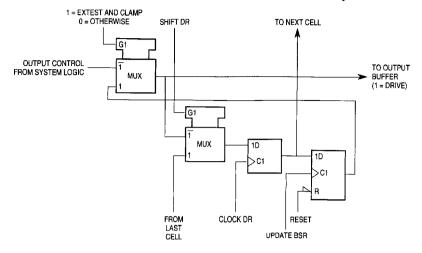

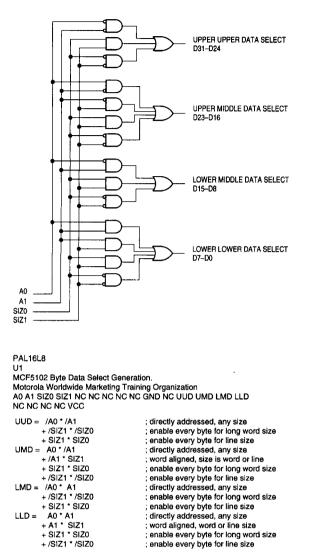

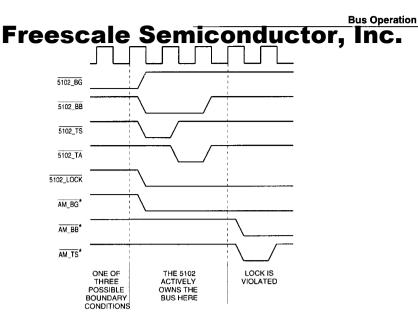

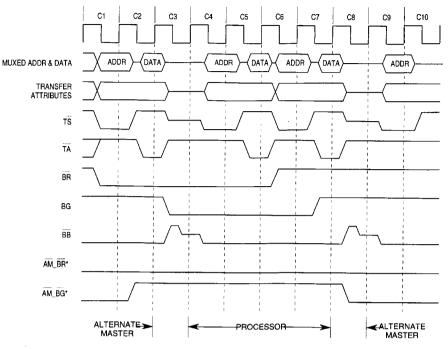

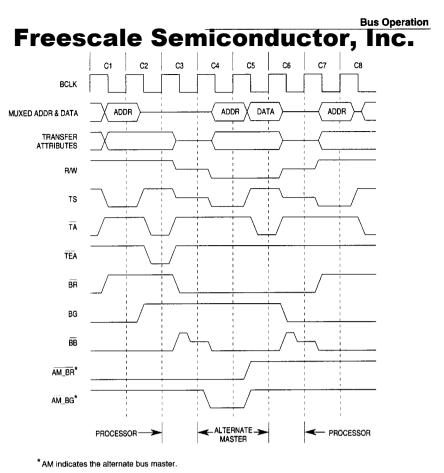

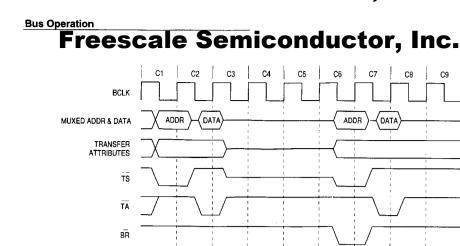

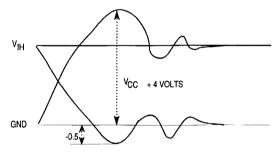

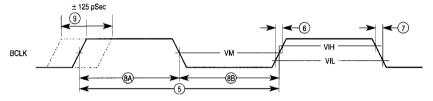

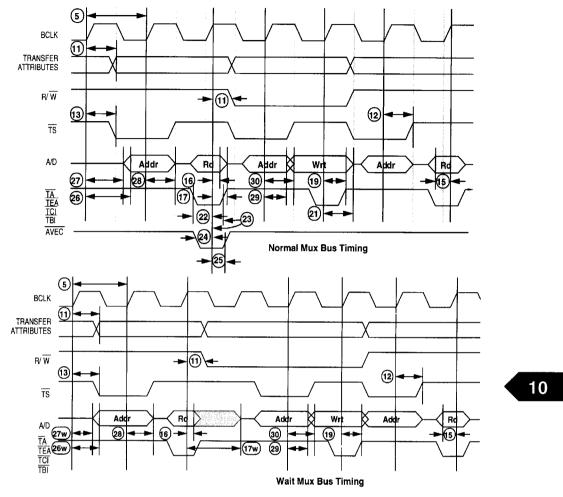

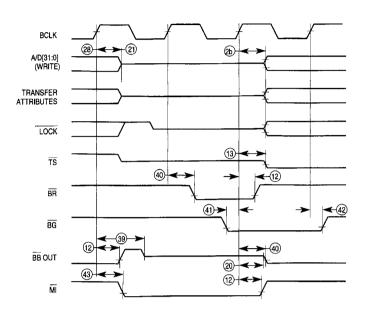

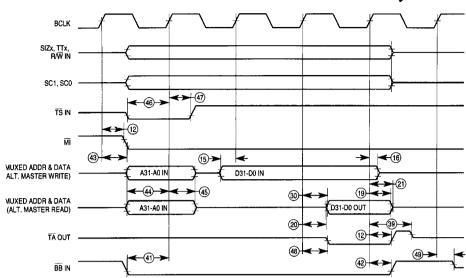

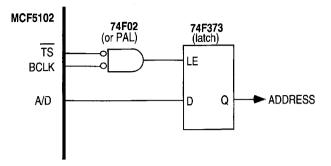

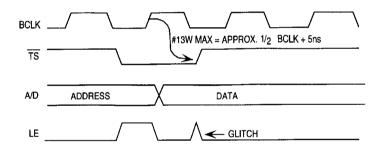

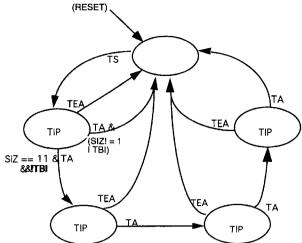

| 8.2.1   | Access Fault Exception                            |      |