# MMCCMB2114 Controller and Memory Board

**User's Manual**

#### **Important Notice to Users**

While every effort has been made to ensure the accuracy of all information in this document, Motorola assumes no liability to any party for any loss or damage caused by errors or omissions or by statements of any kind in this document, its updates, supplements, or special editions, whether such errors are omissions or statements resulting from negligence, accident, or any other cause. Motorola further assumes no liability arising out of the application or use of any information, product, or system described herein: nor any liability for incidental or consequential damages arising from the use of this document. Motorola disclaims all warranties regarding the information contained herein, whether expressed, implied, or statutory, *including implied warranties of merchantability or fitness for a particular purpose*. Motorola makes no representation that the interconnection of products in the manner described herein will not infringe on existing or future patent rights, nor do the descriptions contained herein imply the granting or license to make, use or sell equipment constructed in accordance with this description.

### **Equal Opportunity**

Motorola, Inc., is an Equal Opportunity / Affirmative Action Employer.

#### **Trademarks**

This document includes these trademarks:

Motorola and the Motorola logo are registered trademarks of Motorola, Inc.

Windows and Windows 95 are registered trademarks of Microsoft Corporation in the U.S. and other countries.

Intel is a registered trademark of Intel Corporation.

For an electronic copy of this book, visit Motorola's web site at http://mcu.motsps.com/documentation

© Motorola, Inc., 2002; All Rights Reserved

# **Contents**

|     | CMB2114 Quick Start Guide               | 9  |

|-----|-----------------------------------------|----|

|     | Section 1. General Information          | 13 |

| 1.1 | Introduction                            | 13 |

| 1.2 | CMB2114 Features                        | 13 |

| 1.3 | System and User Requirements            | 14 |

| 1.4 | CMB2114 Layout                          | 15 |

|     | Section 2. Preparation and Installation | 19 |

| 2.1 | Configuring Board Components            | 19 |

| 2.2 | Making Computer System Connections      | 25 |

| 2.3 | Performing the CMB2114 Selftest         | 26 |

| 2.4 | Memory Maps                             | 28 |

| 2.5 | Chip Select 1 Emulation                 | 30 |

| 2.6 | Memory Mapped I/O Operation             | 31 |

| 2.7 | Using the Prototyping Area              | 33 |

| 2.8 | Reprogramming the CPLD                  | 33 |

|     | Section 3. Support Information          | 35 |

| 3.1 | Embedded Code Debugging Options         | 35 |

| 3.2 | Using Metrowerks MetroTRK Debugger      |    |

| 3.3 | Using the SysDS Loader                  |    |

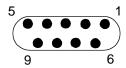

|     | Section 4. Connector Information        | 61 |

| 4.1 | MAPI Connectors                         | 61 |

| 4.2 | CPLD Programming Connector              | 69 |

| 4.3 | OnCE Connector                          | 70 |

| 4.4 | Logic Analyzer Connectors               | 71 |

| 4.5 | RS-232 Connectors                       | 75 |

| 4.6 | SRAM External Standby Power Connector   | 76 |

| 4.7 | Prototyping Connector Sites             | 76 |

|     | Index                                   | 81 |

Contents

# **Figures**

| 1-1  | MMCCMB2114 Controller and Memory Board Layout       | 16 |

|------|-----------------------------------------------------|----|

| 2-1  | User Option Switches (S1, S2) Factory Configuration | 23 |

| 2-2  | MMIO Register                                       | 31 |

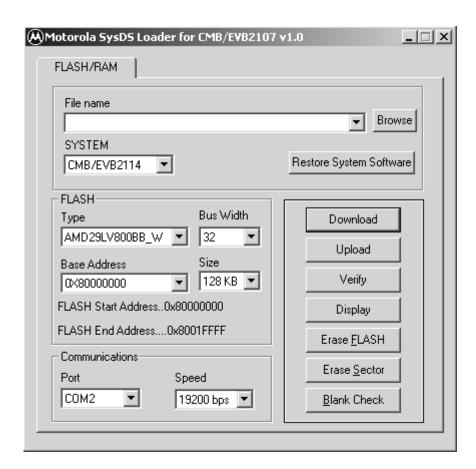

| 3-1  | On Chip FLASH Version SysDS Loader Main Screen      | 50 |

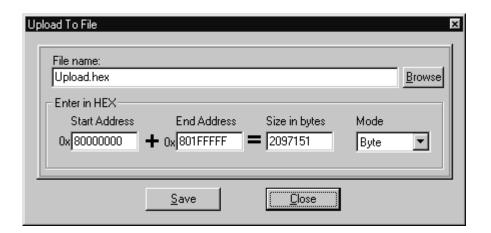

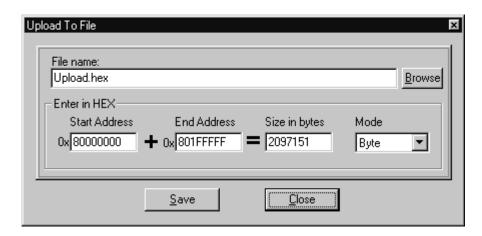

| 3-2  | Upload To File Dialog Box                           | 51 |

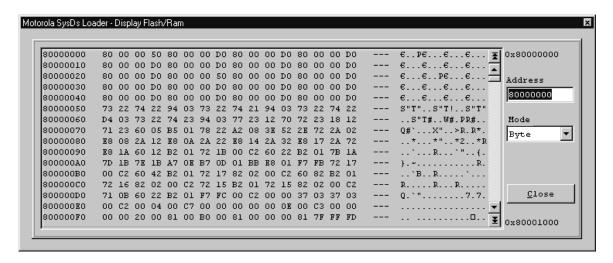

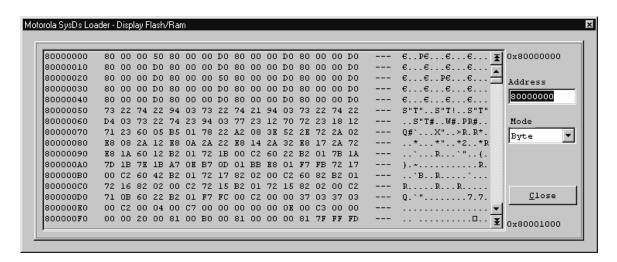

| 3-3  | Display Flash/Ram Screen                            | 53 |

| 3-4  | On Board SysDS Loader Version Main Screen           | 55 |

| 3-5  | Upload To File Dialog Box                           | 57 |

| 3-6  | Display Flash/Ram Screen                            | 58 |

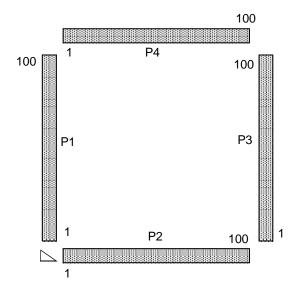

| 4-1  | MAPI Connectors Orientation                         | 61 |

| 4-2  | MAPI Connector P1/J1 Pin Assignments                | 62 |

| 4-3  | MAPI Connector P2/J2 Pin Assignments                | 64 |

| 4-4  | MAPI Connector P3/J3 Pin Assignments                | 66 |

| 4-5  | MAPI Connector P4/J4 Pin Assignments                | 68 |

| 4-6  | CPLD Programming Connector J6 Pin Assignments       | 70 |

| 4-7  | OnCE Connector J7 Pin Assignments                   | 71 |

| 4-8  | Logic Analyzer Connector J5 (A) Pin Assignments     | 72 |

| 4-9  | Logic Analyzer Connector J17 (D) Pin Assignments    | 73 |

| 4-10 | Logic Analyzer Connector J18 (C) Pin Assignments    | 74 |

| 4-11 | RS-232 Connector.                                   | 75 |

| 4-12 | Internal SRAM Standby External Power Connector      | 76 |

| 4-13 | Connector Location J40 Pin Assignments              | 77 |

| 4-14 | Connector Location J51 Pin Assignments              | 78 |

| 4-15 | Connector Location J52 Pin Assignments              | 79 |

| 4-16 | Connector Location J53 Pin Assignments              | 80 |

Figures

# **Tables**

| 1-1  | MMCCMB2114 Controller and Memory Board Specifications. | . 17 |

|------|--------------------------------------------------------|------|

| 2-1  | Component Settings                                     | . 19 |

| 2-2  | CMB2114 Selftest LED Sequence                          | . 27 |

| 2-3  | Default Memory Map                                     | . 28 |

| 2-4  | Joint CMB2114/MPFB1200 Memory Map                      | . 29 |

| 2-5  | Alternate Memory Map                                   | . 30 |

| 3-1  | Picobug Commands                                       | . 36 |

| 4-1  | MAPI Connector P1/J1 Signal Descriptions               | . 63 |

| 4-2  | MAPI Connector P2/J2 Signal Descriptions               | . 65 |

| 4-3  | MAPI Connector P3/J3 Signal Descriptions               | . 67 |

| 4-4  | MAPI Connector P4/J4 Signal Descriptions               | . 69 |

| 4-5  | CPLD Programming Connector J6 Signal Descriptions      | . 70 |

| 4-6  | OnCE Connector J7 Signal Descriptions                  | . 71 |

| 4-7  | Logic Analyzer Connector J5 (A) Signal Descriptions    | . 72 |

| 4-8  | Logic Analyzer Connector J17 (D) Signal Descriptions   | . 73 |

| 4-9  | Logic Analyzer Connector J18 (C) Signal Descriptions   | . 74 |

| 4-10 | RS-232 Connector J57, J58 Pin Assignments              | . 75 |

| 4-11 | Connector Location J40 Signal Description              | . 77 |

| 4-12 | Connector Location J51 Signal Descriptions             | . 78 |

| 4-13 | Connector Location J52 Signal Descriptions             | . 79 |

| 4-14 | Connector Location J53 Signal Descriptions             | . 80 |

Tables

# CMB2114 Quick Start Guide

Make sure that power is disconnected from your MMCCMB2114 Controller and Memory Board (CMB2114), and from your development system. Then follow these quick-start steps to make your CMB2114 ready for use as quickly as possible.

#### **ESD CAUTION:**

Motorola development systems include open-construction printed circuit boards that contain static-sensitive components. These boards are subject to damage from electrostatic discharge (ESD). To prevent such damage, you must use static-safe work surfaces and grounding straps, as defined in ANSI/EOS/ESD S6.1 and ANSI/EOS/ESD S4.1. All handling of these boards must be in accordance with ANSI/EAI 625.

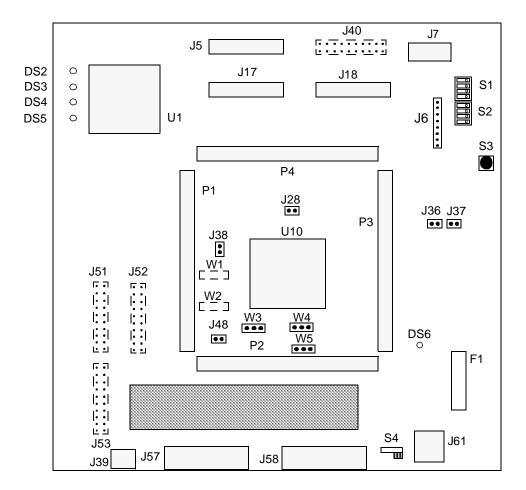

## Set the User Option Switches to Their Factory Defaults

Your CMB2114 contains two user option switches, S1 and S2. Each switch contains four subswitches. Make sure that subswitches USR0 and USR2 of user option switch S2 are set in the OFF position. The remaining subswitches of both the user option switches should be set in the ON position.

## Set the Jumper Headers to Their Factory Defaults

- 1. Make sure that a jumper is installed in power headers J28, J37, J38, and J48.

- 2. Make sure that a jumper is installed between pin 2 and 3 of jumper header W3.

- 3. Make sure that a jumper is installed between pins 1 and 2 of jumper headers W4 and W5.

- 4. Make sure *there is no jumper installed* between pads 1 and 2 of jumper header J50.

## Connect the CMB2114 to Your Computer System

To connect your CMB2114 to a computer system:

- Connect an RS-232 cable between CMB2114 connector J58 labelled PORT A on the silkscreen and the appropriate serial port of your computer.

- Connect your 12-volt power supply to line power and to CMB2114

connector J61 labelled +12V PWR IN on the silkscreen. Use switch S4

to turn power on. The green colored LED DS6 lights to confirm that the

CMB2114 is powered.

#### Note

Should the LED DS6 not light, you may need to replace the fuse at location F1, next to power connector J61. Use a BUS GMA-1.5A fast blow fuse, or comparable.

## **Start the Picobug Monitor**

The Picobug monitor comes burned into the external FLASH memory devices of your CMB2114.

#### **Notes**

Before you start the Picobug monitor, make sure that you have an RS-232 connection between CMB2114 connector J58 and a serial port of your computer. Make sure that power to your CMB2114 is turned off.

The commands and menu selections in the instructions provided in this subsection are specific to the Hyperterminal terminal-emulation program. If you use a different terminal-emulation program, you must make corresponding changes in the commands and menu selections of the instructions provided in this subsection.

To start the monitor for use as a standalone debugger by using Hyperterminal:

- 1. Start the Hyperterminal program.

- 2. Select **File>Properties**.

- 3. Select the COM port being used by the host computer from the **Connect using** list box in the **Properties** dialog box.

- 4. Click the **Configure** button in the **Properties** dialog box.

- 5. Use the **Configuration** dialog box to set the communications properties:

- 19200 baud

- 8 data bits

- no parity

- 1 stop bit

- no flow control

- select the appropriate communications port

- 6. Click OK.

- 7. Apply power to the CMB2114. The Picobug monitor starts automatically, displaying the command prompt: picobug>.

## **Download and Run Sample Application**

- 1. Type 10 at the picobug command prompt and press Enter.

- 2. In the HyperTerminal menu bar, select **Transfer>Send Text File**. The **Send Text File** window appears.

- 3. Navigate to the following directory on the MMC2114 CD-ROM root directory:

- Dev\_Sys\Mmc2114\Quickstart\Sample\_led\_app. This location contains the sample project files.

- 4. Double-click the out.elf.s file. The application code starts to get transferred to the CMB2114. This operation may take a few moments.

- Once the file has been downloaded, the following message appears on the picobug prompt: "Done downloading. The target PC is set to 8xxx xxxx"

## **CAUTION:**

Do not cycle power supply (turn OFF and ON) while the application is being downloaded to the board. This will cause the download operation to fail.

5. Type g at the picobug prompt and press Enter. This runs the application on the CMB2114.

The User Status LEDs DS5 through DS2 momentarily display the 5 (0101) flashing pattern. The pattern then changes to A (1010). Next, the program walks a bit from LED DS2 to LED DS5 to light each LED independently. Finally, all LED's are lit up. This pattern then repeats at a faster rate. The fast and slow patterns are repeated continuously till the program is stopped.

#### CMB2114 Quick Start Guide

6. To stop the application and return to the picobug prompt, press the RESET switch S3 on the CMB2114.

For more information on using picobug monitor and other debugging utilities, refer **Section 3.**

## **Section 1. General Information**

#### 1.1 Introduction

The MMCCMB2114 Controller and Memory Board (CMB2114) is a development tool for Motorola's M•CORE™ processor family that lets you develop code to be embedded in an MMC2114 microcontroller unit (MCU).

As a standalone tool, the CMB2114 uses an RS-232 connection to your computer. This connection lets you use Motorola's M•CORE System Development Software (SysDS), the GNU source-level debugger, or the Metrowerks MetroTRK debug software. The SysDS consists of a loader, the Picobug monitor, and a built-in selftest. The CMB2114 also has a OnCE<sup>TM</sup> connector, enabling you to use a debugging application that requires one.

Optionally, you may use the CMB2114 with a different emulator product, such as the Motorola Enhanced Background Debug Interface (EBDI), or the Metrowerks CodeWarrior<sup>TM</sup> integrated development environment (IDE).

Motorola's SysDS loader lets you download your code into the FLASH memory of the MMC2114 MCU and the CMB2114 for execution or for storage in non-volatile memory. You can also use Motorola's SysDS loader to download you code into the static random access memory (SRAM) of CMB2114 for execution.

The CMB2114 combines easily with other, optional development boards from Motorola, such as the MPFB1200 Platform Board. Such an optional board expands CMB2114 capacity, enhances CMB2114 performance, or adds to CMB2114 features.

#### 1.2 CMB2114 Features

The CMB2114 features:

- 144-pin, quad flat pack MMC2114 resident MCU.

- 2 megabytes FLASH memory, configurable for 16- or 32-bit operations.

- 2 megabytes fast static RAM (FSRAM), configurable for 16- or 32-bit operations.

- Xilinx complex programmable logic device (CPLD).

- Connector header for programming Xilinx CPLD.

#### **General Information**

- On-board 5-volt and 3.3-volt supply.

- ON/OFF power switch and power LED.

- Two RS-232 serial communication ports.

- On Chip Emulation (OnCE) connector.

- External clock input connector.

- Four user-accessible light emitting diodes (LEDs.)

- Two dual inline package (DIP) switches for system configuration and firmware selection.

- User prototyping (breadboard) area.

- A modular, all purpose interface (MAPI 400) connector ring, on the top and bottom of the CMB2114, for easy connection to other, compatible development boards.

- Three 38-pin Mictor logic analyzer connectors.

- Motorola's SysDS.

- Metrowerks MetroTRK debug software

- GNU source-level debugger (from the Free Software Foundation).

- Metrowerks CodeWarrior<sup>TM</sup> IDE (30-day trial version)

- Four locations for optional, user-installed prototyping connectors

- External clock source connector

- 5 volts or 3.3 volts Analog to Digital Convertor (ADC) operation

- Break out pads for GPIO, interrupts, SCI, timer, and analog-digital converter (ADC) signals.

## 1.3 System and User Requirements

You need an IBM PC or compatible computer, running the Windows 9x/2000 or Windows NT 4.0 operating system. The computer requires a Pentium or equivalent microprocessor, 64 megabytes of RAM, 150 megabytes of free hard-disk space, a Super Video Graphics Array (SVGA) color monitor, and an RS-232 serial-communications port. To use the Picobug debug monitor, you also need Hyperterminal or a comparable terminal-emulation program.

To get the most from your CMB2114, you should be an experienced C or M•CORE assembly programmer.

The power supply that comes with your CMB2114 converts line power to the input power that the CMB2114 needs: 12 volts @ 1.2 amperes.

## 1.4 CMB2114 Layout

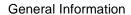

Figure 1-1 shows the layout of the CMB2114. Connectors P1 through P4, on the top of the board, are the MAPI I/O and interrupt connectors. The corresponding MAPI connectors on the bottom of the CMB2114 are J1 through J4.

Connector J6 is the CPLD programming connector. Connector J7 is the OnCE connector. Connectors J5, J17, and J18 are the logic analyzer connectors. Connector J36 is for external standby power for internal SRAM. Connector J39 is a surface-mount adapter (SMA) connector for external clock input. Connector J57 and J58 are the port B and port A RS-232 serial connectors, respectively. Connector J61 is the connector for 12-volt input power.

Switches S1 and S2 configure several aspects of memory organization and access. Switch S3 is the reset switch. Switch S4 is the power switch.

Several two-pin jumper headers are convenient current measurement points for various power signals:

- J28, 3.3-volt power to the resident MCU at location U10;

- J37, standby power for internal SRAM;

- J38, power for internal FLASH; and

- J48, 5-volt or 3.3-volt power to the queued analog-digital converter (QADC).

To measure the current of any of these signals, temporarily remove the jumper, then connect the leads of your meter to the header pins.

Jumper headers W1 and W2 let you select a 3.3-volt or 5-volt ADC supply. The factory configuration specifies 5-volt ADC supply. These jumper headers are not populated on the board.

Jumper headers W3 through W5 enable you to select either an on-board crystal oscillator or an external clock.

Figure 1-1 MMCCMB2114 Controller and Memory Board Layout

LEDs DS2 through DS5 are general-purpose status indicators. LED DS6 confirms operating power.

The CMB2114 prototyping area is adjacent to MAPI connector P2 and the RS-232 connectors (J57, J58). Ground connections are the left and right columns of this area. The area's top row includes connection points for Analog Power (APWR), Analog Ground (AGND), 3.3 volts, and 5 volts.

Note the four groups of eyelets at the sites J40, J51, J52, and J53 in the upper-right and lower-left areas of the CMB2114. Although the factory does not populate these sites, you may access many signals at these sites. For this, you may install prototyping connectors that must be 2-by-10-pin connectors with pins at 0.1-inch centers, such as the Berg 69192-620 connector.

Location F1 is for the CMB2114 fuse.

The resident MCU, at location U10, is an MMC2114 device, in a 144-pin QFP package. The CPLD is at location U1.

Table 1-1 lists CMB2114 specifications.

**Table 1-1 MMCCMB2114 Controller and Memory Board Specifications**

| Characteristic                    | Specifications                                                                       |

|-----------------------------------|--------------------------------------------------------------------------------------|

| MCU extension I/O port            | High speed complementary metal oxide semiconductor (HCMOS) compatible                |

| Operating temperature             | 0° to 40° C                                                                          |

| Storage temperature               | -40° to +85° C                                                                       |

| Relative humidity                 | 0 to 90% (non-condensing)                                                            |

| Reference clock crystal frequency | 8 megahertz                                                                          |

| External clock                    | 32, 24, 16 or 8 megahertz, depending on the Phase Locked Loop (PLL) setting          |

| Power requirements                | 12 volts dc, at a minimum of 150-milliamperes, provided from a separate power source |

| Dimensions                        | 6.9 x 8.2 inches (175 x 208 mm)                                                      |

**General Information**

# Section 2. Preparation and Installation

You can follow the instructions in this chapter to configure your CMB2114, and hook it up to your computer system.

#### **ESD CAUTION:**

Motorola development systems include open-construction printed circuit boards that contain static-sensitive components. These boards are subject to damage from electrostatic discharge (ESD). To prevent such damage, you must use static-safe work surfaces and grounding straps, as defined in ANSI/EOS/ESD S6.1 and ANSI/EOS/ESD S4.1. All handling of these boards must be in accordance with ANSI/EAI 625.

## 2.1 Configuring Board Components

Table 2-1 is a summary of configuration settings.

**Table 2-1 Component Settings**

| Component                                          | Position | Effect                                                                                                                                                                                                                                    |

|----------------------------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                    | ON       | This setting configures the board to boot from chip-select-0 (CS0) memory, and disables the internal FLASH of the board.  Default factory setting.                                                                                        |

| User Options Switch<br>S1, Boot Ex/In<br>Subswitch | OFF      | In master mode, this setting configures the board to boot from internal-FLASH memory.  In emulation mode, this setting configures internal FLASH emulation on chip-select-1 (CS1) memory. However, the board cannot boot from CS1 memory. |

| Data 32/16 subswitch                               | ON       | This setting specifies a 32-bit external data bus.  Default factory setting.                                                                                                                                                              |

| of user option switch<br>S1                        | OFF      | This setting specifies a 16-bit external data bus. Microcontroller unit (MCU) data lines 15—0 become general purpose input-output (GPIO) lines, and are available at J40.                                                                 |

**Table 2-1 Component Settings (Continued)**

| Component                                                           | Position                                                             | Effect                                                                                                                          |

|---------------------------------------------------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Swap 02/20 subswitch of user option switch                          | ON                                                                   | This setting configures the board for CS0 control of external FLASH and chip-select-2 (CS2) control of external SRAM.           |

| S1                                                                  |                                                                      | Default factory setting.                                                                                                        |

|                                                                     | OFF                                                                  | This setting configures the board for CS2 control of external FLASH and CS0 control of external SRAM.                           |

|                                                                     | Subswitch M0 — ON<br>Subswitch M1 — ON                               | This setting configures the board to run in master mode.                                                                        |

|                                                                     |                                                                      | Default factory setting.                                                                                                        |

| M0 subswitch of user                                                | Subswitch M0 — ON                                                    | This setting configures the board to run in emulation mode and disables internal FLASH emulation on CS1.                        |

| options switch S1 and M1 subswitch of user option switch S2         | Subswitch M1 — OFF                                                   | In addition to this setting, CS1 should be configured for normal operation by turning Boot Ex/In and Swap 02/20 subswitches ON. |

|                                                                     | Subswitch M0 — OFF<br>Subswitch M1 — ON                              | This setting configures the board to run in single-chip mode.                                                                   |

|                                                                     | Subswitch M0 — OFF<br>Subswitch M1 — OFF                             | This setting configures the board to run in emulation mode and enables internal FLASH emulation on CS1.                         |

|                                                                     | Subswitch USR0 — OFF<br>Subswitch USR1 — OFF<br>Subswitch USR2 — OFF | This setting specifies built-in selftest firmware module to be run out of reset.                                                |

|                                                                     | Subswitch USR0 — OFF<br>Subswitch USR1 — ON<br>Subswitch USR2 — OFF  | This setting specifies Picobug monitor firmware module to be run out of reset.  Default factory setting.                        |

| User Option Switch S2,<br>USR0 — USR2<br>Subswitches <sup>(1)</sup> | Subswitch USR0 — ON<br>Subswitch USR1 — OFF<br>Subswitch USR2 — OFF  | This setting specifies Programmer firmware module to be run out of reset.                                                       |

|                                                                     | Subswitch USR0 — ON<br>Subswitch USR1 — ON<br>Subswitch USR2 — OFF   | This setting specifies MetroTRK firmware module to be run out of reset.                                                         |

|                                                                     | Subswitch USR0 — ON<br>Subswitch USR1 — ON<br>Subswitch USR2 — ON    | This setting specifies user code to be run out of reset.                                                                        |

**Table 2-1 Component Settings (Continued)**

| Component                                                                                    | Position | Effect                                                                                                                                                 |

|----------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reset Switch, S3                                                                             |          | Push S3 to reset all board components.                                                                                                                 |

| Power Switch, S4                                                                             | OFF      | Setting S4 to the OFF position turns power OFF.  Default factory setting.                                                                              |

|                                                                                              | ON       | Setting S4 to the ON position turns power ON.                                                                                                          |

|                                                                                              |          | A jumper installed on a power header connects the specified power signal.                                                                              |

| <ul><li>Power Headers:</li><li>MCU 3V (J28)</li><li>Internal RAM standby (J37)</li></ul>     |          | A jumper installed on each power header is the default factory setting.  You should leave the jumper installed on the power headers during normal use. |

| <ul> <li>Internal chip<br/>FLASH voltage<br/>(J38)</li> <li>ADC voltage<br/>(J48)</li> </ul> | 00       | With the jumpers removed, meter leads can be connected to the individual pins of any power header to measure the current of the power signal.          |

**Table 2-1 Component Settings (Continued)**

| Component                             | Position                                                                                                                                     | Effect                                                                                                                 |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

|                                       | W3 — Jumper between pins 2 and 3<br>W4 — Jumper between pins 2 and 3<br>W5 — Jumper between pins 2 and 3<br>J50 — Don't care                 | Selects on-board crystal (Y1) as clock source with Phase Locked Loop (PLL) enabled.                                    |

|                                       | W3 — Jumper between pins 2 and 3 W4 — Jumper between pins 1 and 2 W5 — Jumper between pins 1 and 2 J50 — Jumper pads 1 and 2 open            | Selects on-board clock oscillator (Y2) as clock source with Phase Locked Loop (PLL) enabled.  Default factory setting. |

| Jumper headers W3,<br>W4, W5, and J50 | W3 — Jumper between pins 2 and 3<br>W4 — Jumper between pins 1 and 2<br>W5 — Jumper between pins 1 and 2<br>J50 — Jumper pads 1 and 2 closed | Selects the external clock input at J39 as clock source with Phase Locked Loop (PLL) enabled.                          |

|                                       | W3 — Jumper between pins 1 and 2 W4 — Jumper between pins 1 and 2 W5 — Jumper between pins 1 and 2 J50 — Jumper pads 1 and 2 open            | Selects on-board clock oscillator (Y2) as clock source with Phase Locked Loop (PLL) disabled.                          |

|                                       | W3 — Jumper between pins 1 and 2<br>W4 — Jumper between pins 1 and 2<br>W5 — Jumper between pins 1 and 2<br>J50 — Jumper pads 1 and 2 closed | Selects the external clock input at J39 as clock source with Phase Locked Loop (PLL) disabled.                         |

<sup>1.</sup> USR0, USR1, and USR2 subswitch settings other than those specified in this table will select the Picobug monitor firmware module to be run out of reset.

## 2.1.1 Setting the User Option Switches

The subswitches of user option switches S1 and S2 configure several aspects of board initialization and operation, including the mode of operation and the firmware module to be run out of reset. Figure 2-1 shows the factory configuration:

- 32-bit, external data bus;

- CS0 controls the boot memory and the external FLASH;

- Internal FLASH is disabled;

- CS2 controls the SRAM;

- Master mode; and

- Picobug firmware module to be run out of reset.

Figure 2-1 User Option Switches (S1, S2) Factory Configuration

For a different configuration, reset the S1 and S2 subswitches per Table 2-1.

**Note** Changes you make to settings of the Boot Ex/In, Data 32/16, Swap 02/20, M0, or M1 subswitches do not take effect until the next reset or powerup of your CMB2114.

## 2.1.2 Using the Power Headers (J28, J37, J38, J48)

Your CMB2114 has the following power headers:

- J28 3.3-volt power to the U10 resident MCU,

- J37 standby power for internal SRAM of the U10 resident MCU,

- J38 power for internal FLASH of the U10 resident MCU,

- J48 5-volt or 3.3-volt power to the queued analog-digital converter (QADC).

During normal use of your CMB2114, leave the jumpers on all of these headers.

To measure the current of any of these signals:

- 1. Turn CMB2114 power off by setting switch S4 to the OFF position.

- 2. Remove the jumper from the power header to be checked.

#### Preparation and Installation

- 3. Connect meter leads to the header pins.

- 4. Turn CMB2114 power ON by using switch S4, and read the current from the meter.

- 5. Turn CMB2114 power OFF by using switch S4.

- 6. Disconnect the meter leads from the power header you just checked.

- 7. Reinstall the jumper in the power header.

- 8. Restore power by setting switch S4 to the ON position.

#### 2.1.3 Setting Jumper Headers

The jumper headers in CMB2114 allow you to select power supply and clock sources. Detailed explanations of the jumper settings follow.

#### 2.1.3.1 Jumper Headers W1 and W2

Jumper headers W1 and W2 allow you to select power supply for the internal analog-digital converter (ADC). These jumper headers are not populated on the board. The factory ships your CMB2114 with a 0-ohm resistance installed between pads 1 and 2 of components R24 and R25, which are in parallel to jumper headers W1 and W2, respectively. This setting for W1 and W2 specifies 5-volt VDDH and 5-volt VDDA to the ADC, respectively.

Alternatively, you can specify 3.3-volt VDDH and 3.3-volt VDDA to the ADC, respectively. For this, you need to first remove the 0-ohm resistance installed between pads 1 and 2 of components R24 and R25. Next, install the 0-ohm resistance between pads 2 and 3 of components R24 and R25.

#### 2.1.3.2 Jumper Headers W3, W4, W5, and J50

The CMB2114 has an on-board crystal oscillator at locationY1, an on-board clock oscillator at location Y2, and an external clock input at location J39. Additionally, their outputs can be routed through a PLL that allows you to set the desired clock frequency.

Jumper headers W3, W4, W5, and J50 allow you to select either an on-board clock source or an external clock source. The settings of these jumper headers also determine if the PLL is enabled or diabled. Jumper headers W3, W4, and W5 are three-pin headers, while jumper header J50 is a two-pin header in which you can install a 0-Ohm resistance.

The factory setting is:

- A jumper between pins 2 and 3 of jumper header W3

- A jumper between pins 1 and 2 of jumper headers W4 and W5

- A jumper wire installed between pads 1 and 2 of jumper header J50.

This setting selects the on-board clock oscillator as the clock source to the MMC2114 MCU with the PLL enabled.

For alternative settings of clock sources, refer **Table 2-1**.

## 2.2 Making Computer System Connections

When you have configured your CMB2114, you are ready to connect it to your computer system:

- 1. Disconnect power from your CMB2114 and from your development system.

- 2. For RS-232 communication directly with your host computer, connect an RS-232 cable between CMB2114 connector J58 (port A) and the appropriate serial port of your computer.

- 3. Alternatively, to you use an Enhanced Background Debug Interface (EBDI) with your CMB2114, connect the 14-lead target cable between CMB2114 connector J7 and the EBDI. Then use an RS-232 cable to connect the EBDI to your host computer. Using an EBDI means that you do not need to use CMB2114 connector J58 at all. However, a target board could communicate through connector J58.

- For using an EBDI, the Boot Ex/In sub switch must be set to the OFF position so that the board boots from the internal memory.

- 4. Optional: If your code, running in a target board, supports RS-232 communication with the CMB2114, you can connect a second RS-232 cable between the target board and CMB2114 connector J57 (port B).

- 5. Optional: You may use the CMB2114 with an MPFB1200 platform board.

To do so, you must:

- a. Connect the boards via their MAPI rings.

- b. Hold the CMB2114 directly above the other board.

- c. Turn the CMB2114 so that the right-triangle silk screen markings line up. Then press the CMB2114 down onto the other board. CMB2114 connectors J1 through J4, on the bottom of the board, must connect with the corresponding MAPI connectors P1 through P4, on the top of the other board.

- 6. Optional: You may use a logic analyzer with the CMB2114. If you do, connect appropriate cables to any of the logic analyzer connectors: J5, J17, or J18. Such a cable must terminate with a compatible Mictor connector. Section 4 includes pin assignments and cable descriptions for the logic analyzer connectors. (Note the Tektronix-pattern pin numbering.)

- 7. If you are using the CMB2114 as a standalone tool, connect your 12-volt power supply to line power and to CMB2114 connector J61. Use switch S4 to turn on power. The green colored LED DS6 lights to confirm that the CMB2114 is powered.

- Should the LED DS6 *not* light, you may need to replace the fuse at location F1, next to power connector J61. Use a BUS GMA-1.5A fuse, or compatible.

- 8. If you did connect the CMB2114 to a platform board, apply power to the platform board per its instructions. LED DS6 lights to confirm that the CMB2114 receives power from the platform board. (As in step 6, should the LEDs *not* light, you may need to replace the platform-board fuse.)

This completes system connections. You are ready to perform a selftest, per the instructions of subsection 2.4. You can begin debugging or other development activities, per the instructions of Chapter 3.

## 2.3 Performing the CMB2114 Selftest

Once you have configured your CMB2114, you can perform a selftest of its components.

- 1. Turn off CMB2114 power by setting switch S4 to the OFF position. Power LED DS6 should be out.

- 2. Set switch S2 for the built-in selftest. Subswitches USR0, USR1, and USR2 should all be in the OFF position.

- 3. Turn on power by using switch S4. LED DS6 lights to confirm power, and the CMB2114 begins its selftest.

4. LEDs DS2 through DS5 light and go out during the test, according to the sequence shown in Table 2-2.

**Table 2-2 CMB2114 Selftest LED Sequence**

| DS2 | DS3 | DS4 | DS5                              | Test Action                  |

|-----|-----|-----|----------------------------------|------------------------------|

| OFF | ON  | OFF | ON                               | 8-bit write to memory.       |

| ON  | OFF | ON  | OFF                              | 8-bit read from memory. (1)  |

| OFF | ON  | OFF | ON                               | 16-bit write to memory.      |

| ON  | OFF | ON  | OFF 16-bit read from memory. (1) |                              |

| OFF | ON  | OFF | ON                               | 32-bit write to memory.      |

| ON  | OFF | ON  | OFF                              | 32-bit read from memory. (1) |

- Should all four LEDs stay lit at this point, the CMB2114 has failed the SRAM test, aborting the rest of the selftest. Contact Motorola customer support for assistance.

- 5. Then individual LEDs light several times in the sequence, DS5, DS4, DS3, and DS2.

- 6. When all four LEDs go out, the CMB2114 has passed the selftest. If any LEDs stay lit, the CMB2114 has failed the selftest. Contact Motorola customer support for assistance.

- 7. Turn off CMB2114 power by using switch S4.

- 8. Configure subswitches USR0, USR1, and USR2 for your next development activity before restoring power to the CMB2114.

## 2.4 Memory Maps

Table 2-3 shows the default memory map where the Swap 02/20 subswitch is ON.

**Table 2-3 Default Memory Map**

| Address Range              | Sub Range                  | Memory Resource                                                           | Related<br>Chip Select |  |

|----------------------------|----------------------------|---------------------------------------------------------------------------|------------------------|--|

| 0x8000_0000<br>0x801F FFFF |                            | CMB FLASH<br>(2 megabytes)                                                |                        |  |

| UXOUTF_FFFF                | 0x8000_0000<br>0x8001_FFFF | System System Software (128 kilobytes Sectors 0—3)                        |                        |  |

|                            | 0x8002_0000<br>0x801F_FFFF | User Code<br>(1920 kilobytes<br>Sectors 4 — 18)                           | CS0                    |  |

| 0x8020_0000<br>0x807F_FFFF |                            | User address space<br>(6 megabytes)                                       |                        |  |

| 0x8100_0000<br>0x811F_FFFF |                            | CMB SRAM<br>(2 megabytes) <sup>(1)</sup>                                  |                        |  |

|                            | 0x8100_0000<br>0x8100_BFFF | Reserved for System<br>Software<br>(48 kilobytes)                         |                        |  |

|                            | 0x8100_C000<br>0x811F_FFFF | User Code<br>(2000 kilobytes)                                             | CS2                    |  |

| 0x8120_0000<br>0x817F FFFB |                            | User address space (6 megabytes) <sup>(1)</sup>                           |                        |  |

| 0x817F_FFFC                |                            | MMIO read-only byte<br>(reads in USR0, USR1,<br>USR2 subswitch settings.) |                        |  |

| 0x817F_FFFD                |                            | MMIO write-only byte<br>(controls LEDs)                                   |                        |  |

If you use the CMB2114 with an MPFB1200 platform board, and if platform-board SRAM is associated with the same chip select as CMB2114 SRAM, the MMIO function uses the last four bytes of CMB SRAM.

Table 2-4 shows the combined memory map for a CMB2114 and an MPFB1200 platform board, each with factory settings. This yields eight megabytes each of FLASH memory and SRAM.

Note

Note that CMB2114 factory settings configure the board to run in master mode. This memory map also is valid for CMB2114 emulation mode, with chip-select 1 internal FLASH emulation disabled.

The CMB2114 Data 32/16 subswitch must be ON for this MPFB1200 memory map to be valid, but the CMB2114 Boot Ex/In subswitch has no effect on the map.

Table 2-4 Joint CMB2114/MPFB1200 Memory Map

| Address Range              | Use                          | Size                   | Chip<br>Select |

|----------------------------|------------------------------|------------------------|----------------|

| 0x8000_0000<br>0x801F_FFFF | CMB2114 FLASH                | 2 megabytes            | CS0            |

| 0x8020_0000<br>0x807F_FFFF | MPFB1200 FLASH               | 6 megabytes            | CS0            |

| 0x8080_0000<br>0x809F_FFFF | [Unused]                     |                        |                |

| 0x80A0_0000<br>0x80FF_FFFF | MPFB1200 SRAM <sup>(1)</sup> | 6 megabytes            | CS1            |

| 0x8100_0000<br>0x811F_FFFF | CMB2114 SRAM                 | 2 megabyte             | CS2            |

| 0x8120_0000<br>0x817F_FFFF | [Unused]                     |                        |                |

| 0x8180_0000<br>0x8180_0FFF | MPFB1200 Peripherals         | 4 kilobytes            | CS3            |

| 0x8180_1000<br>0x818F_FFFF | MPFB1200 User Space D        | 1 megabyte<br>(almost) | CS3            |

For the alternate MPFB SRAM address range 0x8120\_0000 through 0x817F\_FFFB, use the MPFB main SRAM jumper header (W2) to select CS2.

Table 2-5 shows the alternate CMB2114 memory map where the Swap 02/20 subswitch is OFF.

Table 2-5 Alternate Memory Map

| Address Range | Memory Resource                                                              | Related<br>Chip Select |

|---------------|------------------------------------------------------------------------------|------------------------|

| 0x8000_0000   | CMB SRAM                                                                     |                        |

| 0x801F_FFFF   | (2 megabytes)                                                                |                        |

| 0x8020_0000   | User address space                                                           |                        |

| 0x807F_FFFB   | (6 megabytes)                                                                | CS0                    |

| 0x807F_FFFC   | MMIO read-only byte<br>(reads in USR0, USR1,<br>USR2 subswitch<br>settings.) |                        |

| 0x807F_FFFD   | MMIO write-only byte (controls LEDs)                                         |                        |

| 0x8100_0000   | CMB FLASH                                                                    |                        |

| 0x811F_FFFF   | (2 megabytes)                                                                | CS2                    |

| 0x8120_0000   | User address space                                                           | 032                    |

| 0x817F_FFFF   | (6 megabytes)                                                                |                        |

Note

Using the alternate memory map means that you cannot use the Motorola system software, which is FLASH based. For debugging in the alternate memory map, you must use an EBDI or other product that communicates through the OnCE interface.

## 2.5 Chip Select 1 Emulation

Chip select 1 emulation pertains to three cases of M1, M0, and Swap 02/20 subswitch settings.

Case I—M1 OFF, M0 OFF, Swap 02/20 ON.

These subswitch settings configure emulation mode. MCU memory range  $0x0000\_0000 - 0x0003\_FFFF$ , under chip-select-1 control, gets mapped to CMB2114 SRAM. Chip select 2 provides access to the same physical memory, but at CMB2114 addresses  $0x8104\_0000 - 0x8107\_FFFF$ . Motorola system software programs chip select 1 for one wait state.

**Note** Chip-select-1 emulation is not an exact simulation of internal FLASH operation, which has no wait states. Actual internal FLASH operation is faster than chip-select-1 emulation.

• Case II—M1 OFF, M0 OFF, Swap 02/20 OFF.

These subswitch settings also configure emulation mode. MCU memory range  $0x0000\_0000 - 0x0003\_FFFF$ , under chip-select-1 control, gets mapped to CMB2114 internal FLASH. Chip select 2 provides access to the same physical memory, but at CMB2114 addresses  $0x8004\_0000 - 0x8007\_FFFF$ . For debugging in this configuration, you must use an EBDI or other product that communicates through the OnCE interface. (Motorola system software does not support this configuration.)

• Case III—M1 OFF, M0 ON, Swap 02/20 ON.

These subswitch settings also configure emulation mode. Chip select 1 does not specify any CMB2114 memory. Motorola system software disables chip-select-1 emulation, and programs chip select 1 for three wait states. In this configuration, your code can use chip select 1 to specify platform-board or other user-defined memory.

## 2.6 Memory Mapped I/O Operation

The MCU operating mode determines the implementation of memory mapped I/O (MMIO) operation.

1. In master or emulation mode, the CPLD MMIO register reads the settings of subswitches USR0 through USR2 and controls the status LEDs DS2 through DS5. The register consists of two bytes, as shown in Figure 2-2. These bytes are mapped to the first two bytes of the last valid SRAM 32-bit address.

| 817F_FFFC (807F_FFFC) |      |      |           | 817F_FFFD (807F_FFFD) |          |         |         |         |         |

|-----------------------|------|------|-----------|-----------------------|----------|---------|---------|---------|---------|

| D31                   | D30  | D29  | D28 — D24 | D23 — D21             | D20      | D19     | D18     | D17     | D16     |

| USR2                  | USR1 | USR0 | Not Used  | Not Used              | Not Used | LED DS5 | LED DS4 | LED DS3 | LED DS2 |

Figure 2-2 MMIO Register

#### Preparation and Installation

The upper byte of the register is read only.

- Bits D31 through D29 show the positions of subswitches USR2 through USR0, respectively. A subswitch OFF setting produces a 1 bit value; a subswitch ON setting produces a 0 bit value.

- This byte is at address 0x817F\_FFFC (or 0x807F\_FFFC if the Swap 02/20 subswitch is OFF).

The lower byte of the register is write only and is cleared by a reset.

- Bits D19 through D16 control status LEDs DS5 through DS2, respectively: set bits turn ON the corresponding LEDs, clear bits turn OFF the corresponding LEDs.

- This byte is at address 0x817F\_FFFD (or 0x807F\_FFFD if the swap 02/20 subswitch is OFF).

- 2. In single chip mode, Port H controls USR subswitch and status LED functionality.

- Port H bit 7 must be configured as a low output.

- Port H bits 6 though 4 read the settings of subswitches USR2 through USR0, respectively.

- Port H bits 3 through 0 control status LEDs DS5 through DS2, respectively: set bits turn ON the corresponding LEDs, clear bits turn OFF the corresponding LEDs.

## 2.7 Using the Prototyping Area

The CMB2114 prototyping area lets you add your own components to the board. Merely insert the component's feet through holes in the board, then solder the feet in place to hold the component in position. Run appropriate leads from the new component to board power and ground locations.

Note the connection points of the prototyping area:

- Ground columns on either side,

- Analog power three points at the upper-left corner,

- Analog ground three points of the top row,

- 3.3 volt power three points of the top row, and

- 5-volt power three points at the upper-right corner.

The prototyping connector site J40 is in the upper-right area and the prototyping connector sites J51, J52, and J53 are in the lower-left area of the board, respectively.

## 2.8 Reprogramming the CPLD

You can reprogram the CPLD if you want to add test circuits through the CPLD instead of hard wiring to the bread board, and to add circuits to simulate development software, such as an interval interrupt generator.

To reprogram the CPLD you need:

- A parallel cable (model DLC5) for connection between the parallel port of the host PC and the CPLD programming connector J6. This cable can be purchased from Xilinx.

- Xilinx Foundation series software version 3.1i or higher or Webpack ISE software version 3.21 or higher. The Webpack ISE program is freeware and can be downloaded from the Xilinx website:

```

www.xilinx.com/sxpresso/webpack.htm

```

You can use the projects provided on the MMC2114 CD to reprogram the CPLD. The MMC2114 CD contains the Verilog version of the project as well as the schematic entry version that uses the Foundation tool.

The schematic entry version and the Verilog version of the project are located at the following path on the MMC2114 CD:

Schematic entry — Dev Sys/MMC2114/CPLD/PD042.zip

#### Preparation and Installation

Verilog — Dev Sys/MMC2114/CPLD/PD042 verilog.zip

#### Note

The schematic entry version of the project requires Foundation software for synthesis. However, the Verilog version of the project can be used with Webpack as well as Foundation software.

You can modify the project source files according to your requirements.

### **CAUTION:**

- 1. Do not remove modules in the project source files as they are critical to system operation.

- 2. Do not try to change the pin assignments of the CPLD as these are fixed by the layout.

You can also restore the factory settings of the CPLD by using the same projects. Instructions for restoring the factory settings of the CPLD are provided in a text file on the MMC2114 CD at the following location:

Dev\_Sys/MMC2114/CPLD/readme.txt

•

## **Section 3. Support Information**

You can follow the instructions in this chapter for using the debugging tools available for your CMB2114 and for using Motorola's SysDS Loader.

## 3.1 Embedded Code Debugging Options

You have several options available for debugging embedded code. To debug embedded code, you may use:

- The Picobug monitor as standalone software

- The GNU source-level debugger with the Picobug monitor

- Metrowerks Target Resident Kernel (MetroTRK) debugger

Other firms may produce additional software to run, test, and modify the code you develop for embedding in a MMC2114 MCU.

## 3.1.1 Using the Picobug Monitor

The Picobug monitor comes burned into the external FLASH memory devices of your CMB2114. Before you start the Picobug monitor, make sure that you have an RS-232 connection between CMB2114 connector J58 and a serial port of your computer.

You need the Hyperterminal terminal-emulation program to use the Picobug monitor as a standalone debugger. If you use a different terminal-emulation program, you must make corresponding changes in the commands and menu selections of the instructions provided in this subsection.

To start the monitor for use as a standalone debugger by using Hyperterminal:

- 1. Disconnect power from your CMB2114.

- 2. Start the Hyperterminal program.

- 3. Select **File > Properties**. The **Properties** dialog box appears.

- 4. Select the COM port being used by the host computer from the **Connect using** list box in the **Properties** dialog box.

- 5. Click the **Configure** button in the **Properties** dialog box. The **Configuration** dialog box appears.

#### **Support Information**

- 6. Use the configuration dialog box to set the communications properties:

- 19200 baud

- 8 data bits

- no parity

- 1 stop bit

- no flow control

- select the appropriate communications port

- 7. Click **OK**.

- 8. Set the subswitches of user option switch S2 to specify the Picobug firmware module. Set the USR0 and USR2 subswitches in the OFF position, and USR1 subswitch in the ON position.

- 9. Reconnect power to the CMB2114 and press the reset switch (S3.)

The Picobug monitor starts automatically, displaying the command prompt: picobug>.

To use the Picobug monitor, merely enter commands at the prompt. Table 3-1 explains these commands. To see a list of these commands on your computer screen, type a question mark or type he at the command prompt.

**Table 3-1 Picobug Commands**

| Command      | Explanation                                                                                                                                                                                                                                |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| br [address] | Breakpoint:  • With optional address value, sets a new breakpoint at that address.  • Without any address value, lists all current breakpoints.                                                                                            |  |

| g [address]  | Go:  • With optional address value, starts code execution from that address.  • Without any address value, starts code execution from the current program-counter value.  In either case, execution stops when it arrives at a breakpoint. |  |

| gr           | Go to Return:  Executes code from the current program-counter value to the return address of the calling routine. (Should execution arrive at a breakpoint before encountering the return address, execution stops at the breakpoint.)     |  |

| gt [address] | ess]  Go to Address:  Executes code from the current program-counter value to the specified address value. (Should execution arrive at a breakpoint before encountering the specified address, execution stops at the breakpoint.)         |  |

| he           | Help Displays available commands, identical to the ? command.                                                                                                                                                                              |  |

**Table 3-1 Picobug Commands (Continued)**

| Command                             | Explanation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| lo [address]                        | Download:  • With optional address value, downloads a binary image to that address in SRAM.  • Without any address value, downloads to SRAM an S-record text file.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| md [address1 [address2]]<br>[;size] | Memory Display:  • With optional address1 and address2 values, displays memory contents between the addresses.  • With optional address1 value, displays contents of 16 memory bytes.  • With no address value, defaults to the last address viewed.  • The optional size value specifies the format: b (bytes, the default), h (half words), w (words), or i (instructions).                                                                                                                                                                                                                                                                                                                                          |

| mds [address]                       | Memory Display 256:  • With optional address value, displays contents of 256 memory bytes, starting at that address.  • With no address value, displays contents of 256 memory bytes, starting from the last address viewed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| mm [address [value]] [;size]        | <ul> <li>Modify Memory:</li> <li>With optional address and value parameter values, assigns that value to the address location.</li> <li>With optional address value but no value parameter value, prompts for a value for the address location, then prompts for a new value for the next location. To stop modification, enter a period instead of a new value.</li> <li>With no optional address value, prompts for a value for the last address viewed, then prompts for a new value for the next location. To stop modification, enter a period instead of a new value.</li> <li>The optional size value, specifies the format: b (bytes, the default), h (half words), w (words), or i (instructions).</li> </ul> |

| nobr [address]                      | No Breakpoint:  • With optional address value, removes the breakpoint from that address.  • Without any address value, removes all the breakpoints.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| reset                               | Reset: Resets the CPU and peripherals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| rd [name]                           | Register Display:  • With optional <i>name</i> value, displays the value of that CPU register.  • Without any <i>name</i> value, displays the values of all CPU registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| rm [name [value]]                   | Register Modify: Assigns the <i>value</i> parameter value to the <i>name</i> CPU register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| t                                   | Trace (Step): Single steps one instruction; identical to the s command.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| S                                   | Step (Trace):<br>Single steps one instruction; identical to the t command.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ?                                   | Help Displays available commands, identical to the he command.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

## 3.1.2 Picobug Sample Session

1. This sample session begins with the Picobug prompt:

picobug>

2. To see the contents of all registers, enter the Register Display (rd) command without any name value:

```

picobug> rd

```

The system responds with a display such as this:

|                   |          | 50100002 | fpc      | fffffffe | epc      | 8101d0c0 | рс      |

|-------------------|----------|----------|----------|----------|----------|----------|---------|

|                   |          | 04000200 | fpsr     | 80000000 | epsr     | 80000000 | psr     |

| r 8100dc00        | vbr      | 00c90800 | 00000100 | 02200008 | 80010040 | bad0beef | ss0-ss4 |

| 00000009 8100b000 | 0000000  | 00002000 | 00c30000 | 80010040 | 817ffffd | bad0beef | r0-r7   |

| 8100e7c4 8001125c | 000000c0 | 00cc0004 | 0800000  | 0000000f | 80010040 | 81000024 | r8-r15  |

3. To see the contents of a specific register, such as the epc register, enter the Register Display (rd) command *with* the name value:

```

picobug> rd epc

```

The system responds with a display such as this:

```

epc: FFFFFFE

```

4. To see the contents of a specific memory location, enter the Memory Display (md) command with the location address. An optional size value (in this case w, for word) may be part of the command:

```

picobuq> md 0x8101d000 ; w

```

The system responds with a display such as this:

```

8101D000: 710B1210

```

5. To see the contents of a memory range, enter the Memory Display (md) command with the beginning and ending addresses. An optional size value (in this case b, for byte) may be part of the command:

```

picobug> md 0x8101d000 0x8101d016 ; b

```

The system responds with a display such as this:

```

8101D000: 71 0B 12 10 7F 0B 00 00 24 70 9F 00 8F 00 20 70 q......$p....p

8101D010: 00 CF 00 00 24 70 9F

```

6. To download into SRAM a program executable, in S-record format, enter the Download (lo) command without any address value:

```

picobug> lo

```

The system waits for you to send the program executable file. To do so, open the Transfer menu and select Send Text File. This opens a file-select dialog box. Use this dialog box to specify the appropriate S-record file, then click the Open button. As soon as the download is complete (this may take several minutes), a confirmation message appears, followed by the Picobug prompt:

```

Done downloading. The target PC is set to 8101d000.

\label{eq:pc} \mbox{picobug>}

```

7. To see the new contents of registers, enter the Register Display (rd) command again, without any name value:

```

picobug> rd

```

The system responds with an updated display, which shows that the pc register value reflects the start of the program just downloaded:

|                   |          | 50100002 | fpc      | fffffffe | epc      | 8101d000 | рс      |

|-------------------|----------|----------|----------|----------|----------|----------|---------|

|                   |          | 04000200 | fpsr     | 80000000 | epsr     | 80000000 | psr     |

| 8100dc00          | vbr      | 00c90800 | 00000100 | 02200008 | 80010040 | bad0beef | ss0-ss4 |

| 00000009 8100b000 | 0000000  | 00002000 | 00c30000 | 80010040 | 817ffffd | bad0beef | r0-r7   |

| 8100e7c4 8001125c | 000000c0 | 00cc0004 | 0800000  | 0000000f | 80010040 | 81000024 | r8-r15  |

8. To set a breakpoint at address 0x8101d11e, enter this address as part of the Breakpoint (br) command:

```

picobug> br 0x8101d11e

```

The Picobug prompt reappears, confirming that the system set the breakpoint:

picobug>

9. To see the list of breakpoints, enter the Breakpoint (br) command *without* any address value:

```

picobug> br

```

The system responds with the addresses of breakpoints, in this case only the breakpoint set in step 8:

8101D11E

10. To start program execution, enter the Go (g) command:

```

picobug> g

```

In this instance, the breakpoint set during step 8 stops code execution. The system responds with this new display of register values:

At breakpoint!!

|                         | 50100002 | fpc      | 8101d11e | epc      | 8101d11e | рс        |

|-------------------------|----------|----------|----------|----------|----------|-----------|

|                         | 04000200 | fpsr     | 80000100 | epsr     | 80000100 | psr       |

| vbr 8100dc00            | 00c90800 | 00000100 | 02200008 | 80010040 | bad0beef | ss0-ss4   |

| 00000 00000001 817ffffd | 00002000 | 0000001  | 00000000 | 8101f000 | 8101efd8 | r0-r7     |

| 000c0 8100e7c4 8101d056 | 00cc0004 | 0800000  | 000000f  | 80010040 | 8101efd8 | r8-r15    |

|                         |          |          | r6, (r7) | stb      | B607     | 8101D11E: |

11. To remove all breakpoints, enter the No Breakpoint (nobr) command, without any address value:

```

picobug> nobr

```

The Picobug prompt reappears, confirming that the system has removed the breakpoints:

picobug>

12. To see the list of breakpoints again, once more enter the Breakpoint (br) command without any address value:

```

picobug> br

```

As there are no longer any breakpoints, the system responds with the Picobug prompt:

picobug>

- 13. To continue with this example session, enter another appropriate command. For example, to resume program execution, enter the Go (g) command.

- 14. To end your Picobug session, remove power from the CMB and close the terminal-emulation program.

## 3.1.3 Using the GNU Source-Level Debugger

The GNU source-level debugger is on the CD-ROM that comes with your CMB2114. The GNU software works with the Picobug monitor to provide source-level debugging for your code.

Install the GNU software by performing the following steps:

1. Insert the MMC2114 CD-ROM into your CD-ROM drive. The install shield should begin automatically. If the install shield does not start automatically, select **Start>Run**. The **Run** dialog box appears. Use the **Run** dialog box to run the Autorun.exe file of the CD-ROM.

- 2. An M•CORE install shield screen appears. Click the M•CORE Tools button. This brings up a second install shield screen.

- To install GNU software, click the second screen's Install GNU Tools button, then follow the instructions of successive screens. An installation-complete message appears, indicating successful installation.

**Note** Install GNU software into the default directory. Do not browse. Changing the installation directory may give undesirable results.

4. Click the **OK** in the installation-complete message box to return to the second install shield screen.

After the installation is complete, configure your CMB2114 for using GNU software by performing the following steps:

- 1. Disconnect power from your CMB2114.

- 2. Connect the RS-232 cable between CMB2114 connector J58 and the serial port of your computer. If appropriate for your serial port, use the DB9/DB25 adapter.

- 3. Make sure switches S1 and S2 have the factory settings. Subswitches USR0 and USR2 should be in the OFF position and subswitch USR1 should be in the ON position.

- 4. Make sure that your +12-volt power supply is turned off or disconnected from line power. Connect the power supply cable to CMB2114 connector J61.

- 5. Apply power to your CMB2114. Green LED DS6 lights to confirm power.

Next, build a sample application by performing the following steps:

- 1. Copy the CD-ROM subdirectory dev\_sys\MMC2114\gnusample to the root directory of your hard disk. For example, the root directory C:\.

- 2. Open an MS-DOS window, and change to the gnusample subdirectory of your hard disk.

- 3. When the MS-DOS prompt returns, type testgnu and press the Enter key. This action loads, compiles, and links the sample application. Ignore any "could not find" messages. Leave the MS-DOS window open.

# NP

#### Support Information

Note:

If the GNU tools do not work after you have installed them, your initial environment space may be lesser than 4096 bytes. The way to make this setting may be different for each system. For assistance, refer to your Windows documentation, to Microsoft technical support, or to Motorola M2CORE technical support.

To debug the sample application, perform the following steps:

- 1. At the MS-DOS prompt, type gdb-mcore testgnu.elf and press the Enter key.

- 2. At the GNU Debug (GDB) prompt, type target picobug com2. If you are using a different communications port, change this command appropriately. Next, press the Enter key.

- 3. Ignore any "0x0 in ?? ()" line. At the GDB prompt, type load testgnu.elf and press the Enter key.

- 4. At the GDB prompt, type list. Press the Enter key several times to view the application.

- 5. At the GDB prompt, set several breakpoints. Type:

- BR 30 (for application line 30) and press Enter;

- BR 33 and press Enter;

- BR 36 and press Enter;

- BR 39 and press Enter.

- 6. At the GDB prompt, type run and press the Enter key. The application executes until it reaches line 30. LED DS5 lights.

- 7. At the GDB prompt, type the continue command c and press Enter. The application executes to line 33 (LED DS4 lights). Type additional continue commands for execution to break at line 36 (LED DS3 lights), line 39 (LED DS2 lights), and line 30 (again).

- 8. At the GDB prompt, type BR 41 and press Enter. This sets another breakpoint at the end of the program.

- 9. At the next four GDB prompts, type del 1, del 2, del 3, and del 4, pressing Enter after each command. These four commands delete the breakpoints set during step 5, above.

- 10. At the GDB prompt, type c and presse Enter. The application runs through its normal loop, flashing each LED 10 times before stopping at line 41.

- 11. To quit the debugger application, type q at the GDB prompt and press Enter.

You can now create and debug your own application.

## 3.2 Using Metrowerks MetroTRK Debugger

Metrowerks Target Resident Kernel (MetroTRK) is a debug monitor for use with applications built with the CodeWarrior<sup>TM</sup> Integrated Development Environment (IDE). To use MetroTRK Debugger, you need to install the CodeWarrior tools on your computer.

To install the CodeWarrior IDE on your computer:

- 1. Insert the CodeWarrior CD-ROM into your CD-ROM drive. The CodeWarrior installation starts automatically.

- 2. Click the **Launch CodeWarrior Setup** button and follow the instructions to install the IDE. Instructions for activating the CodeWarrior license in file License\_Readme.txt. (The default path for this file is C:\Program Files\Metrowerks\CodeWarrior.)

After you have installed the CodeWarrior IDE on your computer, follow these steps to create a serial connection and configure the CMB2114 components:

- 1. Connect the CMB2114 to your computer.

- a. Connect the RS-232 cable between CMB2114 connector J58 and the serial port of your computer. (If appropriate for your serial port, use the DB9/DB25 adapter.)

- b. Make sure that the +12-volt power supply is turned off (or disconnected from line power), and that CMB2114 power switch S4 is set to the OFF position. Connect the power supply cable to CMB/EVB2114 connector J61.

- 2. Start CMB2114 communication.

- a. Start HyperTerminal program. (If a message asks about installing a modem, click the **No** button.) The **Connection Description** dialog box appears.

- b. Enter the connection name and click OK. The **Connect To** dialog box appears.