# MPC5125 Microcontroller Reference Manual

**Devices Supported:** MPC5125

Document Number: MPC5125RM

Rev 3

10/2011

This page is intentionally left blank

# Chapter 1 Overview

| 1.1 |           | ion1                                                |

|-----|-----------|-----------------------------------------------------|

| 1.2 | Chip-Lev  | vel Features                                        |

| 1.3 |           | Features                                            |

|     |           | e300 Processor Core                                 |

|     |           | Display Interface Unit (DIU)                        |

|     |           | USB Controller3                                     |

|     | 1.3.4     | Direct Memory Access (DMA) Controller               |

|     |           | DDR SDRAM Memory Controller                         |

|     |           | 32 KB On-chip SRAM                                  |

|     | 1.3.7     | Fast Ethernet Controller (FEC)                      |

|     | 1.3.8     | NAND Flash Interface                                |

|     | 1.3.9     | Local Plus Bus (LPC) Interface                      |

|     | 1.3.10    | Secure Digital Host Controller (SDHC)               |

|     | 1.3.11    | Controller Area Network (CAN)                       |

|     | 1.3.12    | Integrated Circuit Communication (I <sup>2</sup> C) |

|     |           | Programmable Serial Controller (PSC)                |

|     |           | J1850 Byte Data Link Controller (BDLC) Interface    |

|     |           | General Purpose I/Os (GPIO)                         |

|     | 1.3.16    | On-chip Real-time Clock (RTC)5                      |

|     |           | IC Identification Module (IIM)                      |

|     | 1.3.18    | On-chip Temperature Sensor                          |

|     | 1.3.19    | Power Modes                                         |

|     |           | System Timers                                       |

|     |           | IEEE 1149.1 Compliant JTAG Boundary Scan            |

| 1.4 |           | er Environment $\ldots$                             |

|     | 1         |                                                     |

|     |           | Chapter 2                                           |

|     |           | System Configuration and Memory Map                 |

|     |           | (XLBMEN + Mem Map)                                  |

| 2.1 | Introduct | ion                                                 |

| 2.1 |           | Map and Register Definition                         |

| ۷,۷ | •         | Local Memory Map Overview and Example               |

|     |           | Address Translation and Mapping                     |

|     |           | Window into Configuration Space                     |

|     |           | Local Access Windows                                |

|     |           | Local Access Register Memory Map                    |

|     |           | Overlap of Local Access Windows                     |

|     |           | Configuring Local Access Windows                    |

| 2.3 |           | Configuration                                       |

| 2.5 |           | System Configuration Register Memory Map            |

|     | 4.3.1     | by stem coming transfer internet y true             |

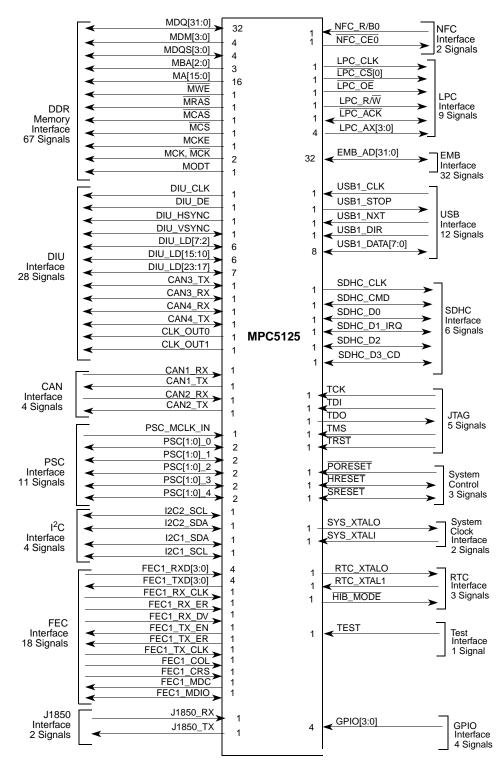

# Chapter 3 Signal Descriptions

| 3.1 |                                       | ction                                         |      |

|-----|---------------------------------------|-----------------------------------------------|------|

| 3.2 | 3.1.1<br>Signal 9                     | Signals Overview                              |      |

| 3.2 | orginar i                             | States During Reset                           | . 31 |

|     |                                       | Chapter 4                                     |      |

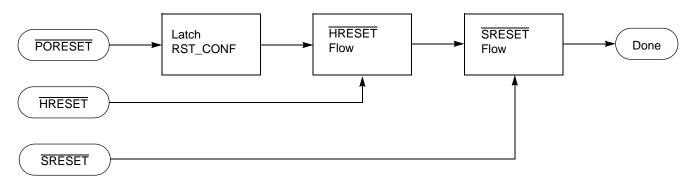

|     |                                       | Reset                                         |      |

| 4.1 | Introdu                               | ction                                         | 61   |

| 4.2 |                                       | On Initialization (PORESET)                   |      |

| 4.3 |                                       | T Flow                                        |      |

| 7.5 | 4.3.1                                 | Sources                                       |      |

|     | 4.3.2                                 | Impacts                                       |      |

| 4.4 |                                       | T Flow                                        |      |

|     | 4.4.1                                 | Sources                                       |      |

|     | 4.4.2                                 | Impacts                                       |      |

| 4.5 | Reset C                               | Configuration Word (RST_CONF)                 |      |

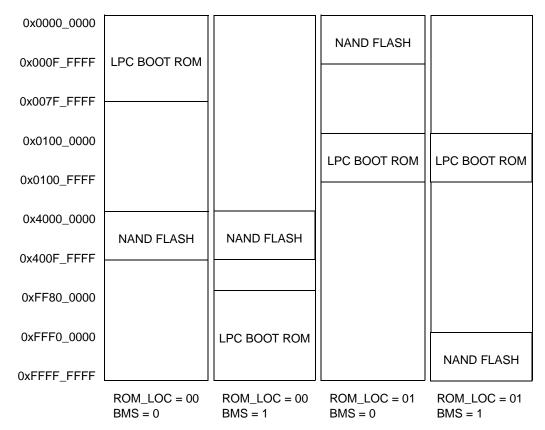

|     | 4.5.1                                 | BMS Operation                                 |      |

|     | 4.5.2                                 | RTC at Reset                                  | . 66 |

|     | 4.5.3                                 | JTAG Reset                                    | . 66 |

|     | 4.5.4                                 | Boot Vector Selection                         | . 66 |

|     | 4.5.5                                 | Boot Memory Interface Selection               | . 66 |

|     | 4.5.6                                 | LPC Initialization Sequence                   | . 67 |

|     | 4.5.7                                 | NFC Initialization Sequence                   |      |

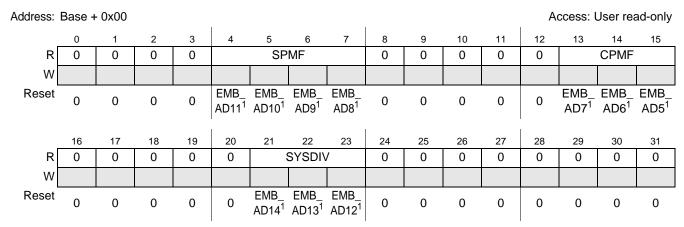

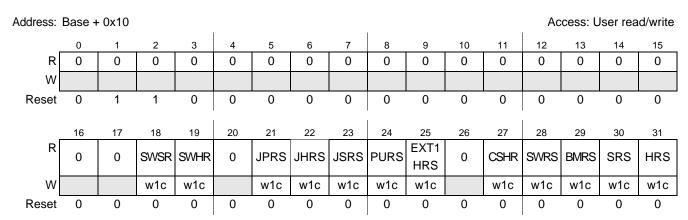

| 4.6 | Memor                                 | • 1                                           |      |

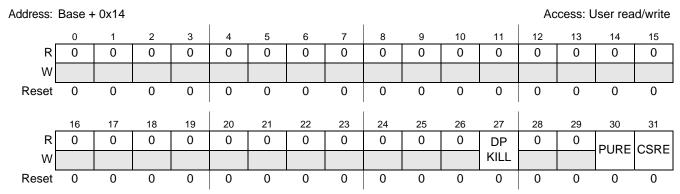

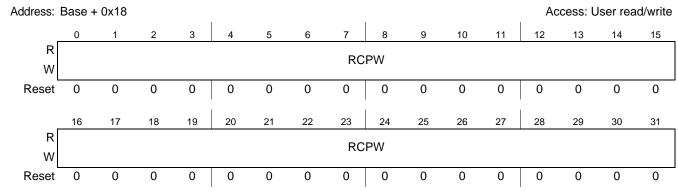

|     | 4.6.1                                 | Reset Configuration Word Low (RCWL) Register  |      |

|     | 4.6.2                                 | Reset Configuration Word High (RCWH) Register |      |

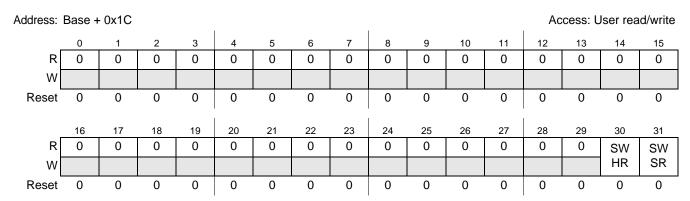

|     | 4.6.3                                 | Reset Status Register (RSR)                   |      |

|     | 4.6.4                                 | Reset Mode Register (RMR)                     |      |

|     | 4.6.5                                 | Reset Protection Register (RPR)               |      |

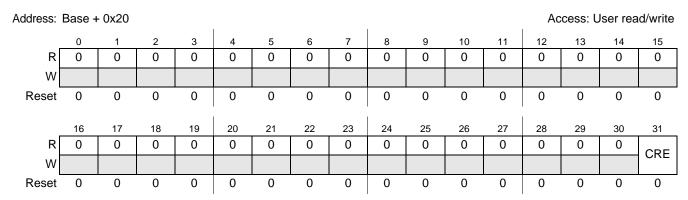

|     | 4.6.6                                 | Reset Control Register (RCR)                  |      |

|     | 4.6.7                                 | Reset Control Enable Register (RCER)          | . 74 |

|     |                                       | Chapter 5                                     |      |

|     |                                       | •                                             |      |

|     |                                       | Clocks and Low-Power Modes                    |      |

| 5.1 |                                       | ction                                         |      |

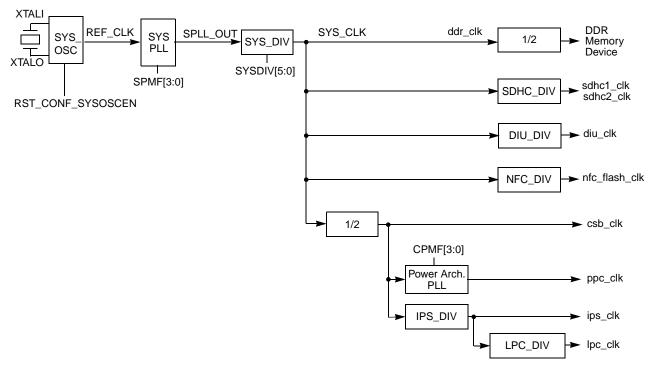

| 5.2 | · · · · · · · · · · · · · · · · · · · | Clock Generation                              |      |

|     | 5.2.1                                 | Peripheral Clock Domains                      |      |

|     | 5.2.2                                 | System Oscillator Disable                     |      |

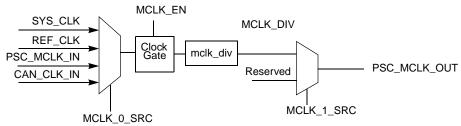

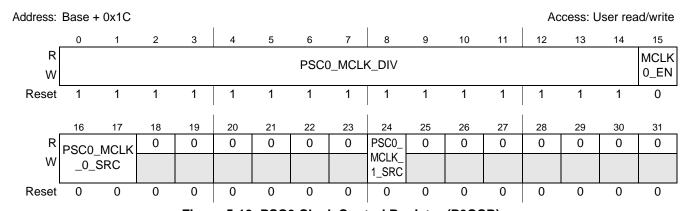

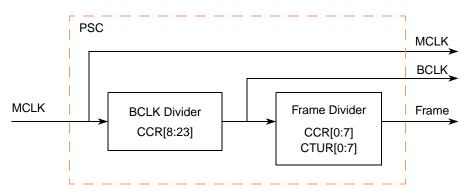

|     | 5.2.3                                 | PSC Clock Generation                          |      |

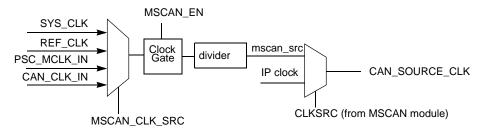

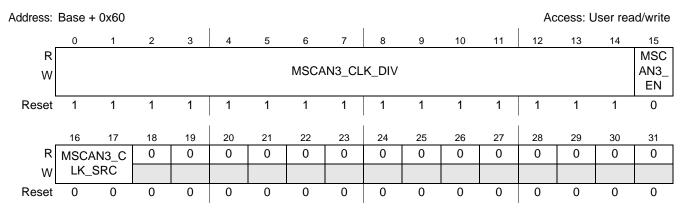

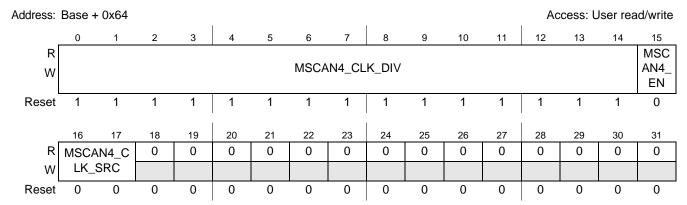

|     | 5.2.4                                 | MSCAN Clock Generation                        |      |

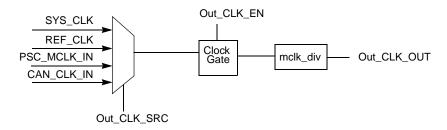

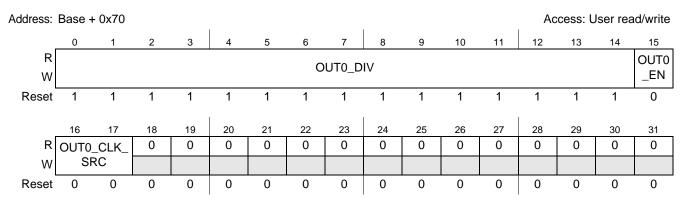

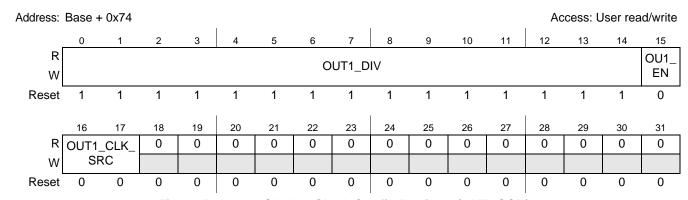

|     | 5.2.5<br>5.2.6                        | OUT Clock Generation                          |      |

|     | 5.2.6                                 | RTC Clock Generation                          |      |

|     | 3.2.1                                 | System FLL lock detection                     | . 19 |

|     |                                       |                                               |      |

|     | 5.2.8 System PLL and e300 PLL                            | 79  |

|-----|----------------------------------------------------------|-----|

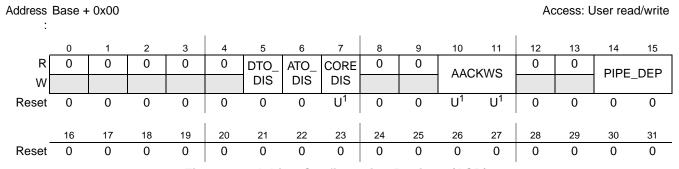

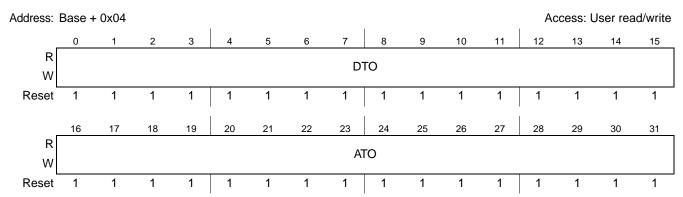

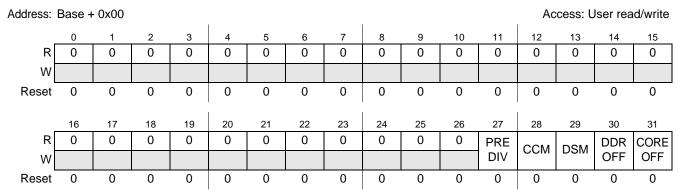

| 5.3 | Clock Control Module                                     | 80  |

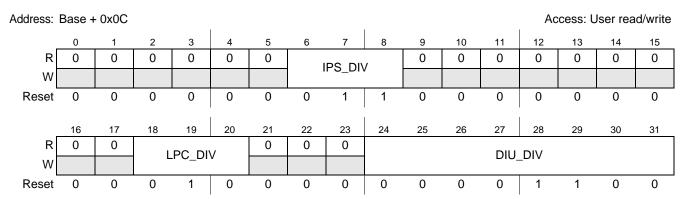

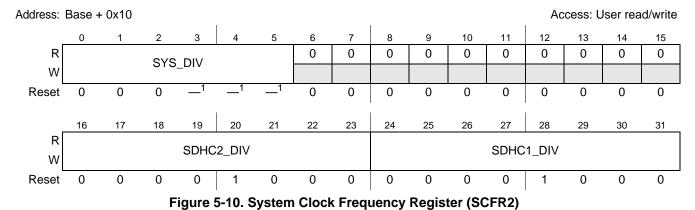

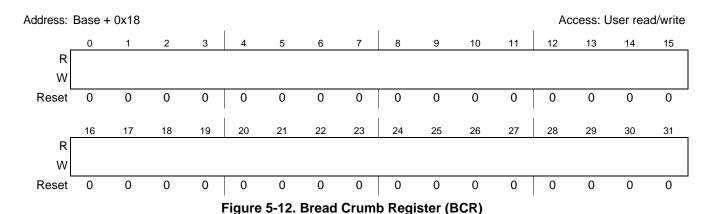

|     | 5.3.1 Memory Map/Register Definition                     | 80  |

|     |                                                          |     |

|     | Chapter 6                                                |     |

|     | Byte Data Link Controller (BDLC)                         |     |

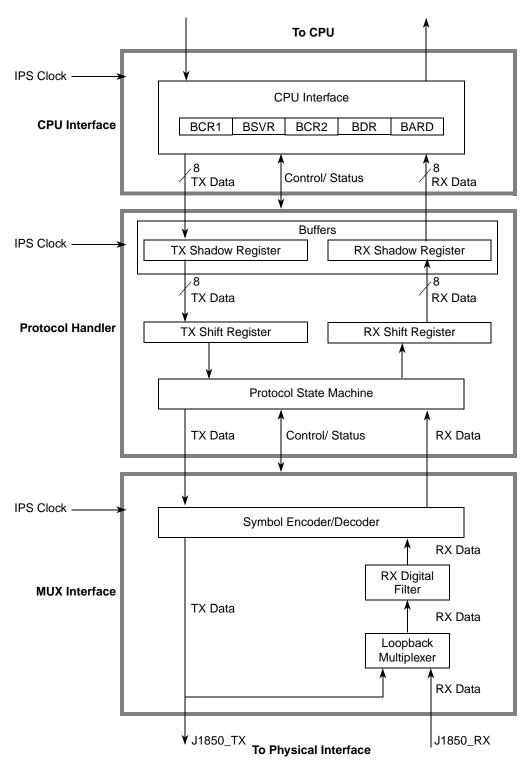

| 6.1 | Introduction                                             | 111 |

|     | 6.1.1 Features                                           |     |

| 6.2 | External Signal Description                              |     |

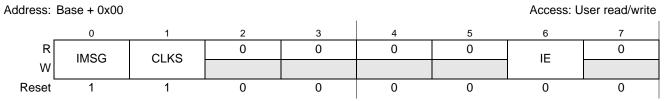

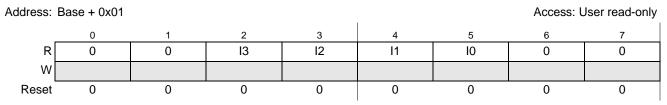

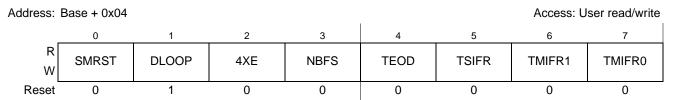

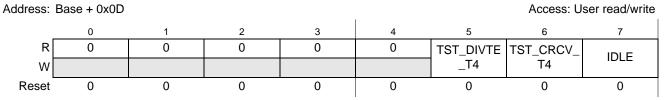

| 6.3 | Memory Map and Register Definition                       |     |

|     | 6.3.1 Memory Map                                         |     |

|     | 6.3.2 Register Summary                                   |     |

| 6.4 | Functional Description                                   | 129 |

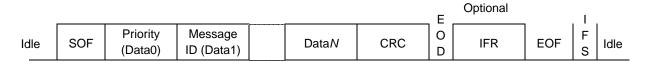

|     | 6.4.1 J1850 Frame Format                                 |     |

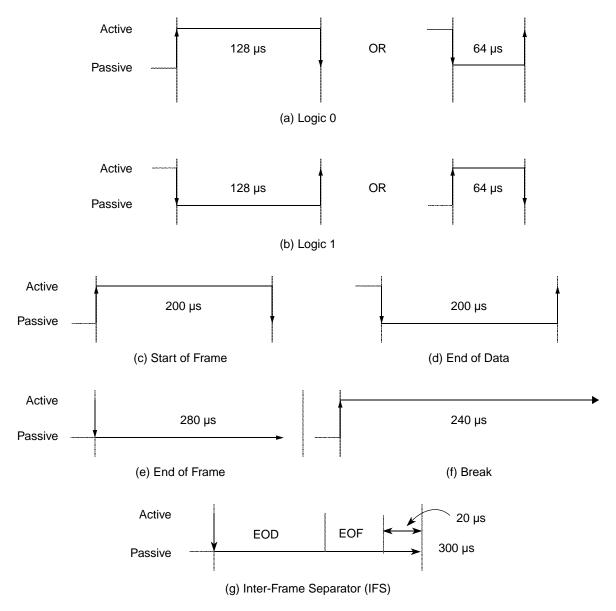

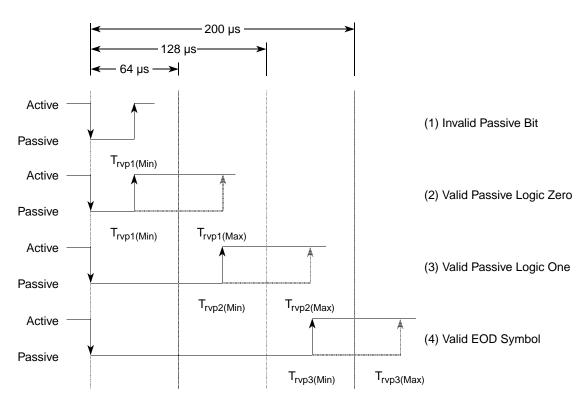

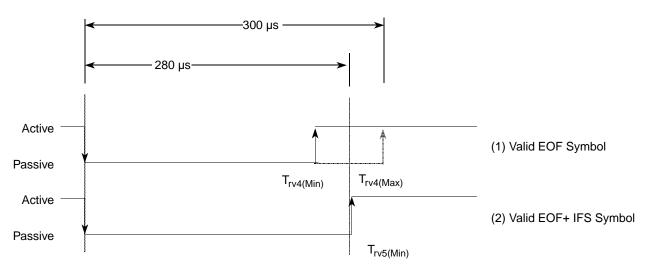

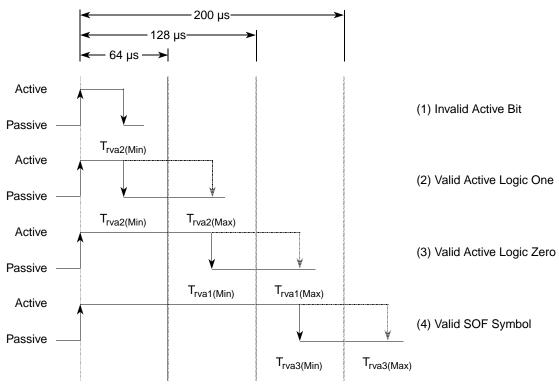

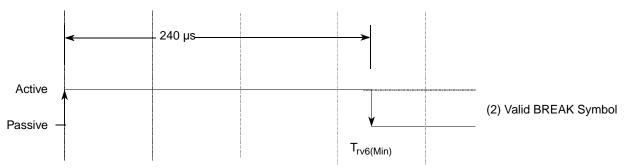

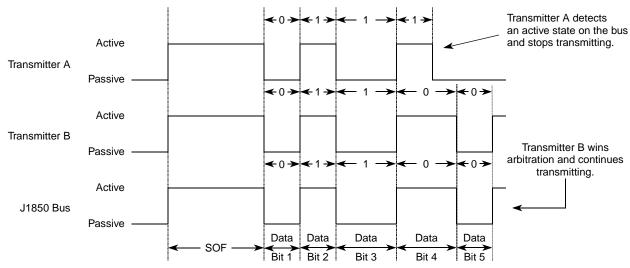

|     | 6.4.2 J1850 VPW Symbols                                  | 131 |

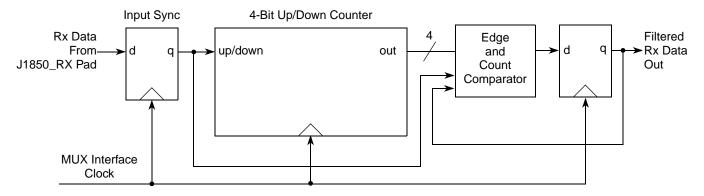

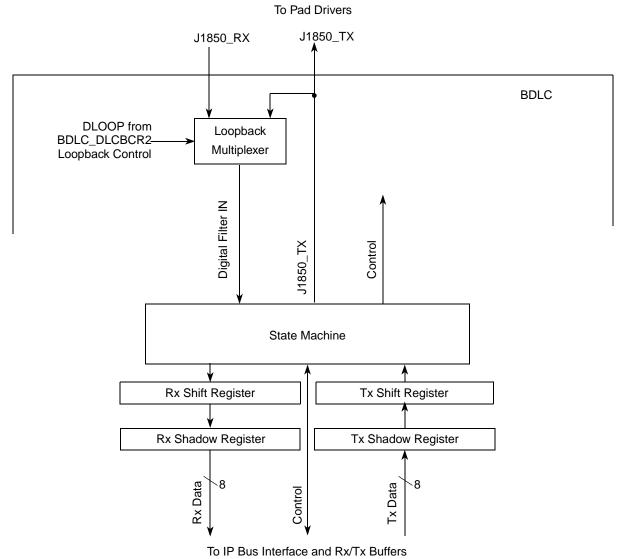

|     | 6.4.3 MUX Interface                                      | 143 |

|     | 6.4.4 Protocol Handler                                   | 145 |

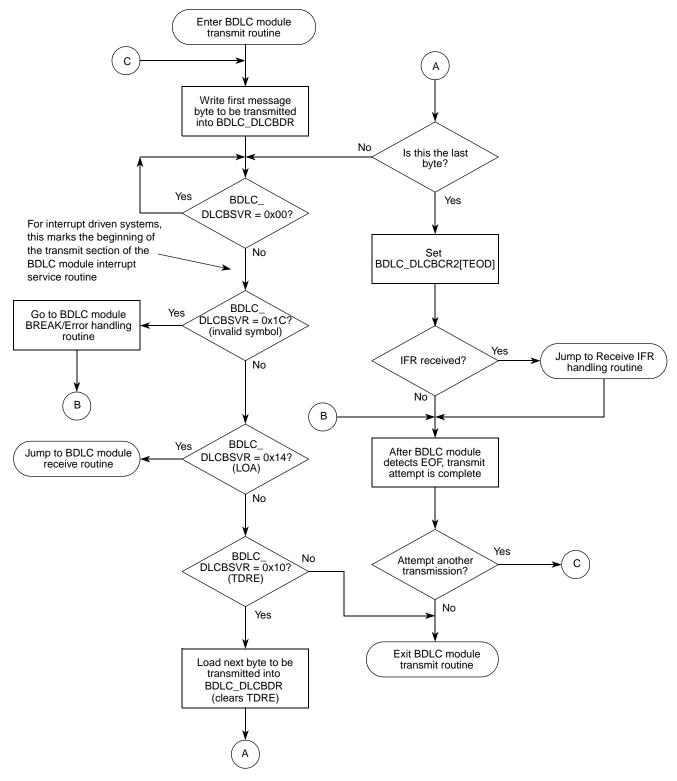

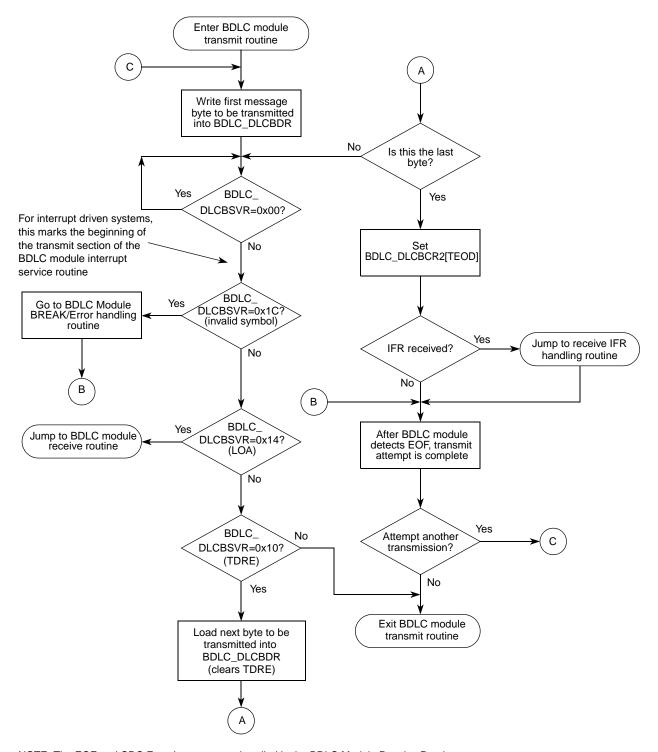

|     | 6.4.5 Transmitting a Message                             | 147 |

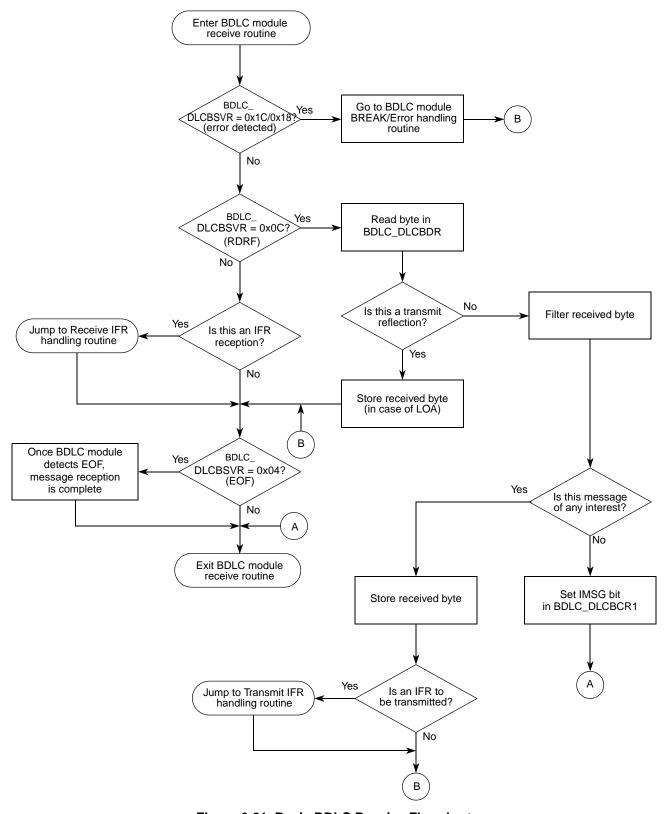

|     | 6.4.6 Receiving A Message                                | 152 |

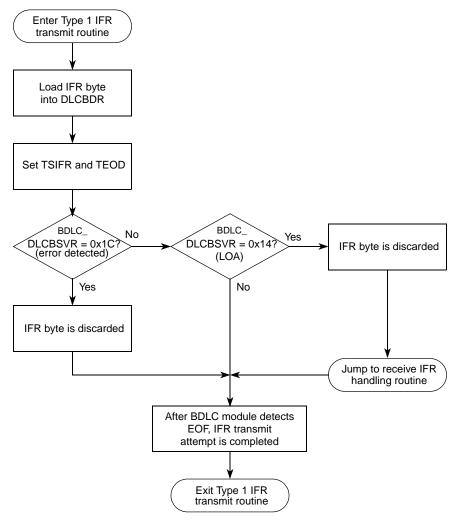

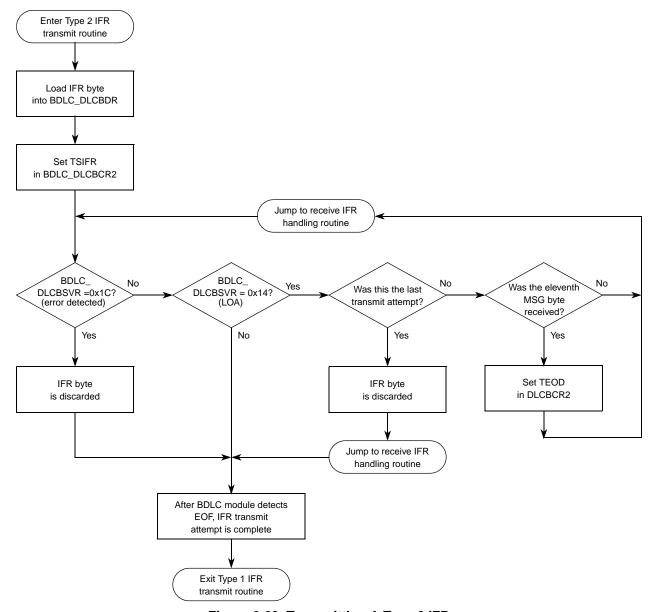

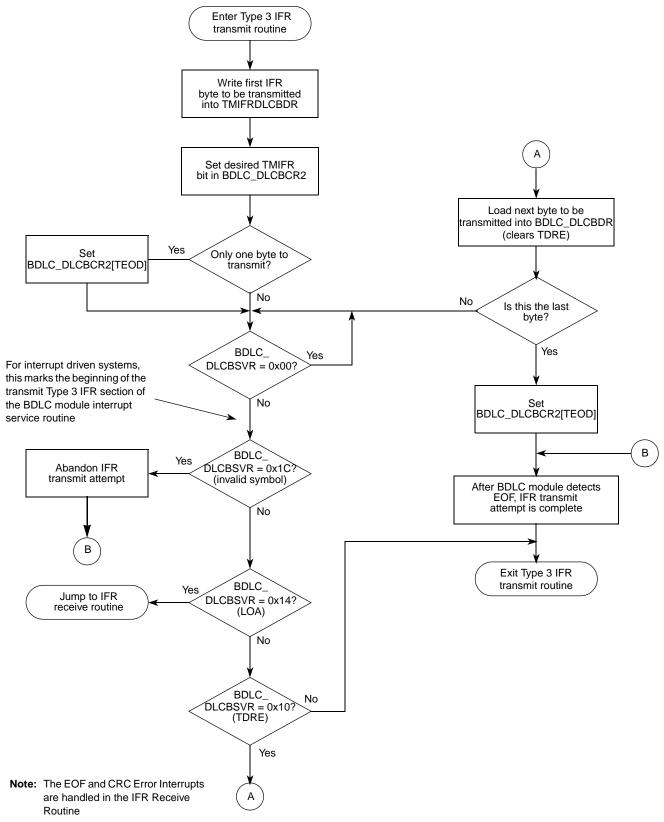

|     | 6.4.7 Transmitting an In-Frame Response (IFR)            | 156 |

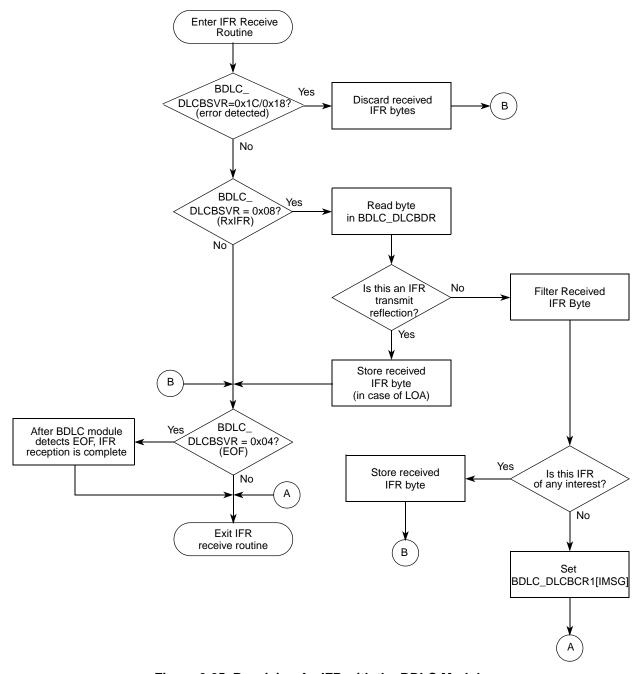

|     | 6.4.8 Receiving An In-Frame Response (IFR)               | 165 |

|     | 6.4.9 Special BDLC Module Operations                     | 167 |

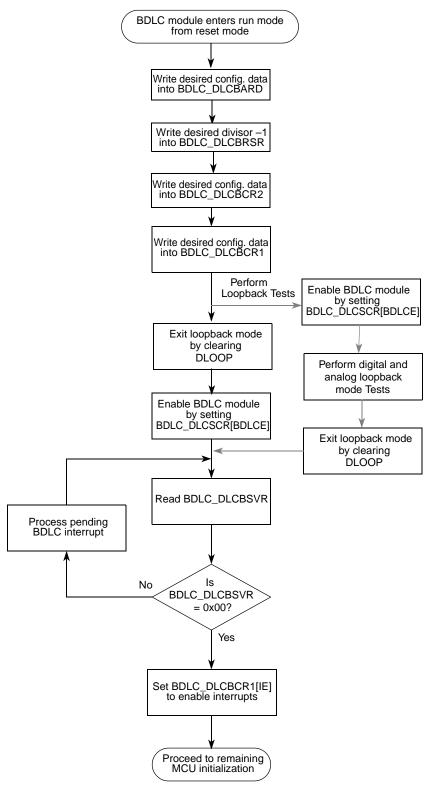

| 6.5 | Initialization Information                               | 169 |

|     | 6.5.1 Initializing the Configuration Bits                |     |

|     | 6.5.2 Exiting Loopback Mode and Enabling the BDLC Module |     |

|     | 6.5.3 Enabling BDLC Interrupts                           | 170 |

|     | <b>0</b> 1                                               |     |

|     | Chapter 7                                                |     |

|     | CPU e300 Core Power Architecture                         |     |

| 7.1 | Introduction                                             |     |

| 7.2 | e300c4 Processor Core Functional Overview                | 173 |

| 7.3 | e300c4 Core Reference Manual                             | 174 |

| 7.4 | Unsupported e300c4 Core Features                         | 174 |

|     | 7.4.1 Instructions                                       |     |

|     | 7.4.2 CSB Parity                                         | 174 |

|     |                                                          |     |

|     | Chapter 8                                                |     |

|     | CSB Arbiter and Bus Monitor                              |     |

| 8.1 | Introduction                                             | 175 |

|     | 8.1.1 Features                                           | 175 |

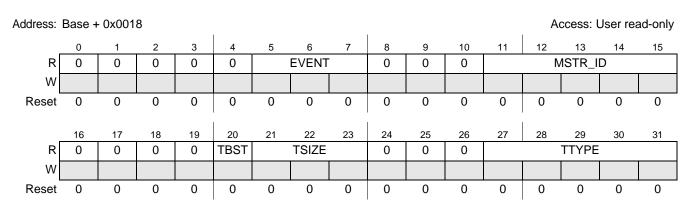

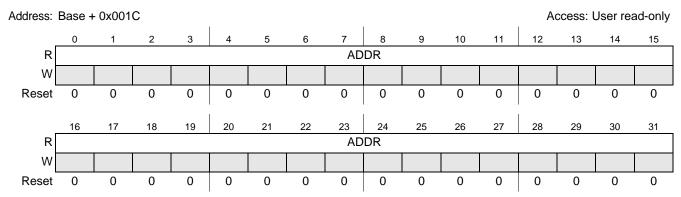

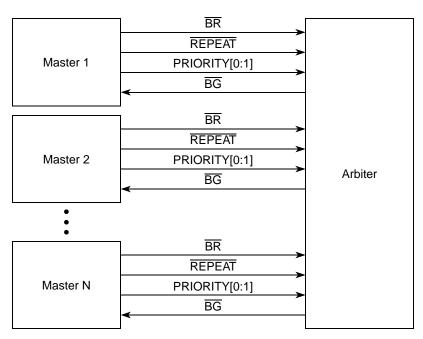

| 8.2 | Memory Map/Register Definition                           | 176 |

|     | 8.2.1 Register Descriptions                              | 176 |

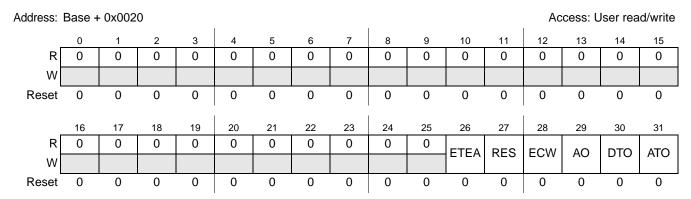

| 8.3 | Functional Description                                   | 186 |

|     | 8.3.1 Arbitration Policy                                 | 186 |

|     |                                                          |     |

|     |                                                          |     |

|      | 8.3.2 Bus Error Detection                 | 189 |

|------|-------------------------------------------|-----|

| 8.4  | Initialization/Applications Information   | 192 |

|      | 8.4.1 Initialization Sequence             | 192 |

|      | 8.4.2 Error Handling Sequence             | 193 |

|      |                                           |     |

|      | Chapter 9                                 |     |

|      | Direct Memory Access (DMA)                |     |

| 9.1  | Introduction                              |     |

|      | 9.1.1 Features                            |     |

| 9.2  | Memory Map and Register Definition        |     |

|      | 9.2.1 Register Descriptions               |     |

| 9.3  | Initialization/Application Information    |     |

|      | 9.3.1 DMA Initialization                  |     |

|      | 9.3.2 DMA Programming Errors              |     |

|      | 9.3.3 DMA Arbitration Mode Considerations |     |

|      | 9.3.4 DMA Transfer                        |     |

|      | 9.3.5 TCD Status                          |     |

|      | 9.3.6 Channel Linking                     |     |

|      | 9.3.7 Dynamic Programming                 | 237 |

|      | Chapter 10                                |     |

|      | Display Interface Unit (DIU)              |     |

| 10.1 | Introduction                              | 230 |

| 10.1 | 10.1.1 Features                           |     |

|      | 10.1.2 Modes of Operation                 |     |

| 10.2 | External Signal Description               |     |

| 10.3 | Memory Map and Register Definition        |     |

|      | 10.3.1 Memory Map                         |     |

|      | 10.3.2 Register Summary                   |     |

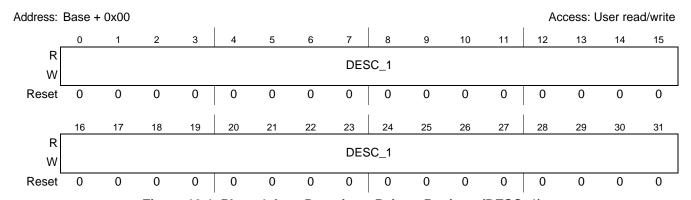

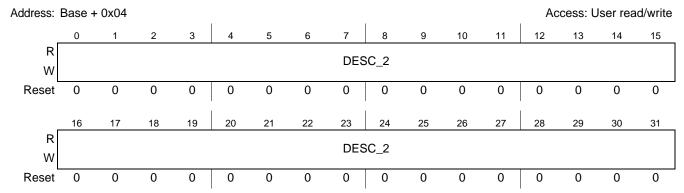

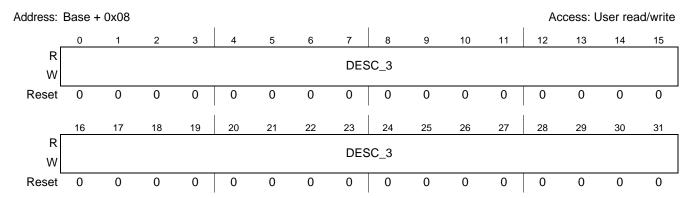

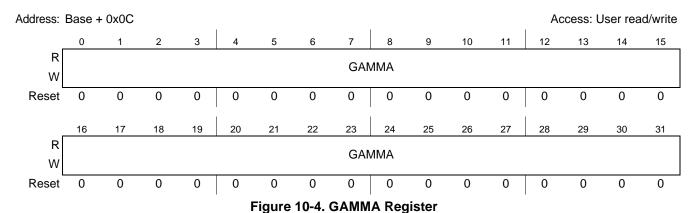

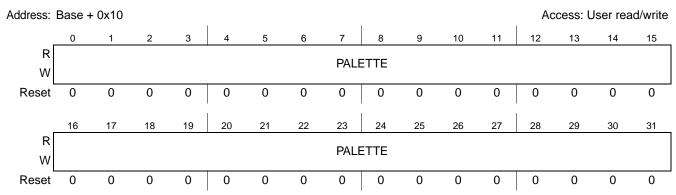

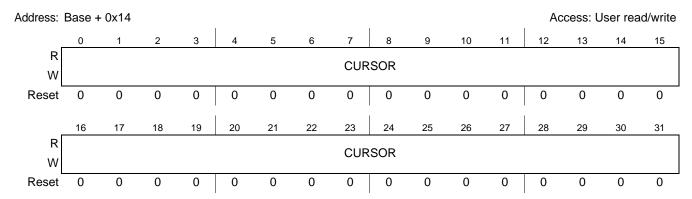

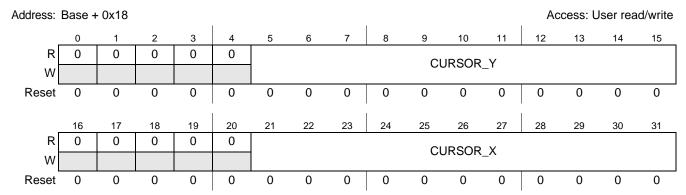

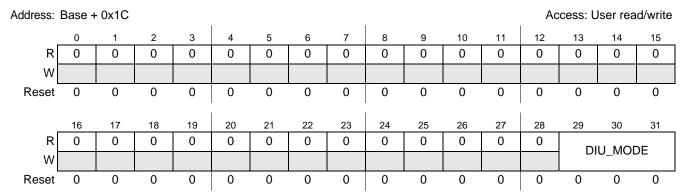

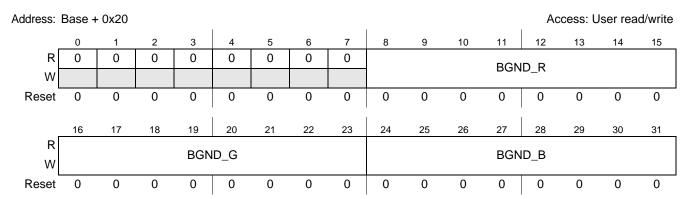

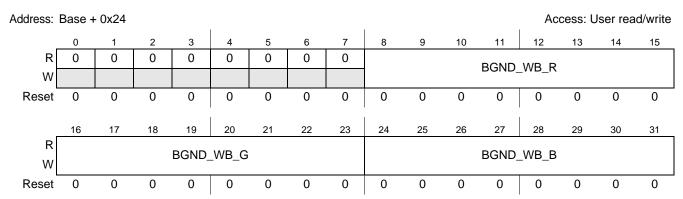

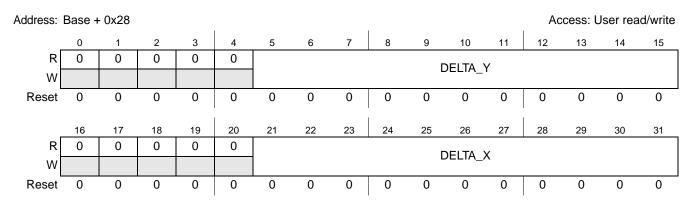

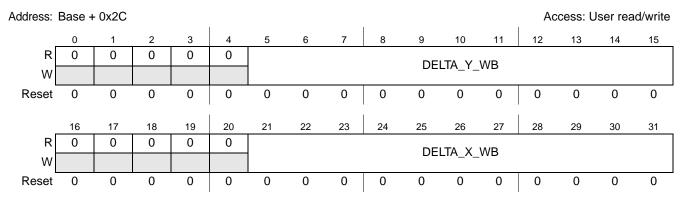

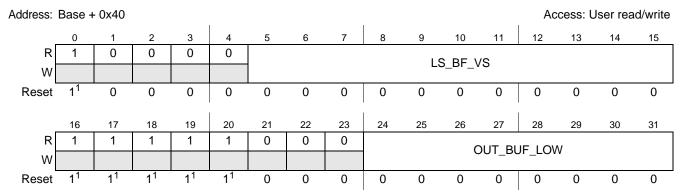

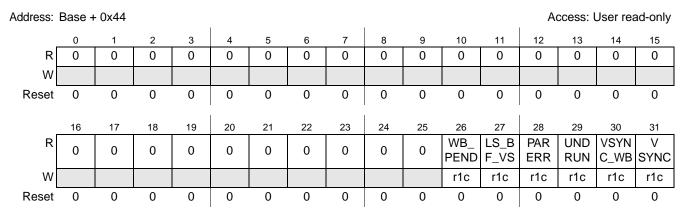

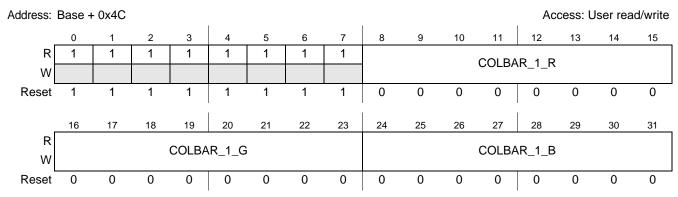

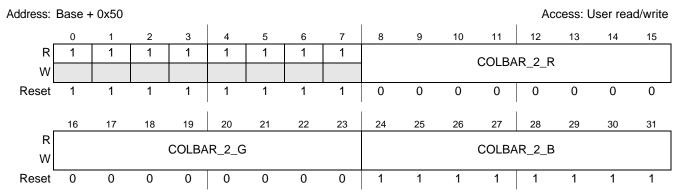

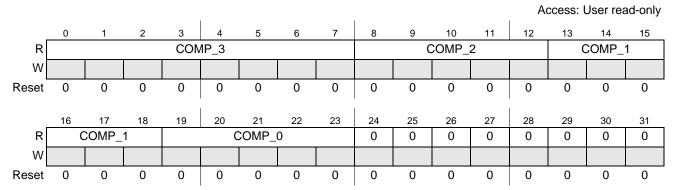

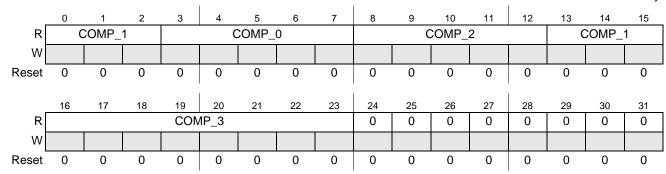

|      | 10.3.3 Register Descriptions              |     |

| 10.4 | Functional Description                    |     |

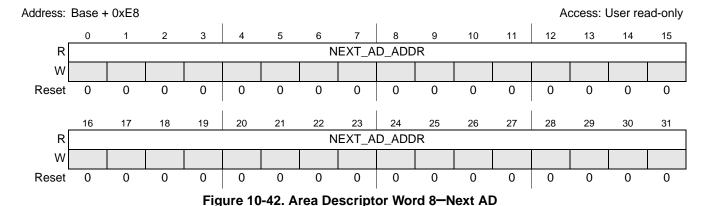

|      | 10.4.1 Area Descriptor                    | 263 |

|      | 10.4.2 Area Descriptor Format             |     |

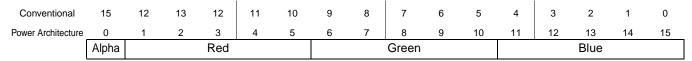

|      | 10.4.3 Pixel Structure                    | 272 |

|      | 10.4.4 Pixel Format Conversion            | 273 |

|      | 10.4.5 Alpha Blending                     | 274 |

|      | 10.4.6 Chroma Keying                      | 275 |

|      | 10.4.7 Gamma Correction                   | 275 |

|      | 10.4.8 Cursor                             |     |

|      | 10.4.9 Writeback Operation                |     |

|      | 10.4.10Color Bar Generation               |     |

|      | 10.4.11Interrupt Generation               |     |

|      | 10.4.12Dynamic Priority Generation        |     |

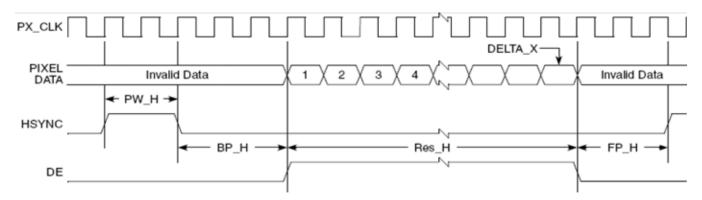

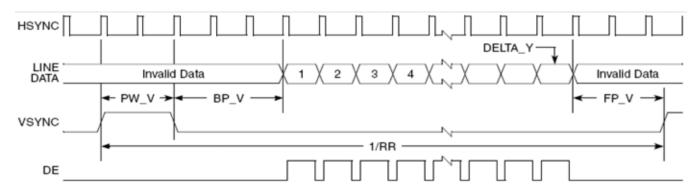

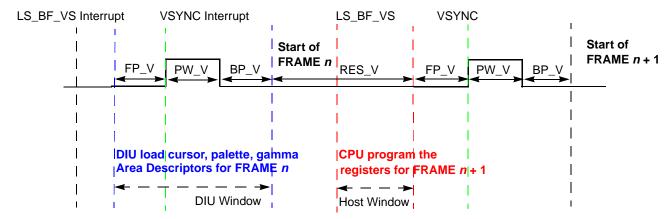

|      | 10.4.13Display Signal Timing              | 281 |

| 10.5 | Initialization/Application Information                         | . 282 |

|------|----------------------------------------------------------------|-------|

|      | 10.5.1 DIU Initialization                                      | . 282 |

|      | 10.5.2 Controlling DIU Planes after the DIU is Enabled         | . 283 |

|      | 10.5.3 Synchronizing with the Host (CPU)                       |       |

|      | 10.5.4 Recovering from Parameter Error                         |       |

|      | 10.5.5 Recovering from Underrun Error                          |       |

|      |                                                                |       |

|      | Chapter 11                                                     |       |

|      | DRAM Controller                                                |       |

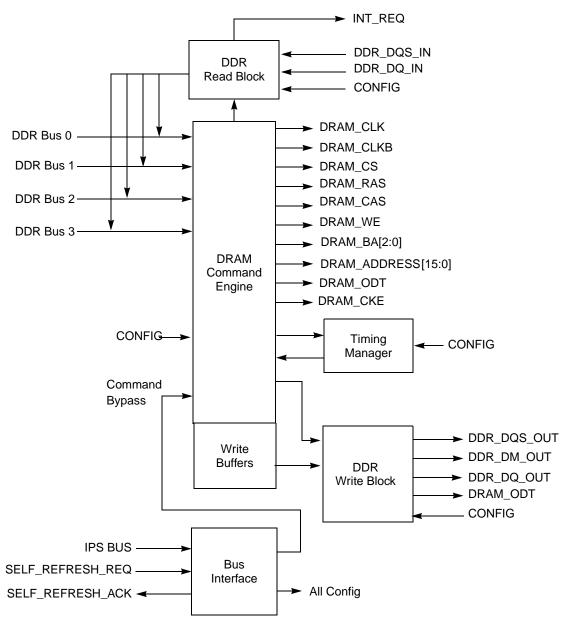

| 11.1 | Introduction                                                   | . 285 |

|      | 11.1.1 Overview                                                |       |

| 11.2 | Features                                                       |       |

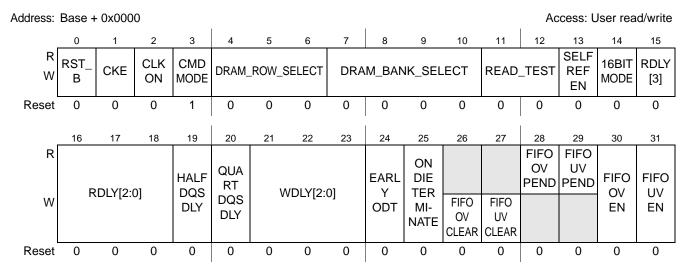

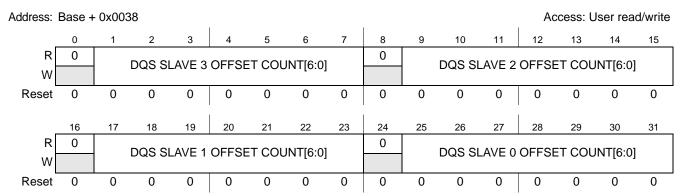

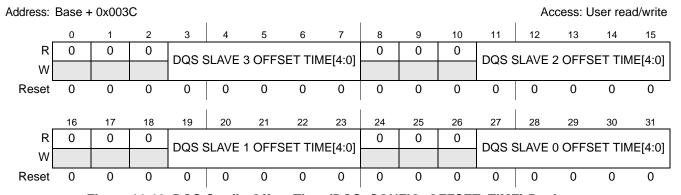

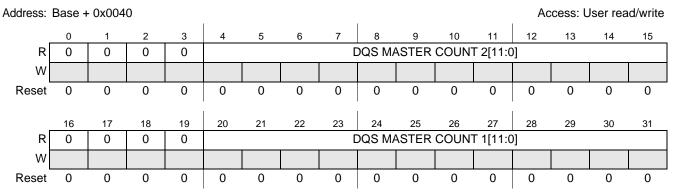

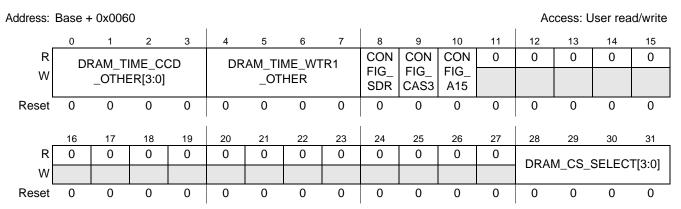

|      | Memory Map and Register Definition                             |       |

| 11.0 | 11.3.1 Memory Map                                              |       |

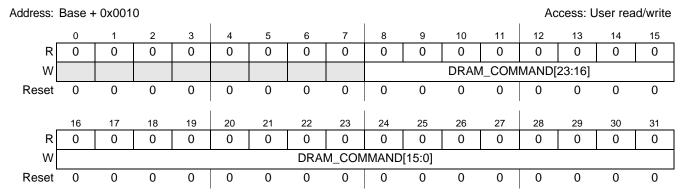

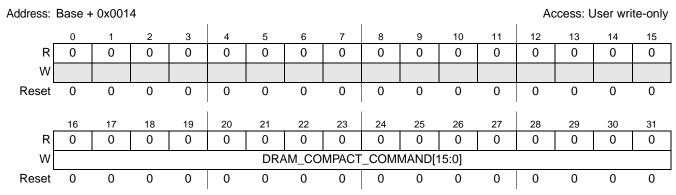

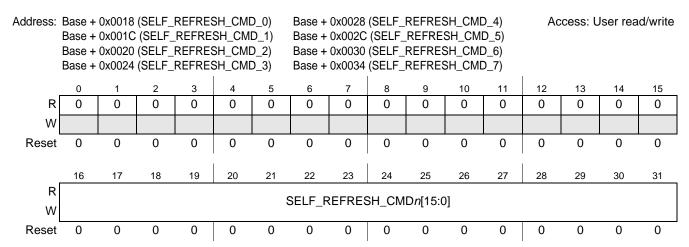

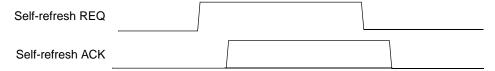

|      | 11.3.2 Register Descriptions                                   |       |

| 11 4 | Functional Description                                         |       |

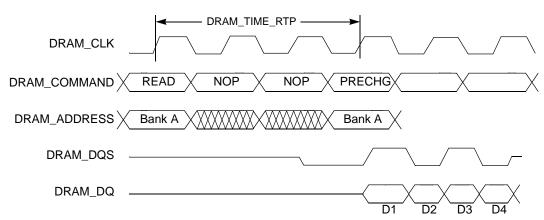

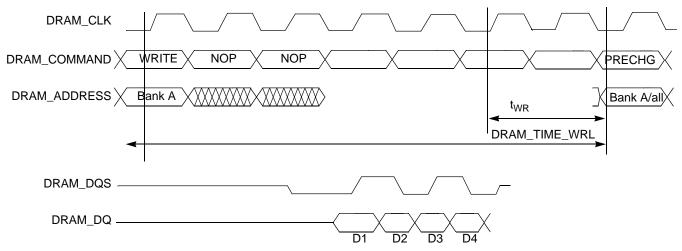

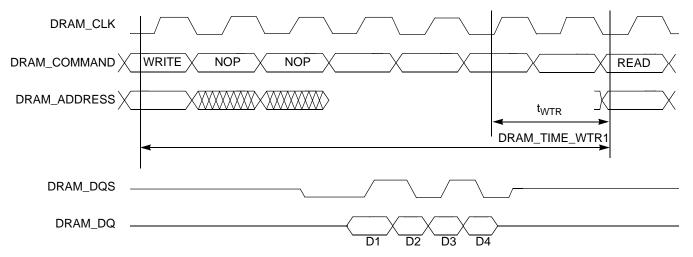

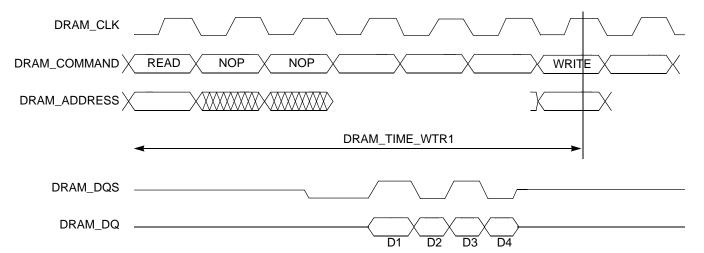

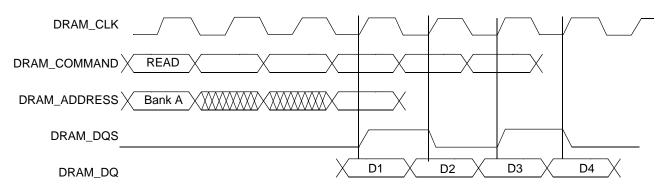

|      | 11.4.1 Interfacing with the DRAM                               |       |

|      | 11.4.2 Programming DRAM Device Internal Configuration Register |       |

|      | 11.4.3 DRAM Command Engine                                     |       |

|      | 11.4.4 Write Buffer                                            |       |

|      | 11.4.5 Timing Manager                                          |       |

|      | 11.4.6 DRAM Read Block and DRAM Write Block                    |       |

|      | 11.4.7 Bus Interface                                           |       |

|      |                                                                |       |

|      | Chapter 12                                                     |       |

|      | Multi-port DRAM Controller Priority Manager                    |       |

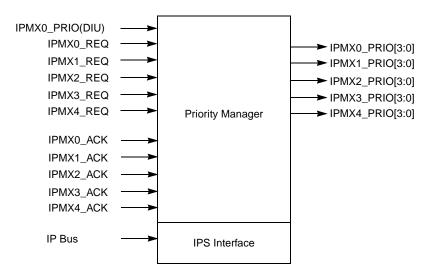

| 12.1 | Introduction                                                   | . 309 |

|      | 12.1.1 Features                                                | . 310 |

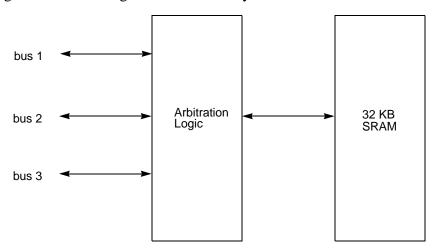

| 12.2 | Bus Connections                                                | . 310 |

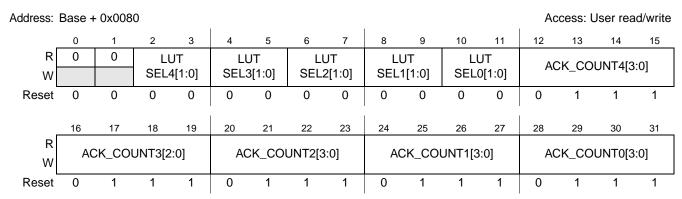

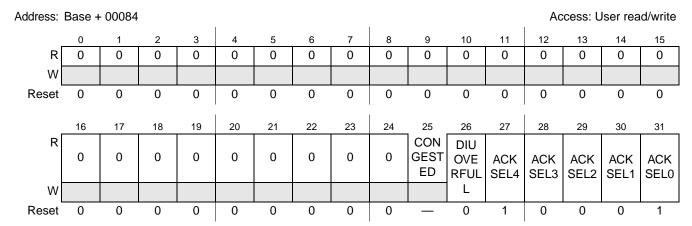

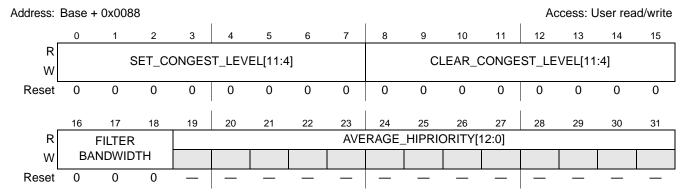

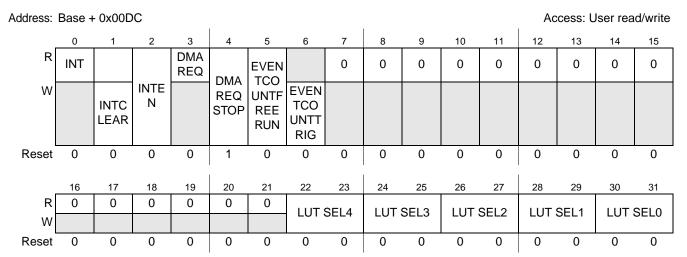

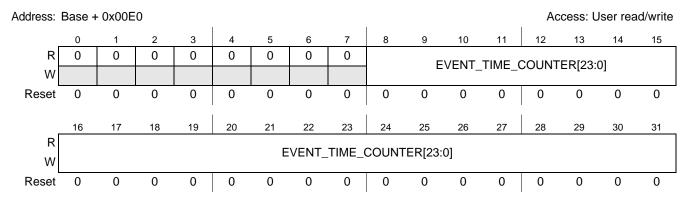

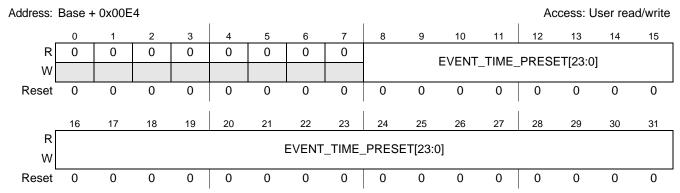

| 12.3 | Memory Map and Register Definition                             | . 310 |

|      | 12.3.1 Memory Map                                              | . 310 |

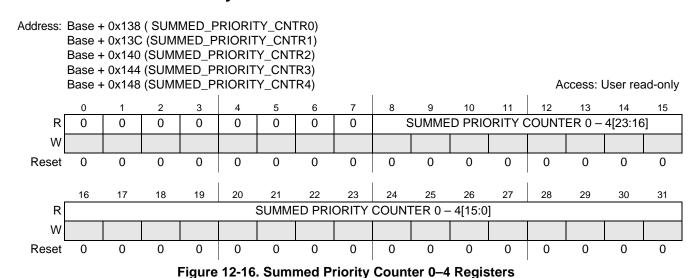

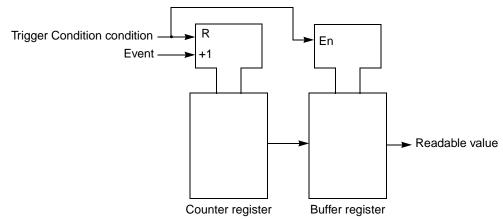

|      | 12.3.2 Register Descriptions                                   | . 313 |

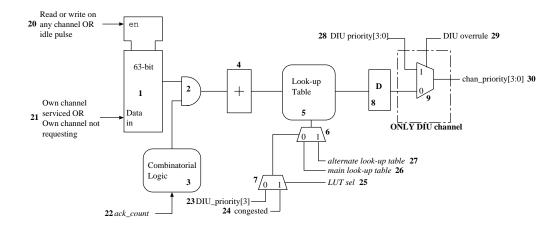

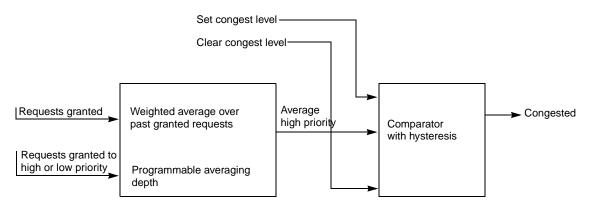

| 12.4 | Functional Description                                         | . 327 |

|      | 12.4.1 Description of Operation — Overview                     | . 327 |

|      | 12.4.2 Block Diagram                                           | . 327 |

|      | 12.4.3 Congestion Detector                                     | . 329 |

|      |                                                                |       |

|      | Chapter 13                                                     |       |

|      | External Memory Bus (EMB)                                      |       |

| 13.1 | Introduction                                                   |       |

|      | 13.1.1 Overview                                                |       |

|      | 13.1.2 Features                                                | . 331 |

| 13.2 | Functional Description                                         |       |

|      | 13.2.1 EMB Mux                                                 | . 331 |

|      |                                                                |       |

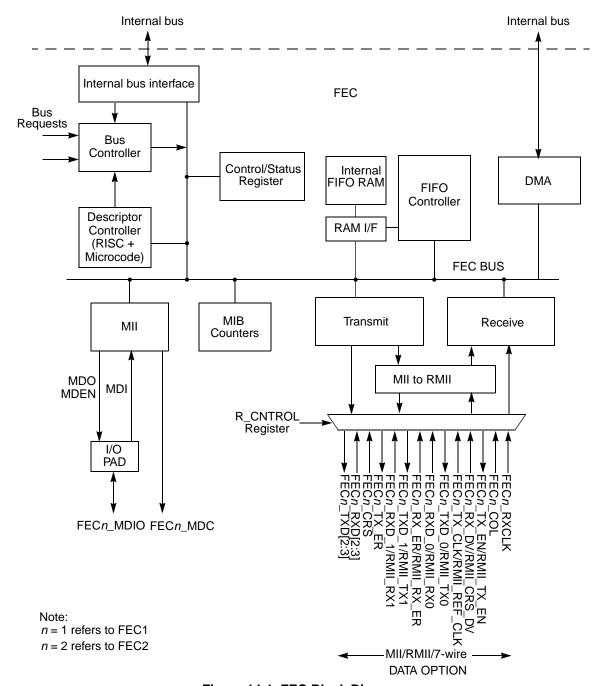

# Chapter 14 Fast Ethernet Controller (FEC)

| 14.1 | Introduction                                        | 333 |

|------|-----------------------------------------------------|-----|

|      | 14.1.1 FEC Top Level                                | 333 |

|      | 14.1.2 Features                                     | 335 |

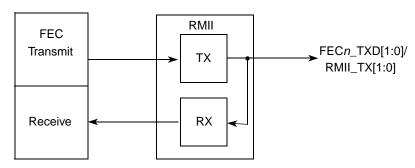

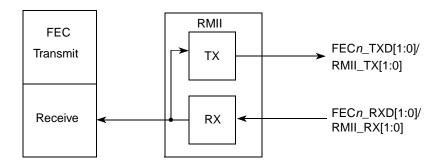

|      | 14.1.3 Modes of Operation                           | 336 |

| 14.2 | External Signal Description (Off Chip)              |     |

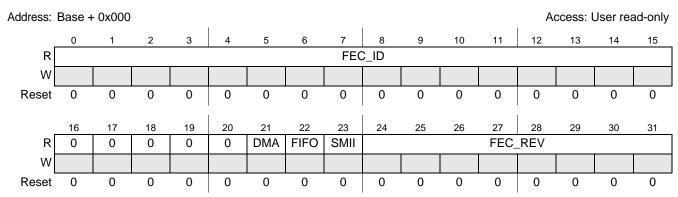

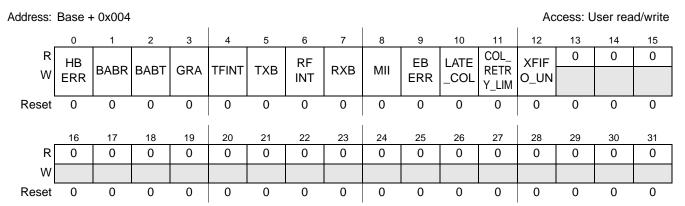

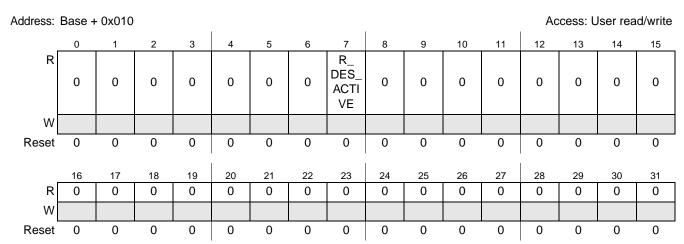

| 14.3 | Memory Map and Register Definition                  |     |

|      | 14.3.1 Overview                                     |     |

|      | 14.3.2 Top-Level Module Memory Map                  |     |

|      | 14.3.3 Detailed Memory Map—Control/Status Registers |     |

|      | 14.3.4 MIB Block Counters Memory Map                |     |

|      | 14.3.5 Register Descriptions                        |     |

| 14.4 | Initialization Information                          |     |

|      | 14.4.1 Initialization Prior to Asserting ETHER_EN   |     |

| 14.5 | Buffer Descriptors                                  |     |

|      | 14.5.1 Driver/DMA Operation with Buffer Descriptors |     |

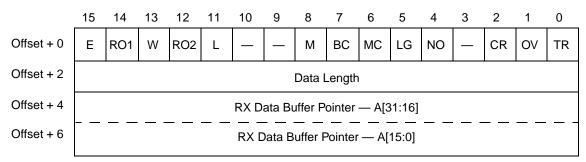

|      | 14.5.2 Ethernet Receive Buffer Descriptor (RxBD)    |     |

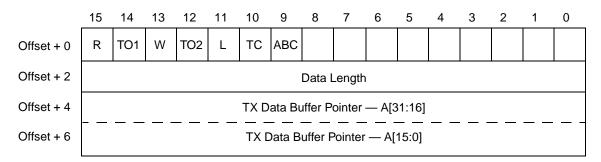

|      | 14.5.3 Ethernet Transmit Buffer Descriptor          |     |

| 14.6 | Network Interface Options                           |     |

|      | 14.6.1 FEC Frame Transmission                       |     |

|      | 14.6.2 FEC Frame Reception                          |     |

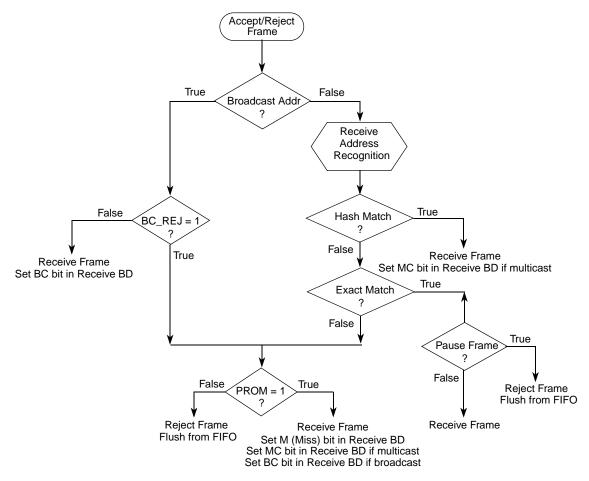

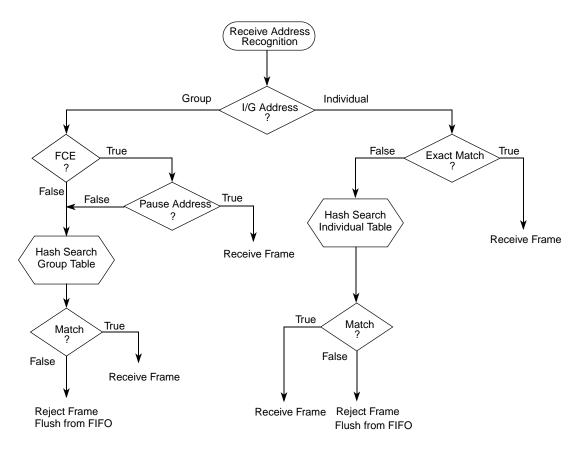

|      | 14.6.3 Ethernet Address Recognition                 |     |

|      | 14.6.4 Full-Duplex Flow Control                     |     |

|      | 14.6.5 Inter-Packet Gap Time                        |     |

|      | 14.6.6 Collision Handling                           |     |

|      | 14.6.7 MII Internal and External Loopback           |     |

|      | 14.6.8 RMII Loopback                                |     |

|      | 14.6.9 RMII Echo                                    |     |

|      | 14.6.10Ethernet Error-Handling Procedure            |     |

|      | 14.6.11Transmission Errors                          |     |

|      | 14.6.12Reception Errors                             |     |

|      |                                                     |     |

|      | Chapter 15                                          |     |

|      | General Purpose Timers (GPT)                        |     |

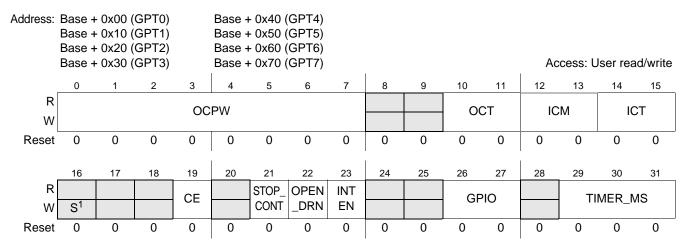

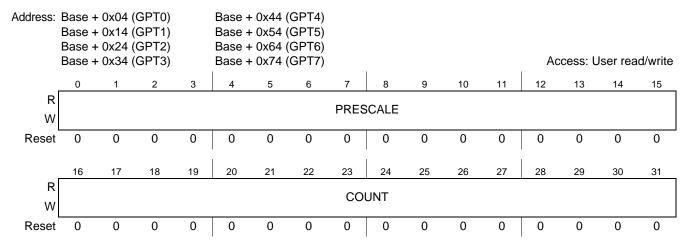

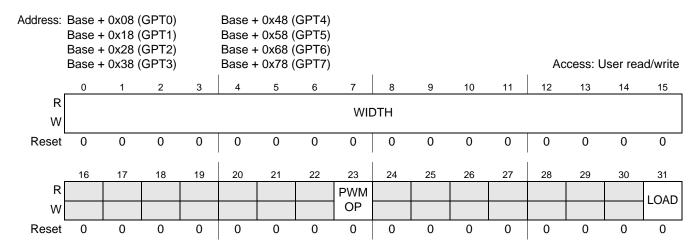

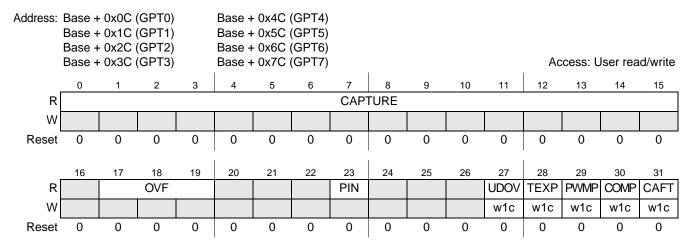

| 15.1 | Introduction                                        | 387 |

|      | 15.1.1 Modes of Operation                           |     |

|      | 15.1.2 Detailed Signal Descriptions                 |     |

| 15.2 | Memory Map and Register Definition                  |     |

| 10.2 | 15.2.1 Register Descriptions                        |     |

| 15 3 | Functional Description                              |     |

| 10.0 | 15.3.1 Input Capture Mode                           |     |

|      | 15.3.2 Changing Sub-Modes                           |     |

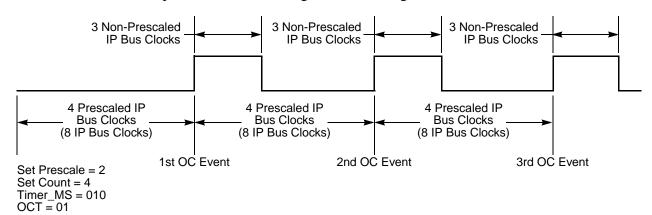

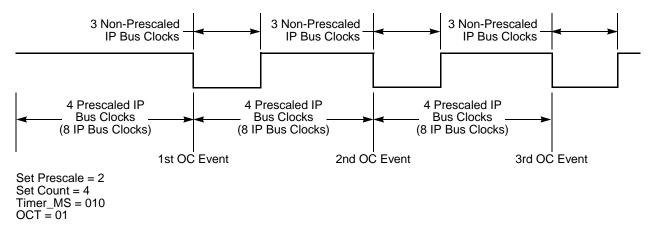

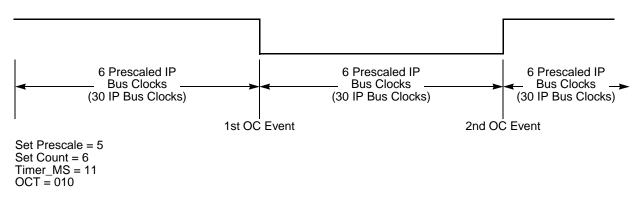

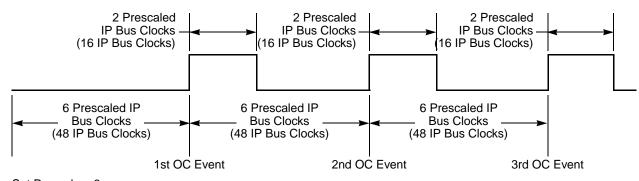

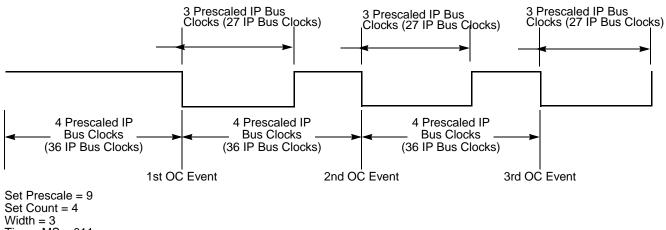

|      | 15.3.3 Output Compare                               |     |

|      | 15.5.5 Output Compare                               |     |

|      | 15.3.4 Force Output Low Immediately                 |     |

|------|-----------------------------------------------------|-----|

|      | 15.3.5 Output Pulse High                            | 399 |

|      | 15.3.6 Output Pulse Low                             | 400 |

|      | 15.3.7 Output Toggle                                | 400 |

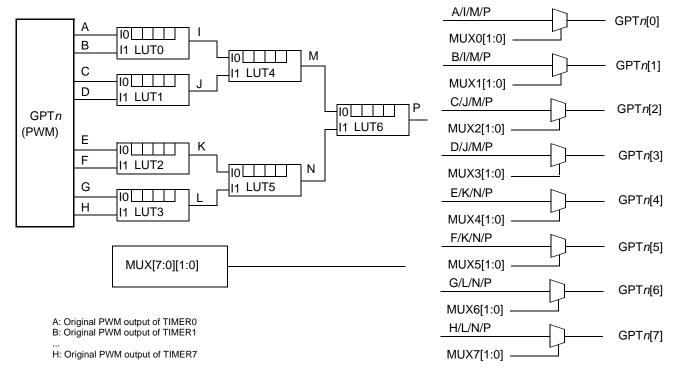

|      | 15.3.8 Pulse Width Modulation                       | 401 |

|      | 15.3.9 Simple GPIO                                  |     |

|      |                                                     |     |

|      | Chapter 16                                          |     |

|      | General Purpose I/O (GPIO)                          |     |

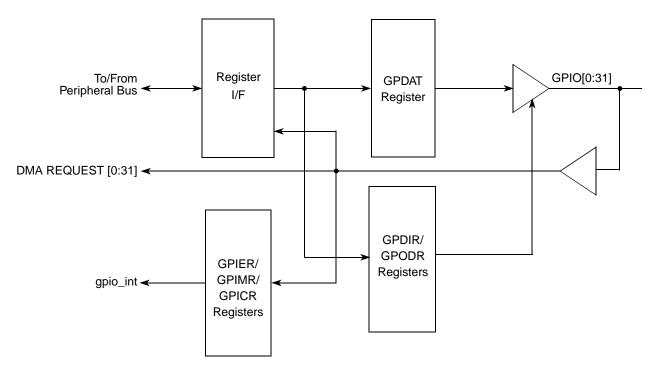

| 16.1 | Introduction                                        | 405 |

|      | Features                                            |     |

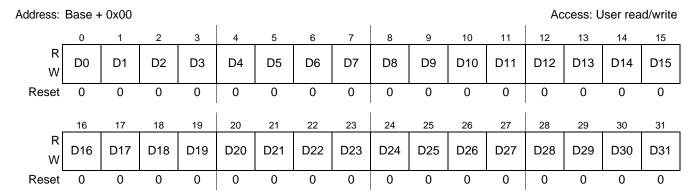

|      | Memory Map/Register Definition                      |     |

| 10.5 | 16.3.1 Register Descriptions                        |     |

| 16 / | Functional Description                              |     |

| 10.4 | Tunctional Description                              | 412 |

|      | Chapter 17                                          |     |

|      | • • • • • • • • • • • • • • • • • • •               |     |

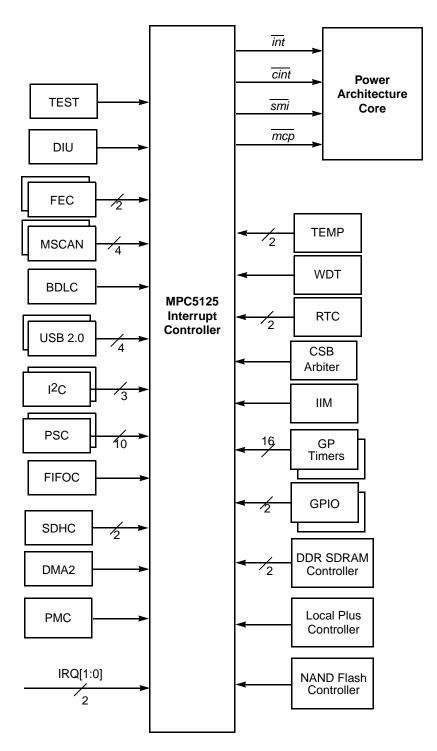

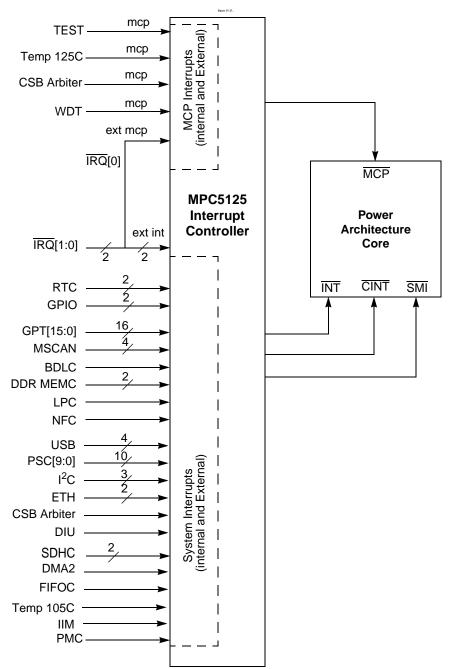

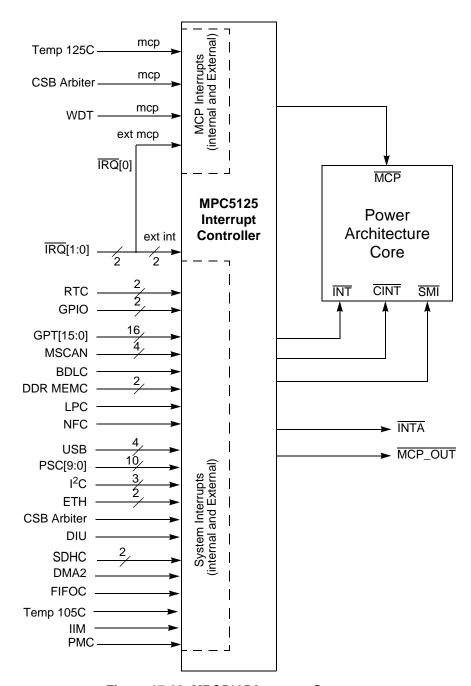

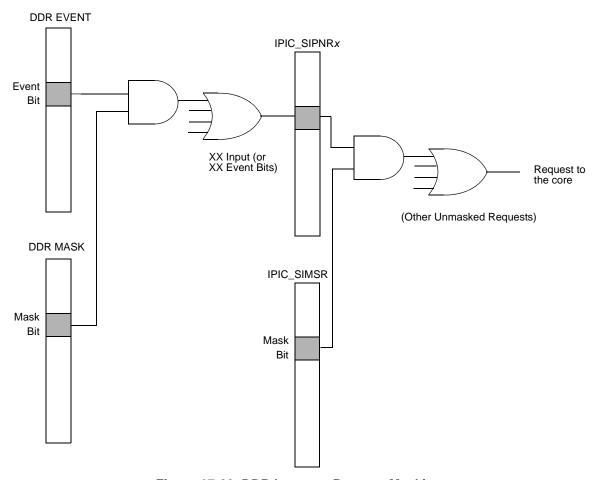

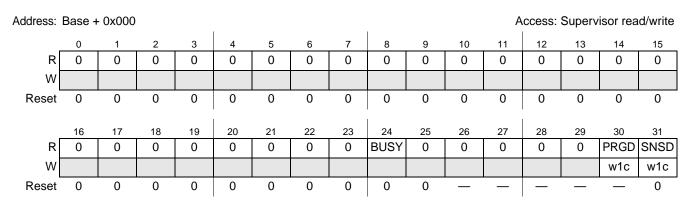

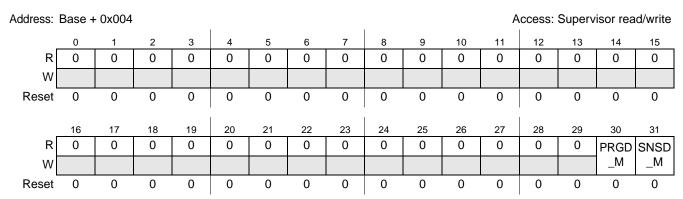

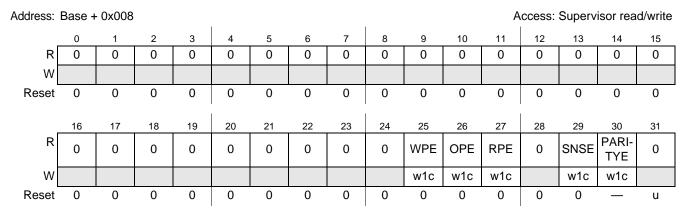

|      | Integrated Programmable Interrupt Controller (IPIC) |     |

| 17.1 | Introduction                                        |     |

|      | 17.1.1 Overview                                     |     |

|      | 17.1.2 Features                                     |     |

|      | 17.1.3 Modes of Operation                           |     |

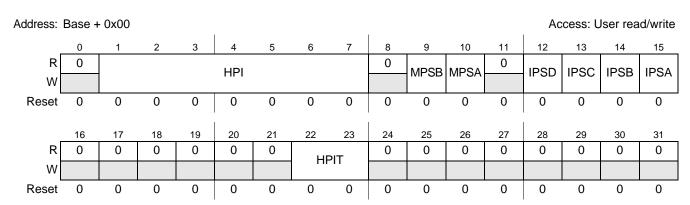

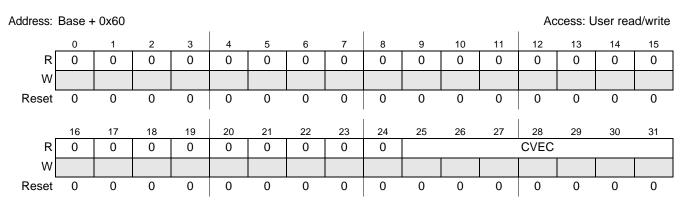

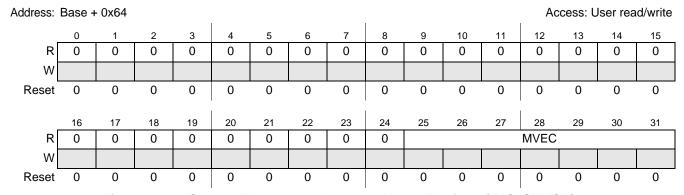

| 17.2 | Memory Map/Register Definition                      |     |

|      | 17.2.1 Register Summary                             |     |

| 17.3 | Functional Description                              |     |

|      | 17.3.1 Interrupt Types                              |     |

|      | 17.3.2 Interrupt Configuration                      |     |

|      | 17.3.3 Internal Interrupts Group Relative Priority  |     |

|      | 17.3.4 Mixed Interrupts Group Relative Priority     |     |

|      | 17.3.5 Highest Priority Interrupt                   |     |

|      | 17.3.6 Interrupt Source Priorities                  |     |

|      | 17.3.7 Masking Interrupt Sources                    |     |

|      | 17.3.8 Interrupt Vector Generation and Calculation  |     |

|      | 17.3.9 Machine Check Interrupts                     | 456 |

|      | Chantar 40                                          |     |

|      | Chapter 18                                          |     |

|      | IIM/Fusebox                                         |     |

| 18.1 | Introduction                                        | 457 |

| 18.2 | Overview                                            | 457 |

|      | 18.2.1 Features                                     | 457 |

|      | 18.2.2 Modes of Operation                           | 457 |

| 18.3 | Memory Map and Register Definition                  |     |

|      | 18.3.1 Memory Map                                   |     |

|      | 18.3.2 Register Descriptions                        |     |

| 18.4 | Functional Description                              |     |

|      |                                                     |     |

|       | 18.4.1 Fuse Bank 1                                        | . 468 |

|-------|-----------------------------------------------------------|-------|

|       | Chapter 19<br>Inter-Integrated Circuit (I <sup>2</sup> C) |       |

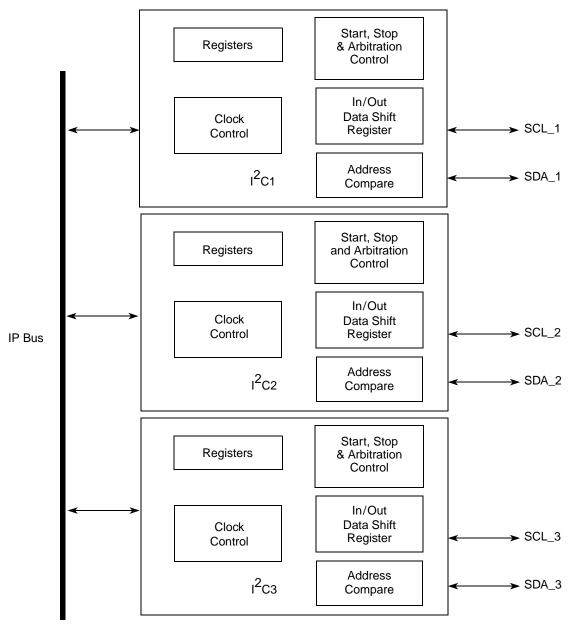

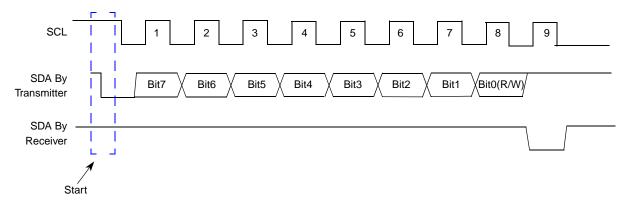

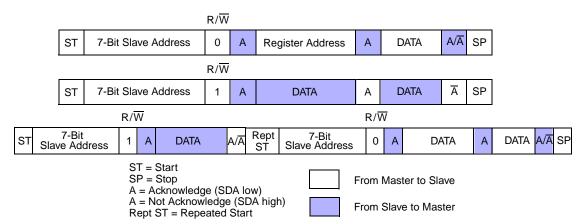

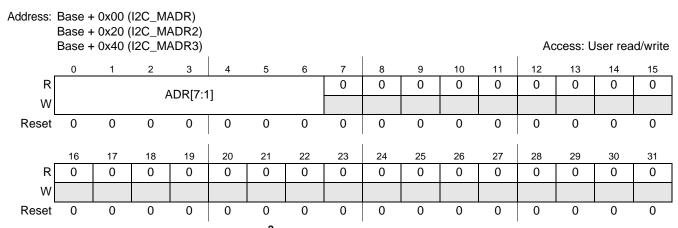

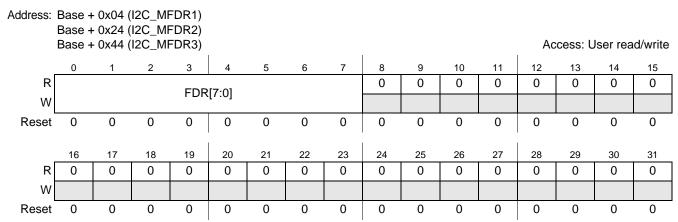

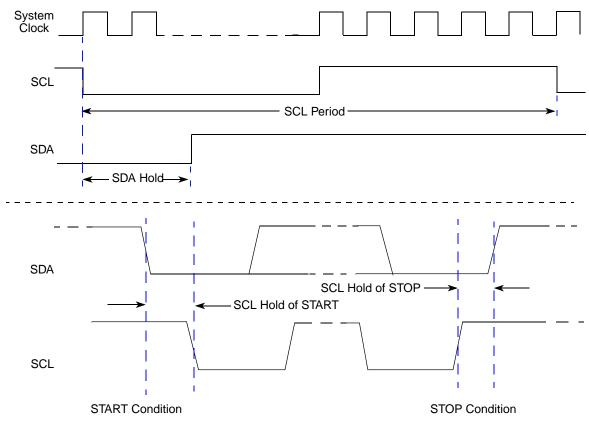

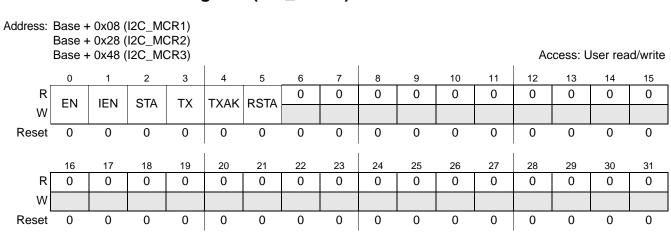

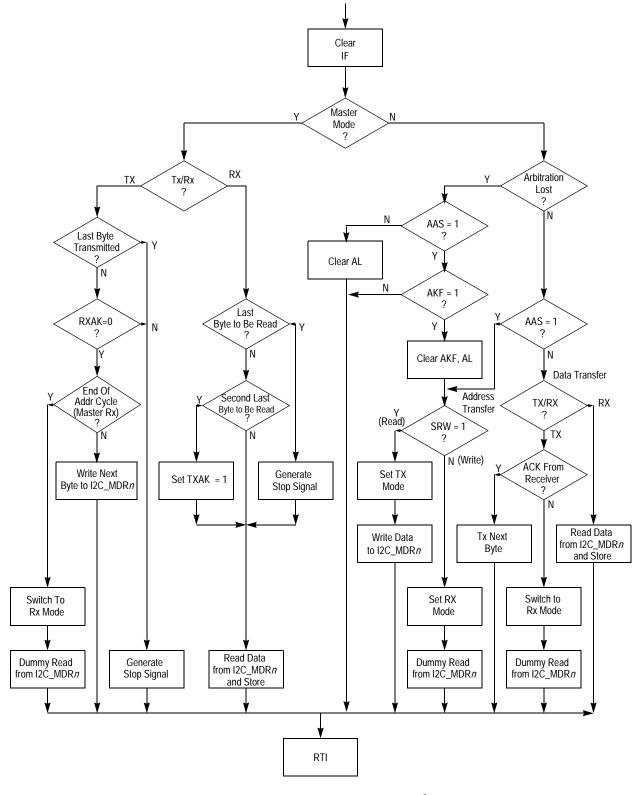

| 19.1  | Overview                                                  | . 469 |

|       | 19.1.1 Features                                           | . 470 |

|       | 19.1.2 I2C Controller                                     | . 471 |

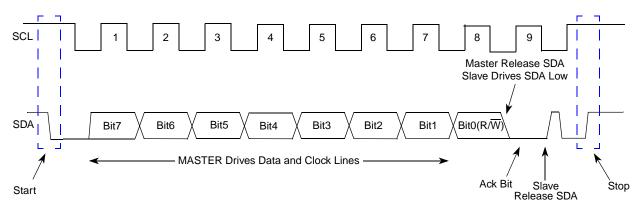

|       | 19.1.3 START Signal                                       |       |

|       | 19.1.4 STOP Signal                                        |       |

|       | 19.1.5 Acknowledge                                        |       |

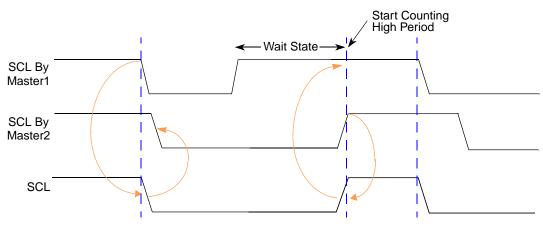

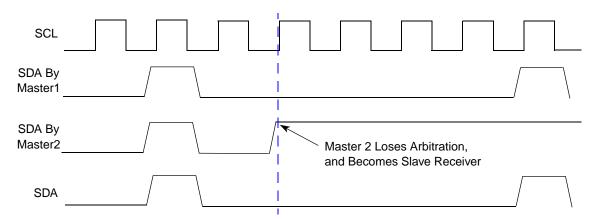

|       | 19.1.6 Arbitration                                        |       |

|       | External Signal Description                               |       |

| 19.3  | Memory Map and Register Definition                        |       |

| 10.4  | 19.3.1 Register Descriptions                              |       |

|       | Initialization Sequence                                   |       |

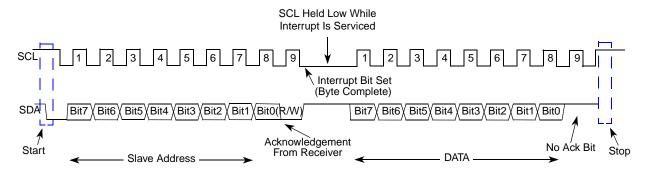

| 19.5  | Transfer Initiation and Interrupt                         |       |

|       | 19.5.1 Post-Transfer Software Response                    |       |

|       | 19.5.2 Slave Mode                                         |       |

|       | 19.5.3 Special Note on AKF                                | . 492 |

|       | Chapter 20<br>I/O Control                                 |       |

| 20.1  | Introduction                                              |       |

|       | 20.1.1 Overview                                           |       |

| • • • | 20.1.2 Features                                           |       |

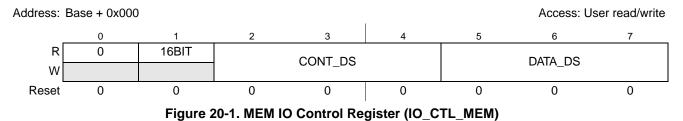

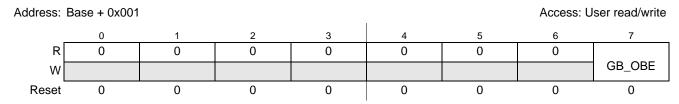

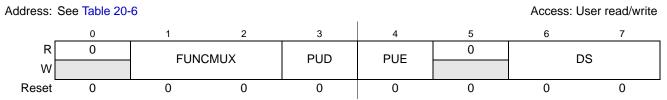

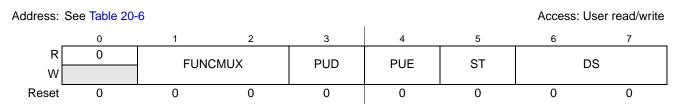

| 20.2  | Memory Map and Register Definition                        |       |

|       | 20.2.1 Memory Map                                         |       |

| 20.2  | 20.2.2 Register Descriptions                              |       |

| 20.3  | Application Information                                   | . 518 |

|       | Chapter 21                                                |       |

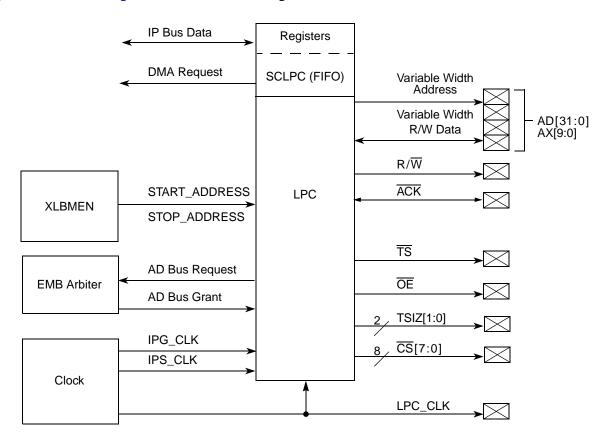

|       | LocalPlus Bus Controller (LPC)                            |       |

| 21.1  | Introduction                                              | . 519 |

|       | 21.1.1 Features                                           | . 519 |

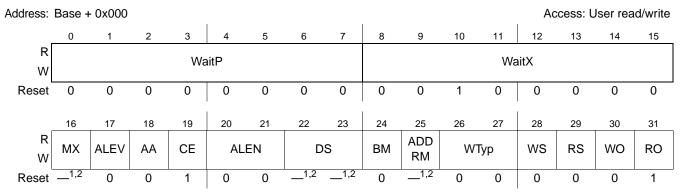

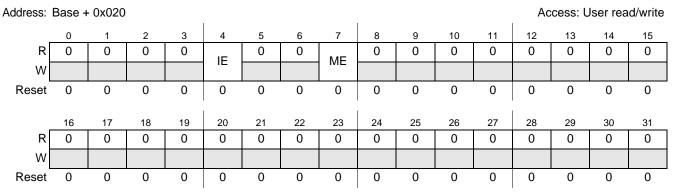

| 21.2  | Memory Map and Register Definition                        | . 521 |

|       | 21.2.1 Register Descriptions                              | . 522 |

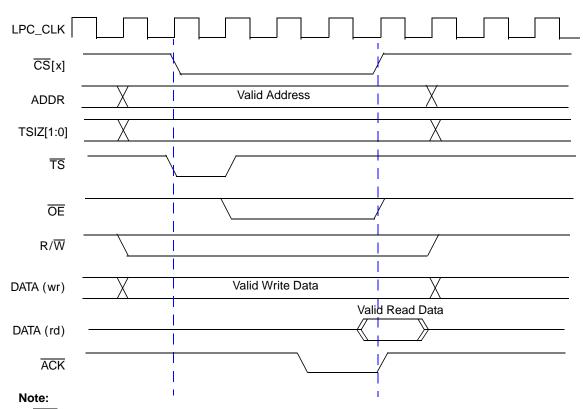

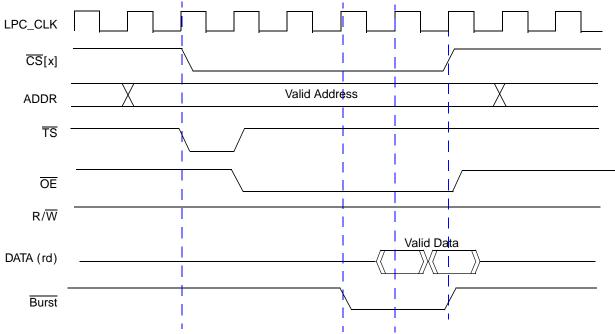

| 21.3  | Functional Description                                    | . 540 |

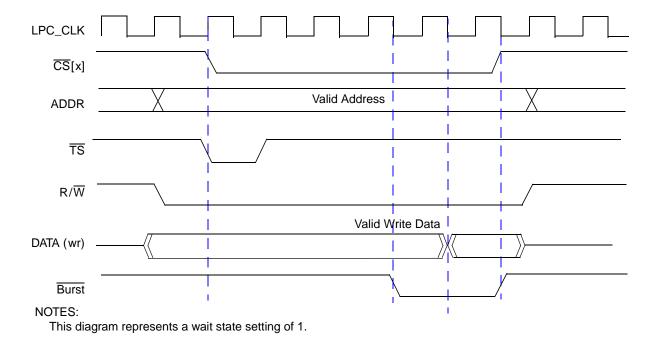

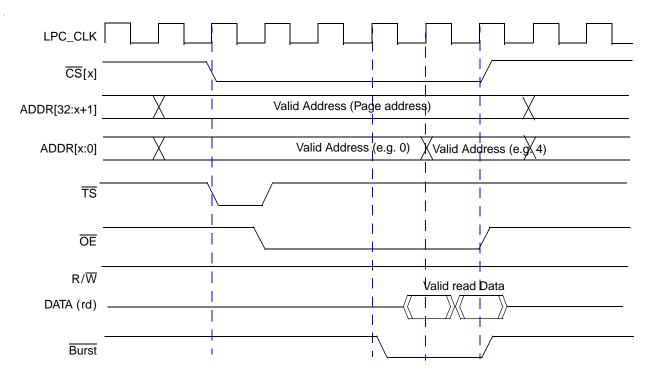

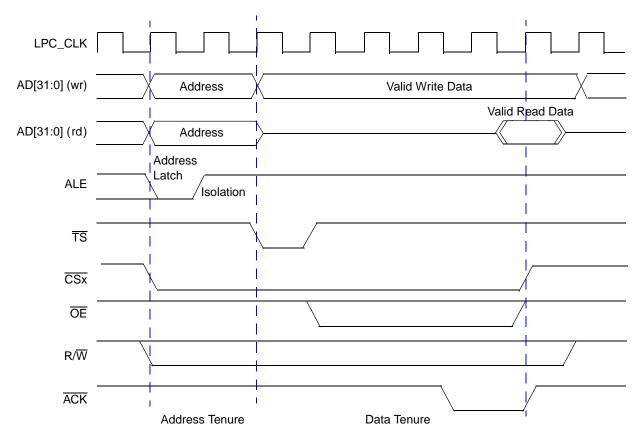

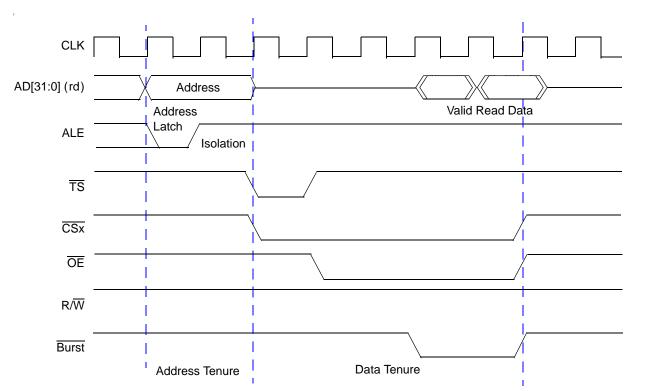

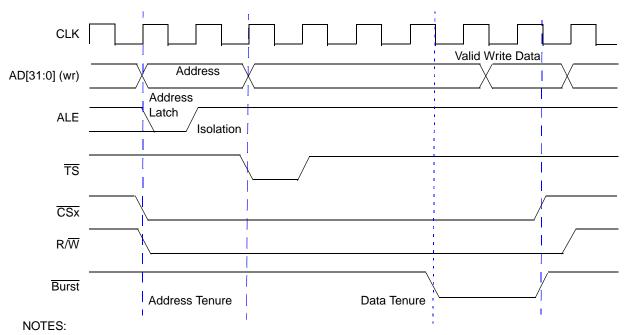

|       | 21.3.1 Non-Muxed Mode                                     | . 540 |

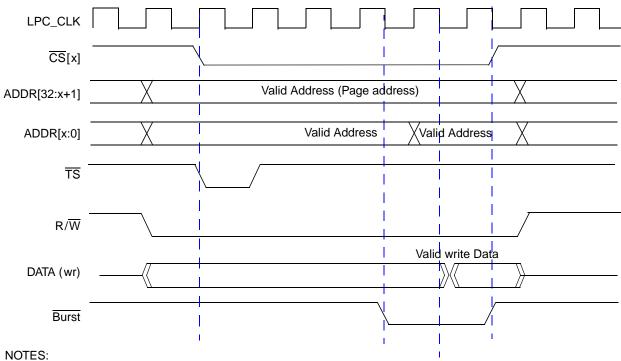

|       | 21.3.2 Muxed Mode                                         | . 548 |

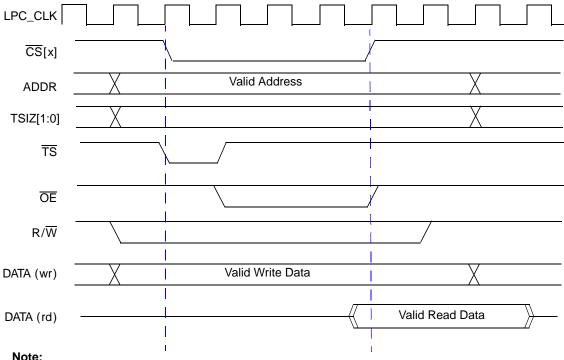

|       | 21.3.3 SCLPC Interface                                    |       |

|       | 21.3.4 Programmer's Model                                 | . 556 |

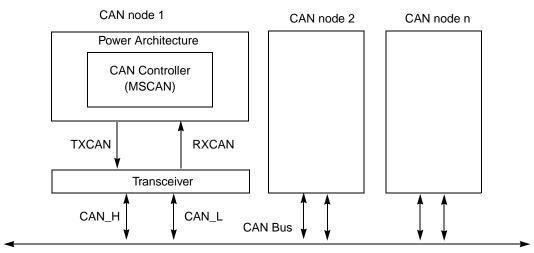

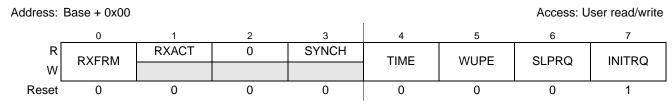

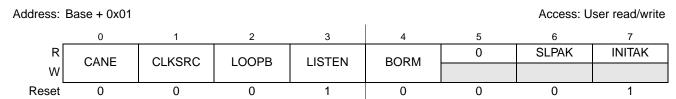

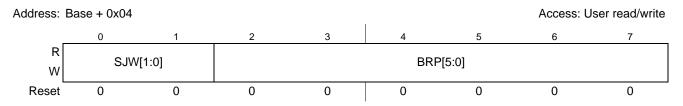

# Chapter 22 MSCAN

| 22.1 | Introduction                                 | 557 |

|------|----------------------------------------------|-----|

|      | 22.1.1 Features                              | 557 |

| 22.2 | External Signal Description                  | 558 |

|      | 22.2.1 CAN Receiver Input Pins               | 559 |

|      | 22.2.2 CAN Transmitter Output Pins           | 559 |

|      | 22.2.3 CAN System                            |     |

| 22.3 |                                              |     |

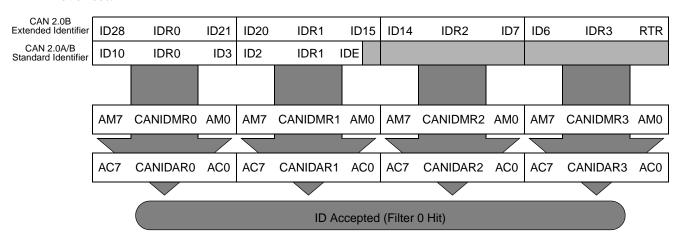

|      | 22.3.1 Register Summary                      |     |

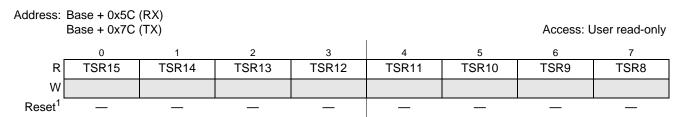

|      | 22.3.2 Register Descriptions                 |     |

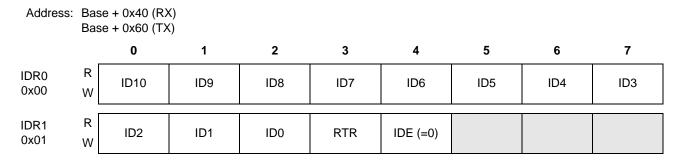

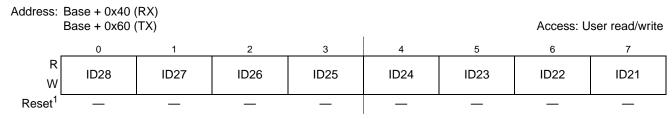

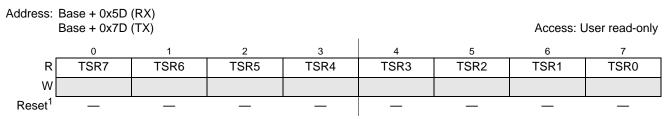

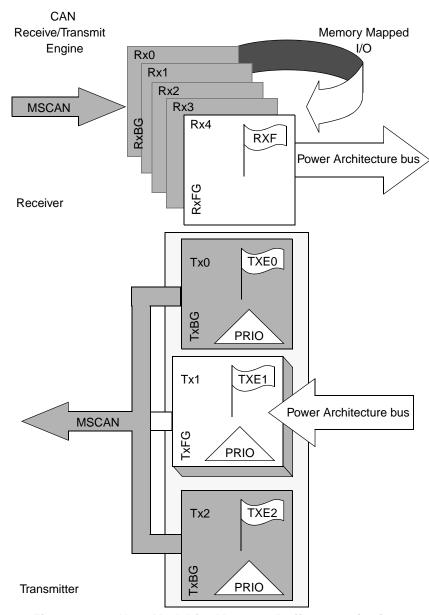

|      | 22.3.3 Programmer's Model of Message Storage |     |

| 22.4 | Functional Description                       |     |

|      | 22.4.1 General                               |     |

|      | 22.4.2 Message Storage                       | 592 |

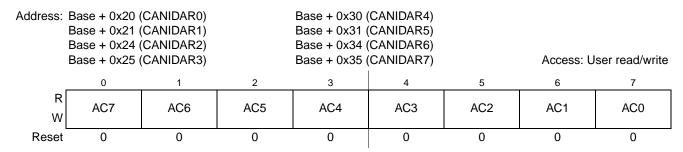

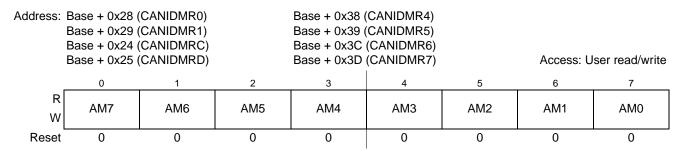

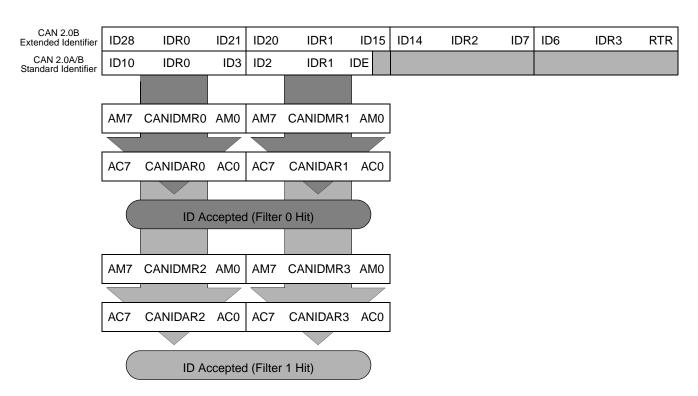

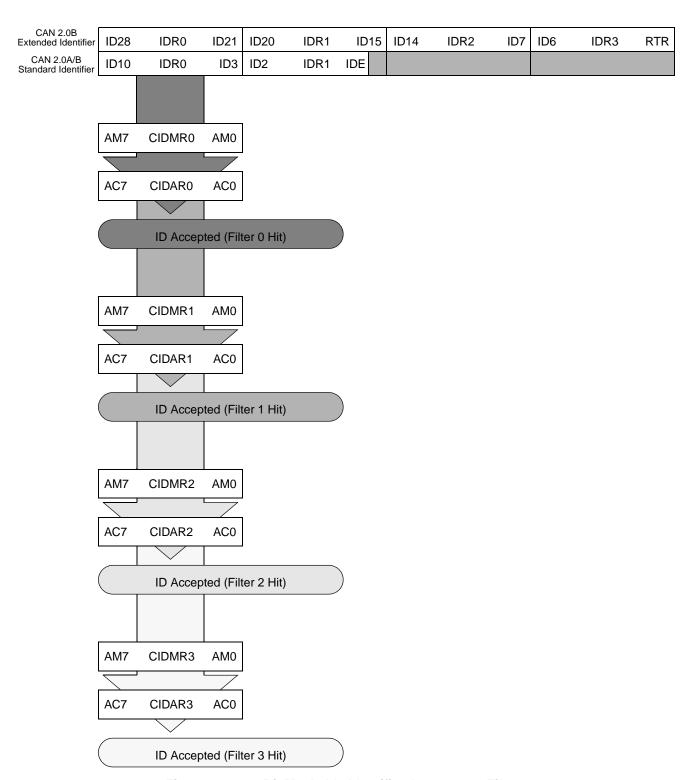

|      | 22.4.3 Identifier Acceptance Filter          | 595 |

|      | 22.4.4 Protocol Violation Protection         |     |

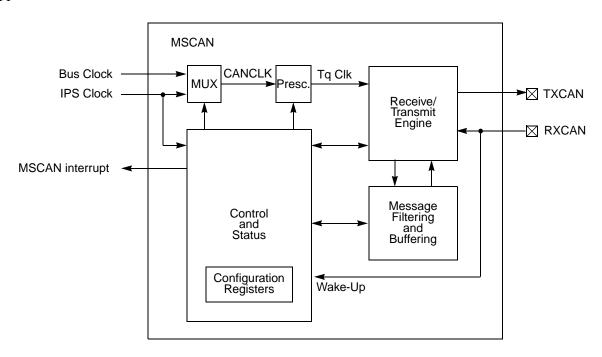

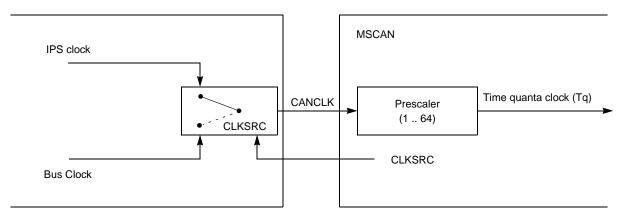

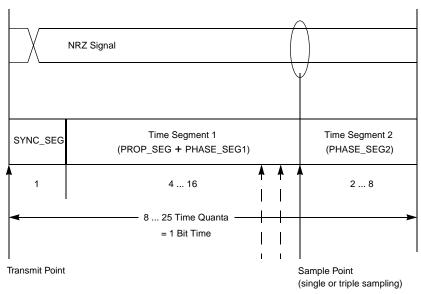

|      | 22.4.5 Clock System                          | 599 |

|      | 22.4.6 Timer Link                            |     |

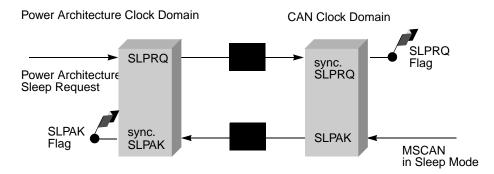

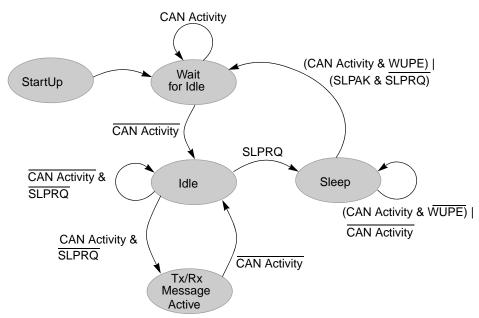

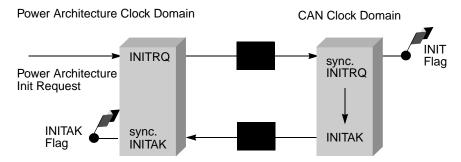

|      | 22.4.7 Modes of Operation                    | 602 |

|      | 22.4.8 Low Power Options                     |     |

|      | 22.4.9 Reset Initialization                  |     |

|      | 22.4.10Interrupts                            | 606 |

|      | 22.4.11 Description of Interrupt Operation   |     |

|      | 22.4.12Interrupt Acknowledge                 |     |

|      | 22.4.13Recovery from Deep Sleep Mode         | 608 |

|      | 22.4.14MSCAN Initialization                  |     |

|      | 22.4.15Bus-Off Recovery                      | 609 |

|      |                                              |     |

|      | Chapter 23                                   |     |

|      | NAND Flash Controller (NFC)                  |     |

| 23.1 | Introduction                                 | 611 |

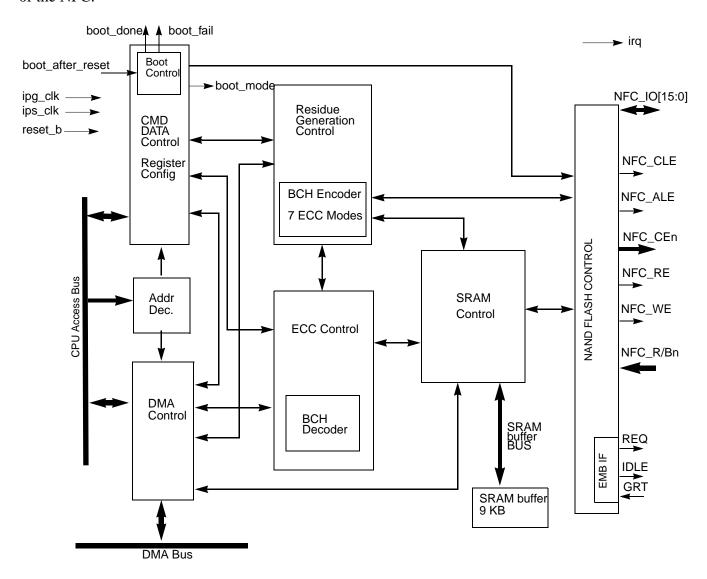

| 23.2 | Overview                                     | 612 |

| 23.3 | Features                                     | 612 |

| 23.4 | External Signal Description                  | 612 |

|      | 23.4.1 Overview                              |     |

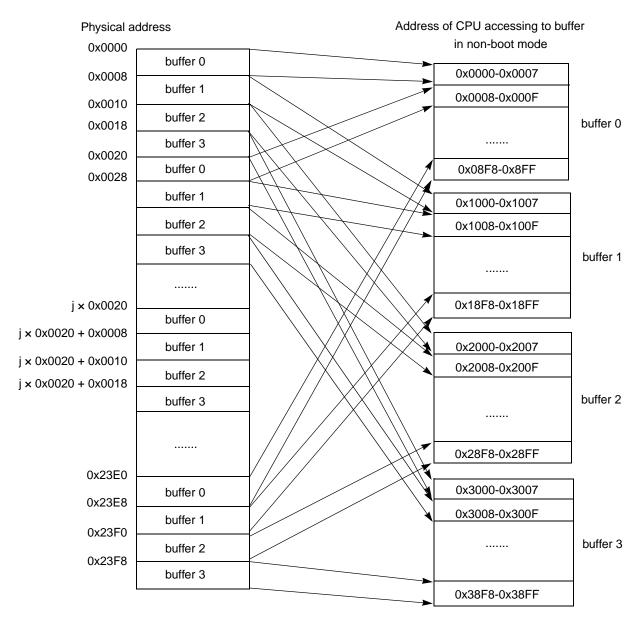

| 23.5 | NFC Buffer Memory Space                      |     |

|      | Memory Map and Register Definition           |     |

|      | 23.6.1 Memory Map                            |     |

|      | 23.6.2 Register Summary                      |     |

| 23.7 | Register Descriptions                        |     |

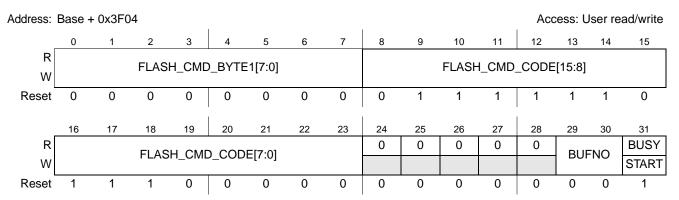

|      | 23.7.1 Flash Command 1 register (FLASH_CMD1) |     |

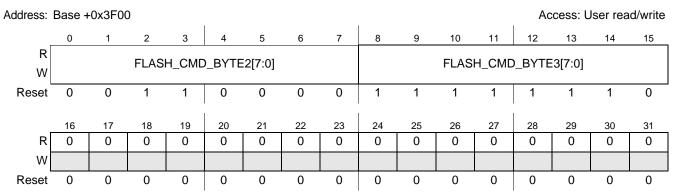

|      | 23.7.2 Flash Command 2 register (FLASH_CMD2) |     |

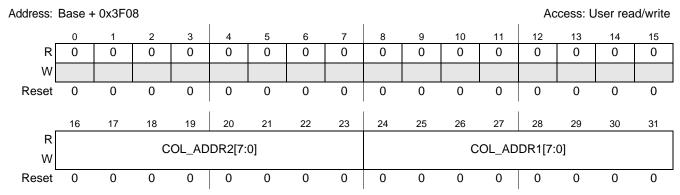

|      | 23.7.3 Column Address register (COL_ADDR)    |     |

|      | · · · · · · · · · · · · · · · · · · ·        |     |

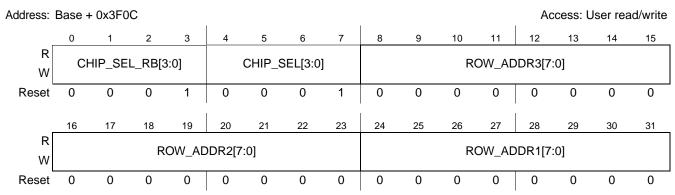

|              | 23.7.4 Row Address register (ROW_ADDR)                      | 620  |

|--------------|-------------------------------------------------------------|------|

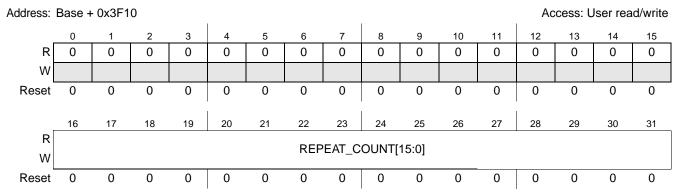

|              | 23.7.5 Flash Command Repeat register (FLASH_COMMAND_REPEAT) | 620  |

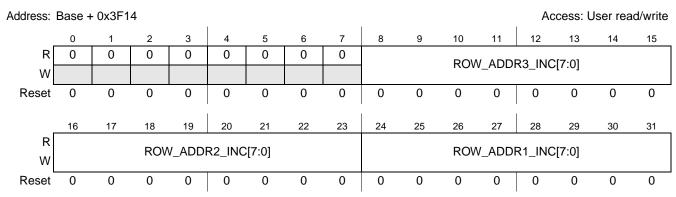

|              | 23.7.6 Row Address Increment register (ROW_ADDR_INC)        | 621  |

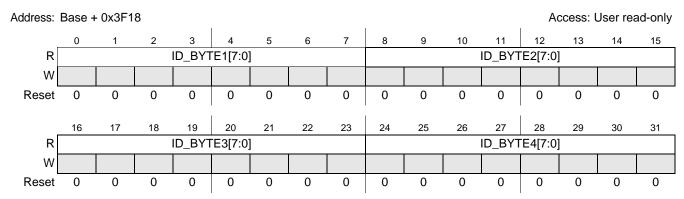

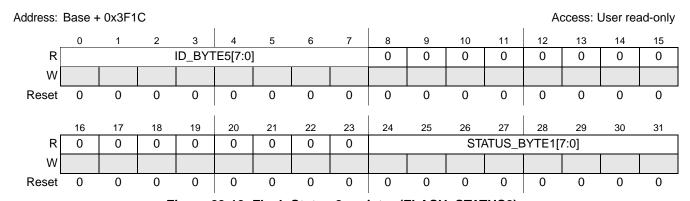

|              | 23.7.7 Flash Status 1 register (FLASH_STATUS1)              | 622  |

|              | 23.7.8 Flash Status 2 register (FLASH_STATUS2)              | 622  |

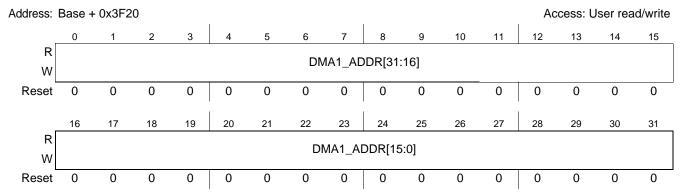

|              | 23.7.9 DMA1 Address register (DMA1_ADDR)                    | 623  |

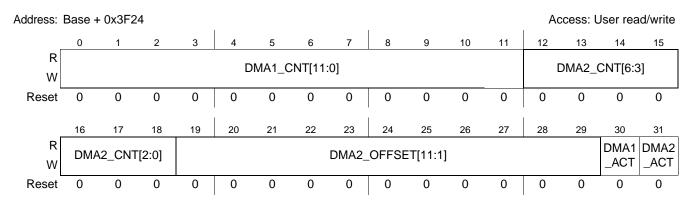

|              | 23.7.10DMA Configuration register (DMA_CONFIG)              | 623  |

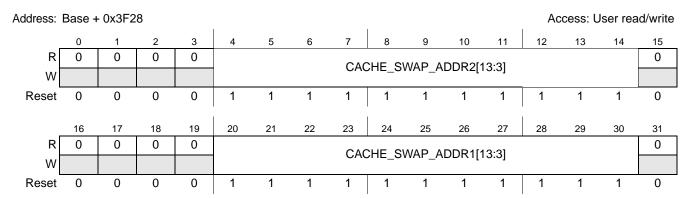

|              | 23.7.11Cache Swap register (CACHE_SWAP)                     |      |

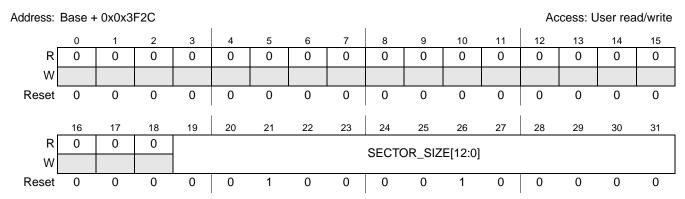

|              | 23.7.12Sector Size register (SECTOR_SIZE)                   | 625  |

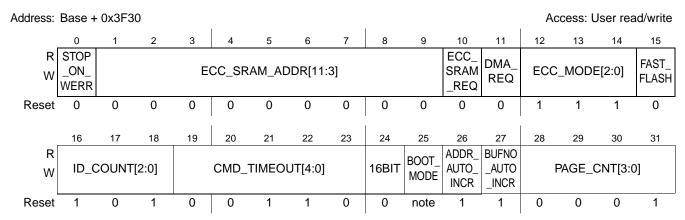

|              | 23.7.13Flash Configuration register (FLASH_CONFIG)          |      |

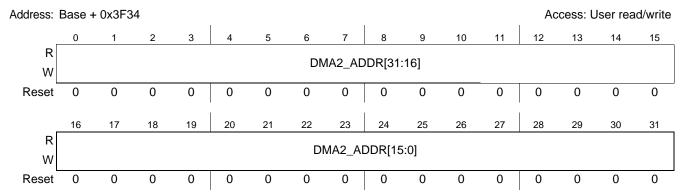

|              | 23.7.14DMA2 Address register (DMA2_ADDR)                    | 627  |

|              | 23.7.15IRQ and Status register (IRQ_STATUS)                 |      |

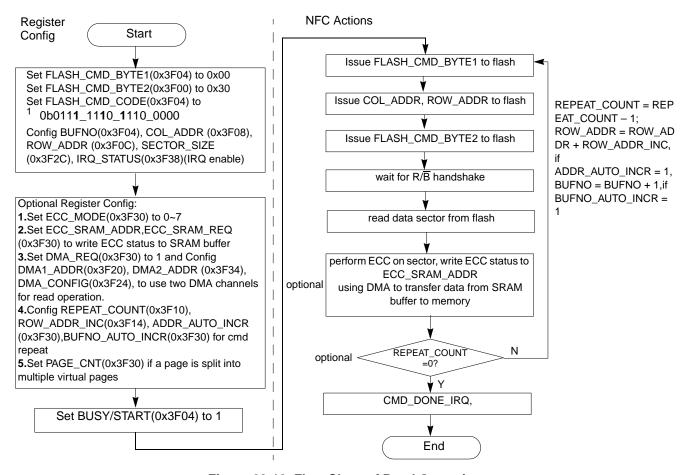

| 23.8         | Functional Description                                      | 629  |

|              | 23.8.1 Error Corrector Status                               | 631  |

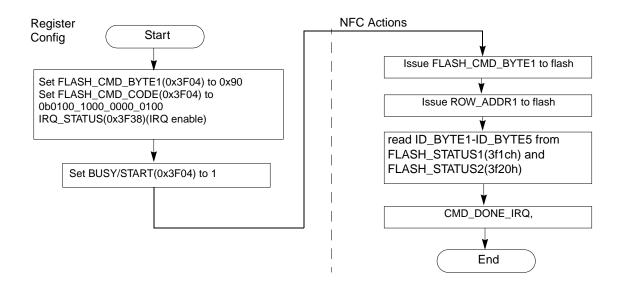

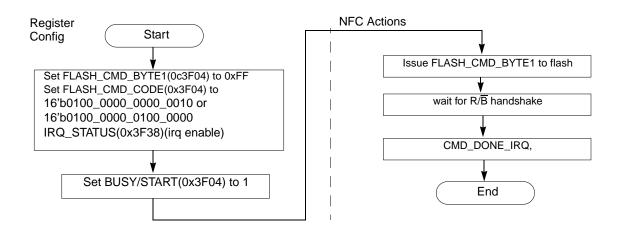

|              | 23.8.2 NFC Basic Commands                                   | 631  |

|              | 23.8.3 NAND Flash boot                                      |      |

|              | 23.8.4 Fast Flash Configuration for EDO                     | 639  |

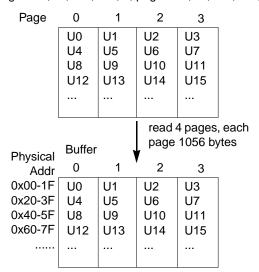

|              | 23.8.5 Organization of Data in the NAND Flash               |      |

|              | 23.8.6 Flash Command Sequencer                              | 642  |

|              | Chapter 24                                                  |      |

|              | Power Management Control Module (PMC)                       |      |

| 24.1         | Introduction                                                | 6/15 |

| <b>24.</b> 1 | 24.1.1 Features                                             |      |

| 24.2         | Memory Map and Register Definition                          |      |

| 27.2         | 24.2.1 Memory Map                                           |      |

|              | 24.2.2 Register Descriptions                                |      |

| 24 3         | Functional Description                                      |      |

| 21.5         | 24.3.1 Full-Power Mode                                      |      |

|              | 24.3.2 Doze Mode                                            |      |

|              | 24.3.3 Nap Mode                                             |      |

|              | 24.3.4 Sleep Mode                                           |      |

|              | 24.3.5 Deep Sleep Mode                                      |      |

|              | 24.3.6 Core PLL Change Mode                                 |      |

|              | 24.3.7 PRE_DIV Copy Enable Mode                             |      |

|              | 24.3.8 Low-Power Configurations                             |      |

|              | Chantar 25                                                  |      |

|              | Chapter 25                                                  |      |

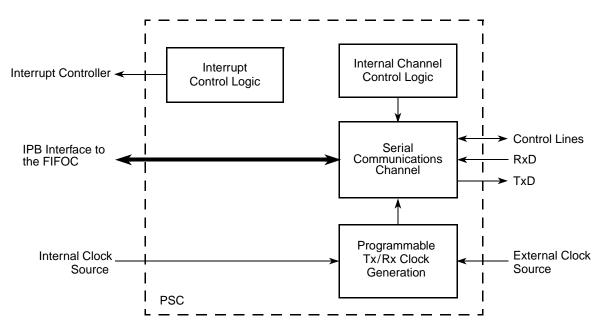

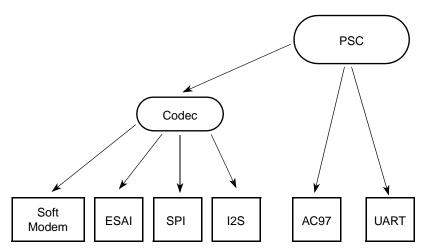

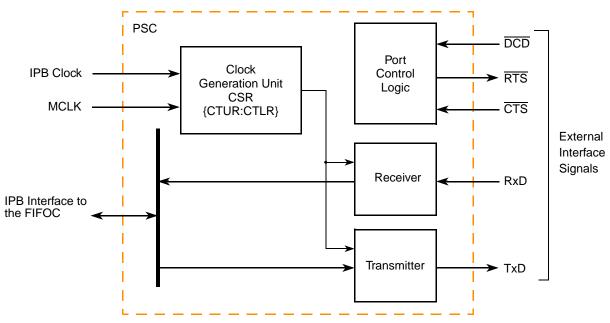

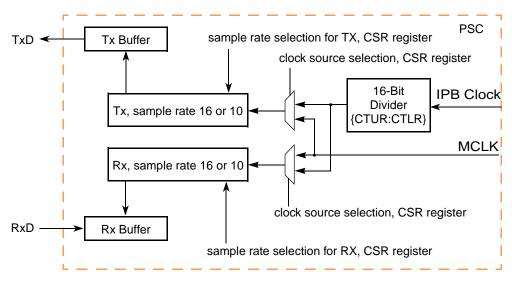

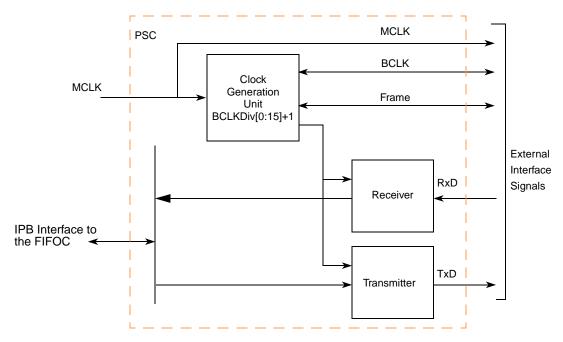

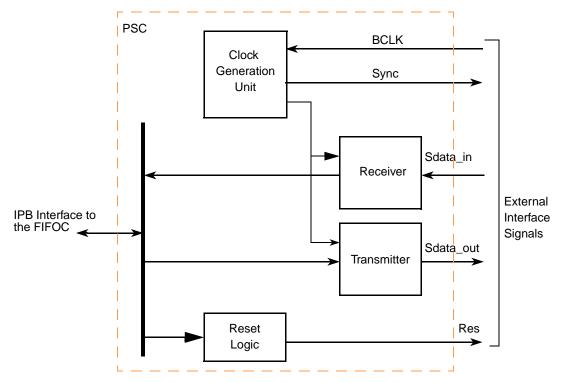

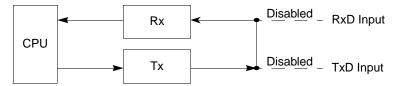

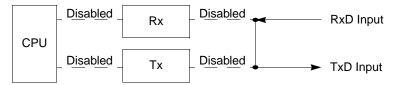

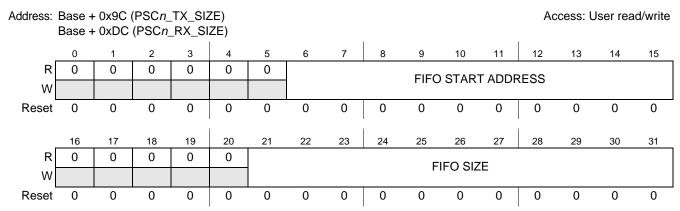

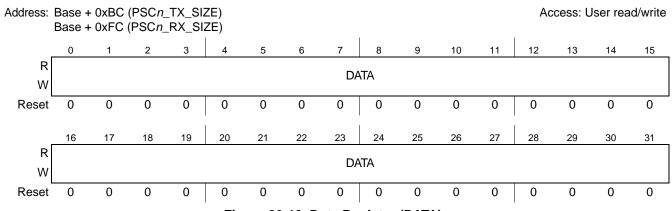

| 25.1         | Programmable Serial Controller (PSC) Introduction           | 650  |

|              | Features                                                    |      |

|              | PSC Functions Overview                                      |      |

|              | Memory Map and Registers                                    |      |

| 43.4         | Memory Map and Registers                                    |      |

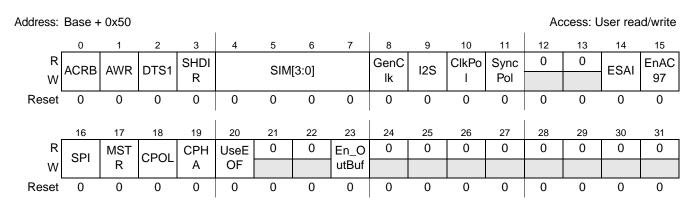

|              | 25.4.1 Register Descriptions                                |      |

| 25.5 | Modes of Operation                                                                      | 690     |

|------|-----------------------------------------------------------------------------------------|---------|

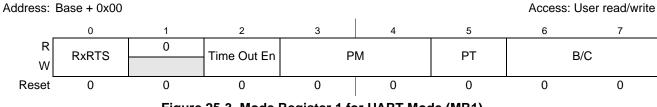

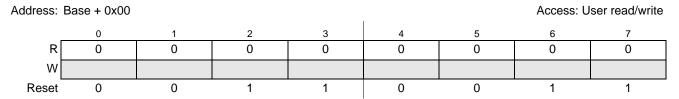

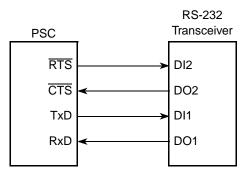

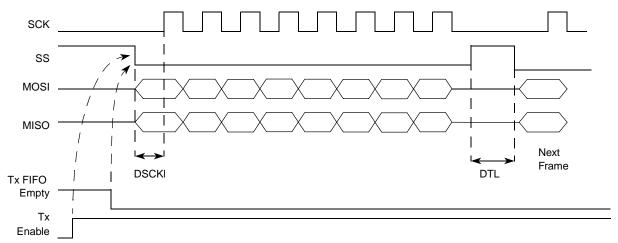

|      | 25.5.1 PSC in UART Mode                                                                 | 690     |

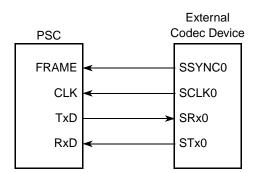

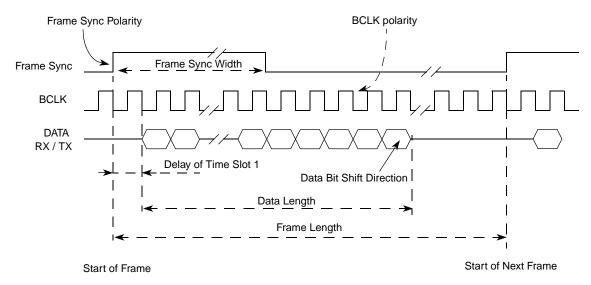

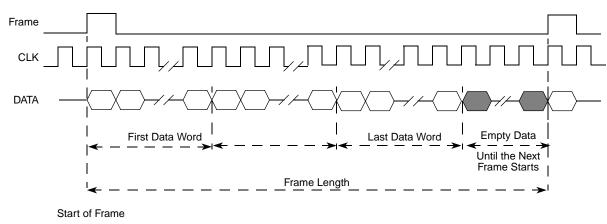

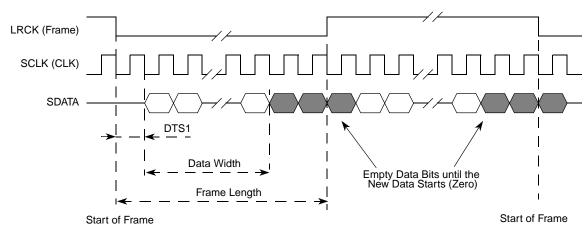

|      | 25.5.2 PSC in Codec Mode                                                                | 697     |

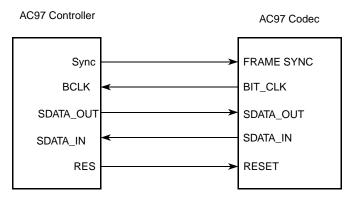

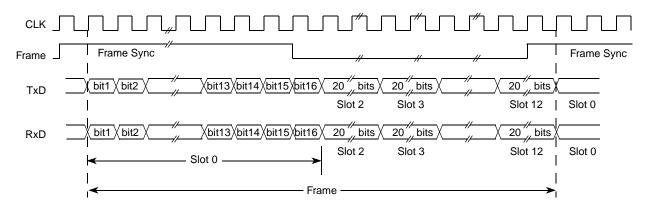

|      | 25.5.3 PSC in AC97 Mode                                                                 | 707     |

|      | 25.5.4 Local Loop-Back Mode                                                             | 711     |

|      | 25.5.5 Remote Loop-Back Mode                                                            |         |

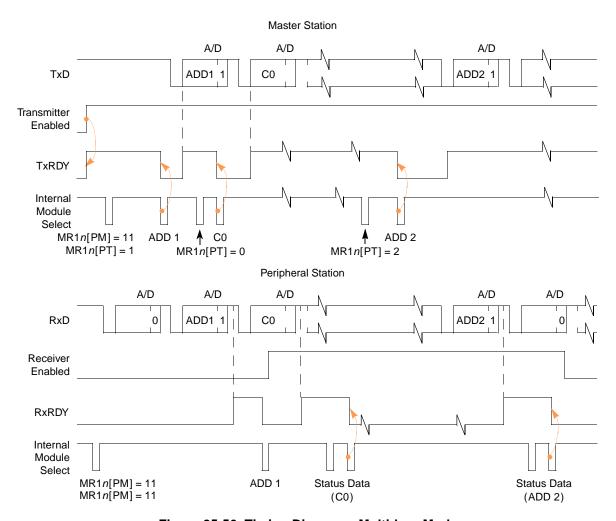

|      | 25.5.6 Multidrop Mode                                                                   |         |

|      |                                                                                         |         |

|      | Chapter 26                                                                              |         |

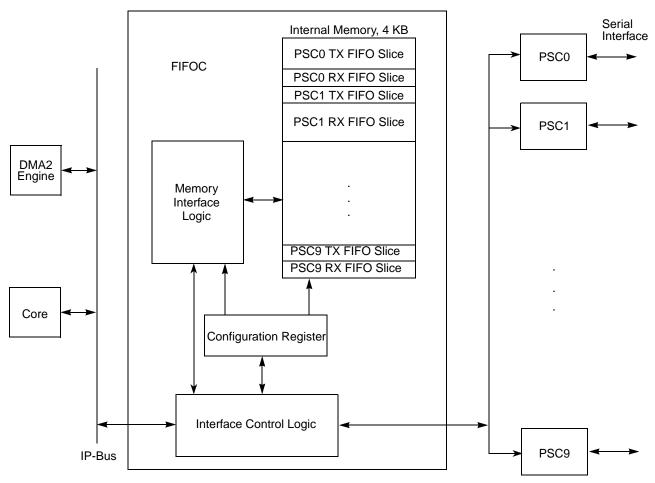

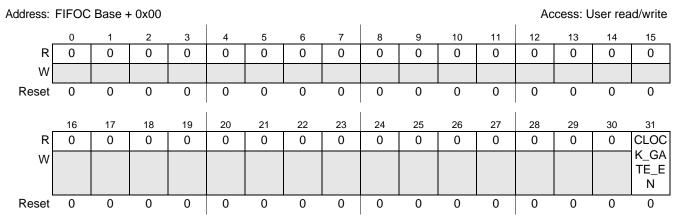

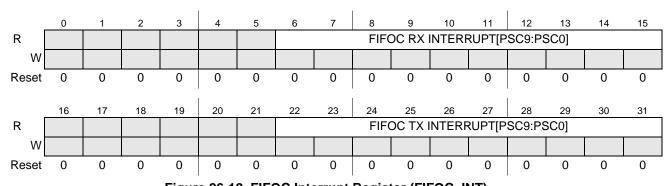

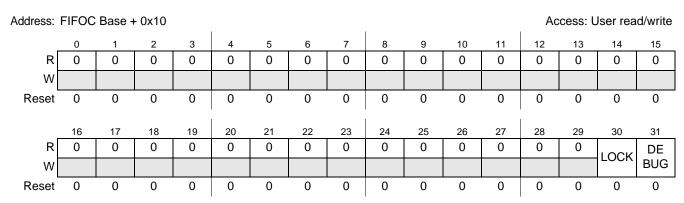

|      | PSC Centralized FIFO Controller (FIFOC)                                                 |         |

| 26.1 | Introduction                                                                            | 715     |

|      | 26.1.1 Features                                                                         |         |

|      | 26.1.2 Modes of Operation                                                               |         |

| 26.2 | Memory Map and Register Definition                                                      |         |

|      | 26.2.1 Register Descriptions                                                            |         |

| 26.3 | Functional Description                                                                  |         |

|      |                                                                                         |         |

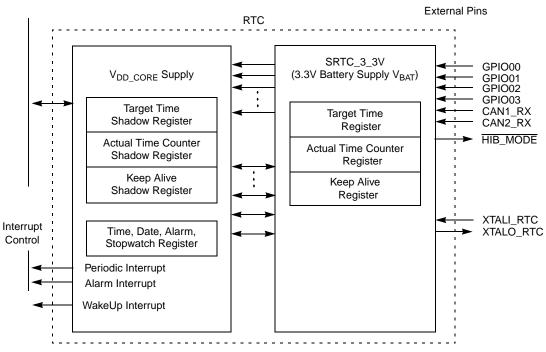

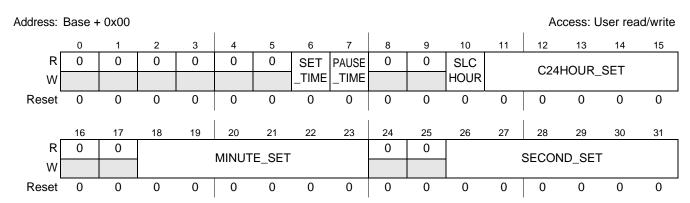

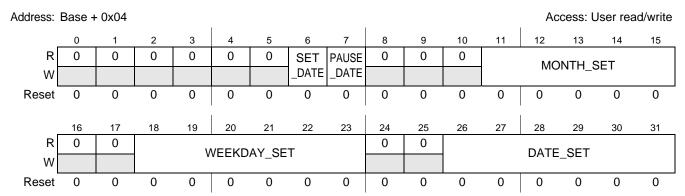

|      | Chapter 27                                                                              |         |

|      | Real Time Clock (RTC)                                                                   |         |

| 27.1 | Introduction                                                                            |         |

|      | 27.1.1 Features                                                                         |         |

| 27.2 | External Signal Descriptions                                                            |         |

| 27.3 | J 1 0                                                                                   |         |

|      | 27.3.1 Memory Map                                                                       |         |

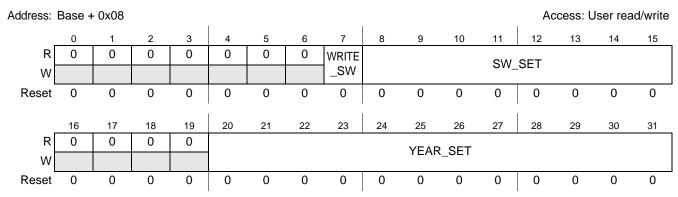

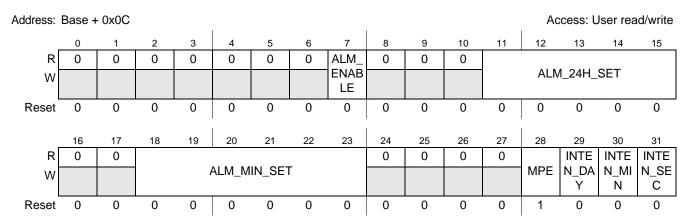

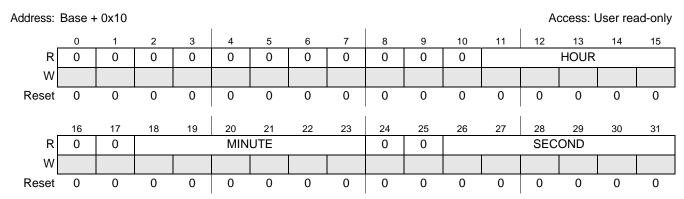

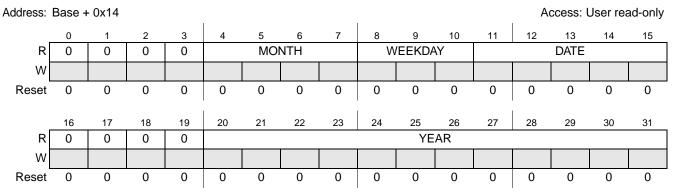

|      | 27.3.2 Register Descriptions                                                            |         |

| 27.4 | Functional Description                                                                  |         |

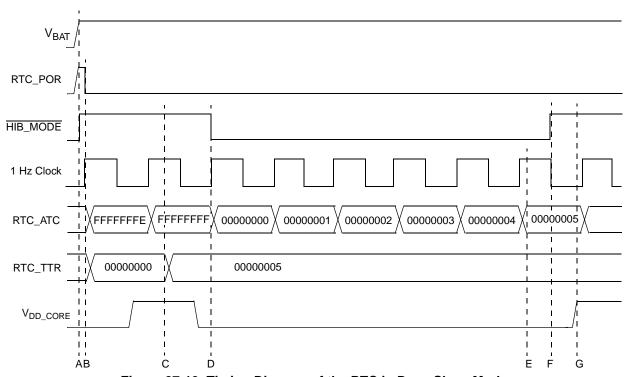

|      | 27.4.1 Behavior at Power On                                                             |         |

|      | 27.4.2 Behavior of Wakeup Sources                                                       |         |

|      | 27.4.3 Behavior During Power Off (Hibernation Mode)                                     |         |

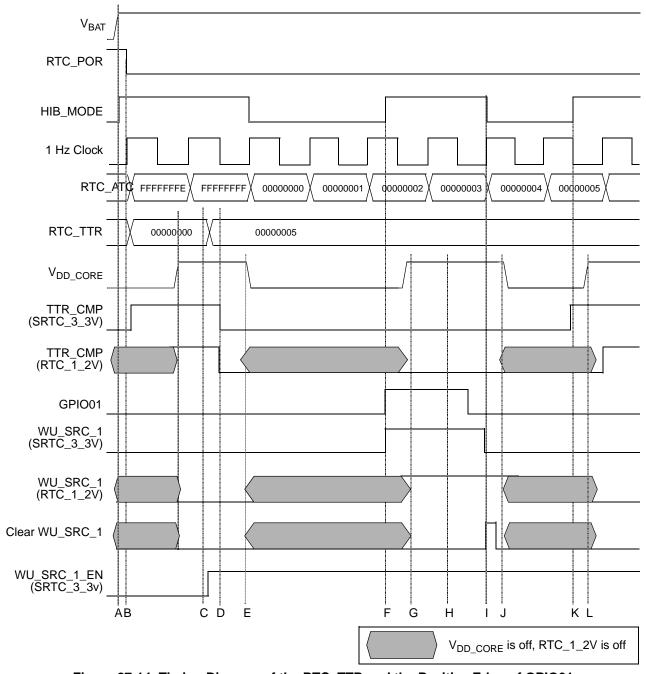

|      | 27.4.4 RTC Response to Target Time Register/Actual Time Count Register and External Wal | _       |

|      | Sources                                                                                 |         |

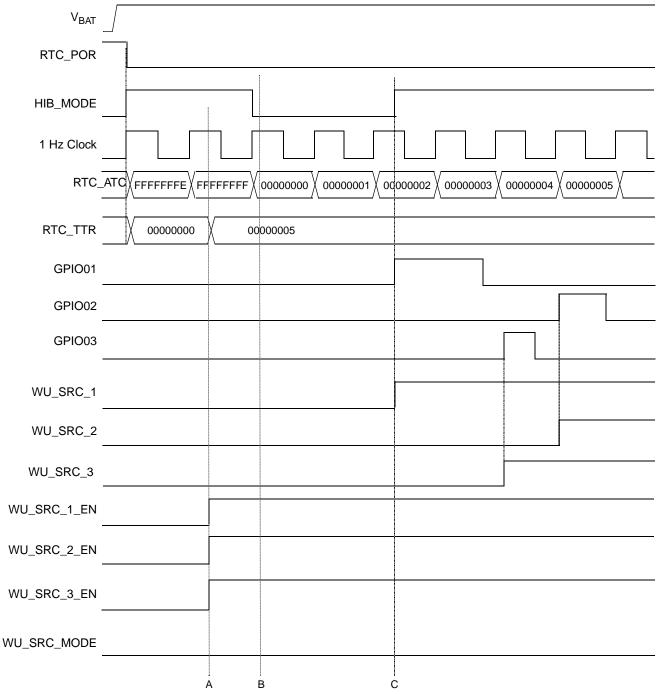

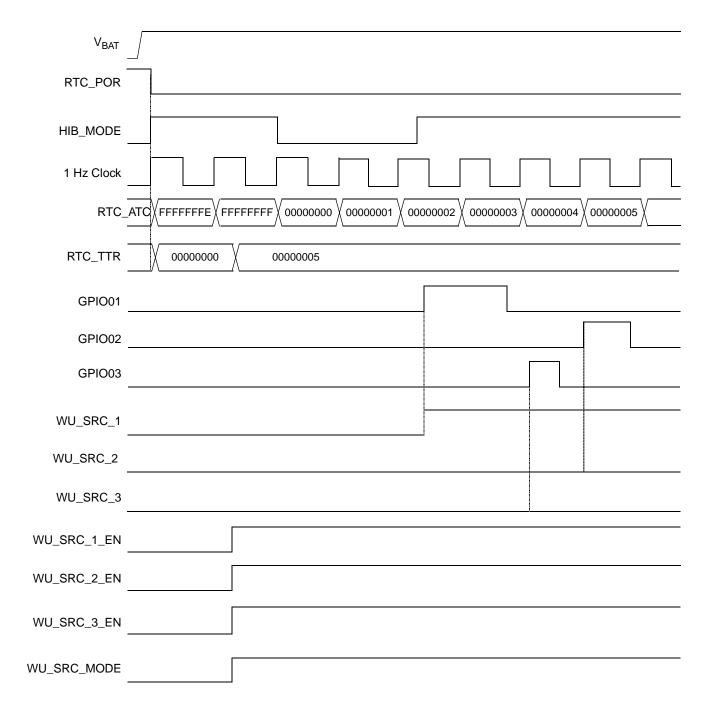

|      | 27.4.5 RTC Response to External Wakeup Sources                                          | 751     |

|      | Chapter 28                                                                              |         |

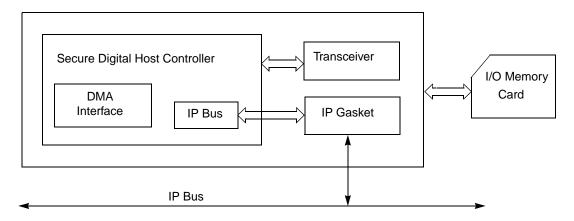

|      | Secure Digital Host Controller (SDHC)                                                   |         |

| 28 1 | Introduction                                                                            | 755     |

| 20.1 | 28.1.1 Features                                                                         |         |

| 28.2 | External Signal Description                                                             |         |

| 20.2 | 28.2.1 Detailed Signal Descriptions                                                     |         |

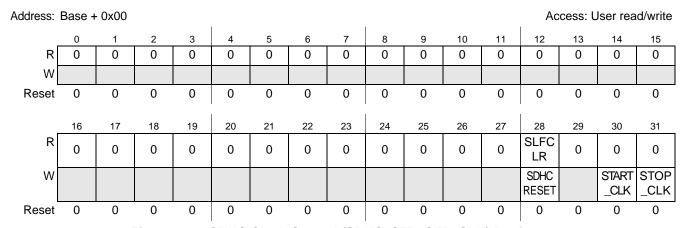

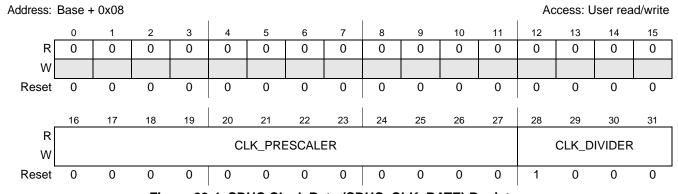

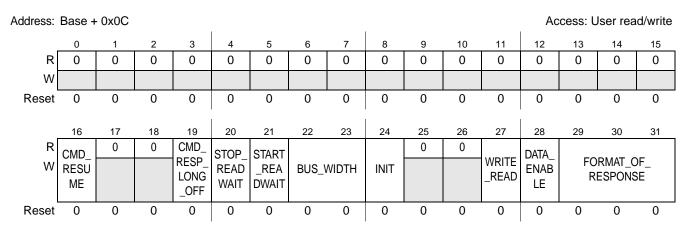

| 28.3 | Memory Map and Register Definition                                                      |         |

| 20.3 | 28.3.1 Memory Map                                                                       |         |

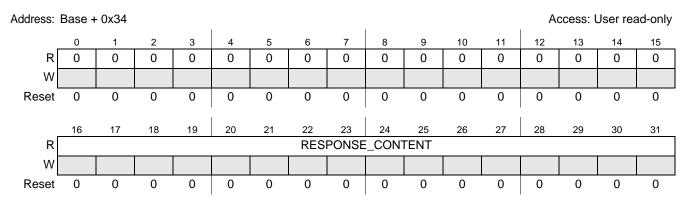

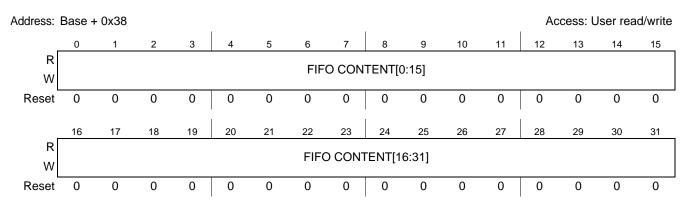

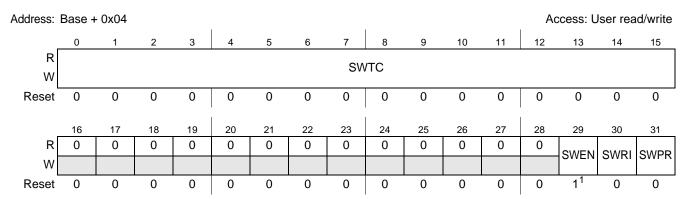

|      | 28.3.2 Register Descriptions                                                            |         |

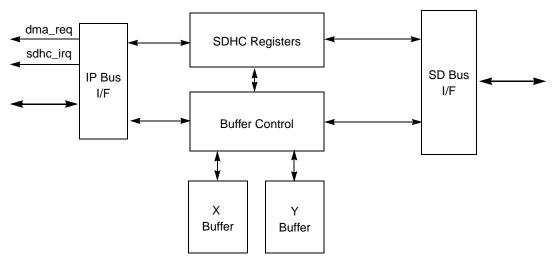

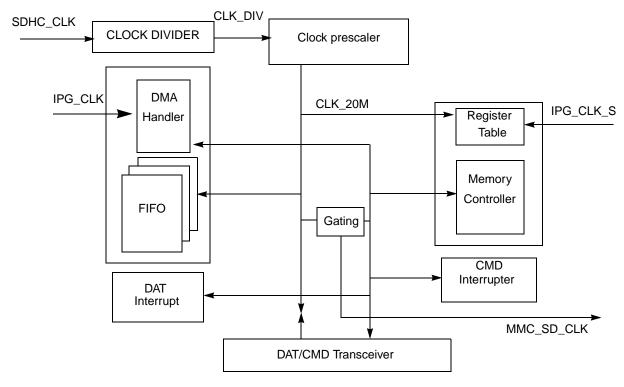

| 28 4 | Functional Description                                                                  |         |

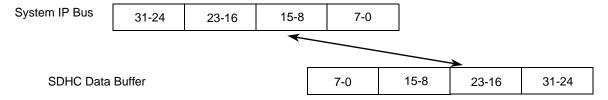

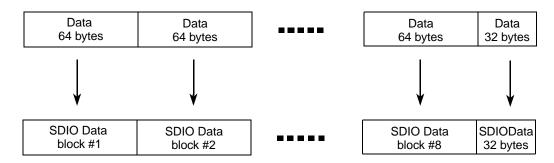

| 20.∓ | 28.4.1 Data Buffers                                                                     |         |

|      | 20 Dum Dullois                                                                          | , , , , |

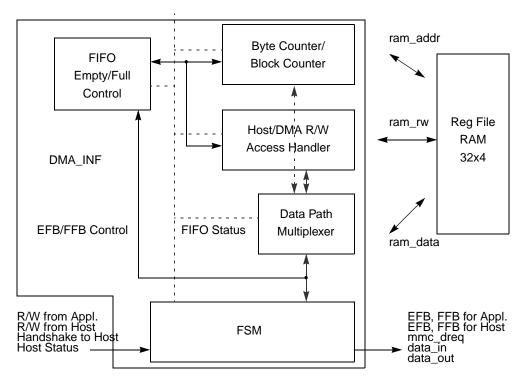

|      | 28.4.2 DMA Interface                                     | 781 |

|------|----------------------------------------------------------|-----|

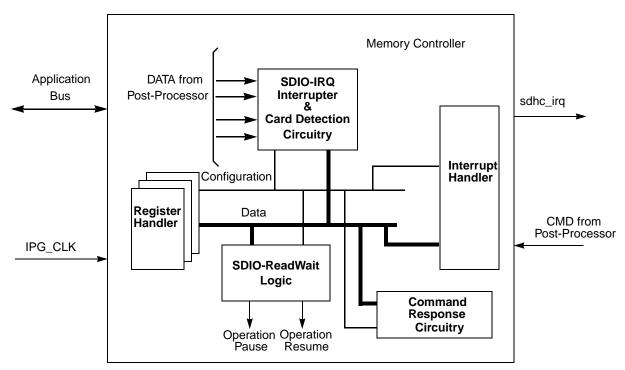

|      | 28.4.3 Memory Controller                                 | 782 |

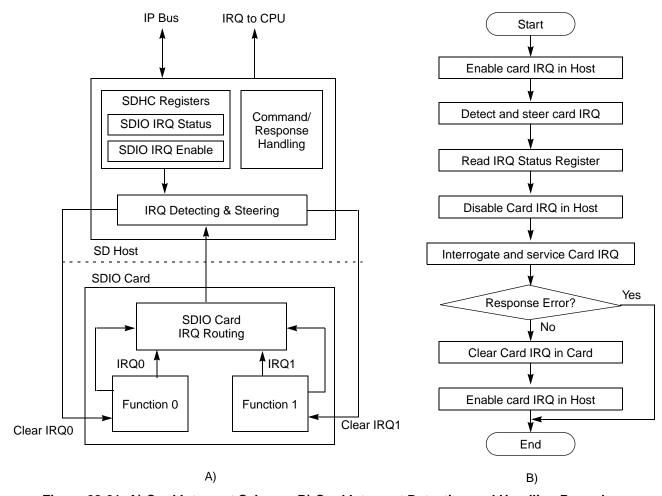

|      | 28.4.4 SDIO Card Interrupt                               | 783 |

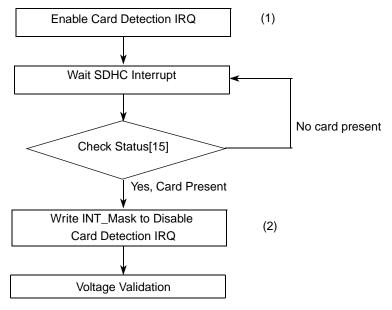

|      | 28.4.5 Card Insertion and Removal Detection              | 785 |

|      | 28.4.6 Power Management                                  | 786 |

|      | 28.4.7 System Clock Controller                           |     |

| 28.5 |                                                          |     |

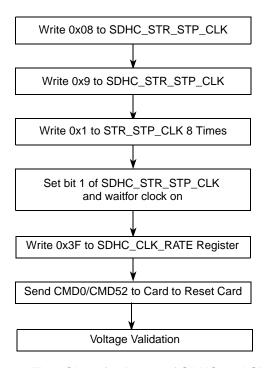

|      | 28.5.1 MMC_SD_CLK Control                                | 788 |

|      | 28.5.2 Command Submit – Response Receive Basic Operation |     |

|      | 28.5.3 Card Identification Mode                          |     |

|      | 28.5.4 Card Access                                       | 793 |

|      | 28.5.5 Switch Card Mode                                  | 796 |

|      | Chapter 29                                               |     |

|      | Software Watchdog Timer (WDT)                            |     |

| 29.1 | Introduction                                             | 799 |

| 27.1 | 29.1.1 Features                                          |     |

|      | 29.1.2 Modes of Operation                                |     |

| 29.2 | Memory Map/Register Definition                           |     |

|      | 29.2.1 Memory Map                                        |     |

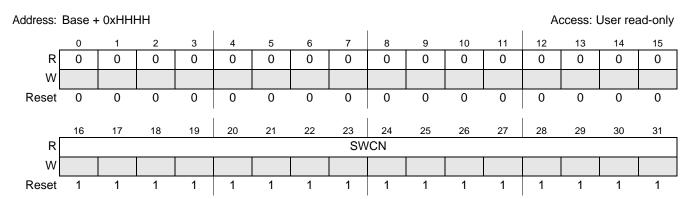

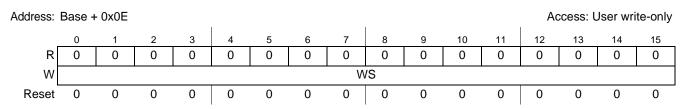

|      | 29.2.2 Register Descriptions                             |     |

| 29.3 | Functional Description                                   |     |

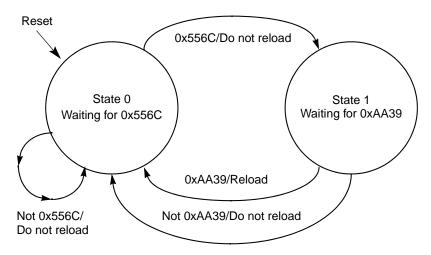

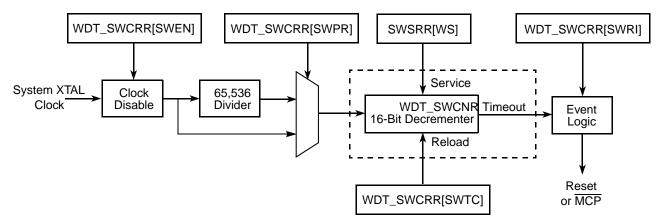

| _,   | 29.3.1 Software Watchdog Timer Unit                      |     |

|      | 29.3.2 Modes of Operation                                |     |

|      | Chapter 30                                               |     |

|      | SRAM Memory (MEM)                                        |     |

| 30.1 | Introduction                                             | 807 |

|      | Chapter 31                                               |     |

|      | Temperature Sensor                                       |     |

| 31.1 | Introduction                                             | 809 |

|      | 31.1.1 Normal Operation Mode                             |     |

|      |                                                          |     |

|      | Chapter 32                                               |     |

| 22.1 | Universal Serial Bus Interface with On-The-Go            | 011 |

| 32.1 | Introduction                                             |     |

|      | 32.1.2 Features                                          |     |

|      |                                                          |     |

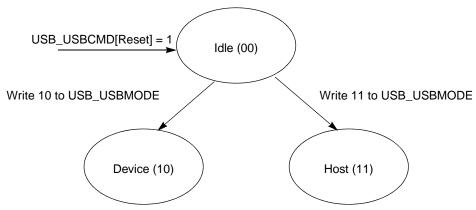

| 32.2 | 32.1.3 Modes of Operation                                |     |

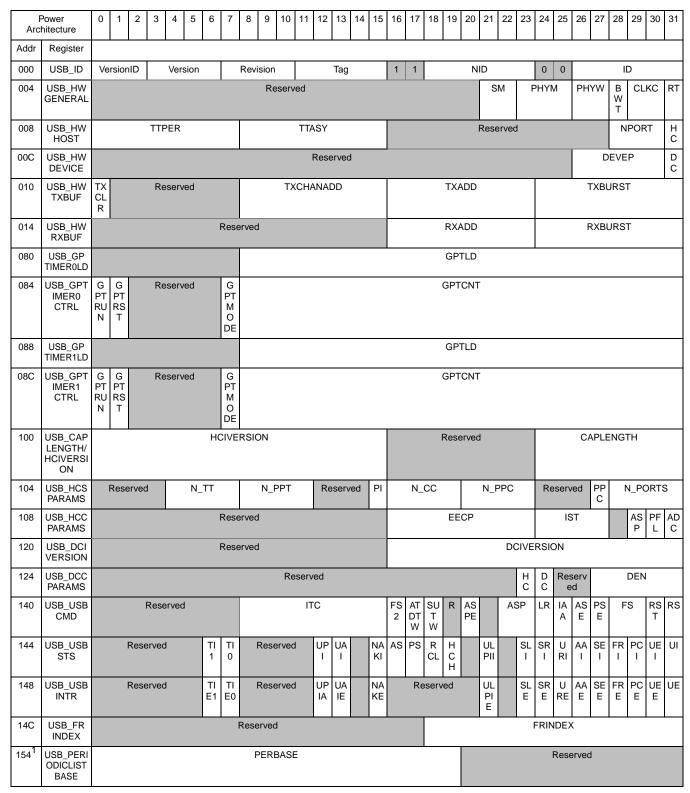

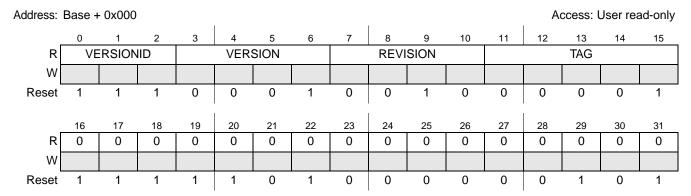

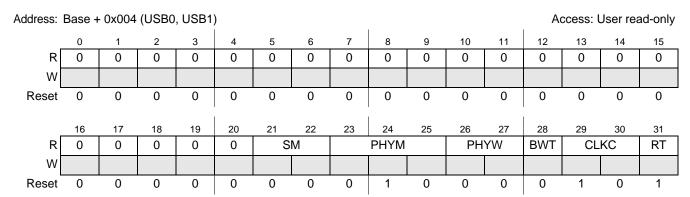

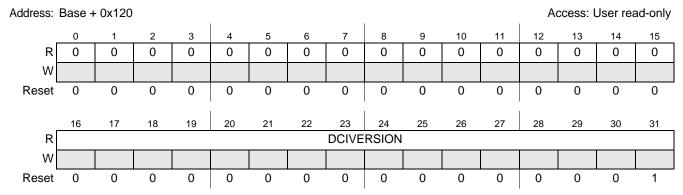

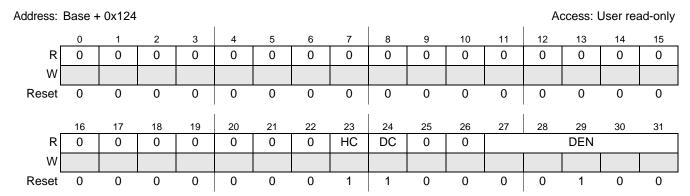

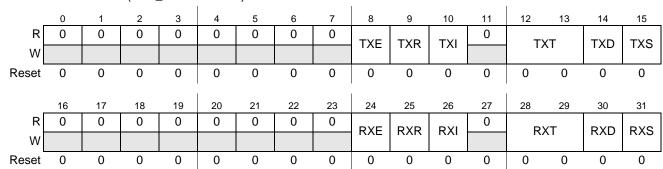

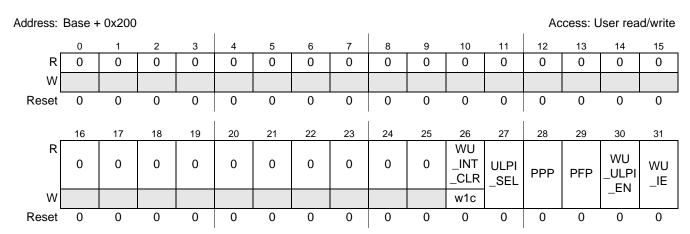

| 34.4 | 32.2.1 Module Identification Registers                   |     |

|      | 32.2.2 Capability Registers                              |     |

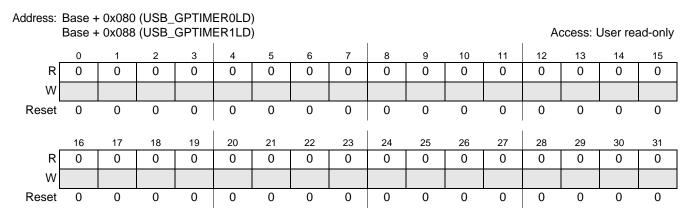

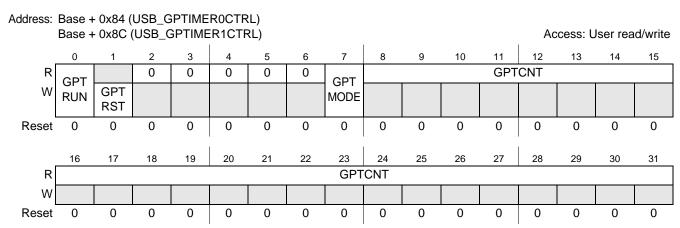

|      | 32.2.3 Device/Host Timer Registers (Non-EHCI)            |     |

|      | 32.2.3 Device/fiost Tiller Registers (Noil-EffCI)        | 620 |

|      |                                                          |     |

|      | 32.2.4 Operational Registers                                       | 828 |

|------|--------------------------------------------------------------------|-----|

| 32.3 | Functional Description                                             | 864 |

|      | 32.3.1 System Interface                                            |     |

|      | 32.3.2 DMA Engine                                                  | 865 |

|      | 32.3.3 FIFO RAM Controller                                         | 865 |

| 32.4 | OTG Operations                                                     | 865 |

|      | 32.4.1 Register Bits                                               | 865 |

|      | 32.4.2 Hardware Assist                                             | 866 |

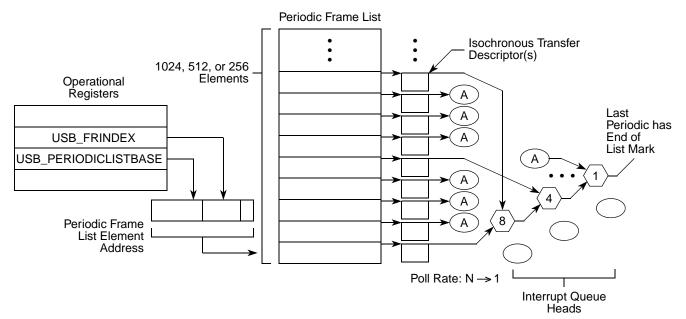

| 32.5 | Host Data Structures                                               | 868 |

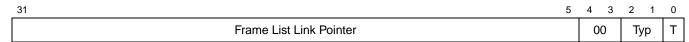

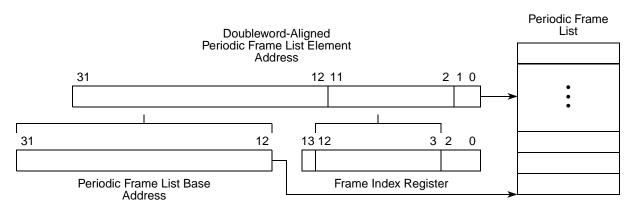

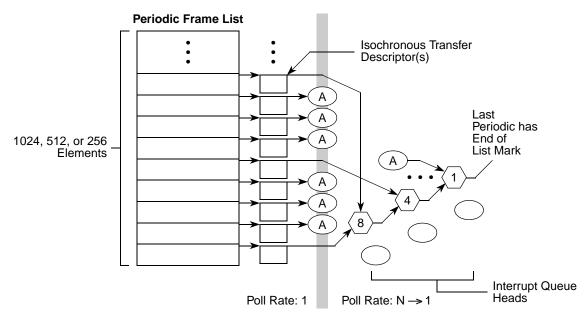

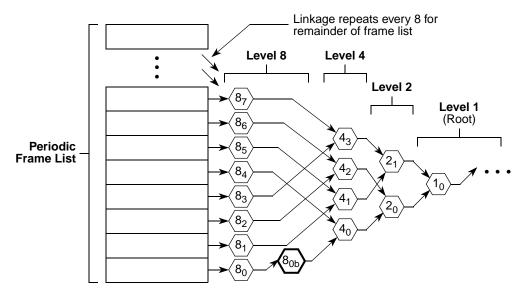

|      | 32.5.1 Periodic Frame List                                         | 868 |

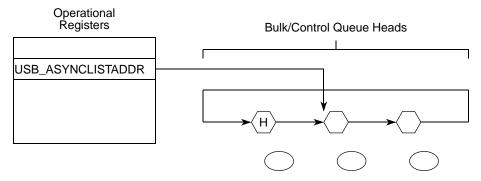

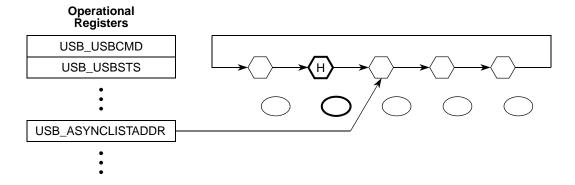

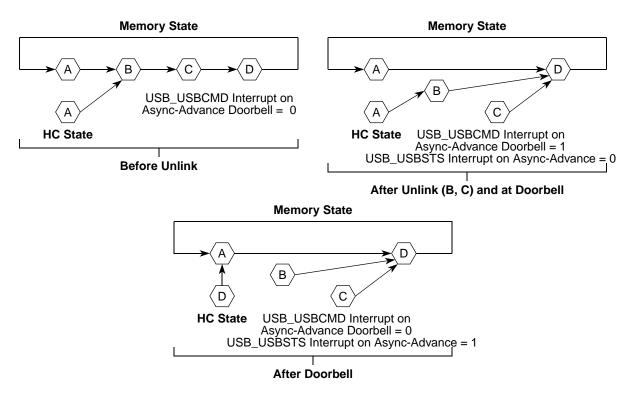

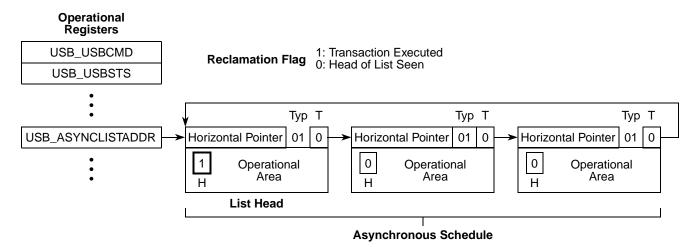

|      | 32.5.2 Asynchronous List Queue Head Pointer                        | 870 |

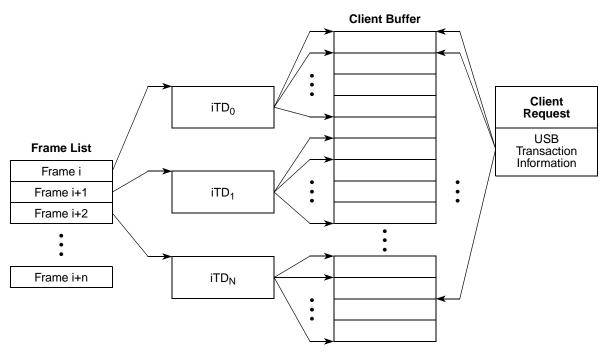

|      | 32.5.3 Isochronous (High-Speed) Transfer Descriptor (iTD)          | 870 |

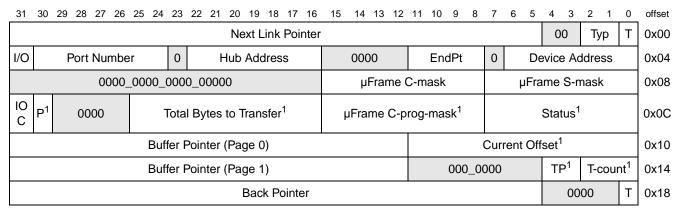

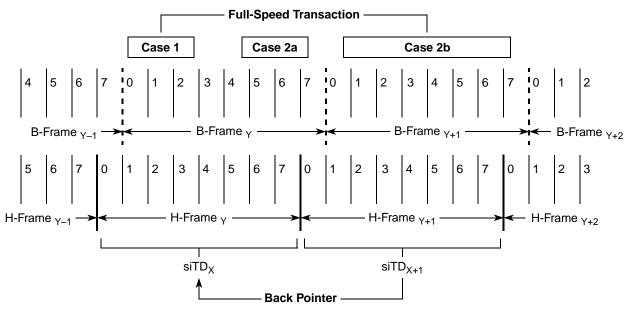

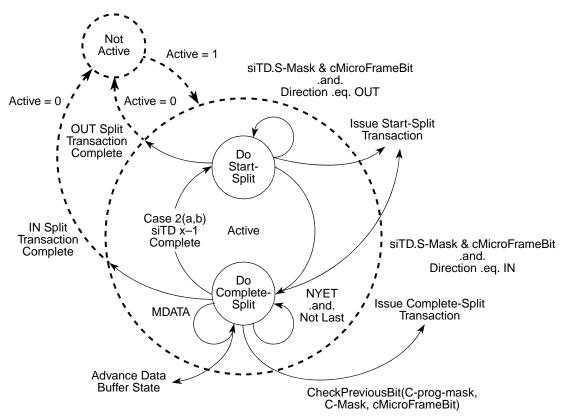

|      | 32.5.4 Split Transaction Isochronous Transfer Descriptor (siTD)    |     |

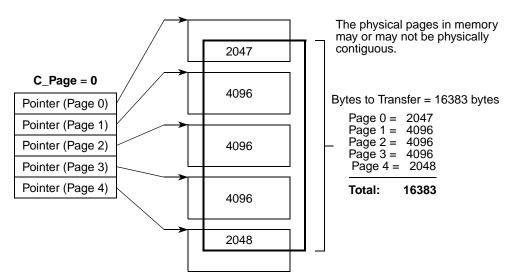

|      | 32.5.5 Queue Element Transfer Descriptor (qTD)                     |     |

|      | 32.5.6 Queue Head                                                  | 882 |

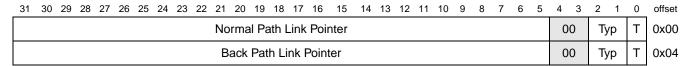

|      | 32.5.7 Periodic Frame Span Traversal Node (FSTN)                   | 887 |

| 32.6 | Host Operational Model                                             | 888 |

|      | 32.6.1 Host Controller Initialization                              | 889 |

|      | 32.6.2 Suspend/Resume                                              | 890 |

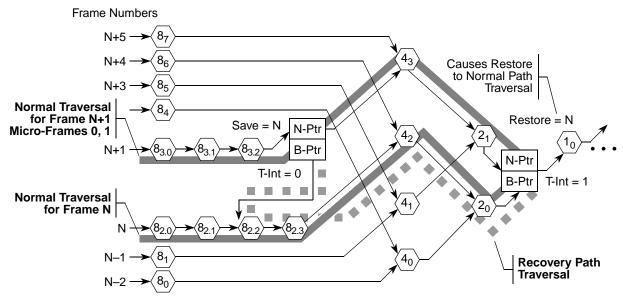

|      | 32.6.3 Schedule Traversal Rules                                    | 892 |

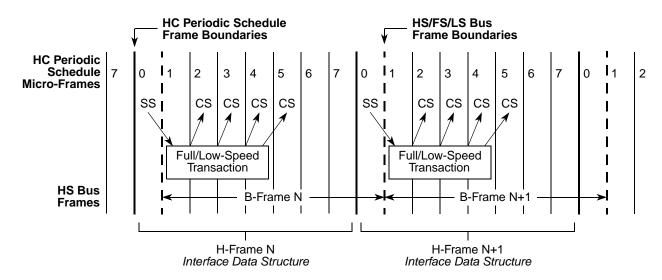

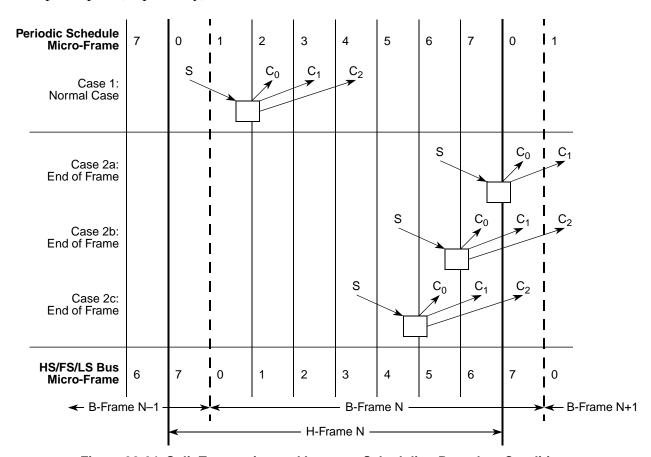

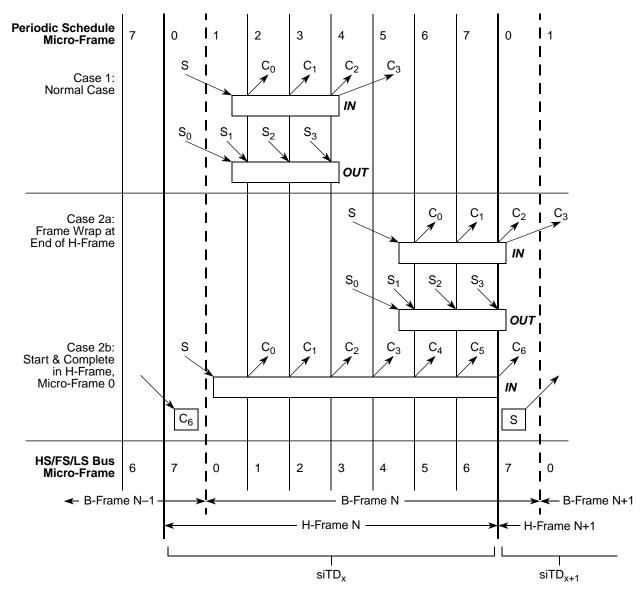

|      | 32.6.4 Periodic Schedule Frame Boundaries vs. Bus Frame Boundaries | 894 |

|      | 32.6.5 Periodic Schedule                                           | 896 |

|      | 32.6.6 Managing Isochronous Transfers Using iTDs                   | 897 |

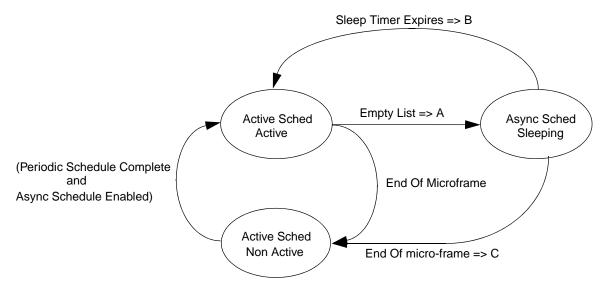

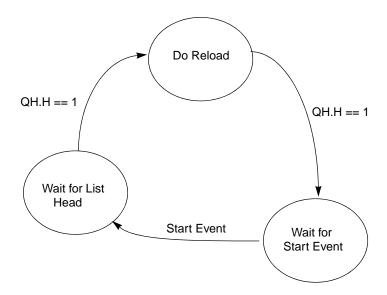

|      | 32.6.7 Asynchronous Schedule                                       | 901 |

|      | 32.6.8 Operational Model for NAK Counter                           | 909 |

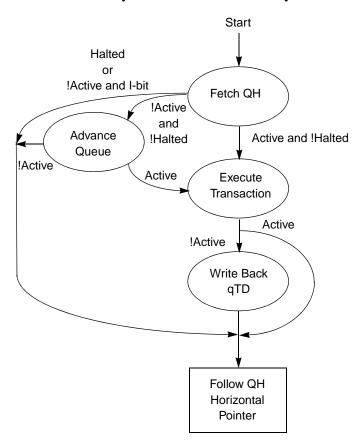

|      | 32.6.9 Managing Control/Bulk/Interrupt Transfers via Queue Heads   | 911 |

|      | 32.6.10Ping Control                                                | 922 |

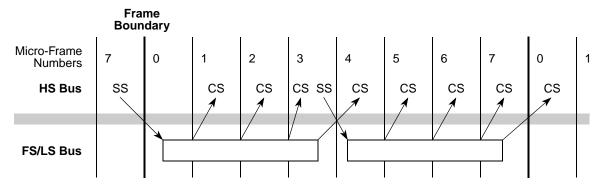

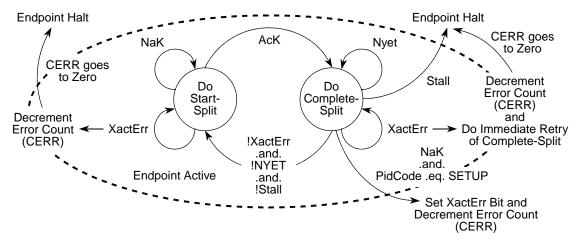

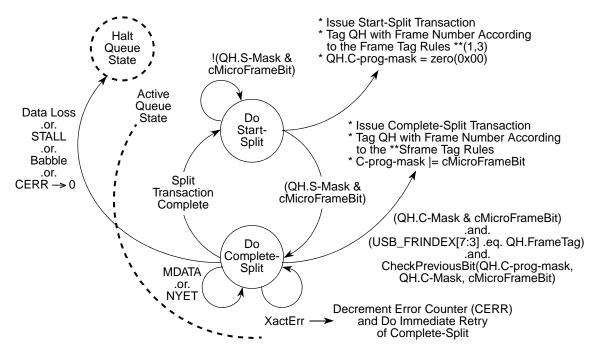

|      | 32.6.11Split Transactions                                          | 923 |

|      | 32.6.12Host Controller Pause                                       | 951 |

|      | 32.6.13Port Test Modes                                             | 952 |

|      | 32.6.14Interrupts                                                  | 952 |

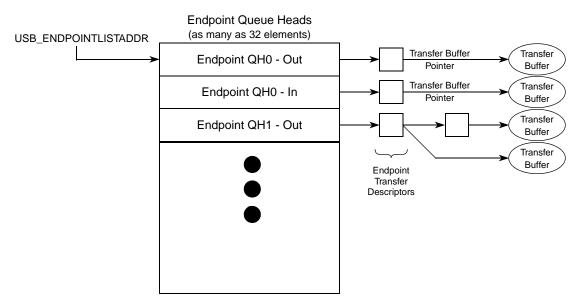

| 32.7 | Device Data Structures                                             |     |

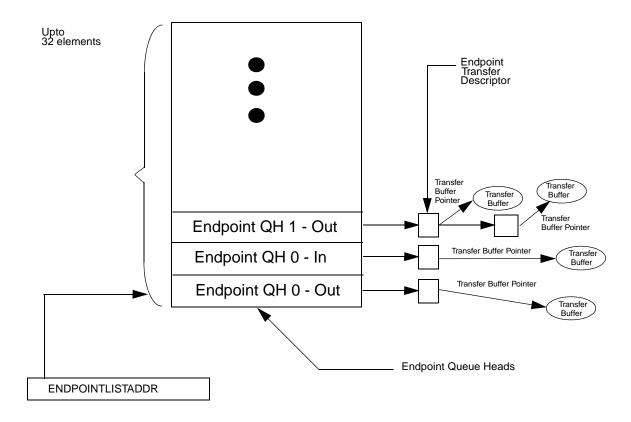

|      | 32.7.1 Endpoint Queue Head                                         | 957 |

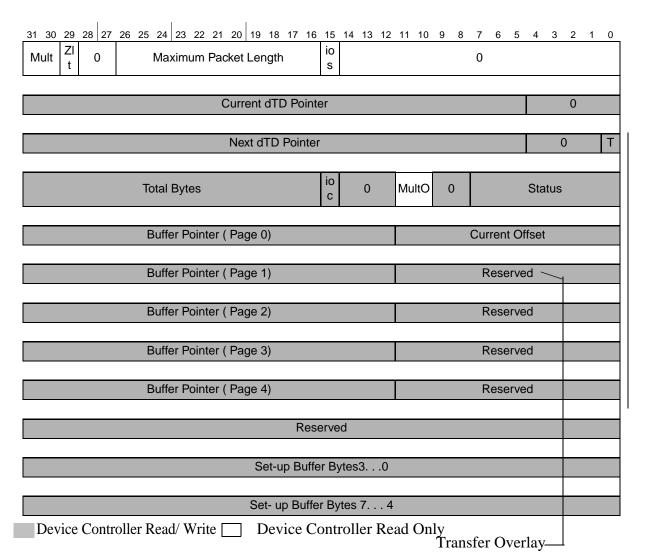

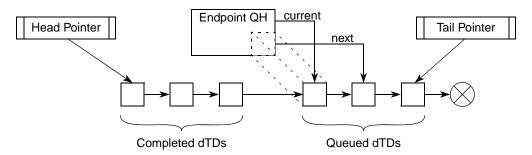

|      | 32.7.2 Endpoint Transfer Descriptor (dTD)                          | 960 |

| 32.8 | Device Operational Model                                           | 962 |

|      | 32.8.1 Device Controller Initialization                            | 962 |

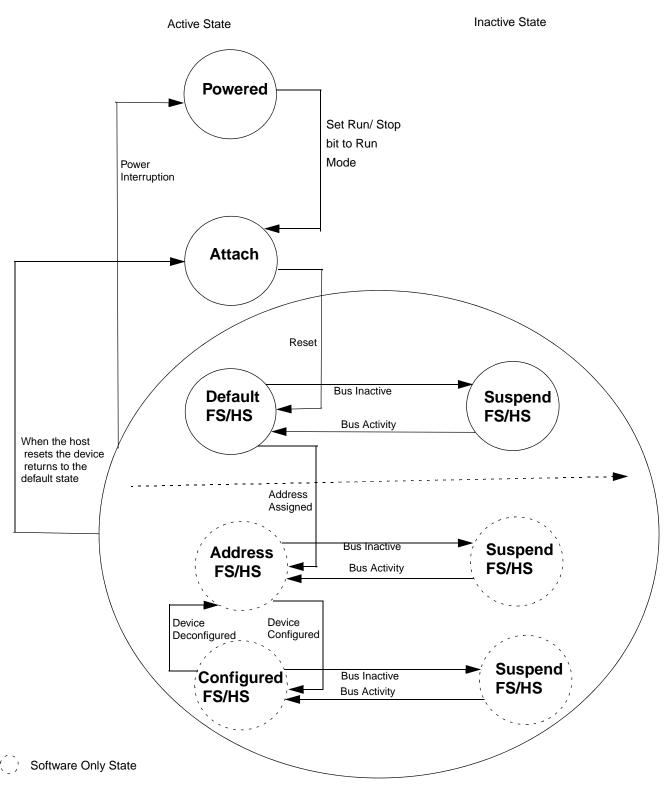

|      | 32.8.2 Port State and Control                                      | 963 |

|      | 32.8.3 Bus Reset                                                   |     |

|      | 32.8.4 Managing Endpoints                                          | 967 |

|      | 32.8.5 Device Operational Model For Packet Transfers               |     |

|      | 32.8.6 Managing Queue Heads                                        |     |

|      | 32.8.7 Managing Transfers with Transfer Descriptors                | 979 |

|      | 32.8.8 Device Error Matrix                                         | 981 |

|      | 32.8.9 Servicing Interrupts                                        |     |

|      | 32.8.10Deviations from the EHCI Specifications                     | 983 |

|      |                                                                    |     |

#### **About this book**

This reference manual describes the MPC5125 microcontroller family for software and hardware developers. Information regarding bus timing, signal behavior, and AC, DC, and thermal characteristics are detailed in the device data sheet (MPC5125 Data Sheet).

The information in this book is subject to change without notice, as described in the disclaimers on the title page. As with any technical documentation, the reader needs to make sure to use the most recent version of the documentation.

To locate any published errata or updates for this document, visit the Freescale web site at http://www.freescale.com/.

#### **Audience**

This manual is intended for system software and hardware developers and applications programmers who want to develop products with the MPC5125 microcontroller family. It is assumed that the reader understands operating systems, microprocessor system design, basic principles of software and hardware, and basic details of the Power architecture.

# **Organization**

Following is a summary and brief description of the major sections of this manual:

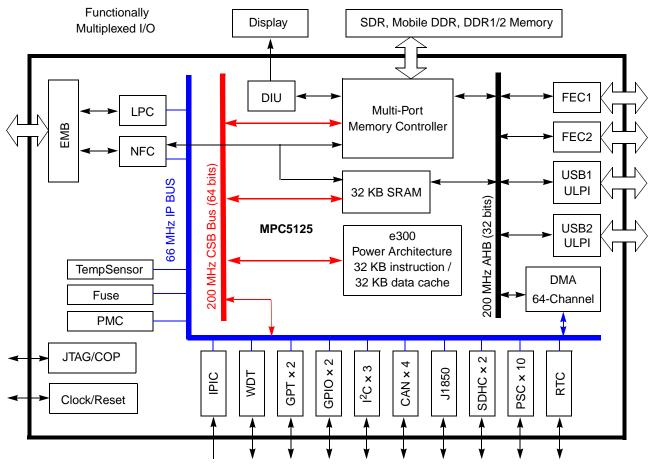

- Chapter 1, "Overview," includes general descriptions of the modules and features incorporated in the device while focusing on new features.

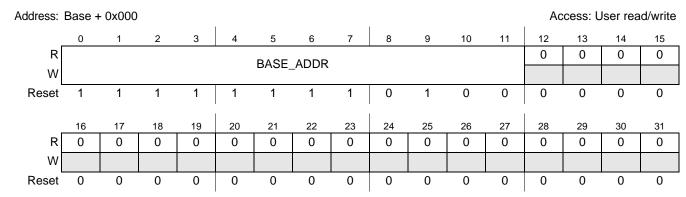

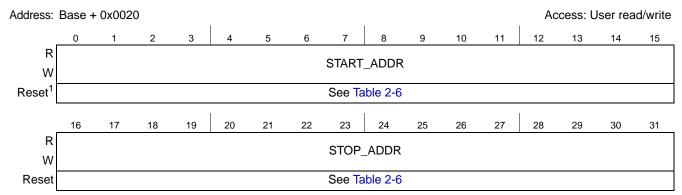

- Chapter 2, "System Configuration and Memory Map (XLBMEN + Mem Map)," describes the memory map and configuration for the MPC5125.

- Chapter 3, "Signal Descriptions," summarizes the external signal functions, their static electrical characteristics, and pad configuration settings for the MPC5125.

- Chapter 4, "Reset," describes the reset sources available on the MPC5125, including details on status flags and default configurations.

- Chapter 5, "Clocks and Low-Power Modes," describes the various clock sources that are available on the MPC5125 device.

- Chapter 6, "Byte Data Link Controller (BDLC)," describes the BDLC, which is a Society of Automotive Engineers (SAE) J1850-compatible serial network communication module.

- Chapter 7, "CPU e300 Core Power Architecture," describes the organization of the Power

processor core on the MPC5125, and gives an overview of the programming models as they are

implemented on the device.

- Chapter 8, "CSB Arbiter and Bus Monitor," describes the Coherent Systems Bus (CSB) arbiter and its configuration, control, and status registers.

- Chapter 9, "Direct Memory Access (DMA)," describes the DMA controller implemented on the MPC5125.

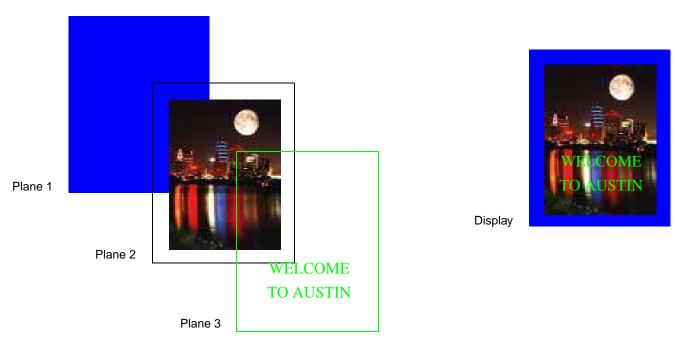

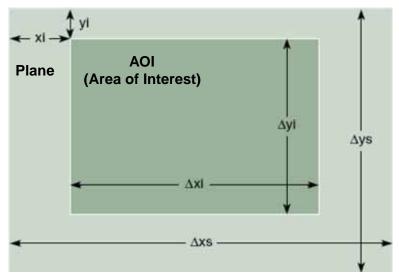

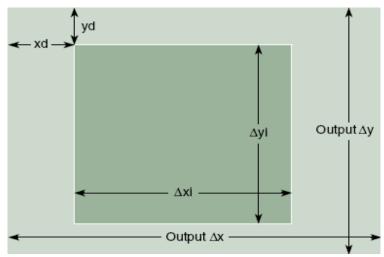

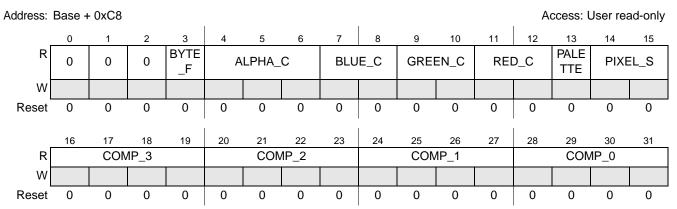

- Chapter 10, "Display Interface Unit (DIU)," describes the Display Interface Unit (DIU) implemented on the MPC5125.

- Chapter 11, "DRAM Controller," describes the multi-port DRAM controller that supports Mobile-DDR, DDR-1, DDR-2, and SDR memories.

- Chapter 12, "Multi-port DRAM Controller Priority Manager," describes the priority manager for the DRAM controller.

- Chapter 13, "External Memory Bus (EMB)," describes how the LPC and the NFC share the External Memory Bus.

- Chapter 14, "Fast Ethernet Controller (FEC)," describes the feature set, operation, and programming model of the FEC block.

- Chapter 15, "General Purpose Timers (GPT)," describes eight independent timer channels that perform general purpose timer and general purpose I/O (GPIO) functions.

- Chapter 16, "General Purpose I/O (GPIO)," describes the general purpose I/O module, including pin descriptions, register settings and interrupt capabilities.

- Chapter 17, "Integrated Programmable Interrupt Controller (IPIC)," summarizes the software and hardware interrupts for the MPC5125 device.

- Chapter 18, "IIM/Fusebox," describes the module that provides an interface for reading and programming information stored in on-chip fuse elements.

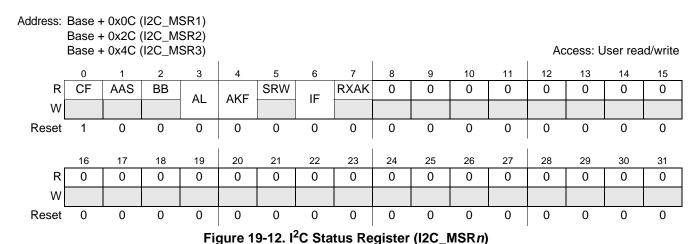

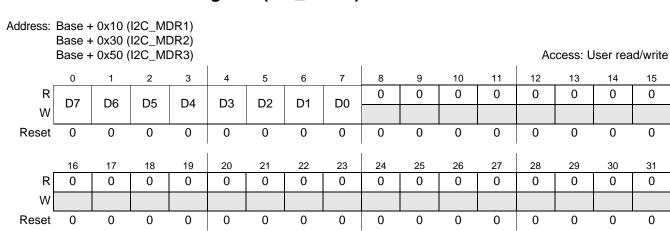

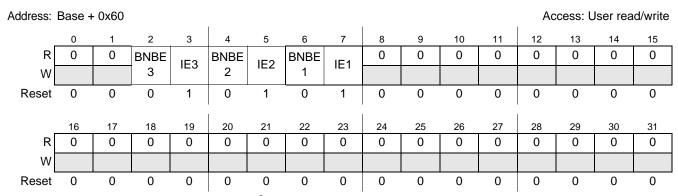

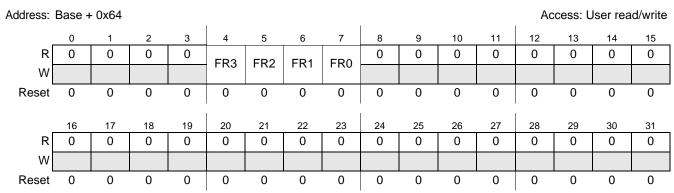

- Chapter 19, "Inter-Integrated Circuit (I2C)," describes the I<sup>2</sup>C module, including I<sup>2</sup>C protocol, clock synchronization, and I<sup>2</sup>C programming model registers.

- Chapter 20, "I/O Control," describes the controls for the functional muxing and configuration of the pads.

- Chapter 21, "LocalPlus Bus Controller (LPC)," describes the external bus interface of the MPC5125.

- Chapter 22, "MSCAN," describes the CAN module, a communication controller implementing the CAN protocol according to Bosch Specification version 2.0B.

- Chapter 23, "NAND Flash Controller (NFC)," describes the interface to standard NAND flash memory devices.

- Chapter 24, "Power Management Control Module (PMC)," describes the power blocks that provide voltage control for the internal logic of the device.

- Chapter 25, "Programmable Serial Controller (PSC)," describes the UART, AC97, Codec, and I<sup>2</sup>S modes.

- Chapter 26, "PSC Centralized FIFO Controller (FIFOC)," describes the centralized FIFO controller for the PSC modules.

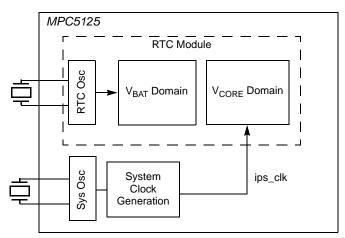

- Chapter 27, "Real Time Clock (RTC)," describes the real time clock.

- Chapter 28, "Secure Digital Host Controller (SDHC)," describes the module that interfaces to Multimedia Cards (MMC), Secure Digital (SD) memory cards, and I/O cards.

- Chapter 29, "Software Watchdog Timer (WDT)," describes the counter that guards against software errors by periodically issuing a reset unless interrupted by software.

- Chapter 30, "SRAM Memory (MEM)," describes the on-chip static RAM (SRAM) implementation.

- Chapter 31, "Temperature Sensor," describes the module that monitors the internal temperature of the MPC5125.

- Chapter 32, "Universal Serial Bus Interface with On-The-Go," describes the universal serial bus (USB) interface on the MPC5125.

- Appendix A, "Memory Map," provides a detailed listing of the memory-mapped registers for the MPC5125.

# Suggested reading

This section lists additional reading that provides background for the information in this manual as well as general information about PowerPC architecture.

#### **General information**

Useful information about the PowerPC architecture and computer architecture in general:

- Programming Environments Manual for 32-Bit Implementations of the PowerPC<sup>TM</sup> Architecture (MPCFPE32B)

- *Using Microprocessors and Microcomputers: The Motorola Family,* William C. Wray, Ross Bannatyne, Joseph D. Greenfield

- Computer Architecture: A Quantitative Approach, Second Edition, by John L. Hennessy and David A. Patterson.

- Computer Organization and Design: The Hardware/Software Interface, Second Edition, David A. Patterson and John L. Hennessy.

#### PowerPC documentation

PowerPC documentation is available from the sources listed on the back cover of this manual, as well as http://www.freescale.com/powerarchitecture.

- Reference manuals (formerly called user's manuals)—These books provide details about individual PowerPC implementations and are intended to be used in conjunction with the *PowerPC Programmers Reference Manual*.

- Addenda/errata to reference manuals—Because some processors have follow-on parts, an addendum is provided that describes the additional features and functionality changes. Also, if mistakes are found within a reference manual, an errata document will be issued before the next published release of the reference manual. These addenda/errata are intended for use with the corresponding reference manuals.

- Data sheets—Data sheets provide specific information regarding pin-out diagrams, bus timing, signal behavior, and AC, DC, and thermal characteristics, as well as other design considerations.

- Product briefs—Each device has a product brief that provides an overview of its features. This document is roughly equivalent to the overview (Chapter 1) of a device's reference manual.

• Application notes—These short documents address specific design issues useful to programmers and engineers working with Freescale Semiconductor processors.

Additional literature is published as new processors become available. For a current list of PowerPC documentation, refer to http://www.freescale.com/powerarchitecture.

#### Conventions

This document uses the following notational conventions:

cleared/set When a bit takes the value zero, it is said to be cleared; when it takes a value of

one, it is said to be set.

reserved When a bit or address is reserved, it should not be written. If read, its value is

cannot be not guaranteed. Reading or writing to reserved bits or addresses may

cause unexpected results.

MNEMONICS In text, instruction mnemonics are shown in uppercase.

mnemonics In code and tables, instruction mnemonics are shown in lowercase.

*italics* Italics indicate variable command parameters.

Book titles in text are set in italics.

ObO Prefix to denote binary number (e.g., 0b0110\_0111)

0x0 Prefix to denote hexadecimal number (e.g., 0xFFF0\_FFFC)

b Suffix to denote binary number (e.g., 0110\_0111b) d Suffix to denote decimal number (e.g., 12345d)

h Suffix to denote hexadecimal number (e.g., FFF0\_FFFCh)

REG[FIELD] Abbreviations for registers are shown in uppercase. Specific bits, fields, or ranges

appear in brackets. For example, RAMBAR[BA] identifies the base address field

in the RAM base address register.

nibble A 4-bit data unit

byte An 8-bit data unit

halfword A 16-bit data unit

word A 32-bit data unit

doubleword A 64-bit data unit

x In some contexts, such as signal encodings, x (without italics) indicates a "don't

care" condition.

*x* With italics, used to express an undefined alphanumeric value (e.g., a variable in

an equation); or a variable alphabetic character in a bit, register, or module name

(e.g., DSPI\_x could refer to DSPI\_A or DSPI\_B).

*n* Used to express an undefined numerical value; or a variable numeric character in

a bit, register, or module name (e.g., EIFn could refer to EIF1 or EIF0).

<sup>1.</sup> The only exceptions to this appear in the discussion of serial communication modules that support variable-length data transmission units. To simplify the discussion these units are referred to as words regardless of length.

NOT logical operator

AND logical operator

OR logical operator

Field concatenation operator

OVERBAR

An overbar indicates that a signal is active-low.

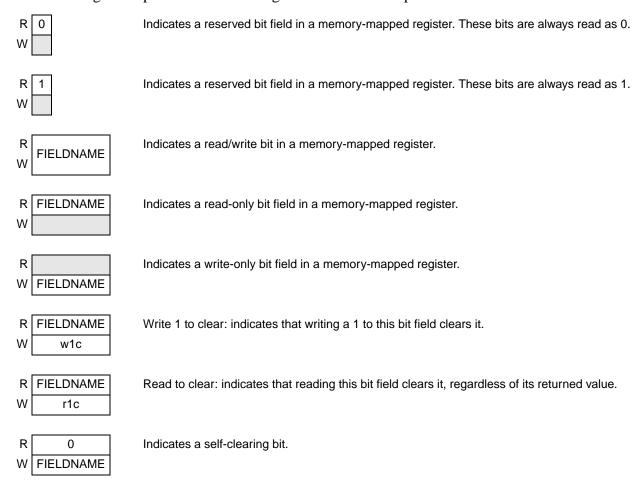

# **Register figure conventions**

This document uses the following conventions for the register reset values in register figures:

— Bit value is undefined at reset.

U Bit value is unchanged by reset. Previous value preserved during reset.

[signal\_name] Reset value is determined by the polarity of the indicated signal.

The following descriptions are used in register bit field description tables:

# **Acronyms and Abbreviations**

Table i lists some acronyms and abbreviations used in this document.

**Table i. Acronyms and Abbreviated Terms**

| Term                    | Meaning                                                |  |  |

|-------------------------|--------------------------------------------------------|--|--|

| ADC                     | Analog-to-digital converter                            |  |  |

| ALU                     | Arithmetic logic unit                                  |  |  |

| BDM                     | Background debug mode                                  |  |  |

| BIST Built-in self test |                                                        |  |  |

| BSDL                    | Boundary-scan description language                     |  |  |

| CODEC Code/decode       |                                                        |  |  |

| DAC                     | Digital-to-analog conversion                           |  |  |

| DMA                     | Direct memory access                                   |  |  |

| DSP                     | Digital signal processing                              |  |  |

| EA                      | Effective address                                      |  |  |

| FIFO                    | First-in, first-out                                    |  |  |

| GPIO                    | General-purpose I/O                                    |  |  |

| I <sup>2</sup> C        | Inter-integrated circuit                               |  |  |

| IEEE                    | Institute for Electrical and Electronics Engineers     |  |  |

| IFP                     | Instruction fetch pipeline                             |  |  |

| IPL                     | Interrupt priority level                               |  |  |

| JEDEC                   | Joint Electron Device Engineering Council              |  |  |

| JTAG                    | Joint Test Action Group                                |  |  |

| LIFO                    | Last-in, first-out                                     |  |  |

| LRU                     | Least recently used                                    |  |  |

| LSB                     | Least-significant byte                                 |  |  |

| LVI                     | Low-voltage interrupt                                  |  |  |

| Isb                     | Least-significant bit                                  |  |  |

| MAC                     | Multiply accumulate unit, also Media access controller |  |  |

| MSB                     | Most-significant byte                                  |  |  |

| msb                     | Most-significant bit                                   |  |  |

| Mux Multiplex           |                                                        |  |  |

| NOP                     | No operation                                           |  |  |

| OEP                     | Operand execution pipeline                             |  |  |

| PC                      | Program counter                                        |  |  |

## Table i. Acronyms and Abbreviated Terms (continued)

| Term                            | Meaning                                                 |  |  |

|---------------------------------|---------------------------------------------------------|--|--|

| PLIC                            | Physical layer interface controller                     |  |  |

| PLL                             | Phase-locked loop                                       |  |  |

| POR                             | Power-on reset                                          |  |  |

| RISC                            | Reduced instruction set computing                       |  |  |

| Rx                              | Rx Receive                                              |  |  |

| SOF Start of frame              |                                                         |  |  |

| TAP Test access port            |                                                         |  |  |

| TTL Transistor transistor logic |                                                         |  |  |

| Tx                              | Transmit                                                |  |  |

| UART                            | Universal asynchronous/synchronous receiver transmitter |  |  |

| USB                             | Universal serial bus                                    |  |  |

# **Terminology Conventions**

Table ii shows terminology conventions used throughout this document.

**Table ii. Notational Conventions**

| Instruction                                                   | Operand Syntax                                                                        |  |  |  |  |  |

|---------------------------------------------------------------|---------------------------------------------------------------------------------------|--|--|--|--|--|

| Opcode Wildcard                                               |                                                                                       |  |  |  |  |  |

| cc Logical condition (example: NE for not equal)              |                                                                                       |  |  |  |  |  |

|                                                               | Register Specifications                                                               |  |  |  |  |  |

| An Any address register n (example: A3 is address register 3) |                                                                                       |  |  |  |  |  |

| Ay,Ax                                                         | Source and destination address registers, respectively                                |  |  |  |  |  |

| Dn                                                            | Any data register n (example: D5 is data register 5)                                  |  |  |  |  |  |

| Dy,Dx                                                         | Source and destination data registers, respectively                                   |  |  |  |  |  |

| Rc                                                            | Any control register (example VBR is the vector base register)                        |  |  |  |  |  |

| Rm                                                            | MAC registers (ACC, MAC, MASK)                                                        |  |  |  |  |  |

| Rn                                                            | Any address or data register                                                          |  |  |  |  |  |

| Rw                                                            | Destination register w (used for MAC instructions only)                               |  |  |  |  |  |

| Ry,Rx                                                         | Any source and destination registers, respectively                                    |  |  |  |  |  |

| Xi                                                            | Index register i (can be an address or data register: Ai, Di)                         |  |  |  |  |  |

|                                                               | Miscellaneous Operands                                                                |  |  |  |  |  |

| # <data></data>                                               | Immediate data following the 16-bit operation word of the instruction                 |  |  |  |  |  |

| <ea></ea>                                                     | Effective address                                                                     |  |  |  |  |  |

| <ea>y,<ea>x</ea></ea>                                         | Source and destination effective addresses, respectively                              |  |  |  |  |  |

| <label></label>                                               | Assembly language program label                                                       |  |  |  |  |  |

| <li><li><li><li></li></li></li></li>                          | List of registers for MOVEM instruction (example: D3–D0)                              |  |  |  |  |  |

| <shift></shift>                                               | Shift operation: shift left (<<), shift right (>>)                                    |  |  |  |  |  |

| <size></size>                                                 | Operand data size: byte (B), word (W), longword (L)                                   |  |  |  |  |  |

| bc                                                            | Instruction and data caches                                                           |  |  |  |  |  |

| dc                                                            | Data cache                                                                            |  |  |  |  |  |

| ic                                                            | Instruction cache                                                                     |  |  |  |  |  |

| # <vector></vector>                                           | Identifies the 4-bit vector number for trap instructions                              |  |  |  |  |  |

| <>                                                            | identifies an indirect data address referencing memory                                |  |  |  |  |  |

| <xxx></xxx>                                                   | identifies an absolute address referencing memory                                     |  |  |  |  |  |

| d <i>n</i>                                                    | Signal displacement value, <i>n</i> bits wide (example: d16 is a 16-bit displacement) |  |  |  |  |  |

| SF                                                            | Scale factor (x1, x2, x4 for indexed addressing mode, <<1n>> for MAC operations)      |  |  |  |  |  |

# Table ii. Notational Conventions (continued)

| Instruction                                                                                      | Operand Syntax                                                                                                                                                                                                                                                                                                                  |  |  |  |

|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Operations                                                                                       |                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| +                                                                                                | Arithmetic addition or postincrement indicator                                                                                                                                                                                                                                                                                  |  |  |  |

| -                                                                                                | Arithmetic subtraction or predecrement indicator                                                                                                                                                                                                                                                                                |  |  |  |

| х                                                                                                | Arithmetic multiplication                                                                                                                                                                                                                                                                                                       |  |  |  |

| /                                                                                                | Arithmetic division                                                                                                                                                                                                                                                                                                             |  |  |  |

| ~                                                                                                | Invert; operand is logically complemented                                                                                                                                                                                                                                                                                       |  |  |  |

| &                                                                                                | Logical AND                                                                                                                                                                                                                                                                                                                     |  |  |  |

| I                                                                                                | Logical OR                                                                                                                                                                                                                                                                                                                      |  |  |  |

| ^                                                                                                | Logical exclusive OR                                                                                                                                                                                                                                                                                                            |  |  |  |

| <<                                                                                               | Shift left (example: D0 << 3 is shift D0 left 3 bits)                                                                                                                                                                                                                                                                           |  |  |  |

| >>                                                                                               | Shift right (example: D0 >> 3 is shift D0 right 3 bits)                                                                                                                                                                                                                                                                         |  |  |  |

| $\rightarrow$                                                                                    | Source operand is moved to destination operand                                                                                                                                                                                                                                                                                  |  |  |  |

| $\longleftrightarrow$                                                                            | Two operands are exchanged                                                                                                                                                                                                                                                                                                      |  |  |  |

| sign-extended                                                                                    | All bits of the upper portion are made equal to the high-order bit of the lower portion                                                                                                                                                                                                                                         |  |  |  |

| If <condition><br/>then <operations><br/>else <operations></operations></operations></condition> | Test the condition. If true, the operations after then are performed. If the condition is false and the optional else clause is present, the operations after else are performed. If the condition is false and else is omitted, the instruction performs no operation. Refer to the Bcc instruction description as an example. |  |  |  |

|                                                                                                  | Subfields and Qualifiers                                                                                                                                                                                                                                                                                                        |  |  |  |

| {}                                                                                               | Optional operation                                                                                                                                                                                                                                                                                                              |  |  |  |

| ()                                                                                               | Identifies an indirect address                                                                                                                                                                                                                                                                                                  |  |  |  |

| d <sub>n</sub>                                                                                   | Displacement value, n-bits wide (example: d <sub>16</sub> is a 16-bit displacement)                                                                                                                                                                                                                                             |  |  |  |

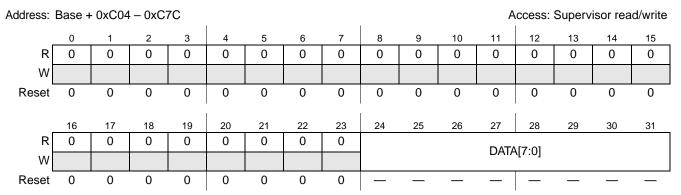

| Address                                                                                          | Calculated effective address (pointer)                                                                                                                                                                                                                                                                                          |  |  |  |