MSC8122RMAD Rev. 10, 12/2007

# **MSC8122**

### Reference Manual Addendum

This document provides updates to revision 3 of the *MSC8122 Reference Manual (MSC8122RM)*. The changes are organized by the chapters that are affected.

#### Contents

| 1  | About This Book                       | 2  |

|----|---------------------------------------|----|

| 2  | MSC8122 Overview                      | 2  |

| 3  | External Signals                      | 3  |

| 4  | Reset                                 | 3  |

| 5  | Clocks                                | 4  |

| 6  | Memory Map                            | 4  |

| 7  | Extended Core                         |    |

| 8  | System Bus                            | 5  |

| 9  | Direct Slave Interface (DSI)          | 5  |

| 10 | Direct Memory Access (DMA) Controller | 6  |

| 11 | Interrupt Processing                  | 8  |

| 12 | Debugging                             | 8  |

| 13 | Internal Peripheral Bus (IPBus)       | 9  |

| 14 | TDM Interface                         | 9  |

| 15 | UART                                  | 11 |

| 16 | Timers                                | 11 |

| 17 | Ethernet Controller                   | 12 |

| 18 | Programming Reference                 | 12 |

|    |                                       |    |

It This Book

## 1 About This Book

<sup>C</sup> In the *Other MSC8122 Documentation* section on page xxvii, delete the first bullet.

## 2 MSC8122 Overview

<sup>CP</sup> Replace the 3-Mode Signal Multiplexing row in **Table 1-3** on page 1-3 with the following:

| 3-Mode Signal Multiplexing | 64-bit DSI and 32-bit system bus. |

|----------------------------|-----------------------------------|

|                            | 32-bit DSI and 64-bit system bus. |

|                            | 32-bit DSI and 32-bit system bus. |

**\*** Replace the Time-Division Multiplexing (TDM) row in **Table 1-5** on page 1-4 with the following:

| Time-Division Multiplexing (TDM) | Lip to four independent TDM modules, each with the following features:                                                                                            |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                  | <ul><li>Up to four independent TDM modules, each with the following features:</li><li>Optional operating configurations:</li></ul>                                |

|                                  | <ul> <li>Optional operating configurations.</li> <li>Totally independent receive and transmit channels, each having one data line, one clock line,</li> </ul>     |

|                                  | and one frame sync line                                                                                                                                           |

|                                  | <ul> <li>Four data lines with one clock and one frame sync shared among the transmit and receive<br/>lines.</li> </ul>                                            |

|                                  | <ul> <li>—Glueless interface to E1/T1 framers and switches as well as to common buses such as ST-<br/>BUS.</li> </ul>                                             |

|                                  | <ul> <li>Hardware A-law/μ-law conversion</li> </ul>                                                                                                               |

|                                  | • Up to 62.5 Mbps per TDM (62.5 MHz bit clock if one data line is used, 31.25 MHz if two data lines are used, 15.625 MHz if four data lines are used).            |

|                                  | Up to 256 channels.                                                                                                                                               |

|                                  | <ul> <li>Up to 16 MB per channel buffer (granularity 8 bytes), where A/μ law buffer size is double<br/>(granularity 16 byte).</li> </ul>                          |

|                                  | <ul> <li>Receive buffers share one global write offset pointer that is written to the same offset relative to<br/>their start address.</li> </ul>                 |

|                                  | <ul> <li>Transmit buffers share one global read offset pointer that is read from the same offset relative to<br/>their start address.</li> </ul>                  |

|                                  | All channels share the same word size.                                                                                                                            |

|                                  | • Two programmable receive and two programmable transmit threshold levels with interrupt generation that can be used, for example, to implement double buffering. |

|                                  | <ul> <li>Each channel can be programmed to be active or inactive.</li> </ul>                                                                                      |

|                                  | <ul> <li>2-, 4-, 8-, or 16-bit channels are stored in the internal memory as 2-, 4-, 8-, or 16-bit channels, respectively.</li> </ul>                             |

|                                  | <ul> <li>The TDM Transmitter Sync Signal (TxTSYN) can be configured as either input or output.</li> </ul>                                                         |

|                                  | <ul> <li>Frame Sync and Data signals can be programmed to be sampled either on the rising edge or on</li> </ul>                                                   |

|                                  | the falling edge of the clock.                                                                                                                                    |

|                                  | <ul> <li>Frame sync can be programmed as active low or active high.</li> </ul>                                                                                    |

|                                  | • Selectable delay (0–3 bits) between the Frame Sync signal and the beginning of the frame.                                                                       |

|                                  | MSB or LSB first support.                                                                                                                                         |

The Table 1-5 on page 1-6, replace the 15th bullet in the Ethernet Controller row with the following:

| Ethernet Controller | • Ethernet PHY can be exposed either on GPIO pins or on the high ms bits of the DSI/system bus |

|---------------------|------------------------------------------------------------------------------------------------|

|                     | when the DSI and system bus are both 32 bits wide.                                             |

<sup>C</sup> In Section 1.2.8 on page 1-21, change the second sentence in the first paragraph to the following:

It can also connect to multiple framers and switches as well as to common buses such as the ST-BUS.

### 3 External Signals

<sup>C</sup> Replace the GPIO29 row in **Table 3-7** on page 3-26 with the following:

| GPIO29   | Input/ Output | <b>General-Purpose Input Output 29</b><br>One of 32 GPIO signals used as GPIO or as one of two dedicated inputs or one of two dedicated outputs.<br>For details, refer to the <i>MSC8122 Reference Manual</i> GPIO programming model. |

|----------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHIP_ID3 | Input         | <b>Chip ID 3</b><br>Determines the chip ID of the MSC8122 DSI. It is sampled on the rising edge of PORESET signal.                                                                                                                    |

| ETHTX_EN | Output        | Ethernet Transmit Enable<br>Used to enable the Ethernet transmit controller for MII and RMII modes.                                                                                                                                   |

**Replace the TRST** row in **Table 3-9** on page 3-27 with the following:

| TRST | Input | Test Reset                                                                        |

|------|-------|-----------------------------------------------------------------------------------|

|      |       | Asynchronously initializes the test controller; must be asserted during power up. |

### 4 Reset

Change the next to last line in **Table 5-2** on page 5-2 to the following:

| SC140 Extended Cores Reset           | Yes | Yes | Yes | Yes |

|--------------------------------------|-----|-----|-----|-----|

| (PC points to boot starting address) |     |     |     |     |

Add the following note after the first paragraph in **Section 5.2** on page 5-4:

**Note:** Do not use the default HRCW which clears the HRCW[DLLDIS] bit. Because the MSC8113 does not support DLL operation, make sure that the HRCW[DLLDIS] bit is always set after reset.

**Replace the 01 row in Table 5-5 on page 5-4 with the following:**

| 01 | Reset configuration write through the 60x-compatible system bus.<br>MSC8122 is a configuration slave. If the HRCW is not written during 1024 CLKIN cycles, it<br>gets a default value of all zeros.<br><b>Note:</b> Always ensure that a valid configuration is written to the HRCW through the system<br>bus. The default configuration is not wolid |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | bus. The default configuration is not valid.                                                                                                                                                                                                                                                                                                          |

<sup>CP</sup> Delete **Section 5.5.1** and renumber the succeeding subsections.

**Replace the DLLDIS** row in **Table 5-8** with the following:

| DLLDIS<br>27 | 0 | <b>DLL Disable</b><br>Defines whether the DLL mechanism is disabled.<br>See <b>Section 7.3</b> , <i>Clock Configuration</i> . | 0<br>1 | No DLL bypass.<br>DLL bypass. |

|--------------|---|-------------------------------------------------------------------------------------------------------------------------------|--------|-------------------------------|

|              |   | Note: The MSC8122 does not support DLL operation. Always write a 1 to this bit to configure the device correctly.             |        |                               |

## 5 Clocks

ks

- Change the third bullet in **Section 7.2.1** on page 7-3 to the following:

- CLKIN mode. This is the recommended clock scheme for high-frequency synchronous memory interface (SDRAM).

## 6 Memory Map

The Table 8-2 on page 8-8, replace the rows for memory locations 00EFFE40 to 00EFFEDF with the following:

| 00EFFE40          | EDCA0_CTRL  | EDCA0 Control Register  | 2 |  |

|-------------------|-------------|-------------------------|---|--|

| 00EFFE44          | EDCA1_CTRL  | EDCA1 Control Register  | 2 |  |

| 00EFFE48          | EDCA2_CTRL  | EDCA2 Control Register  | 2 |  |

| 00EFFE4C          | EDCA3_CTRL  | EDCA3 Control Register  | 2 |  |

| 00EFFE50          | EDCA4_CTRL  | EDCA4 Control Register  | 2 |  |

| 00EFFE54          | EDCA5_CTRL  | EDCA5 Control Register  | 2 |  |

| 00EFFE58-00EFFE5F |             | Reserved                |   |  |

| 00EFFE60          | EDCA0_REFA  | EDCA0 reference value A | 4 |  |

| 00EFFE64          | EDCA1_REFA  | EDCA1 reference value A | 4 |  |

| 00EFFE68          | EDCA2_REFA  | EDCA2 reference value A | 4 |  |

| 00EFFE6C          | EDCA3_REFA  | EDCA3 reference value A | 4 |  |

| 00EFFE70          | EDCA4_REFA  | EDCA4 reference value A | 4 |  |

| 00EFFE74          | EDCA51_REFA | EDCA5 reference value A | 4 |  |

| 00EFFE78-00EFFE7F | Reserved    |                         |   |  |

| 00EFFE80          | EDCA0_REFB  | EDCA0 reference value B | 4 |  |

| 00EFFE84          | EDCA1_REFB  | EDCA1 reference value B | 4 |  |

| 00EFFE88          | EDCA2_REFB  | EDCA2 reference value B | 4 |  |

| 00EFFE8C          | EDCA3_REFB  | EDCA3 reference value B | 4 |  |

| 00EFFE90          | EDCA4_REFB  | EDCA4 reference value B | 4 |  |

| 00EFFE94          | EDCA5_REFB  | EDCA5 reference value B | 4 |  |

| 00EFFE98-00EFFEBF |             | Reserved                |   |  |

| 00EFFEC0          | EDCA0_MASK  | EDCA0 Mask Register     | 4 |  |

| 00EFFEC4          | EDCA1_MASK  | EDCA1 Mask Register     | 4 |  |

| 00EFFEC8          | EDCA2_MASK  | EDCA2 Mask Register     | 4 |  |

| 00EFFECC          | EDCA3_MASK  | EDCA3 Mask Register     | 4 |  |

| 00EFFED0          | EDCA4_MASK  | EDCA4 Mask Register     | 4 |  |

| 00EFFED4          | EDCA5_MASK  | EDCA5 Mask Register     | 4 |  |

| 00EFFED8-00EFFEDF |             | Reserved                |   |  |

|                   |             |                         |   |  |

## 7 Extended Core

<sup>C</sup> In **Table 9-10** on page 9-21, replace the **PFOFF** row with the following:

| PFOFF | 0 | Prefetch                        | 0 | Prefetch mode enabled (default after boot). |

|-------|---|---------------------------------|---|---------------------------------------------|

| 11    |   | Enables/disables Prefetch mode. | 1 | Prefetch mode disabled (value after reset). |

### 8 System Bus

<sup>CP</sup> Replace **Table 13-11** on page 13-22 with the following:

| TC[0-2] | System Bus          | Local Bus               |

|---------|---------------------|-------------------------|

| 000     | Reserved            | System-Local bus bridge |

| 001     | DSI                 | DSI                     |

| 010     | Reserved            | TDM                     |

| 011     | Ethernet Controller | Ethernet Controller     |

| 100     | Reserved            | Reserved                |

| 101     | SC140 cores         | Reserved                |

| 110     | DMA                 | DMA                     |

| 111     | DMA                 | DMA                     |

Table 13-11. Transfer Code Encoding

## 9 Direct Slave Interface (DSI)

<sup>CP</sup> On page 14-2, change the second note to the following two notes:

- Note: For the description of the DSI external signals, see Chapter 3, External Signals.

- **Note:** In systems that include a host device that connects to the MSC8122 through the DSI and the MSC8122 connects to other MSC8122 or MSC8126 devices through the system bus, all devices on the system bus must allow 64-bit read access for reads initiated by the host device. This is because any read access by the host through the DSI is translated by the MSC8122 DSI block as a 64-bit read access.

<sup>C</sup> In **Table 14-7** on page 14-30, replace the HTAAD row with the following:

| end of the access. HTAAD is valid only for asynchronous<br>accesses. See <b>Section 14.3.3</b> for details.<br><b>Note:</b> The reset value is 0—the device does not drive<br>HTA high after a host access. If the system uses<br>a pull-up resistor, you must set the HT <u>AAD</u> bit.<br>Until HTAAD is set, the rising slope of HTA at<br>the end of the access depends on the strength<br>of the pull-up resistor; this results in a long delay<br>for access termination. |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

t Memory Access (DMA) Controller

## 10 Direct Memory Access (DMA) Controller

- <sup>CP</sup> Remove the note at the bottom of page 16-1. Refer to the MCS8122 Chip Errata for details.

- <sup>C</sup> Add the following note to the end of **Section 16.2.2**:

- **Note:** DMA channels are coupled in pairs (0 and 1, 2 and 3, up to 14 and 15). Do not use two coupled channels simultaneously for flyby or single access transactions.

- The Section 16.2.4, delete the last sentence on page 16-20.

The Section 16.2.4 on page 16-20, add the following Example 16-4 after Example 16-3:

#### Example 16-4. Missing DMA Interrupt in Chained Buffer

- **Scenario:** The DMA controller is activated with a chained buffer. Every buffer should generate an interrupt when it is done. The interrupt service routine (ISR) performed by the core clears the relevant status bit in the DSTR. If an additional buffer completes before the core clears the DSTR bit, the core does not receive the appropriate interrupt because it is a level interrupt.

- **Solution:** Make sure that the ISR clears the DSTR bit as soon as possible. You can read the DCHCR after the interrupt is processed to determine whether another buffer was completed or if the DMA channel is still active.

- <sup>C</sup> Replace **Table 16-4** on page 16-25 with the following:

#### **Table 16-4.** DCPRAM Values for a Chained Buffer and a Simple Buffer

| BD | DCPRAM Pa | rameters | Value  | Description                                                                          |

|----|-----------|----------|--------|--------------------------------------------------------------------------------------|

| 0  | BD_ADDR   |          | 0x1000 | External memory buffer current address                                               |

|    | BD_ATTR   | INTRPT   | 0x0    | Do not generate an interrupt when buffer ends                                        |

|    |           | CONT     | 0x1    | Continuous mode. Do not shut down the channel when size reaches zero                 |

|    |           | NO_INC   | 0x0    | Increment address after request is serviced                                          |

|    |           | NBD      | 0x1    | When size reaches zero, next request calls buffer1                                   |

|    |           | TSZ      | 0x4    | Maximum transfer size is one burst                                                   |

|    |           | RD       | 0x1    | Read buffer                                                                          |

|    | BD_BSIZE  |          | 0x20   | Buffer base size of cyclic buffer                                                    |

| 1  | BD_ADDR   |          | 0x2000 | External memory buffer current address                                               |

|    | BD_ATTR   | INTRPT   | 0x0    | Do not generate interrupt when the buffer ends. The channel generates the interrupt. |

|    |           | CONT     | 0      | Non-continuous mode. The channel is closed when the size reaches zero                |

|    |           | NO_INC   | 0x0    | Increment address after request is serviced                                          |

|    |           | TSZ      | 0x4    | Maximum transfer size is one burst                                                   |

|    |           | RD       | 0x1    | Read buffer                                                                          |

|    | BD_BSIZE  |          | 0x200  | Buffer base size of cyclic buffer                                                    |

Add the following new section after **Section 16.3.1.2**:

### 16.3.1.3 DMA Arbitration Device Level Considerations

Any access issued by the DMA controller must pass two arbitration layers: the DMA arbitration and the bus controller arbitration. The first arbitration selects the DMA channel that generates the bus access. The second arbitration is the selection of the master by the bus arbitrator (DMA controller, TDM interface, Ethernet controller, DSI, and so on). The DMA arbiter selects the channel priority based on the values of DCHCRx[PRIO] and DPCR[AM]. The bus arbitrat uses BD\_ATTRx[BP] to select the channel priority on the bus.

You must assign correlating priorities to ensure correct operation of the transfers. The hierarchical arbitration may cause a high priority task to delay a low priority task pending in the bus arbiter.

Example 16-5. Multiple Device Arbitration

| Scenario: | Two DMA tasks (DMA_1 and DMA_2) are activated to use the device local bus. In addition, the TDM interface uses the local bus. The DMA controller uses fixed priority mode with the following setting:<br>— DMA_1: DCHCR[PRIO] = 0 (high), BD_ATTRx[BP] = 2 (high)<br>— DMA_2: DCHCR[PRIO] = F (low), BD_ATTRx[BP] = 0 (low)<br>The local bus arbiter uses the following priorities, from high to low:                                                                                                                                                                                                                                                                                                                   |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | — DMA_1, TDM, DMA_2 At some point during the operation, the DMA controller has no available data from DMA_1 and DMA_2 wins the arbitration. The DMA controller generates a low priority bus access based on the DMA_2 settings. At the same time, the TDM interface also attempts to access the local bus. The local bus arbitrator grants the bus to the TDM interface because its priority is higher than DMA_2. The TDM uses the bus. If, during the TDM transfers, DMA_1 has data to transfer, it tries to generate a bus access, but the DMA_2 access is still pending. This scenario causes the high priority DMA_1 activity to wait due to the pending low priority access by DMA_2. and the ongoing TDM access. |

| Solution: | Assign the TDM a lower priority than DMA_2 to prevent the situation in the scenario from occurring.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

The Section 16.3.2, delete the last sentence on page 16-32 before the note at the end of the section.

rupt Processing

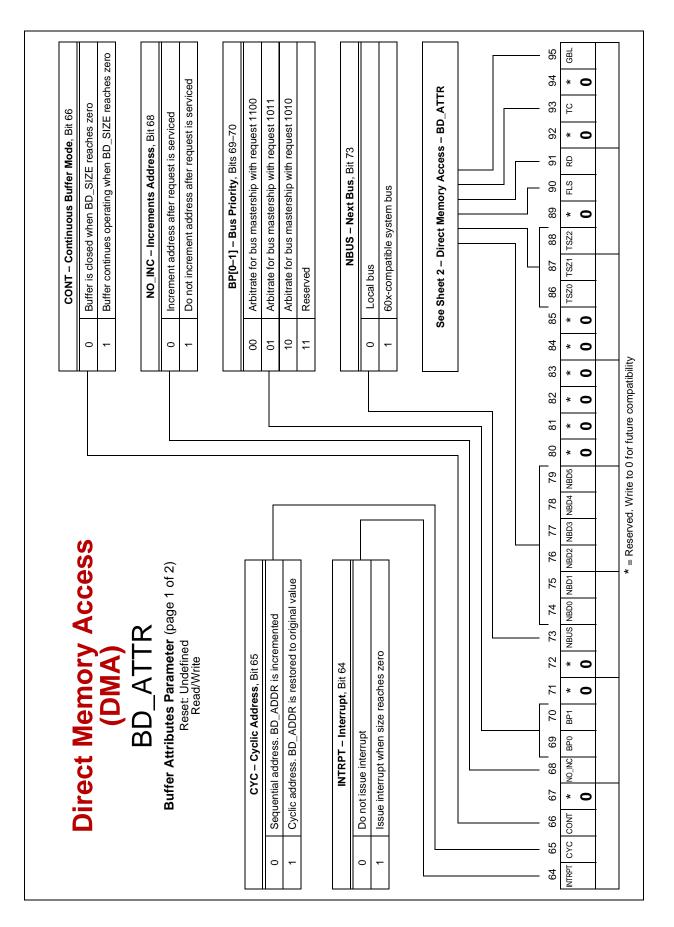

<sup>CP</sup> Replace **Table 16-9** and the subsequent bulleted list with the following:

| Bits   | Name     | Description                                                                                                                                                                                                                                                                                                                                                           |

|--------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0–31   | BD_ADDR  | <b>Buffer current address</b><br>Holds the buffer address pointer. If the buffer is cyclic, the original address value is restored when<br>the BD_SIZE value reaches zero by decrementing BD_BSIZE from BD_ADDR. See <b>Section</b><br><b>16.2.4.2</b> , <i>Cyclic Buffer</i> , on page 16-22.                                                                        |

| 32–63  | BD_SIZE  | <b>Size of transfer left for the current buffer</b><br>Contains the remaining size of the buffer. This value decrements by the transfer block size each<br>time the DMA controller issues a transaction, until it reaches zero. When BD_SIZE reaches zero,<br>the original value is restored to the value of BD_BSIZE. Program BD_SIZE with a value larger<br>than 0. |

| 64–95  | BD_ATTR  | Buffer attributes and temporary data<br>A 32-bit parameter that describes the attributes of the channel handling this buffer.<br>See Table 16-10.                                                                                                                                                                                                                     |

| 96–127 | BD_BSIZE | Buffer base size<br>Holds the base size of the buffer. if used, program BD_SIZE with a value greater than 0.                                                                                                                                                                                                                                                          |

#### Table 16-9. DCPRAM Bit Descriptions

### **11 Interrupt Processing**

$\bigcirc$  In **Table 17-9** on page 17-20, replace the 0x25  $\overline{\text{IRQ5}}$  row with the following:

| 0x25 | IRQ5 | Ethernet controller Receive Inter Frame Gap Status Interrupt | 0x940 |

|------|------|--------------------------------------------------------------|-------|

|      |      | (RIFGSI)<br>Note: RIFGSI is only used in SMII mode.          |       |

## 12 Debugging

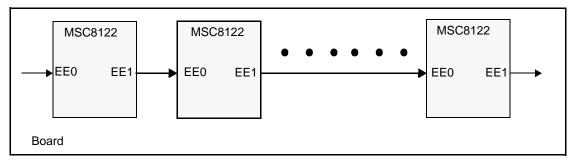

**G** Replace **Figure 18-8** with the following:

### Figure 18-8. Board EE Signal Interconnectivity

<sup>CP</sup> In Section 19.1 on page 19-1, change the second sentence to the following:

The TDM bus connects gluelessly to most T1/E1 framers as well as to common buses such as the ST-BUS.

### 14 TDM Interface

In the first part of Chapter 20 on page 20-1, change the second sentence in the second paragraph to the following:

The TDM bus connects gluelessly to most T1/E1 framers as well as to common buses such as the ST-BUS.

On page 20-2, change the first full sentence on line 4 by deleting "for transparent channels" before "is 16 MB", so that the sentence reads:

Buffer size is 16 MB for transparent channels and 32 MB for A-law/ $\mu$ -law channels.

- Add the following note at the end of **Section 20.2.4.3** on page 20-20:

- **Note:** Error interrupts from the TDM are driven directly to the LIC by the TDMx Receive Error Interrupt and TDMx Transmit Error Interrupt bits (TDMxRER[RSE] and TDMxTER[TSE]) when the interrupts are enabled. Therefore, the interrupt handler should clear these bits by writing a 1 to them before clearing the LIC-related status register and before returning to normal operation (exiting the interrupt handler).

<sup>CP</sup> In Section 20.2.6.2 on page 20-23, change the third bullet about the receive channel to the following:

- Receive Data Buffer Displacement. TDMxRDBDR[RDBD] field, page 20-60. Adding this field to the first byte of receive data buffer n indicates the location to which the TDM will write next: RGBA << 16 + RCDBA + RDBD is the current write pointer to the receive data buffer n. In most cases, the RDBD can be used to indicate that data is written to the buffer and can be processed. However, in some cases in which the local bus is extremely busy and the TDM bus priority is low, the pointer may be updated before the data is actually written to internal memory. This typically affects the last channel transmitted. In all cases, when configured to reflect the last buffer completion, assertion of the receive buffer threshold interrupt indicates that the data was updated in memory.</li>

- Add the following paragraph to the end of **Section 20.2.6.3** on page 20-26:

The TDM threshold interrupt can be programmed as pulse or level (TDMxRIR[RFTL] and TDMsdTIR[TFTL]). When level interrupt is used, you must clear the relevant bit (TDMxRER[RFTE/RSTE] and TDMxTER[TFTE/TSTE]) during interrupt handling. If the bits are not cleared, the TDM does not generate a new interrupt when it reaches the threshold the next time. Pulse interrupt mode does not require that these bits be cleared; the TDM continues to generate an interrupt toward the LIC every time it reaches the threshold. The LIC must be programmed to comply with the selected interrupt mode.

The Section 20.2.6.4 on page 20-27, replace the first paragraph with the following:

#### Interface

When the TDMxRFP[RUBM] bit is set (see page 20-46), the two receive channels are directed to one buffer in the local bus. The buffer parameters are stored in the TDMxRCPR0. The number of channels must be two (RNCF = 0x01), the number of active links must be one (RTSAL = 0b0000 or 0b0100 or 0b1100), and the number of bits per channel must be four, eight, or sixteen (RCS = 0b0011 or 0b0111. or 0b1111). The channel parameters of channels 0 and 1 are located in the TDMxRCPR0 register. Unified Buffer mode essentially creates a one-channel link that is typically used in point-to-point connections. When TDMxTFP[TUBM] =1, data is transmitted from one buffer into two transmit channels, each four, eight, or sixteen bits wide.

The Section 20.5 on page 20-31, change the first bullet in Step 3 to the following:

- Program the Transmit Sync Out (TSO) bit according the Transmit Sync signal direction (input or output) used in your system.

- <sup>CP</sup> In Section 20.5 on page 20-32, change the fifth bullet in Step 3 to the following:

- Clear the Receive Data Edge bit (RDE = 0x0), so that the receive data is sampled on the positive edge.

- The Section 20.7.2 on page 20-52, replace Table 20-22 with the following:

| Name             | Reset | Description                                                                                                       | Settings                                                                                                            |

|------------------|-------|-------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| 0–29             | 0     | Reserved. Write to zero for future compatibility.                                                                 |                                                                                                                     |

| <b>LTS</b><br>30 | 0     | Learn Transmit Sync<br>Determines whether the adaptation machine<br>learns the transmit sync or the receive sync. | <ol> <li>Adaptation machine learn the receive sync.</li> <li>Adaptation machine learn the transmit sync.</li> </ol> |

| <b>AME</b><br>31 | 0     | Adaptation Machine Enable<br>Determines whether the adaptation machine is<br>enabled or disabled.                 | <ul><li>0 Adaptation machine is disabled.</li><li>1 Adaptation machine is enabled</li></ul>                         |

#### Table 20-22. TDMxACR Bit Descriptions

The Table 20-38 on page 20-64, replace the RFTE and RSTE rows with the following:

| <b>RFTE</b><br>30 | 0 | <b>Receive First Threshold Event</b><br>This field is set when the first thresholds of all the received<br>data buffers are filled with received data. The first threshold<br>pointer is determined by the Receive Data Buffer First<br>Threshold field (RDBFT). For details, see <b>Section 20.2.6.3</b> . | 0 | No receive first threshold<br>event has occurred.<br>A receive first threshold event<br>has occurred.   |

|-------------------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---------------------------------------------------------------------------------------------------------|

| RSTE<br>31        | 0 | Receive Second Threshold Event<br>This field is set when the second thresholds of all the receive<br>data buffers are filled with received data. The second<br>threshold pointer is determined by the Receive Data Buffer<br>Second Threshold. (RDBST) field. For details, see Section<br>20.2.6            | 0 | No receive second threshold<br>event has occurred.<br>A receive second threshold<br>event has occurred. |

UART

<sup>CP</sup> In **Table 20-41** on page 20-66, replace the **RENS** row with the following:

| <b>RENS</b><br>31 | 0 | Receive Enable StatusIndicates whether all the receiver parts are enabled/disabled.The propagation of the enable/disable may be delayedbecause of the different clocks domains.Note:If the serial clock is not toggling, this bit may not reflect<br>updated values. | 0 | The receiver machine is<br>disabled.<br>The receiver machine is<br>enabled. |  |

|-------------------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----------------------------------------------------------------------------|--|

|-------------------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----------------------------------------------------------------------------|--|

<sup>C</sup> In **Table 20-42** on page 20-67, replace the **TENS** row with the following:

| <b>TENS</b><br>31 | 0 | Transmit Enable StatusIndicates whether all the transmitter parts are<br>enabled/disabled. The propagation of the enable/disable may<br>be delayed because of the different clock domains.Note:If the serial clock is not toggling, this bit may not reflect<br>updated values. | 0 | The transmit machine is<br>disabled.<br>The transmit machine is<br>enabled. |

|-------------------|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----------------------------------------------------------------------------|

|-------------------|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----------------------------------------------------------------------------|

## 15 UART

The Section 21.1.1 on page 21-8, replace the second note on the page with the following:

**Note:** When the shift register is empty (the TC and TDRE flags are set), transmission starts no more than one bit time after the data register is written. If only the TC interrupt source is enabled (SCICR[TCIE] = 1, SCICR[TIE] = 0), then you must ensure at least one bit time interval between successive writes to the SCIDR to enable the transmitter software to write twice to the SCIDR per interrupt.

- Note: The formula for calculating the baud rate is: SCI baud rate = SCI system  $clock/(16 \times SBR)$ .

- Note: The baud-rate generator is disabled until the SCICR[TE] bit or the SCICR[RE] bit is set for the first time after reset. The baud-rate generator is disabled when SBR = 0.

### 16 Timers

The Table 22-8 on page 22-12, change the CYC row to the following:

| CYC | 0 | Cyclic/One-Shot                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0 | One-Shot mode. |

|-----|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------|

| 31  |   | <ul> <li>Defines whether the Timer Ax mode of operation is cyclic or one-shot. In One-Shot mode, the counter of Timer-n counts up until it equals the TCMPAx[COMPVAL] field and then stops counting.</li> <li>Note: There are only 2 ways to use a timer properly in one-shot mode: <ol> <li>Set the one-shot timer input clock to be the bus clock</li> <li>The one-shot timer input clock must be higher than the bus clock frequency divided by 4.</li> </ol> </li> </ul> | 1 | Cyclic mode.   |

|     |   | In Cyclic mode, the counter of Timer-n counts from 0 until TCMPA[COMPVAL], wraps back to 0 and continues counting.                                                                                                                                                                                                                                                                                                                                                           |   |                |

The Section 21.6 on page 21-25, replace the two notes before Table 21-8 with the following:

### **17 Ethernet Controller**

**©** Replace the MGTCS row in **Table 25-66** with the following:

| <b>MGTCS</b><br>29–31 | 0 | Management Clock Select<br>Determines the clock frequency of the management clock | 000 BUSES_CLOCK/8<br>divided by 4.  |

|-----------------------|---|-----------------------------------------------------------------------------------|-------------------------------------|

|                       |   | (EC_MDC). Its default value is 000.                                               | 001 BUSES_CLOCK/8<br>divided by 4.  |

|                       |   |                                                                                   | 010 BUSES_CLOCK/8<br>divided by 6.  |

|                       |   |                                                                                   | 011 BUSES_CLOCK/8<br>divided by 8.  |

|                       |   |                                                                                   | 100 BUSES_CLOCK/8<br>divided by 10. |

|                       |   |                                                                                   | 101 BUSES_CLOCK/8<br>divided by 14. |

|                       |   |                                                                                   | 110 BUSES_CLOCK/8<br>divided by 20. |

|                       |   |                                                                                   | 111 BUSES_CLOCK/8<br>divided by 28. |

## **18 Programming Reference**

Replace the System Interface Unit (SIU) programming sheet on p. A-27 and the Direct Memory Access (DMA) BD\_ATTR page 1 of 2 on page A-66 with the following two sheets, respectively:

| Note: LUL. AtRH and LLC. ALRH of the local buse master index number masters.         Prointy of is the indigrets and Finding 15 is the local buse master by entering its index number and proving 15 is the local buse master by entering its index number and number masters.         Configuration.         Configuration.         Configuration.         Devise (b)         Configuration.         Configuration.         Configuration.         Configuration.         Devise (b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0000     0001       0011     0010       0011     0101       1101     1101       1110     1110       1111     1111 | Decaration       0     Reserved       1     Reserved       0     TDM       1     Host bridge       0     DMA high priority       0     BSI       0     DMA low priority       1     DMA low priority       1     Ethernet high priority       1     Ethernet now priority       1     Ethernet now priority |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       2       3       14       5       6       7       18       9       10       11       12       13       14       15       16       17       18       19       20       2         Priority Field 8       Priority Field 9       Priority Field 10       Priority Field 11       Priority Field 12       Priority 12 <td>21 22 23</td> <td>1         24         25         26         27         28         29         30         31           Priority Field 14         Priority Field 15</td> | 21 22 23                                                                                                          | 1         24         25         26         27         28         29         30         31           Priority Field 14         Priority Field 15                                                                                                                                                             |

MSC8122 Reference Manual Addendum, Rev. 10

NX

#### ramming Reference

Programming Reference

#### How to Reach Us:

Home Page: www.freescale.com

Web Support: http://www.freescale.com/support

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 +1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 +1-800 441-2447 or +1-303-675-2140 Fax: +1-303-675-2150 LDCForFreescaleSemiconductor @hibbertgroup.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup>, the Freescale logo, and CodeWarrior are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc., 2004, 2007. All rights reserved.

Document Number: MSC8122RMAD Rev. 10 07/2007