# e200z1 Power Architecture™ Core Reference Manual

Supports e200z1

> e200z1RM Rev. 0 09/2008

#### How to Reach Us:

Home Page:

www.freescale.com

Web Support:

http://www.freescale.com/support

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc.

Technical Information Center, EL516

2100 East Elliot Road

Tempe, Arizona 85284

1-800-521-6274 or

+1-480-768-2130

www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd.

Exchange Building 23F

No. 118 Jianguo Road

Chaoyang District

Beijing 100022

China

+86 010 5879 8000

support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor

Literature Distribution Center

P.O. Box 5405

Denver, Colorado 80217

1-800 441-2447 or

+1-303-675-2140

Fax: +1-303-675-2150

LDCForFreescaleSemiconductor

@hibbertgroup.com

Document Number: e200z1RM

Rev. 0, 09/2008

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale and the Freescale logo are trademarks or registered trademarks of Freescale Semiconductor, Inc. in the U.S. and other countries. All other product or service names are the property of their respective owners. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org. IEEE 754 is a trademark or registered trademark of the Institute of Electrical and Electronics Engineers, Inc. (IEEE). This product is not endorsed or approved by the IEEE.

© Freescale Semiconductor, Inc., 2008. All rights reserved.

| Paragraph<br>Number | Title                                               | Page<br>Number |

|---------------------|-----------------------------------------------------|----------------|

|                     | Chapter 1 e200z1 Overview                           |                |

|                     | e20021 Overview                                     |                |

| 1.1                 | Overview of the e200z1 Cores                        | 1-1            |

| 1.1.1               | Features                                            | 1-1            |

| 1.1.2               | Microarchitecture Summary                           | 1-2            |

| 1.1.2.1             | Instruction Unit Features                           | 1-4            |

| 1.1.2.2             | Integer Unit Features                               | 1-5            |

| 1.1.2.3             | Load/Store Unit Features                            | 1-5            |

| 1.1.2.4             | e200z1 System Bus Features                          | 1-5            |

| 1.1.2.5             | MMU Features                                        | 1-5            |

|                     | Chapter 2                                           |                |

|                     | Register Model                                      |                |

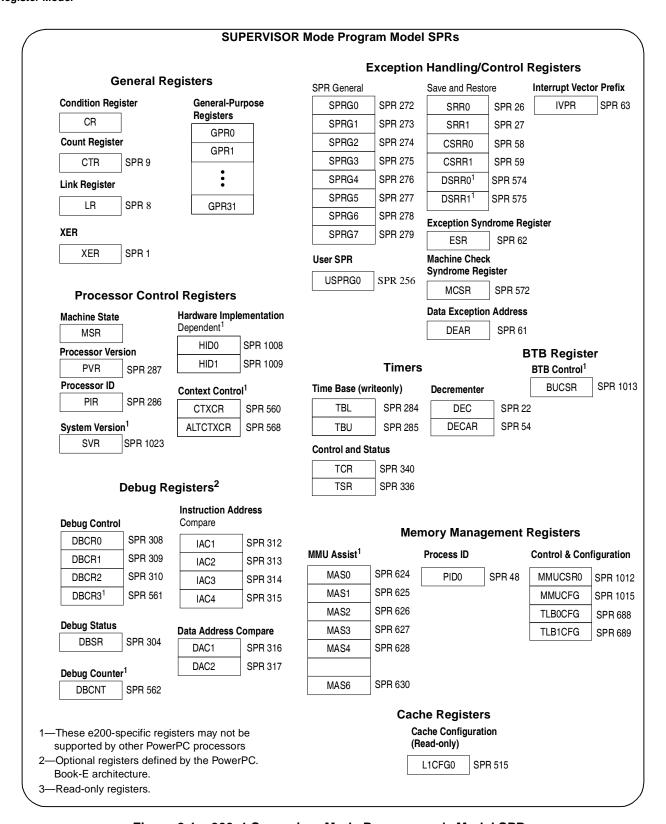

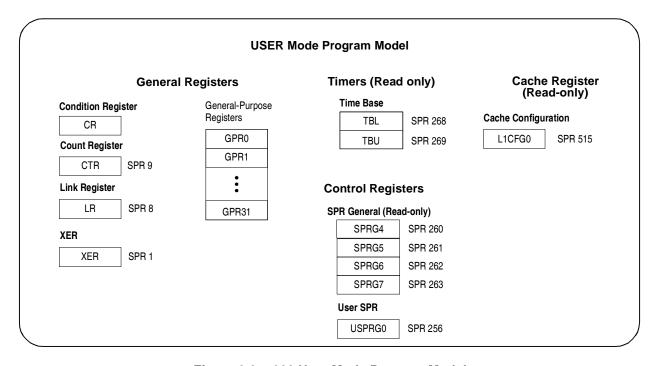

| 2.1                 | Power Architecture Book E Registers                 | 2-4            |

| 2.2                 | e200-Specific Special Purpose Registers             |                |

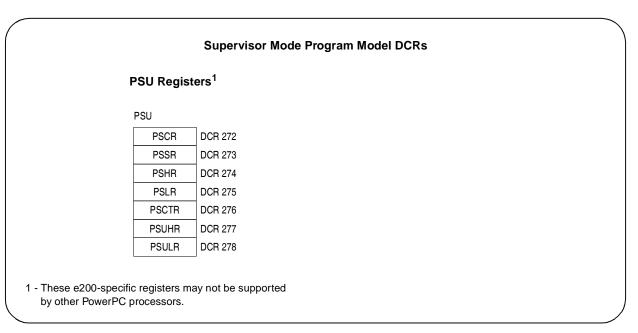

| 2.3                 | e200-Specific Device Control Registers              | 2-7            |

| 2.4                 | Special Purpose Register Descriptions               | 2-8            |

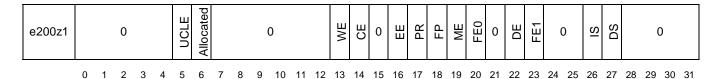

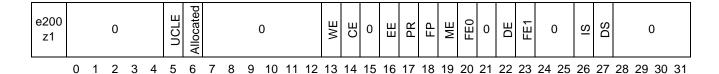

| 2.4.1               | Machine State Register (MSR)                        | 2-8            |

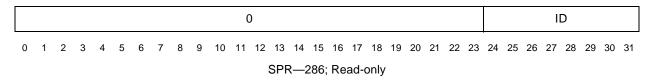

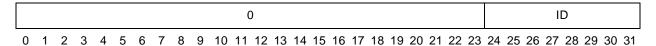

| 2.4.2               | Processor ID Register (PIR)                         | 2-10           |

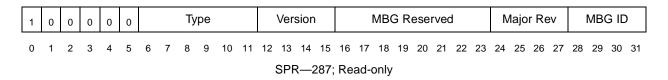

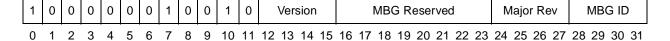

| 2.4.3               | Processor Version Register (PVR)                    | 2-10           |

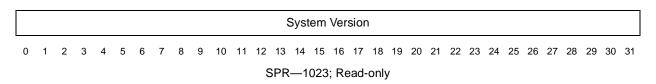

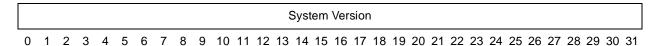

| 2.4.4               | System Version Register (SVR)                       | 2-11           |

| 2.4.5               | Integer Exception Register (XER)                    | 2-11           |

| 2.4.6               | Exception Syndrome Register                         | 2-12           |

| 2.4.6.1             | Power Architecture VLE Mode Instruction Syndrome    | 2-14           |

| 2.4.6.2             | Misaligned Instruction Fetch Syndrome               | 2-14           |

| 2.4.6.3             | Precise External Termination Error Syndrome         | 2-14           |

| 2.4.7               | Machine Check Syndrome Register (MCSR)              | 2-14           |

| 2.4.8               | Timer Control Register (TCR)                        | 2-15           |

| 2.4.9               | Timer Status Register (TSR)                         | 2-17           |

| 2.4.10              | Debug Registers                                     | 2-17           |

| 2.4.11              | Hardware Implementation Dependent Register 0 (HID0) | 2-18           |

| 2.4.12              | Hardware Implementation Dependent Register 1 (HID1) |                |

| 2.4.13              | Branch Unit Control and Status Register (BUCSR)     |                |

| 2.4.14              | L1 Cache Configuration Register (L1CFG0)            | 2-21           |

| 2.4.15              | MMU Control and Status Register (MMUCSR0)           |                |

| Number         | Title                                                   | Number      |

|----------------|---------------------------------------------------------|-------------|

| 2 1 1 -        |                                                         |             |

| 2.4.16         | MMU Configuration Register (MMUCFG)                     |             |

| 2.4.17         | TLB Configuration Registers (TLB0CFG, TLB1CFG)          |             |

| 2.5            | SPR Register Access                                     |             |

| 2.5.1          | Invalid SPR References                                  |             |

| 2.5.2          | Synchronization Requirements for SPRs                   |             |

| 2.5.3          | Special Purpose Register Summary                        |             |

| 2.5.4          | Reset Settings                                          | 2-26        |

|                | Chapter 3 Instruction Model                             |             |

| 0.1            |                                                         | 2.4         |

| 3.1            | Unsupported Instructions and Instruction Forms          |             |

| 3.2            | Optionally Supported Instructions and Instruction Forms |             |

| 3.3            | Implementation Specific Instructions                    |             |

| 3.4            | Book E Instruction Extensions                           |             |

| 3.5            | Memory Access Alignment Support                         |             |

| 3.6            | Memory Synchronization and Reservation Instructions     |             |

| 3.7            | Branch Prediction                                       |             |

| 3.8            | Interruption of Instructions by Interrupt Requests      |             |

| 3.9            | New e200 Instructions                                   |             |

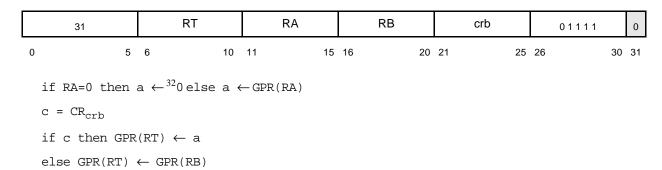

| 3.9.1          | ISEL APU                                                |             |

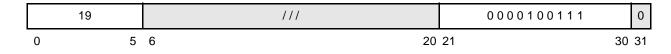

| 3.9.2          | Debug APU                                               |             |

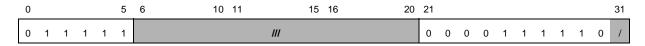

| 3.9.3          | WAIT APU                                                |             |

| 3.10           | Unimplemented SPRs and Read-Only SPRs                   |             |

| 3.11           | Invalid Forms of Instructions                           |             |

| 3.11.1         | Load and Store with Update Instructions                 |             |

| 3.11.2         | Load Multiple Word (lmw, <b>e_lmw</b> ) Instruction     |             |

| 3.11.3         | Branch Conditional to Count Register Instructions       |             |

| 3.11.4         | Instructions with Reserved Fields Non-Zero              |             |

| 3.12<br>3.12.1 | Instruction Summary                                     |             |

| 3.12.1         | Instruction Index Sorted by Mnemonic                    |             |

| 3.12.2         | Instruction Index Sorted by Opcode                      |             |

| 3.13           | Optionally Supported APU Instructions                   | 3-30        |

|                | Chapter 4 Instruction Pipeline and Execution Timing     |             |

| 4.1            | Overview of Operation                                   | <i>∆</i> _1 |

| 4.1.1          | Control Unit                                            |             |

| 4.1.2          | Instruction Unit                                        |             |

| 4.1.3          | Branch Unit                                             |             |

iv Freescale Semiconductor

| Paragraph<br>Number | Title                                                                    | Page<br>Number |

|---------------------|--------------------------------------------------------------------------|----------------|

| 4.1.4               | Instruction Decode Unit                                                  | 4-3            |

| 4.1.5               | Exception Handling                                                       | 4-3            |

| 4.2                 | Execution Units                                                          | 4-3            |

| 4.2.1               | Integer Execution Unit                                                   | 4-3            |

| 4.2.2               | Load/Store Unit                                                          | 4-4            |

| 4.3                 | Instruction Pipeline                                                     | 4-4            |

| 4.3.1               | Description of Pipeline Stages                                           | 4-5            |

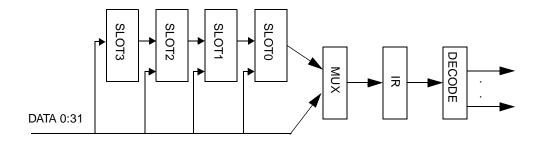

| 4.3.2               | Instruction Buffers                                                      | 4-6            |

| 4.3.2.1             | Branch Prediction in e200z1                                              | 4-6            |

| 4.3.3               | Single-Cycle Instruction Pipeline Operation                              | 4-8            |

| 4.3.4               | Basic Load and Store Instruction Pipeline Operation                      | 4-8            |

| 4.3.5               | Change-of-Flow Instruction Pipeline Operation                            | 4-10           |

| 4.3.6               | Basic Multi-Cycle Instruction Pipeline Operation                         | 4-11           |

| 4.3.7               | Additional Examples of Instruction Pipeline Operation for Load and Store | 4-12           |

| 4.3.8               | Move to/from SPR Instruction Pipeline Operation                          | 4-12           |

| 4.4                 | Control Hazards                                                          | 4-14           |

| 4.5                 | Instruction Serialization                                                | 4-14           |

| 4.5.1               | Completion Serialization                                                 | 4-15           |

| 4.5.2               | Dispatch Serialization                                                   | 4-15           |

| 4.5.3               | Refetch Serialization                                                    | 4-15           |

| 4.6                 | Interrupt Recognition and Exception Processing                           | 4-16           |

| 4.7                 | Instruction Timings                                                      | 4-19           |

| 4.8                 | Operand Placement on Performance                                         | 4-19           |

|                     | Chapter 5 Interrupts and Exceptions                                      |                |

| 5.1                 | e200 Interrupts                                                          | 5-2            |

| 5.2                 | Exception Syndrome Register                                              |                |

| 5.3                 | Machine State Register                                                   |                |

| 5.4                 | Machine Check Syndrome Register (MCSR)                                   |                |

| 5.5                 | Interrupt Vector Prefix Register (IVPR)                                  |                |

| 5.6                 | Interrupt Vector Offset Values (IVORxx)                                  |                |

| 5.7                 | Interrupt Definitions                                                    |                |

| 5.7.1               | Critical Input Interrupt (IVOR0)                                         |                |

| 5.7.2               | Machine Check Interrupt (IVOR1)                                          |                |

| 5.7.2.1             | Machine Check Interrupt Enabled (MSR[ME]=1)                              |                |

| 5.7.2.2             | Checkstop State                                                          |                |

| 5.7.3               | Data Storage Interrupt (IVOR2)                                           |                |

| 5.7.4               | Instruction Storage Interrupt (IVOR3)                                    |                |

| 5.7.5               | External Input Interrupt (IVOR4)                                         |                |

|                     | r · · · · · · · · · · · · · · · · · · ·                                  |                |

e200z1 Power Architecture Core Reference Manual, Rev. 0

| Paragrapn |                                                   | Page   |

|-----------|---------------------------------------------------|--------|

| Number    | Title                                             | Number |

| 5.7.6     | Alignment Interrupt (IVOR5)                       | 5-15   |

| 5.7.7     | Program Interrupt (IVOR6)                         |        |

| 5.7.8     | Floating-Point Unavailable Interrupt (IVOR7)      |        |

| 5.7.9     | System Call Interrupt (IVOR8)                     |        |

| 5.7.10    | Auxiliary Processor Unavailable Interrupt (IVOR9) |        |

| 5.7.11    | Decrementer Interrupt (IVOR10)                    |        |

| 5.7.12    | Fixed-Interval Timer Interrupt (IVOR11)           |        |

| 5.7.13    | Watchdog Timer Interrupt (IVOR12)                 |        |

| 5.7.14    | Data TLB Error Interrupt (IVOR13)                 |        |

| 5.7.15    | Instruction TLB Error Interrupt (IVOR14)          |        |

| 5.7.16    | Debug Interrupt (IVOR15)                          |        |

| 5.7.17    | System Reset Interrupt                            |        |

| 5.8       | Exception Recognition and Priorities              |        |

| 5.8.1     | Exception Priorities                              |        |

| 5.9       | Interrupt Processing                              |        |

| 5.9.1     | Enabling and Disabling Exceptions                 |        |

| 5.9.2     | Returning from an Interrupt Handler               |        |

| 5.10      | Process Switching                                 |        |

|           | Chapter 6                                         |        |

|           | Memory Management Unit                            |        |

| 6.1       | Overview                                          | 6-1    |

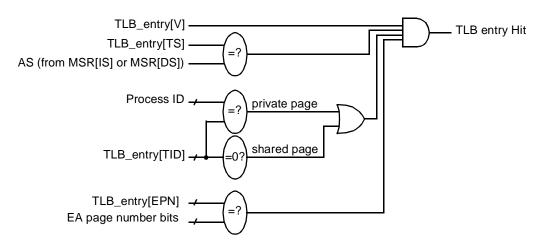

| 6.2       | Effective to Real Address Translation             | 6-1    |

| 6.2.1     | Effective Addresses                               | 6-1    |

| 6.2.2     | Address Spaces                                    | 6-1    |

| 6.2.3     | Process ID                                        | 6-2    |

| 6.2.4     | Translation Flow                                  | 6-2    |

| 6.2.5     | Permissions                                       | 6-4    |

| 6.3       | Translation Lookaside Buffer                      | 6-5    |

| 6.4       | Configuration Information                         | 6-6    |

| 6.4.1     | MMU Configuration Register (MMUCFG)               | 6-6    |

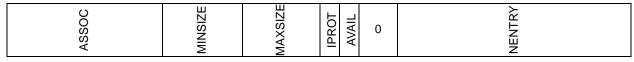

| 6.4.2     | TLB0 Configuration Register (TLB0CFG)             | 6-7    |

| 6.4.3     | TLB1 Configuration Register (TLB1CFG)             |        |

| 6.5       | Software Interface and TLB Instructions           | 6-9    |

| 6.5.1     | TLB Read Entry Instruction (tlbre)                | 6-9    |

| 6.5.2     | TLB Write Entry Instruction (tlbwe)               |        |

| 6.5.3     | TLB Search Instruction (tlbsx)                    |        |

| 6.5.4     | TLB Invalidate (tlbivax) Instruction              |        |

| 6.5.5     | TLB Synchronize Instruction (tlbsync)             |        |

| 6.6       | TLB Operations                                    | 6-12   |

|           |                                                   |        |

| Number Number | Title                                                               | Page<br>Number |

|---------------|---------------------------------------------------------------------|----------------|

| 6.6.1         | Translation Reload                                                  | 6-12           |

| 6.6.2         | Reading the TLB                                                     |                |

| 6.6.3         | Writing the TLB                                                     |                |

| 6.6.4         | Searching the TLB                                                   |                |

| 6.6.5         | TLB Miss Exception Update                                           |                |

| 6.6.6         | IPROT Invalidation Protection                                       |                |

| 6.6.7         | TLB Load on Reset                                                   |                |

| 6.6.8         | The G Bit                                                           | 6-14           |

| 6.7           | MMU Control Registers                                               | 6-14           |

| 6.7.1         | DEAR Register                                                       |                |

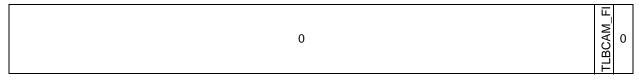

| 6.7.2         | MMU Control and Status Register 0 (MMUCSR0)                         | 6-15           |

| 6.7.3         | MMU Assist Registers (MAS)                                          |                |

| 6.7.4         | MAS Registers Summary                                               |                |

| 6.7.5         | MAS Register Updates                                                |                |

| 6.8           | TLB Coherency Control                                               |                |

| 6.9           | Core Interface Operation for MMU Control Instructions               |                |

| 6.9.1         | Transfer Type Encodings for MMU Control Instructions                | 6-23           |

| 6.10          | Effect of Hardware Debug on MMU Operation                           |                |

|               | Chapter 7 Core Complex Interfaces                                   |                |

| 7.1           | Signal Index                                                        | 7-2            |

| 7.2           | Internal Interface Signals                                          |                |

| 7.3           | Signal Descriptions                                                 | 7-9            |

| 7.3.1         | e200 Processor Clock ( <i>m_clk</i> )                               | 7-9            |

| 7.3.2         | Reset-Related Signals                                               | 7-9            |

| 7.3.2.1       | Power-On Reset ( <i>m_por</i> )                                     | 7-10           |

| 7.3.2.2       | Reset ( <i>p_reset_b</i> )                                          | 7-10           |

| 7.3.2.3       | Reset Out ( <i>p_resetout_b</i> )                                   | 7-10           |

| 7.3.2.4       | Reset Base ( <i>p_rstbase</i> [0:29])                               | 7-10           |

| 7.3.2.5       | Reset Endian Mode ( <i>p_rst_endmode</i> )                          |                |

| 7.3.2.6       | Reset VLE Mode ( <i>p_rst_vlemode</i> )                             | 7-11           |

| 7.3.2.7       | Reset Addr Bypass ( <i>p_addr_bypass</i> )                          | 7-11           |

| 7.3.2.8       | JTAG/OnCE Reset ( <i>j_trst_b</i> )                                 | 7-11           |

| 7.3.3         | Address and Data Buses                                              | 7-11           |

| 7.3.3.1       | Address Bus ( <i>p_d_haddr</i> [31:0], <i>p_i_haddr</i> [31:0])     | 7-11           |

| 7.3.3.2       | Read Data Bus ( <i>p_d_hrdata</i> [31:0], <i>p_i_hrdata</i> [31:0]) |                |

| 7.3.3.3       | Write Data Bus ( <i>p_d_hwdata</i> [31:0])                          | 7-12           |

| 7.3.4         | Transfer Attribute Signals                                          | 7-12           |

| 7.3.4.1       | Transfer Type $(p\_d\_htrans[1:0], p\_i\_htrans[1:0])$              | 7-13           |

|               |                                                                     |                |

e200z1 Power Architecture Core Reference Manual, Rev. 0

| Paragraph<br>Number | Title                                                                                           | Page<br>Number |

|---------------------|-------------------------------------------------------------------------------------------------|----------------|

| 7.3.4.2             | Write ( <i>p_d_hwrite</i> , <i>p_i_hwrite</i> )                                                 | 7-13           |

| 7.3.4.3             | Transfer Size $(p\_d\_hsize[1:0], p\_i\_hsize[1:0])$                                            | 7-13           |

| 7.3.4.4             | Burst Type ( <i>p_d_hburst</i> [2:0], <i>p_i_hburst</i> [2:0])                                  | 7-14           |

| 7.3.4.5             | Protection Control ( <i>p_d_hprot</i> [5:0], <i>p_i_hprot</i> [5:0])                            | 7-14           |

| 7.3.5               | Byte Lane Specification                                                                         |                |

| 7.3.5.1             | Unaligned Access ( <i>p_d_hunalign</i> , <i>p_i_hunalign</i> )                                  | 7-16           |

| 7.3.5.2             | Byte Strobes ( <i>p_d_hbstrb</i> [3:0], <i>p_i_hbstrb</i> [3:0])                                | 7-16           |

| 7.3.6               | Transfer Control Signals                                                                        |                |

| 7.3.6.1             | Transfer Ready ( <i>p_d_hready</i> , <i>p_i_hready</i> )                                        | 7-20           |

| 7.3.6.2             | Transfer Response $(p\_d\_hresp[2:0], p\_i\_hresp[1:0])$                                        | 7-20           |

| 7.3.7               | Interrupt Signals                                                                               | 7-20           |

| 7.3.7.1             | External Input Interrupt Request ( <i>p_extint_b</i> )                                          | 7-21           |

| 7.3.7.2             | Critical Input Interrupt Request ( <i>p_critint_b</i> )                                         | 7-21           |

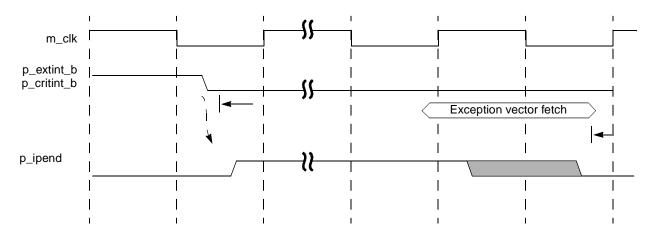

| 7.3.7.3             | Interrupt Pending ( <i>p_ipend</i> )                                                            | 7-21           |

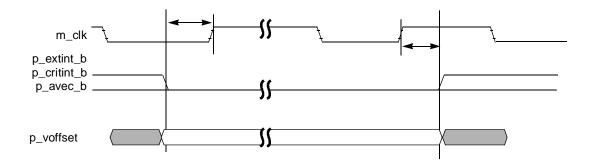

| 7.3.7.4             | Autovector ( <i>p_avec_b</i> )                                                                  | 7-21           |

| 7.3.7.5             | Interrupt Vector Offset (p_voffset[0:9])                                                        | 7-21           |

| 7.3.7.6             | Interrupt Vector Acknowledge (p_iack)                                                           | 7-22           |

| 7.3.7.7             | Machine Check ( <i>p_mcp_b</i> )                                                                | 7-22           |

| 7.3.8               | Timer Facility Signals                                                                          | 7-22           |

| 7.3.8.1             | Timer Disable ( <i>p_tbdisable</i> )                                                            | 7-22           |

| 7.3.8.2             | Timer External Clock ( <i>p_tbclk</i> )                                                         | 7-22           |

| 7.3.8.3             | Timer Interrupt Status ( <i>p_tbint</i> )                                                       | 7-23           |

| 7.3.9               | Processor Reservation Signals                                                                   | 7-23           |

| 7.3.9.1             | CPU Reservation Status ( <i>p_rsrv</i> )                                                        | 7-23           |

| 7.3.9.2             | CPU Reservation Clear ( <i>p_rsrv_clr</i> )                                                     | 7-23           |

| 7.3.10              | Miscellaneous Processor Signals                                                                 | 7-23           |

| 7.3.10.1            | PID0 Outputs ( <i>p_pid0</i> [0:7])                                                             | 7-24           |

| 7.3.10.2            | PID0 Update ( <i>p_pid0_updt</i> )                                                              | 7-24           |

| 7.3.10.3            | HID1 System Control ( <i>p_hid1_sysctl</i> [0:7])                                               | 7-24           |

| 7.3.11              | Processor State Signals                                                                         | 7-24           |

| 7.3.11.1            | Processor Status ( <i>p_pstat</i> [0:6])                                                        | 7-24           |

| 7.3.11.2            | Processor Exception Enable MSR Values ( <i>p_EE</i> , <i>p_CE</i> , <i>p_DE</i> , <i>p_ME</i> ) | 7-26           |

| 7.3.11.3            | Branch Prediction Status ( <i>p_brstat</i> [0:1])                                               | 7-26           |

| 7.3.11.4            | Processor Machine Check ( <i>p_mcp_out</i> )                                                    | 7-26           |

| 7.3.11.5            | Processor Checkstop ( <i>p_chkstop</i> )                                                        | 7-26           |

| 7.3.12              | Power Management Control Signals                                                                | 7-26           |

| 7.3.12.1            | Processor Waiting ( <i>p_waiting</i> )                                                          | 7-26           |

| 7.3.12.2            | Processor Halt Request ( <i>p_halt</i> )                                                        |                |

| 7.3.12.3            | Processor Halted ( <i>p_halted</i> )                                                            | 7-27           |

| 7.3.12.4            | Processor Stop Request ( <i>p_stop</i> )                                                        |                |

| 7.3.12.5            | Processor Stopped (p_stopped)                                                                   |                |

e200z1 Power Architecture Core Reference Manual, Rev. 0

| Paragraph    |                                                 | Page   |

|--------------|-------------------------------------------------|--------|

| Number       | Title                                           | Number |

| 7.3.12.6     | Low-Power Mode Signals (p_doze, p_nap, p_sleep) | 7-27   |

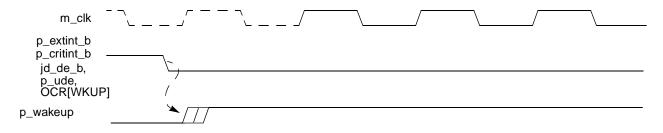

| 7.3.12.7     | Wakeup (p_wakeup)                               | 7-27   |

| 7.3.13       | Debug Event Signals                             | 7-28   |

| 7.3.13.1     | Unconditional Debug Event ( <i>p_ude</i> )      | 7-28   |

| 7.3.13.2     | External Debug Event 1 ( <i>p_devt1</i> )       | 7-28   |

| 7.3.13.3     | External Debug Event 2 (p_devt2)                | 7-28   |

| 7.3.14       | Debug/Emulation (Nexus 1/OnCE) Support Signals  | 7-28   |

| 7.3.14.1     | OnCE Enable (jd_en_once)                        | 7-29   |

| 7.3.14.2     | Debug Session (jd_debug_b)                      | 7-29   |

| 7.3.14.3     | Debug Request ( <i>jd_de_b</i> )                | 7-30   |

| 7.3.14.4     | DE_b Active High Output Enable (jd_de_en)       | 7-30   |

| 7.3.14.5     | Processor Clock On (jd_mclk_on)                 |        |

| 7.3.14.6     | Watchpoint Events (jd_watchpoint[0:7])          | 7-30   |

| 7.3.15       | JTAG Support Signals                            |        |

| 7.3.15.1     | JTAG/OnCE Serial Input ( <i>j_tdi</i> )         |        |

| 7.3.15.2     | JTAG/OnCE Serial Clock ( <i>j_tclk</i> )        |        |

| 7.3.15.3     | JTAG/OnCE Serial Output (j_tdo)                 |        |

| 7.3.15.4     | JTAG/OnCE Test Mode Select ( <i>j_tms</i> )     |        |

| 7.3.15.5     | JTAG/OnCE Test Reset ( <i>j_trst_b</i> )        |        |

| 7.3.15.6     | Test-Logic-Reset (j_tst_log_rst)                | 7-32   |

| 7.3.15.7     | Run-Test/Idle $(j_rti)$                         |        |

| 7.3.15.8     | Capture IR ( <i>j_capture_ir</i> )              |        |

| 7.3.15.9     | Shift IR ( <i>j_shift_ir</i> )                  |        |

| 7.3.15.10    | Update IR (j_update_ir)                         |        |

| 7.3.15.11    | Capture DR ( <i>j_capture_dr</i> )              | 7-32   |

| 7.3.15.12    | Shift DR $(j\_shift\_dr)$                       |        |

| 7.3.15.13    | Update DR (j_update_gp_reg)                     |        |

| 7.3.15.14    | Register Select (j_gp_regsel)                   |        |

| 7.3.15.15    | Enable Once Register Select (j_en_once_regsel)  |        |

| 7.3.15.16    | External Nexus Register Select (j_nexus_regsel) |        |

| 7.3.15.17    | External LSRL Register Select (j_lsrl_regsel)   |        |

| 7.3.15.18    | Serial Data ( <i>j_serial_data</i> )            |        |

| 7.3.15.19    | Key Data In (j_key_in)                          |        |

| 7.3.16       | JTAG ID Signals                                 | 7-35   |

| 7.3.16.1     | JTAG ID Sequence (j_id_sequence[0:1])           |        |

| 7.3.16.2     | JTAG ID Sequence $(j\_id\_sequence[2:9])$       |        |

| 7.3.16.3     | JTAG ID Version $(j\_id\_version[0:3])$         |        |

| 7.4          | Timing Diagrams                                 |        |

| 7.4.1        | Processor Instruction/Data Transfers            | 7-36   |

| 7.4.1.1      | Basic Read Transfer Cycles                      |        |

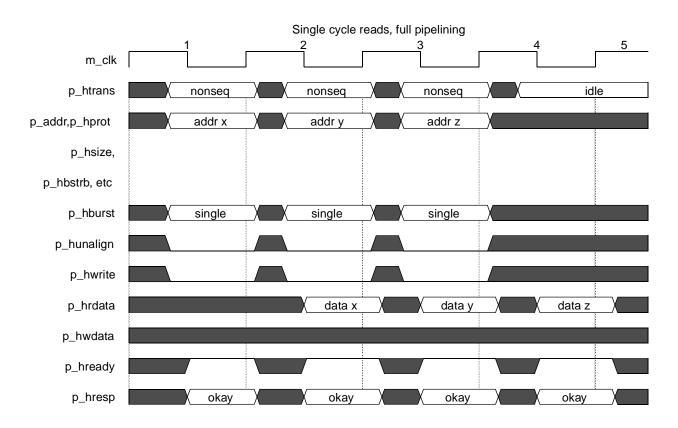

| Clock 1 (C1) | •                                               |        |

|              |                                                 |        |

| Paragrapn<br>Number | Title                                                                  | Page<br>Number |

|---------------------|------------------------------------------------------------------------|----------------|

| Clock 2 (C2): 38    |                                                                        |                |

| Clock 3 (C3): 38    |                                                                        |                |

| Clock 4 (C4): 38    |                                                                        |                |

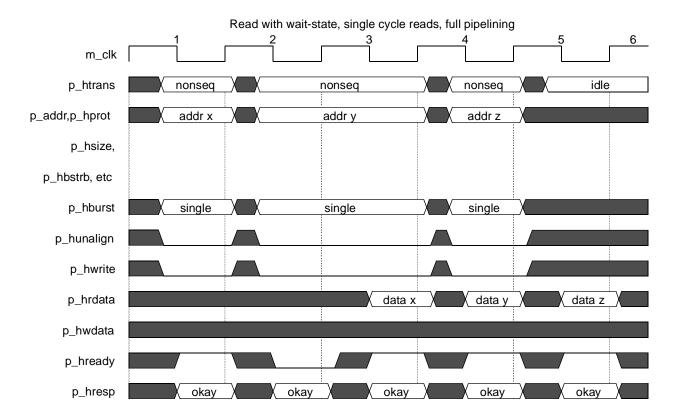

| 7.4.1.2             | Read Transfer with Wait State                                          | 7-38           |

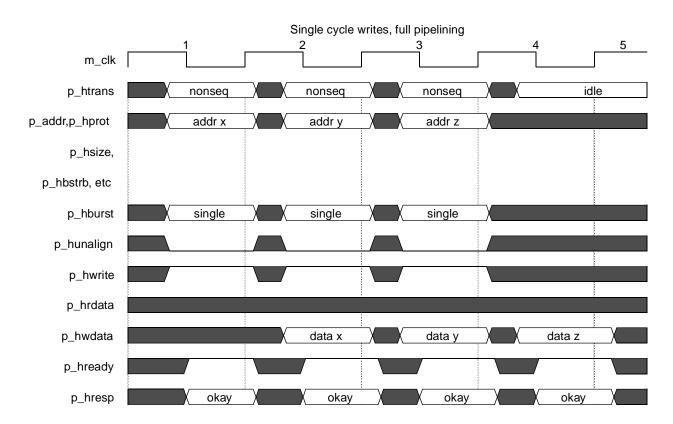

| 7.4.1.3             | Basic Write Transfer Cycles                                            |                |

| Clock 1 (C1): 40    | Duste write fruitsfer Cycles                                           | , 10           |

| Clock 2 (C2): 41    |                                                                        |                |

| Clock 3 (C3): 41    |                                                                        |                |

| Clock 4 (C4): 41    |                                                                        |                |

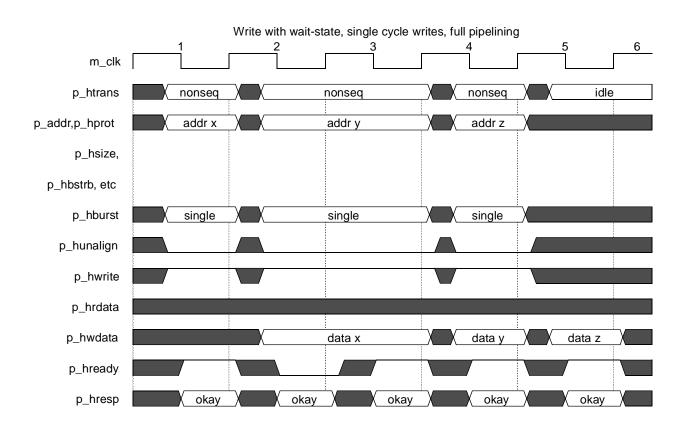

| 7.4.1.4             | Write Transfer with Wait States                                        | 7-41           |

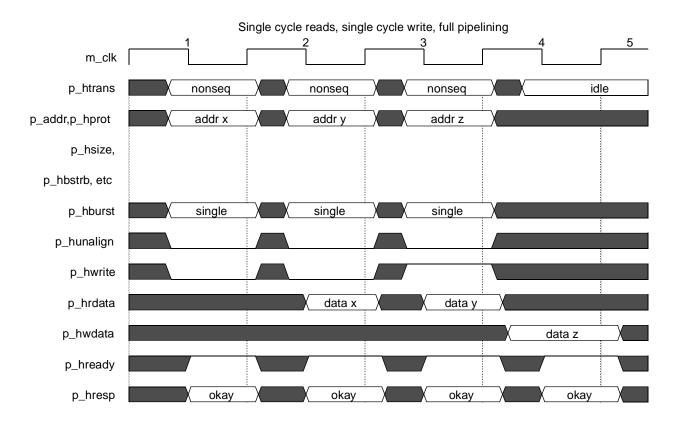

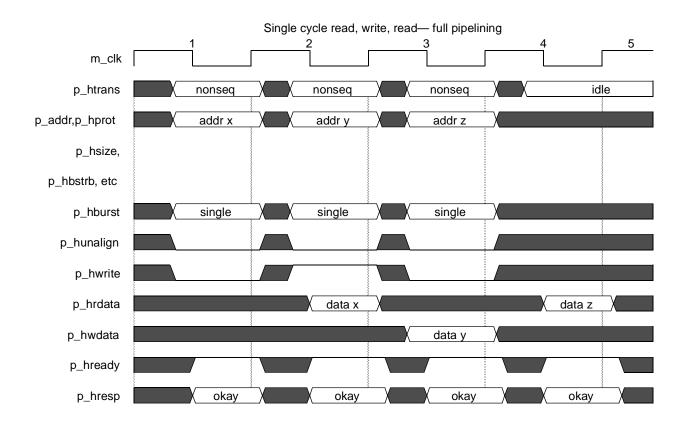

| 7.4.1.5             | Read and Write Transfers                                               | 7-43           |

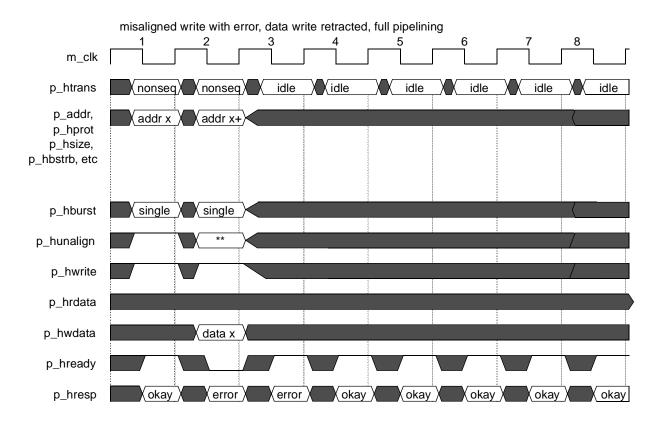

| 7.4.1.6             | Misaligned Accesses                                                    | 7-47           |

| 7.4.1.7             | Burst Accesses                                                         |                |

| 7.4.1.8             | Address Retraction                                                     | 7-56           |

| 7.4.1.9             | Error Termination Operation                                            | 7-58           |

| 7.4.2               | Power Management                                                       | 7-61           |

| 7.4.3               | Interrupt Interface                                                    | 7-62           |

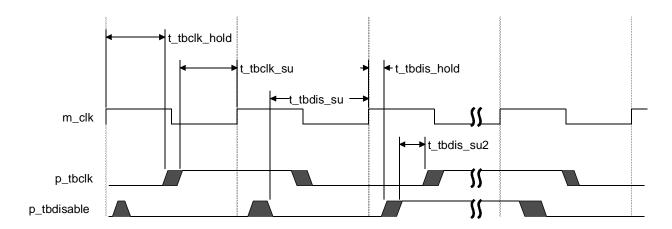

| 7.4.4               | Time Base Interface                                                    | 7-64           |

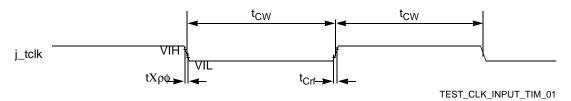

| 7.4.5               | JTAG Test Interface                                                    | 7-65           |

|                     |                                                                        |                |

|                     | Chapter 8                                                              |                |

|                     | Power Management                                                       |                |

| 8.1 Pov             | wer Management                                                         | 8-1            |

| 8.1.1               | Active State                                                           | 8-1            |

| 8.1.2               | Waiting State                                                          | 8-1            |

| 8.1.3               | Halted State                                                           | 8-1            |

| 8.1.4               | Stopped State                                                          | 8-2            |

| 8.1.5               | Power Management Pins                                                  | 8-2            |

|                     | Power Management Control Bits                                          | 8-3            |

|                     | Software Considerations for Power Management using Wait Instructions   |                |

|                     | Software Considerations for Power Management Using Doze, Nap, or Sleep |                |

| 8.1.9               | Debug Considerations for Power Management                              | 8-4            |

|                     | Chapter 9                                                              |                |

|                     | Debug Support                                                          |                |

| 9.1 Ov              | verview                                                                | 9-1            |

|                     | Software Debug Facilities                                              | 9-1            |

| 9.1.1.1             | Power Architecture Book E Compatibility                                |                |

|                     | Additional Debug Facilities                                            |                |

|                     | e200z1 Power Architecture Core Reference Manual, Rev. 0                |                |

x Freescale Semiconductor

| Paragraph<br>Number | Title                                                     | Page<br>Number |

|---------------------|-----------------------------------------------------------|----------------|

| 9.1.3               | Hardware Debug Facilities                                 | 9-2            |

| 9.2                 | Software Debug Events and Exceptions                      | 9-3            |

| 9.2.1               | Instruction Address Compare Event                         |                |

| 9.2.2               | Data Address Compare Event                                |                |

| 9.2.3               | Linked Instruction Address and Data Address Compare Event |                |

| 9.2.4               | Trap Debug Event                                          |                |

| 9.2.5               | Branch Taken Debug Event                                  | 9-7            |

| 9.2.6               | Instruction Complete Debug Event                          | 9-7            |

| 9.2.7               | Interrupt Taken Debug Event                               | 9-7            |

| 9.2.8               | Critical Interrupt Taken Debug Event                      |                |

| 9.2.9               | Return Debug Event                                        | 9-8            |

| 9.2.10              | Critical Return Debug Event                               | 9-8            |

| 9.2.11              | Debug Counter Debug Event                                 | 9-8            |

| 9.2.12              | External Debug Event                                      | 9-8            |

| 9.2.13              | Unconditional Debug Event                                 |                |

| 9.3                 | Debug Registers                                           | 9-9            |

| 9.3.1               | Debug Address and Value Registers                         | 9-9            |

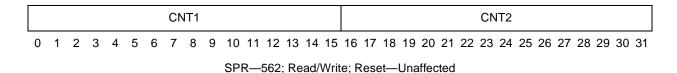

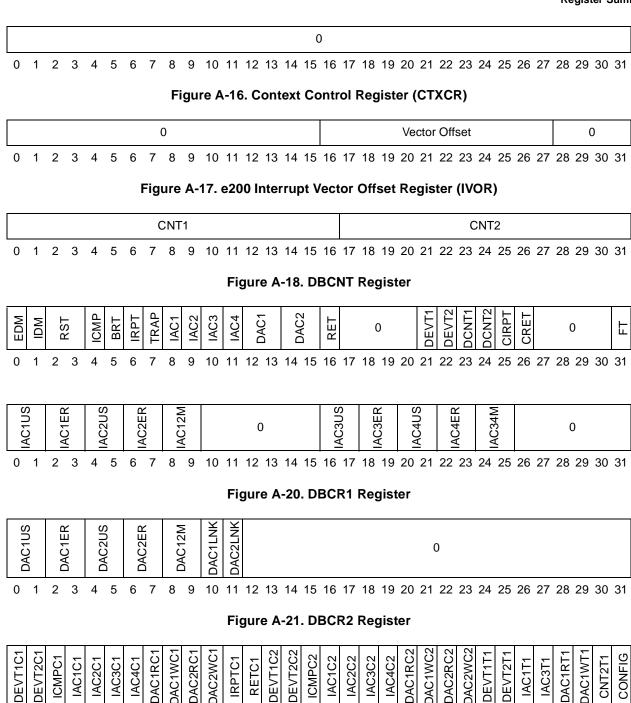

| 9.3.2               | Debug Counter Register (DBCNT)                            |                |

| 9.3.3               | Debug Control and Status Registers                        | 9-10           |

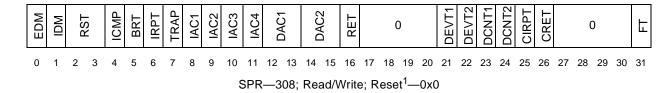

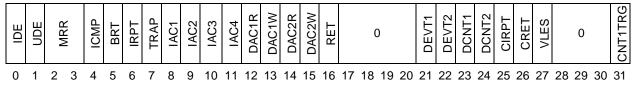

| 9.3.3.1             | Debug Control Register 0 (DBCR0)                          | 9-10           |

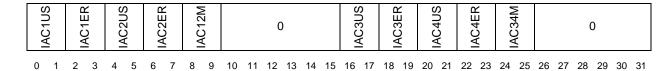

| 9.3.3.2             | Debug Control Register 1 (DBCR1)                          | 9-13           |

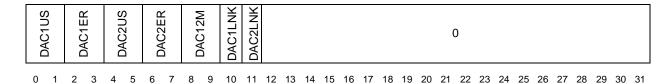

| 9.3.3.3             | Debug Control Register 2 (DBCR2)                          | 9-15           |

| 9.3.3.4             | Debug Control Register 3 (DBCR3)                          | 9-16           |

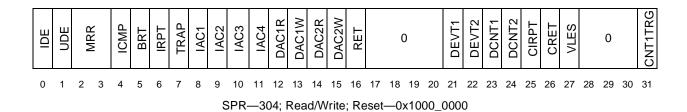

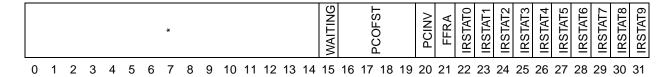

| 9.3.3.5             | Debug Status Register (DBSR)                              | 9-21           |

| 9.4                 | External Debug Support                                    | 9-23           |

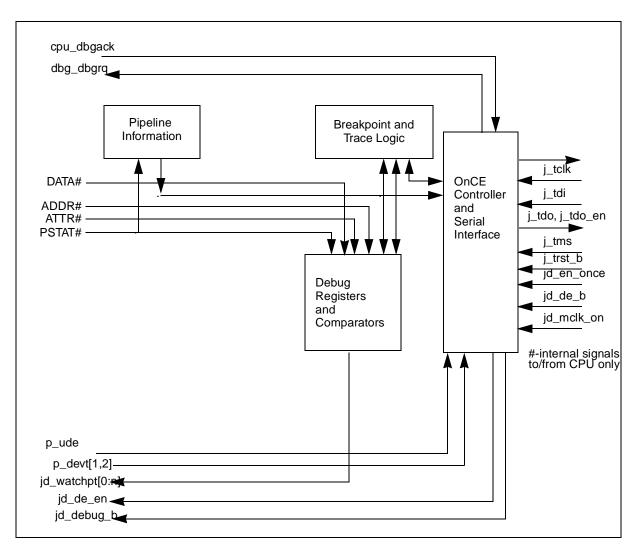

| 9.4.1               | OnCE Introduction                                         | 9-24           |

| 9.4.2               | JTAG/OnCE Pins                                            | 9-27           |

| 9.4.3               | OnCE Internal Interface Signals                           | 9-27           |

| 9.4.3.1             | CPU Debug Request (dbg_dbgrq)                             | 9-27           |

| 9.4.3.2             | CPU Debug Acknowledge (cpu_dbgack)                        | 9-28           |

| 9.4.4               | OnCE Interface Signals                                    |                |

| 9.4.4.1             | OnCE Enable (jd_en_once)                                  | 9-28           |

| 9.4.4.2             | OnCE Debug Request/Event (jd_de_b, jd_de_en)              | 9-28           |

| 9.4.4.3             | e200 OnCE Debug Output (jd_debug_b)                       | 9-29           |

| 9.4.4.4             | e200 CPU Clock On Input (jd_mclk_on)                      | 9-29           |

| 9.4.4.5             | Watchpoint Events (jd_watchpt[0:7])                       | 9-29           |

| 9.4.5               | e200 OnCE Controller and Serial Interface                 | 9-29           |

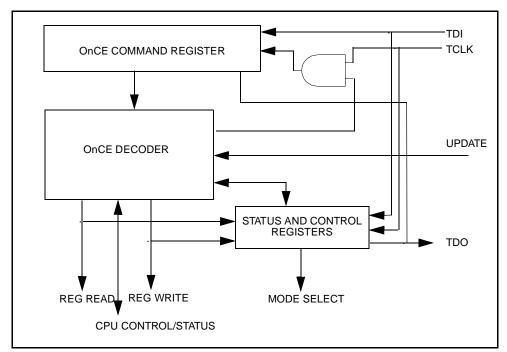

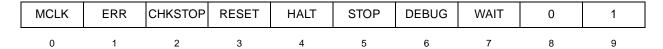

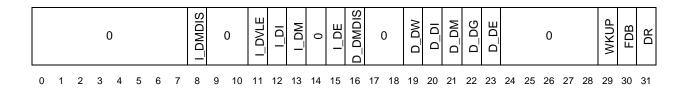

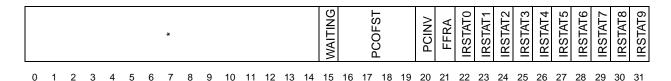

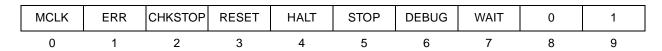

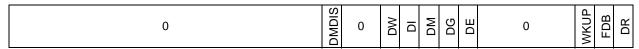

| 9.4.5.1             | e200 OnCE Status Register                                 | 9-30           |

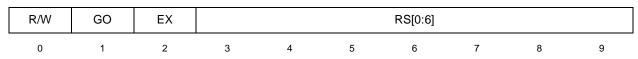

| 9.4.5.2             | e200 OnCE Command Register (OCMD)                         | 9-31           |

| 9.4.5.3             | e200 OnCE Control Register (OCR)                          |                |

| 9.4.6               | Access to Debug Resources                                 |                |

xii

### **Contents**

| Paragraph<br>Number | Title                                                            | Page<br>Number |

|---------------------|------------------------------------------------------------------|----------------|

| 9.4.7               | Methods of Entering Debug Mode                                   | 9-38           |

| 9.4.7.1             | External Debug Request During RESET                              | 9-38           |

| 9.4.7.2             | Debug Request During RESET                                       | 9-38           |

| 9.4.7.3             | Debug Request During Normal Activity                             | 9-38           |

| 9.4.7.4             | Debug Request During Waiting, Halted or Stopped State            | 9-39           |

| 9.4.7.5             | Software Request During Normal Activity                          | 9-39           |

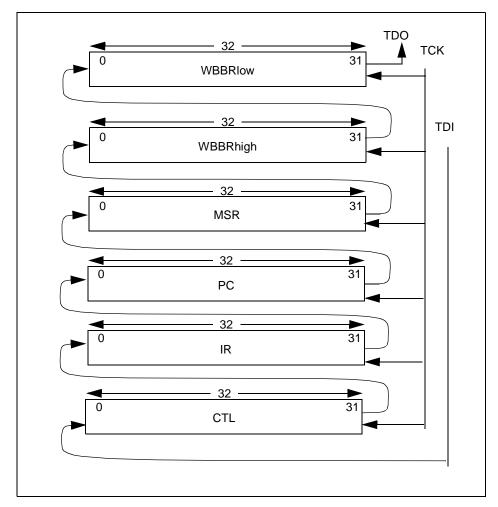

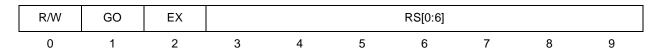

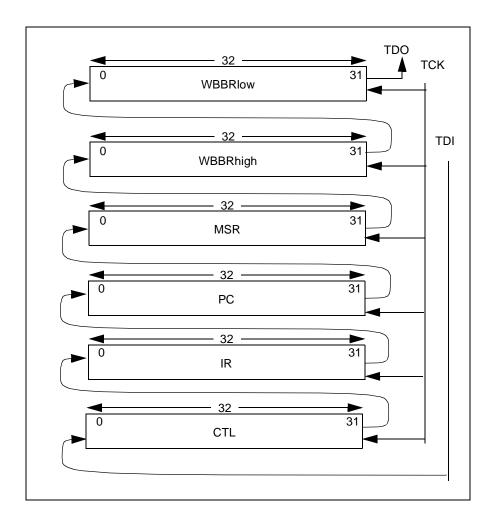

| 9.4.8               | CPU Status and Control Scan Chain Register (CPUSCR)              | 9-39           |

| 9.4.8.1             | Instruction Register (IR)                                        | 9-40           |

| 9.4.8.2             | Control State Register (CTL)                                     | 9-41           |

| 9.4.8.3             | Program Counter Register (PC)                                    | 9-44           |

| 9.4.8.4             | Write-Back Bus Register (WBBRlow, WBBRhigh)                      | 9-44           |

| 9.4.8.5             | Machine State Register (MSR)                                     | 9-45           |

| 9.4.9               | Reserved Registers (Reserved)                                    | 9-45           |

| 9.5                 | Watchpoint Support                                               | 9-45           |

| 9.6                 | Basic Steps for Enabling, Using, and Exiting External Debug Mode | 9-46           |

| 9.7                 | Parallel Signature Unit                                          |                |

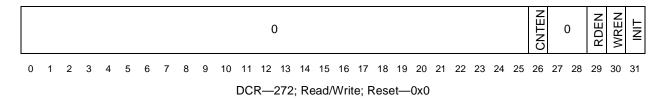

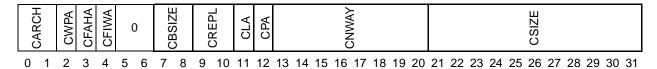

| 9.7.1               | Parallel Signature Control Register (PSCR)                       | 9-48           |

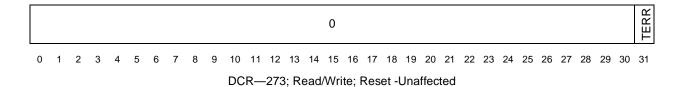

| 9.7.2               | Parallel Signature Status Register (PSSR)                        | 9-49           |

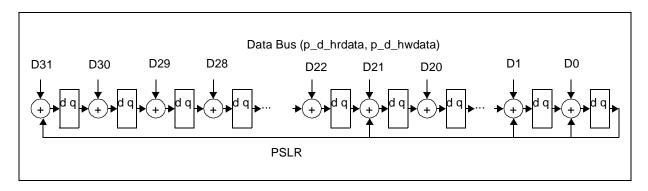

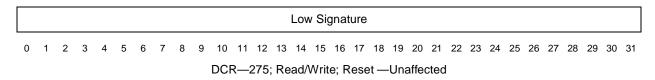

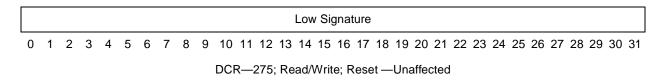

| 9.7.3               | Parallel Signature Low Register (PSLR)                           | 9-50           |

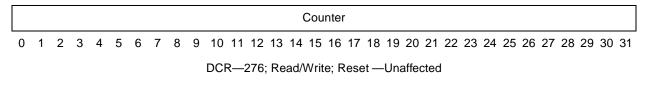

| 9.7.4               | Parallel Signature Counter Register (PSCTR)                      | 9-50           |

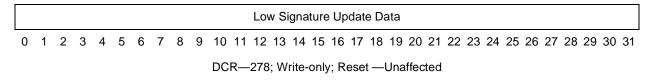

| 9.7.5               | Parallel Signature Update Low Register (PSULR)                   | 9-50           |

|                     |                                                                  |                |

Appendix A Register Summary

Appendix B Revision History

**Glossary**

e200z1 Power Architecture Core Reference Manual, Rev. 0

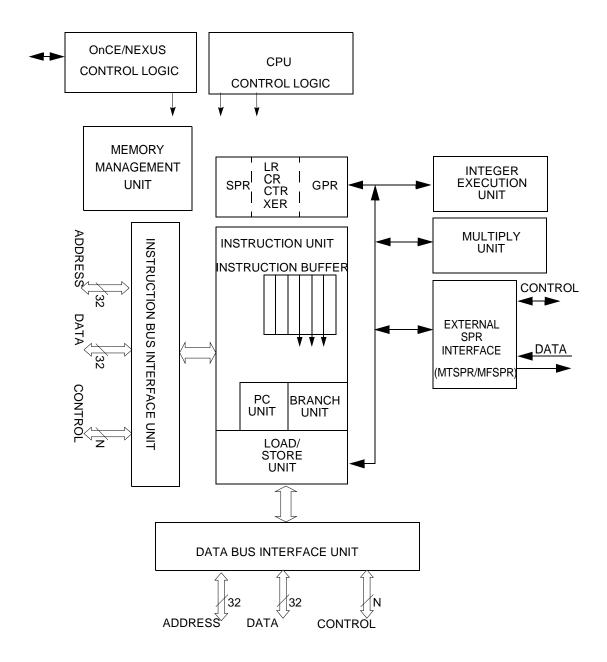

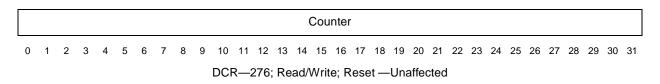

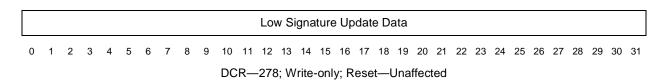

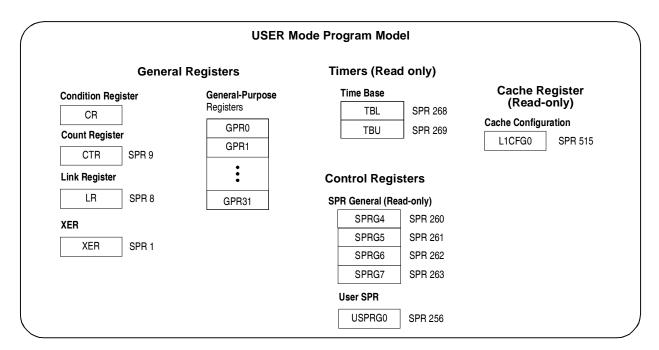

| e200z1 Block Diagram                                                                                                                    | 2-2 ters (DCRs) 2-3                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| <ul> <li>e200 Supervisor Mode Program Model Device Control Register</li> <li>e200 User Mode Program Model</li></ul>                     | zers (DCRs) 2-3 2-3 2-8 2-10 2-10 2-11 2-11 2-12 2-14 2-15 |

| <ul> <li>2-3 e200 User Mode Program Model</li> <li>2-4 Machine State Register (MSR)</li> <li>2-5 Processor ID Register (PIR)</li> </ul> | 2-3 2-8 2-10 2-10 2-11 2-11 2-12 2-14 2-15                 |

| <ul> <li>2-3 e200 User Mode Program Model</li> <li>2-4 Machine State Register (MSR)</li> <li>2-5 Processor ID Register (PIR)</li> </ul> | 2-3 2-8 2-10 2-10 2-11 2-11 2-12 2-14 2-15                 |

| 2-5 Processor ID Register (PIR)                                                                                                         | 2-10 2-10 2-11 2-11 2-12 2-14 2-15                         |

| $\mathcal{E}$                                                                                                                           |                                                            |

|                                                                                                                                         |                                                            |

| 2-6 Processor Version Register (PVR)                                                                                                    |                                                            |

| 2-7 System Version Register (SVR)                                                                                                       |                                                            |

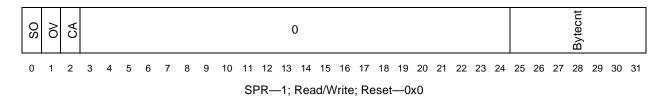

| 2-8 Integer Exception Register (XER)                                                                                                    |                                                            |

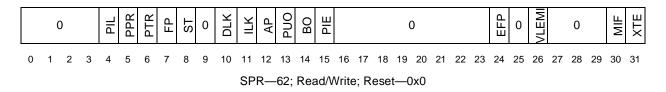

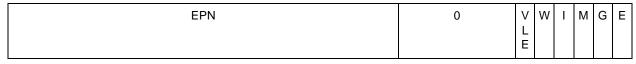

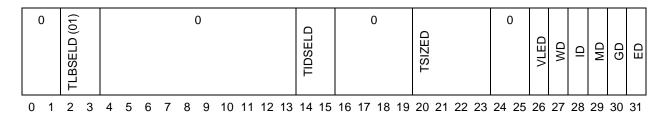

| 2-9 Exception Syndrome Register (ESR)                                                                                                   | 2-15                                                       |

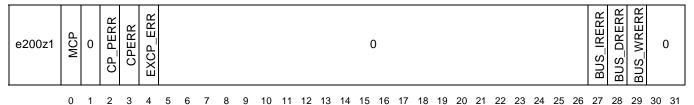

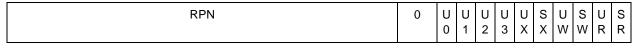

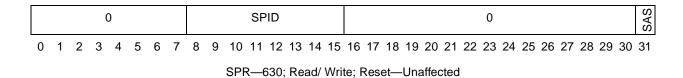

| 2-10 Machine Check Syndrome Register (MCSR)                                                                                             |                                                            |

| 2-11 Timer Control Register (TCR)                                                                                                       | 2 17                                                       |

| 2-12 Timer Status Register (TSR)                                                                                                        |                                                            |

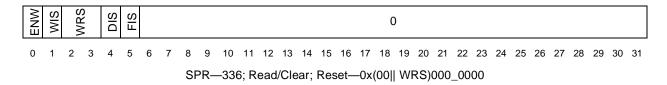

| 2-13 Hardware Implementation Dependent Register 0 (HID0)                                                                                | 2-18                                                       |

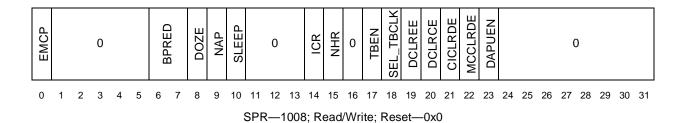

| 2-14 Hardware Implementation Dependent Register 1 (HID1)                                                                                | 2-20                                                       |

| 2-15 Branch Unit Control and Status Register (BUCSR)                                                                                    | 2-21                                                       |

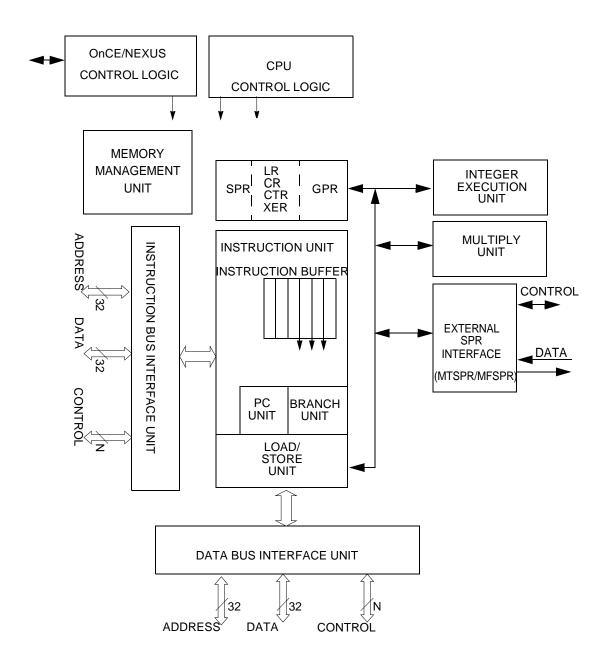

| 4-1 e200z1 Block Diagram                                                                                                                | 4-2                                                        |

| 4-2 Pipeline Diagram                                                                                                                    | 4-5                                                        |

| 4-3 e200 Instruction Buffers                                                                                                            | 4-6                                                        |

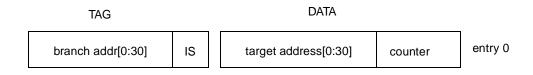

| 4-4 e200 Branch Target Buffer                                                                                                           | 4-8                                                        |

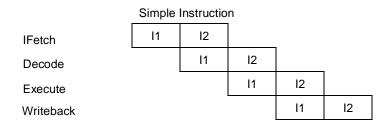

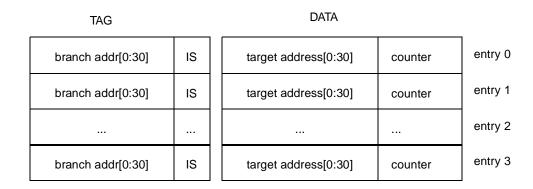

| 4-5 Basic Pipeline Flow, Single Cycle Instructions                                                                                      | 4-8                                                        |

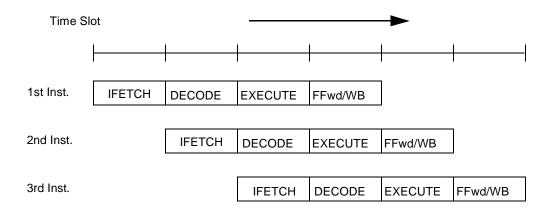

| 4-6 A Load Followed By A Dependent Add Instruction                                                                                      |                                                            |

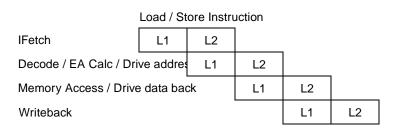

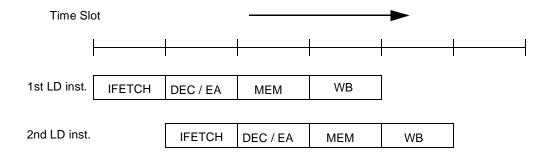

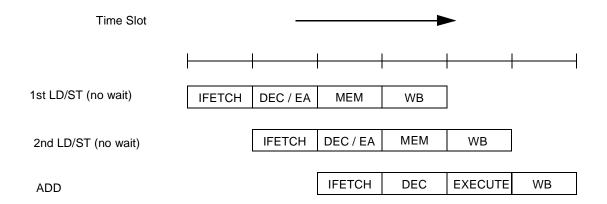

| 4-7 Back-to-back Load Instructions                                                                                                      | 4-9                                                        |

| 4-8 A Load Followed By A Dependent Store Instruction                                                                                    | 4-10                                                       |

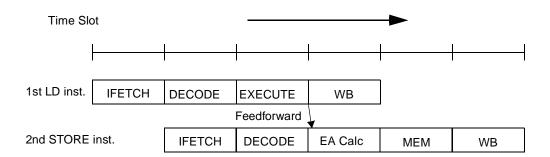

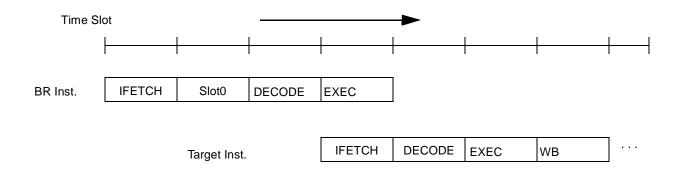

| 4-9 Basic Pipeline Flow, Branch Instructions                                                                                            | 4-10                                                       |

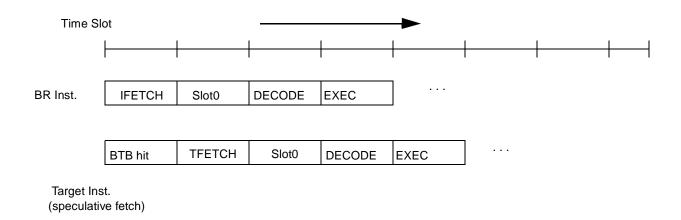

| 4-10 Basic Pipeline Flow, Branch Speculation                                                                                            | 4-11                                                       |

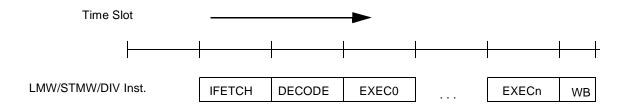

| 4-11 Basic Pipeline Flow, Multi-cycle Instructions                                                                                      |                                                            |

| 4-12 Pipelined Load/Store Instructions                                                                                                  | 4-12                                                       |

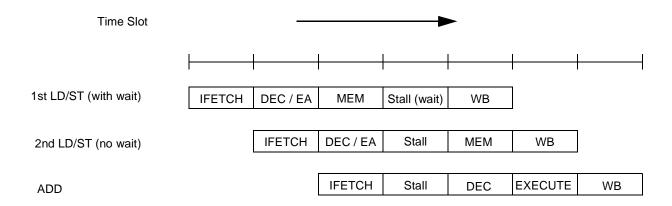

| 4-13 Pipelined Load/Store Instructions with Wait-state                                                                                  |                                                            |

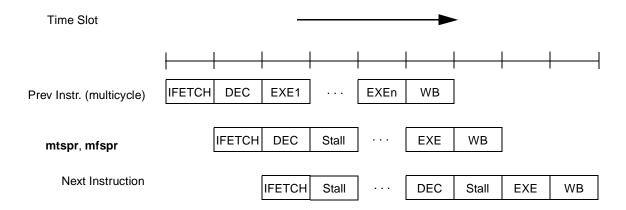

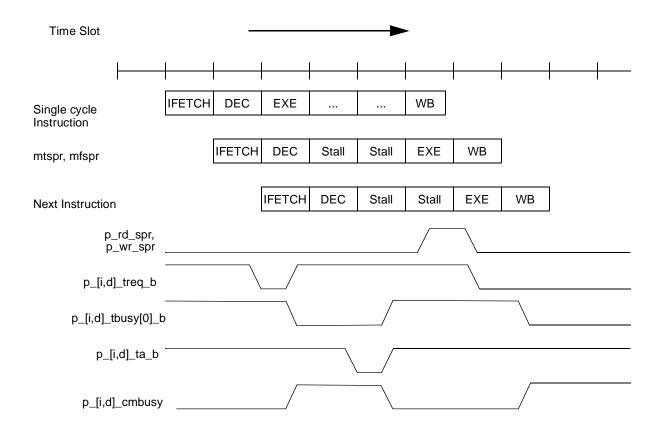

| 4-14 mtspr, mfspr Instruction Execution—(1)                                                                                             | 4-13                                                       |

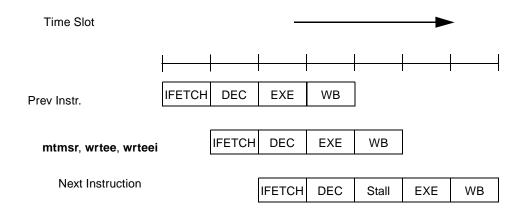

| 4-15 mtmsr, wrtee, wrteei Instruction Execution                                                                                         |                                                            |

| 4-16 DCR, MMU mtspr, mfspr and MMU Management Instruction                                                                               |                                                            |

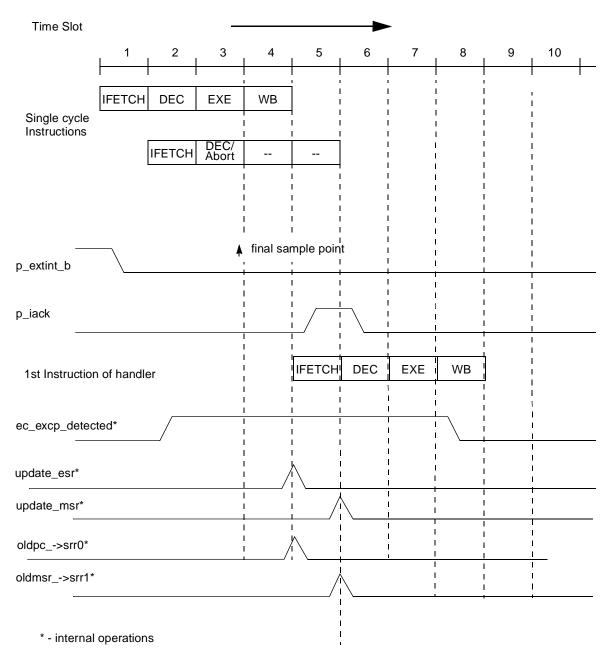

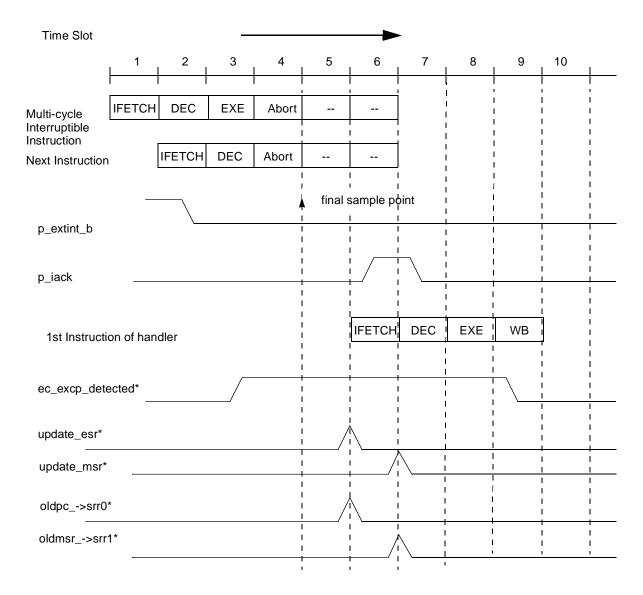

| 4-17 Interrupt Recognition and Handler Instruction Execution                                                                            |                                                            |

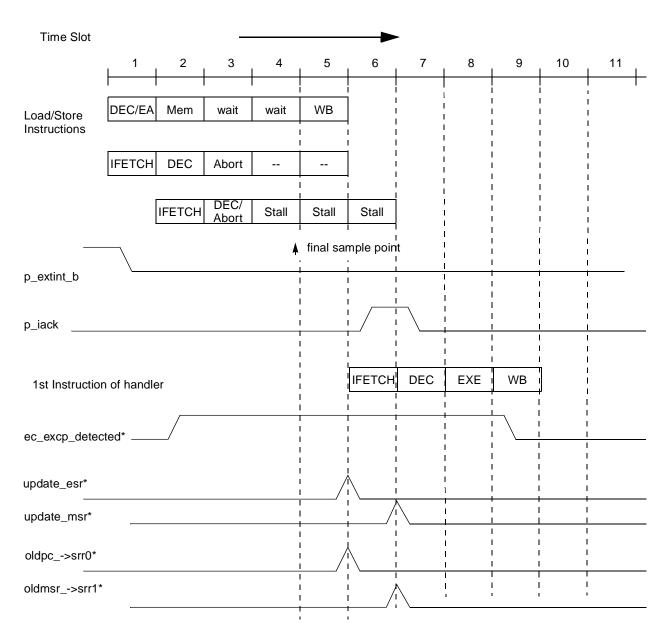

| 4-18 Interrupt Recognition and Handler Instruction Execution—Loa                                                                        |                                                            |

| 4-19 Interrupt Recognition and Handler Instruction Execution—Mu                                                                         |                                                            |

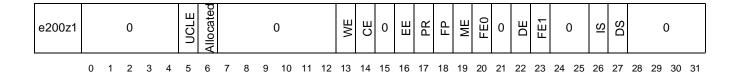

| 5-1 Exception Syndrome Register (ESR)                                                                                                   |                                                            |

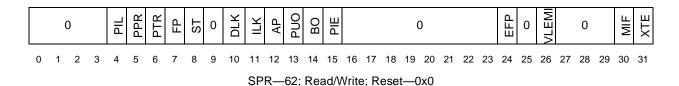

| 5-2 Machine State Register (MSR)                                                                                                        |                                                            |

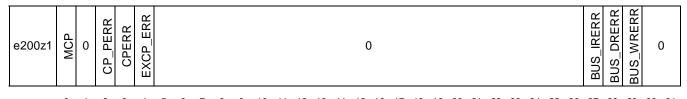

| 5-3 Machine Check Syndrome Register (MCSR)                                                                                              | 5-7                                                        |

| Figure | F F                                                     | Page |

|--------|---------------------------------------------------------|------|

| Number | Title Nun                                               | nber |

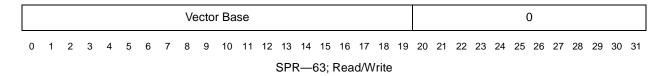

| 5-4    | e200 Interrupt Vector Prefix Register (IVPR)            | 5-9  |

| 5-5    | e200 Interrupt Vector Addresses                         | 5-9  |

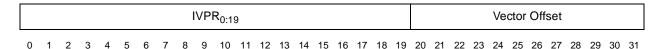

| 6-1    | Virtual Address and TLB-Entry Compare Process           | 6-2  |

| 6-2    | Effective to Real Address Translation Flow              | 6-3  |

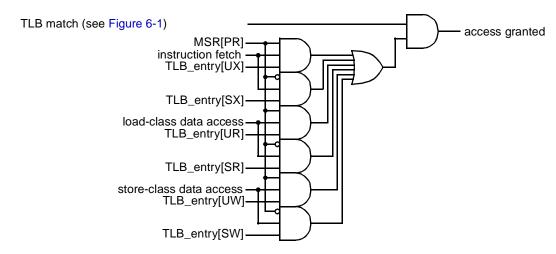

| 6-3    | Granting of Access Permission                           |      |

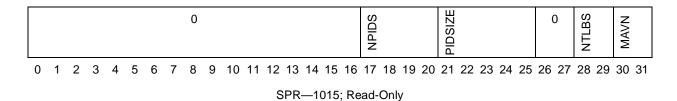

| 6-4    | MMU Configuration Register (MMUCFG)                     | 6-6  |

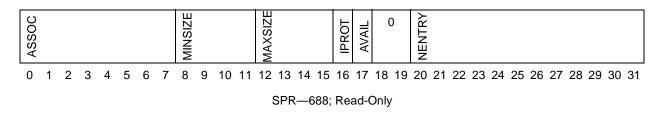

| 6-5    | TLB0 Configuration Register (TLB0CFG)                   | 6-7  |

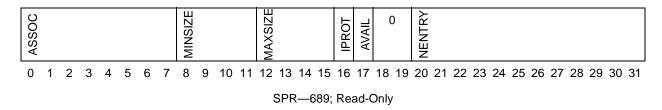

| 6-6    | TLB1 Configuration Register (TLB1CFG)                   | 6-8  |

| 6-7    | DEAR Register                                           | 6-14 |

| 6-8    | MMU Control and Status Register 0 (MMUCSR0)             | 6-15 |

| 6-9    | MMU Assist Register 0 (MAS0)                            | 6-16 |

| 6-10   | MMU Assist Register 1 (MAS1)                            | 6-16 |

| 6-11   | MMU Assist Register 2 (MAS2)                            | 6-18 |

| 6-12   | MMU Assist Register 3 (MAS3)                            | 6-19 |

| 6-13   | MMU Assist Register 4 (MAS4)                            | 6-19 |

| 6-14   | MMU Assist Register 6 (MAS6)                            | 6-20 |

| 6-15   | MMU Assist Registers Summary                            |      |

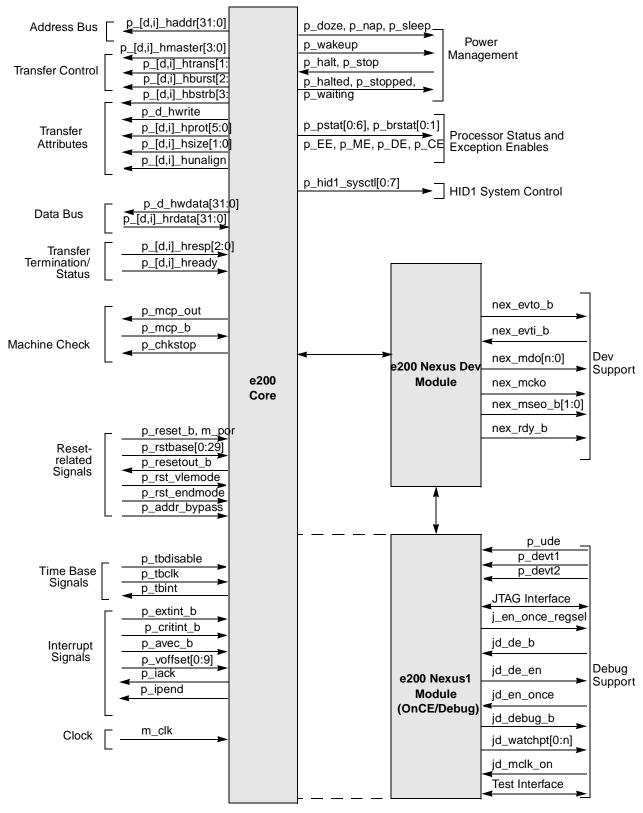

| 7-1    | e200z1 Signal Groups                                    | 7-3  |

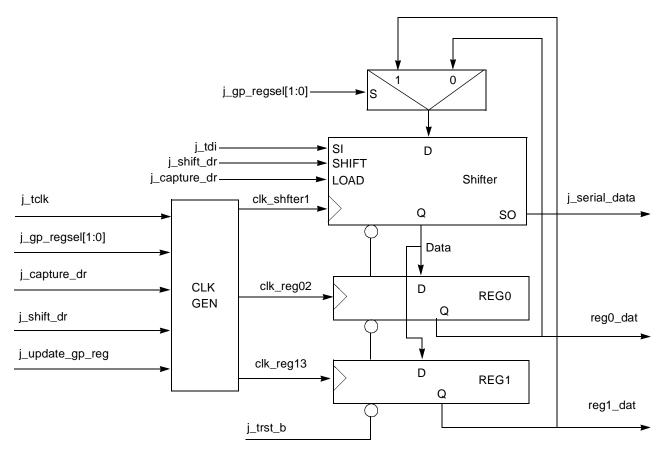

| 7-2    | Example External JTAG Register Design                   | 7-34 |

| 7-3    | Basic Read Transfers                                    | 7-37 |

| 7-4    | Read Transfer with Wait-State                           | 7-39 |

| 7-5    | Basic Write Transfers                                   | 7-40 |

| 7-6    | Write Transfer with Wait-State                          | 7-42 |

| 7-7    | Single Cycle Read and Write Transfers                   | 7-43 |

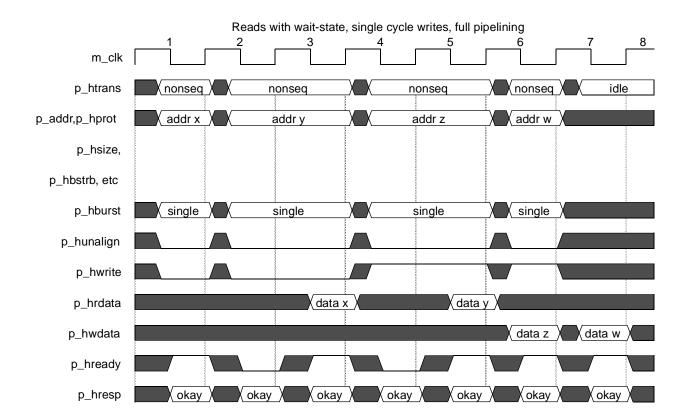

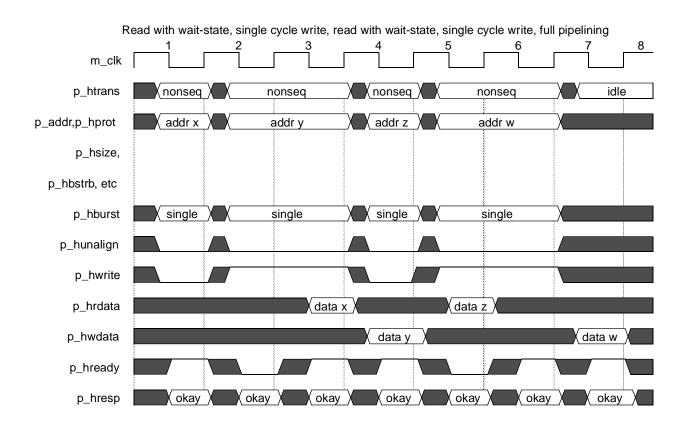

| 7-8    | Single Cycle Read and Write Transfers—2                 | 7-44 |

| 7-9    | Multi-Cycle Read and Write Transfers                    | 7-45 |

| 7-10   | Multi-Cycle Read and Write Transfers—2                  | 7-46 |

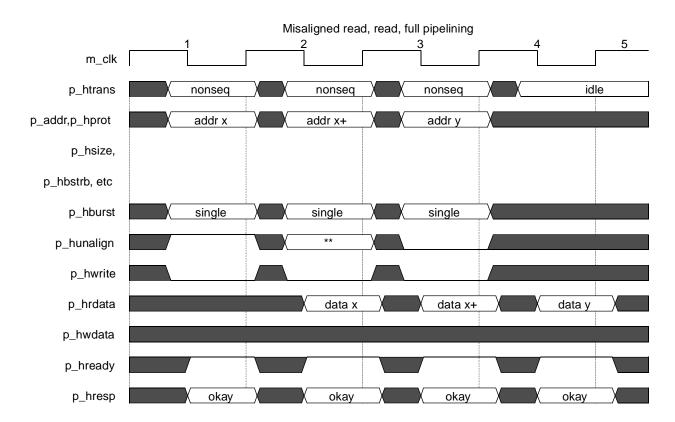

| 7-11   | Misaligned Read Transfer                                | 7-47 |

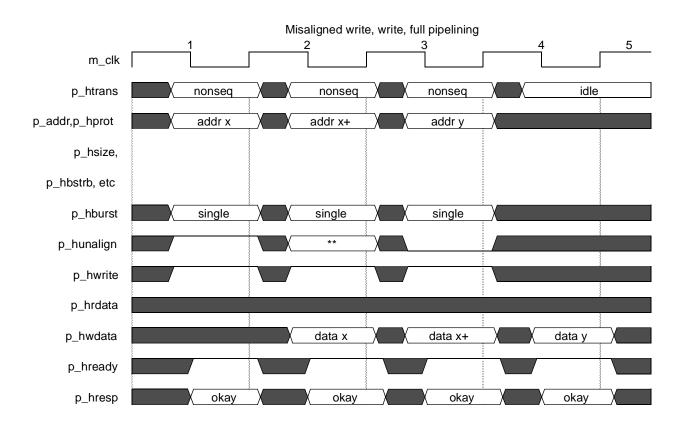

| 7-12   | Misaligned Write Transfer                               | 7-48 |

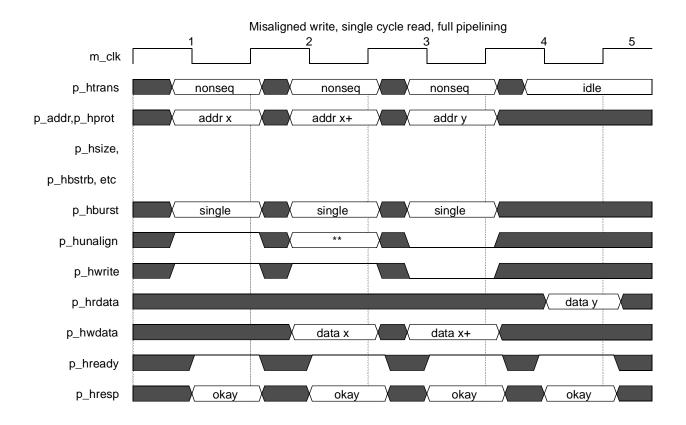

| 7-13   | Misaligned Write, Single Cycle Read Transfer            | 7-49 |

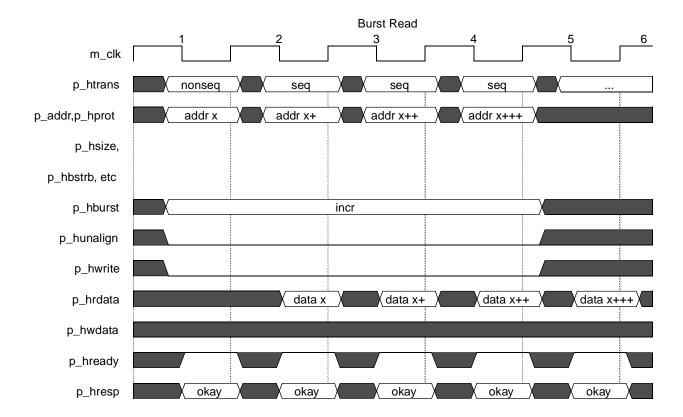

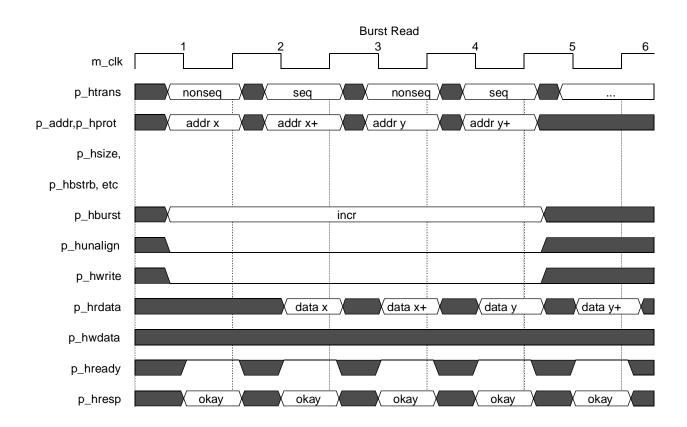

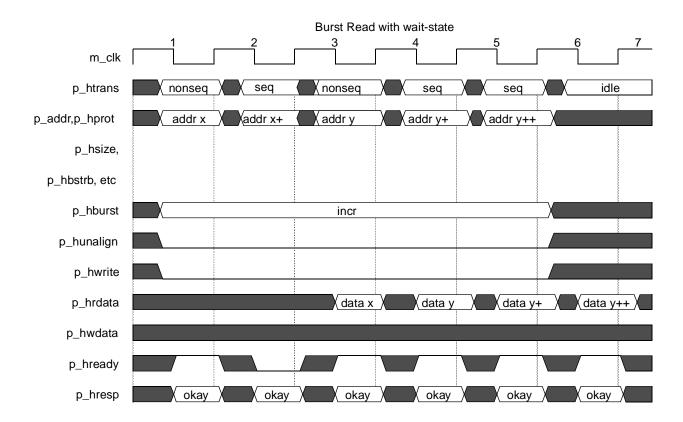

| 7-14   | Burst Read Transfer                                     |      |

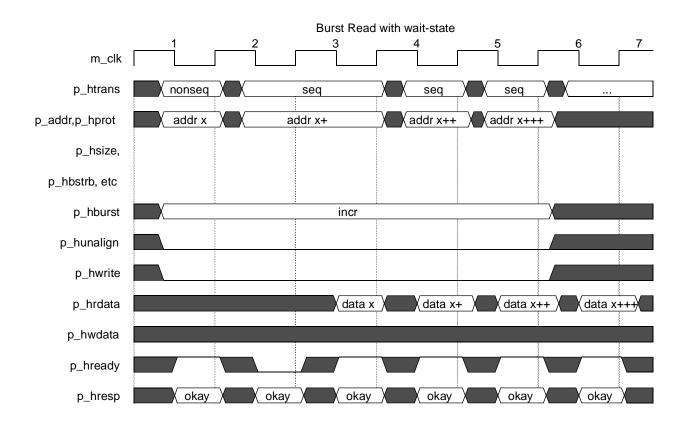

| 7-15   | Burst Read with Wait-State Transfer                     | 7-51 |

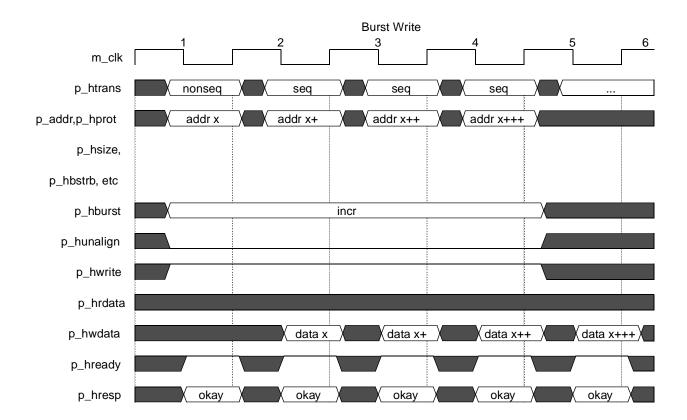

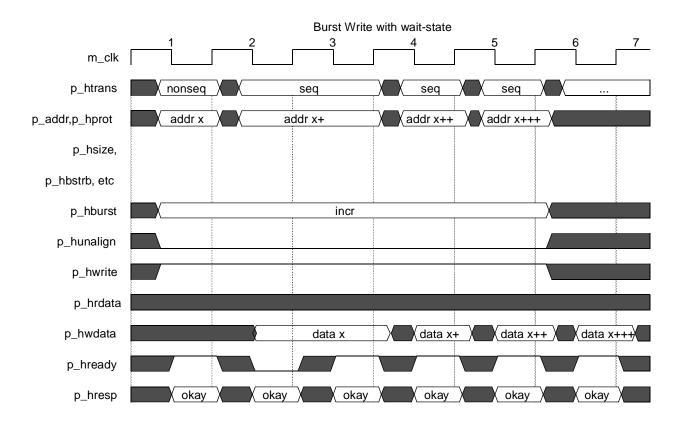

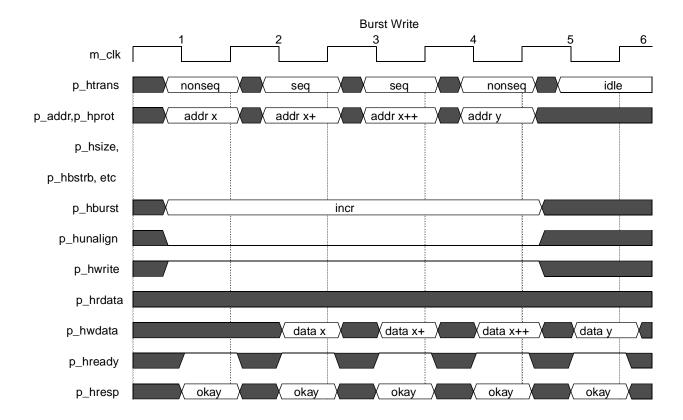

| 7-16   | Burst Write Transfer                                    | 7-52 |

| 7-17   | Burst Write with Wait-State Transfer                    | 7-53 |

| 7-18   | Burst Read Transfers                                    | 7-54 |

| 7-19   | Burst Read with Wait-State Transfer, Retraction         | 7-55 |

| 7-20   | Burst Write Transfers, Single Beat Burst                | 7-56 |

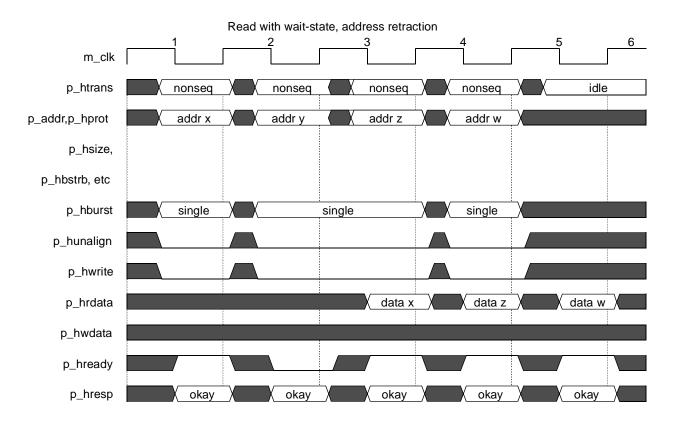

| 7-21   | Read Transfer with Wait-State, Address Retraction       |      |

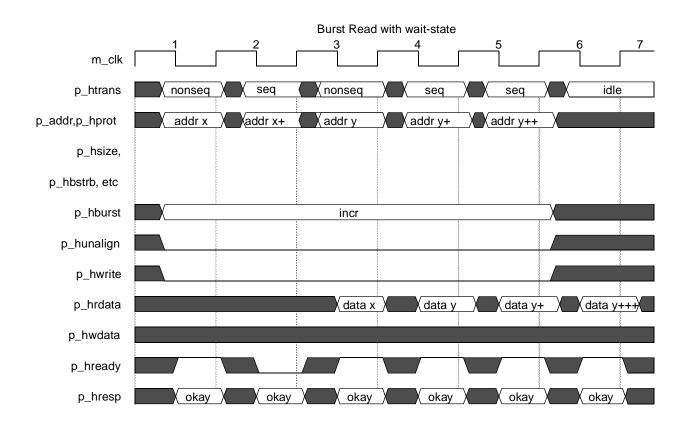

| 7-22   | Burst Read with Wait-State Transfer, Retraction         |      |

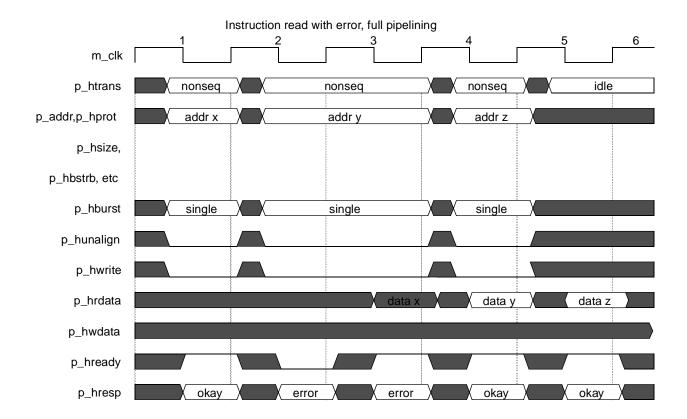

| 7-23   | Read and Write Transfers, Instr. Read Error Termination |      |

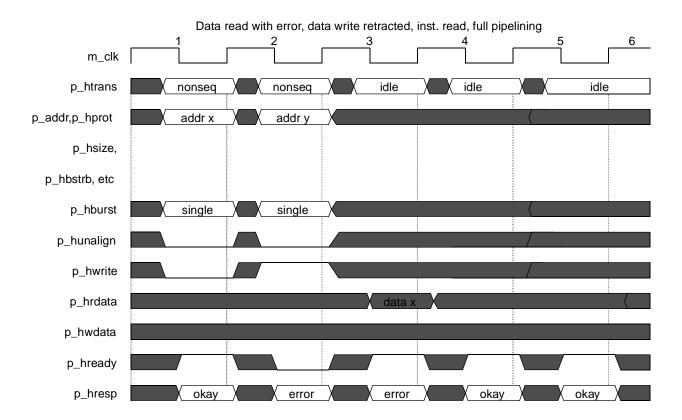

| 7-24   | Data Read Error Termination                             |      |

| Figure       |                                                     | Page   |

|--------------|-----------------------------------------------------|--------|

| Number       | Title                                               | Number |

| 7-25         | Misaligned Write Error Termination                  | 7-61   |

| 7-26         | Wakeup Control Signal ( <i>p_wakeup</i> )           | 7-61   |

| 7-27         | Interrupt Interface Input Signals                   | 7-62   |

| 7-28         | e200 Interrupt Pending Operation                    | 7-62   |

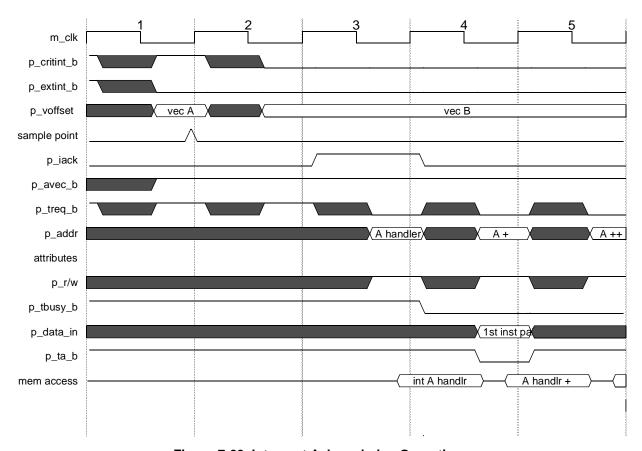

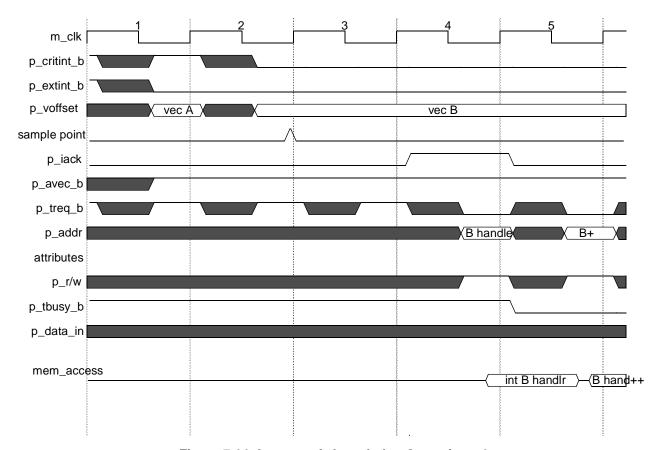

| 7-29         | Interrupt Acknowledge Operation                     | 7-63   |

| 7-30         | Interrupt Acknowledge Operation—2                   | 7-64   |

| 7-31         | Time Base Input Timing                              | 7-65   |

| 7-32         | Test Clock Input Timing                             | 7-65   |

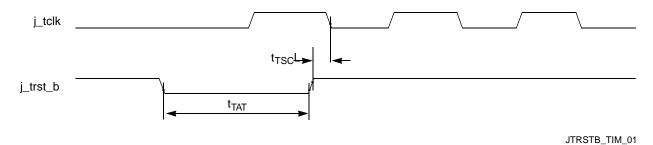

| 7-33         | <i>j_trst_b</i> Timing                              | 7-65   |

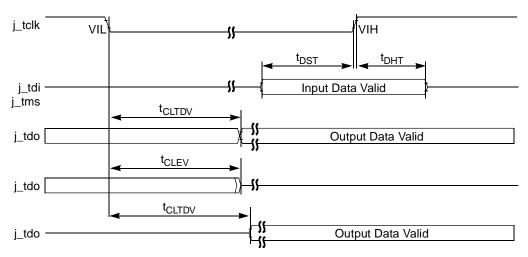

| 7-34         | Test Access Port Timing                             | 7-66   |

| 9-1          | e200 Debug Resources                                | 9-3    |

| 9-2          | DBCNT Register                                      |        |

| 9-3          | DBCR0 Register                                      | 9-10   |

| 9-4          | DBCR1 Register                                      | 9-13   |

| 9-5          | DBCR2 Register                                      |        |

| 9-6          | DBCR3 Register                                      |        |

| 9-7          | DBSR Register                                       |        |

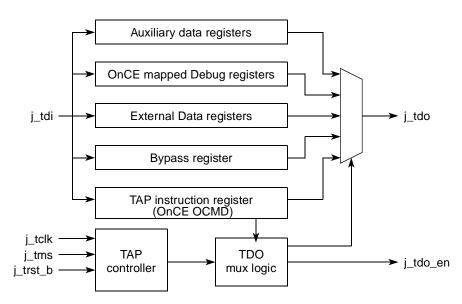

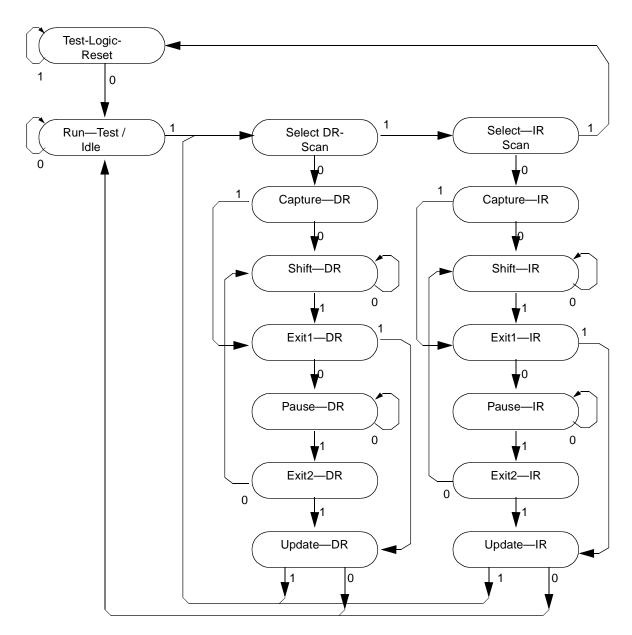

| 9-8          | OnCE TAP Controller and Registers                   |        |

| 9-9          | e200 OnCE Controller and Serial Interface           |        |

| 9-10         | OnCE Status Register                                |        |

| 9-11         | OnCE Command Register                               |        |

| 9-12         | OnCE Control Register                               |        |

| 9-13         | CPU Scan Chain Register (CPUSCR)                    |        |

| 9-14         | Control State Register (CTL)                        |        |

| 9-15         | Parallel Signature Control Register (PSCR)          |        |

| 9-16         | Parallel Signature Status Register (PSSR)           |        |

| 9-17         | Parallel Signature Low Register (PSLR)              |        |

| 9-18         | Parallel Signature Counter Register (PSCTR)         |        |

| 9-19         | Parallel Signature Update Low Register (PSULR)      |        |

| A-1          | e200 User Mode Registers                            |        |

| A-2          | e200 Supervisor Mode Registers                      |        |

| A-3          | e200 Supervisor Mode Device Control Registers (DCR) |        |

| A-4          | Machine State Register (MSR)                        |        |

| A-5          | Processor ID Register (PIR)                         |        |

| A-6          | Processor Version Register (PVR)                    |        |

| A-7          | System Version Register (SVR)                       |        |

| A-8          | Integer Exception Register (XER)                    |        |

| A-9          | Exception Syndrome Register (ESR)                   |        |

| A-10         | Machine Check Syndrome Register (MCSR)              |        |

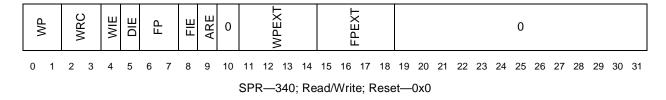

| A-10<br>A-11 | Timer Control Register (TCR)                        |        |

| A-11<br>A-12 | Timer Status Register (TSR)                         |        |

| A-12         | Timer Datus Register (TDR)                          |        |

e200z1 Power Architecture Core Reference Manual, Rev. 0

| Figure<br>Number | Title                                               | Page<br>Number |  |

|------------------|-----------------------------------------------------|----------------|--|

| A-13             | Hardware Implementation Dependent Register 0 (HID0) | A-4            |  |

| A-14             | Hardware Implementation Dependent Register 1 (HID1) | A-4            |  |

| A-15             | Branch Unit Control and Status Register (BUCSR)     | A-4            |  |

| A-16             | Context Control Register (CTXCR)                    | A-5            |  |

| A-17             | e200 Interrupt Vector Offset Register (IVOR)        | A-5            |  |

| A-18             | DBCNT Register                                      | A-5            |  |

| A-20             | DBCR1 Register                                      | A-5            |  |

| A-21             | DBCR2 Register                                      | A-5            |  |

| A-22             | DBCR3 Register                                      | A-5            |  |

| A-23             | DBSR Register                                       | A-6            |  |

| A-24             | OnCE Status Register                                | A-6            |  |

| A-25             | OnCE Command Register                               | A-6            |  |

| A-26             | OnCE Control Register                               | A-6            |  |

| A-27             | CPU Scan Chain Register (CPUSCR)                    | A-7            |  |

| A-28             | Control State Register (CTL)                        | A-7            |  |

| A-29             | L1 Cache Configuration Register 0 (L1CFG0)          | A-7            |  |

| A-30             | MMU Configuration Register (MMUCFG)                 | A-8            |  |

| A-31             | TLB Configuration Registers (TLB0CFG, TLB1CFG)      | A-8            |  |

| A-32             | MMU Control and Status Register 0 (MMUCSR0)         | A-8            |  |

| A-34             | Parallel Signature Control Register (PSCR)          | A-9            |  |

| A-33             | MMU Assist Registers Summary                        | A-9            |  |

| A-35             | Parallel Signature Status Register (PSSR)           | A-10           |  |

| A-36             | Parallel Signature Low Register (PSLR)              | A-10           |  |

| A-37             | Parallel Signature Counter Register (PSCTR)         | A-10           |  |

| A-38             | Parallel Signature Update Low Register (PSULR)      | A-10           |  |

| Table<br>Number | Title                                            | Page<br>Number |

|-----------------|--------------------------------------------------|----------------|

| 2-1             | MSR Field Descriptions                           | 2-8            |

| 2-2             | PIR Field Descriptions                           | 2-10           |

| 2-3             | PVR Field Descriptions                           | 2-10           |

| 2-4             | SVR Field Descriptions                           | 2-11           |

| 2-5             | XER Field Descriptions                           | 2-12           |

| 2-6             | ESR Field Descriptions                           | 2-12           |

| 2-7             | Machine Check Syndrome Register (MCSR)           | 2-15           |

| 2-8             | Timer Control Register Field Descriptions        | 2-16           |

| 2-9             | Timer Status Register Field Descriptions         | 2-17           |

| 2-10            | Hardware Implementation Dependent Register 0     | 2-18           |

| 2-11            | Hardware Implementation Dependent Register 1     | 2-20           |

| 2-12            | Branch Unit Control and Status Register          |                |

| 2-13            | System Response to Invalid SPR Reference         | 2-22           |

| 2-14            | Additional Synchronization Requirements for SPRs | 2-22           |

| 2-15            | Special Purpose Registers                        |                |

| 2-16            | Reset Settings for e200 Resources                |                |

| 3-1             | List of Unsupported Instructions                 | 3-1            |

| 3-2             | List of Optionally Supported Instructions        |                |

| 3-3             | Implementation-Specific Instruction Summary      | 3-2            |

| 3-4             | Instructions Sorted by Mnemonic                  | 3-9            |

| 3-5             | Instructions Sorted by Opcode                    |                |

| 4-1             | Pipeline Stages                                  | 4-4            |

| 4-2             | Instruction Class Cycle Counts                   | 4-19           |

| 4-3             | Performance Effects of Storage Operand Placement | 4-20           |

| 5-1             | Interrupt Classifications                        | 5-2            |

| 5-2             | Exceptions and Conditions                        | 5-2            |

| 5-3             | ESR Bit Settings                                 | 5-4            |

| 5-4             | MSR Bit Settings                                 | 5-6            |

| 5-5             | Machine Check Syndrome Register (MCSR)           | 5-8            |

| 5-6             | IVPR Register Fields                             | 5-9            |

| 5-7             | Hardwired Vector Offset Values                   | 5-9            |

| 5-8             | Critical Input Interrupt—Register Settings       | 5-10           |

| 5-9             | Machine Check Interrupt—Register Settings        | 5-12           |

| 5-10            | Data Storage Interrupt—Register Settings         |                |

| 5-11            | ISI Exceptions and Conditions                    |                |

| 5-12            | Instruction Storage Interrupt—Register Settings  | 5-14           |

| 5-13            | External Input Interrupt—Register Settings       |                |

| 5-14            | Alignment Interrupt—Register Settings            |                |

| Table  |                                                                    | Page   |

|--------|--------------------------------------------------------------------|--------|

| Number | Title                                                              | Number |

| 5-15   | Program Interrupt—Register Settings                                | 5-17   |

| 5-16   | Floating-Point Unavailable Interrupt—Register Settings             | 5-17   |

| 5-17   | System Call Interrupt—Register Settings                            | 5-18   |

| 5-18   | Decrementer Interrupt—Register Settings                            | 5-19   |

| 5-19   | Fixed-Interval Timer Interrupt—Register Settings                   | 5-19   |

| 5-20   | Watchdog Timer Interrupt—Register Settings                         | 5-20   |

| 5-21   | Data TLB Error Interrupt—Register Settings                         | 5-21   |

| 5-22   | Instruction TLB Error Interrupt—Register Settings                  | 5-21   |

| 5-23   | Debug Interrupt—Register Settings                                  | 5-24   |

| 5-24   | TSR Watchdog Timer Reset Status                                    | 5-25   |

| 5-25   | DBSR Most Recent Reset                                             | 5-25   |

| 5-26   | System Reset Interrupt—Register Settings                           | 5-25   |

| 5-27   | e200 Exception Priorities                                          | 5-27   |

| 5-28   | MSR Setting Due to Interrupt                                       | 5-30   |

| 6-1    | Page Size and EPN Field Comparison                                 | 6-3    |

| 6-2    | TLB Entry Bit Definitions                                          |        |

| 6-3    | MMUCFG Field Descriptions                                          | 6-6    |

| 6-4    | TLB0CFG Field Descriptions                                         | 6-7    |

| 6-5    | TLB1CFG Field Descriptions                                         | 6-8    |

| 6-6    | tlbivax EA Bit Definitions                                         | 6-11   |

| 6-7    | TLB Entry 0 Values after Reset                                     | 6-13   |

| 6-8    | MMUCSR0—MMU Control and Status Register 0                          | 6-15   |

| 6-9    | MAS0—MMU Read/Write and Replacement Control                        | 6-16   |

| 6-10   | MAS1—Descriptor Context and Configuration Control                  |        |

| 6-11   | MAS2—EPN and Page Attributes                                       |        |

| 6-12   | MAS3—RPN and Access Control                                        |        |

| 6-13   | MAS4—Hardware Replacement Assist Configuration Register            | 6-19   |

| 6-14   | MAS6—TLB Search Context Register 0                                 |        |

| 6-15   | MMU Assist Register Field Updates                                  |        |

| 6-16   | Transfer Type Encoding                                             |        |

| 7-1    | External Interface Signal Definitions                              |        |

| 7-2    | Internal Interface Signal Definitions                              | 7-7    |

| 7-3    | <i>p_hrdata</i> [31:0] Byte Address Mappings                       |        |

| 7-4    | p_d_hwdata[31:0] Byte Address Mappings                             |        |

| 7-5    | p_[d,i]_htrans[1:0] Transfer Type Encoding                         |        |

| 7-6    | $p_{l}[d,i]_{hsize}$ [1:0] Transfer Size Encoding                  |        |

| 7-7    | $p_{d,i}$ hburst[2:0] Burst Type Encoding                          |        |

| 7-8    | $p_{l}[d,i]_{l}[f]$ Protection Control Encoding                    |        |

| 7-9    | Mapping of Access Attributes to $p\_hprot[4:2]$ Protection Control |        |

| 7-10   | p_hbstrb[3:0] to Byte Address Mappings                             |        |

| 7-11   | Byte Strobe Assertion for Transfers                                |        |

|        |                                                                    |        |

| Table<br>Number | Title                                             | Page<br>Number |

|-----------------|---------------------------------------------------|----------------|

| 7-12            | Big- and Little-Endian Memory Storage             | 7-18           |

| 7-13            | <i>p_d_hresp</i> [2:0] Transfer Response Encoding | 7-20           |

| 7-14            | <i>p_i_hresp</i> [1:0] Transfer Response Encoding |                |

| 7-15            | Processor Status Encoding                         |                |

| 7-16            | Branch Prediction Status Encoding                 | 7-26           |

| 7-17            | e200 Debug/Emulation Support Signals              | 7-29           |

| 7-18            | JTAG Primary Interface Signals                    | 7-30           |

| 7-19            | JTAG Signals Used to Support External Registers   | 7-31           |

| 7-20            | JTAG General Purpose Register Select Decoding     | 7-33           |

| 7-21            | JTAG Register ID Fields                           | 7-35           |

| 7-22            | JTAG ID Register Inputs                           | 7-35           |

| 9-1             | DBCR0 Bit Definitions                             | 9-11           |

| 9-2             | DBCR1 Bit Definitions                             | 9-13           |

| 9-3             | DBCR2 Bit Definitions                             | 9-15           |

| 9-4             | DBCR3 Bit Definitions                             | 9-18           |

| 9-5             | DBSR Bit Definitions                              | 9-22           |

| 9-6             | JTAG/OnCE Primary Interface Signals               | 9-27           |

| 9-7             | OnCE Status Register Bit Definitions              | 9-31           |

| 9-8             | OnCE Command Register Bit Definitions             | 9-32           |

| 9-9             | e200 OnCE Register Addressing                     | 9-33           |

| 9-10            | OnCE Control Register Bit Definitions             | 9-35           |

| 9-11            | OnCE Register Access Requirements                 | 9-37           |

| 9-12            | Watchpoint Output Signal Assignments              | 9-45           |

| 9-13            | PSCR Field Descriptions                           |                |

| 9-14            | PSSR Field Descriptions                           | 9_49           |

Table Page Number Title Number

xx Freescale Semiconductor

## Chapter 1 e200z1 Overview

#### 1.1 Overview of the e200z1 Cores

The e200 processor family is a set of CPU cores that implement low-cost versions of the Power Architecture<sup>TM</sup> Book E architecture. e200 processors are designed for deeply embedded control applications, which require low cost solutions rather than maximum performance.

The processors integrate an integer execution unit, branch control unit, instruction fetch and load/store units, and a multi-ported register file capable of sustaining three read and two write operations per clock. Most integer instructions execute in a single clock cycle. Branch target prefetching is performed by the branch unit to allow single-cycle branches in some cases.

The e200z1 core is a single-issue, 32-bit Power Architecture Book E compliant design with 32-bit general purpose registers (GPRs). Power Architecture Book E floating-point instructions are not supported by e200 in hardware, but are trapped and may be emulated by software. All arithmetic instructions that execute in the core operate on data in the general purpose registers (GPRs).

In addition to the base Power Architecture Book E instruction set support, the core also implements the VLE (variable-length encoding) APU, providing improved code density. The VLE APU is further documented in the *PowerPC*<sup>TM</sup> *VLE APU Definition*, *Version 1.01*, a separate document.

In the remainder of this document, the e200z1 core is also referred to as the "e200z1 core" or "e200 core" when referring to the whole e200 family.

#### 1.1.1 Features

The following is a list of some of the key features of the e200z1 core:

- 32-bit Power Architecture Book E programmer's model

- Single issue, 32-bit CPU

- Implements the VLE APU for reduced code footprint

- In-order execution and retirement

- Precise exception handling

- Branch processing unit

- Dedicated branch address calculation adder

- Branch acceleration using Branch Target Buffer

- Supports independent instruction and data accesses to different memory subsystems, such as SRAM and Flash memory via independent Instruction and Data bus interface units (BIUs).

- Load/store unit

#### e200z1 Overview

- 1 cycle load latency

- Fully pipelined

- Big- and Little-endian support

- Misaligned access support

- Zero load-to-use pipeline bubbles for aligned transfers

- Power management

- Low power design

- Power saving modes: doze, nap, sleep, and wait

- Dynamic power management of execution units

- Testability

- Synthesizeable, full MuxD scan design

- ABIST/MBIST for optional memory arrays

#### 1.1.2 Microarchitecture Summary

The e200 processor utilizes a four stage pipeline for instruction execution. The Instruction Fetch (stage 1), Instruction Decode/Register file Read/Effective Address Calculation (stage 2), Execute/Memory Access (stage 3), and Register Writeback (stage 4) stages operate in an overlapped fashion, allowing single clock instruction execution for most instructions.