# **SL3ICS3001**

**UCODE HSL bumped wafer specification**

Rev. 3.0 — 6 July 2009 070730 Product data sheet addendum PUBLIC

## 1. General description

The SL3ICS3001FW is a contactless tag IC designed for tags and labels for RFID and AIDC system applications.

This specification describes electrical, physical and dimensional properties of Au-bumped, sawn wafers on FFC.

Functionality of the integrated circuit are described in <u>Ref. 2 "Data sheet - SL3ICS3001</u> UCODE HSL, document number: 0728\*\*".

## 2. Ordering information

| Table 1. Ordering information |       |                                               |   |  |  |

|-------------------------------|-------|-----------------------------------------------|---|--|--|

| Type number Package           |       | Version                                       |   |  |  |

|                               | Name  | Description                                   |   |  |  |

| SL3ICS3001FW/V1               | Wafer | Bumped, sawn wafer on FCC, 150 $\mu m,$ inked | - |  |  |

# 3. Mechanical specification

#### 3.1 Wafer

| Designation:                                                            | each wafer is scribed with batch number and wafer number |

|-------------------------------------------------------------------------|----------------------------------------------------------|

| Diameter:                                                               | 200 mm (8")                                              |

| Thickness:                                                              | 150 μm ± 15 μm                                           |

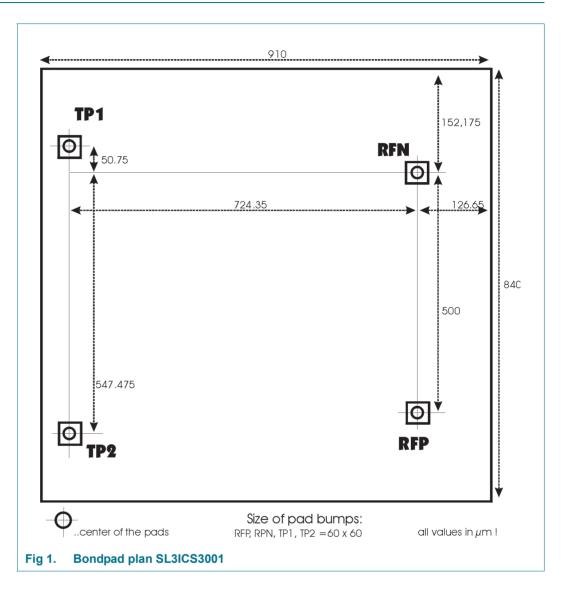

| <ul> <li>Bond pad location:</li> </ul>                                  | see Figure 1 "Bondpad plan SL3ICS3001"                   |

| Electrical connection substrate:                                        | RFN                                                      |

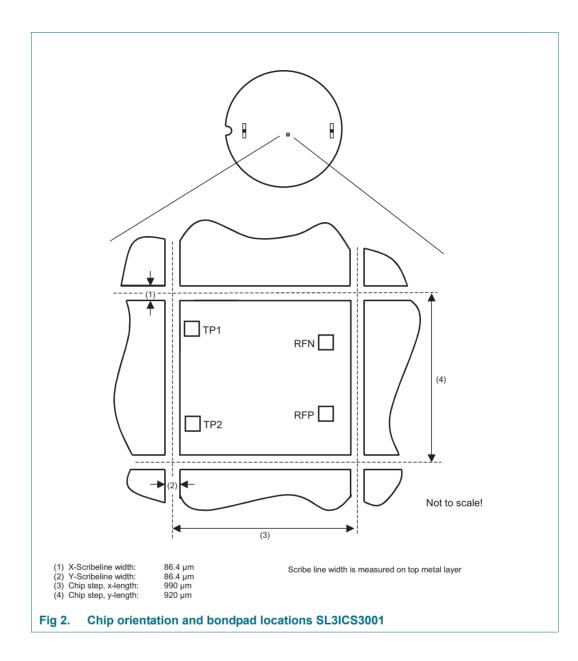

| Orientation of dies relative to notch:<br><u>locations SL3ICS3001</u> " | see Figure 2 "Chip orientation and bondpad               |

| Process:                                                                | C075EE                                                   |

| Batch size:                                                             | 24 wafers                                                |

| Minimum average yield per batch:                                        | 30 %                                                     |

#### 3.2 Wafer backside

- Material:

- Treatment:

- Roughness:

#### 3.3 Chip dimensions

- Die size without scribe:

- Die size with scribe:

- Scribe lines: ٠

### Si ground and stress release $R_a$ max. 0.5 $\mu$ m, $R_t$ max. 5 $\mu$ m

500 nm / 600 nm

35 - 80 HV 0.005

> 70 MPa

18 µm

± 3 μm

±4 μm

± 5 μm

± 1.5 μm

60 x 60 µm (pad RFN is connected to

60 x 60 µm (pads TP1 and TP2 are disconnected when the wafer is sawn)

substrate and ground)

$0.91 \text{ mm x} 0.84 \text{ mm} = 0.76 \text{ mm}^2$  $0.99 \text{ mm x} 0.92 \text{ mm} = 0.91 \text{ mm}^2$ x-line: 86.4 µm (scribe line width is measured on top metal layer) y-line: 86.4 µm (scribe line width is measured on top metal layer)

### 3.4 Passivation on front

| ٠ | Туре:     | sandwich structure     |

|---|-----------|------------------------|

| • | Material: | PSG / Nitride (on top) |

Thickness: •

#### 3.5 Au bump

| • | Bump material: | > 99.9% pure Au    |

|---|----------------|--------------------|

|   | Dump matchai.  | · 00.070 pare 7 ta |

- Bump hardness:

- Bump shear strength:

- · Bump height:

- Bump height uniformity:

- within a die:  $\pm 2 \mu m$

- within a wafer:

- wafer to wafer:

- Bump flatness:

- Bump size:

- RFP, RFN

- TP1, TP2

- · Bump size variation:

- Under bump metallization: sputtered TiW

#### 3.6 Fail die identification

All fail dies are inked according to electrical test results.

Electronic wafer mapping covers the electrical test results and additionally the results of mechanical/visual inspection.

For details please refer to <u>Ref. 1 "Data sheet - General specification for 8" wafer on</u> <u>UV-tape, document number: 1005\*\*"</u>.

### 4. Limiting values

#### Table 2. Limiting values<sup>[1][2]</sup>

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol           | Parameter                       | Conditions       | Min  | Max  | Unit |

|------------------|---------------------------------|------------------|------|------|------|

| I <sub>IN</sub>  | input current                   |                  | -    | ±10  | mA   |

| T <sub>stg</sub> | storage temperature bare die    |                  | -55  | +125 | °C   |

| P <sub>tot</sub> | power dissipation               |                  | -    | 30   | mW   |

| T <sub>amb</sub> | operating temperature           |                  | -40  | +85  | °C   |

| V <sub>ESD</sub> | electrostatic discharge voltage | Human Body Model | 3] _ | ±1   | kV   |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any conditions other than those described in the Operating Conditions and Electrical Characteristics section of this specification is not implied.

[2] This product includes circuitry specifically designed for the protection of its internal devices from the damaging effects of excessive static charge. Nonetheless, it is suggested that conventional precautions be taken to avoid applying greater than the rated maxima.

[3] For ESD measurement, the die chip has been mounted into a CDIP8 package.

<Document ID>

### 5. Characteristics

#### 5.1 DC characteristics

This section provides additional information to the data sheet (<u>Ref. 2</u>) and overrules the data sheet in case of a conflict.

# Table 3.Electrical characteristics $T_{eq} = -25$ to $85 \, \text{C}$

| $I_{amb} = -23$             | $T_{amb} = -25 \ 10 \ 85 \ C$                 |                                                  |            |        |      |       |  |

|-----------------------------|-----------------------------------------------|--------------------------------------------------|------------|--------|------|-------|--|

| Symbol                      | Parameter                                     | Conditions                                       |            | Min    | Max  | Unit  |  |

| $V_{\text{RFP},\text{min}}$ | minimum supply voltage for communcation       |                                                  | <u>[1]</u> | 1.15   | 1.55 | V     |  |

| V <sub>RFP,write</sub>      | minimum supply voltage for EEPROM programming |                                                  | <u>[1]</u> | 2.10   | 2.40 | V     |  |

| I <sub>RFP,typ</sub>        | chip current                                  | V <sub>RFP</sub> = 1.9 V                         |            | -      | 17   | μA    |  |

| R <sub>Mod</sub>            | chip input resistance                         | modulator turned on;<br>I <sub>RFP</sub> = 10 mA |            | -      | 180  | Ω     |  |

| EEPROM                      | characteristics                               |                                                  |            |        |      |       |  |

| t <sub>ret</sub>            | retention time                                | $T_{amb} \le 55 \ ^{\circ}C$                     |            | 10     | -    | year  |  |

| N <sub>endu(W)</sub>        | write endurance                               | $T_{amb} = 22 \ ^{\circ}C$                       |            | 100000 | -    | cycle |  |

[1] The measured operating voltage is the open-circuit voltage of a source with a 50  $\Omega$  output impedance.

#### 5.2 AC characteristics

This section provides additional information to the data sheet (<u>Ref. 2</u>) and overrules the data sheet in case of a conflict.

| Symbol            | Parameter               | Conditions                 |            | Min | Тур         | Max | Unit |

|-------------------|-------------------------|----------------------------|------------|-----|-------------|-----|------|

| Z <sub>867</sub>  | input impedance         | T = 22 °C,<br>f = 867 MHz  | <u>[1]</u> | -   | 41 - j865   | -   | Ω    |

| Z <sub>915</sub>  |                         | T = 22 °C,<br>f = 915 MHz  | <u>[1]</u> | -   | 34.5 - j815 | -   | Ω    |

| Z <sub>2450</sub> |                         | T = 22 °C,<br>f = 2450 MHz | <u>[1]</u> | -   | 11.5 - j295 | -   | Ω    |

| P <sub>867</sub>  | minimum operating power | f = 869.5 MHz              | [2]        | -   | –15         | -   | dBm  |

| P <sub>915</sub>  |                         | f = 915 MHz                | [2]        | -   | -14         | -   | dBm  |

| P <sub>2450</sub> | _                       | f = 2450 MHz               | [2]        | -   | -9          | -   | dBm  |

[1] Measured at typcial "minimum operating power".

[2] Values apply for operation with low modulation index (18%) and high return datarate (4x forward link).

**SL3ICS3001**

# 6. Chip orientation and bond pad locations

<Document ID>

# **SL3ICS3001**

#### UCODE HSL bumped wafer specification

### 7. References

- [1] **Data sheet** *General specification for 8" wafer on UV-tape*, document number: 1005\*\*1

- [2] Data sheet SL3/CS3001 UCODE HSL, document number: 0728\*\*

### 8. Revision history

| Table 5. Rev   | vision history                                                                               |                                                          |                       |            |

|----------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------|-----------------------|------------|

| Document ID    | Release date                                                                                 | Data sheet status                                        | Change notice         | Supersedes |

| 070730         | 20090706                                                                                     | Product data sheet addendum                              | -                     | 070710     |

| Modifications: |                                                                                              | data sheet has been redesigned to of NXP Semiconductors. | o comply with the new | 1          |

|                | <ul> <li>Legal texts have been adapted to the new company name where appropriate.</li> </ul> |                                                          |                       |            |

|                | Section 2 "Ordering                                                                          | ng information": updated                                 |                       |            |

|                | Section 3 "Mecha                                                                             | nical specification": updated                            |                       |            |

|                | Section 7 "Reference                                                                         | nces": updated                                           |                       |            |

| 070710         | October 2003                                                                                 | Preliminary data sheet addendu                           | Im                    | -          |

<sup>1. \*\* ...</sup> document version number

# 9. Legal information

#### 9.1 Data sheet status

| Document status <sup>[1][2]</sup> | Product status <sup>[3]</sup> | Definition                                                                            |

|-----------------------------------|-------------------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet      | Development                   | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet    | Qualification                 | This document contains data from the preliminary specification.                       |

| Product [short] data sheet        | Production                    | This document contains the product specification.                                     |

[1] Please consult the most recently issued document before initiating or completing a design.

[2] The term 'short data sheet' is explained in section "Definitions".

[3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL http://www.nxp.com.

### 9.2 Definitions

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

**Short data sheet** — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

### 9.3 Disclaimers

**General** — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk. **Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) may cause permanent damage to the device. Limiting values are stress ratings only and operation of the device at these or any other conditions above those given in the Characteristics sections of this document is not implied. Exposure to limiting values for extended periods may affect device reliability.

Terms and conditions of sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at <a href="http://www.nxp.com/profile/terms">http://www.nxp.com/profile/terms</a>, including those pertaining to warranty, intellectual property rights infringement and limitation of liability, unless explicitly otherwise agreed to in writing by NXP Semiconductors. In case of any inconsistency or conflict between information in this document and such terms and conditions, the latter will prevail.

**No offer to sell or license** — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from national authorities.

**Quick reference data** — The Quick reference data is an extract of the product data given in the Limiting values and Characteristics sections of this document, and as such is not complete, exhaustive or legally binding.

### 9.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

UCODE - is a trademark of NXP B.V.

## **10. Contact information**

For more information, please visit: <u>http://www.nxp.com</u>

For sales office addresses, please send an email to: salesaddresses@nxp.com

**SL3ICS3001**

## 11. Tables

| Table 1. | Ordering information1               |

|----------|-------------------------------------|

| Table 2. | Limiting values <sup>[1][2]</sup> 4 |

| Table 3. | Electrical characteristics          |

### 12. Figures

| Fig 1. | Bondpad plan SL3ICS3001                | .6 |

|--------|----------------------------------------|----|

| Fig 2. | Chip orientation and bondpad locations |    |

### 13. Contents

| 1                                                  | General description                                                                                                                                                                                                | 1                                                                                                |

|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| 2                                                  | Ordering information                                                                                                                                                                                               | 1                                                                                                |

| 3                                                  | Mechanical specification                                                                                                                                                                                           | 1                                                                                                |

| 3.1                                                | Wafer                                                                                                                                                                                                              | 1                                                                                                |

| 3.2                                                | Wafer backside                                                                                                                                                                                                     | 2                                                                                                |

| 3.3                                                | Chip dimensions                                                                                                                                                                                                    | 2                                                                                                |

| 3.4                                                | Passivation on front                                                                                                                                                                                               | 2                                                                                                |

| 3.5                                                | Au bump                                                                                                                                                                                                            | 2                                                                                                |

| 3.6                                                | Fail die identification                                                                                                                                                                                            | 3                                                                                                |

| 4                                                  | Limiting values                                                                                                                                                                                                    | 4                                                                                                |

| 5                                                  | Characteristics                                                                                                                                                                                                    | 5                                                                                                |

| 5.1                                                | DC characteristics                                                                                                                                                                                                 | 5                                                                                                |

| 5.2                                                | AC characteristics                                                                                                                                                                                                 | 5                                                                                                |

| J.Z                                                |                                                                                                                                                                                                                    | J                                                                                                |

| 6<br>6                                             | Chip orientation and bond pad locations                                                                                                                                                                            | 6                                                                                                |

|                                                    |                                                                                                                                                                                                                    | 6                                                                                                |

| 6                                                  | Chip orientation and bond pad locations                                                                                                                                                                            | 6<br>8                                                                                           |

| 6<br>7                                             | Chip orientation and bond pad locations<br>References                                                                                                                                                              | 6<br>8<br>8                                                                                      |

| 6<br>7<br>8                                        | Chip orientation and bond pad locations<br>References<br>Revision history                                                                                                                                          | 6<br>8<br>8<br>9                                                                                 |

| 6<br>7<br>8<br>9                                   | Chip orientation and bond pad locations<br>References<br>Revision history<br>Legal information                                                                                                                     | 6<br>8<br>8<br>9<br>9                                                                            |

| 6<br>7<br>8<br>9<br>9.1                            | Chip orientation and bond pad locations<br>References<br>Revision history<br>Legal information<br>Data sheet status                                                                                                | 6<br>8<br>8<br>9<br>9<br>9                                                                       |

| 6<br>7<br>8<br>9<br>9.1<br>9.2                     | Chip orientation and bond pad locations<br>References<br>Revision history<br>Legal information<br>Data sheet status                                                                                                | 6<br>8<br>8<br>9<br>9<br>9<br>9                                                                  |

| 6<br>7<br>8<br>9<br>9.1<br>9.2<br>9.3              | Chip orientation and bond pad locations<br>References                                                                                                                                                              | 6<br>8<br>9<br>9<br>9<br>9<br>9                                                                  |

| 6<br>7<br>8<br>9<br>9.1<br>9.2<br>9.3<br>9.4       | Chip orientation and bond pad locations<br>References<br>Revision history.<br>Legal information.<br>Data sheet status<br>Definitions.<br>Disclaimers<br>Trademarks.                                                | 6<br>8<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9 |

| 6<br>7<br>8<br>9<br>9.1<br>9.2<br>9.3<br>9.4<br>10 | Chip orientation and bond pad locations<br>References .<br>Revision history .<br>Legal information .<br>Data sheet status .<br>Definitions .<br>Disclaimers .<br>Trademarks .<br>Contact information .<br>Tables . | 6<br>8<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9 |

Table 4.Electrical AC characteristics5Table 5.Revision history8

SL3ICS3001 .....7

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

#### © NXP B.V. 2010.

founded by

PHILIPS

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 6 July 2009 070730 Document identifier: <Document ID>

All rights reserved.