## AH1014

# Application Hints - Standalone high speed CAN transceiver TJA1042 / TJA1043 / TJA1048 / TJA1051

Rev. 01.50 — 11 Dec 2020

### **Document information**

| Info       | Content                                                                                         |

|------------|-------------------------------------------------------------------------------------------------|

| Title      | Application Hints - Standalone high speed CAN transceiver TJA1042 / TJA1043 / TJA1048 / TJA1051 |

| Department | Systems & Applications                                                                          |

| Keywords   | HS-CAN, TJA1042, TJA1042/3, TJA1043, TJA1048, TJA1051, TJA1051/3, TJA1051/E                     |

NXP Semiconductors AH1014

**Systems & Applications, Automotive Innovation Center**

### **Summary**

The TJA1042, TJA1043, TJA1048, TJA1051 and their variants form the next generation of standalone high speed CAN transceivers from NXP Semiconductors.

The intention of this application hints document is to provide the necessary information for hardware and software designers for creation of automotive applications using the new high speed CAN transceiver generation products. It further on describes the advantages in terms of characteristics and functions offered to a system and how the system design can be simplified by replacing the 2<sup>nd</sup> by the 3<sup>rd</sup> generation HS-CAN transceivers from NXP.

### **Revision history**

| Rev   | Date       | Description                                                                                                                                                                                                                                                                                       |

|-------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01.00 | 2010-04-30 | Initial version                                                                                                                                                                                                                                                                                   |

| 01.10 | 2010-12-01 | Fig 24 Block diagram and pinning of the TJA1048 : new block diagram added with separate mode control Table 14 Average VCC supply current (assuming 500kbit/s) : TJA1048 also supports 10% VCC tolerance, re-calculation of buffer capacitance Chapter 10.3 added: Available CAN Simulation Models |

| 1.20  | 2010-12-03 | List of References updated – data sheets of TJA1042, TJA1043, TJA1048, TJA1051                                                                                                                                                                                                                    |

| 1.30  | 2014-04-04 | Chapter 6.9; Software flow (TJA1043): Figure 41 adapted Chapter 10.2.3; Upgrading Hints TJA1041A – TJA1043: new checkpoint inserted on transition from Low Power Mode to Normal Mode operation                                                                                                    |

| 1.40  | 2015-04-27 | Chapter 6.6, Software flow (TJA1043) extended with alternative bus failure detection strategy                                                                                                                                                                                                     |

| 1.50  | 2020-12-11 | TJA1043: Power-on detection details, "best of supply" concept, Chapter 6.1 (Main features), Chapter 6.5 (PWON), Chapter 6.7 (Local failure diagnosis) References to new ISO11898-2:2016 and SAE J2284-1 to -5 standards updated List of References updated                                        |

### **Contact information**

For additional information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

### **Systems & Applications, Automotive Innovation Center**

### **Contents**

| 1.    | Introduction                                                           | 6            |

|-------|------------------------------------------------------------------------|--------------|

| 1.1   | Standalone high speed CAN transceiver products                         | 8            |

| 1.1.1 | TJA1051 – Basic high speed CAN transceiver                             |              |

| 1.1.2 | TJA1042 – High speed CAN transceiver with Standby Mode                 | 9            |

| 1.1.3 | TJA1048 – Dual high speed CAN transceiver with Standby Mode            | 9            |

| 1.1.4 | TJA1043 – High speed CAN transceiver with Sleep Mode and diagnostics   |              |

| 2.    | Basics of high speed CAN applications                                  | 11           |

| 2.1   | Example of a high speed CAN application                                |              |

| 2.2   | Power management depended high speed CAN transceiver selection         |              |

| 3.    | The TJA1051 - Basic high speed CAN transceiver                         |              |

| 3.1   | Main features                                                          |              |

| 3.2   | Operation modes                                                        |              |

| 3.2.1 | Normal Mode                                                            |              |

| 3.2.2 | Silent Mode                                                            |              |

| 3.2.3 | OFF Mode                                                               | 19           |

| 3.3   | System fail-safe features                                              | 20           |

| 3.3.1 | TXD dominant clamping detection in Normal Mode                         | 20           |

| 3.3.2 | Bus dominant clamping prevention at entering Normal Mode               | 20           |

| 3.3.3 | Undervoltage detection & recovery                                      | 21           |

| 3.4   | Hardware application                                                   | 21           |

| 4.    | The TJA1042 - High speed CAN transceiver with Standby Mode             | 24           |

| 4.1   | Main features                                                          | 24           |

| 4.2   | Operation modes                                                        | 26           |

| 4.2.1 | Normal Mode                                                            | 26           |

| 4.2.2 | Standby Mode                                                           | 27           |

| 4.2.3 | OFF Mode                                                               |              |

| 4.3   | System fail-safe features                                              |              |

| 4.3.1 | TXD dominant clamping detection in Normal Mode                         |              |

| 4.3.2 | Bus dominant clamping prevention at entering Normal Mode               |              |

| 4.3.3 | Bus dominant clamping detection in Standby Mode                        |              |

| 4.3.4 | Undervoltage detection & recovery                                      |              |

| 4.4   | Hardware application                                                   |              |

| 5.    | The TJA1048 - Dual high speed CAN transceiver with Standby Mode        | 33           |

| 5.1   | Main features                                                          |              |

| 5.2   | Operating modes                                                        |              |

| 5.2.1 | Normal Mode                                                            |              |

| 5.2.2 | Standby Mode                                                           |              |

| 5.2.3 | OFF Mode                                                               |              |

| 5.3   | Remote Wake-up (via CAN bus)                                           |              |

| 5.4   | System fail-safe features                                              |              |

| 5.4.1 | TXD dominant clamping detection in Normal Mode                         |              |

| 5.4.2 | Bus dominant clamping prevention at entering Normal Mode               |              |

| 5.4.3 | Undervoltage detection & recovery                                      |              |

| 5.5   | Hardware application                                                   |              |

| 6.    | The TJA1043 – High speed CAN transceiver with Sleep Mode & diagnostics |              |

| 6.1   | Main features                                                          |              |

| 6.2   | Operating modes                                                        |              |

|       |                                                                        | continued >> |

### **Systems & Applications, Automotive Innovation Center**

| 6.2.1  | Normal Mode                                                |     |

|--------|------------------------------------------------------------|-----|

| 6.2.2  | Listen-only Mode                                           |     |

| 6.2.3  | Standby Mode                                               | 45  |

| 6.2.4  | Sleep Mode                                                 |     |

| 6.2.5  | Go-to-Sleep Mode                                           |     |

| 6.3    | Hardware application                                       | 48  |

| 6.4    | Wakeup detection                                           |     |

| 6.5    | Flag signaling                                             |     |

| 6.6    | Bus failure diagnosis                                      |     |

| 6.7    | Local failure diagnosis                                    |     |

| 6.8    | Undervoltage detection & recovery                          |     |

| 6.9    | Software                                                   |     |

| 7.     | Hardware application of common pins                        | 71  |

| 7.1    | Power Supply Pins                                          | 71  |

| 7.1.1  | V <sub>CC</sub> pin                                        | 71  |

| 7.1.2  | Thermal load consideration for the Vcc voltage regulator   | 71  |

| 7.1.3  | Dimensioning the bypass capacitor of the voltage regulator | 72  |

| 7.1.4  | V <sub>IO</sub> pin                                        | 73  |

| 7.2    | Interface Pins                                             | 74  |

| 7.2.1  | TXD pin                                                    |     |

| 7.2.2  | RXD pin                                                    |     |

| 7.3    | Mode control pins EN / STBN / STB / S                      |     |

| 7.4    | Bus Pins CANH / CANL                                       |     |

| 8.     | EMC aspects of high speed CAN                              | 76  |

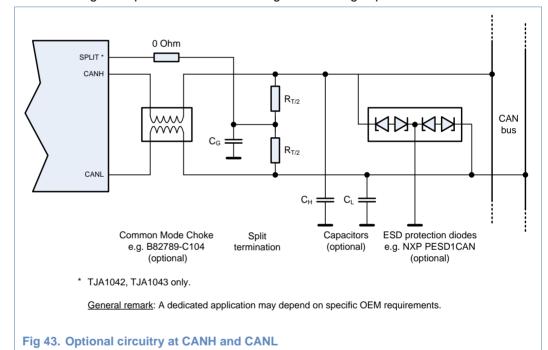

| 8.1    | Common mode choke                                          |     |

| 8.2    | Capacitors                                                 | 77  |

| 8.3    | ESD protection diodes                                      |     |

| 8.4    | Power supply buffering                                     |     |

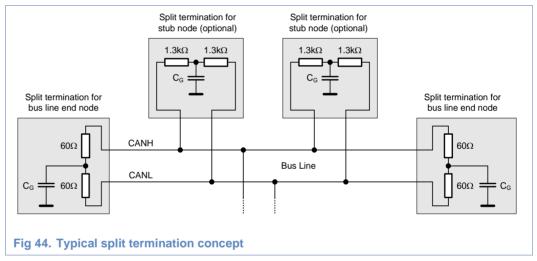

| 8.5    | Split termination concept                                  |     |

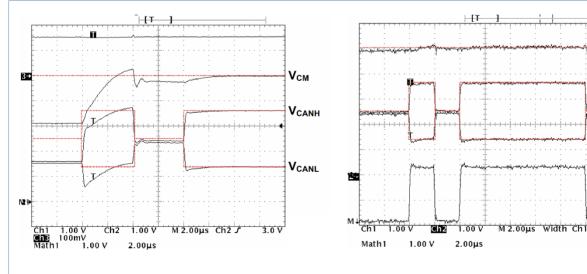

| 8.6    | Summary of EMC improvements                                |     |

| 8.7    | Common mode stabilization via SPLIT pin                    |     |

| 8.8    | GND offset and Common mode range                           |     |

| 8.9    | PCB layout rules (check list)                              |     |

| 9.     | Bus network aspects of high speed CAN                      |     |

| 9.1    | Maximum number of nodes                                    |     |

| 9.2    | Maximum bus line length                                    |     |

| 9.3    | Topology                                                   |     |

| 10.    | Appendix                                                   |     |

| 10.1   | Pin FMEA                                                   | 88  |

| 10.1.1 | TJA1051                                                    | 88  |

| 10.1.2 | TJA1042                                                    | 91  |

| 10.1.3 | TJA1048                                                    |     |

| 10.1.4 | TJA1043                                                    |     |

| 10.2   | Upgrading hints                                            |     |

| 10.2.1 | TJA1050 – TJA1051                                          |     |

| 10.2.2 | TJA1040 – TJA1042                                          |     |

| 10.2.3 | TJA1041A – TJA1043                                         |     |

| 10.3   | Simulation models                                          |     |

| 44     | Abbraviationa                                              | 445 |

continued >>

NXP Semiconductors AH1014

### **Systems & Applications, Automotive Innovation Center**

| 12.  | References        | 116 |

|------|-------------------|-----|

| 13.  | Legal information | 117 |

| 13.1 | Definitions       | 117 |

| 13.2 | Disclaimers       |     |

continued >>

AH1014 **NXP Semiconductors**

### Introduction 1.

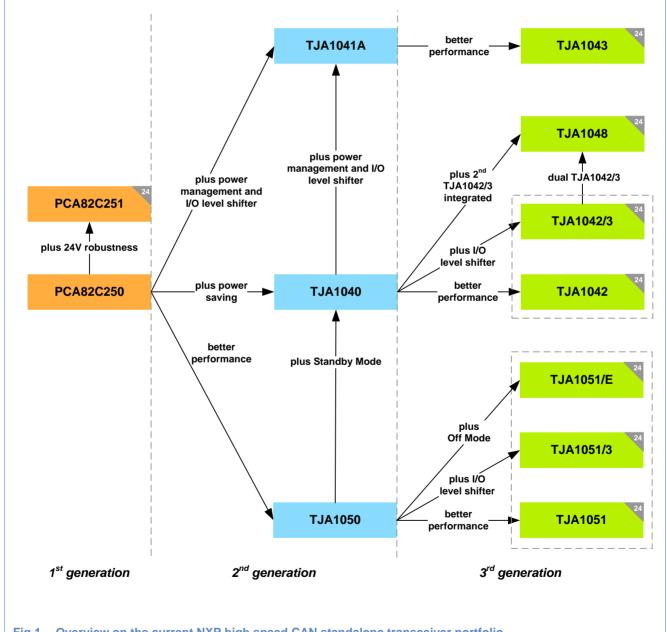

The TJA1042, TJA1043, TJA1048 and TJA1051 and their variants TJA1042/3, TJA1051/3 and TJA1051/E are the next step up from the NXP Semiconductors high speed CAN transceivers TJA1040, TJA1041A and TJA1050 (see Fig 1).

All transceivers provide the physical link between the protocol controller and the physical transmission medium according to the ISO11898-2 [13] and SAE J2284 [14] [15] [16] [17] [18]. This ensures full interoperability with other ISO11898-2 and SAE J2284 compliant transceiver products.

Fig 1. Overview on the current NXP high speed CAN standalone transceiver portfolio

NXP Semiconductors AH1014

### Systems & Applications, Automotive Innovation Center

Beside three versions offering a 100% drop-in replacement (TJA1042, TJA1043 and TJA1051) to their predecessor (TJA1040, TJA1041(A) and TJA1050) three new versions are introduced in the  $3^{rd}$  generation. The new TJA1042/3 and TJA1051/3 allow interfacing to 3V microcontrollers via a new introduced  $V_{IO}$  pin. The new TJA1051/E offers a dedicated Off Mode to completely disable the transceiver. The TJA1048 offers two integrated TJA1042/3 blocks and thus is the new dual high speed CAN standalone transceiver solution from NXP Semiconductors.

Compared to their functional predecessors the 3<sup>rd</sup> generation high speed CAN transceivers from NXP Semiconductors offer

- a significantly improved ESD robustness,

- a further reduction in electromagnetic emission (EME)

- beside an improved electromagnetic immunity (EMI),

- a higher voltage robustness in order to full support 24V applications

- and a predictable undervoltage behavior at all supply conditions

With the extended portfolio of high speed CAN transceivers NXP Semiconductors enables ECU designers to find the best application fitting standalone transceiver product in order to cover all main application specific requirements.

|              |             |                     |        | Modes       |         |       |     | Fail-safe features |                    |                        |                          |                        | Wak             | e-up           |                |                |           |

|--------------|-------------|---------------------|--------|-------------|---------|-------|-----|--------------------|--------------------|------------------------|--------------------------|------------------------|-----------------|----------------|----------------|----------------|-----------|

| HSCAN device | No. of pins | No. of CAN channels | Normal | Listen-only | Standby | Sleep | Off | TXD dominant timer | Bus dominant timer | Undervoltage detection | Short circuit protection | Temperature protection | Error detection | Remote via CAN | Local via WAKE | Host Interface | SPLIT pin |

| TJA1051      | 8           | 1                   | 4      | 4           |         |       |     | 4                  |                    | 4                      | 4                        | 1                      |                 |                |                | 5V             |           |

| TJA1051/3    | 8           | 1                   | 4      | 1           |         |       |     | 4                  |                    | 1                      | 1                        | 1                      |                 |                |                | 3-5V           |           |

| TJA1051/E    | 8           | 1                   | 4      | √           |         |       | 1   | 1                  |                    | 1                      | 1                        | 1                      |                 |                |                | 5V             |           |

| TJA1042      | 8           | 1                   | 1      |             | 1       |       |     | 1                  | 1                  | 1                      | 1                        | 1                      |                 | 1              |                | 5V             | 1         |

| TJA1042/3    | 8           | 1                   | 4      |             | 1       |       |     | 1                  | 1                  | 1                      | 1                        | 1                      |                 | 1              |                | 3-5V           |           |

| TJA1048      | 14          | 2                   | 4      |             | 1       |       |     | 1                  |                    | 1                      | <b>√</b>                 | 1                      |                 | 1              |                | 3-5V           |           |

| TJA1043      | 14          | 1                   | 4      | 1           | 1       | 1     |     | 1                  |                    | <b>√</b>               | √                        | 1                      | 1               | 1              | <b>√</b>       | 3-5V           | 1         |

Fig 2. Feature overview of 3<sup>rd</sup> generation high speed CAN standalone transceiver portfolio

**ΔH1014 NXP Semiconductors**

### 1.1 Standalone high speed CAN transceiver products

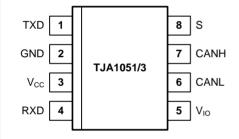

### 1.1.1 TJA1051 - Basic high speed CAN transceiver

### TJA1051 - Basic high speed CAN transceiver TXD 8 S GND CANH TJA1051 CANL $V_{CC}$ RXD 5

- Successor of the TJA1050 basic high speed CAN transceiver

- Normal Mode (transmit / receive CAN data)

- Silent Mode (receiving CAN data only)

- Undervoltage detection on pin Vcc

### TJA1051/3 - Basic high speed CAN transceiver with 3V microcontroller interface

(page 16 ff.)

(page 16 ff.)

- Variant of the TJA1051 basic high speed CAN transceiver including:

- Direct interfacing to microcontrollers with 3V to 5V supply voltage

- Undervoltage detection on pin V<sub>IO</sub>

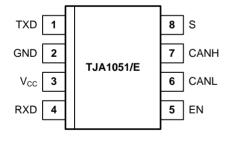

### TJA1051/E - Basic high speed CAN transceiver with Off Mode

n.c.

(page 16 ff.)

- Variant of the TJA1051 basic high speed CAN transceiver including:

- Off Mode (disabled transceiver with zero bus load)

Fig 3. Pin configuration and short functional description of the TJA1051, TJA1051/3 and TJA1051/E

NXP Semiconductors AH1014

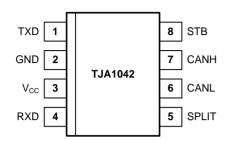

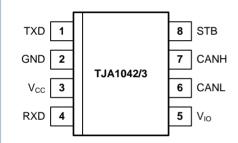

### 1.1.2 TJA1042 - High speed CAN transceiver with Standby Mode

### TJA1042 - High speed CAN transceiver with Standby Mode

(page 24 ff.)

- Successor of the TJA1040 high speed CAN transceiver

- Normal Mode (transmit / receive CAN data)

- Standby Mode (low power mode with CAN wake-up capability)

- SPLIT pin for recessive bus level stabilization

- Bus dominant time-out function in Standby Mode

- Undervoltage detection on pin V<sub>CC</sub>

## TJA1042/3 – High speed CAN transceiver with Standby Mode and 3V microcontroller interface

(page 24 ff.)

- Variant of the TJA1042 high speed CAN transceiver including:

- Direct interfacing to microcontrollers with 3V to 5V supply voltage

- Low power receiver supply in Standby Mode by V<sub>IO</sub> only

- Undervoltage detection on pin V<sub>IO</sub>

- No SPLIT pin for recessive bus level stabilization

Fig 4. Pin configuration and short functional description of the TJA1042 and TJA1042/3

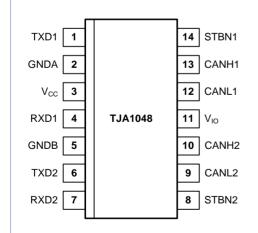

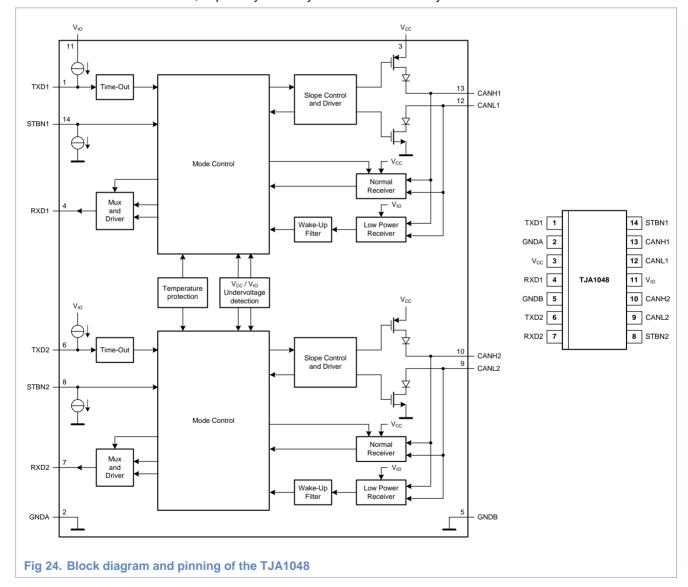

### 1.1.3 TJA1048 – Dual high speed CAN transceiver with Standby Mode

### TJA1048 - Dual high speed CAN transceiver with Standby Mode

(page 32 ff.)

- Dual CAN transceiver based on TJA1042/3

- Normal Mode (transmit / receive CAN data)

- Standby Mode (low power mode with CAN wake-up capability)

- Channel independent mode control

- Direct interfacing to microcontrollers with 3V to 5V supply voltage

- Low power receiver supply in Standby Mode by V<sub>IO</sub> only

- Undervoltage detection on pins Vcc and Vio

- Enhanced CAN wake-up pattern

Fig 5. Pin configuration and short functional description of the TJA1048

AH1014 **NXP Semiconductors**

### Systems & Applications, Automotive Innovation Center

(page 40 ff.)

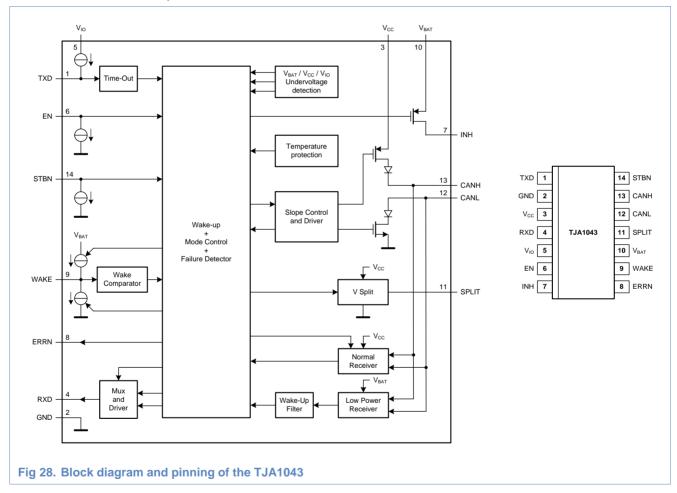

### 1.1.4 TJA1043 - High speed CAN transceiver with Sleep Mode and diagnostics

### TJA1043 - High speed CAN transceiver with Sleep Mode and diagnostics TXD 14 STBN GND 13 CANH $\mathsf{V}_{\mathsf{CC}}$ 3 12 CANL SPLIT RXD **TJA1043** $V_{\text{BAT}}$ 10 $V_{IO}$ ΕN 6 9 WAKE ERRN INH

- Successor of the TJA1041A high speed CAN transceiver

- Normal Mode (transmit / receive CAN data)

- Listen-only Mode (receiving CAN data only)

- Standby Mode (first-level low power mode INH on)

- Sleep Mode (second-level low power mode INH off)

- Local and remote wake-up with wake-up source recognition

- Direct interfacing to microcontrollers with 3V to 5V supply voltage

- SPLIT pin for recessive bus level stabilization

- Undervoltage detection on pins V<sub>BAT</sub>, V<sub>CC</sub> and V<sub>IO</sub>

- Several protection and diagnostic functions

Pin configuration and short functional description of the TJA1043

### 2. Basics of high speed CAN applications

### 2.1 Example of a high speed CAN application

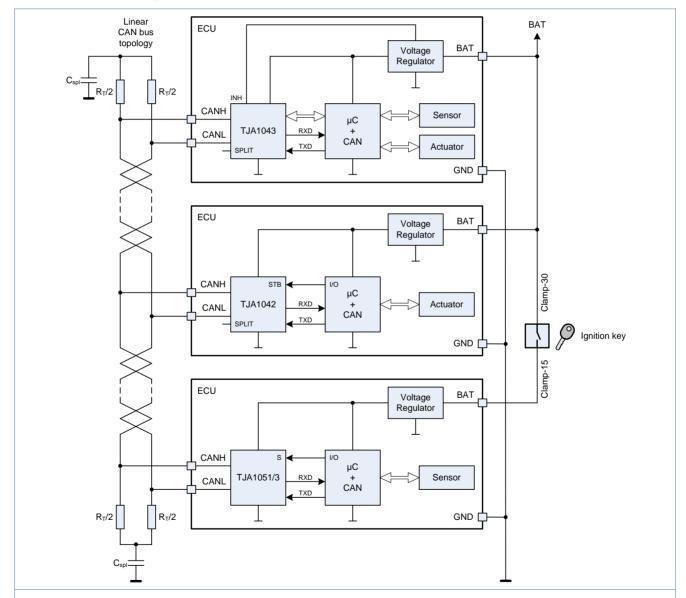

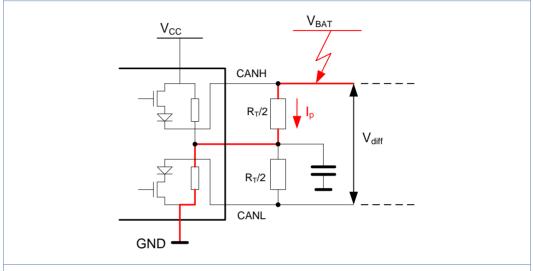

Fig 7 illustrates an example of a high speed CAN application. Several ECUs (Electronic Control Units) are connected via stubs to a linear bus topology. Each bus end is terminated with  $120\Omega$  (R<sub>T</sub>), resulting in the nominal  $60\Omega$  bus load according to ISO11898-2. The figure shows the split termination concept, which is helpful when improving the EMC of high speed CAN bus systems. The former single  $120\Omega$  termination resistor is split into two resistors of half value (R<sub>T</sub>/2) with the center tap connected to ground via the capacitor  $C_{spl}$ .

Fig 7. High speed CAN application example

The block diagram in Fig 7 describes the internal structure of an ECU. Typically, an ECU consists of a standalone transceiver (here the TJA1042, TJA1043 and TJA1051/E) and a host microcontroller with integrated CAN-controller, which are supplied by one or more voltage regulators. While the high speed CAN transceiver needs a +5 V supply to support the ISO11898-2 bus levels, new microcontroller products are increasingly using lower supply voltages like 3,3 V. In this case a dedicated 3,3 V voltage regulator is necessary for the microcontroller. The protocol controller is connected to the transceiver via a serial data output line (TXD) and a serial data input line (RXD). The transceiver is attached to the bus lines via its two bus terminals CANH and CANL, which provide differential receive and transmit capability.

Depending on the selected transceiver different mode control pins (e.g. STB, S, EN) are connected to I/O pins of the host microcontroller for operation mode control. The split termination approach can be further improved using the pin SPLIT of the TJA1042 or TJA1043 for DC stabilization of the common mode voltage (see Section 7.1).

In the case of the TJA1043 there is an additional INH signal line (indicated in Fig 7) controlling the voltage regulator. Leaving control over the voltage regulator(s) for  $V_{CC}$  and  $\mu C$  supply voltage to the TJA1043 allows for an extremely low ECU quiescent current as required in Clamp-30 applications (see Section 1.1).

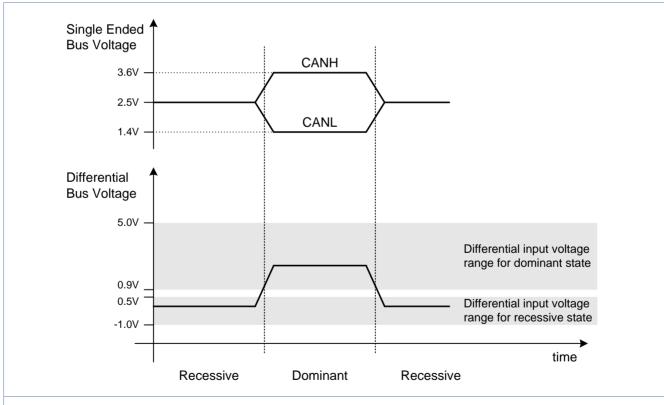

Fig 8. Nominal bus levels according to ISO11898-2

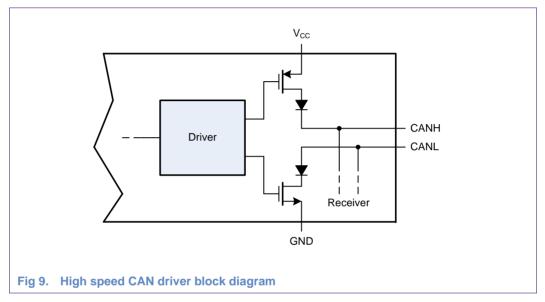

The protocol controller outputs a serial transmit data stream to the TXD input of the transceiver. An internal pull-up function within each NXP high speed CAN transceiver sets the TXD input to logic HIGH, which means that the bus output driver stays recessive in the case of a TXD open circuit condition. In the recessive state (Fig 8) the CANH and CANL pins are biased to a voltage level of  $V_{\rm CC}/2$ . If a logic LOW level is applied to TXD, the output stage is activated, generating a dominant state on the bus line (Fig 8). The output driver CANH provides a source output from  $V_{\rm CC}$  and the output driver CANL a sink output towards GND. This is illustrated in Fig 9 showing the high speed CAN driver block diagram.

If no bus node transmits a dominant bit, the bus stays in recessive state. If one or multiple bus nodes transmit a dominant bit, then the bus lines enter the dominant state overriding the recessive state (wired-AND characteristic).

The receiver converts the differential bus signal to a logic level signal, which is output at RXD. The serial receive data stream is provided to the bus protocol controller for decoding. The internal receiver comparator is always active. It monitors the bus while the bus node is transmitting a message. This is required to support the non-destructive bit-by-bit arbitration scheme of CAN.

### 2.2 Power management depended high speed CAN transceiver selection

In-vehicle high speed CAN networks come with different requirements, depending on the implemented application. First of all, high speed CAN is the ideal choice for all applications which require a high data throughput (up to 1 Mbit/s).

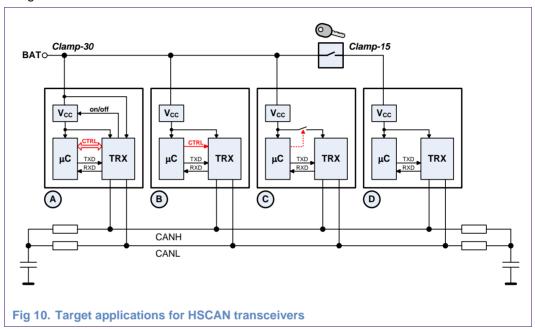

From the ECU power management point of view four different application areas can be distinguished.

**Type A – Available all time** - Applications, which have to be available all time, even when the car is parked and ignition-key is off, are permanently supplied from a permanent battery supply line, often called "Clamp-30". However, those nodes need the possibility to reduce the current consumption for power saving by control of the local ECU supply ( $V_{CC}$ ). These type A applications allow switching off the entire supply system of the ECU including the microcontroller supply while keeping the wake-up capability via CAN possible.

The TJA1043 is the first choice for these applications. It can be put into its Sleep Mode (all  $V_{CC}$  and  $V_{IO}$  supplies off), which allows reducing the total current consumption of the entire ECU down to typically 20uA, while keeping the capability to receive wake-up events from the bus and to restart the application.

**Type B – Always active microcontroller** - Those applications, which need an always-active microcontroller, are permanently supplied from the battery supply line "Clamp-30" using a continuously active V<sub>CC</sub> supply. In order to reduce the ECU power consumption, the transceiver needs to be set into a mode with reduced supply current while its supply stays active.

Here the Standby Mode of the TJA1042, TJA1042/3 and TJA1048 offers the best choice. During Standby Mode the device reduces the transceiver supply current (via VCC and VIO) to a minimum, while still monitoring the CAN bus lines for bus traffic.

If monitoring the bus traffic is not required the TJA1051/E is the best selection. The TJA1051/E can be switched into Off Mode. During Off Mode the device reduces the transceiver supply current (as in Standby Mode of the TJA1042) and additionally disengages from the bus (zero load).

Type C – Always active microcontroller & controlled transceiver supply - Dedicated applications, which need an always-active microcontroller and therefore are permanently supplied from the "Clamp-30" line, additionally come with a microcontroller controlled transceiver voltage supply. In contrast to type B applications, further current can be saved, because the transceiver becomes completely un-powered by microcontroller control. These applications require absolute passive bus behavior of the transceiver, while its voltage supply is inactive. This is important in order not to affect the remaining bus system, which might continue communication.

Most suitable for such kind of applications are the TJA1042 variants, the TJA1051 variants as well as the TJA1048. All named HSCAN transceiver types disengage from the bus, if unpowered and thus behave absolutely passive.

**Type D – Only active at ignition-key switched on** - Applications, which do not need to be available with ignition-key off, are simply switched off and become totally un-powered during ignition-key off. They are supplied from a switched battery supply line, often called "Clamp-15". This supply line is only switched on with ignition-key on. Depending on system requirements, e.g. partial communication of the still supplied nodes during ignition-key off, these un-powered nodes need to behave passively towards the remaining bus, similar to type C applications.

As for type C applications, it is recommended to use the TJA1042 variants, the TJA1051 variants as well as the TJA1048 due to their absolutely passive behavior to the bus when becoming unpowered.

15 of 118

# )

### 3. The TJA1051 - Basic high speed CAN transceiver

### 3.1 Main features

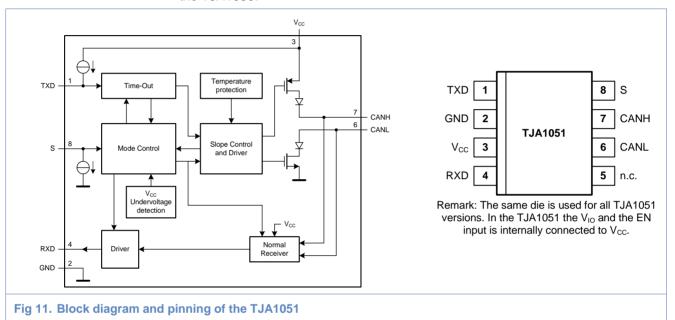

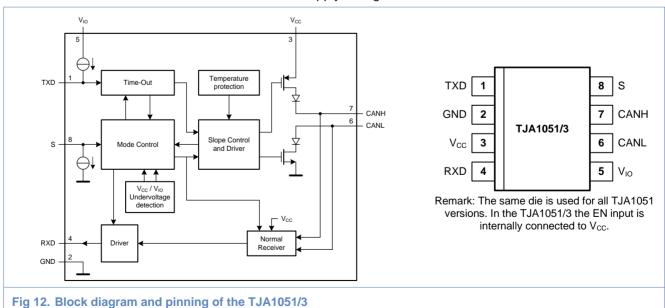

The TJA1051 is the basic high speed CAN transceiver is being delivered in three versions, distinguished only by the function of pin 5:

• TJA1051 – the version with pin 5 open (n.c.) is 100% backwards compatible with the TJA1050:

TJA1051/3 – the version with a V<sub>IO</sub> pin allows for direct interfacing to microcontrollers with supply voltages down to 3V:

TJA1051/E – the version with a EN pin allows disabling the transceivers requiring lowest guiescent current with disengaging from the bus (zero load):

### Systems & Applications, Automotive Innovation Center

### 3.2 Operation modes

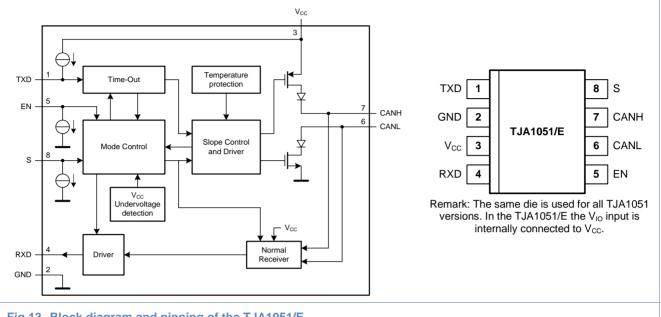

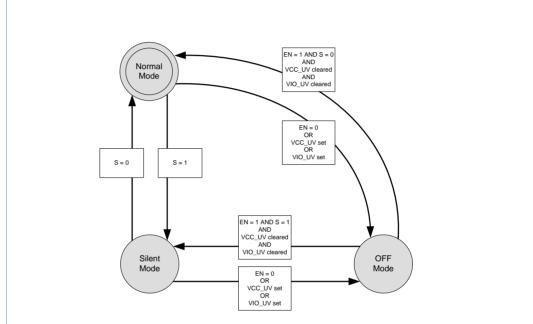

The TJA1051 offers 2 different power modes, Normal Mode and Silent Mode which are directly selectable. Taking into account the TJA1051/E with its EN input pin and the undervoltage detection a third power mode is available, the so-called OFF Mode. Fig 14 shows how the different operation modes can be entered. Every mode provides a certain behavior and terminates the CAN channel to a certain value. The following sub-chapters give a short overview of those features.

Remark: The same die is used for all TJA1051 versions.

- In the TJA1051 the  $V_{\text{IO}}$  and the EN input is internally connected to  $V_{\text{CC}}.$

- In the TJA1051/3 the EN input is internally connected to V<sub>CC</sub>.

- In the TJA1051/E the  $V_{\text{IO}}$  input is internally connected to  $V_{\text{CC}}.$

Fig 14. State diagram TJA1051, TJA1051/3 and TJA1051/E

### 3.2.1 Normal Mode

In Normal Mode the CAN communication is enabled. The digital bit stream input at TXD is transferred into corresponding analog bus signals. Simultaneously, the transceiver monitors the bus, converting the analog bus signals into the corresponding digital bit stream output at RXD. The bus lines are biased to Vcc/2 in recessive state and the transmitter is enabled. The Normal Mode is entered setting pin S to LOW. Due to an internal pull-down function it is the default mode if pin S is unconnected.

In Normal Mode the transceiver provides following functions:

- The CAN transmitter is active.

- The CAN receiver is active.

- CANH and CANL are biased to Vcc/2.

- V<sub>CC</sub> and V<sub>IO</sub> undervoltage detectors are active for undervoltage detection.

# The TJA1051 - Basic high speed CAN transceiver

### 3.2.2 Silent Mode

The Silent Mode is used to disable the transmitter of the TJA1051 regardless of the TXD input signal. In Silent Mode the TJA1051 is not capable of transmitting CAN messages, but all other functions, including the receiver, continue to operate. The Silent Mode is entered setting pin S to HIGH.

### **Babbling idiot protection**

The Silent Mode allows a node to be set to a state, in which it is absolutely passive to the bus. It becomes necessary when a CAN-controller gets out of control and unintentionally sends messages ("Babbling idiot"), that block the bus. Activating the Silent Mode by the microcontroller allows the bus to be released even when there is no direct access from the microcontroller to the CAN-controller. The Silent Mode is very useful for achieving high system reliability required by today's electronic applications.

### **Listen-only function**

In Silent Mode RXD monitors the bus lines as usual. Thus, the Silent Mode provides a Listen-Only Mode for diagnostic features. It ensures that a node does not influence the bus with dominant bits.

In Silent Mode the transceiver provides following functions:

- The CAN transmitter is off.

- The CAN receiver is active.

- CANH and CANL are biased to V<sub>CC</sub>/2.

- V<sub>CC</sub> and V<sub>IO</sub> undervoltage detectors are active for undervoltage detection.

### 3.2.3 OFF Mode

The non-operation OFF Mode is introduced offering total passive behaviour to the CAN bus system. The OFF Mode is entered by undervoltage detection on  $V_{\rm CC}$  or  $V_{\rm IO}$  (TJA1051/3 only) or by setting pin EN to LOW (TJA1051/E only). In OFF Mode the TJA1051 requires very low current for operation.

In OFF Mode the transceiver provides following functions:

- The CAN transmitter is off.

- · The CAN receiver is off.

- · CANH and CANL are floating (lowest leakage current on bus pins).

- V<sub>CC</sub> and V<sub>IO</sub> undervoltage detectors are active for undervoltage recovery.

| Table 1. Cr | iaracteristics | or the airrere | nt modes                                      |                 |                  |          |         |              |

|-------------|----------------|----------------|-----------------------------------------------|-----------------|------------------|----------|---------|--------------|

| Operating   | S pin          | EN pin         | V <sub>CC</sub> or V <sub>IO</sub> undervolt. | RXI             | ) pin            | Bus bias | TXD pin | CAN driver   |

| mode        |                |                | undervoit.                                    | Low             | High             |          |         |              |

| Normal      | 0              | 1              | no                                            | Bus<br>dominant | Bus              | Vcc/2    | 0       | dominant [1] |

|             |                |                |                                               | dominant        | recessive        |          | 1       | recessive    |

| Silent      | 1              | 1              | no                                            | Bus<br>dominant | Bus<br>recessive | Vcc/2    | X       | off          |

| OFF         | Х              | 0              | Х                                             | -               | -                | float    | Х       | off          |

|             | Х              | X              | ves                                           |                 |                  |          |         |              |

Table 1 Characteristics of the different modes

### 3.3 System fail-safe features

### 3.3.1 TXD dominant clamping detection in Normal Mode

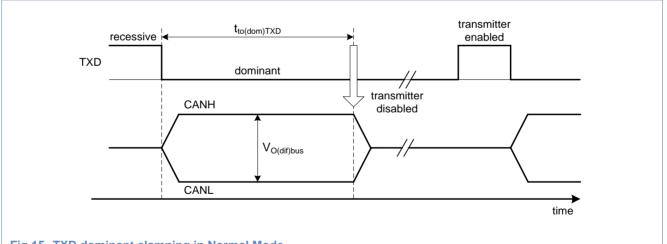

The TXD dominant clamping detection prevents an erroneous CAN-controller from clamping the bus to dominant level by a continuously dominant TXD signal.

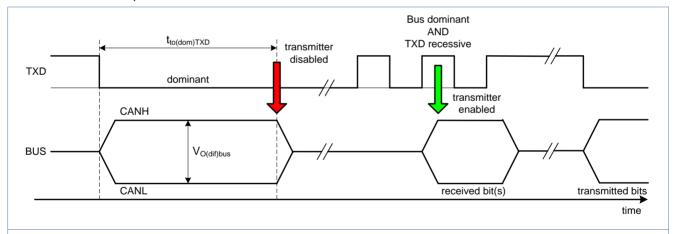

After a maximum allowable TXD dominant time  $t_{to(dom)TXD}$  the transmitter is disabled. According to the CAN protocol only a maximum of eleven successive dominant bits are allowed on TXD (worst case of five successive dominant bits followed immediately by an error frame). Along with the minimum allowable TXD dominant time, this limits the minimum bit rate to 40 kbit/s.

Fig 15. TXD dominant clamping in Normal Mode

### 3.3.2 Bus dominant clamping prevention at entering Normal Mode

Before transmitting the first dominant bit to the bus in Normal Mode the TXD pin once needs to be set HIGH in order to prevent a transceiver initially clamping the entire bus when starting up with not well defined TXD port setting of the microcontroller.

<sup>[1]</sup>  $t < t_{to(dom)TXD}$ , afterwards the TXD dominant clamping detection disables the transmitter.

### 3.3.3 Undervoltage detection & recovery

Compared to their predecessor TJA1050, the TJA1051 versions take advantage of high precision integrated undervoltage detection on their supply pins (see Table 2). Without this function undervoltage conditions might result in unwanted system behaviour, if the supply leaves the specified range. (e.g. the bus pins might bias to GND).

Table 2. Mode control at undervoltage conditions

| Undervoltag | e condition     | HS-CAN with Silent Mode |                  |                       |  |  |  |  |

|-------------|-----------------|-------------------------|------------------|-----------------------|--|--|--|--|

| Vcc         | V <sub>IO</sub> | TJA1051                 | TJA1051/3        | TJA1051/E             |  |  |  |  |

| no          | no              | Normal or Silent        | Normal or Silent | Normal, Silent or Off |  |  |  |  |

| yes         | no              | Off                     | Off              | Off                   |  |  |  |  |

| no          | yes             | not applicable          | Off              | not applicable        |  |  |  |  |

| yes         | yes             | Off                     | Off              | Off                   |  |  |  |  |

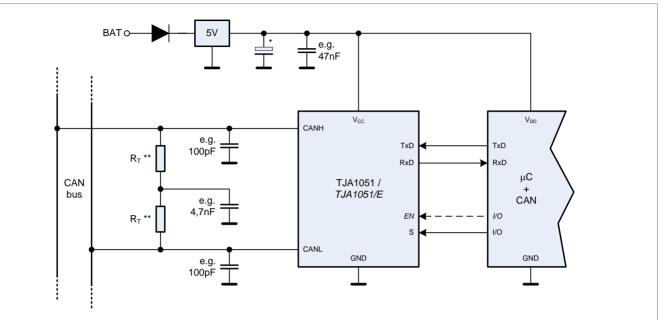

### 3.4 Hardware application

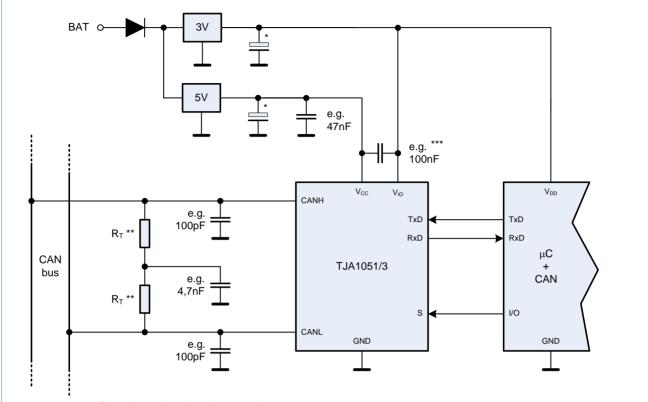

Fig 16 and Fig 17 show how to integrate the TJA1051 and its variants within a typical application. The application examples assume either a 5V or a 3V supplied host microcontroller. In each example there is a dedicated 5V regulator supplying the TJA1051 transceiver on its VCC supply pin (necessary for proper CAN transmit capability).

- \* Size of capacitor depends on regulator.

- \*\* For bus line end nodes RT = 60Ohm in order to support the "Split termination concept"

For stub nodes an optional "weak" termination of e.g. RT = 1,3kOhm can be foreseen, if required by the OEM.

<u>General remark</u>: A dedicated application may depend on specific OEM requirements.

Fig 16. Typical application with TJA1051 or TJA1051/E and a 5V microcontroller

- \* Size of capacitor depends on regulator.

- \*\* For bus line end nodes  $R_T = 60 \text{ Ohm}$  in order to support the "Split termination concept". For stub nodes an optional "weak" termination of e.g.  $R_T = 1,3k\text{Ohm}$  can be foreseen, if required by the OEM.

- \*\*\* Decoupling V<sub>IO</sub> to V<sub>CC</sub> (instead GND) with a capacitor close to the pins achieves a high-frequent short of the supplies and thus improves the electromagnetic immunity for the TJA1051/3 by enabling the same HF-conditions like existing with V<sub>CC</sub> connected directly to V<sub>IO</sub> in 5V-only environments.

General remark: A dedicated application may depend on specific OEM requirements.

Fig 17. Typical application with TJA1051/3 and a 3V microcontroller

Note: For detailed hardware application guidance please refer to chapter 7 explaining how the pins of the TJA1051 are properly connected in an application environment.

# The TJA1042 - High speed CAN transceiver with Standby Mode

### 4. The TJA1042 - High speed CAN transceiver with Standby Mode

### 4.1 Main features

The TJA1042 is the high speed CAN transceiver providing a low power mode (called Standby Mode) beside a Normal Mode. It is being delivered in two versions, distinguished only by the function of pin 5:

TJA1042 – the version with a SPLIT output is 100% backwards compatible with the TJA1040:

TJA1042/3 – the version with a V<sub>IO</sub> pin allows for direct interfacing to microcontrollers with supply voltages down to 3V:

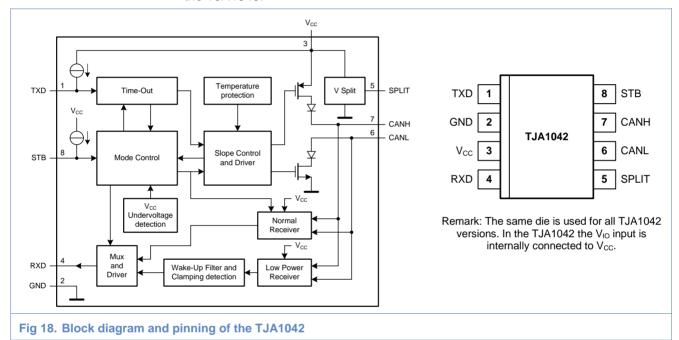

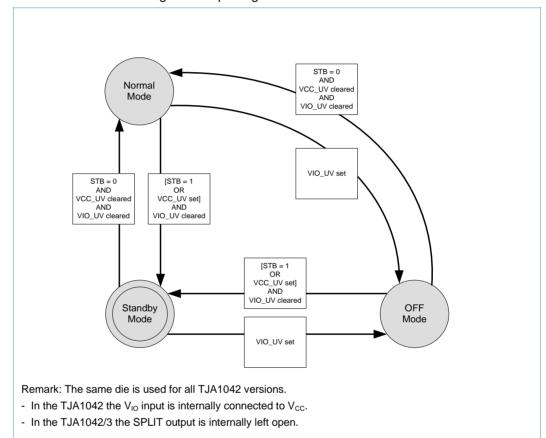

### 4.2 Operation modes

The TJA1042 offers 2 different power modes, Normal Mode and Standby Mode which are directly selectable. Taking into account the undervoltage detection a third power mode is available, the so-called OFF Mode. Fig 20 shows how the different operation modes can be entered. Every mode provides a certain behavior and terminates the CAN channel to a certain value. The following sub-chapters give a short overview of those features.

Fig 20. State diagram TJA1042 and TJA1042/3

### 4.2.1 Normal Mode

In Normal Mode the CAN communication is enabled. The digital bit stream input at TXD is transferred into corresponding analog bus signals. Simultaneously, the transceiver monitors the bus, converting the analog bus signals into the corresponding digital bit stream output at RXD. The bus lines are biased to  $V_{\rm CC}/2$  in recessive state and the transmitter is enabled. The Normal Mode is entered setting pin STB to LOW.

In Normal Mode the transceiver provides following functions:

- The CAN transmitter is active.

- The normal CAN receiver is active.

- The low power CAN receiver is active.

- CANH and CANL are biased to Vcc/2.

### Pin RXD reflects the normal CAN Receiver.

- SPLIT is biased to Vcc/2 (TJA1042 only).

- Vcc and Vio undervoltage detectors are active for undervoltage detection.

### 4.2.2 Standby Mode

The Standby Mode is used to reduce the power consumption of the TJA1042 significantly. In Standby Mode the TJA1042 is not capable of transmitting and receiving regular CAN messages, but it monitors the bus for CAN messages.

Only a low power CAN receiver is active, monitoring the bus lines for activity. The bus wake-up filter ensures that only bus dominant and bus recessive states that persist longer than  $t_{fltr(wake)bus}$  are reflected on the RXD pin. The low-power receiver is supplied by the  $V_{IO}$  pin, thus even with a switched off  $V_{CC}$  supply the TJA1042/3 offers full support of detecting a remote wake-up via the bus with lowest supply current. This allows 3V microcontroller designs to entirely disable all 5V supplies in the system while staying wake able via the CAN bus lines.

To reduce the current consumption as far as possible the bus is terminated to GND rather than biased to  $V_{\rm CC}/2$  as in Normal Mode. The Standby Mode is selected setting pin STB to HIGH or by undervoltage detection on  $V_{\rm CC}$ . Due to an internal pull-up function on the STB pin it is the default mode if pin STB is unconnected.

In Standby Mode the transceiver provides following functions:

- The CAN transmitter is off.

- The normal CAN receiver is off.

- The low power CAN receiver is active.

- · CANH and CANL are biased to GND.

- SPLIT is floating (TJA1042 only) (lowest leakage current on SPLIT pin).

- Pin RXD reflects the low-power CAN Receiver.

- V<sub>CC</sub> undervoltage detector is active for undervoltage detection / recovery.

- V<sub>IO</sub> undervoltage detector is active for undervoltage detection.

### 4.2.3 OFF Mode

The non-operation OFF Mode is introduced offering total passive behaviour to the CAN bus system. The OFF Mode is entered by undervoltage detection on  $V_{IO}$ .

In OFF Mode the transceiver provides following functions:

- · The CAN transmitter is off.

- The normal CAN receiver is off.

- The low power CAN receiver is off.

- CANH and CANL are floating (lowest leakage current on bus pins).

- SPLIT is floating (TJA1042 only) (lowest leakage current on SPLIT pin).

- V<sub>CC</sub> and V<sub>IO</sub> undervoltage detectors are active for undervoltage recovery.

Table 3. Characteristics of the different modes

| Operating | STB pin | Vcc     | Vio     | RXI                 | ) pin                  | Bus bias | SPLIT pin | TXD pin | CAN driver   |  |

|-----------|---------|---------|---------|---------------------|------------------------|----------|-----------|---------|--------------|--|

| mode      |         | underv. | underv. | Low                 | High                   |          |           |         |              |  |

| Normal    | 0       | no      | no      | Bus                 | Bus                    | Vcc/2    | Vcc/2     | 0       | dominant [1] |  |

|           |         |         |         | dominant recessive  |                        |          |           | 1       | recessive    |  |

| Standby   | 1       | X       | no      | Wake-up             | No wake-               | GND      | float     | Χ       | off          |  |

|           | Χ       | yes     | no      | request<br>detected | up request<br>detected |          |           |         |              |  |

| OFF       | Х       | Х       | Yes     | -                   | -                      | float    | float     | Χ       | off          |  |

<sup>[1]</sup>  $t < t_{to(dom)TXD}$ , afterwards the TXD dominant clamping detection disables the transmitter.

### 4.3 System fail-safe features

### 4.3.1 TXD dominant clamping detection in Normal Mode

As the TJA1051 the TJA1042 provides TXD dominant clamping detection in Normal Mode. Please refer to chapter 3.3.1 for more details.

### 4.3.2 Bus dominant clamping prevention at entering Normal Mode

As the TJA1051 the TJA1042 provides bus dominant clamping prevention at entering Normal Mode. Please refer to chapter 3.3.2 for more details.

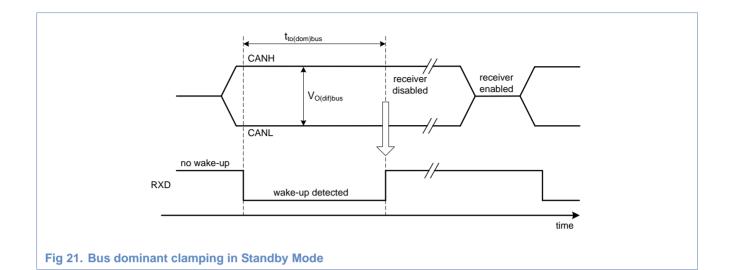

### 4.3.3 Bus dominant clamping detection in Standby Mode

For system safety reasons a new bus dominant timeout function in Standby Mode is introduced in the TJA1042. At any bus dominant condition in Standby Mode the RXD pin gets switched LOW. If the dominant condition holds for longer than the timeout  $t_{to(dom)bus}$ , the RXD pin gets set HIGH again in order to prevent generating a permanent wake-up request at a bus failure condition. Consequently a system can now enter the Standby Mode even with a permanently dominant clamped bus.

### 4.3.4 Undervoltage detection & recovery

Compared to their predecessor TJA1040, the TJA1042 versions take advantage of high precision integrated undervoltage detection on their supply pins (see Table 4). Without this function undervoltage conditions might result in unwanted system behavior, if the supply leaves the specified range. (e.g. the bus pins might bias to GND).

Table 4. TJA1042 and TJA1042/3 mode control at undervoltage conditions

| Undervoltag | e condition     | HS-CAN with Standby Mode |                   |  |  |  |

|-------------|-----------------|--------------------------|-------------------|--|--|--|

| Vcc         | V <sub>IO</sub> | TJA1042                  | TJA1042/3         |  |  |  |

| no          | no              | Normal or Standby        | Normal or Standby |  |  |  |

| yes         | no              | Standby                  | Standby           |  |  |  |

| no          | yes             | not applicable           | OFF               |  |  |  |

| yes         | yes             | OFF                      | OFF               |  |  |  |

### 4.4 Hardware application

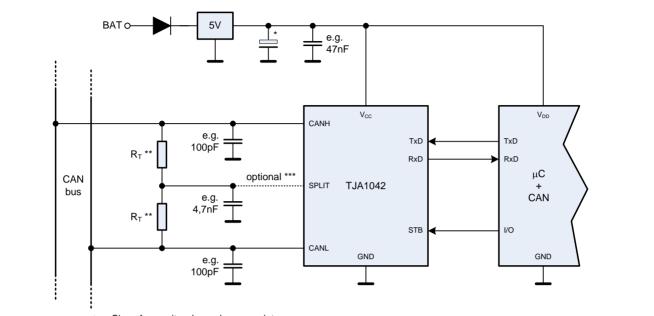

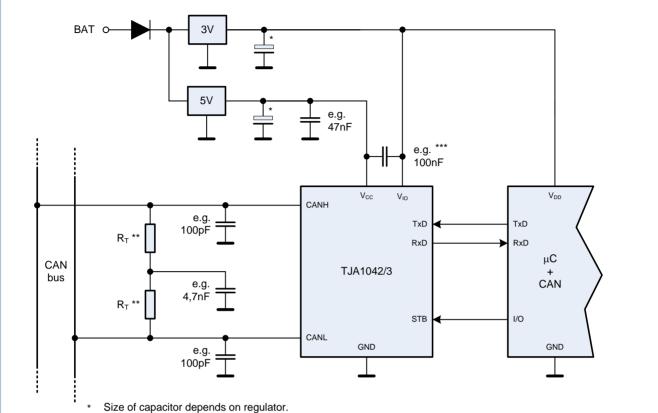

Fig 22 and Fig 23 show how to integrate the TJA1042 and the TJA1042/3 within a typical application. The application examples assume either a 5V or a 3V supplied host microcontroller. In each example there is a dedicated 5V regulator supplying the TJA1042 transceiver on its  $V_{CC}$  supply pin (necessary for proper CAN transmit capability).

- \* Size of capacitor depends on regulator.

- \*\* For bus line end nodes RT = 60Ohm in order to support the "Split termination concept"

For stub nodes an optional "weak" termination of e.g. RT = 1,3kOhm can be foreseen, if required by the OEM.

- \*\*\* Optional common mode stabilization by a voltage source of V<sub>CC</sub>/2 at the pin SPLIT.

General remark: A dedicated application may depend on specific OEM requirements.

Fig 22. Typical application with TJA1042 and a 5V microcontroller

### **Systems & Applications, Automotive Innovation Center**

- For bus line end nodes  $R_T = 600$ hm in order to support the "Split termination concept". For stub nodes an optional "weak" termination of e.g.  $R_T = 1,3$ kOhm can be foreseen, if required by the OEM.

- \*\*\* Decoupling V<sub>IO</sub> to V<sub>CC</sub> (instead GND) with a capacitor close to the pins achieves a high-frequent short of the supplies and thus improves the electromagnetic immunity for the TJA1042/3 by enabling the same HFconditions like existing with V<sub>CC</sub> connected directly to V<sub>IO</sub> in 5V-only environments.

General remark: A dedicated application may depend on specific OEM requirements.

Fig 23. Typical application with TJA1042/3 and a 3V microcontroller

Note: For detailed hardware application guidance please refer to chapter 7 explaining how the pins of the TJA1042 are properly connected in an application environment.

# The TJA1048 - Dual high speed CAN transceiver with Standby Mode

### 5. The TJA1048 - Dual high speed CAN transceiver with Standby Mode

### 5.1 Main features

The TJA1048 is the first dual high-speed CAN transceiver from NXP Semiconductors providing two independent CAN channels with a low power mode (called Standby Mode) besides a Normal Mode. The TJA1048 can be interfaced directly to microcontrollers with supply voltages from 3V to 5V.

The TJA1048 is the excellent choice for all types of HS-CAN networks containing more than one HS-CAN interface that require a low-power mode with wake-up capability via the CAN bus, especially for Body Control and Gateway units.

### **Systems & Applications, Automotive Innovation Center**

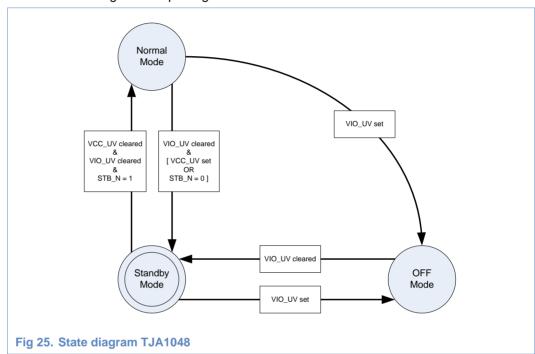

### 5.2 Operating modes

The TJA1048 offers 2 different power modes, Normal Mode and Standby Mode which are directly selectable for each CAN channel. Taking into account the  $V_{\rm IO}$  undervoltage condition a third power mode can be entered, the so-called OFF Mode, selected generally for both CAN channels. Fig 25 shows how the different operation modes can be entered. Every mode provides a certain behavior and terminates the CAN channel to a certain value. The following sub-chapters give a short overview of those features.

### 5.2.1 Normal Mode

In Normal Mode the CAN communication is enabled. The digital bit stream input at TXD is transferred into corresponding analog bus signals. Simultaneously, the transceiver monitors the bus, converting the analog bus signals into the corresponding digital bit stream output at RXD. The bus lines are biased to  $V_{\rm CC}/2$  in recessive state and the transmitter is enabled. The Normal Mode is entered setting STBN1 or STBN2 to HIGH. Switching into Normal Mode is CAN channel independently.

In Normal Mode the transceiver provides the following functions:

- The CAN transmitter is active.

- The normal CAN receiver is active.

- The low power CAN receiver is active.

- CANH and CANL are biased to Vcc/2.

- Pin RXD reflects the normal CAN Receiver.

- V<sub>CC</sub> and V<sub>IO</sub> undervoltage detectors are active for undervoltage detection.

# The TJA1048 - Dual high speed CAN transceiver with Standby Mode

### 5.2.2 Standby Mode

The Standby Mode is used to reduce the power consumption of the TJA1048 significantly. In Standby Mode the specific CAN channel is not capable of transmitting and receiving regular CAN messages, but it monitors the bus for CAN messages. After passing the wake-up filter the bus signal is transferred to RXD with an additional time delay tfltr(wake)bus. To reduce the current consumption as far as possible the bus is terminated to GND rather than biased to Vcc/2 as in Normal Mode. The Standby Mode is selected setting STBN1 or STBN2 to LOW channel independently or by undervoltage detection on Vcc for both channels at the same time. Due to an internal pull-down function on the pins STBN1 and STBN2 it is the default mode if the pins are unconnected.

In Standby Mode the transceiver provides the following functions:

- · The CAN transmitter is off.

- The normal CAN receiver is off.

- The low power CAN receiver is active.

- CANH and CANL are biaed to GND.

- Pin RXD reflects the low power CAN receiver .

- V<sub>IO</sub> undervoltage detector is active for undervoltage detection.

- Vcc undervoltage detector may be disabled

### 5.2.3 OFF Mode

The non-operation Off Mode is introduced offering total passive behaviour to bus system. The OFF Mode is entered by undervoltage detection on  $V_{IO}$ . Entering and leaving OFF Mode is done for both channels at the same time, thus not independently. In OFF Mode the transceiver provides the following functions:

- · The CAN transmitter is off.

- The normal CAN receiver is off.

- The low power CAN receiver is off.

- CANH and CANL are floating (lowest leakage current on bus pins).

- V<sub>IO</sub> undervoltage detector is active for u ndervoltage detection.

- Vcc undervoltage detector may be disabled

Table 5. Characteristics of the different modes

| Ch1 Op. | Ch2 Op.<br>mode | STBN1<br>pin | STBN2<br>pin | V <sub>CC</sub> underv. | V <sub>IO</sub> underv. | RXD                     | RXD1 pin                  |       | RXD                     | 2 pin                     | Bus2<br>bias |

|---------|-----------------|--------------|--------------|-------------------------|-------------------------|-------------------------|---------------------------|-------|-------------------------|---------------------------|--------------|

|         |                 |              |              |                         |                         | Low                     | High                      |       | Low                     | High                      |              |

| Normal  | Normal          | 1            | 1            | no                      | no                      | Bus<br>dom.             | Bus<br>rec.               | Vcc/2 | Bus<br>dom.             | Bus<br>rec.               | Vcc/2        |

| Standby | Normal          | 0            | 1            | no                      | no                      | Wake-<br>up<br>detected | No<br>wake-up<br>detected | GND   | Bus<br>dom.             | Bus<br>rec.               | Vcc/2        |

| Normal  | Standby         | 1            | 0            | no                      | no                      | Bus<br>dom.             | Bus<br>rec.               | Vcc/2 | Wake-<br>up<br>detected | No<br>wake-up<br>detected | GND          |

| Standby | Standby         | 0            | 0            | no                      | no                      | Wake-<br>up<br>detected | No<br>wake-up<br>detected | GND   | Wake-<br>up<br>detected | No<br>wake-up<br>detected | GND          |

| Standby | Standby         | Х            | Х            | yes                     | no                      | Wake-<br>up<br>detected | No<br>wake-up<br>detected | GND   | Wake-<br>up<br>detected | No<br>wake-up<br>detected | GND          |

| OFF     | OFF             | Х            | Х            | Х                       | yes                     | -                       | -                         | float | -                       | -                         | float        |

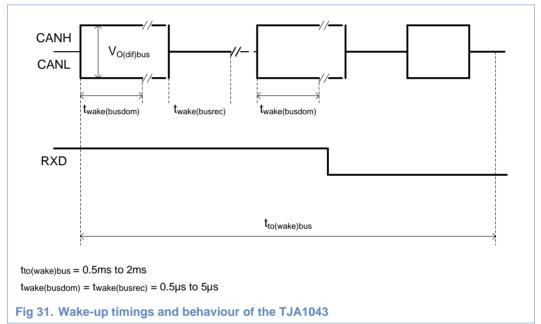

### 5.3 Remote Wake-up (via CAN bus)

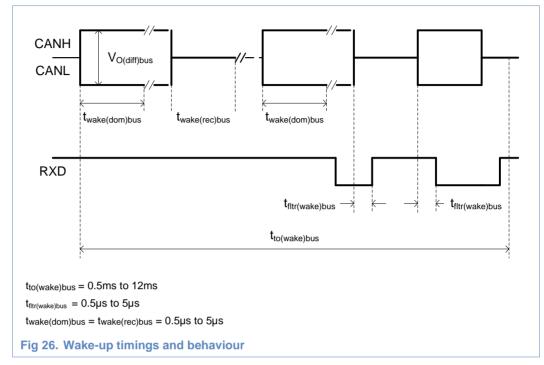

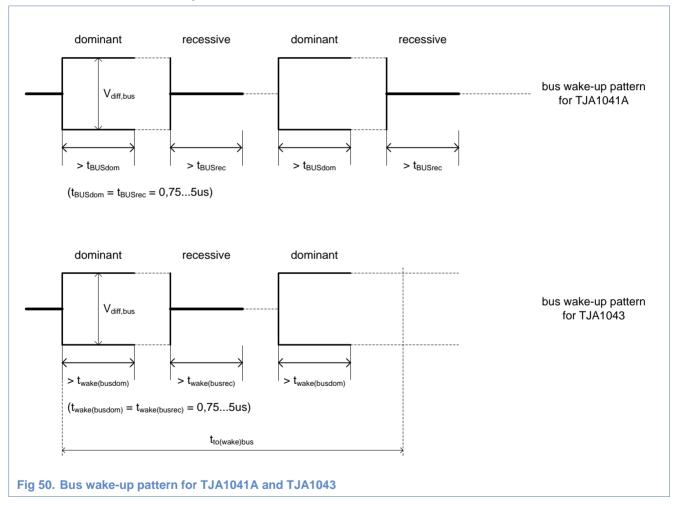

In comparison to the TJA1042 the TJA1048 offers a slightly enhanced remote wake-up procedure. The TJA1042 in Standby Mode transfers the bus signal to RXD with an additional time delay tfttr(wake)bus in oder to filter noise and spikes.

A dedicated wake-up sequence (specified in ISO11898-2 and SAE J2284) must be received to wake-up the TJA1048 from Standby Mode. This filtering improves the robustness against spurious wake-up events due to a dominant clamped CAN bus or dominant phases caused by noise or spikes on the bus.

The wake-up pattern consists of:

- A dominant phase of at least twake(busdom) followed by

- A recessive phase of at least twake(busrec) followed by

- A dominant phase of at least twake(busdom)

The complete dominant-recessive-dominant pattern must be completed within  $t_{to(wake)bus}$  to be recognized as a valid wake-up pattern (see Fig 26). Otherwise the internal wake-up logic gets reset and the complete wake-up pattern needs to be re-applied to the low power receiver of CAN1 or CAN2 before generating a proper remote wake-up. Pins RXD1 and RXD2 will remain recessive until the wake-up event has been triggered.

After the wake-up sequence has been detected, the TJA1048 behaves equal to the TJA1042 and will remain in Standby Mode with the bus signals reflected on RXD1/RXD2. Note that dominant or recessive phases less than tfltr(wake)bus will not be detected by the low power differential receiver and will not be reflected on RXD1/RXD2 in Standby Mode.

A wake-up event will not be registered if any of the following events occurs while a wakeup sequence is being received:

- The TJA1048 switches to Normal Mode

- The complete wake-up pattern was not received within tto(wake)bus

- A V<sub>IO</sub> undervoltage was detected (V<sub>IO</sub> < V<sub>uvd(VIO)</sub>)

If any of these events occurs while a wake-up sequence is being received, the internal wake-up logic will be reset and the complete wake-up sequence will have to be retransmitted to trigger a wake-up event.

### 5.4 System fail-safe features

### 5.4.1 TXD dominant clamping detection in Normal Mode

As the TJA1051, TJA1042 the TJA1048 provides TXD dominant clamping detection in Normal Mode for each CAN channel. Please refer to chapter 3.3.1 for more details.

### 5.4.2 Bus dominant clamping prevention at entering Normal Mode

As the TJA1051, TJA1042 the TJA1048 provides bus dominant clamping prevention at entering Normal Mode. Please refer to chapter 3.3.2for more details.

## The TJA1048 - Dual high speed CAN transceiver with Standby Mode

### 5.4.3 Undervoltage detection & recovery

The TJA1048 provides two supply pins,  $V_{CC}$  and  $V_{IO}$ . The  $V_{CC}$  voltage is needed for the CAN physical interface.  $V_{CC}$  provides the current needed for the CAN transmitter and receiver in Normal Mode. Pin  $V_{IO}$  should be connected to the microcontroller supply voltage. This will adjust the signal levels of pins TXD1, TXD2, RXD1, RXD2, STBN1 and STBN2 to the I/O levels of the microcontroller. Pin  $V_{IO}$  also provides the internal supply voltage for the low power differential receiver of each integrated transceivers. For applications running in low power, this allows the bus lines to be monitored for activity even if there is no supply voltage on pin  $V_{CC}$ .

Both voltages are independent from each other. An undervoltage detection circuitry at  $V_{\rm CC}$  and  $V_{\rm IO}$  indicates either a  $V_{\rm CC}$  or  $V_{\rm IO}$  undervoltage condition that is used for mode control. A  $V_{\rm CC}$  undervoltage condition forces both CAN channels of the TJA1048 to enter Standby Mode. The logic state of pins STBN1 and STBN2 will be ignored until  $V_{\rm CC}$  has recovered. This allows saving current in case of switching off the supply voltage or faulty behaviour of host electronic control unit. As long as  $V_{\rm IO}$  keeps present the TJA1048 offers the full wake-up capability. A  $V_{\rm IO}$  undervoltage condition forces both CAN channels of the TJA1048 to switch off (OFF Mode) and to disengages from the bus (zero load) until  $V_{\rm IO}$  has recovered. In OFF Mode both CAN transceiver behave passive to the bus. Table 6 gives an overview of the undervoltage behaviour. As long as no undervoltage is detected the TJA1048 keeps fully operational.

Table 6. Device behaviour in different power conditions

| Undervoltaç<br>V <sub>CC</sub> | ge condition<br>V <sub>IO</sub> | Operating mode    | CAN1 / CAN2 biasing | Bus wake-up capability |

|--------------------------------|---------------------------------|-------------------|---------------------|------------------------|

| no                             | no                              | Normal or Standby | Vcc/2 or GND        | yes                    |

| yes                            | no                              | Standby           | GND                 | yes                    |

| no                             | yes                             | OFF               | float               | no                     |

| yes                            | yes                             | OFF               | float               | no                     |

## The TJA1048 - Dual high speed CAN transceiver with Standby Mode

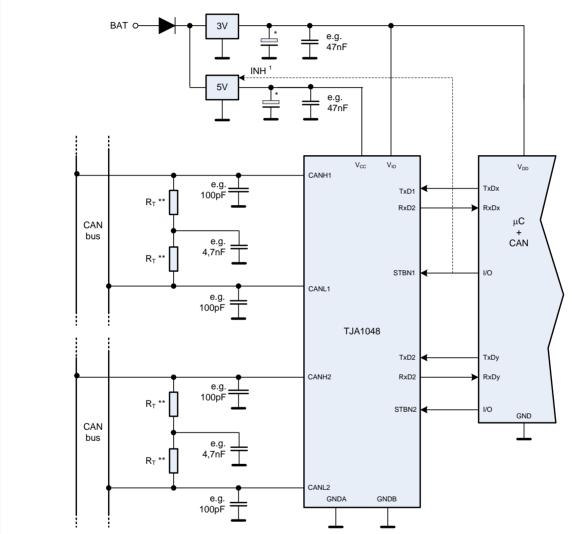

### 5.5 Hardware application

Fig 27 shows how to integrate the TJA1048 within a typical application. The application examples assume 3V supplied host microcontroller. There is a dedicated 5V regulator supplying the TJA1048 transceiver on its  $V_{CC}$  supply pin (necessary for proper CAN transmit capability).

- \* Size of capacitor depends on regulator.

- \*\* For bus line end nodes  $R_T = 60\text{Ohm}$  in order to support the "Split termination concept". For stub nodes an optional "weak" termination of e.g.  $R_T = 1,3$ kOhm can be foreseen, if required by the OEM.

General remark: A dedicated application may depend on specific OEM requirements.

(1) Switching off the 5V supply if both channels in Standby Mode (dotted line) is optional

Fig 27. Application diagram TJA1048

Note: For detailed hardware application guidance please refer to chapter 7 explaining how the pins of the TJA1048 are properly connected in an application environment.

### 6. The TJA1043 – High speed CAN transceiver with Sleep Mode & diagnostics

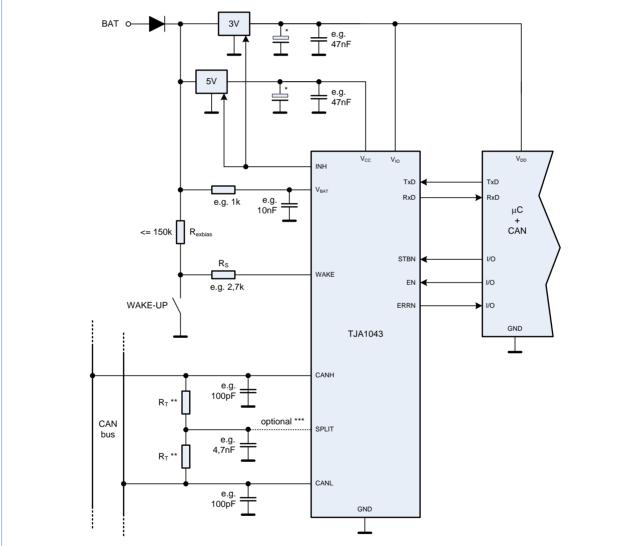

### 6.1 Main features

The TJA1043 is the ideal choice for high speed CAN nodes that need to be available all time "Clamp-30", even when the internal  $V_{IO}$  and  $V_{CC}$  supplies are switched off. It is a step up from the TJA1041A high speed CAN transceiver, offering enhanced low power management with wake up detection and recognition beside several protection and diagnostic functions. The TJA1043 builds the high end of the  $3^{rd}$  generation high speed CAN portfoilio from NXP Semiconductors.

### **Low Power Management**

Many in-vehicle networking architectures require the availability of the high speed CAN bus even when ignition key is off. This requires permanently battery supplied ECUs with lowest current consumption. The low power management of the TJA1043 allows reducing the quiescent current consumption of an ECU to about typ. 20  $\mu A.$  This current consumption is low enough to allow permanent battery supply of the transceiver and

keeping wakeup capability via the bus. This way the system can react on local events as well as on CAN messages, resulting in wakeup of the complete bus system.

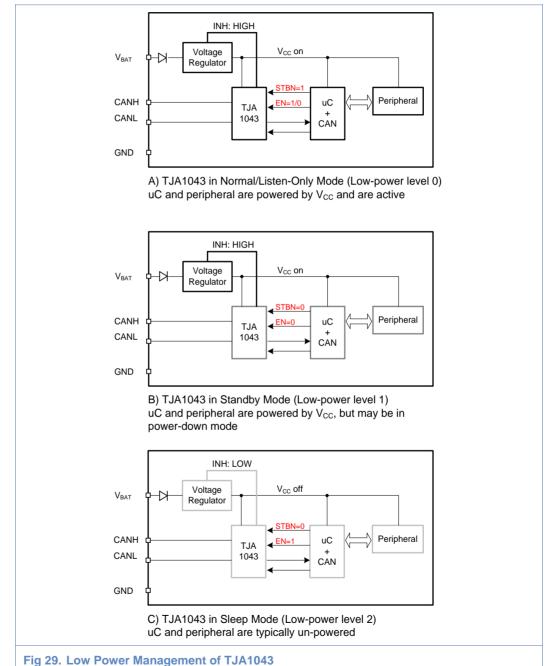

The operating modes of the TJA1043 (Normal, Listen-Only, Standby, Sleep, Go-to-Sleep) establish a low power management with three different levels as sketched in Fig 29 and Table 7. In level 0 the ECU components (voltage regulator, microcontroller, transceiver and peripherals) are active and powered. The TJA1043 is either in Normal or Listen-Only Mode. The transceiver and the host microcontroller are powered by the active Vcc supply.

AH1014\_v1.5\_Application Hints TJA1042\_43\_48\_51.doc

The next level of low power, level 1, is achieved with the TJA1043 operating in Standby Mode. The microcontroller, transceiver and peripherals are still powered by the active  $V_{CC}$  supply, but the functionality is often reduced to a minimum in order to save current. In the case of the TJA1043 the function is reduced to detection of wakeup events only. Transmit and receive function as provided in Normal Mode is not available. The host microcontroller is often put in a power-down condition in order to save additional current.

The low power level 2 is associated to the Sleep Mode of the TJA1043. In Sleep Mode the external voltage regulator(s), supplying the transceiver and host microcontroller, is (are) typically switched off via the INH output signal of the transceiver. The  $V_{CC}$  supply for the transceiver and microcontroller is not available. While the host microcontroller and peripherals are completely un-powered, the TJA1043 keeps powered via the battery supply pin  $V_{BAT}$ . This supply is needed to ensure wakeup capability either via the bus or via a local wakeup event. The low power level 2 guarantees the lowest current consumption of a node.

Table 7. Characteristics of the different low power modes

| Low power level         | Operating mode         | V <sub>CC</sub> supply | uC         | Node power consumption |

|-------------------------|------------------------|------------------------|------------|------------------------|

| Level 0<br>(Bus active) | Normal,<br>Listen-only | Active                 | Powered    | Normal                 |

| Level 1                 | Standby                | Active                 | Powered    | Low                    |

| Level 2                 | Sleep                  | Off                    | Un-powered | Very Low               |

### Bus failure diagnosis

The TJA1043 can detect short circuits on the bus wires and signal them to the host microcontroller. While physical bus failures normally lead to interruption of bus communication, there are certain bus failures that are tolerated within the physical layer of high speed CAN. Without the bus failure diagnosis feature of the TJA1043 the application microcontroller would not have a chance to become aware of those bus failures. Apart from increasing current consumption, those bus failures are responsible for poor EMC performance.

### System fail-safe features

The system fail-safe features of the TJA1043 aim to keep the impact of possible local failures, like pin short-circuits, confined to the corrupted node only. After detection of a local failure, appropriate measures are taken to keep the remaining bus operable as long as possible. There are protections against TXD Dominant Clamping, TXD/RXD Short Circuit and Bus Dominant Clamping.

Additionally the TJA1043 features a "best-off" supply strategy. Therefore, the internal circuitry is able to survive deep cranking situations on the battery supply line through the VCC buffer caps on ECU designs. VCC and VBAT are internally connected through diodes to keep the TJA1043 powered as long as possible in case  $V_{BAT}$  drops below its undervoltage threshold while  $V_{CC}$  is still present.

### 6.2 Operating modes

The TJA1043 provides five different operating modes, which are controlled by the input pins STBN and EN. The reference state diagram for the operating modes can be found in the data sheet [7]. In the case of an undervoltage condition on the pin  $V_{\text{CC}}$  or  $V_{\text{IO}}$ , the transceiver is forced into Sleep Mode, overruling the current mode selection at the pins STBN and EN. In the case of an undervoltage condition on the pin  $V_{\text{BAT}}$  the transceiver is forced into Standby Mode.

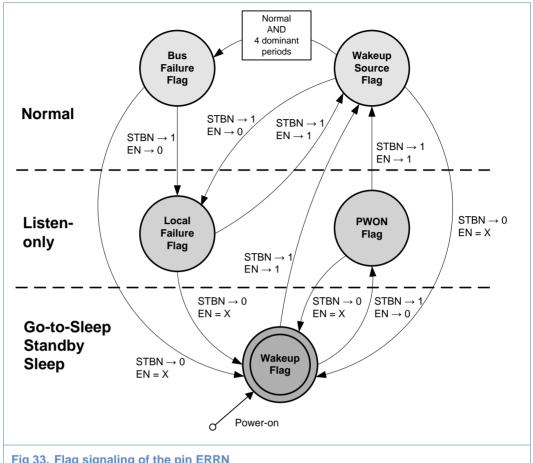

Depending on the operating mode the transceiver shows different behavior for the receiver and bus driver as well as on output pins like ERRN and RXD. Table 1 summarizes the characteristics in each operating mode.

### 6.2.1 Normal Mode

For CAN communication the Normal Mode is chosen. The digital bit stream input at TXD is transferred into corresponding analog bus signals. Simultaneously, the transceiver monitors the bus, converting the analog bus signals into the corresponding digital bit stream output at RXD. The external voltage regulator is active, the bus lines are biased to Vcc/2 and the transmitter is enabled. The Normal Mode is entered setting STBN and HIGH and EN to HIGH level.

In Normal Mode the transceiver provides the following functions:

- The CAN transmitter is active.

- The normal CAN receiver is active, pin RXD reflects the normal CAN Receiver.

- The local and bus wakeup function are disabled.

- INH is active (V<sub>BAT</sub> level).

- CANH and CANL are biased to Vcc/2.

- SPLIT is biased to Vcc/2.

- VBAT, VCC and VIO undervoltage detectors are active for undervoltage detection.

- · Local and bus failure diagnosis is active.

- Pin ERRN provides either the Wakeup Source or the Bus Failure Flag.

### 6.2.2 Listen-only Mode

In general the Listen-Only Mode has two different functions. First, it realizes a Listen-Only behavior. The node is only allowed to receive messages from the bus but not to transmit onto the bus. The digital bit stream from the CAN-controller at TXD is simply ignored. In this way a node can be prevented from influencing the bus.

Secondly, the Listen-Only Mode provides the Local Failure flag and PWON flag at the pin ERRN, which can be read by the microcontroller. For flag signalling at the pin ERRN refer to Chapter 6.5. The Listen-Only Mode is entered setting STBN to HIGH and EN to LOW level.

In Listen-only Mode the transceiver provides the following functions:

- The CAN transmitter is off.

- The normal CAN receiver is active, pin RXD reflects the normal CAN Receiver.

- The local and bus wakeup function are disabled.

- INH is active (V<sub>BAT</sub> level).

- CANH and CANL are biased to Vcc/2.

- SPLIT is biased to V<sub>CC</sub>/2.

- V<sub>BAT</sub>, V<sub>CC</sub> and V<sub>IO</sub> undervoltage detectors are active for undervoltage detection.

- Local failure diagnosis is active.

- Pin ERRN provides either the Pwon or Local Failure Flag.

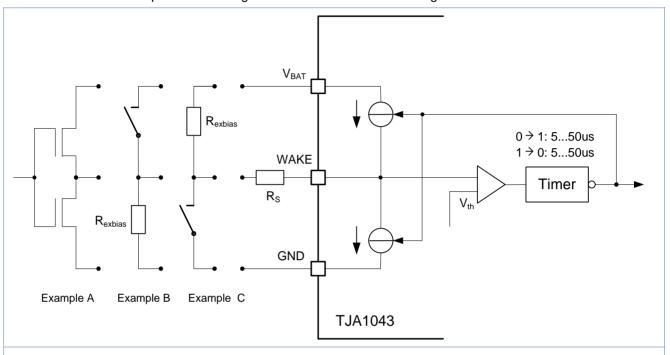

### 6.2.3 Standby Mode

Standby Mode is used to achieve low power level 1. Power consumption of the TJA1043 is significantly reduced compared to Normal or Listen-Only Mode. In Standby Mode the TJA1043 is not capable of transmitting and receiving regular CAN messages. However, the TJA1043 monitors the bus for CAN messages. Whenever a wakeup pattern is detected on the bus, indicating bus traffic, the internal Wakeup flag is set. The TJA1043 can also receive a local wakeup via the pin WAKE. On detection of a remote or local wakeup the internal Wakeup flag is set. In Standby Mode this flag is output at the pins ERRN and RXD. To reduce the current consumption as far as possible the bus is terminated to GND rather than biased to Vcc/2 as in Normal or Listen-Only Mode. Standby Mode is selected setting STBN to LOW and EN to LOW level.

In Standby Mode the transceiver provides the following functions:

- · The CAN transmitter is off.

- The normal CAN receiver is off.

- The local and bus wakeup function are active.

- INH is active (VBAT level).

- CANH and CANL are biased to GND.

- SPLIT is floating (lowest leakage current on SPLIT pin).

- V<sub>BAT</sub>, V<sub>CC</sub> and V<sub>IO</sub> undervoltage detectors are active for undervoltage detection.

- Pin ERRN and pin RXD provide the Wakeup Flag (if VBAT and VIO are present)

### 6.2.4 Sleep Mode

Sleep Mode is used to achieve low power level 2. While the transceiver current consumption is the same as in Standby Mode, it allows further reduction of the system current consumption by switching off the external voltage regulator (Vcc supply) for the transceiver, host microcontroller etc.

The only difference between Sleep and Standby Mode concerns the pin INH. It provides a battery related open drain output to control one or more external voltage regulators. In Sleep Mode the pin INH is set floating compared to a HIGH signal ( $V_{BAT}$ -based) in all other modes (also Standby Mode), typically disabling the voltage regulator(s) for the transceiver and microcontroller. While the microcontroller is completely un-powered (no  $V_{CC}$  supply), the TJA1043 keeps partly alive via its battery supply. It allows the transceiver to monitor the bus for CAN messages. In fact, the transceiver is the device controlling autonomously the  $V_{CC}$  supply for the ECU.

In Sleep Mode the transceiver provides the following functions:

- The CAN transmitter is off.

- · The normal CAN receiver is off.

- The local and bus wakeup function are active.

- INH is floating (lowest leakage current on INH pin).

- CANH and CANL are biased to GND.

- SPLIT is floating (lowest leakage current on SPLIT pin).

- V<sub>BAT</sub>, V<sub>CC</sub> and V<sub>IO</sub> undervoltage detectors are active for undervoltage detection.

- Pin ERRN and pin RXD provide the Wakeup Flag (if V<sub>BAT</sub> and V<sub>IO</sub> are present)

Wakeup from Sleep Mode is generally possible via two channels (see also chapter 6.4):

- · Wakeup via a remote wakeup sequence on the bus

- Local wakeup via an edge at pin WAKE

On wakeup, the pin INH goes HIGH enabling the external voltage regulator(s) again. The Wakeup flag is set for a local or remote wakeup. It is reflected at the pins ERRN and RXD. As in Standby Mode, the bus lines CANH and CANL are terminated to GND. Table 1 summarizes the characteristics of the TJA1043 in the different operating modes.

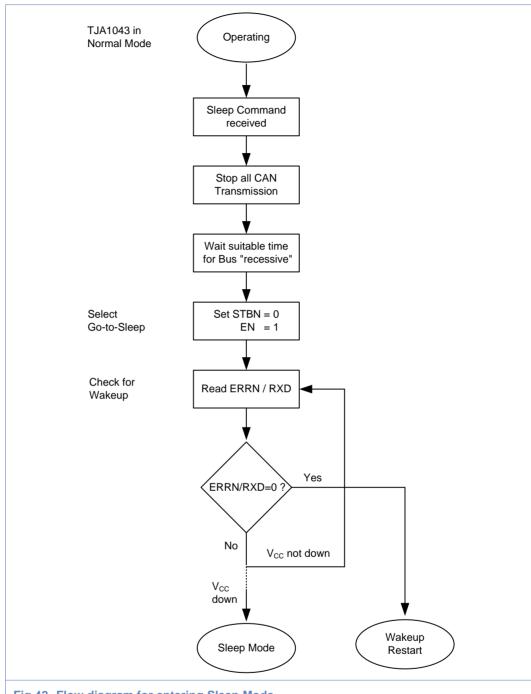

The only way to put the TJA1043 into Sleep Mode is using the Go-to-Sleep Mode (STBN to LOW, EN to HIGH). If it is selected for longer than the minimum hold time of go-to-sleep command  $t_{h(min)}$  [7], the transceiver is automatically forced into Sleep Mode switching the pin INH to floating.

A mode transition from Sleep Mode to any other mode via STBN and EN is possible, even if the supplies  $V_{\text{CC}}$  and  $V_{\text{IO}}$  were not present all time during Sleep Mode. Once a rising edge on the pin STBN is detected (provided that the VIO is present) the selected mode on pin EN (either Normal or Listen-only) will be entered.

A continuous situation, where one part of the nodes is in Normal or Listen-Only Mode while the other part is in Standby or Sleep Mode, should be avoided due to the different bus biasing in these modes. Otherwise a continuous DC common mode current would flow from one part to the other.

### 6.2.5 Go-to-Sleep Mode

The Go-to-Sleep Mode has the meaning of a command rather than the meaning of a typical operating mode. It is used to put the TJA1043 into Sleep Mode. Due to the spread of the minimum hold time of go-to-sleep command  $t_{h(min)}$  [7] the Go-to Sleep Mode must be selected for longer than the maximum value in order to make sure the Sleep Mode is entered reliably. Immediately after selecting the Go-to Sleep Mode the transmitter is disabled, the bus lines are terminated to GND and the Wakeup flag information is signalled at the pins ERRN and RXD. The Go-to Sleep Mode is selected with STBN to LOW and EN to HIGH level.

Remark: The Go-to Sleep Command might become overruled by a wake-up event, if this wake-up event occurs simultaneously with the Go-to Sleep Command. In this case, the wake-up will be signalled on RXD and ERRN as desired, while INH stays active HIGH.

Table 8. Characteristics of the different modes

| Operating   | STBN | EN  | ERR                                                   | ERRN pin RXD p                              |                 | ) pin            | Bus bias | INH pin          |

|-------------|------|-----|-------------------------------------------------------|---------------------------------------------|-----------------|------------------|----------|------------------|

| mode        | pin  | pin | Low                                                   | High                                        | Low             | High             |          |                  |

| Normal      | 1    | 1   | Bus failure flag<br>set <sup>[1]</sup>                | Bus failure flag<br>reset <sup>[1]</sup>    | Bus<br>dominant | Bus<br>recessive | Vcc/2    | V <sub>BAT</sub> |

|             |      |     | Wakeup Source<br>flag: Local<br>wakeup <sup>[2]</sup> | Wakeup Source<br>flag: Remote<br>wakeup [2] |                 |                  |          |                  |

| Listen-only | 1    | 0   | PWON flag set [3]                                     | PWON flag reset                             | t               |                  |          |                  |

|             |      |     | Local failure flag<br>set [4]                         | Local failure flag<br>reset [4]             |                 |                  |          |                  |

| Go-to-Sleep | 0    | 1   | Wakeup flag<br>set <sup>[5]</sup>                     | Wakeup flag<br>reset [5]                    | Wakeup          | Wakeup           | GND      |                  |

| Standby     | 0    | 0   | Ser 🖾                                                 | ieset,                                      | flag set [5]    | flag reset [5]   |          |                  |

| Sleep [6]   | 0    | Х   |                                                       |                                             |                 |                  |          | float            |

<sup>[1]</sup> Valid after the 4<sup>th</sup> dominant to recessive edge at TXD after entering the Normal Mode (each dominant period should be at least 4us).

<sup>[2]</sup> Valid before the 4<sup>th</sup> dominant to recessive edge at TXD after entering Normal Mode.

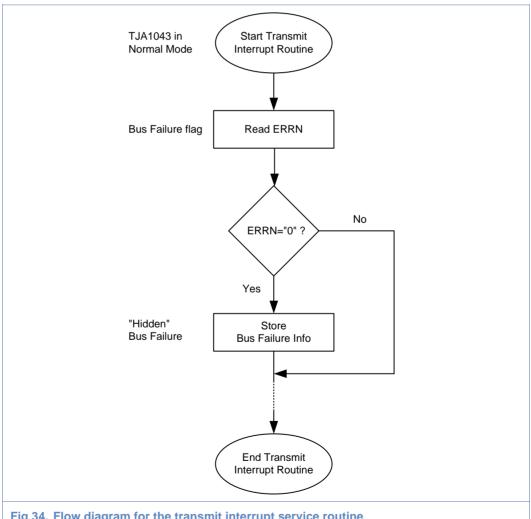

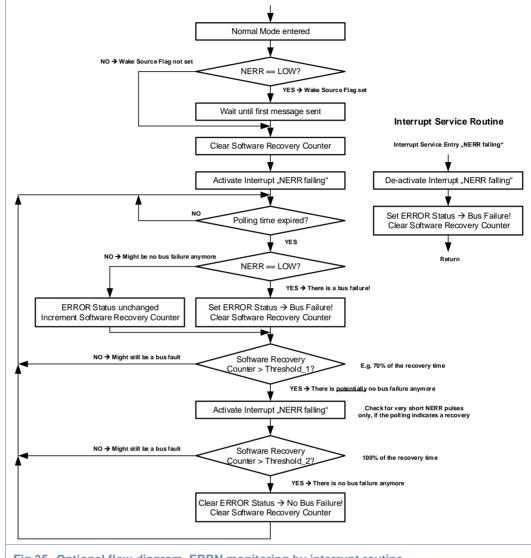

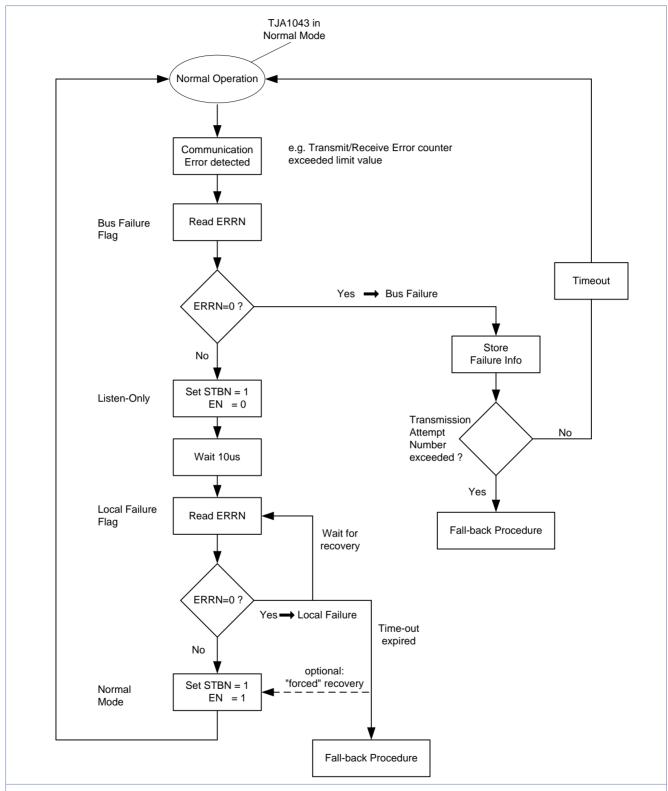

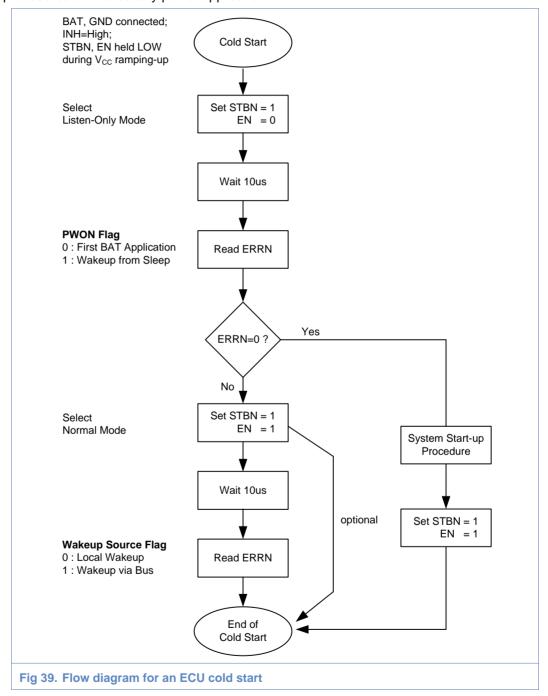

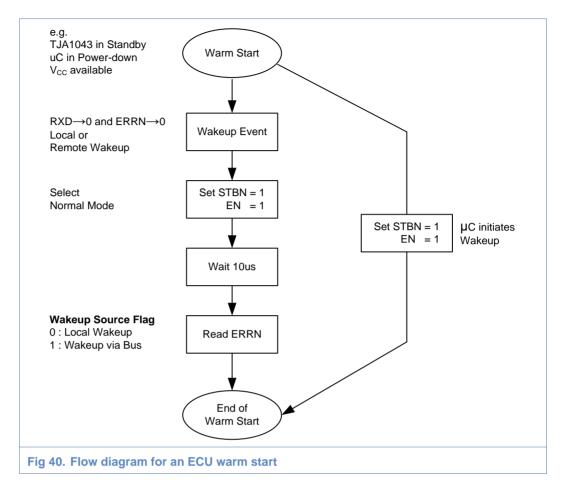

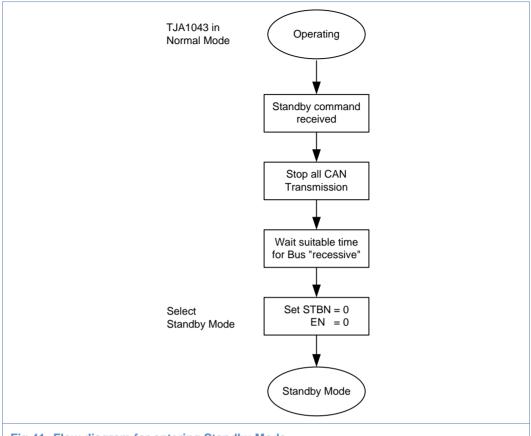

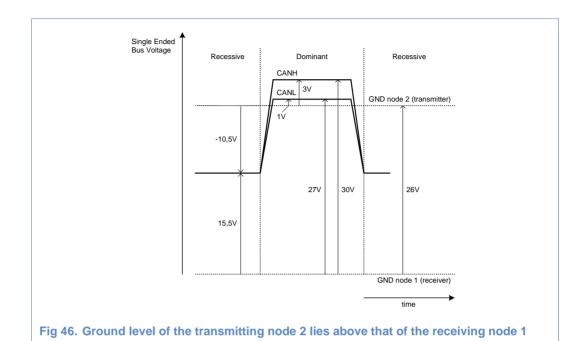

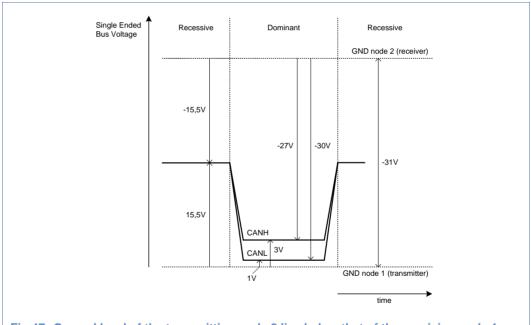

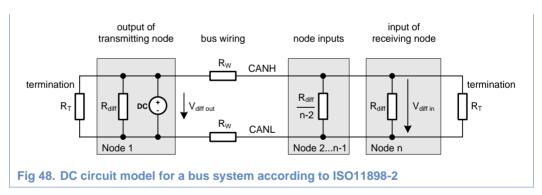

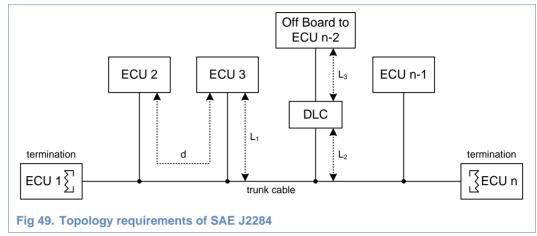

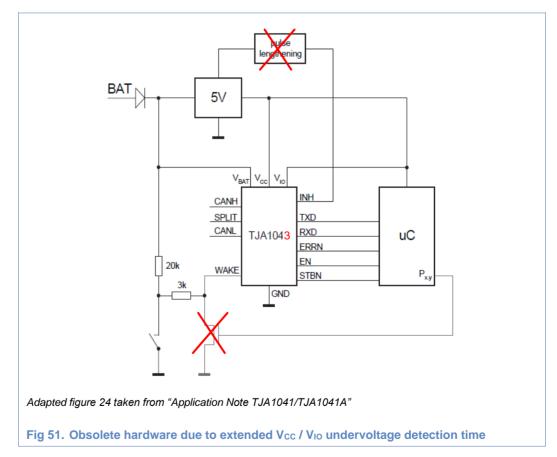

<sup>[3]</sup> Valid if V<sub>IO</sub> and V<sub>CC</sub> are present and coming from Sleep, Standby or Go-to-Sleep Mode.