# **Reset Controller**

# What you will learn

- What reset sources are available?

- How the reset inputs are handled

- How to initialize the clocks

- How to configure from reset

- How to initialize from reset

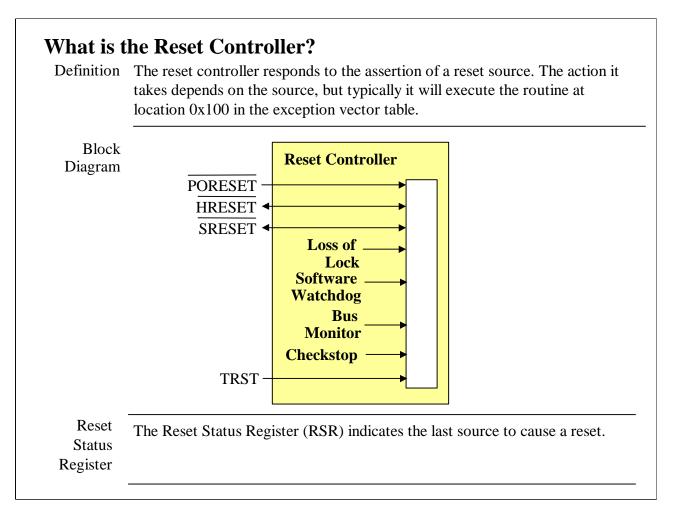

Features 1. There are eight sources of interrupts. Four are external pins and four are internal sources.

2. HRESET\* and SRESET\* are bidirectional. They can be asserted by external

2. HRESE1\* and SRESE1\* are bidirectional. They can be asserted by external devices, therefore, inputs. From PORESET, they will be asserted also, therefore they can be outputs.

Description

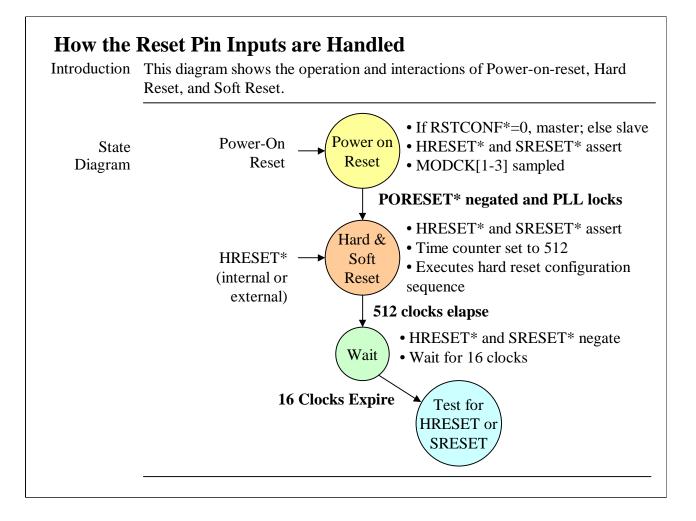

When the power-on-reset pin is asserted (for at least 16 clocks after external power is at least 2/3 VCC), the MPC8260 enters the Power on Reset State. If the RSTCONF pin is asserted, this device becomes a master, otherwise a slave.

When PORESET is negated and the PLL locks, the 8260 moves to the Hard and Soft Reset state where assertion of the hard and soft reset pins is assured for 512 clocks and the hard reset configuration occurs.

After 512 clocks elapses, the 8260 moves into the Wait state for 16 clocks. Here HRESET and SRESET are negated.

Finally, the 8260 goes into the Test for HRESET and SRESET state where, if either pin should be asserted, it will again respond.

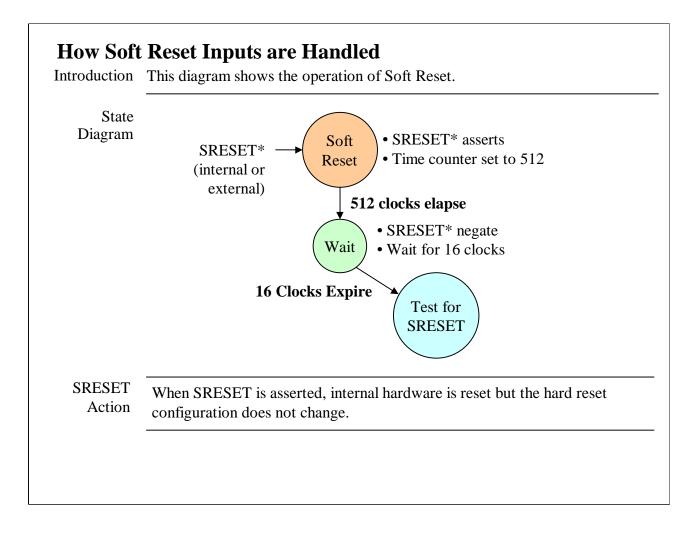

Description

1. When When SRESET is asserted, the 8260 moves into the Soft Reset state.

3. After 512 clocks elapses, the 8260 moves into the Wait state for 16 clocks. Here SRESET are negated.

4. Finally, the 8260 goes into the Test for SRESET state where, if the SRESET pin should be asserted, it will again respond.

#### How MODCK[1-3] Affect the Clocks

| Clock<br>Default<br>Modes                                                                                                                                          | MO | DCK[4-7] -<br>MODCK<br>[1-3] | data from the<br>Input<br>Clock<br>Frequency | e Hard Reset<br>CPM<br>Multiply<br>Factor | CPM<br>Frequency | on Word<br>Core<br>Multiply<br>Factor | Core<br>Frequency |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------------------------------|----------------------------------------------|-------------------------------------------|------------------|---------------------------------------|-------------------|--|

|                                                                                                                                                                    |    | 000                          | 33 MHz                                       | 3                                         | 100 MHz          | 4                                     | 133 MHz           |  |

|                                                                                                                                                                    |    | 001                          | 33 MHz                                       | 3                                         | 100 MHz          | 5                                     | 166 MHz           |  |

|                                                                                                                                                                    |    | 010                          | 33 MHz                                       | 4                                         | 133 MHz          | 4                                     | 133 MHz           |  |

|                                                                                                                                                                    |    | 011                          | 33 MHz                                       | 4                                         | 133 MHz          | 5                                     | 166 MHz           |  |

|                                                                                                                                                                    |    | 100                          | 66 MHz                                       | 2                                         | 133 MHz          | 2.5                                   | 166 MHz           |  |

|                                                                                                                                                                    |    | 101                          | 66 MHz                                       | 2                                         | 133 MHz          | 3                                     | 200 MHz           |  |

|                                                                                                                                                                    |    | 110                          | 66 MHz                                       | 2.5                                       | 166 MHz          | 2.5                                   | 166 MHz           |  |

|                                                                                                                                                                    |    | 111                          | 66 MHz                                       | 2.5                                       | 166 MHz          | 3                                     | 200 MHz           |  |

| MODCK[4-7] The defaults are with MODCK[4-7] = 0. Other core and CPM frequencies<br>are available for other values of MODCK[4-7] ranging from 66 MHz to 300<br>MHz. |    |                              |                                              |                                           |                  |                                       |                   |  |

Description 1. Here's a summary of the operating frequency options for all values of MODCK[1-3].

2. Getting some clock information from the pins and some from the configuration word is a compromise between the number of pins used and the flexibility offered. One must roughly select the clock frequencies using pins for the system to start and fetch the reset configuration word. Then a fimer tune is possible.

| RSR      | Rec     | ot St | atuel    | Paris | tor |         |          |     |     |         |    |    |      | D    | . 5-4                 |

|----------|---------|-------|----------|-------|-----|---------|----------|-----|-----|---------|----|----|------|------|-----------------------|

|          | - KCS   |       | 3 atus 1 | -     |     | 6       | 7        | 0   | 0   | 10      | 11 | 10 | 12   |      |                       |

| 0        | 1       | 2     | 3        | 4     | 5   | 6       | 7        | 8   | 9   | 10      | 11 | 12 | 13   | 14   | 13                    |

| 16       | 17      | 18    | 19       | 20    | 21  | 22      | 23       | 24  | 25  | 26      | 27 | 28 | 29   | 30   | 31                    |

|          |         |       |          |       |     |         |          |     |     | JT      | CS | SW | BM   | ES   | EF                    |

|          |         |       |          |       | -   |         |          |     |     | RS      | RS | RS | RS   | RS   | RS                    |

|          | 1       | 2     | 3        | U     | 5   | 6       | 7        | 8   | 9   | 10      | 11 | 12 | 13   |      | 5-5<br>15<br>CS<br>RE |

| Hard     | Rese    | t Cor | nfigur   | ation | woi | rd      |          |     |     |         |    |    |      | P    | 5-7                   |

| 0        | 1       | 2     | 3        | 4     | 5   | 6       | 7        | 8   | 9   | 10      | 11 | 12 | 13   | 14   | 15                    |

| EA<br>RB |         |       | EB<br>M  | Bl    | PS  | CI<br>P | IS<br>PS | L20 | CPC | DP      | PC | -  |      | ISB  |                       |

| 16       | 17      | 18    | 19       | 20    | 21  | 22      | 23       | 24  | 25  | 26      | 27 | 28 | 29   | 30   | 31                    |

| BM<br>S  | BB<br>D | M     | MR       | LB    | PC  | AP      | PPC      | CS1 | 0PC | PH<br>E | -  | Ν  | 10D0 | CK_F | Η                     |

Description 1. This is the programming model for reset.

2. In the RSR, there are 6 bits, one for each possible reset source (except TRST). These bits can be read to determine the source of the interrupt. Then the bit is cleared by writing a 1 to it.

3. RMR has one bit which determines if a checkstop will cause a reset or if it will allow the processor to stay in the checkstop state.

4. The Hard Reset Configuration Word is initialized from reset providing initial values to a number of parameters such as ISB, the initial internal space base select.

Description

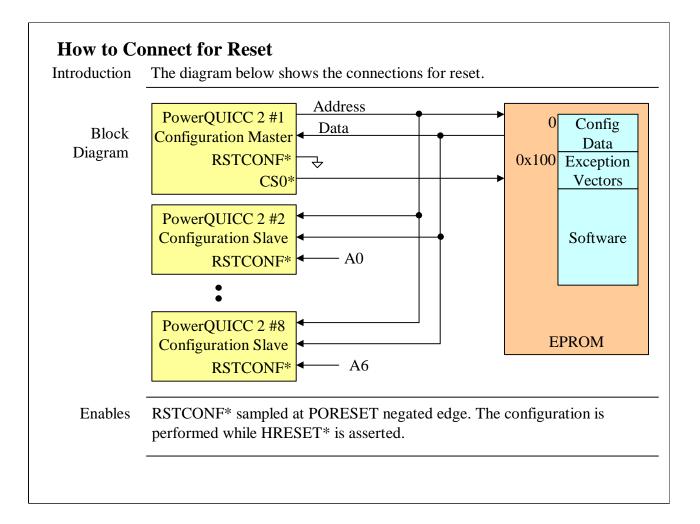

1. The PowerQUICC 2s in the system are setup such that there is one configuration master (RSTCONF always low), amd multiple slaves (RSTCONF connected to A0 to A6 as necessary).

2. Configuration data is located at address 0 of the exception table.

3. To program on-board flash from reset, the user can drive RSTCNF high to select the default configuration, program the flash, then drive RSTCONF low during subsequent resets.

| How the Master Configures the PowerQUICC 2s<br>Introduction The diagram below shows the steps in configuration. |        |     |            |                                                                   |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------|--------|-----|------------|-------------------------------------------------------------------|--|--|--|--|

| -                                                                                                               | Access | R/W | Address    | Description                                                       |  |  |  |  |

| Configuration                                                                                                   | 1      | R   | 0xFE000000 | D 141 / 1 / /                                                     |  |  |  |  |

| Master                                                                                                          | 2      | R   | 0xFE000008 | Read 4 bytes and store to                                         |  |  |  |  |

| Reset                                                                                                           | 3      | R   | 0xFE000010 | Hard Reset Config Word,<br>Master                                 |  |  |  |  |

| Steps                                                                                                           | 4      | R   | 0xFE000018 | 1viusioi                                                          |  |  |  |  |

|                                                                                                                 | 5      | R   | 0xFE000020 |                                                                   |  |  |  |  |

|                                                                                                                 | 6      | R   | 0xFE000028 | Read 4 bytes and store to<br>Hard Reset Config Word,<br>1st slave |  |  |  |  |

|                                                                                                                 | 7      | R   | 0xFE000030 |                                                                   |  |  |  |  |

|                                                                                                                 | 8      | R   | 0xFE000038 |                                                                   |  |  |  |  |

|                                                                                                                 | 9      | W   | 0x7E000000 |                                                                   |  |  |  |  |

|                                                                                                                 |        |     | •          |                                                                   |  |  |  |  |

|                                                                                                                 | 35     | R   | 0xFE0000E0 |                                                                   |  |  |  |  |

|                                                                                                                 | 36     | R   | 0xFE0000E8 | Read 4 bytes and store to                                         |  |  |  |  |

|                                                                                                                 | 37     | R   | 0xFE0000F0 | Hard Reset Config Word,                                           |  |  |  |  |

|                                                                                                                 | 38     | R   | 0xFE0000F8 | 7th slave                                                         |  |  |  |  |

|                                                                                                                 | 39     | W   | 0xFC000000 |                                                                   |  |  |  |  |

Description 1. All reads are 1 byte. All writes are 1 word.

2. Because the configuration master has no advance knowledge about the number of slaves, it always executes all accesses coming out of reset.

| –<br>PORESET*      | HRESET* and SRESET*.       | Then for PORESET* and HRESET*          |

|--------------------|----------------------------|----------------------------------------|

| l HRESET*<br>Table | Pin can be input or output | Pin is an input                        |

|                    | Pin is three-statable      | Pin is in high-impedance               |

|                    | Pin is always an output    | Pin is driven to negated logical value |

|                    |                            |                                        |

| Step | Action                                      | Example                                                    |

|------|---------------------------------------------|------------------------------------------------------------|

| 1    | MSR initialization                          | lis r3,0<br>ori r3,r3,0x1002<br>mtmsr r3                   |

| 2    | IMMR initialization                         | lis r4,0x0471<br>lis r3,0x0F01<br>stw r4,IMMR(r3)          |

| 3    | Init System Protection Reg,<br>SYPCR (4-33) | <pre>lis r3,0xFFFF ori r3,r3,0xFFC3 stw r3,SYPCR(r4)</pre> |

| 4    | Invalidate BATs                             |                                                            |

| 5    | Invalidate TLBs                             |                                                            |

| 6    | Init Clock Config Reg,SCCR<br>(9-7)         | lis r3,0<br>ori r3,r3,1<br>stw r3,SCCR(r4)                 |

| 7    | Init Bus Config Reg, BCR<br>(4-25)          | lis r3,0x100C<br>stw r3,BCR(r4)                            |

### **Steps in Initialization (1 of 4)**

Comments Step 1:Enables the machine check exception and recoverable interrupt mode.

Step 2: Initializes IMMR to a new value. The original value input to the hardware configuration word at reset must be known. If the original value is satisfactory, this step can be skipped.

Step 3: Sets up the software watchdog and bus monitor (hardware watchdog). Can be written to only one time.

Step 4: The valid bits for the Block Address Translation in the MMU can come up valid from reset. They must be invalidated.

Step 5: The Translation Lookaside Buffer entries in the MMU can come up valid from reset. They must be invalidated.

Step 6: The System Clock Control register affects low power and BRGCLK.

Step 7: Affects various configuration parameters of the 60x bus including External Bus Mode, Secondary Cache, and parity type.

| Step | Action                                                                   | Comment                                                  |

|------|--------------------------------------------------------------------------|----------------------------------------------------------|

| 8    | Init 60x Bus Arbiter Config Reg,<br>PPC_ACR (4-27)                       | li r3,2<br>stb r3,PPC_ACR(r4)                            |

| 9    | Init 60x Bus Arbitration-Level<br>Regs, PPC_ALRH & L<br>(4-28)           | lis r3,0x0126<br>ori r3,r3,0x7893<br>stw r3,PPC_ALRH(r4) |

| 10   | Init SIU Module Config Reg,SIUMCR(4-30)                                  | lis r3,0x0820<br>stw r3,SIUMCR(r4)                       |

| 11   | Init 60x Bus Transfer Error<br>Status & Control Reg, TESCR1<br>(4-34)    | li r3,0x4000<br>stw r3,TESCR1(r4)                        |

| 12   | Init Local Bus Transfer Error<br>Status & Control Reg, LTESCR1<br>(4-36) | li r3,0x4000<br>stw r3,LTESCR1(r4)                       |

| 13   | Init Memory Refresh Timer<br>Prescalar Reg, MPTPR<br>(10-32)             | li r5,0x4000<br>sth r5,MPTPR(r4)                         |

Comments Step 8: Defines the arbiter modes and the parking master on 60x bus. Step 9: Defines the arbitration priority of the various bus masters. Step 10: Selects the functionality of many of the "system" pins such as the IRQs, parity pins and L2 cache pins. Step 11: Enables (or disables) parity on 60x bus. Step 12: Enables (or disables) parity on local bus. Step 13: Initializes the refresh prescalar register.

| Step | Action                              | Comment                                                                                                                                       |

|------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 14   | Init the Memory Controller (10-1)   |                                                                                                                                               |

| 15   | Relocate the EVT from ROM<br>to RAM | <pre>vloop:<br/>addic. r3,r3,-1<br/>lwz r6,0(r5)<br/>addi r5,r5,4<br/>stw r6,0(r2)<br/>addi r2,r2,4<br/>bne vloop</pre>                       |

| 16   | Init BAT Regs                       |                                                                                                                                               |

| 17   | Init Caches                         | <pre>mfspr r5,HID0<br/>ori r5,r5,0x8800<br/>andi r6,r5,0xF7FF<br/>mtspr HID0,r5<br/>isync<br/>sync<br/>mtspr HID0,r6<br/>isync<br/>sync</pre> |

Comments Step 14:Initialize the memory contoller for the desired configuration. Step 15: Relocate the exception vector table from ROM to RAM. If necessary, MSR[IP] should be changed. Step 16: Initialize and enable the MMU. In this example, only Block Address Translation is used. If Page Translation is to be used, it should be initialized here also. Step 17: Initialize and enable the caches.

### **Steps in Initialization (4 of 4)**

| Step | Action                 | Comment                                                    |

|------|------------------------|------------------------------------------------------------|

| 18   | Init the Stack Pointer | Lis r1,SP_INIT@h<br>ori r1,r1,SP_INIT@l<br>stwu r0,-72(r1) |

Comments Step 18: Initialize the stack pointer, r1.