# DSP56654 Baseband Digital Signal Processor

User's Manual

Rev. 0, 08/1999

DigitalDNA, M•CORE, Mfax, and OnCE are trademarks of Motorola, Inc.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use. even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part.

Motorola and All other tradenames, trademarks, and registered trademarks are the property of their respective owners.

#### How to reach us:

**USA/EUROPE/Locations Not Listed**: Motorola Literature Distribution; P.O. Box 5405, Denver, Colorado, 80217 1-303-675-2140 or 1-800-441-2447

**JAPAN**: Motorola Japan, Ltd.; SPS, Technical Information Center, 3-20-1, Minami-Azabu, Minato-ku, Tokyo 106-8573 Japan. 81-3-3440-3569

**ASIA/PACIFIC**: Motorola Semiconductors H.K. Ltd., Silicon Harbour Centre, 2 Dai King Street, Tai Po Industrial Estate, 2 Tai Po, N.T., Hong Kong. 852-26668334

Customer Focus Center: 1-800-521-6274

Mfax™: RMFAX0@email.sps.mot.com —TOUCHTONE 1-602-244-6609

-US & Canada ONLY 1-800-774-1848

-http://sps.motorola.com/mfax/

HOME PAGE: http://motorola.com/sps

Motorola DSP Products Home Page: http://www.motorola-dsp.com

© Copyright Motorola, Inc., 1999. All rights reserved.

# **Table of Contents**

#### **Preface**

# Chapter 1 Introduction

| 1.1   | DSP56654 Key Features                   |

|-------|-----------------------------------------|

| 1.2   | Architecture Overview                   |

| 1.2.1 | MCU                                     |

| 1.2.2 | DSP                                     |

| 1.2.3 | MCU–DSP Interface                       |

|       |                                         |

|       | Chapter 2                               |

|       | Signal/Connection Description           |

| 2.1   | Power                                   |

| 2.2   | Ground                                  |

| 2.3   | Clock and Phase-Locked Loop             |

| 2.4   | External Interface Module               |

| 2.5   | Reset, Mode, and Multiplexer Control2-7 |

| 2.6   | DSP X/Y Visibility Port                 |

| 2.7   | Interrupts                              |

| 2.8   | Protocol Timer                          |

| 2.9   | Keypad Port                             |

| 2.10  | UARTA                                   |

| 2.11  | UARTB 2-17                              |

| 2.12  | QSPIA 2-17                              |

| 2.13  | QSPIB                                   |

| 2.14  | SCP2-19                                 |

| 2.15  | SAP 2-20                                |

| 2.16  | BBP                                     |

| 2.17  | MCU Emulation Port                      |

| 2.18  | Debug Port Control                      |

| 2 19  | ITAG Test Access Port 2-23              |

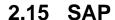

## Chapter 3 Memory Maps

| 3.1   | MCU Memory Map                          | 3-1 |

|-------|-----------------------------------------|-----|

| 3.1.1 | ROM                                     | 3-1 |

| 3.1.2 | RAM                                     | 3-3 |

| 3.1.3 | Memory-Mapped Peripherals               | 3-3 |

| 3.1.4 | External Memory Space                   | 3-4 |

| 3.1.5 | Reserved Memory                         | 3-4 |

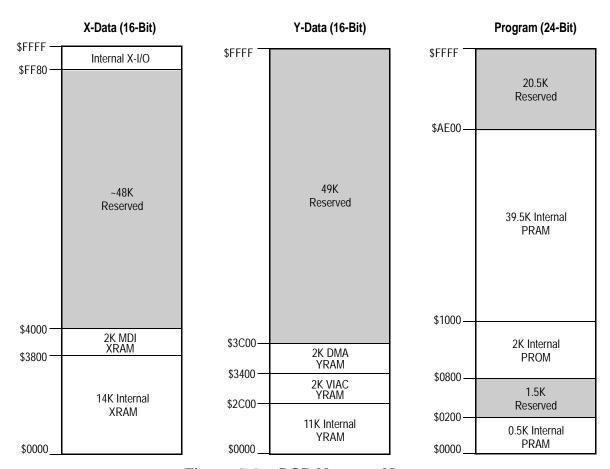

| 3.2   | DSP Memory Map and Descriptions         | 3-4 |

| 3.2.1 | X Data Memory                           | 3-5 |

| 3.2.2 | Y Data Memory                           | 3-6 |

| 3.2.3 | Program Memory                          | 3-6 |

| 3.2.4 | Reserved Memory                         | 3-6 |

|       |                                         |     |

|       | Chapter 4                               |     |

|       | Core Operation and Configuration        |     |

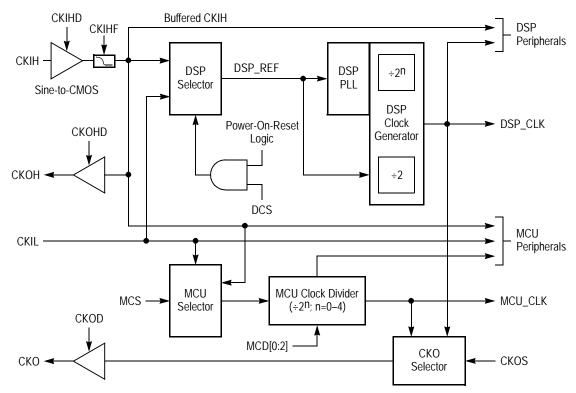

| 4.1   | Clock Generation                        | 4-1 |

| 4.1.1 | MCU_CLK                                 | 4-2 |

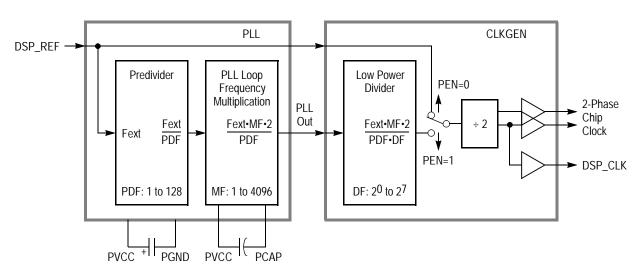

| 4.1.2 | DSP_CLK                                 | 4-3 |

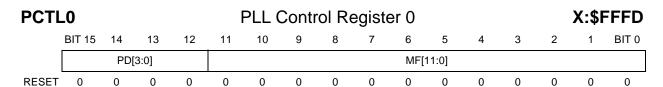

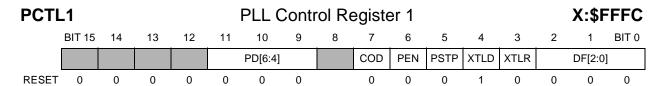

| 4.1.3 | Clock and PLL Registers                 | 4-5 |

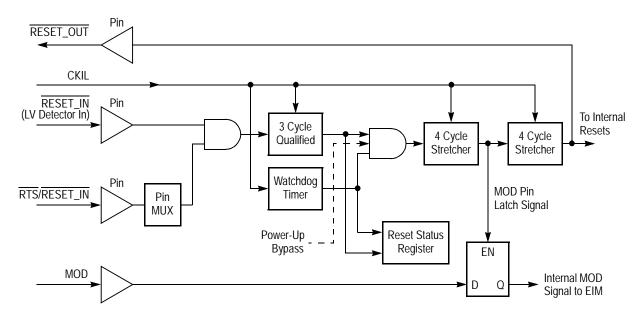

| 4.2   | Low Power Modes                         | 4-8 |

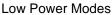

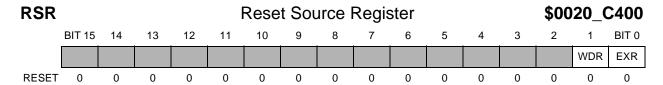

| 4.3   | Reset                                   | 4-9 |

| 4.3.1 | MCU Reset 4                             | -11 |

| 4.3.2 | DSP Reset                               | -12 |

| 4.4   | DSP Configuration                       | -12 |

| 4.4.1 | Operating Mode Register                 | -12 |

| 4.4.2 | Patch Address Registers4                | -14 |

| 4.4.3 | Device Identification Register          | -15 |

| 4.5   | I/O Multiplexing                        | -15 |

| 4.5.1 | DSP Program Address Visibility          |     |

| 4.5.2 | DSP X/Y Data Visibility                 | -18 |

| 4.5.3 | JTAG Debug Port                         | -20 |

| 4.5.4 | Timer Multiplexing 4                    | -21 |

| 4.5.5 | General-Purpose Port Control Register 4 | -22 |

#### Chapter 5 MCU–DSP Interface

| 5.1   | MDI Memory                                |

|-------|-------------------------------------------|

| 5.1.1 | DSP-Side Memory Mapping                   |

| 5.1.2 | MCU-Side Memory Mapping                   |

| 5.1.3 | Shared Memory Access Contention 5-3       |

| 5.1.4 | Shared Memory Timing                      |

| 5.2   | MDI Messages and Control                  |

| 5.2.1 | MDI Messaging System 5-6                  |

| 5.2.2 | Message Protocols                         |

| 5.2.3 | MDI Interrupt Sources                     |

| 5.2.4 | Event Update Timing                       |

| 5.2.5 | MCU-DSP Troubleshooting                   |

| 5.3   | Low-Power Modes                           |

| 5.3.1 | MCU Low-Power Modes                       |

| 5.3.2 | DSP Low-Power Modes                       |

| 5.3.3 | Shared Memory in DSP STOP Mode            |

| 5.4   | Resetting the MDI                         |

| 5.5   | MDI Software Restriction Summary          |

| 5.6   | MDI Registers                             |

| 5.6.1 | MCU-Side Registers                        |

| 5.6.2 | DSP-Side Registers                        |

|       |                                           |

|       | Chapter 6 External Interface Module       |

|       |                                           |

| 6.1   | EIM Signals                               |

| 6.2   | Chip Select Address Ranges                |

| 6.3   | EIM Features                              |

| 6.3.1 | Configurable Bus Sizing                   |

| 6.3.2 | External Boot ROM Control 6-5             |

| 6.3.3 | Bus Watchdog Operation                    |

| 6.3.4 | Error Conditions6-7                       |

| 6.3.5 | Displaying the Internal Bus (Show Cycles) |

| 6.3.6 | Programmable Output Generation 6-7        |

| 6.3.7 | Emulation Port                            |

| 6.4   | EIM Registers                             |

# Chapter 7 Interrupts

| 7.1   | MCU Interrupt Controller                                |

|-------|---------------------------------------------------------|

| 7.1.1 | Functional Overview                                     |

| 7.1.2 | Exception Priority                                      |

| 7.1.3 | Enabling MCU Interrupt Sources                          |

| 7.1.4 | Interrupt Sources                                       |

| 7.1.5 | MCU Interrupt Registers                                 |

| 7.2   | DSP Interrupt Controller                                |

| 7.2.1 | DSP Interrupt Sources                                   |

| 7.2.2 | Enabling DSP Interrupt Sources                          |

| 7.2.3 | DSP Interrupt Control Registers                         |

| 7.3   | Edge Port                                               |

|       |                                                         |

|       | Chapter 8                                               |

|       | Queued Serial Peripheral Interfaces                     |

| 8.1   | Features                                                |

| 8.1.1 | Programmable Baud Rates 8-2                             |

| 8.1.2 | Programmable Queue Lengths and Continuous Transfers 8-2 |

| 8.1.3 | Programmable Peripheral Chip-Selects 8-2                |

| 8.1.4 | Programmable Queue Pointers 8-3                         |

| 8.1.5 | Four Transfer Activation Triggers                       |

| 8.1.6 | Programmable Delay after Transfer 8-3                   |

| 8.1.7 | Loading a Programmable Address at the End of Queue      |

| 8.1.8 | Pause Enable at Queue Entry Boundaries 8-3              |

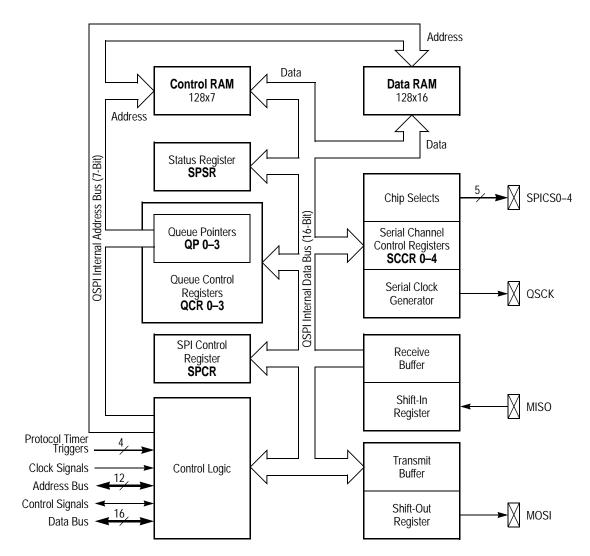

| 8.2   | QSPI Architecture                                       |

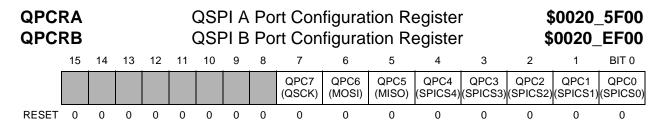

| 8.2.1 | QSPI Pins                                               |

| 8.2.2 | Control Registers                                       |

| 8.2.3 | Functional Modules                                      |

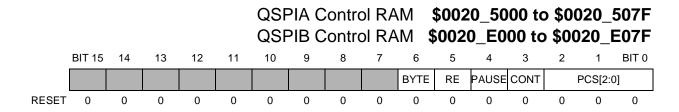

| 8.2.4 | RAM 8-7                                                 |

| 8.3   | QSPI Operation                                          |

| 8.3.1 | Initialization                                          |

| 8.3.2 | Queue Transfer Cycle 8-9                                |

| 8.3.3 | Ending a Transfer Cycle 8-10                            |

| 8.3.4 | Breaking a Transfer Cycle 8-10                          |

| 8.3.5 | Halting the QSPI 8-11                                   |

| 8.3.6 | Error Interrupts 8-11                                   |

| 8.3.7 | Low Power Modes                                         |

| 8.4   | OSPI Registers and Memory                               |

| 8.4.1  | QSPI Control Registers            |

|--------|-----------------------------------|

| 8.4.2  | MCU Transfer Triggers             |

| 8.4.3  | Control And Data RAM 8-23         |

| 8.4.4  | GPIO Registers                    |

|        |                                   |

|        | Chapter 9                         |

|        | Timers                            |

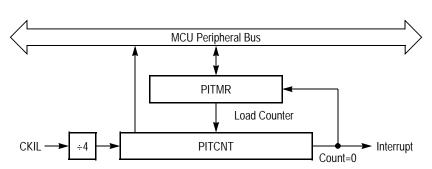

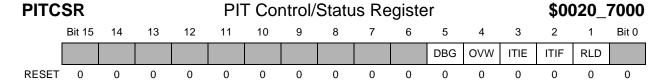

| 9.1    | Periodic Interrupt Timer          |

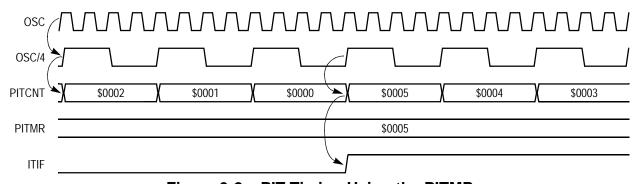

| 9.1.1  | PIT Operation                     |

| 9.1.2  | PIT Registers                     |

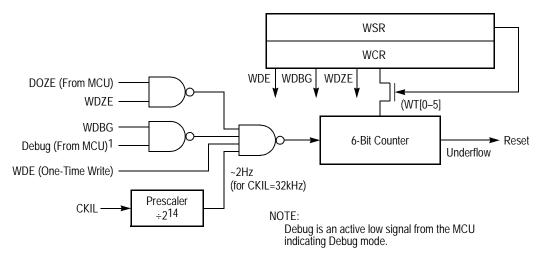

| 9.2    | Watchdog Timer                    |

| 9.2.1  | Watchdog Timer Operation          |

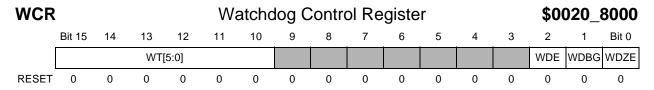

| 9.2.2  | Watchdog Timer Registers9-6       |

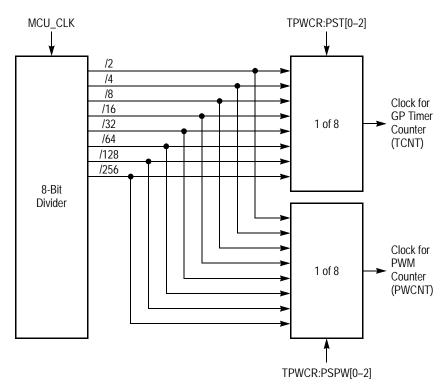

| 9.3    | GP Timer and PWM                  |

| 9.3.1  | GP Timer                          |

| 9.3.2  | Pulse Width Modulator             |

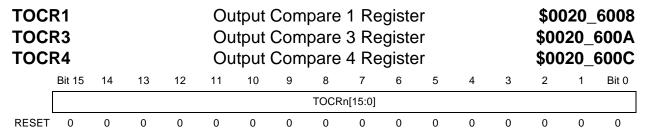

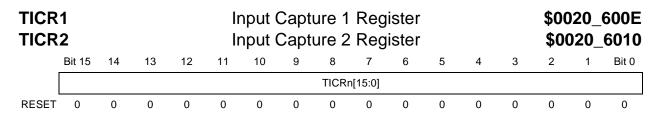

| 9.3.3  | GP Timer and PWM Registers9-13    |

|        |                                   |

|        | Chapter 10                        |

|        | Protocol Timer                    |

| 10.1   | Protocol Timer Architecture       |

| 10.1.1 | Timing Signals and Components     |

| 10.1.2 | 2 Event Table                     |

| 10.1.3 | B Event Generation                |

| 10.2   | PT Operation                      |

| 10.2.1 | Frame Events                      |

| 10.2.2 |                                   |

| 10.2.3 | 3 Operating Modes                 |

| 10.2.4 | 4 Error Detection                 |

| 10.2.5 | 5 Interrupts                      |

| 10.2.6 | 1 1 ' '                           |

| 10.3   | PT Event Codes                    |

| 10.4   | PT Registers                      |

| 10.4.1 |                                   |

| 10.4.2 | $\epsilon$                        |

| 10.5   | Protocol Timer Programing Example |

#### Chapter 11 UARTs

| 11.1   | UART Definitions                |

|--------|---------------------------------|

| 11.2   | UART Architecture               |

| 11.2.1 | Transmitter                     |

| 11.2.2 | Receiver                        |

| 11.2.3 | Clock Generator                 |

| 11.2.4 | Infrared Interface              |

| 11.2.5 | UART Pins                       |

| 11.2.6 | Frame Configuration             |

| 11.3   | UART Operation                  |

| 11.3.1 | Transmission                    |

| 11.3.2 | Reception                       |

| 11.3.3 |                                 |

| 11.3.4 |                                 |

| 11.3.5 |                                 |

| 11.3.6 | 8                               |

|        | UART Registers                  |

| 11.4.1 |                                 |

| 11.4.2 | GPIO Registers                  |

|        | Chapter 12                      |

|        | Chapter 12<br>Smart Card Port   |

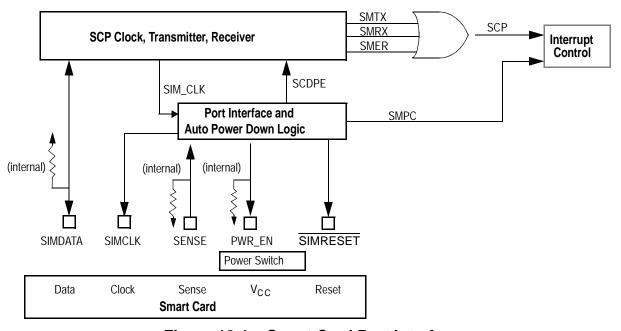

| 12.1   | SCP Architecture                |

| 12.1.1 |                                 |

| 12.1.2 |                                 |

| 12.1.3 | Power Up/Down                   |

| 12.2   | SCP Operation                   |

| 12.2.1 | Activation/Deactivation Control |

| 12.2.2 | Clock Generation                |

| 12.2.3 | Data Transactions               |

| 12.2.4 | Low Power Modes                 |

| 12.2.5 | Interrupts                      |

| 12.3   | SCP Registers                   |

| 12.3.1 | SCP Control Registers           |

| 12.3.2 | GPIO                            |

## Chapter 13 Keypad Port

| 13.1 Keypad Operation                      |       |

|--------------------------------------------|-------|

| 13.1.1 Pin Configuration                   | 13-2  |

| 13.1.2 Keypad Matrix Polling               | 13-3  |

| 13.1.3 Standby and Low Power Operation     | 13-3  |

| 13.1.4 Noise Suppression on Keypad Inputs  | 13-3  |

| 13.2 Keypad Port Registers                 | 13-4  |

| Chapter 14                                 |       |

| Chapter 14 Serial Audio and Baseband Ports |       |

| 14.1 Data and Control Pins                 | 1/1_3 |

| 14.2 Transmit and Receive Clocks           |       |

| 14.2.1 Clock Sources                       |       |

| 14.2.2 Clock Frequency                     |       |

| 14.2.3 Clock Polarity                      |       |

| 14.2.4 Bit Rate Multiplier (SAP Only)      |       |

| 14.3 TDM Options                           |       |

| 14.3.1 Synchronous and Asynchronous Modes  |       |

| 14.3.2 Frame Configuration                 |       |

| 14.3.3 Frame Sync                          |       |

| 14.3.4 Serial I/O Flags                    | 14-9  |

| 14.3.5 TDM Interrupts                      | 14-9  |

| 14.4 Data Transmission and Reception       |       |

| 14.4.1 Data Transmission                   | 14-10 |

| 14.4.2 Data Reception                      | 14-12 |

| 14.4.3 Data Formats                        | 14-13 |

| 14.5 Software Reset                        | 14-13 |

| 14.6 General-Purpose Timer (SAP Only)      | 14-13 |

| 14.7 Frame Counters (BBP Only)             | 14-14 |

| 14.8 Interrupts                            | 14-15 |

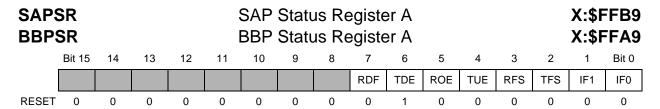

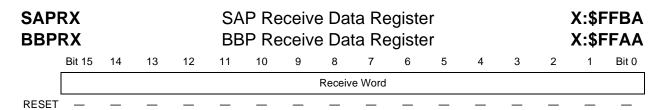

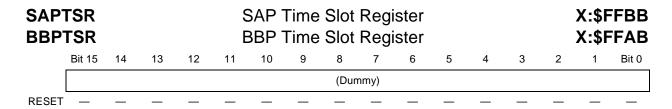

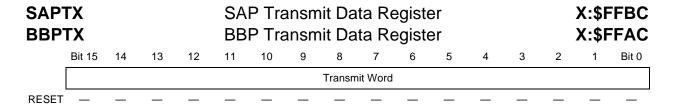

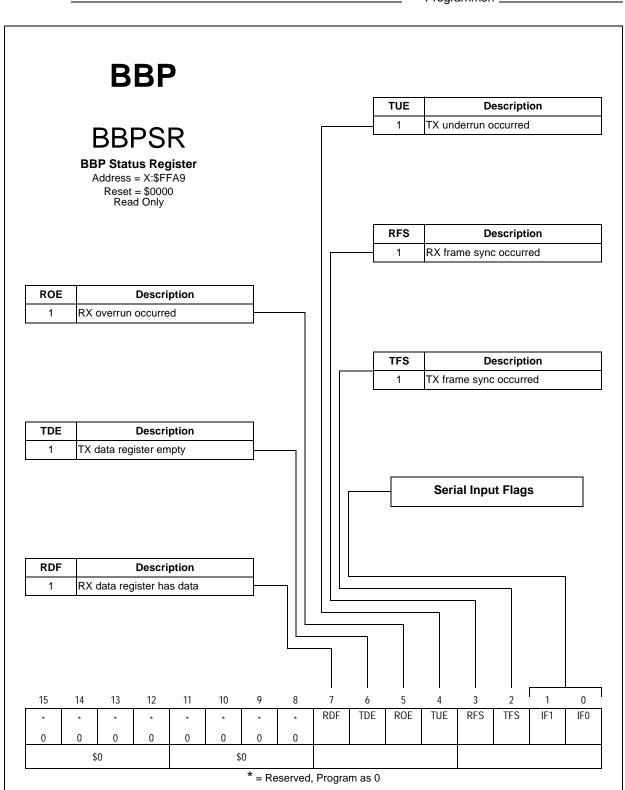

| 14.9 SAP and BBP Control Registers         | 14-16 |

| 14.9.1 SAP and BBP Control Registers       | 14-18 |

| 14.9.2 GPIO Registers                      | 14-25 |

## Chapter 15 DSP Peripheral DMA Controller

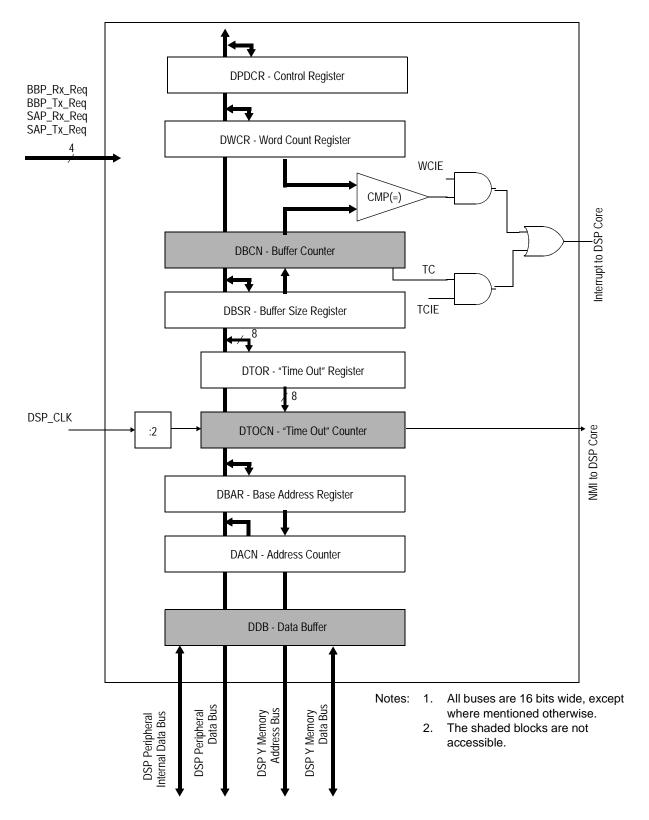

| 15.1 DPD Architecture                           |

|-------------------------------------------------|

| 15.2 DPD Operation                              |

| 15.2.1 DPD Setup                                |

| 15.2.2 Initiating a DPD Transfer                |

| 15.2.3 The DPD Transfer Process                 |

| 15.2.4 DPD Operation in Low Power Modes         |

| 15.3 DPD Registers                              |

|                                                 |

| Chapter 16                                      |

| Viterbi Accelerator                             |

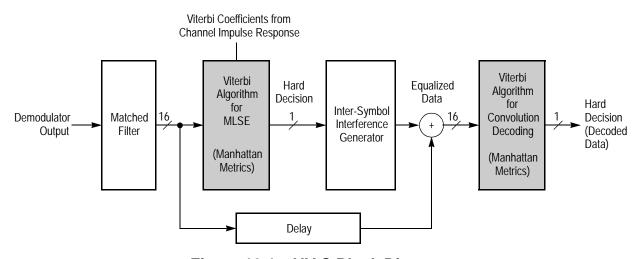

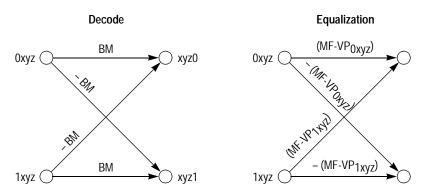

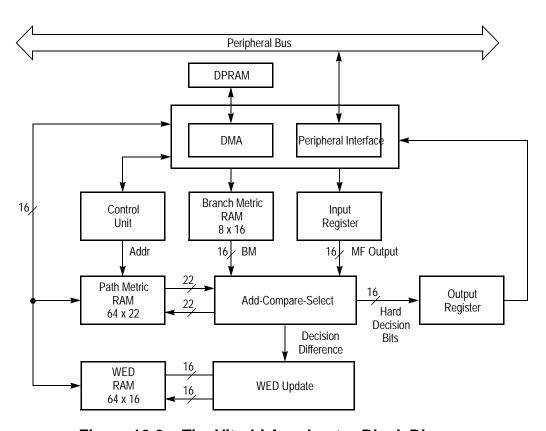

| 16.1 The Viterbi Butterfly Implementation       |

| 16.2 VIAC Architecture                          |

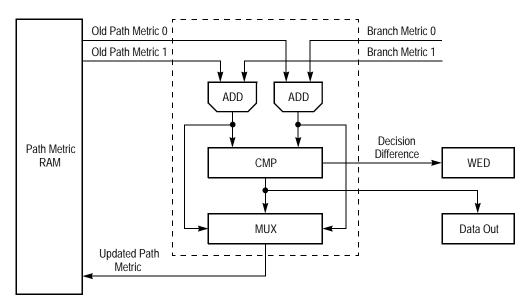

| 16.2.1 ACS                                      |

| 16.2.2 WED                                      |

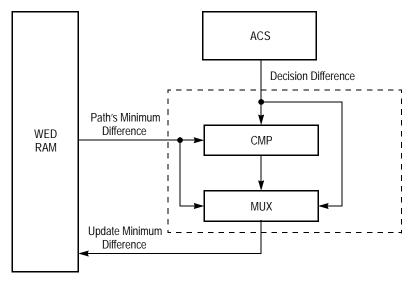

| 16.2.3 Path Metric RAM                          |

| 16.2.4 Branch Metric RAM                        |

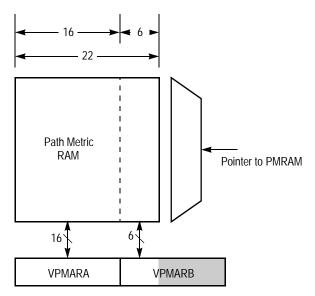

| 16.2.5 DMA                                      |

| 16.3 VIAC Pipeline                              |

| 16.3.1 VIAC Throughput                          |

| 16.3.2 Pipeline Content and Timing              |

| 16.3.3 Pipeline Structure                       |

| 16.4 VIAC Operation                             |

| 16.4.1 VIAC Operational States                  |

| 16.4.2 VIAC Operation In Equalization           |

| 16.4.3 VIAC Operation In Convolutional Decoding |

| 16.4.4 VIAC interrupts                          |

| 16.5 Control Registers                          |

#### Chapter 17 JTAG Port

| 17.1       | DSP56600 Core JTAG Operation              |

|------------|-------------------------------------------|

| 17.1.1     | JTAG Pins                                 |

| 17.1.2     | DSP TAP Controller                        |

| 17.1.3     | Instruction Register                      |

| 17.2       | Test Registers                            |

| 17.2.1     | Boundary Scan Register (BSR)              |

| 17.2.2     | Bypass Register                           |

| 17.2.3     | Identification Register                   |

| 17.3       | DSP56654 JTAG Port Restrictions           |

| 17.3.1     | Normal Operation                          |

| 17.3.2     | Test Modes                                |

| 17.3.3     | STOP Mode                                 |

| 17.4       | MCU TAP Controller                        |

| 17.4.1     | Entering MCU OnCE Mode via JTAG Control   |

| 17.4.2     | Release from Debug Mode for DSP and MCU   |

|            | A 11 A                                    |

|            | Appendix A<br>DSP56654 DSP Bootloader     |

| A.1        | Boot Modes                                |

| A.2        | Mode A: Normal MDI Boot                   |

| A.2.1      | Short and Long Messages                   |

| A.2.2      | Message Descriptions                      |

| A.2.3      | Comments on Normal Boot Mode Usage        |

| A.2.4      | Example of Program Download and Execution |

| A.3        | Mode B: Shared Memory Boot                |

| A.4        | Mode C: Messaging Unit Boot               |

| A.5        | Bootstrap Program                         |

|            | Annandiy P                                |

|            | Appendix B Equates and Header Files       |

| D 1        | MCU EquatesB-1                            |

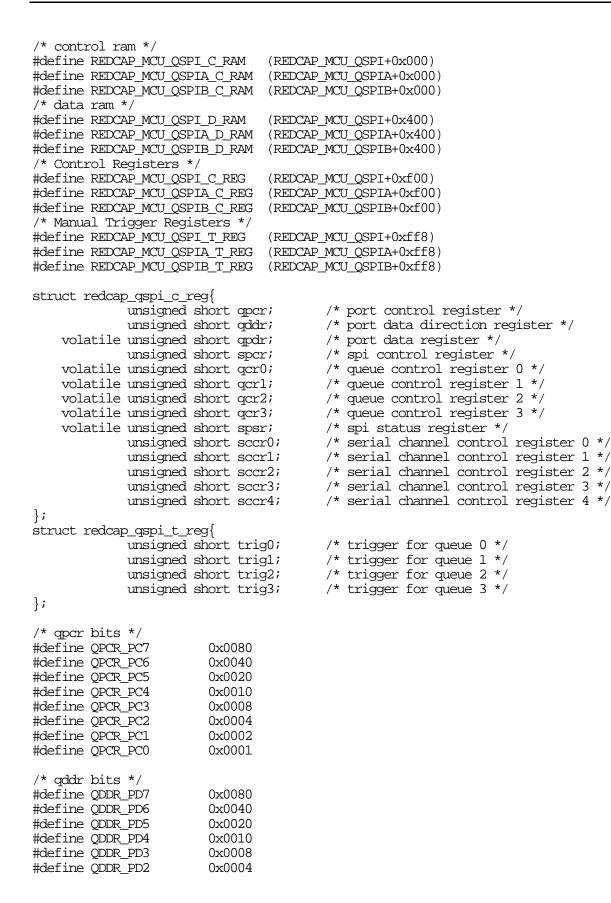

| B.1<br>B.2 | MCU Include File                          |

| B.3        |                                           |

| D.3        | DSP Equates                               |

| Appendix C            |   |

|-----------------------|---|

| Boundary Scan Registe | r |

| C.1 | BSR Bit Definitions                  |

|-----|--------------------------------------|

| C.2 | Boundary Scan Description Language   |

|     | Appendix D<br>Programmer's Reference |

| D.1 | MCU Instruction Reference Tables     |

| D.2 | DSP Instruction Reference Tables     |

| D.3 | MCU Internal I/O Memory Map          |

| D.4 | DSP Internal I/O Memory Map          |

| D.5 | Register Index                       |

| D.6 | Acronym Changes                      |

Appendix E Programmer's Data Sheets

# **List of Figures**

| Figure 1-1. | DSP56654 Block Diagram                                | 1-2  |

|-------------|-------------------------------------------------------|------|

| Figure 2-1. | Signal Group Organization                             | 2-2  |

| Figure 3-1. | MCU Memory Map                                        | 3-2  |

| Figure 3-2. | DSP Memory Map                                        | 3-5  |

| Figure 4-1. | DSP56654 Clock Scheme                                 | 4-2  |

| Figure 4-2. | DSP PLL and Clock Generator                           | 4-3  |

| Figure 4-3. | DSP56654 Reset Circuit                                | 4-10 |

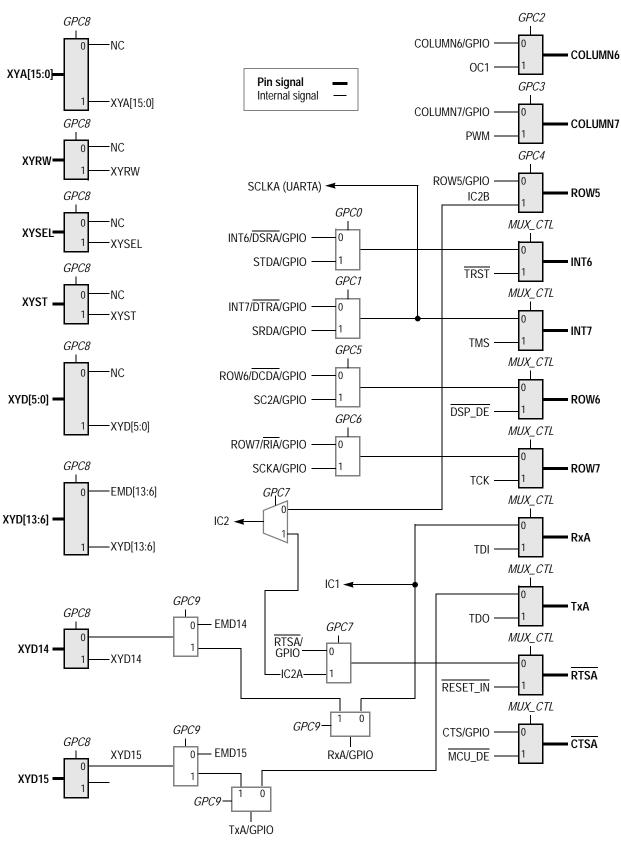

| Figure 4-4. | MUX Connectivity Scheme                               | 4-16 |

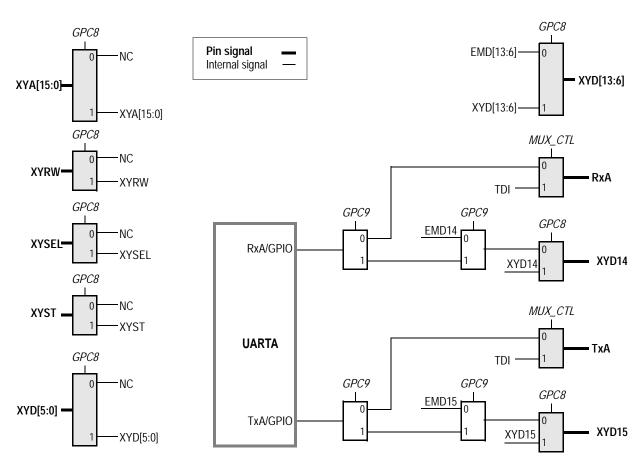

| Figure 4-5. | XYDV Pins and Alternate Functions                     | 4-19 |

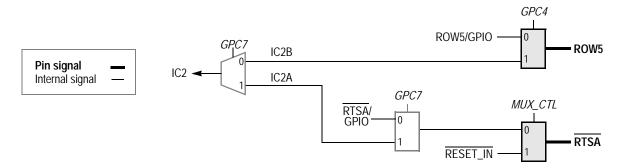

| Figure 4-6. | IC2 Signal Sources                                    | 4-21 |

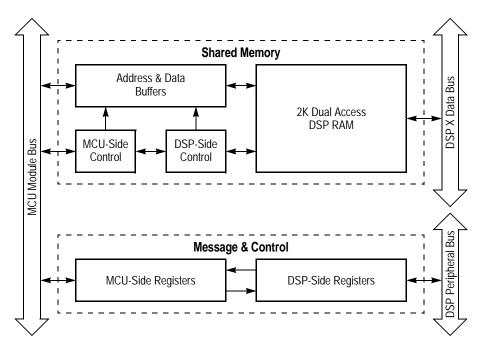

| Figure 5-1. | MDI Block Diagram                                     | 5-1  |

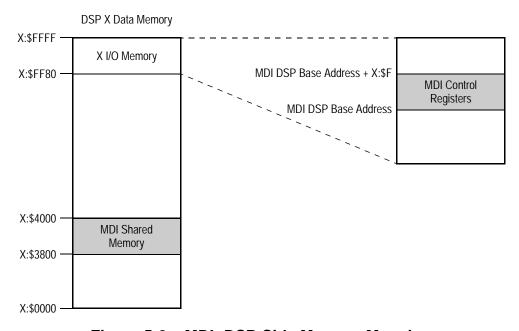

| Figure 5-2. | MDI: DSP-Side Memory Mapping                          | 5-2  |

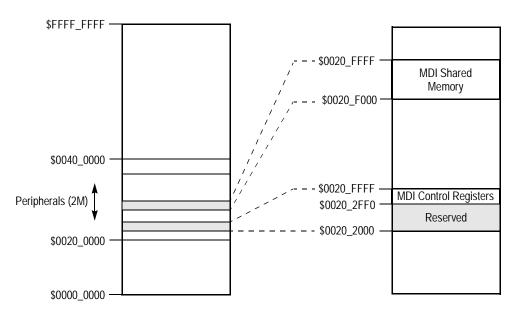

| Figure 5-3. | MDI: MCU-Side Memory Mapping                          | 5-3  |

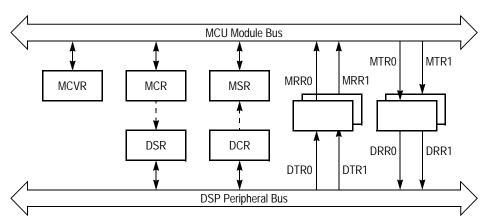

| Figure 5-4. | MDI Register Symmetry                                 | 5-7  |

| Figure 5-5. | MDI Message Exchange                                  | 5-8  |

| Figure 5-6. | DSP-to-MCU General Purpose Interrupt                  | 5-9  |

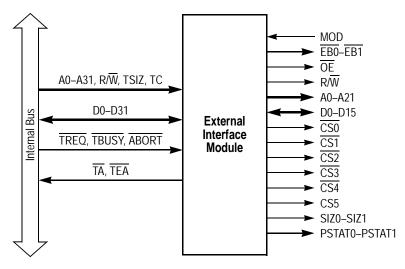

| Figure 6-1. | EIM Block Diagram                                     | 6-1  |

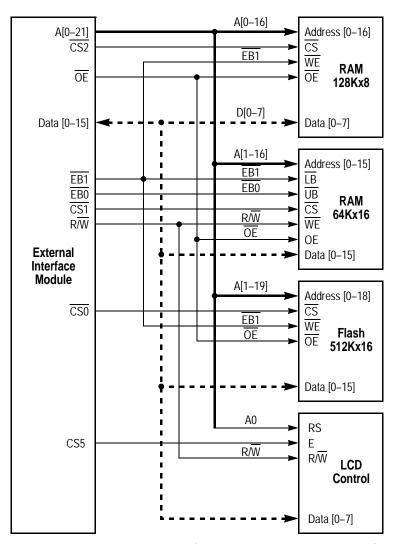

| Figure 6-2. | Example EIM Interface to Memory and Peripherals       | 6-2  |

| Figure 7-1. | MCU Interrupt Controller                              | 7-2  |

| Figure 7-2. | Hardware Priority Flowchart                           | 7-3  |

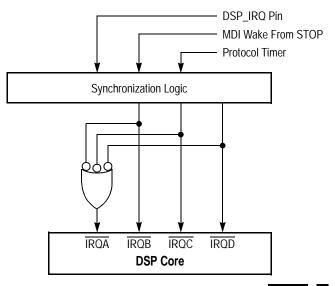

| Figure 7-3. | Internal Connection of $\overline{IRQA}-\overline{D}$ | 7-12 |

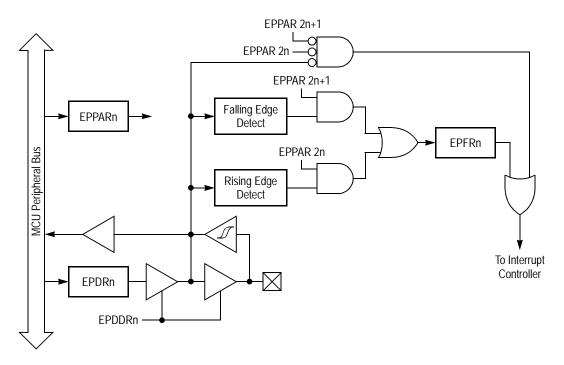

| Figure 7-4. | Edge I/O Pin                                          | 7-18 |

| Figure 8-1. | QSPI Signal Flow                                      | 8-5  |

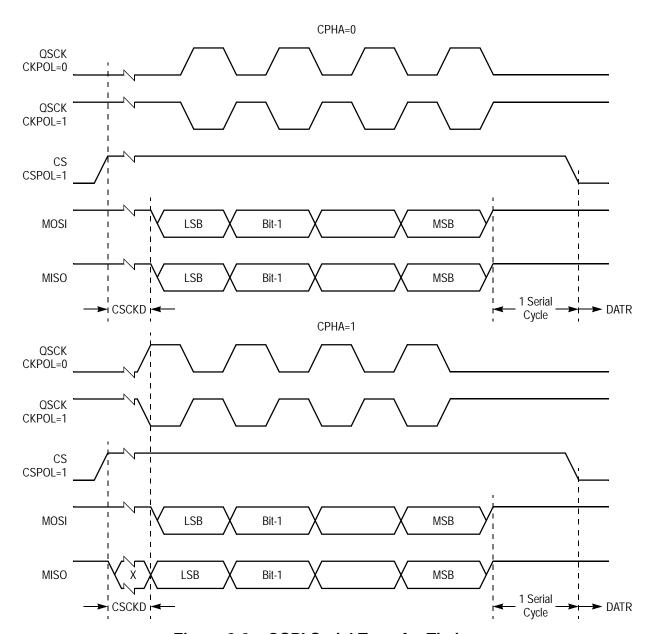

| Figure 8-2. | QSPI Serial Transfer Timing                           | 8-22 |

| Figure 9-1. | PIT Block Diagram                                     | 9-2  |

| Figure 9-2. | PIT Timing Using the PITMR                            | 9-2  |

| Figure 9-3. | Watchdog Timer Block Diagram                          | 9-5  |

| Figure 9-4.  | GP Timer/PWM Clocks                                      |

|--------------|----------------------------------------------------------|

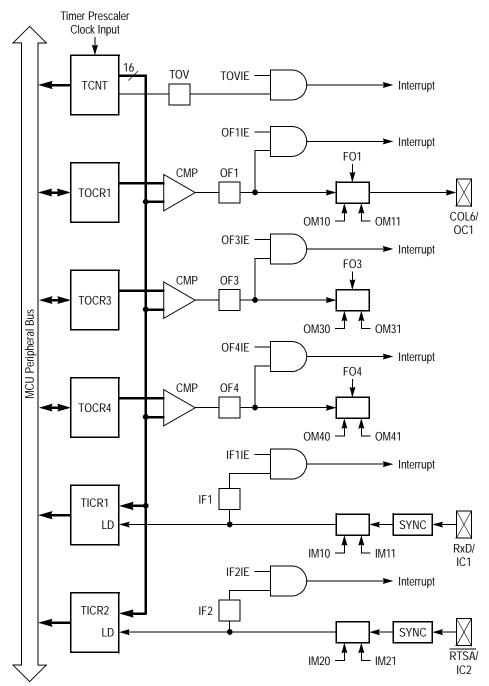

| Figure 9-5.  | GP Timer Block Diagram                                   |

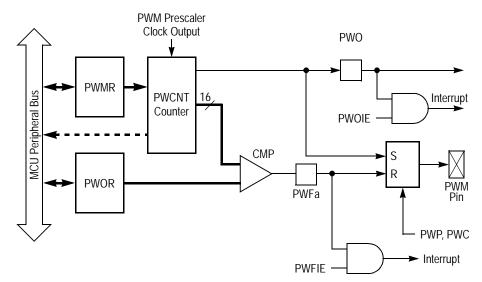

| Figure 9-6.  | PWM Block Diagram                                        |

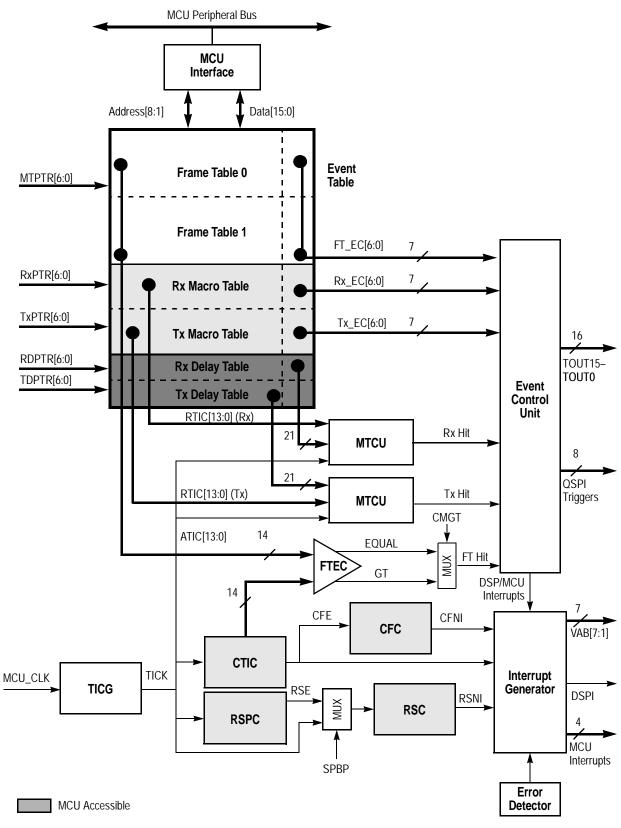

| Figure 10-1. | Protocol Timer Block Diagram                             |

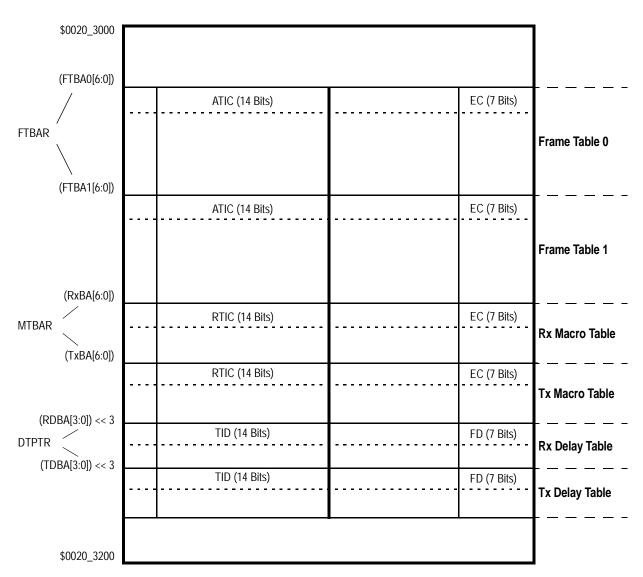

| Figure 10-2. | Event Table Structure                                    |

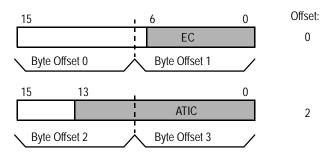

| Figure 10-3. | Frame Table Entry                                        |

| Figure 10-4. | Macro Table Entry                                        |

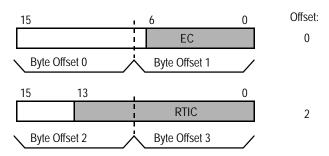

| Figure 10-5. | Delay Table Entry                                        |

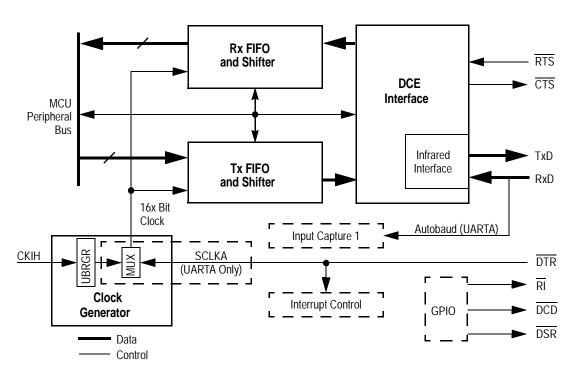

| Figure 11-1. | UART Block Diagram                                       |

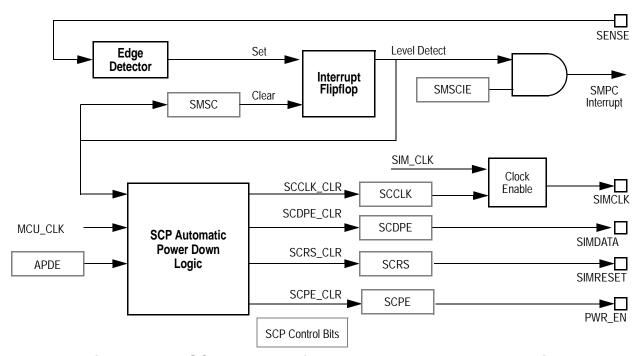

| Figure 12-1. | Smart Card Port Interface                                |

| Figure 12-2. | SCP: Port Interface and Auto Power Down Logic            |

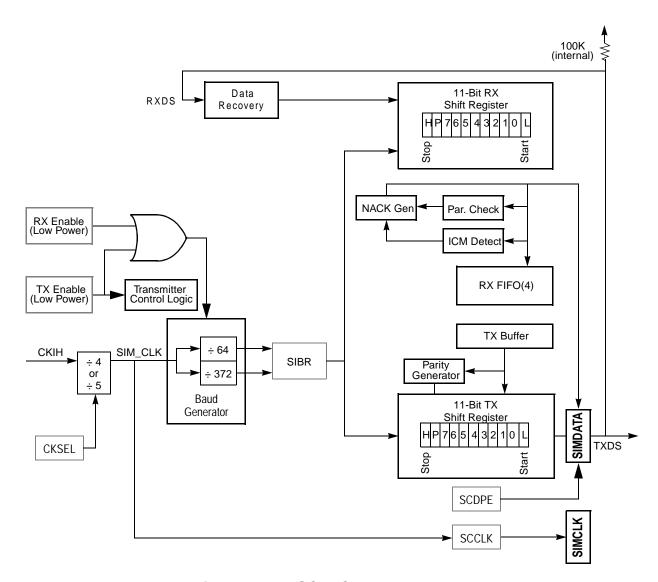

| Figure 12-3. | SCP: Clocks and Data                                     |

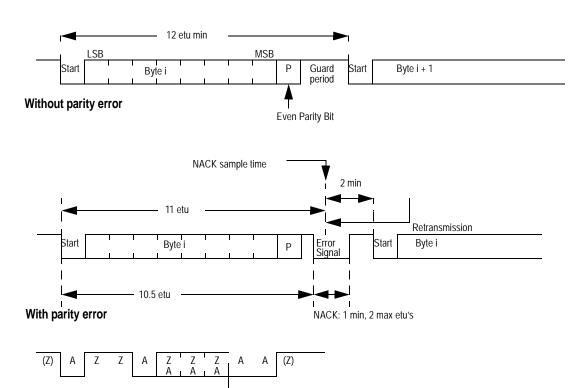

| Figure 12-4. | SCP Data Formats                                         |

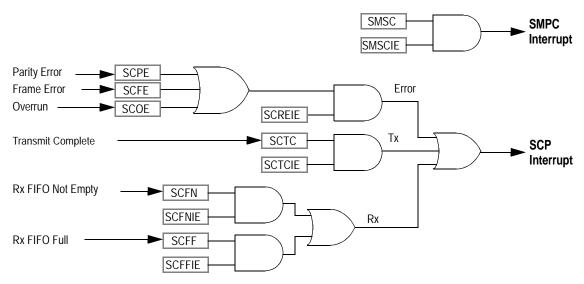

| Figure 12-5. | SCP Interrupts                                           |

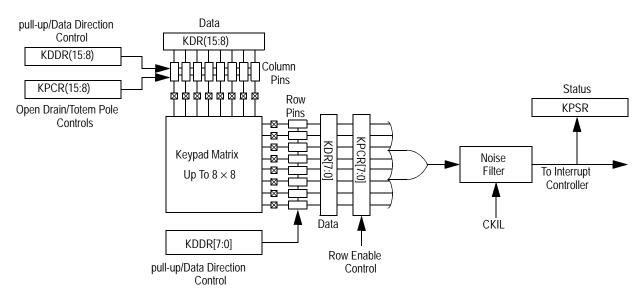

| Figure 13-1. | Keypad Port Block Diagram                                |

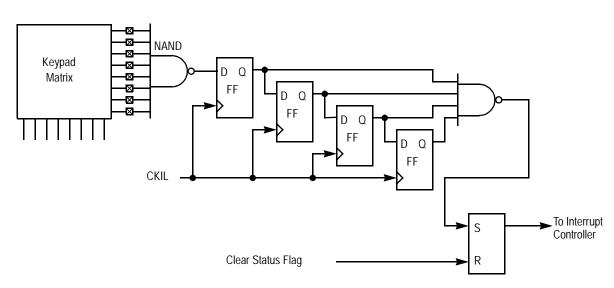

| Figure 13-2. | Glitch Suppressor Functional Diagram                     |

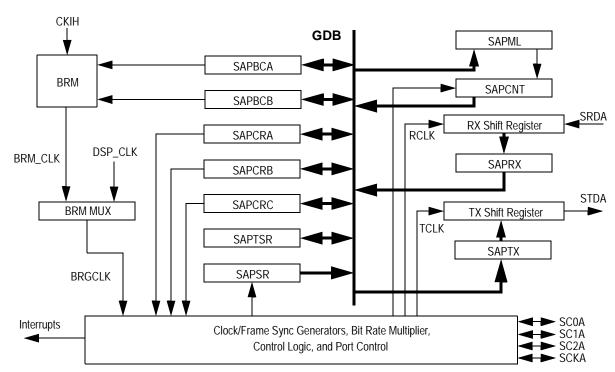

| Figure 14-1. | SAP Block Diagram                                        |

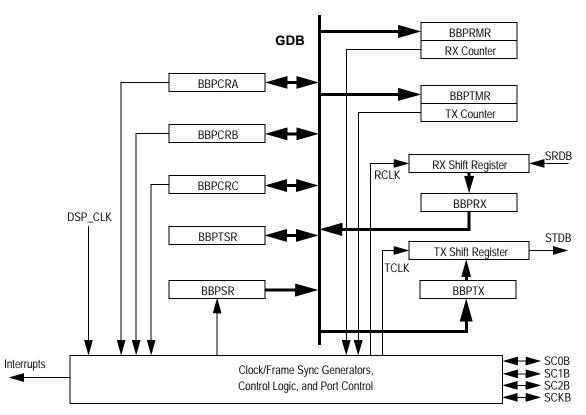

| Figure 14-2. | BBP Block Diagram                                        |

| Figure 15-1. | DPD Block Diagram                                        |

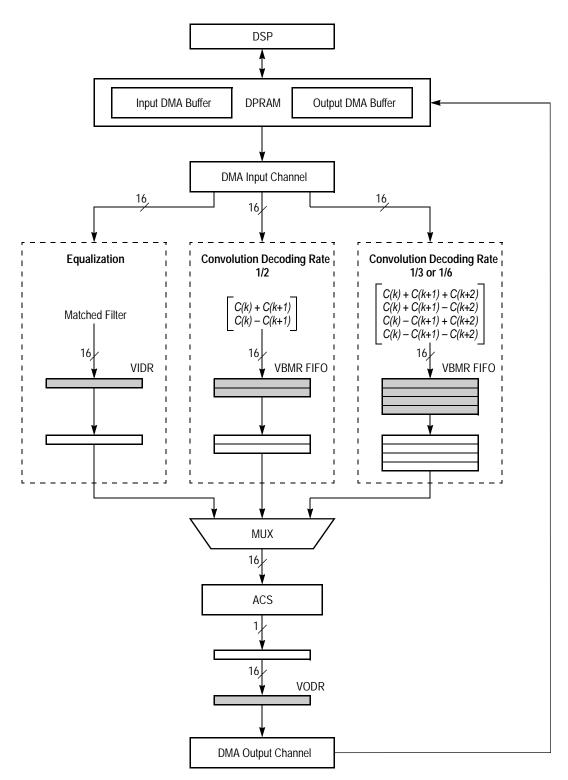

| Figure 16-1. | VIAC Block Diagram                                       |

| Figure 16-2. | Viterbi Butterfly Structure                              |

| Figure 16-3. | The Viterbi Accelerator Block Diagram                    |

| Figure 16-4. | ACS—Add Compare Select Function                          |

| Figure 16-5. | WED—Window Error Detection Function                      |

| Figure 16-6. | VPMAR FIFO                                               |

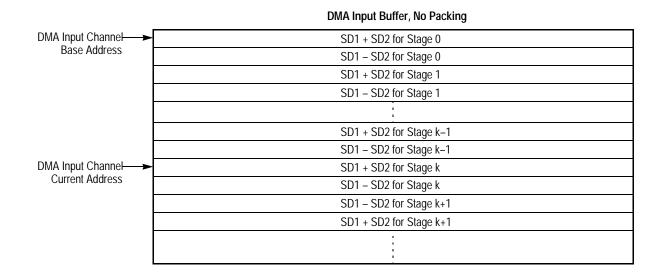

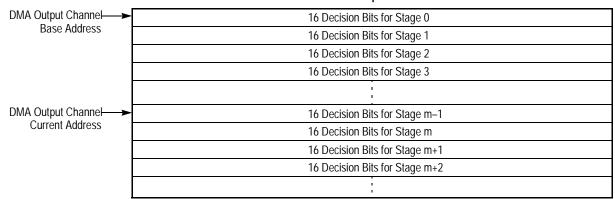

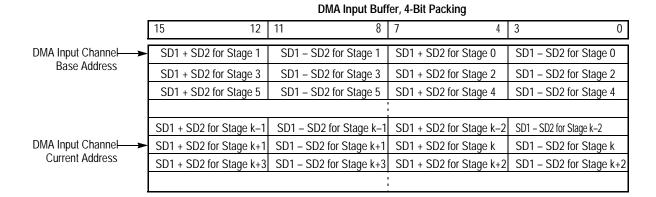

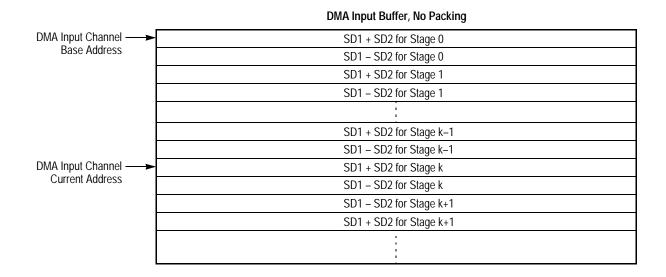

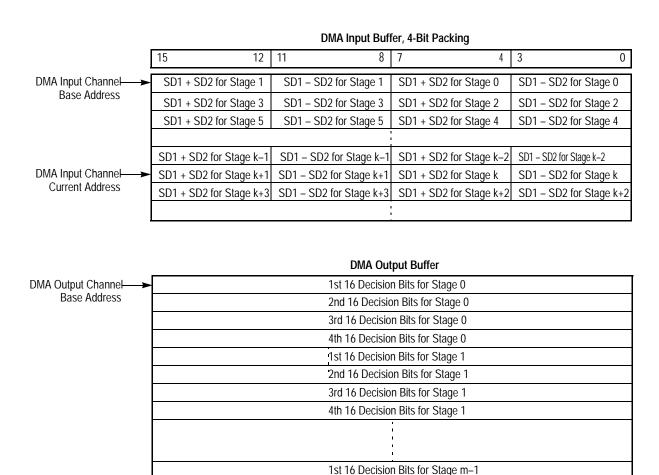

| Figure 16-7. | DMA Buffers in Equalization                              |

| Figure 16-8. | DMA Organization: CR = 1/2, CL = 5, No Packing 16-10     |

| Figure 16-9. | DMA Organization: CR = 1/2, CL = 5, 8-Bit Packing 16-11  |

| Figure 16-10 | .DMA Organization: CR = 1/2, CL = 5, 4-Bit Packing 16-12 |

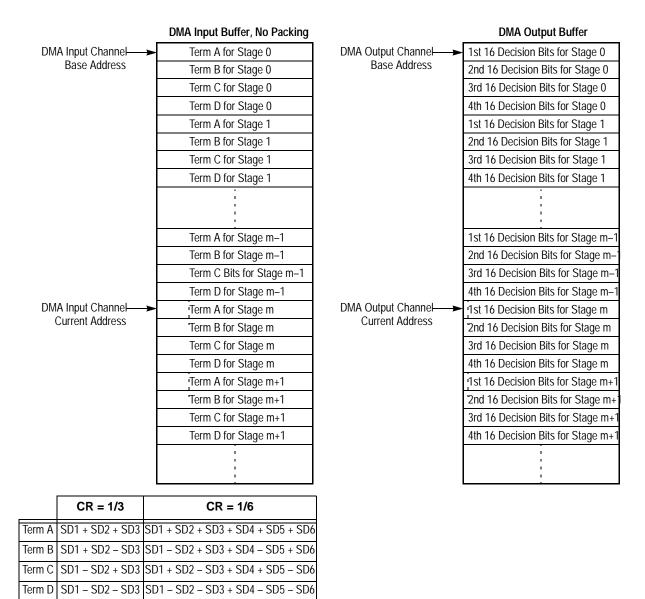

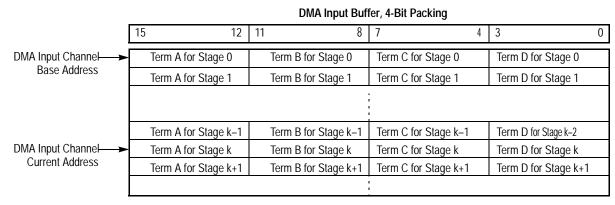

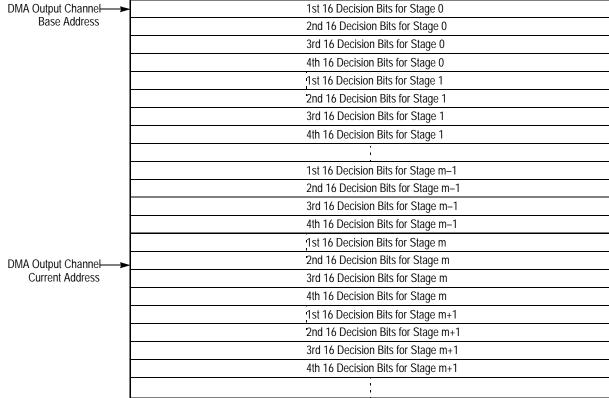

| Figure 16-11 | .DMA Organization: CR = 1/2, CL = 7, No Packing          |

| Figure 16-12 | .DMA Organization: CR = 1/2, CL = 7, 8-Bit Packing 16-14 |

| Figure 16-13. DMA Organization: $CR = 1/2$ , $CL = 7$ , 4-Bit Packing               |

|-------------------------------------------------------------------------------------|

| Figure 16-14.DMA Organization: $CR = 1/3$ or $1/6$ , $CL = 7$ , No Packing 16-16    |

| Figure 16-15.DMA Organization: $CR = 1/3$ or $1/6$ , $CL = 7$ , 8-Bit Packing 16-17 |

| Figure 16-16.DMA Organization: $CR = 1/3$ or $1/6$ , $CL = 7$ , 4-Bit Packing 16-18 |

| Figure 16-17. Pipeline Flow                                                         |

| Figure 16-18. VIAC Pipeline in Lockstep Mode                                        |

| Figure 16-19. VIAC Pipeline in Independent Mode                                     |

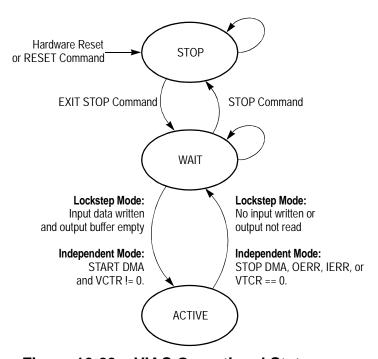

| Figure 16-20. VIAC Operational States                                               |

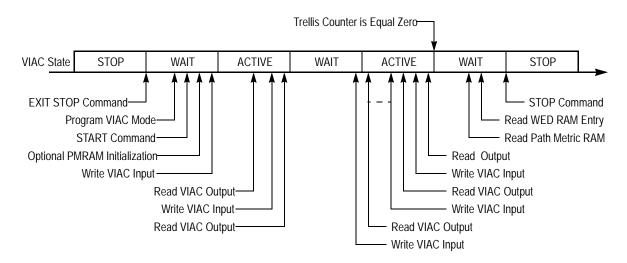

| Figure 16-21. Typical VIAC Operation in Lockstep Mode                               |

| Figure 16-22. Typical VIAC Operation in Independent Mode                            |

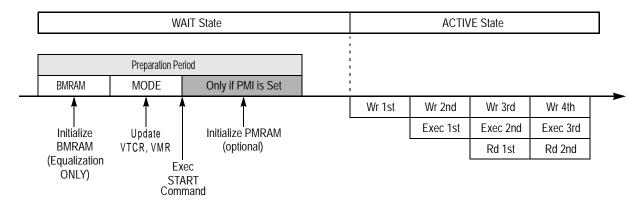

| Figure 16-23. VIAC Preparation: Lockstep Mode                                       |

| Figure 16-24. VIAC Preparation: Independent Mode                                    |

| Figure 17-1. DSP56654 JTAG Block Diagram                                            |

| Figure 17-2. DSP56600 Core JTAG Block Diagram                                       |

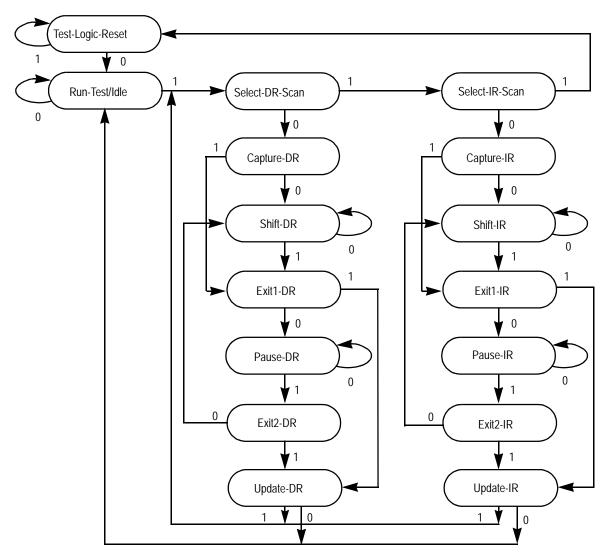

| Figure 17-3. TAP Controller State Machine                                           |

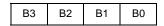

| Figure 17-4. JTAG Instruction Register                                              |

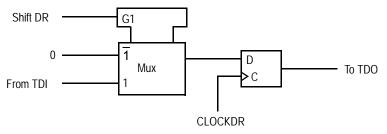

| Figure 17-5. JTAG Bypass Register                                                   |

| Figure 17-6. JTAG ID Register                                                       |

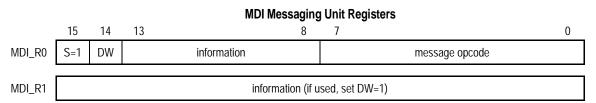

| Figure A-1. Short Message Format                                                    |

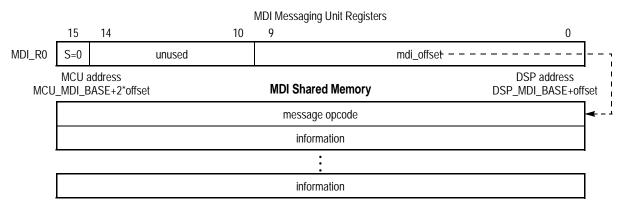

| Figure A-2. Long Message Format                                                     |

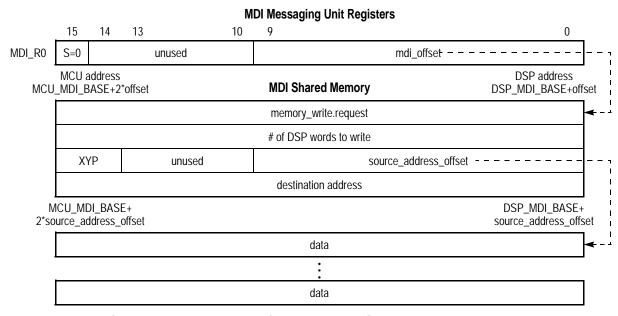

| Figure A-3. Format of memory_write.request Message                                  |

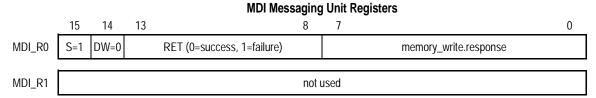

| Figure A-4. Format of message_write.response Message                                |

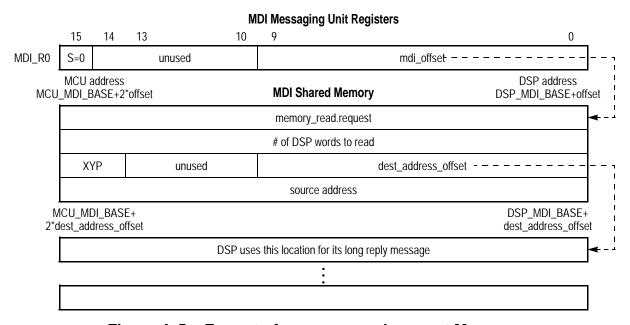

| Figure A-5. Format of memory_read.request Message                                   |

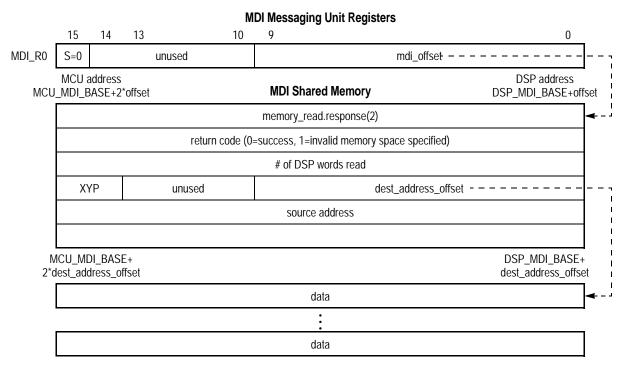

| Figure A-6. Format of memory_read.response Message                                  |

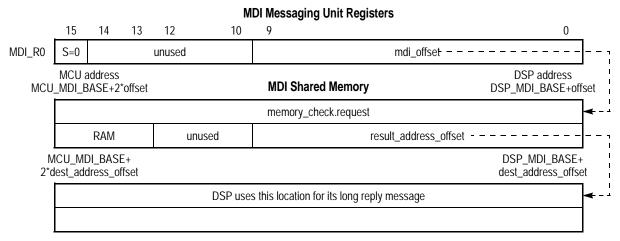

| Figure A-7. Format of memory_check.request Message                                  |

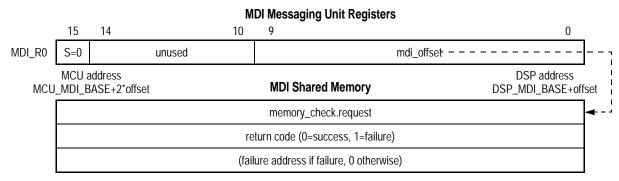

| Figure A-8. Format of memory_check.request Message                                  |

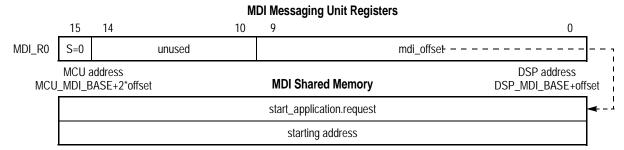

| Figure A-9. Format of start_application.request Message A-11                        |

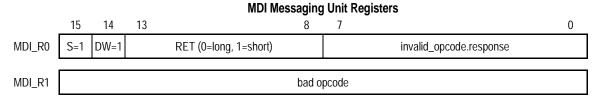

| Figure A-10. Format of invalid_opcode.response Message                              |

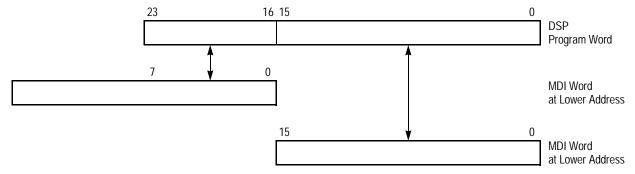

| Figure A-11. Mapping of DSP Program Memory Words to MDI Message Words A-13          |

# **List of Tables**

| Table 2-1.  | DSP56654 Signal Functional Group Allocations |

|-------------|----------------------------------------------|

| Table 2-2.  | Power                                        |

| Table 2-3.  | Ground                                       |

| Table 2-4.  | PLL and Clock Signals                        |

| Table 2-5.  | External Interface Module                    |

| Table 2-6.  | Reset, Mode, and Multiplexer Control Signals |

| Table 2-7.  | DSP X/Y Visibility Port                      |

| Table 2-8.  | Interrupt Signals                            |

| Table 2-9.  | Protocol Timer Output Signals                |

| Table 2-10. | Keypad Port Signals                          |

| Table 2-11. | UARTA Signals                                |

| Table 2-12. | UARTB Signals 2-17                           |

| Table 2-13. | QSPIA Signals                                |

| Table 2-14. | QSPIB Signals                                |

| Table 2-15. | SCP Signals                                  |

| Table 2-16. | SAP Signals                                  |

| Table 2-17. | BBP Signals                                  |

| Table 2-18. | Emulation Port Signals                       |

| Table 2-19. | Debug Control Signals                        |

| Table 2-20. | JTAG Port Signals                            |

| Table 4-1.  | MCU and MCU Peripherals Clock Source         |

| Table 4-2.  | CKCTL Description                            |

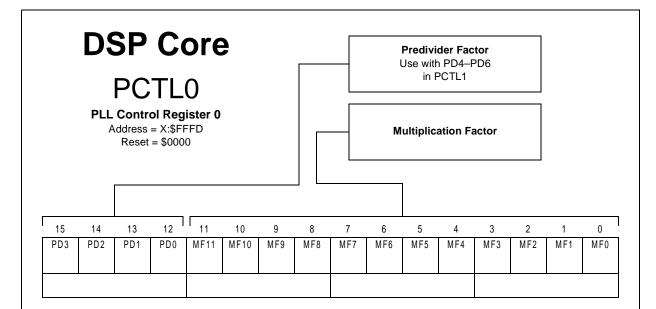

| Table 4-3.  | PCTL0 Descriptions                           |

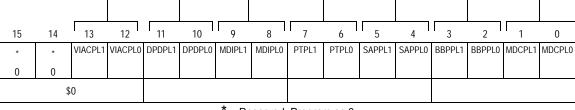

| Table 4-4.  | PCTL1 Description                            |

| Table 4-5.  | MCU Peripherals in Low Power Mode            |

| Table 4-6.  | DSP Peripherals in Low Power Modes           |

| Table 4-7.  | Programmable Power-Saving Features           |

| Table 4-8.  | RSR Description 4-11                 |

|-------------|--------------------------------------|

| Table 4-9.  | OMR Description                      |

| Table 4-10. | Patch JUMP Targets                   |

| Table 4-11. | Pin Functions in PAV Mode            |

| Table 4-12. | DSP XYDV Pins                        |

| Table 4-13. | Debug Port Pin Multiplexing          |

| Table 4-14. | Timer Pin Multiplexing 4-21          |

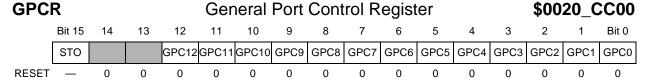

| Table 4-15. | GPCR Description                     |

| Table 5-1.  | MCU MDI Access Timing                |

| Table 5-2.  | MDI Registers and Symmetry           |

| Table 5-3.  | MCU Wake-up Events                   |

| Table 5-4.  | MDI Reset Sources                    |

| Table 5-5.  | General Restrictions                 |

| Table 5-6.  | DSP-Side Restrictions                |

| Table 5-7.  | MCU-Side Restrictions                |

| Table 5-8.  | MDI Signalling and Control Registers |

| Table 5-9.  | MCU–DSP Register Correspondence      |

| Table 5-10. | MCVR Description                     |

| Table 5-11. | MCR Description                      |

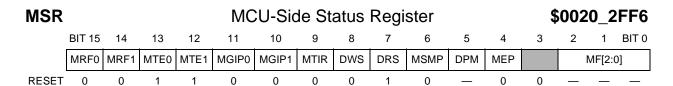

| Table 5-12. | MSR Description                      |

| Table 5-13. | MTR1 Description                     |

| Table 5-14. | MTR0 Description                     |

| Table 5-15. | MRR1 Description                     |

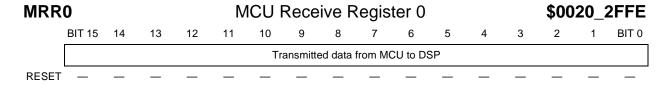

| Table 5-16. | MRR0 Description                     |

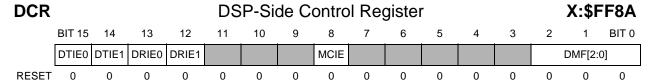

| Table 5-17. | DCR Description                      |

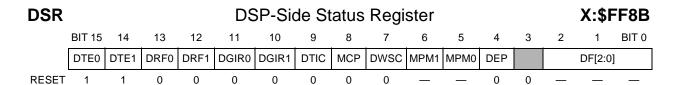

| Table 5-18. | DSR Description. 5-25                |

| Table 5-19. | DTR1 Description                     |

| Table 5-20. | DTR0 Description                     |

| Table 5-21. | DRR1 Description                     |

| Table 5-22. | DRR0 Description                     |

| Table 6-1.  | EIM Signal Description               |

| Table 6-2.  | Chip Select Address Range 6-4                        |

|-------------|------------------------------------------------------|

| Table 6-3.  | Interface Requirements for Read and Write Cycles 6-6 |

| Table 6-4.  | SIZ[1:0] Encoding                                    |

| Table 6-5.  | PSTAT[3:0] Encoding                                  |

| Table 6-6.  | CSCRn Description                                    |

| Table 6-7.  | EIMCR Description                                    |

| Table 6-8.  | EMDDR Description 6-13                               |

| Table 6-9.  | EMDR Description 6-13                                |

| Table 7-1.  | MCU Interrupt Sources                                |

| Table 7-2.  | ISR Description                                      |

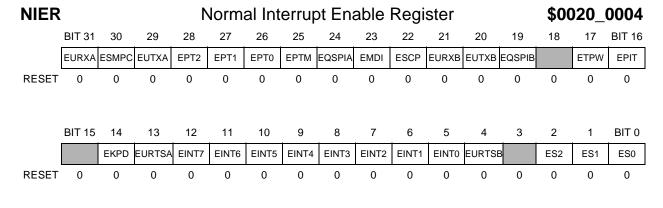

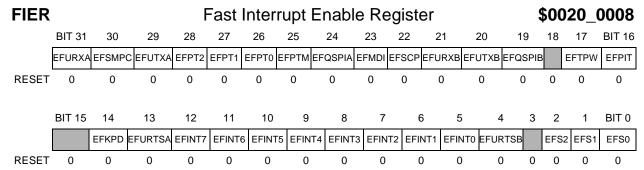

| Table 7-3.  | NIER/FIER Description                                |

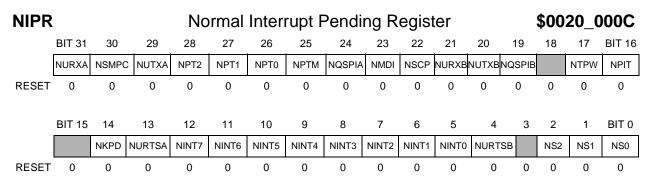

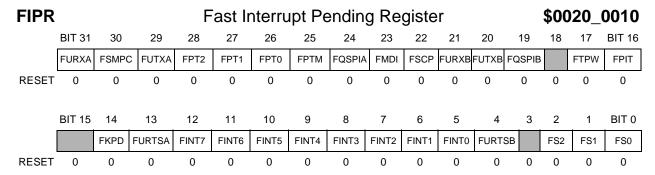

| Table 7-4.  | NIPR and FIPR Description                            |

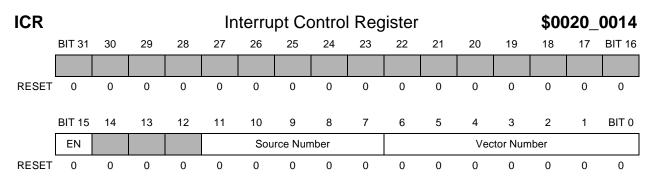

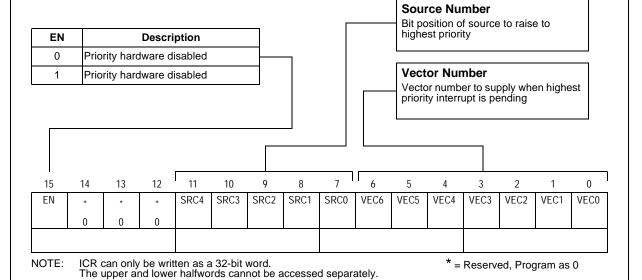

| Table 7-5.  | ICR Description                                      |

| Table 7-6.  | DSP Interrupt Sources                                |

| Table 7-7.  | Interrupt Source Priorities within an IPL            |

| Table 7-8.  | IPRP Description                                     |

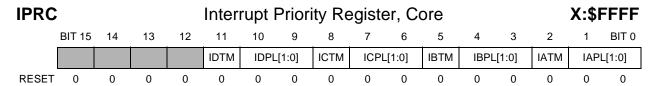

| Table 7-9.  | IPRC Description                                     |

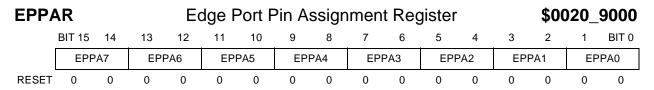

| Table 7-10. | EPPAR Description                                    |

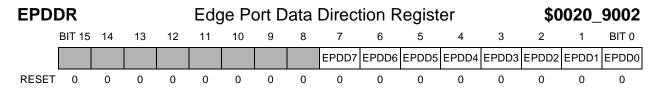

| Table 7-11. | EPDDR Description                                    |

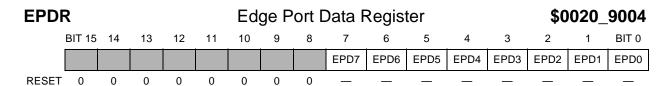

| Table 7-12. | EPDR Description                                     |

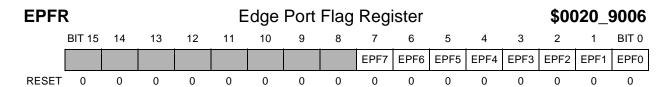

| Table 7-13. | EPFR Description                                     |

| Table 8-1.  | Serial Control Port Signals                          |

| Table 8-2.  | QSPI Register/Memory Summary 8-13                    |

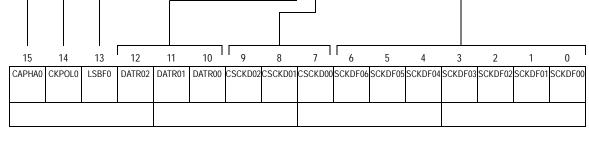

| Table 8-3.  | SPCR Description                                     |

| Table 8-4.  | QCR Description 8-16                                 |

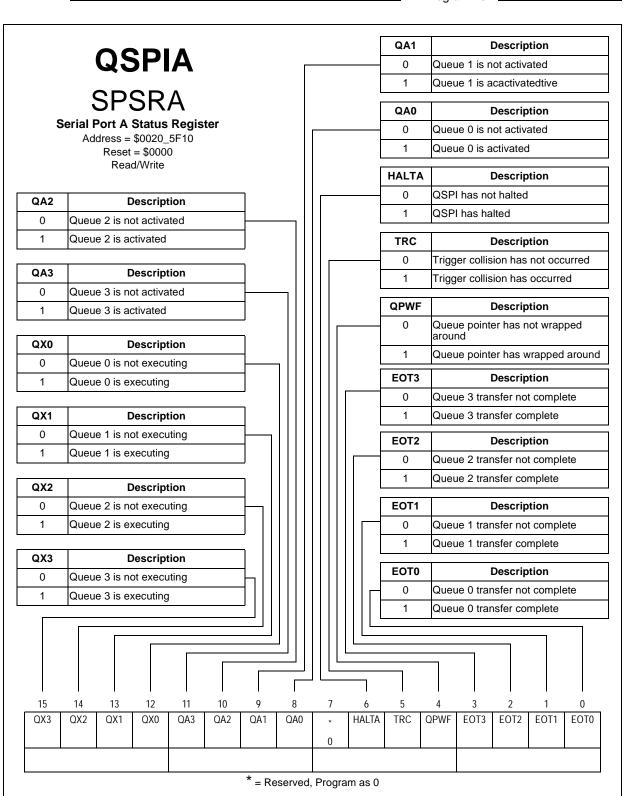

| Table 8-5.  | SPSR Description                                     |

| Table 8-6.  | SCCR Description 8-20                                |

| Table 8-7.  | QSPI Control RAM Description 8-23                    |

| Table 8-8.  | QPCR Description                                     |

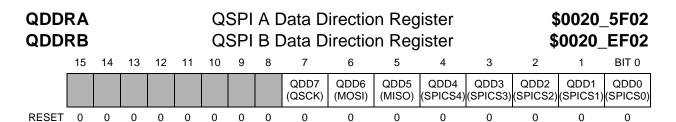

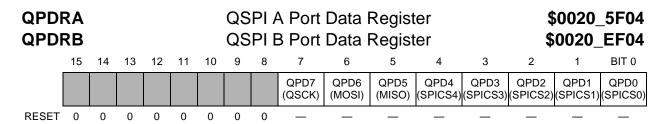

| Table 8-9.  | QDDR Description                                     |

| Table 8-10. | QPDR Description                                     |

| Table 9-1.   | ITCSR Description                                  | . 9-3 |

|--------------|----------------------------------------------------|-------|

| Table 9-2.   | WCR Description                                    | . 9-6 |

| Table 9-3.   | Timer Signal Multiplexing                          | . 9-7 |

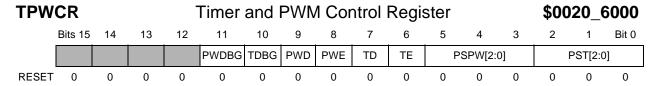

| Table 9-4.   | TPWCR Description                                  | 9-13  |

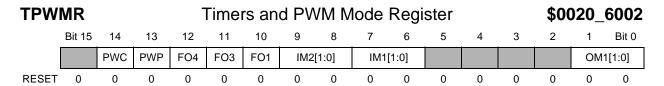

| Table 9-5.   | TPWMR Description                                  | 9-14  |

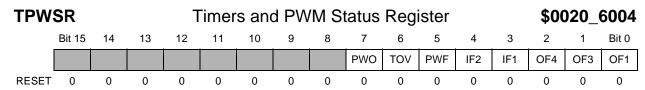

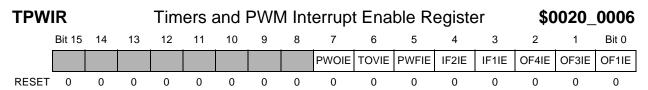

| Table 9-6.   | TPWSR Description                                  | 9-15  |

| Table 9-7.   | GNRC Description                                   | 9-16  |

| Table 10-1.  | Protocol Timer Operation Mode Summary              | 10-10 |

| Table 10-2.  | Protocol Timer Interrupt Sources                   | 10-12 |

| Table 10-3.  | PT Port Pin Assignment                             | 10-13 |

| Table 10-4.  | Protocol Timer Event List                          | 10-14 |

| Table 10-5.  | Protocol Timer Register Summary                    | 10-17 |

| Table 10-6.  | PTCR Description                                   | 10-19 |

| Table 10-7.  | Additional Conditions for Generating PT Interrupts | 10-20 |

| Table 10-8.  | PTIER Description                                  | 10-21 |

| Table 10-9.  | PTSR Description                                   | 10-22 |

| Table 10-10. | PTEVR Description                                  | 10-23 |

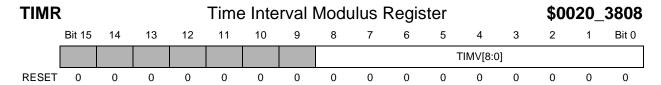

| Table 10-11. | TIMR Description                                   | 10-23 |

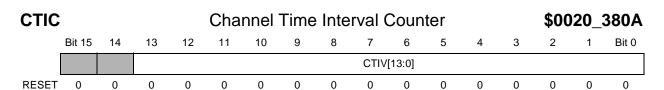

| Table 10-12. | CTIC Description                                   | 10-24 |

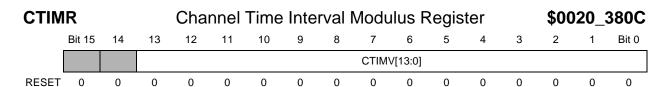

| Table 10-13. | CTIMR Description                                  | 10-24 |

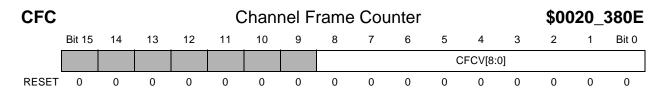

| Table 10-14. | CFC Description                                    | 10-24 |

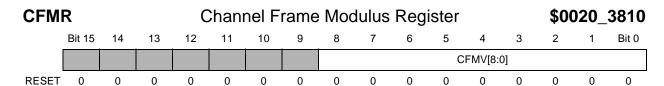

| Table 10-15. | CFMR Description                                   | 10-25 |

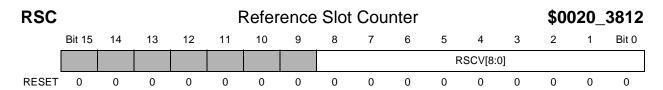

| Table 10-16. | RSC Description                                    | 10-25 |

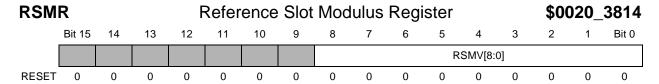

| Table 10-17. | RSMR Description                                   | 10-25 |

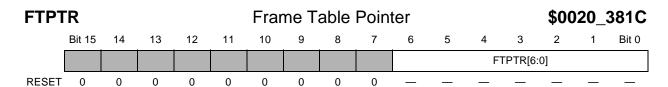

| Table 10-18. | FTPTR Description                                  | 10-26 |

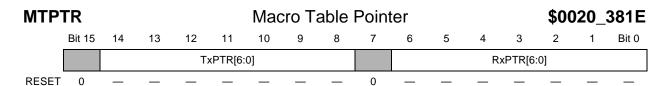

| Table 10-19. | MTPTR Description                                  | 10-26 |

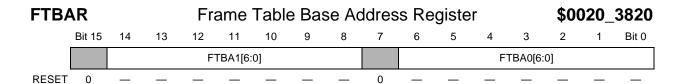

| Table 10-20. | FTBAR Description                                  | 10-26 |

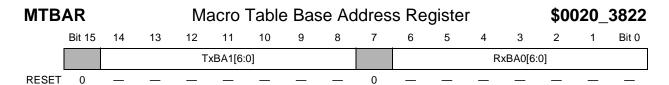

| Table 10-21. | MTBAR Description                                  | 10-27 |

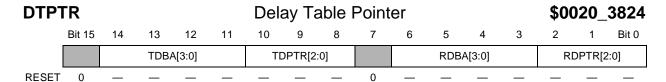

| Table 10-22. | DTPTR Description                                  | 10-27 |

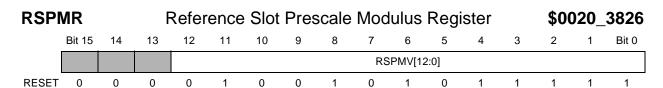

| Table 10-23. | RSPMR Description                                  | 10-28 |

| Table 10-24. | PTPCR Description                                  | 10-29 |

| Table 10-25. | PTDDR Description                     | 1-29 |

|--------------|---------------------------------------|------|

| Table 10-26. | PTPDR Description                     | )-29 |

| Table 11-1.  | Suggested GPIO Pins for UARTA Signals | 1-5  |

| Table 11-2.  | UART Low Power Mode Operation         | 1-8  |

| Table 11-3.  | UART Register Summary                 | 1-9  |

| Table 11-4.  | URX Description                       | -10  |

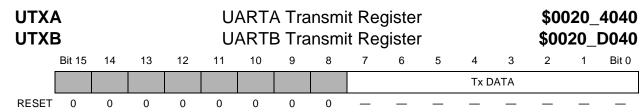

| Table 11-5.  | UTX Description                       | -11  |

| Table 11-6.  | UCR1 Description                      | -12  |

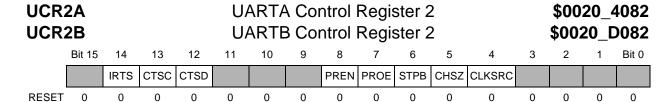

| Table 11-7.  | UCR2 Description                      | -14  |

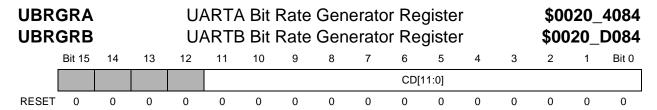

| Table 11-8.  | UBRGR Description                     | -15  |

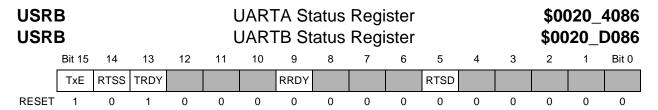

| Table 11-9.  | USR Description                       | -15  |

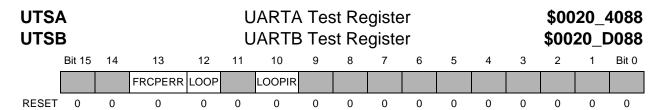

| Table 11-10. | UTS Description                       | -16  |

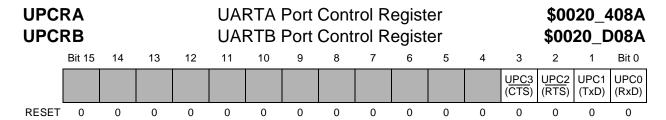

| Table 11-11. | UPCR Description                      | -17  |

| Table 11-12. | UDDR Description                      | -17  |

| Table 11-13. | UPDR Description                      | -17  |

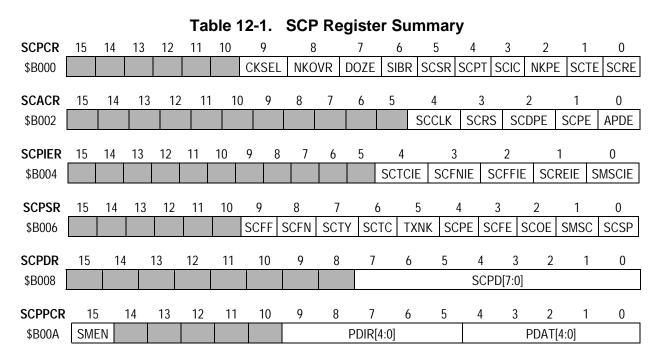

| Table 12-1.  | SCP Register Summary                  | -10  |

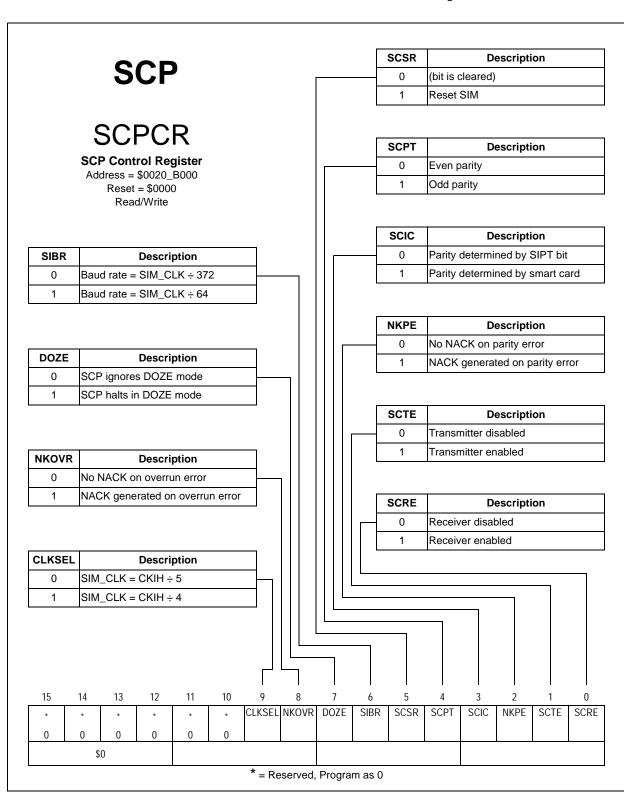

| Table 12-2.  | SCPCR Description                     | -11  |

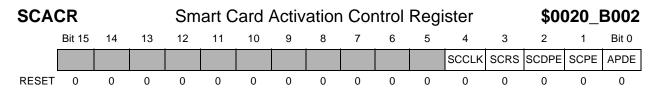

| Table 12-3.  | SCACR Description                     | :-12 |

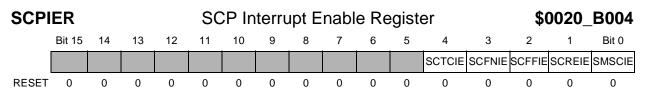

| Table 12-4.  | SCPIER Description                    | :-13 |

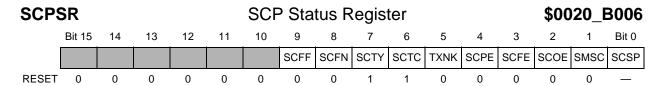

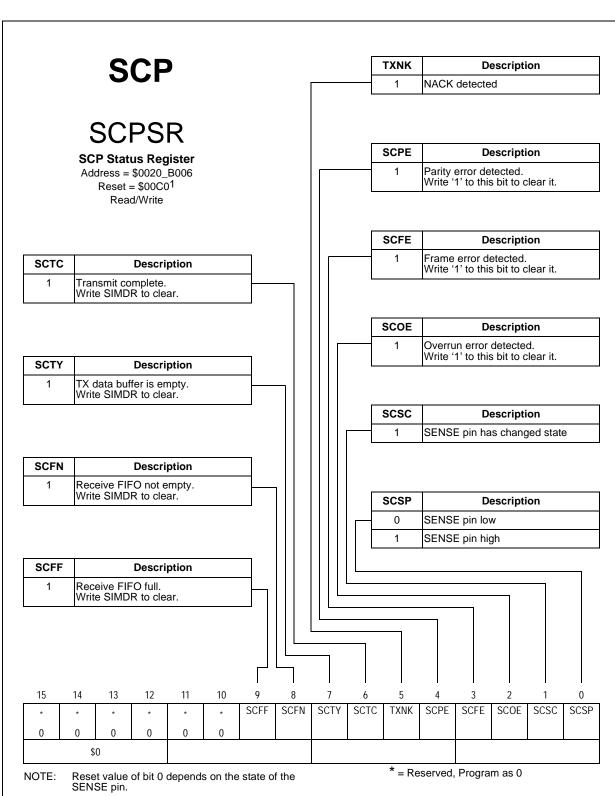

| Table 12-5.  | SCPSR Description                     | 14   |

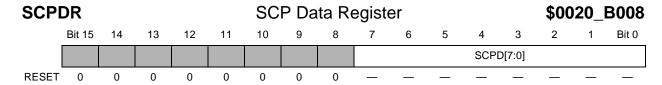

| Table 12-6.  | SCPDR Description                     | -15  |

| Table 12-7.  | SCP Pin GPIO Bit Assignments          | :-16 |

| Table 12-8.  | SCPPCR Description                    | -16  |

| Table 13-1.  | Keypad Port Pull-up Resistor Control  | 3-2  |

| Table 13-2.  | Keypad Port Register Summary          | 3-4  |

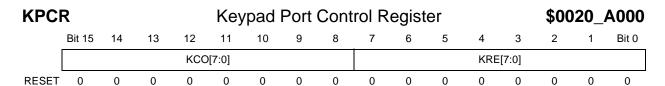

| Table 13-3.  | KPCR Description                      | 3-5  |

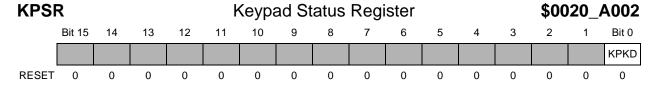

| Table 13-4.  | KPSR Description                      | 3-5  |

| Table 13-5.  | KDDR Description                      | 3-6  |

| Table 13-6.  | KPDR Description                      | 3-6  |

| Table 14-1.  | SAP and BBP Pins                      | 4-3  |

| Table 14-2.  | SAP/BBP Clock Sources                 | 4-4  |

| Table 14-3.  | Register Settings to Generate a 2.048 MHz Clock | 1-6         |

|--------------|-------------------------------------------------|-------------|

| Table 14-4.  | Frame Configuration                             | 1-7         |

| Table 14-5.  | SAP and BBP Interrupts                          | 15          |

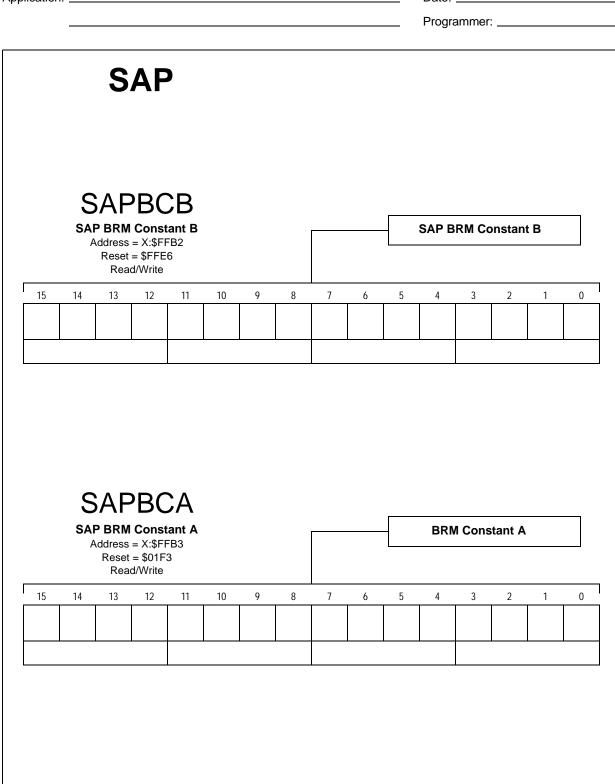

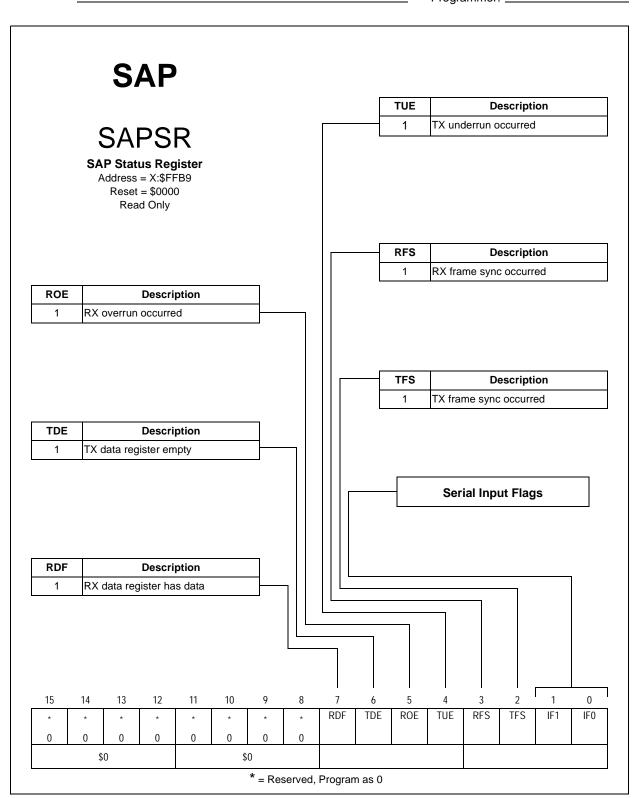

| Table 14-6.  | Serial Audio Port Register Summary              | 16          |

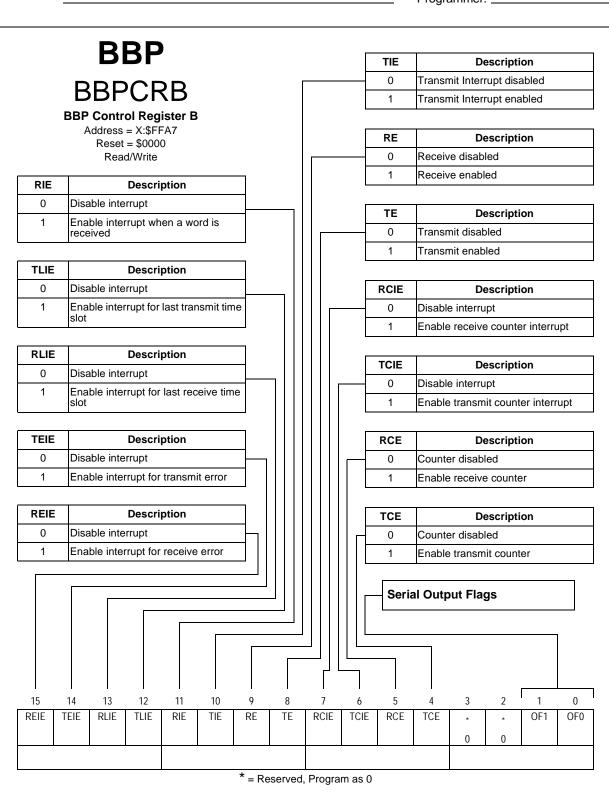

| Table 14-7.  | Baseband Port Register Summary                  | 17          |

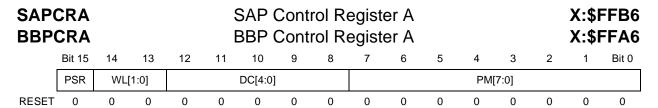

| Table 14-8.  | SAP/BBP CRA Description                         | 19          |

| Table 14-9.  | SAP/BBP CRB Description                         | 20          |

| Table 14-10. | SAP/BBP CRC Description                         | 22          |

| Table 14-11. | SAP/BBP Status Register Description             | 24          |

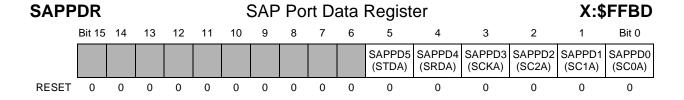

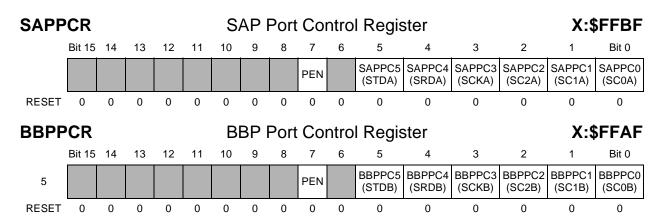

| Table 14-12. | SAP/BBP PDR Description                         | 26          |

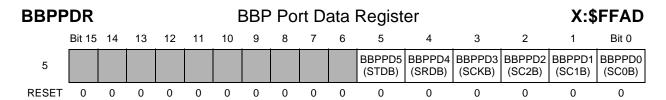

| Table 14-13. | SAP/BBP DDR Description                         | 26          |

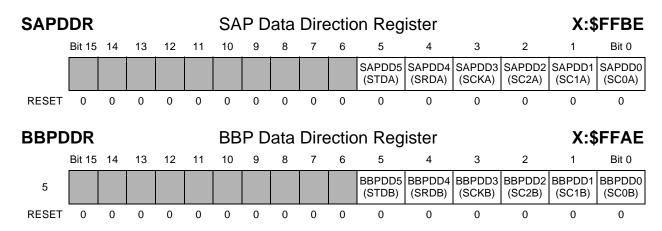

| Table 14-14. | SAP/BBP PCR Description                         | 27          |

| Table 15-1.  | DPD Channel Selection                           | 5-3         |

| Table 15-2.  | DPD Transfer Triggers                           | 5-4         |

| Table 15-3.  | DPDCR Description                               | 5-8         |

| Table 16-1.  | Pipeline Flow                                   | 20          |

| Table 16-2.  | VCSR Description                                | 36          |

| Table 16-3.  | VMR Description                                 | 38          |

| Table 17-1.  | DSP JTAG Pins                                   | 7-4         |

| Table 17-2.  | JTAG Instructions                               | 7-6         |

| Table 17-3.  | Entering MCU OnCE Mode                          | 13          |

| Table 17-4.  | Releasing the MCU and DSP from Debug Modes 17-  | 14          |

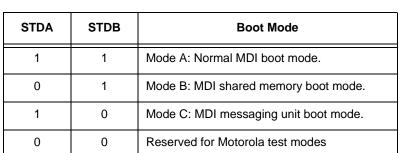

| Table A-1.   | DSP56654 Boot Modes                             | <b>\</b> -2 |

| Table A-2.   | Message Summary                                 | <b>\</b> -4 |

| Table A-3.   | XYP field                                       | <b>\</b> -5 |

| Table C-1.   | BSR Bit Definitions                             | J-2         |

| Table D-1.   | MCU Instruction Set Summary                     | <b>)-</b> 1 |

| Table D-2.   | MCU Instruction Syntax Notation                 | <b>)-</b> 6 |

| Table D-3.   | MCU Instruction Opcode Notation                 | <b>)-</b> 6 |

| Table D-4.   | DSP Instruction Set Summary                     | <b>)</b> -7 |

| Table D-5.   | Program Word and Timing Symbols                 | 13          |

| Table D-6.  | Condition Code Register (CCR) Symbols | D-13  |

|-------------|---------------------------------------|-------|

| Table D-7.  | Condition Code Register Notation      | D-13  |

| Table D-8.  | MCU Internal I/O Memory Map           | D-14  |

| Table D-9.  | DSP Internal I/O Memory Map           | D-20  |

| Table D-10. | Register Index                        | D-23  |

| Table D-11. | DSP56654 Acronym Changes              | D-29  |

| Table E-1.  | List of Programmer's Sheets           | . E-1 |

# **List of Examples**

| Example 5 -1.  | Program Loop That Stalls MCU Access to Shared Memory    | 5-4 |

|----------------|---------------------------------------------------------|-----|

| Example 5 -2.  | Program Loop With No Stall                              | 5-4 |

| Example 5 -3.  | Dummy Event to Allow MCU to Track DSP Power Mode Change | -13 |

| Example 11 -1. | UART Baud Error Calculation                             | 1-7 |

| Example A-1.   | Normal Boot                                             | -14 |

| Example A-2.   | Shared Memory Boot                                      | -16 |

| Example A-3.   | Messaging Unit Boot                                     | -17 |

## **Preface**

#### Conventions

The following conventions are used in this manual:

- Bits within registers are always listed from most significant bit (MSB) to least significant bit (LSB).

- 1 byte = 8 bits

1 halfword = 16 bits = 2 bytes

1 word = 32 bits = 4 bytes

- Bits within a register are indicated AA[n:0] when more than one bit is involved in a description. For purposes of description, the bits are presented as if they were contiguous within a register, regardless of their actual physical locations in a register.

- All bits in a register are read/write unless otherwise noted.

- When a bit is described as "set," its value is 1. When a bit is described as "cleared," its value is 0.

- Register bits that are unused or reserved for future use are read as 0 and should be written with 0 to ensure future compatibility. In the register descriptions, each of these bits is indicated with a shaded box ( ).

- The word "reset" is used in three different contexts in this manual:

- There is a reset instruction that is always written as "RESET".

- In lower case, "reset" refers to the reset function. A leading capital letter is used as grammar dictates.

- "Reset" refers to the Reset state.

- The word "pin" is a generic term for any pin on the chip. Because of on-chip pin multiplexing, more than one signal may be present on any given pin.

- Pins or signals that are asserted low (made active when pulled to ground) have an overbar over their name; for example, the \$\overline{SSO}\$ pin is asserted low.

• Hex values are indicated with a dollar sign (\$) preceding the hex value as follows: X:\$FFFF is the X memory address for the Interrupt Priority Register—Core (IPR-C).

Code examples are displayed in a monospaced font, as shown in Example 1.

#### Example 1. Code Example

```

BFSET #$0007,X:PCC ; Configure: line 1

; MISOO, MOSIO, SCKO for SPI masterline 2

; ~SSO as PC3 for GPIO line 3

```

- In code examples, the names of pins or signals that are asserted low are preceded by a tilde. In the previous example, line 3 refers to the  $\overline{SSO}$  pin (shown as ~sso).

- The word "assert" means that a high true (active high) signal is pulled high to  $V_{CC}$  or that a low true (active low) signal is pulled low to ground. The word "deassert" means that a high true signal is pulled low to ground or that a low true signal is pulled high to  $V_{CC}$ . These conventions are summarized in Table 1.

Table 1. Signal States

| Signal/Symbol | Logic State | Signal State | Voltage                      |

|---------------|-------------|--------------|------------------------------|

| PIN           | True        | Asserted     | Ground <sup>1</sup>          |

| PIN           | False       | Deasserted   | V <sub>CC</sub> <sup>2</sup> |

| PIN           | True        | Asserted     | V <sub>CC</sub>              |

| PIN           | False       | Deasserted   | Ground                       |

<sup>1.</sup> Ground is an acceptable low-voltage level. See the appropriate data sheet for the range of acceptable low-voltage levels (typically a TTL logic low).

#### **Documentation**

This manual (DSP56654UM/D) is one of a set of five documents that provides complete product information for the DSP56654. The other four documents include the following:

- *M•CORE Reference Manual* (MCORERM/AD)

- MMC2001 Reference Manual (MMC2001M/AD

- DSP56600 Family Manual (DSP56600FM/AD)

- DSP56654 Technical Data Sheet (DSP56654/D)

V<sub>CC</sub> is an acceptable high-voltage level. See the appropriate data sheet for the range of acceptable high-voltage levels (typically a TTL logic high).

# Chapter 1 Introduction

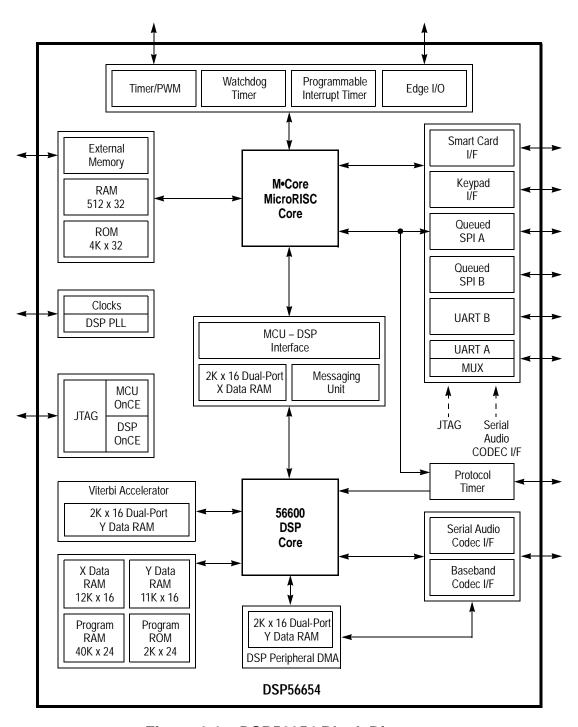

Motorola designed the ROM-based DSP56654 to support the rigorous demands of the cellular subscriber market. The high level of on-chip integration in the DSP56654 minimizes application system design complexity and component count, resulting in very compact implementations. This integration also yields very low power consumption and cost-effective system performance. The DSP56654 chip combines Motorola's 32-bit M•CORE<sup>TM</sup> MicroRISC Engine and the DSP56600 Digital Signal Processor (DSP) core with on-chip memory, a protocol timer, and custom peripherals to provide a single-chip cellular base-band processor. A block diagram of the DSP56654 is shown in Figure 1-1.

## 1.1 DSP56654 Key Features

The following list summarizes the key features of the DSP56654.

- M•CORE (MCU) core

- 32-bit load/store M•CORE RISC architecture

- Fixed 16-bit instruction length

- 16-entry 32-bit general-purpose register file

- 32-bit internal address and data buses

- Efficient four-stage, fully interlocked execution pipeline

- Single-cycle execution for most instructions, two cycles for branches and memory accesses

- Special branch, byte, and bit manipulation instructions

- Support for byte, halfword, and word memory accesses

- Fast interrupt support via vectoring/auto-vectoring and a 16-entry dedicated alternate register file

Figure 1-1. DSP56654 Block Diagram

- DSP core

- DSP56600 architecture

- Single-cycle arithmetic instructions

- Fully pipelined 16 × 16-bit parallel multiply accumulator (MAC)

- Two 40-bit accumulators including extension bits

- 40-bit parallel barrel shifter

- Highly parallel instruction set with unique DSP addressing modes

- Position-independent code support

- Nested hardware DO loops

- Fast auto-return interrupts

- On-chip support for software patching and enhancements

- Real-time trace capability via external address bus

- On-chip memory

- $-4K \times 32$ -bit MCU ROM

- 512 × 32-bit MCU RAM

- $-2K \times 24$ -bit DSP program ROM

- $-40K \times 24$ -bit DSP program RAM

- $-14K \times 16$ -bit X data RAM:

- 12K general access RAM

- 2K Dual-Port MDI RAM

- $-15K \times 16$ -bit Y data RAM:

- 11K general access RAM

- 2K Dual-Port DPD RAM

- 2K Dual-Port VIAC RAM

- On-chip peripherals

- Fully programmable phase-locked loop (PLL) for DSP clock generation

- External Interface Module (EIM) for glueless system integration

- External 22-bit address and 16-bit data MCU buses

- 32-source MCU interrupt controller

- Intelligent MCU/DSP interface (MDI) with 2K × 16-bit dual-port RAM as well as messaging status and control unit

- Serial Audio Codec Port (SAP)

- Serial Baseband Codec Port (BBP)

- DPS Peripheral DMA (DPD) for independent SAP/BBP operation

- Viterbi Accelerator (VIAC)

- Protocol timer frees the MCU from radio channel timing events

- Two Queued Serial Peripheral Interface (QSPI) ports

- Keypad port capable of scanning up to an  $8 \times 8$  matrix keypad

- General-purpose MCU and DSP timers

- Pulse Width Modulation (PWM) output

- Two Universal Asynchronous Receiver/Transmitter (UART) ports with FIFO

- IEEE 1149.1-compliant boundary scan JTAG test access port (TAP)

- Integrated DSP/MCU On-Chip Emulation (OnCE<sup>TM</sup>) module

- DSP program and X/Y data visibility modes for system development

- ISO 7816-compatible smart card port

- Operating features

- Comprehensive static and dynamic power management

- MCU operating frequency: DC to 16.8 MHz at 1.8 V

- DSP operating frequency: DC to 58.8 MHz at 1.8 V

- Internal operating voltage range: 1.8–2.5 V with 3.1 V-tolerant I/O

- Operating temperature: -40° to 85°C ambient

- Package option:  $17 \times 17$  mm, 256-lead PBGA

#### 1.2 Architecture Overview

The DSP56654 combines the control and I/O capability of the M•CORE MCU with the signal processing power of the DSP56600 core to provide a complete system solution for a cellular baseband system. The DSP subsystem has a closed architecture, meaning that all DSP memory is contained on the device and the DSP address and data buses do not appear external to the device. The MCU subsystem provides both on-chip memory and an external bus interface. Both processors provide external interrupt pins.

The two cores communicate through the MDI, which includes a block of dual-access RAM.

Each core generates its own independent clock, and the DSP core contains a PLL as part of its clock generation subsystem. Each processor and its associated peripherals have several low-power standby modes.

A single JTAG port is shared by the two cores for debug and test purposes. The JTAG port is integrated with on-chip emulation modules for both the MCU and the DSP, providing a non-intrusive way to interact with the processors and their peripherals and memory. The MCU has additional external debug pins for in-circuit emulation. The DSP program address bus is multiplexed on other DSP56654 pins.

The pins associated with most peripherals can be programmed individually to function as general-purpose input/output signals (GPIO) if their primary functions are not required. (The exceptions are the MCU pulse width modulator and general-purpose timer, which have no GPIO capability, and the SmartCard Port (SCP), whose five pins must all function either as SCP pins or GPIO (i.e., cannot be individually programmed).

#### 1.2.1 MCU

This section describes the MCU core, peripherals, and memory.

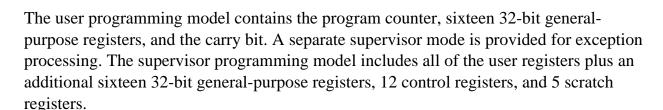

#### 1.2.1.1 Core Description

The M•CORE MCU utilizes a four-stage pipeline for instruction execution. The instruction fetch, instruction decode/register file read, execute, and register write-back stages operate in an overlapped fashion, allowing most instructions to execute in a single clock cycle. Sixteen general-purpose registers are provided for source operands and instruction results.

The execution unit consists of a 32-bit arithmetic/logic unit (ALU), a 32-bit barrel shifter, a find-first-one unit (FFO), result feed-forward hardware, and miscellaneous support hardware for multiplication and multiple register loads and stores. Arithmetic and logical operations are executed in a single cycle with the exception of the multiply and divide instructions. The FFO unit operates in a single clock cycle.

The program counter unit contains a PC incrementer and a dedicated branch address adder to minimize delays during change-of-flow operations. Memory load and store operations are provided for byte, halfword, and word (32-bit) data with automatic zero extension of byte and halfword load data. These instructions can execute in two clock cycles. Load and store multiple register instructions allow low overhead context save and restore operations.

A single condition code/carry (C) bit is provided for condition testing and to implement arithmetic and logical operations greater than 32 bits. A 16-entry alternate register file is provided to minimize exception processing overhead, and the CPU supports both vectored and auto-vectored interrupts.

For a complete description of M•CORE architecture, refer to the *M•CORE Reference Manual*.

#### 1.2.1.2 MCU-Side Peripherals

The MCU-side peripherals for the DSP56654 support a variety of I/O functions, including radio channel timing, signal generation, periodic interrupts, smart card interface, LCD displays, and key pads.

- A **keypad port** supports up to 8 rows and 8 columns.

- Each of two **QSPIs** enables serial communication to multiple peripheral devices through a single port.

- The **SCP** provides user information to an external device through a smart card port.

- Each of two **UART**s connects to a modem or another computer.

- An **edge I/O port** enables up to eight external interrupts.

- An **interrupt controller** prioritizes up to 32 peripheral interrupts.

- Four timers are provided, including

- a **periodic interval timer** to generate periodic interrupts

- a watchdog timer to protect against system failure

- a **pwm** and **general-purpose timer** to generate custom signals

- a **protocol timer** with TDMA counters for radio channel control, event scheduling, QSPI triggers or generating interrupts to either core.

- MCU OnCE facilitates test and debug.

#### 1.2.1.3 MCU-Side Memory

All MCU memory is 32 bits (1 word) wide. On-chip MCU memory includes 512 words of RAM and 4K words of ROM. In addition, the EIM provides a 22-bit address/16-bit data bus with control signals to access external memory. Programmable timing on this bus allows the use of a wide range of memory devices. As many as six external memory banks can be connected.

#### 1.2.2 DSP

This section describes the DSP core, peripherals, and memory.

#### 1.2.2.1 Core Description

The DSP56600 core contains a data arithmetic logic unit, an address generation unit, a program control unit, and program patch logic.

#### 1.2.2.1.1 Data Arithmetic Logic Unit

The data arithmetic logic unit (ALU) performs all data arithmetic and logical operations in the DSP core. The components of the data ALU include the following:

- Four 16-bit input general purpose registers: X1, X0, Y1, and Y0

- A parallel, fully pipelined MAC

- Six data ALU registers (A2, A1, A0, B2, B1, and B0) that are concatenated into two general-purpose, 40-bit accumulators, A and B

- An accumulator shifter that is an asynchronous parallel shifter with a 40-bit input and a 40-bit output

- A bit field unit (BFU) with a 40-bit barrel shifter

- Two data bus shifter/limiter circuits

The data ALU registers can be read or written over the X data bus (XDB) and the Y data bus (YDB) as 16- or 32-bit operands. The source operands for the data ALU, which can be 16, 32, or 40 bits, always originate from data ALU registers. The results of all data ALU operations are stored in an accumulator.

A seven-stage pipeline executes one instruction per clock cycle. The destination of every arithmetic operation can be used as a source operand for the immediate following operation without penalty.

The MAC unit comprises the main arithmetic processing unit of the DSP core and performs all of the calculations on data operands. For arithmetic instructions, the unit accepts as many as three input operands and outputs one 40-bit result, formatted as Extension:Most Significant Product:Least Significant Product (EXT:MSP:LSP).

The multiplier executes 16-bit  $\times$  16-bit, parallel, fractional multiplies, between two's-complement signed, unsigned, or mixed operands. The 32-bit product is right-justified and added to the 40-bit contents of either the A or B accumulator. A 40-bit result can be stored as a 16-bit operand. The LSP can either be truncated or rounded into the MSP. Rounding is performed if specified.

The address generation unit (AGU) performs the effective address calculations using integer arithmetic necessary to address data operands in memory and contains the registers used to generate the addresses. It implements four types of arithmetic: linear, modulo, multiple wrap-around modulo, and reverse-carry. The AGU operates in parallel with other chip resources to minimize address-generation overhead.

The AGU is divided into two halves, each with its own address ALU. Each address ALU has four sets of register triplets, and each register triplet is composed of an address register, an offset register, and a modifier register. The two address ALUs are identical. Each contains a 16-bit full adder (referred to as an offset adder).

A second full adder (referred to as a modulo adder) adds the summed result of the first full adder to a modulo value that is stored in its respective modifier register. A third full adder (called a reverse-carry adder) is also provided.

The offset adder and the reverse-carry adder are in parallel and share common inputs. The only difference between them is that they carry propagates in opposite directions. Test logic determines which of the three summed results of the full adders is output.

Each address ALU can update one address register from its respective address register file during one instruction cycle. The contents of the associated modifier register specifies the type of arithmetic to be used in the address register update calculation. The modifier value is decoded in the address ALU.

#### 1.2.2.1.3 Program Control Unit

The program control unit (PCU) performs instruction prefetch, instruction decoding, hardware DO loop control and exception processing. The PCU implements a seven-stage pipeline and controls the different processing states of the DSP core. The PCU consists of three hardware blocks:

- program decode controller (PDC)

- program address generator (PAG)

- program interrupt controller (PIC)

The PDC decodes the 24-bit instruction loaded into the instruction latch and generates all signals necessary for pipeline control. The PAG contains all the hardware needed for program address generation, system stack and loop control. The PIC arbitrates among all interrupt requests and generates the appropriate interrupt vector address.

The PCU implements its functions using the following registers:

- PC—Program Counter register

- SR—Status Register

- LA—Loop Address register

- LC—Loop Counter register

- VBA—Vector Base Address register

- SZ—Size register

- SP—Stack Pointer

- OMR—Operating Mode Register

- SC—Stack Counter register

The PCU also includes a hardware System Stack (SS).

#### 1.2.2.1.4 Program Patch Logic

The program patch logic (PPL) block provides a way to adjust program code in the onchip ROM without generating a new mask. Implementing the code correction is done by replacing a piece of ROM-based code with a patch program stored in RAM. The PPL consists of four patch address registers (PAR0–PAR3) and four patch address comparators. Each PAR points to a starting location in the ROM code where the program flow is to be changed. The PC register in the PCU is compared to each PAR. When an address of a fetched instruction is identical to an address stored in one of the PARs, the program data bus is forced to a corresponding JMP instruction, replacing the instruction that otherwise would have been fetched from the ROM.

#### 1.2.2.2 DSP-Side Peripherals

The DSP-side peripherals for the DSP56654 are primarily targeted at handling baseband and audio processing.

- Two synchronous serial ports connect to external codecs to process received baseband information.

- The SAP connects to a standard audio codec. This port also provides a general-purpose timer.

- The **BBP** connects to a standard RF/IF codec.

- The DPD provides direct memory access for the SAP or BBP to enable these peripherals to operate without DSP intervention.

• DSP OnCE and data bus visibility facilitate test and debug.

#### 1.2.2.3 DSP-Side Memory

All DSP memory is contained on-chip. DSP program memory is 24 bits wide, while data memory is 16 bits (1 halfword) wide. Program ROM is 2K by 24 bits, and program RAM is 40K by 24 bits. Data memory is organized into two separate areas, X and Y, each accessed by its own address and data buses. The 14K halfwords of X data RAM include 12K for general use and 2K dual-port RAM for the MDI. Y data RAM is 15K by 16 bits, including 11K for general use, 2K dual-port RAM for the DPD, and 2K dual-port RAM for the VIAC.

#### 1.2.3 MCU-DSP Interface

The MDI provides a way for the MCU and DSP cores to communicate with each other. It contains a message and control unit as well as  $2K \times 16$ -bit dual-ported RAM.

# **Chapter 2 Signal/Connection Description**

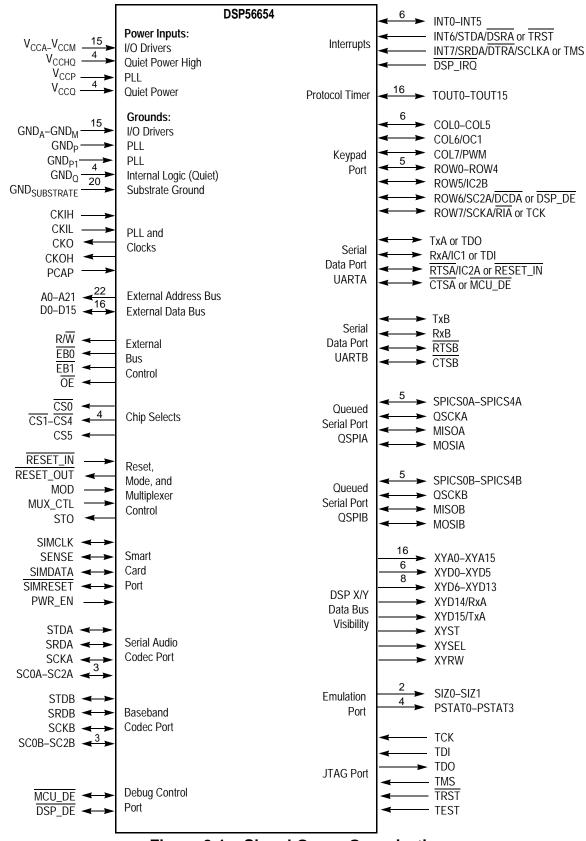

The DSP56654 input and output signals are organized into functional groups in Table 2-1 below and in Figure 2-1 on page 2-2. Many of the pins in the DSP56654 have multiple functions. In Table 2-1, pin function is described to reflect primary pin function. Subsequent tables in this section are named for these primary functions and provide full descriptions of all signals on the pins.

Table 2-1. DSP56654 Signal Functional Group Allocations

|                              | Number of<br>Signals        | Detailed<br>Description  |                          |

|------------------------------|-----------------------------|--------------------------|--------------------------|

| Power (V <sub>CCx</sub> )    |                             | 19                       | Table 2-2                |

| Function-specific groun      | 23                          | Table 2-3                |                          |

| Substrate ground (GND        | SUBSTRATE)                  | 20                       |                          |

| PLL and clocks               |                             | 5                        | Table 2-4                |

| External Interface Modu      | ıle (EIM)                   | 48                       | Table 2-5                |

| Reset, mode, and multi       | plexer control              | 5                        | Table 2-6                |

| DSP X/Y visibility port      |                             | 35                       | Table 2-7                |

| External interrupts          |                             | 9                        | Table 2-8                |

| Protocol Timer               |                             | 16                       | Table 2-9                |

| Keypad port                  | 16                          | Table 2-10               |                          |

| UARTA<br>UARTB               |                             | 4 4                      | Table 2-11<br>Table 2-12 |

| Queued Serial Peripher QSPIB | 8<br>8                      | Table 2-13<br>Table 2-14 |                          |

| Smart Card Port (SCP)        |                             | 5                        | Table 2-15               |

| Serial Audio Codec Por       | t (SAP)                     | 6                        | Table 2-16               |

| Baseband Codec Port (        | 6                           | Table 2-17               |                          |

| Development & Test           | Emulation port              | 6                        | Table 2-18               |

|                              | Debug control port          | 2                        |                          |

|                              | JTAG test access port (TAP) | 6                        | Table 2-20               |

Figure 2-1. Signal Group Organization

## 2.1 Power

The DSP56654 power pins are listed in Table 2-2.

Table 2-2. Power

|                   | 14.0.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Power Signals     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| V <sub>CCA</sub>  | Address bus power—These linessupply isolated power to the address bus drivers.                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| V <sub>CCB</sub>  | SIM power—This line supplies isolated power for the smart card I/O drivers.                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| V <sub>CCC</sub>  | Bus control power—This line supplies power to the bus control logic.                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| V <sub>CCD</sub>  | Data bus power—These lines supply power to the data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| V <sub>CCE</sub>  | Audio codec port power—This line supplies power to audio codec I/O drivers.                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| V <sub>CCF</sub>  | Clock output power—This line supplies a quiet power source for the CKOUT output. Ensure that the input voltage to this line is well-regulated and uses an extremely low impedance path to tie to the $V_{CC}$ power rail. Use a 0.1 $\mu F$ bypass capacitor located as close as possible to the chip package to connect between the $V_{CCF}$ line and the $GND_F$ line.                                                                                                                           |  |

| V <sub>CCG</sub>  | <b>GPIO power</b> —This line supplies power to the GPIO, keypad, UARTs, interrupts, STO, and JTAG I/O drivers.                                                                                                                                                                                                                                                                                                                                                                                      |  |

| V <sub>CCH</sub>  | Baseband codec and timer power—This line supplies power to the baseband codec, QSPIs, and Timer I/O drivers.                                                                                                                                                                                                                                                                                                                                                                                        |  |

| V <sub>CCHQ</sub> | <b>Quiet power high</b> —These lines supply a quiet power source to the pre-driver voltage converters. This value should be equal to the maximum value of the power supplies of the chip I/O drivers (i.e., the maximum of $V_{CCA}$ , $V_{CCB}$ , $V_{CCC}$ , $V_{CCD}$ , $V_{CCE}$ , $V_{CCF}$ , $V_{CCG}$ , $V_{CCH}$ , and $V_{CCK}$ ).                                                                                                                                                         |  |

| V <sub>CCK</sub>  | Emulation port power—This line supplies power to the emulation port I/O drivers.                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| V <sub>CCL</sub>  | DSP X/Y address visibility and port control power—This line supplies power to the DSP address visibility and port control system                                                                                                                                                                                                                                                                                                                                                                    |  |

| V <sub>CCM</sub>  | DSP X/Y data visibility power—This line supplies power to the DSP data visibility system.                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| V <sub>CC P</sub> | Analog PLL circuit power—This line is dedicated to the analog PLL circuits and must remain noise-free to ensure stable PLL frequency and performance. Ensure that the input voltage to this line is well-regulated and uses an extremely low impedance path to tie to the $V_{CC}$ power ail. Use a 0.1 $\mu$ F capacitor and a 0.01 $\mu$ F capacitor located as close as possible to the chip package to connect between the $V_{CCP}$ line and the GND <sub>P</sub> and GND <sub>P1</sub> lines. |  |

| V <sub>CCQ</sub>  | <b>Quiet power</b> —These lines supply a quiet power source to the internal logic circuits. Ensure that the input voltage to this line is well-regulated and uses an extremely low impedance path to tie to the $V_{CC}$ power rail. Use a 0.1 $\mu$ F bypass capacitor located as close as possible to the chip package to connect between the $V_{CCQ}$ lines and the GND <sub>Q</sub> lines.                                                                                                     |  |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

## 2.2 Ground

The DSP56654 ground pins are listed in Table 2-3.

Table 2-3. Ground

| Ground Signals           | Description                                                                                                                  |  |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------|--|

| GND <sub>A</sub>         | Address bus ground—These lines connect system ground to the address bus.                                                     |  |

| GND <sub>B</sub>         | SIM ground—These lines connect system ground to the smart card bus.                                                          |  |

| GND <sub>C</sub>         | Bus control ground—This line connects ground to the bus control logic.                                                       |  |

| GND <sub>D</sub>         | Data bus ground—These lines connect system ground to the data bus.                                                           |  |

| GND <sub>E</sub>         | Audio codec port ground—These lines connect system ground to the audio codec port.                                           |  |

| GND <sub>F</sub>         | Clock output ground—This line supplies a quiet ground connection for the clock output drivers.                               |  |

| $GND_G$                  | <b>GPIO ground</b> —These lines connect system ground to GPIO, keypad, data port, interrupts, STO, and JTAG I/O drivers.     |  |

| GND <sub>H</sub>         | <b>Baseband codec and timer ground</b> —These lines connect system ground to the baseband codec and timer I/O drivers.       |  |

| GND <sub>K</sub>         | <b>Emulation port ground</b> —These lines connect system ground to the emulation port I/O drivers.                           |  |

| GND <sub>L</sub>         | DSP X/Y address visibility and port control ground—This line grounds the DSP X/Y address visibility and port control system. |  |

| GND <sub>M</sub>         | DSP X/Y data visibility ground—This line grounds the DSP data visibility system.                                             |  |

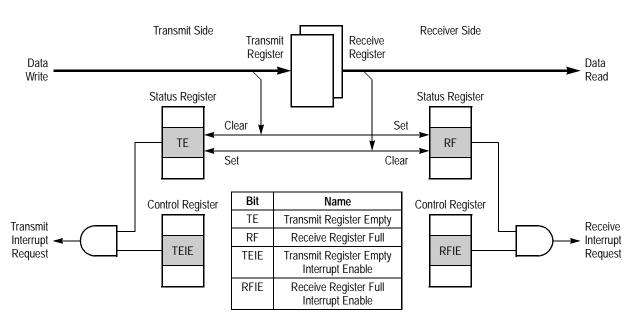

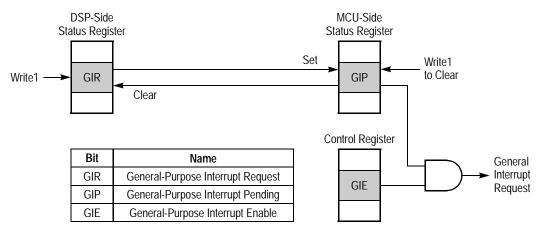

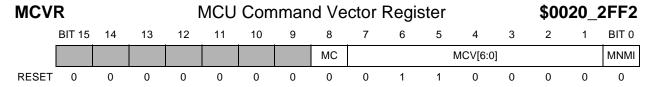

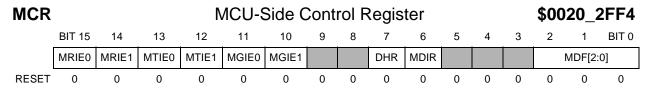

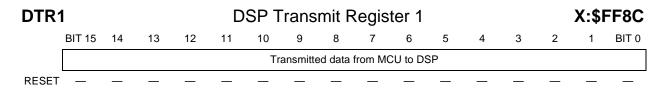

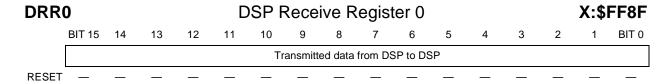

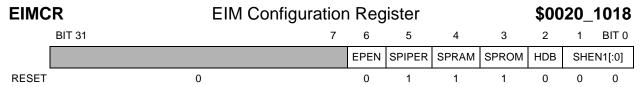

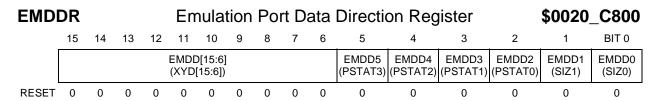

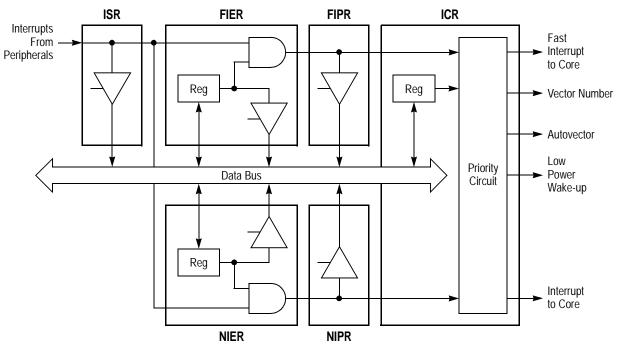

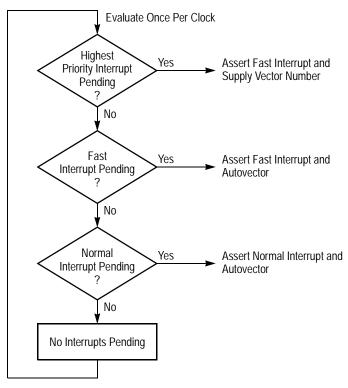

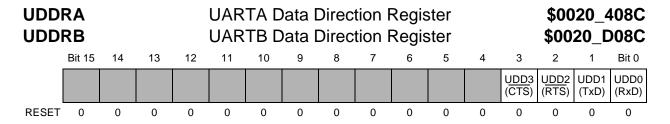

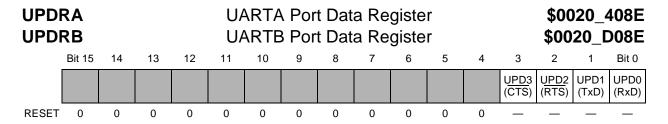

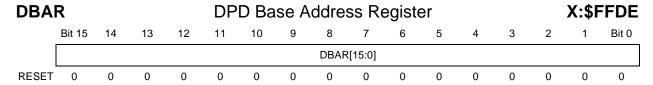

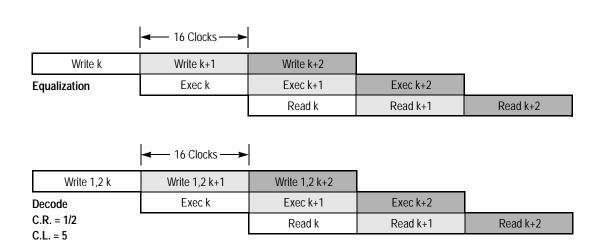

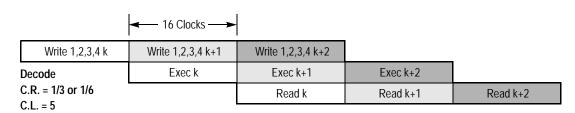

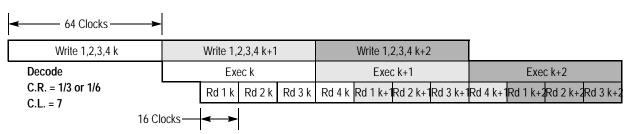

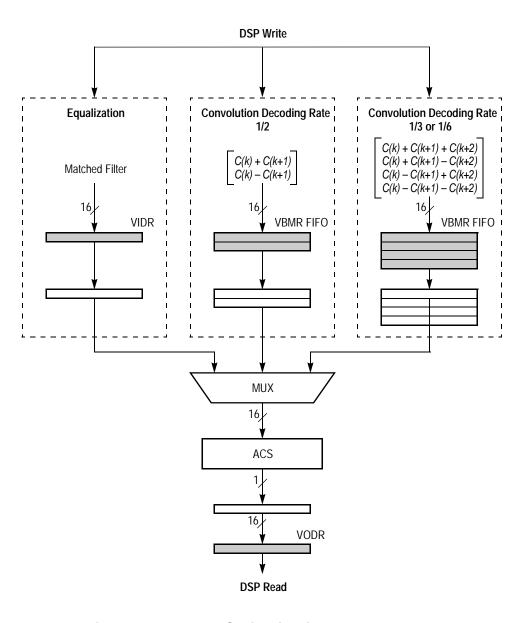

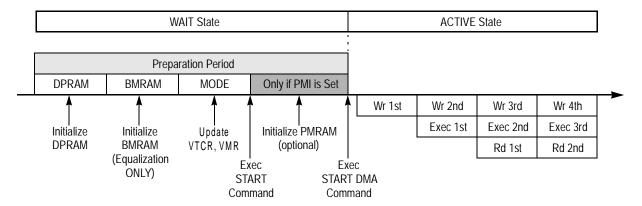

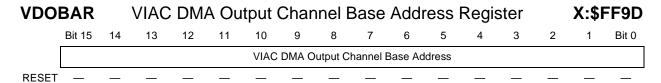

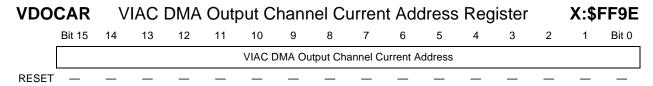

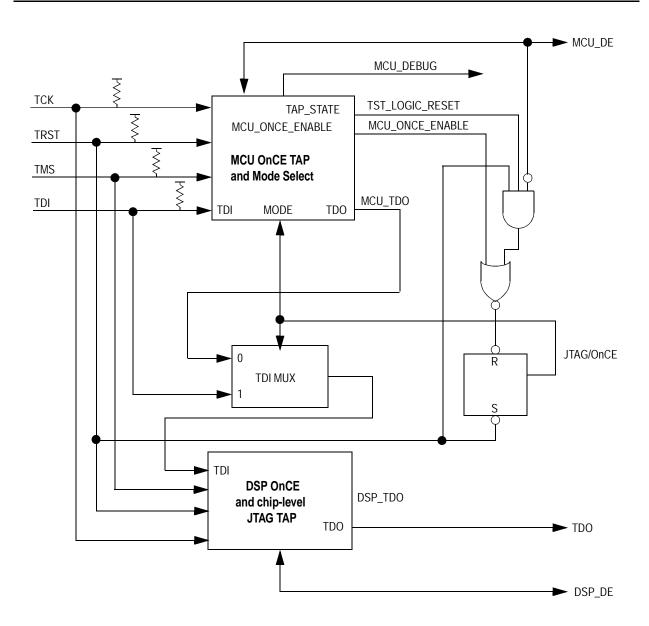

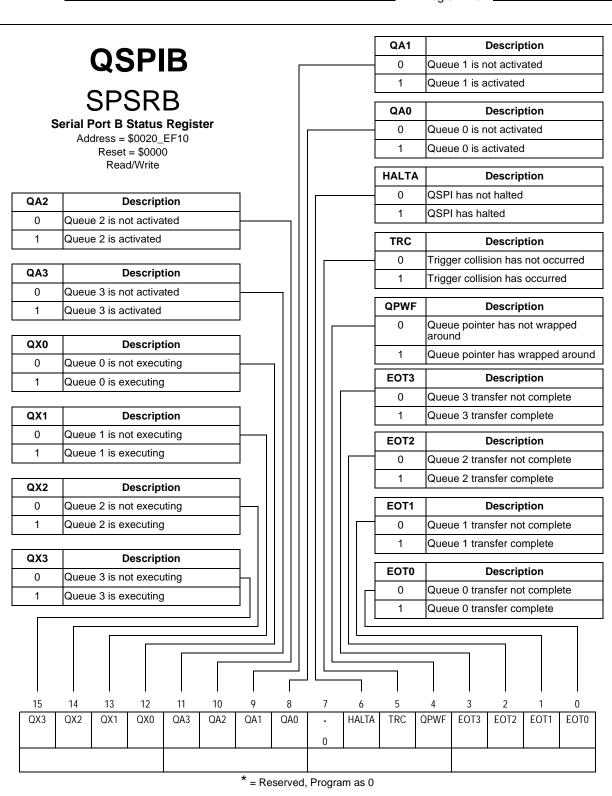

| GND <sub>P</sub>         | Analog PLL circuit ground—This line supplies a dedicated quiet ground connection for the analog PLL circuits.                |  |