## 56852

**User Manual**

## 56852 Digitial Signal Controller

DSP56852UM Rev. 4 06/2005

freescale.com

This manual is one of a set of three documents. For complete product information, it is necessary to have all three documents. They are: 56800E Reference Manual, 56852 User Manual, and Technical Data Sheet.

HOME PAGE: http://www.freescale.com

Order this document as <u>DSP56F852UM - Rev 4.0</u> June, 2005

#### **Summary of Changes and Updates:**

Clarified SPI Chapter Section 12.9.1.5 and 12.9.2.7 Appendix C Packaging and Pin Information was removed and is now contained in the 56852 Data Sheet Converted to Freescale format

## TABLE OF CONTENTS

## **Chapter 1 56852 Overview**

| 1.1     | Introduction                                        | 1-3           |

|---------|-----------------------------------------------------|---------------|

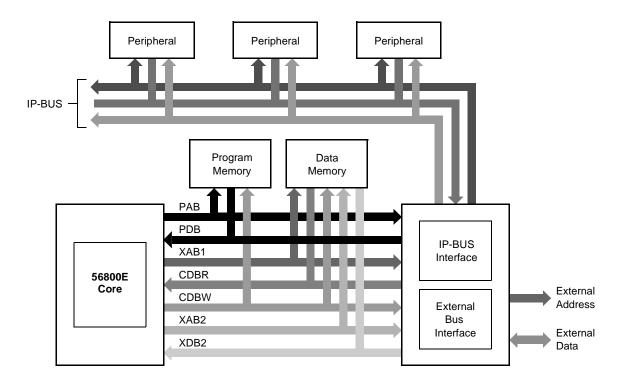

| 1.2     | 56800E Core Description                             | 1-4           |

| 1.2.1   | Key Features                                        |               |

| 1.2.2   | 56800E Core Enhancements                            |               |

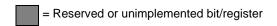

| 1.2.3   | System Architecture and Peripheral Interface        | 1-5           |

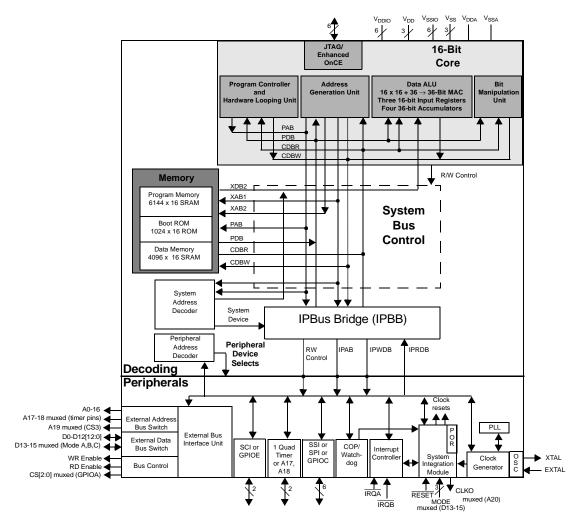

| 1.2.4   | 56800E Core Block Diagram                           | 1-7           |

| 1.2.5   | Address Buses                                       | 1-8           |

| 1.2.6   | Data Buses                                          |               |

| 1.2.7   | Data Arithmetic Logic Unit (Data ALU)               | I <b>-</b> 10 |

| 1.2.8   | Address Generation Unit (AGU)                       |               |

| 1.2.9   | Program Controller and Hardware Looping Unit        |               |

| 1.2.10  | Bit Manipulation Unit                               |               |

| 1.2.11  | Programmable Chip Selects                           |               |

| 1.2.12  | Enhanced On-Chip Emulation (EOnCE) Module           |               |

| 1.2.13  | Clocks                                              |               |

| 1.2.13. |                                                     |               |

| 1.2.13. |                                                     |               |

| 1.2.13. |                                                     |               |

| 1.2.13. |                                                     |               |

|         | 56852 Architectural Overview                        |               |

|         | System Bus Controller                               |               |

| 1.4.1   | Operation Method                                    |               |

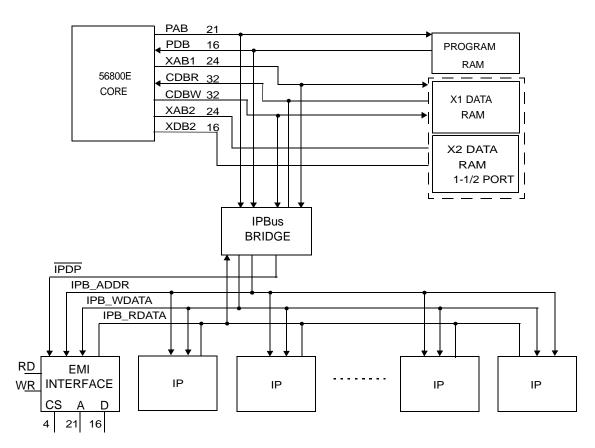

| 1.4.2   | IPBus Bridge (IPBB)                                 |               |

| 1.4.2.1 | System Side Operation                               |               |

| 1.4.2.2 |                                                     |               |

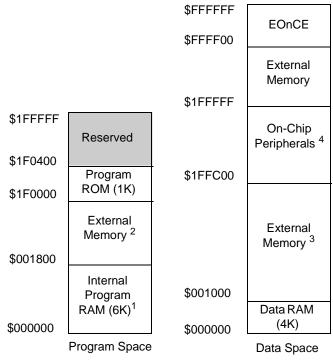

|         | 56852 Memory                                        |               |

|         | 56852 Peripheral Blocks                             |               |

| 1.6.1   | Energy Information                                  |               |

| 1.6.2   | COP/Watchdog Timer Module                           |               |

| 1.6.3   | Peripheral Interrupts/Interrupt Controller Module   |               |

| 1.6.4   | Serial Communications Interface Module (SCI)        |               |

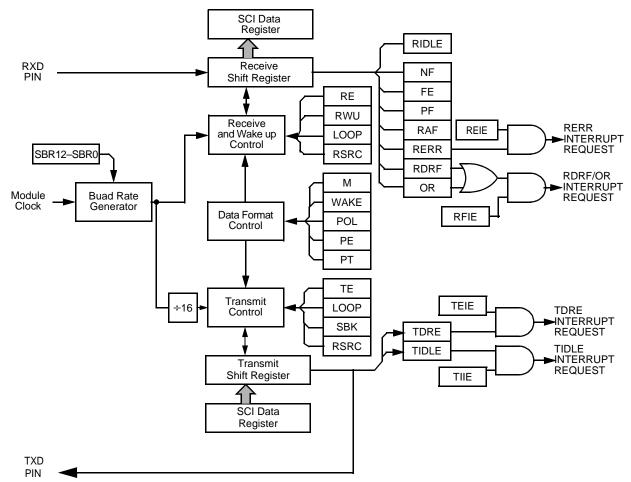

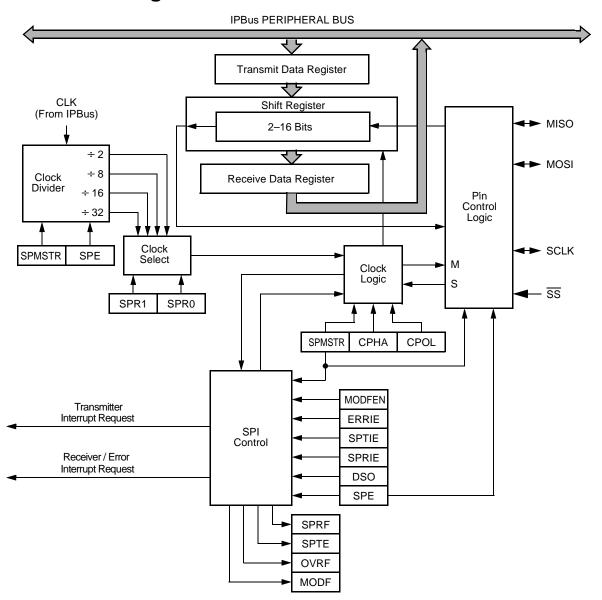

| 1.6.5   | Serial Peripheral Interface Module (SPI)            |               |

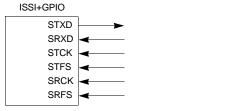

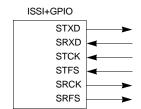

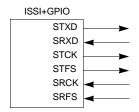

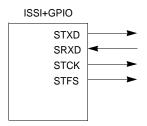

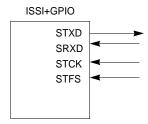

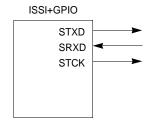

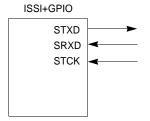

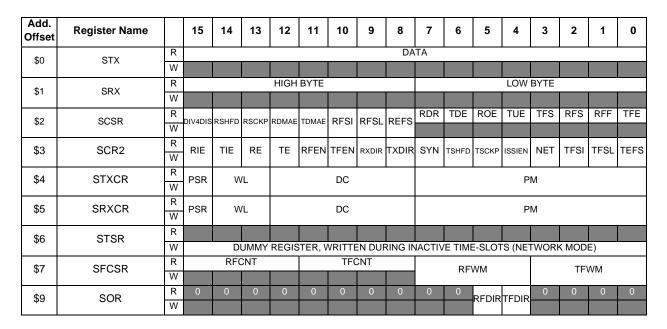

| 1.6.6   | Improved Synchronous Serial Interface Module (ISSI) |               |

| 1.6.7   | Quad Timer Module (TMR)                             |               |

| 1.6.8   | General Purpose Input/Output Port (GPIO)            |               |

| 1.6.9   | Resets1                                             | 1-22          |

Table of Contents, Rev. 4

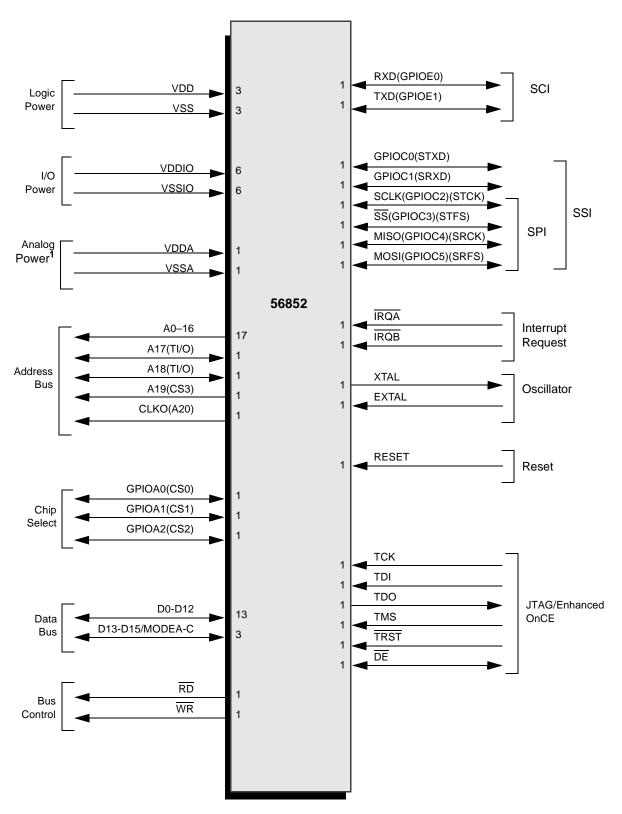

|        | pter 2<br>Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.1    | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2.2    | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.3    | Signal and Package Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|        | pter 3<br>mory (MEM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3.1    | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3.2    | Program Boot ROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.2.1  | Boot Mode 0: Bootstrap From Byte-Wide External Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3.2.2  | Boot Mode 1: Bootstrap From SPI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.2.3  | Boot Mode 2: Normal Expanded Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3.2.4  | Boot Mode 3: Development Expanded Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3.2.5  | Boot Mode 4: Bootstrap From Host Port–Single Strobe Clocking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3.2.6  | Boot Mode 5: Bootstrap From Host Port–Dual Strobe Clocking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3.2.7  | Boot Mode 6: Bootstrap From SCI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.2.8  | Boot Mode 7: Reserved for Future Use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3.3    | Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3.3.1  | Memory Register Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.3.1. | The state of the s |

| 3.3.2  | Interrupt Vectors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|        | pter 4<br>tem Integration Module (SIM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4.1    | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4.2    | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

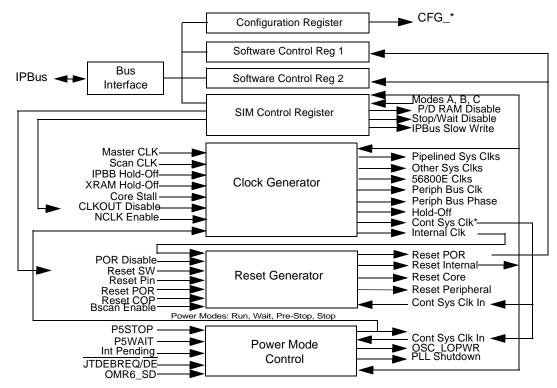

| 4.3    | SIM Block Diagram4-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4.4    | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4.4.1  | SIM Interface Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

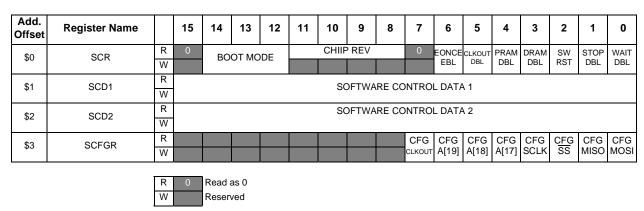

| 4.5    | Module Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4.6    | Register Descriptions (SYS_BASE = \$1FFF08)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4.6.1  | SIM Control Register (SCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4.6.1. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4.6.1. | 2 Boot Mode—Bits 14–124-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4.6.1. | the state of the s |

| 4.6.1. | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4.6.1. | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4.6.1. | 2.4 Boot Mode 3: Development Expanded Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4.6.1.2.5 | 5 Boot Modes 4–5: Reserved                          | 4-11 |

|-----------|-----------------------------------------------------|------|

| 4.6.1.2.6 | Boot Mode 6: Bootstrap from SCI Port                | 4-11 |

| 4.6.1.2.7 |                                                     |      |

| 4.6.1.3   | Reserved—Bits 11–7                                  | 4-11 |

| 4.6.1.4   | Enhanced OnCE Enable (OnCE_EBL)—Bit 6               | 4-12 |

| 4.6.1.5   | CLKOUT Disable (CLKOUT_DBL)—Bit 5                   | 4-12 |

| 4.6.1.6   | Program RAM Disable (PRAM_DBL)—Bit 4                | 4-12 |

| 4.6.1.7   | Data RAM Disable (DRAM_DBL)—Bit 3                   | 4-12 |

| 4.6.1.8   | Software Reset (SW_RST)—Bit 2                       | 4-12 |

| 4.6.1.9   | Stop Disable (STOP_DBL)—Bit 1                       | 4-12 |

| 4.6.1.10  | Wait Disable (WAIT_DBL)—Bit 0                       | 4-12 |

| 4.6.2     | SIM Software Control Data 1 (SCD1)                  | 4-13 |

| 4.6.2.1   | Software Control Data 1 (SSCR1)—Bits 15–0           | 4-13 |

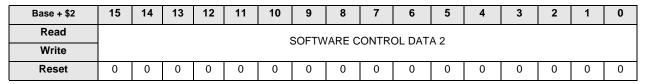

| 4.6.3     | Software Control Data 2 (SCD2)                      | 4-13 |

| 4.6.3.1   | Software Control Data 2 (SCD2)—Bits 15–0            | 4-13 |

| 4.6.4     | SIM Configuration Register (SCFGR)                  | 4-14 |

| 4.6.4.1   | Reserved—Bits 15–8                                  | 4-14 |

| 4.6.4.2   | Configure Clock Out (CFG_CLKOUT)—Bit 7              | 4-14 |

| 4.6.4.3   | Configure A[19] Output (CFG_A[19])—Bit 6            | 4-14 |

| 4.6.4.4   | Configure A[18] Output (CFG_A[18])—Bit 5            | 4-14 |

| 4.6.4.5   | Configure A[17] Output (CFG_A[17])—Bit 4            | 4-14 |

| 4.6.4.6   | Configure Serial Clock (CFG_SCLK)—Bit 3             | 4-14 |

| 4.6.4.7   | Configure Slave Select Output (CFG_SS)—Bit 2        | 4-15 |

| 4.6.4.8   | Configure Master In/Slave Out (CFG_MISO)—Bit 1      | 4-15 |

| 4.6.4.9   | Configure Master Out/Slave In (CFG_MOSI)—Bit 0      | 4-15 |

| 4.7 Ir    | mplementation                                       | 4-15 |

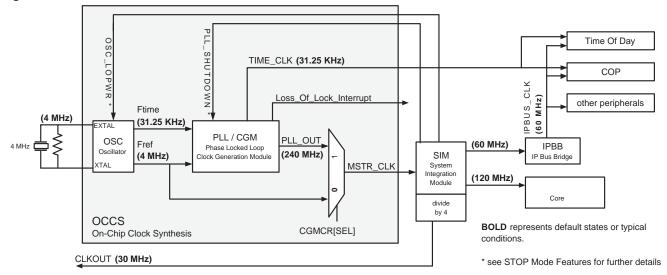

| 4.7.1     | Clock Generation Concepts                           | 4-15 |

| 4.7.2     | Clock Hold-Off                                      | 4-16 |

| 4.7.3     | Core Stall                                          | 4-16 |

| 4.7.4     | Wait Request                                        | 4-16 |

| 4.7.5     | Transaction Abort                                   | 4-16 |

| 4.7.6     | Coordination of Peripheral and System Buses by IPBB | 4-17 |

| 4.7.7     | Clock Waveforms                                     | 4-17 |

| 4.8 G     | Generated Clocks                                    | 4-18 |

| 4.9 G     | Senerated Resets                                    | 4-18 |

| 4 10 P    | Power Mode Controls                                 | 4-19 |

# **Chapter 5 External Memory Interface (EMI)**

| 5.1     | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 5-3       |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 5.2     | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 5-3       |

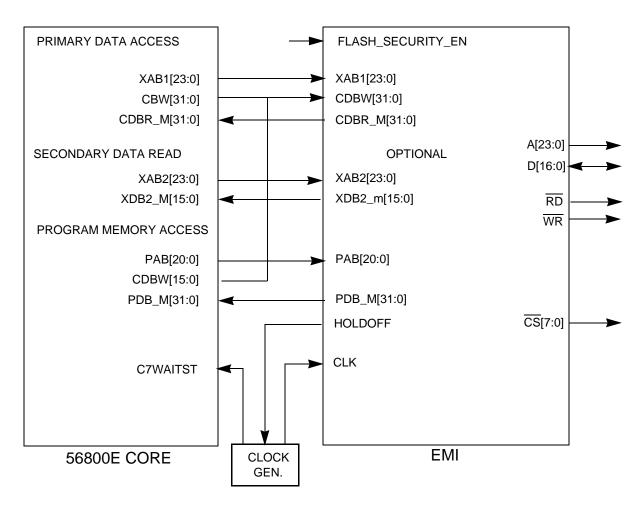

| 5.3     | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 5-4       |

| 5.3.1   | Core Interface Detail                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |

| 5.4     | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 5-5       |

| 5.5     | Module Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 5-5       |