# LH79524/LH79525 User's Guide

#### Specifications are subject to change without notice.

Suggested applications (if any) are for standard use; See *Important Restrictions* for limitations on special applications. See *Limited Warranty* for NXP's product warranty. The Limited Warranty is in lieu, and exclusive of, all other warranties, express or implied. ALL EXPRESS AND IMPLIED WARRANTIES, INCLUDING THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR USE AND FITNESS FOR A PARTICULAR PURPOSE, ARE SPECIFICALLY EXCLUDED. In no event will NXP be liable, or in any way responsible, for any incidental or consequential economic or property damage.

Purchase of I<sup>2</sup>C components from NXP Corporation or one of its sublicensed Associated Companies conveys a license under the NXP I<sup>2</sup>C Patent. Rights are granted to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by NXP.

LH79524/LH79525 MCU User's Guide Produced by NXP Semiconductors © 2004-2009 Copyright NXP Semiconductors.

### **Content Revisions**

This document contains the following changes to content, causing it to differ from previous versions. Minor typographical changes, where they do not affect content, are not tracked here.

#### **Record of Revisions**

| DATE     | PAGE<br>NO. | SECTION, TABLE, OR ILLUSTRATION   | SUMMARY OF CHANGES                                                  |

|----------|-------------|-----------------------------------|---------------------------------------------------------------------|

|          | Throughout  | _                                 | Updated version number to Version 1.0.                              |

|          | Throughout  | _                                 | "Preliminary" removed from all references.                          |

|          | 5-3         | Section 5.1.1                     | Section added to clarify operation.                                 |

|          | 7-16        | Section 7.2.4.5                   | Corrected nWAIT description.                                        |

|          | 7-32        | Section 7.5.2.3                   | Corrected settings of bit 8.                                        |

|          | 9-5         | Section 9.1.5                     | Added section.                                                      |

|          | 13-3        | Section 13.1.1                    | Section added to clarify reset of System and USB PLLs.              |

|          | 13-9        | Table 13-5                        | "IMPORTANT" note added.                                             |

|          | 13-14       | Section 13.2.2.4                  | Phrase added to clarify reset of System and USB PLLs.               |

|          | 13-17       | Section 13.2.2.7                  | Corrected equation.                                                 |

| 11-30-06 | 13-18       | Section 13.2.2.8                  | Corrected equation.                                                 |

| 11-30-06 | 13-32       | Section 13.2.2.21                 | Added text regarding changing from Standard Mode to FastBus Mode    |

|          | 13-33       | Table 13-53,<br>Section 13.2.2.22 | Definition of SYSPREDIV and equation corrected.                     |

|          | 13-34       | Table 13-55,<br>Section 13.2.2.23 | Definition of USBPREDIV and equation corrected.                     |

|          | 14-8        | Section 14.1.6.4                  | Section rewritten for clarity.                                      |

|          | 14-13       | Section 14.2.2.3                  | Clarified handling transactions less than, or greater than 16 bits. |

|          | 14-20       | Section 14.2.2.10                 | Text added to clarify operation.                                    |

|          | 15-3        | Section 15.1.1                    | Rewrote section for clarity.                                        |

|          | 16-27       | Section 16.3.2.14                 | Text added to clarify operation.                                    |

#### Record of Revisions (Cont'd)

| DATE    | PAGE<br>NO. | SECTION, TABLE, OR ILLUSTRATION | SUMMARY OF CHANGES                                                                        |

|---------|-------------|---------------------------------|-------------------------------------------------------------------------------------------|

|         | _           | Throughout                      | Version updated to 1.1.                                                                   |

|         | 5-4         | Section 5.1.2.1                 | Section added to clarify DMA priority.                                                    |

|         | 4-18 – 4-19 | Section 4.4.2                   | Enhanced text in Section 4.4.2.1 and Section 4.4.2.2, and added Section 4.4.2.3.          |

|         | 4-21        | Table 4-15                      | HSW clarified for AD-TFT panels.                                                          |

| 6-16-07 | 5-10        | Section 5.2.2.4                 | Added second paragraph to advise users to correctly specify DMA parameters.               |

|         | 9-3         | Section 9.1.1                   | Added final paragraph describing effect of external pullup resistor to timing.            |

|         | 9-7         | Table 9-5                       | Bit descriptions enhanced for the SABT and STOP bits.                                     |

|         | 13-34       | Section 13.2.2.23               | Reduced power suggestion when not using USB added; Power Down bit (bit 13) made RESERVED. |

|         | 14-8        | Section 14.1.6.2                | Corrected reference to SSE bit to bit position 1 in CTL1.                                 |

|         | 17-4        | Section 17.1.4.2                | Added this section.                                                                       |

|         | 17-21       | Section 17.2.3.3                | Text added to describe the STALL function for EP 0.                                       |

|         |             |                                 |                                                                                           |

| 8-27-07 | All         | _                               | All references to Sharp replaced with NXP. Revision number rolled to Version 1.2.         |

| 3-04-09 | 7-48        | Table 7-47                      | Corrected memory configuration.                                                           |

## **Table of Contents**

| Pretace                                                 |         |

|---------------------------------------------------------|---------|

| Conventions and Terms                                   | XXXV    |

| Unconnected (Floating) Inputs                           | XXXV    |

| Multiplexed Pins                                        | xxxv    |

| Pin Names                                               | xxxvi   |

| Peripheral Devices                                      | xxxvi   |

| Register Addresses                                      | xxxvi   |

| Register Tables                                         | xxxvii  |

| Numeric Values                                          | xxxviii |

| Block Diagrams                                          | xxxviii |

| What's in This User's Guide                             | xl      |

| Chapter 1 – Overview                                    | xl      |

| Chapter 2 – ADC and Brownout Detector                   | xl      |

| Chapter 3 – Boot Controller                             | xl      |

| Chapter 4 – Color LCD Controller                        |         |

| Chapter 5 – DMA Controller                              | xl      |

| Chapter 6 – Ethernet MAC                                | xl      |

| Chapter 7 – External Memory Controller                  | xli     |

| Chapter 8 – General Purpose Input/Output                | xli     |

| Chapter 9 – I2C Interface                               |         |

| Chapter 10 – I2S Converter                              |         |

| Chapter 11 – I/O Configuration                          | xli     |

| Chapter 12 – Real Time Clock                            |         |

| Chapter 13 – Reset, Clock Generation and Power Control  |         |

| Chapter 14 – Synchronous Serial Port                    |         |

| Chapter 15 – Timers                                     |         |

| Chapter 16 – UARTs                                      |         |

| Chapter 17 – USB Device                                 |         |

| Chapter 18 – Vectored Interrupt Controller              | xlii    |

| Chapter 19 – Watchdog Timer                             |         |

| Appendix – Glossary                                     | xlii    |

| • • • • • • • • • • • • • • • • • • • •                 |         |

| Chapter 1 – Overview                                    | 1.0     |

| 1.1 Bus Architecture                                    |         |

| 1.2 Power Supply                                        |         |

| 1.2.1 Linear Regulator                                  |         |

| 1.2.2 Phase Locked Loop Power                           |         |

| 1.3 Clock Strategy                                      |         |

| 1.3.1 Bus Clocking Modes                                |         |

| 1.3.1.1 Standard Bus Clocking Modes                     |         |

| 1.3.1.2 Synchronous and Asynchronous Bus Clocking Modes |         |

| 1.3.1.3 Fastbus Extension Bus Clocking Mode             |         |

| 1.4 Reset Strategy                                      |         |

| 1.4.1 Resetting the Test Access Port Controller         | 1-9     |

| 1.4.2 Hardware Requirements at Reset                      | 1-10 |

|-----------------------------------------------------------|------|

| 1.4.2.1 Floating Inputs                                   |      |

| 1.4.2.2 Test Pins                                         |      |

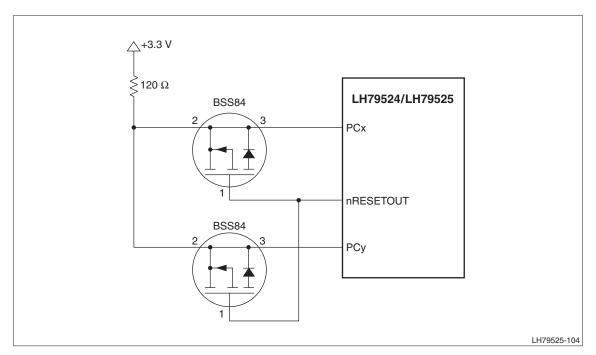

| 1.4.2.3 Active Pull Ups                                   | 1-11 |

| 1.5 AHB Bus Master Priority and Arbitration               |      |

| 1.6 Memory Interface Architecture                         |      |

| 1.7 Instruction and Data Cache                            |      |

| 1.8 Memory Management Unit (MMU)                          | 1-17 |

| Chapter 2 – Analog-to-Digital Converter/Brownout Detector |      |

| 2.1 Theory of Operation                                   | 2-1  |

| 2.1.1 Operational Summary                                 |      |

| 2.1.2 Bias-and-Control Network                            |      |

| 2.1.3 Clock Generator                                     | 2-5  |

| 2.1.4 Brownout Detector                                   | 2-5  |

| 2.1.5 SAR Architecture                                    | 2-5  |

| 2.1.6 Battery Control Feature                             |      |

| 2.1.7 Timing Formulas                                     |      |

| 2.1.8 Interrupts                                          |      |

| 2.1.8.1 Brownout Interrupt                                | 2-8  |

| 2.1.8.2 Pen Interrupt                                     | 2-9  |

| 2.1.8.3 End-of-Sequence Interrupt                         |      |

| 2.1.8.4 FIFO Watermark Interrupt                          | 2-9  |

| 2.1.8.5 FIFO Overrun Interrupt                            | 2-9  |

| 2.1.9 Application Details                                 | 2-9  |

| 2.2 Register Reference                                    | 2-10 |

| 2.2.1 Memory Map                                          | 2-10 |

| 2.2.2 Register Descriptions                               | 2-11 |

| 2.2.2.1 High Word Register (HW)                           | 2-11 |

| 2.2.2.2 Low Word Register (LW)                            | 2-13 |

| 2.2.2.3 Results Register (RR)                             | 2-14 |

| 2.2.2.4 Interrupt Mask Register (IM)                      |      |

| 2.2.2.5 Power Configuration Register (PC)                 | 2-16 |

| 2.2.2.6 General Configuration Register (GC)               | 2-18 |

| 2.2.2.7 General Status Register (GS)                      | 2-19 |

| 2.2.2.8 Interrupt Status Register (IS)                    | 2-20 |

| 2.2.2.9 FIFO Status Register (FS)                         | 2-21 |

| 2.2.2.10 Control Bank Registers                           |      |

| 2.2.2.11 Idle High Word Register (IHWCTRL)                |      |

| 2.2.2.12 Idle Low Word Register (ILWCTRL)                 | 2-24 |

| 2.2.2.13 Masked Interrupt Status Register (MIS)           |      |

| 2.2.2.14 Interrupt Clear Register (IC)                    | 2-26 |

ii

| Chapter 3 – Boot Controller                                |                 |

|------------------------------------------------------------|-----------------|

| 3.1 Theory of Operation                                    | 3-2             |

| 3.1.1 Boot Device Determination                            | 3-2             |

| 3.1.1.1 NAND Flash Operation                               | 3-4             |

| 3.1.2 Hardware Design Considerations                       | 3-4             |

| 3.1.2.1 Active Pullups To Signal Boot Mode                 | 3-4             |

| 3.1.2.2 NAND Flash Hardware Design                         | 3-5             |

| 3.1.3 Booting Using the I2C Interface                      |                 |

| 3.1.4 Booting from UART                                    |                 |

| 3.2 Register Reference                                     |                 |

| 3.2.1 Memory Map                                           |                 |

| 3.2.2 Register Definitions                                 |                 |

| 3.2.2.1 Power-up Boot Configuration Register (PBC)         |                 |

| 3.2.3 nCS1 Override Register (CS1OV)                       |                 |

| 3.2.4 External Peripheral Mapping Register (EPM)           |                 |

| Chapter 4 – Color Liquid Crystal Display Controller        |                 |

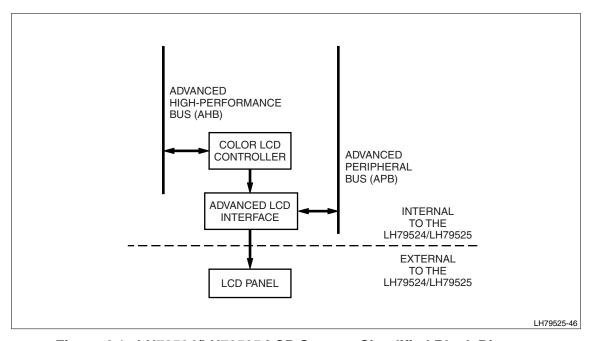

| 4.1 Introduction                                           | 4-1             |

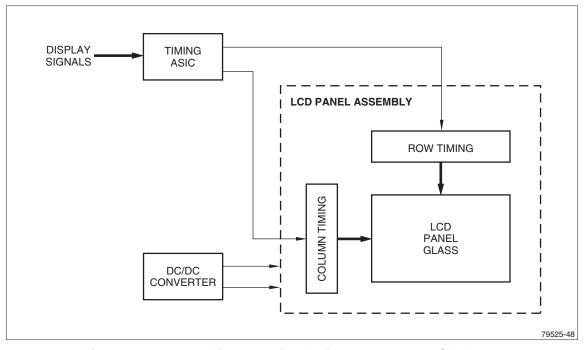

| 4.1.1 LCD Panel Architecture                               |                 |

| 4.2 CLCDC Features                                         | 4-3             |

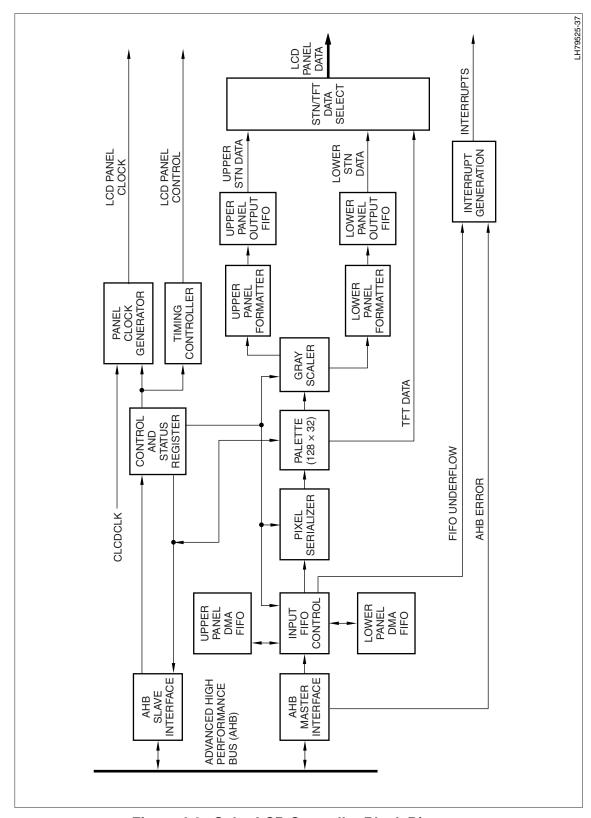

| 4.3 Theory of Operation                                    |                 |

| 4.3.1 Supported Displays and Panels                        |                 |

| 4.3.2 Frame Buffer                                         |                 |

| 4.3.3 LCD DMA FIFOs                                        |                 |

| 4.3.4 Pixel Serializer                                     |                 |

| 4.3.5 How Pixels are Stored in Memory                      |                 |

| 4.3.6 Palette RAM                                          |                 |

| 4.3.6.1 Grayscale Algorithm                                |                 |

| 4.3.6.2 Interrupts                                         |                 |

| 4.3.6.3 LCD Panel Resolutions                              |                 |

| 4.3.7 LCD Data Multiplexing                                |                 |

| 4.3.8 LCD Interface Timing Signals                         |                 |

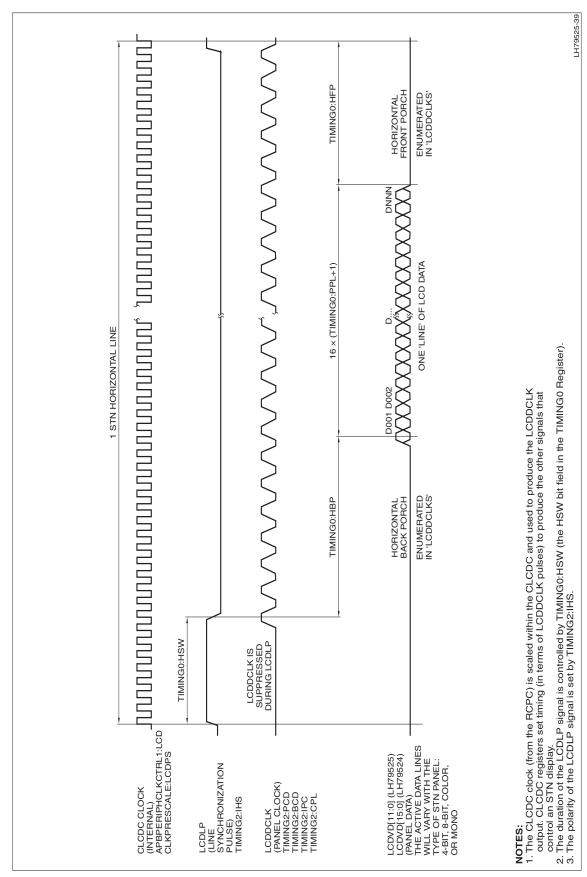

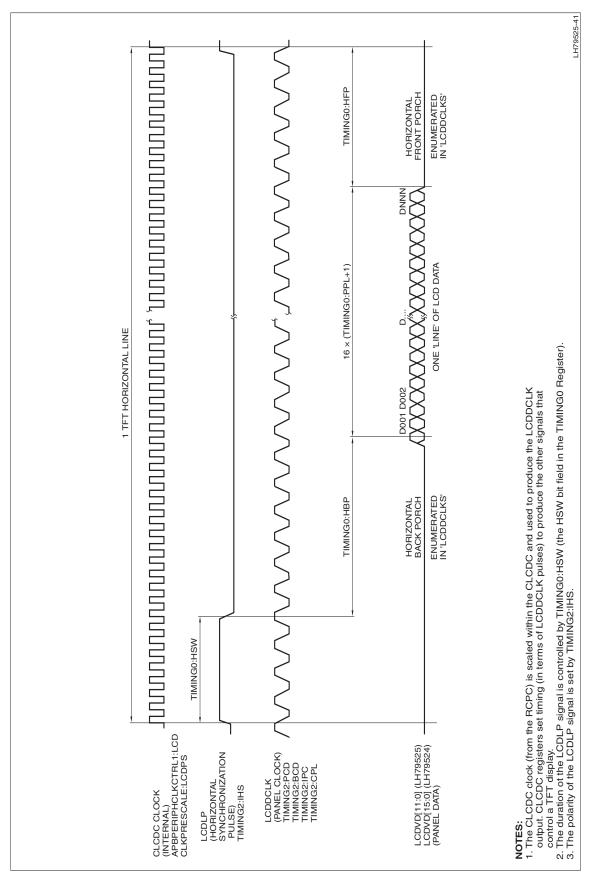

| 4.3.8.1 LCD Horizontal Timing Signals                      |                 |

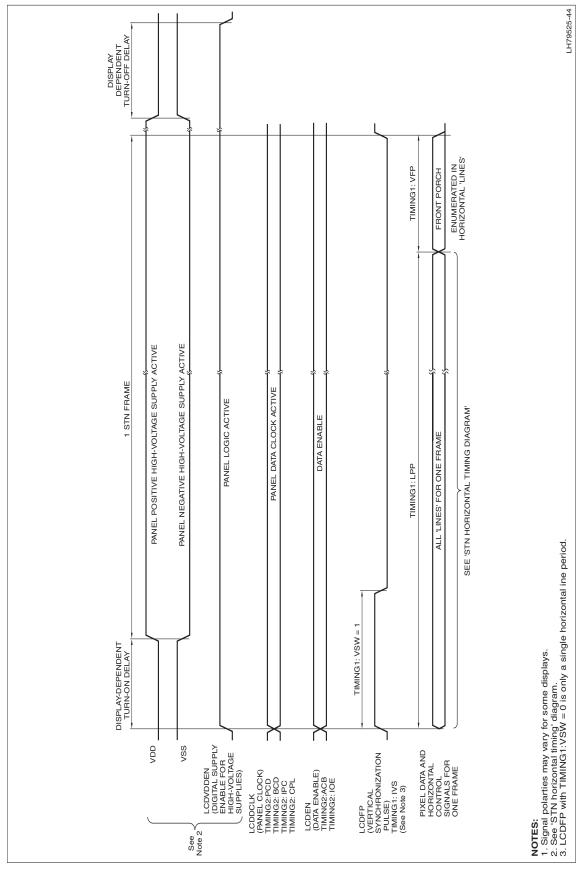

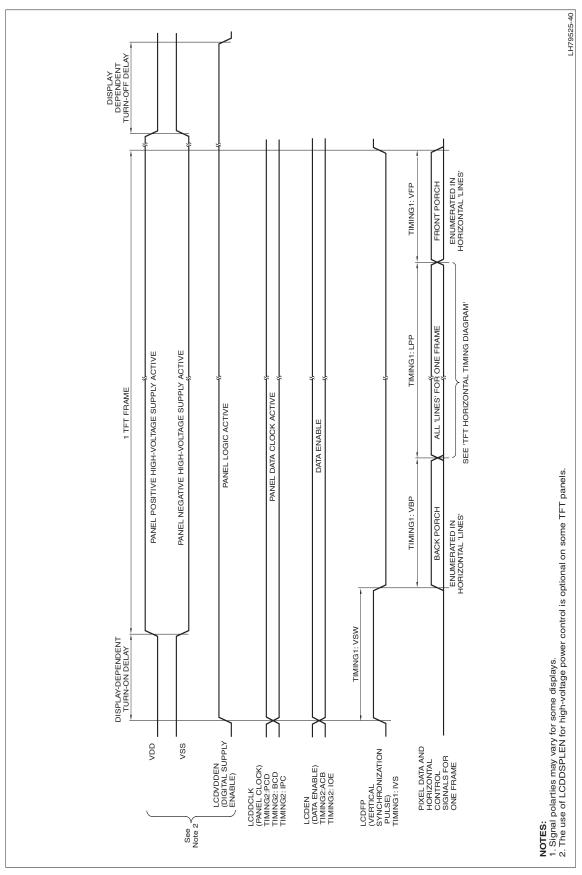

| 4.3.8.2 LCD Vertical Timing Signals                        |                 |

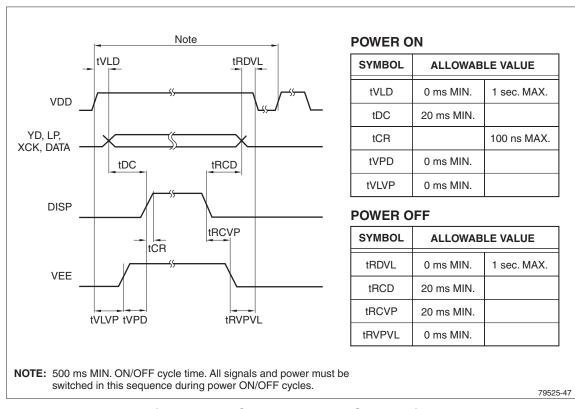

| 4.3.9 LCD Power Sequencing at Turn-On and Turn-Off         |                 |

| 4.3.9.1 Minimizing a Retained Image on the LCD             |                 |

| 4.3.10 Interrupts                                          |                 |

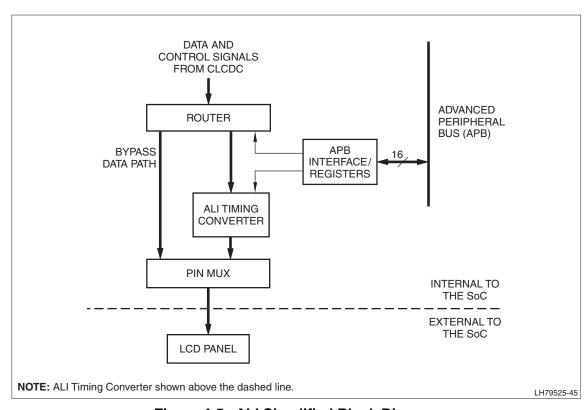

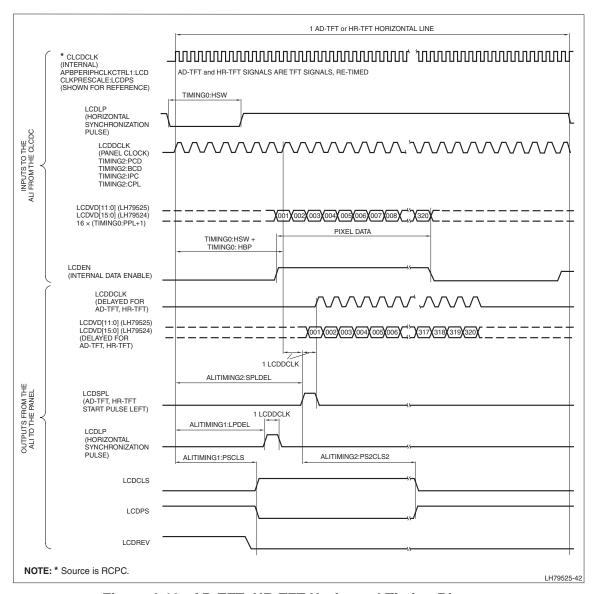

| 4.4 Advanced LCD Interface                                 |                 |

| 4.4.1 ALI Theory of Operation                              |                 |

| 4.4.2 ALI Operating Modes                                  |                 |

| 4.4.2.1 Bypass Mode                                        |                 |

| 4.4.2.2 Active Mode                                        |                 |

| 4.5 CLCDC Register Reference                               |                 |

| 4.5.1 Enabling the CLCDC                                   |                 |

| 4.5.2 CLCDC Memory Map                                     |                 |

| 4.5.3 CLCDC Register Descriptions                          |                 |

| 4.5.3.1 Horizontal Timing Panel Control Register (TIMING0) |                 |

| 4.5.3.2 Vertical Timing Panel Control Register (TIMING1)   |                 |

|                                                            | 1 <del>44</del> |

| 4.5.3.3 Clock and Signal Polarity Control Register (TIMING2)    | 4-24 |

|-----------------------------------------------------------------|------|

| 4.5.3.4 Upper Panel Frame Buffer Base Address Register (UPBASE) | 4-26 |

| 4.5.3.5 Lower Panel Frame Buffer Base Address Register (LPBASE) | 4-27 |

| 4.5.3.6 Interrupt Enable Register (INTREN)                      | 4-28 |

| 4.5.3.7 CLCDC Control Register (CTRL)                           | 4-29 |

| 4.5.3.8 Raw Interrupt Status Register (STATUS)                  |      |

| 4.5.3.9 Masked Interrupt Status Register (INTERRUPT)            |      |

| 4.5.3.10 Interrupt Clear Register (INTCLR)                      |      |

| 4.5.3.11 LCD Upper Panel and Lower Panel Frame Buffer Current   |      |

| Address Register (UPCURR and LPCURR)                            | 4-35 |

| 4.5.3.12 256 × 16-bit Color Palette Register (PALETTE)          |      |

| 4.5.4 ALI Register Reference                                    |      |

| 4.5.5 ALI Memory Map                                            |      |

| 4.5.6 ALI Register Descriptions                                 |      |

| 4.5.6.1 Setup Register (ALISETUP)                               |      |

| 4.5.6.2 Control Register (ALICTRL)                              |      |

| 4.5.6.3 Timing Delay Register 1 (ALITIMING1)                    |      |

| 4.5.6.4 Timing Delay Register 2 (ALITIMING2)                    |      |

| 4.6 Timing Waveforms                                            |      |

| 4.6.1 STN Horizontal Timing                                     |      |

| 4.6.2 STN Vertical Timing                                       |      |

| 4.6.3 TFT Horizontal Timing                                     |      |

| 4.6.4 TFT Vertical Timing                                       |      |

| 4.6.5 AD-TFT/HR-TFT Horizontal Timing Waveforms                 |      |

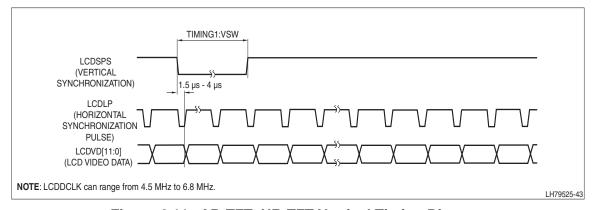

| 4.6.6 AD-TFT/HR-TFT Vertical Timing Waveforms                   |      |

| Chapter 5 – Direct Memory Access Controller                     |      |

| 5.1 Theory Of Operation                                         | 5-2  |

| 5.1.1 Use for SSP and UART                                      |      |

| 5.1.2 Changing Mode from Memory to Peripheral                   |      |

| 5.1.3 Interrupt, Error, and Status Registers                    |      |

| 5.1.3.1 Interrupts                                              |      |

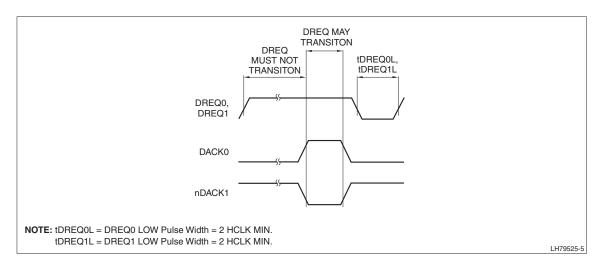

| 5.1.4 External DMA Handshake Signal Timing                      |      |

| 5.2 Register Reference                                          |      |

| 5.2.1 Memory Map                                                |      |

| 5.2.2 Register Definitions                                      |      |

| 5.2.2.1 Source Base Registers (SOURCELO and SOURCEHI)           |      |

| 5.2.2.2 Destination Base Registers (DESTLO and DESTHI)          |      |

| 5.2.2.3 Maximum Count Register (MAX)                            |      |

| 5.2.2.4 Control Register (CTRL)                                 |      |

| 5.2.2.5 Current Source Registers (CURSHI and CURSLO)            |      |

| 5.2.2.6 Current Destination Registers (CURDHI and CURDLO)       |      |

| 5.2.2.7 Terminal Count Register (TCNT)                          |      |

| 5.2.2.8 Interrupt Mask Register (MASK)                          |      |

| 5.2.2.9 Interrupt Clear Register (CLR)                          |      |

| 5.2.2.10 Status Register (STATUS)                               |      |

| 3.2.2. 10 Status Hegister (STATOS)                              | 5-17 |

| Chapter 6 – Ethernet MAC Controller                           |      |

|---------------------------------------------------------------|------|

| 6.1 Theory of Operation                                       |      |

| 6.1.1 Operational Overview                                    | 6-3  |

| 6.1.1.1 Setup                                                 | 6-4  |

| 6.1.1.2 Statistics                                            | 6-4  |

| 6.1.1.3 Detailed Descriptions                                 | 6-4  |

| 6.1.2 Memory Interface                                        | 6-4  |

| 6.1.2.1 FIFO                                                  | 6-4  |

| 6.1.2.2 Receive Buffers                                       | 6-4  |

| 6.1.2.3 Transmit Buffer                                       | 6-7  |

| 6.1.3 Receive Block                                           | 6-9  |

| 6.1.4 Transmit Block                                          | 6-9  |

| 6.1.4.1 Pause Frame Support                                   | 6-10 |

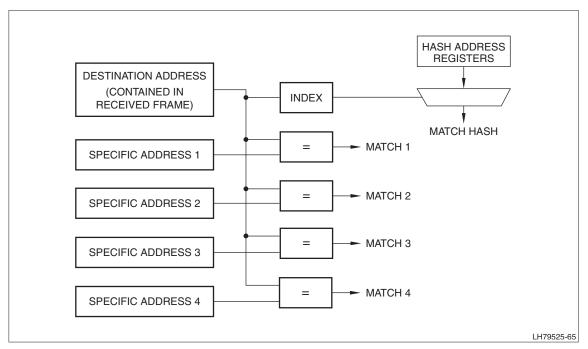

| 6.1.5 Address Checking Block                                  | 6-11 |

| 6.1.5.1 Broadcast Address                                     | 6-12 |

| 6.1.5.2 Hash Addressing                                       | 6-12 |

| 6.1.5.3 Copy All Frames (Promiscuous Mode)                    | 6-12 |

| 6.1.5.4 Type ID Checking                                      | 6-13 |

| 6.1.5.5 VLAN Support                                          | 6-13 |

| 6.2 Programming Model                                         | 6-13 |

| 6.2.1 Initialization                                          | 6-14 |

| 6.2.1.1 Receive Buffer List                                   | 6-14 |

| 6.2.1.2 Transmit Buffer List                                  | 6-16 |

| 6.2.1.3 Transmitting Frames                                   | 6-16 |

| 6.2.1.4 Local Loop Back Mode                                  | 6-16 |

| 6.2.1.5 PHY Maintenance                                       | 6-17 |

| 6.2.1.6 Interrupts                                            | 6-17 |

| 6.3 Register Reference                                        |      |

| 6.3.1 Memory Map                                              | 6-18 |

| 6.3.2 Control, Configuration, And Status Register Definitions | 6-20 |

| 6.3.2.1 Network Control Register (NETCTL)                     |      |

| 6.3.2.2 Network Configuration Register (NETCONFIG)            |      |

| 6.3.2.3 Network Status Register (NETSTATUS)                   |      |

| 6.3.2.4 Transmit Status Register (TXSTATUS)                   | 6-25 |

| 6.3.2.5 Receive Buffer Queue Pointer (RXBQP)                  | 6-27 |

| 6.3.2.6 Transmit Buffer Queue Pointer (TXBQP)                 |      |

| 6.3.2.7 Receive Status Register (RXSTATUS)                    |      |

| 6.3.2.8 Interrupt Status Register (INSTATUS)                  |      |

| 6.3.2.9 Interrupt Enable Register (ENABLE)                    |      |

| 6.3.2.10 Interrupt Disable Register (DISABLE)                 |      |

| 6.3.2.11 Interrupt Mask Register (MASK)                       |      |

| 6.3.2.12 PHY Maintenance Register (PHYMAINT)                  | 6-35 |

| 6.3.2.13 Pause Time Register (PAUSETIME)                      |      |

| 6.3.2.14 Transmit Pause Quantum (TXPAUSEQUAN)                 |      |

| 6.3.3 Statistics Register Definitions                         |      |

| 6.3.3.1 Pause Frames Received (PAUSEFRRX)                     |      |

| 6.3.3.2 Frames Transmitted OK (FRMTXOK)                       | 6-38 |

| 6.3.3.3 Single Collision Frames (SINGLECOL)       | 6-38   |

|---------------------------------------------------|--------|

| 6.3.3.4 Multiple Collision Frames (MULTFRM)       | . 6-39 |

| 6.3.3.5 Frames Received OK (FRMRXOK)              | . 6-39 |

| 6.3.3.6 Frame Check Sequence Errors (FRCHK)       | . 6-40 |

| 6.3.3.7 Alignment Errors (ALIGNERR)               |        |

| 6.3.3.8 Deferred Transmission Frames (DEFTXFRM)   |        |

| 6.3.3.9 Late Collisions (LATECOL)                 |        |

| 6.3.3.10 Excessive Collisions (EXCOL)             |        |

| 6.3.3.11 Transmit Underrun Errors (TXUNDER)       |        |

| 6.3.3.12 Carrier Sense Errors (SENSERR)           |        |

| 6.3.3.13 Receive Resource Errors (RXRERR)         |        |

| 6.3.3.14 Receive Overrun Errors (RXOVERR)         |        |

| 6.3.3.15 Receive Symbol Errors (RXSYMERR)         |        |

| 6.3.3.16 Excessive Length Error Register (LENERR) |        |

| 6.3.3.17 Receive Jabbers (RXJAB)                  |        |

| 6.3.3.18 Undersize Frames (UNDERFRM)              |        |

| 6.3.3.19 SQE Test Errors (SQERR)                  |        |

| 6.3.3.20 Received Length Field Mismatch (RXLEN)   |        |

| 6.3.3.21 Transmitted Pause Frames (TXPAUSEFM)     |        |

| 6.3.4 Matching Registers                          |        |

| 6.3.4.1 Hash Register Bottom (HASHBOT)            |        |

| 6.3.4.2 Hash Register Top (HASHTOP)               |        |

| 6.3.4.3 Specific Address 1 Bottom (SPECAD1BOT)    |        |

| 6.3.4.4 Specific Address 1 Top (SPECAD1TOP)       |        |

| 6.3.4.5 Specific Address 2 Bottom (SPECAD2BOT)    |        |

| 6.3.4.6 Specific Address 2 Top (SPECAD2TOP)       |        |

| 6.3.4.7 Specific Address 3 Bottom (SPECAD3BOT)    |        |

| 6.3.4.8 Specific Address 3 Top (SPECAD3TOP)       |        |

| 6.3.4.9 Specific Address 4 Bottom (SPECAD4BOT)    |        |

| 6.3.4.10 Specific Address 4 Top (SPECAD4TOP)      |        |

| 6.3.4.11 Type ID Checking (IDCHK)                 |        |

|                                                   |        |

| Chapter 7 – External Memory Controller            |        |

| 7.1 Theory of Operation                           |        |

| 7.1.1 External Memory Map                         |        |

| 7.1.1.1 nCS1 Memory Configuration                 |        |

| 7.2 Static Memory                                 |        |

| 7.2.1 Static Memory Operation                     |        |

| 7.2.2 Hardware Design                             |        |

| 7.2.2.1 Address Connectivity                      |        |

| 7.2.3 Software Design                             |        |

| 7.2.3.1 Simple Shifting Subroutine                |        |

| 7.2.4 Static Memory Device Selection              |        |

| 7.2.4.1 Static Memory Timing Control              |        |

| 7.2.4.2 Bus Turnaround                            |        |

| 7.2.4.3 Byte Lane Control                         |        |

| 7.2.4.4 Write Protection                          |        |

| 7.2.4.5 nWAIT Transfers                           | 7-16   |

νi

| 7.2.4.6 Extended Wait Transfers                                    | 7-17  |

|--------------------------------------------------------------------|-------|

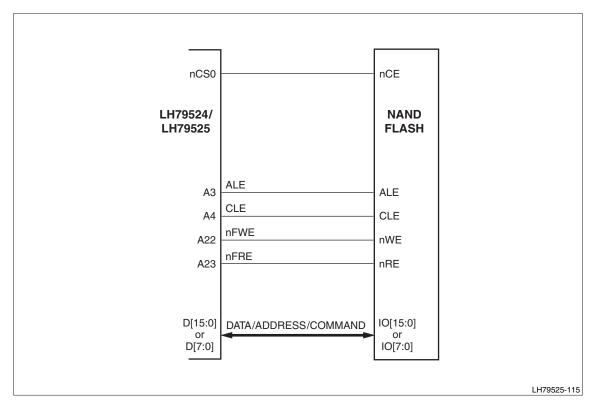

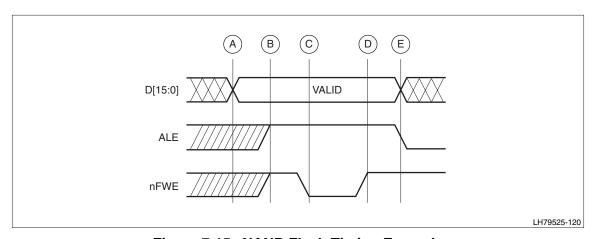

| 7.3 Interfacing with NAND Flash                                    | 7-17  |

| 7.3.1 Booting Example                                              | 7-17  |

| 7.3.2 General NAND Flash Access                                    | 7-20  |

| 7.3.2.1 Transaction Example                                        | 7-20  |

| 7.3.2.2 16-bit Example Transaction                                 |       |

| 7.3.2.3 Address Examples                                           |       |

| 7.4 Dynamic Memory                                                 |       |

| 7.4.1 Write-protection                                             |       |

| 7.4.2 Access Sequencing and Memory Width                           |       |

| 7.4.3 Bus Address Mapping                                          |       |

| 7.4.4 Data Mask Signals                                            |       |

| 7.5 Register Reference                                             |       |

| 7.5.1 Memory Map                                                   |       |

| 7.5.2 Register Definitions                                         |       |

| 7.5.2.1 Control Register (CONTROL)                                 |       |

| 7.5.2.2 Status Register (STATUS)                                   |       |

| 7.5.2.3 Configuration Register (CONFIG)                            |       |

| 7.5.2.4 Dynamic Memory Control Register (DYNMCTRL)                 |       |

| 7.5.2.5 Dynamic Refresh Register (DYNMREF)                         |       |

| 7.5.2.6 Dynamic Memory Read Configuration Register (DYNMRCON)      |       |

| 7.5.2.7 Dynamic Precharge Command Period Register (PRECHARGE).     |       |

| 7.5.2.8 Dynamic Memory Active to Precharge Command Period          | 7 -00 |

| Register (DYNM2PRE)                                                | 7-37  |

| 7.5.2.9 Dynamic Memory Self-Refresh Exit Time Register (REFEXIT)   |       |

| 7.5.2.10 Dynamic Memory Last Data Out to Active Time               | 7 00  |

| Register (DOACTIVE)                                                | 7-30  |

| 7.5.2.11 Dynamic Memory Data-In to Active Time Register (DIACTIVE) |       |

| 7.5.2.12 Dynamic Memory Write Recovery Time Register (DWRT)        |       |

| 7.5.2.13 Dynamic Memory Active to Active Command                   | / 국1  |

| Period Register (DYNACTCMD)                                        | 7-42  |

| 7.5.2.14 Dynamic Memory Auto-Refresh Period, and Auto-Refresh      | / 42  |

| to Active Command Period Register (DYNAUTO)                        | 7-43  |

| 7.5.2.15 Dynamic Memory Exit Self-Refresh to Active Command        | / 40  |

| Time Register (DYNREFEXIT)                                         | 7-44  |

| 7.5.2.16 Dynamic Memory Active Bank A to Active Bank B             | /     |

| Time Register (DYNACTIVEAB)                                        | 7-45  |

| 7.5.2.17 Dynamic Memory Load Mode Register to                      | 7 40  |

| Active Command Time Register (DYNAMICTMRD)                         | 7-46  |

| 7.5.2.18 Static Memory Extended Wait Register (WAIT)               |       |

| 7.5.2.19 Dynamic Configuration Register for nDCS0                  | / 4/  |

| and nDCS1 (DYNCFGx)                                                | 7-48  |

| 7.5.2.20 Dynamic Memory RAS and CAS Delay Register for             | , +0  |

| nDCS0 and nDCS1 (DYNRASCASx)                                       | 7-51  |

| 7.5.2.21 Static Memory Configuration Register (SCONFIGx)           |       |

| 7.5.2.22 Static Memory Write Enable Delay Registers (SWAITWENx)    |       |

| 7.5.2.22 Static Memory Output Fnable Delay Registers (SWAITWEINX)  |       |

|                                                                    |       |

| 7.5.2.24 Static Memory Read Delay Registers (SWAITRDx)         | 7-56  |

|----------------------------------------------------------------|-------|

| 7.5.2.25 Static Memory Page Mode Read Delay Registers          |       |

| (SWAITPAGEx)                                                   | 7-57  |

| 7.5.2.26 Static Memory Write Delay Registers (SWAITWRx)        | 7-58  |

| 7.5.2.27 Static Memory Turn Around Delay Registers (STURNx)    |       |

| Chapter 8 – General Purpose Input/Output                       |       |

| 8.1 Theory of Operation                                        | 8-1   |

| 8.1.1 Port Configuration                                       |       |

| 8.1.1.1 Multiplexing                                           |       |

| 8.2 Register Reference                                         |       |

| 8.2.1 Memory Map                                               |       |

| 8.2.2 Register Descriptions                                    |       |

| 8.2.2.1 Port A/C/E/G/I/K/M Data Registers (P1DRx)              |       |

| 8.2.2.2 Port B/D/F/H/J/L/N Data Register (P2DRx)               |       |

| 8.2.2.3 Port A/C/E/G/I/K Data Direction Register (P1DDRx)      |       |

| 8.2.2.4 Port B/D/F/H/L/N Data Direction Register               |       |

| _                                                              |       |

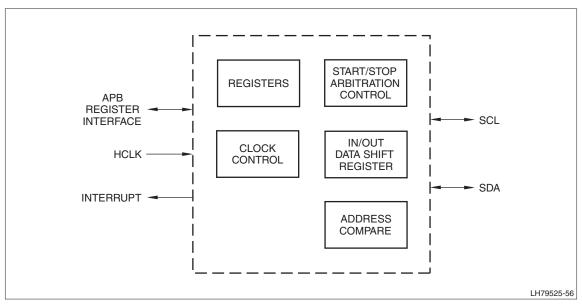

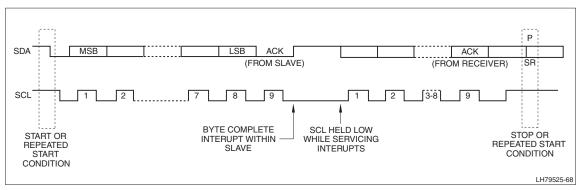

| Chapter 9 – I <sup>2</sup> C Module 9.1 Theory of Operation    | 0-2   |

| 9.1.1 Setting I <sup>2</sup> C Clock Timing                    |       |

| 9.1.1 Setting 1 C clock Timing                                 |       |

| 9.1.3 Slave Mode                                               |       |

| 9.1.4 Master Mode                                              |       |

| 9.1.5 Resetting a Locked Slave                                 |       |

| 9.2 Register Reference                                         |       |

| 9.2.1 Memory Map                                               |       |

| 9.2.2 Register Definitions                                     |       |

| 9.2.2.1 I <sup>2</sup> C Configuration Register (ICCON)        |       |

| 9.2.2.2 I <sup>2</sup> C Slave Address Register (ICSAR)        |       |

| 9.2.2.3 I <sup>2</sup> C Upper Slave Address Register (ICUSAR) |       |

| 9.2.2.4 I <sup>2</sup> C Data Register (ICDATA)                |       |

| 9.2.2.5 I <sup>2</sup> C Clock High Time Register (ICHCNT)     |       |

| 9.2.2.6 I <sup>2</sup> C Clock Low Time Register (ICLCNT)      |       |

| 9.2.2.7 I <sup>2</sup> C Status Register (ICSTAT)              |       |

|                                                                |       |

| Chapter 10 – I <sup>2</sup> S Converter                        | 10.0  |

| 10.1 Theory of Operation                                       |       |

| 10.1.1 Conversion                                              |       |

| 10.1.2 Driving/Latching Edges                                  |       |

| 10.1.3 Transmission                                            |       |

| 10.1.3.1 Master Mode Transmission                              |       |

| 10.1.3.2 Slave Mode Transmission                               |       |

| 10.1.4 Reception                                               |       |

| 10.1.4.1 Master Mode Reception                                 |       |

| 10.1.4.2 Slave Mode Reception                                  |       |

| 10.1.5 Suppression of SSPFSSIN                                 |       |

| 10.1.6 Channel Management                                      |       |

| 10.1.7 Interrupts                                              | 10-11 |

| 10.1.7.1 SSP Protocol Error Interrupt                            | 10-11 |

|------------------------------------------------------------------|-------|

| 10.1.7.2 External Codec Protocol Error Interrupt                 | 10-11 |

| 10.1.7.3 Transmit FIFO Underrun Interrupt                        | 10-11 |

| 10.1.7.4 Receive Interrupt                                       | 10-12 |

| 10.1.7.5 Transmit Interrupt                                      | 10-12 |

| 10.1.7.6 Receive Overrun Interrupt                               | 10-12 |

| 10.1.7.7 Receive Timeout Interrupt                               | 10-12 |

| 10.1.7.8 I <sup>2</sup> SINTR                                    |       |

| 10.2 Register Reference                                          |       |

| 10.2.1 Memory Map                                                |       |

| 10.2.2 Register Descriptions                                     |       |

| 10.2.2.1 Control Register (CTRL)                                 |       |

| 10.2.2.2 Status Register (STAT)                                  |       |

| 10.2.2.3 Interrupt Mask Set or Clear Register (IMSC)             |       |

| 10.2.2.4 Raw Interrupt Status Register (RIS)                     |       |

| 10.2.2.5 Masked Interrupt Status Register (MIS)                  |       |

| 10.2.2.6 Interrupt Clear Register (ICR)                          |       |

| . ,                                                              | 10 =0 |

| Chapter 11 – I/O Configuration                                   |       |

| 11.1 Theory of Operation                                         |       |

| 11.2 Register Reference                                          |       |

| 11.2.1 Memory Map                                                |       |

| 11.2.2 Register Definitions                                      |       |

| 11.2.2.1 Multiplexing Control 1 Register (MUXCTL1)               |       |

| 11.2.2.2 Resistor Configuration Control 1 Register (RESCTL1)     |       |

| 11.2.2.3 Multiplexing Control 3 Register (MUXCTL3)               |       |

| 11.2.2.4 Resistor Configuration Control 3 Register (RESCTL3)     |       |

| 11.2.2.5 Multiplexing Control 4 Register (MUXCTL4)               |       |

| 11.2.2.6 Resistor Configuration Control 4 Register (RESCTL4)     |       |

| 11.2.2.7 Multiplexing Control 5 Register (MUXCTL5)               |       |

| 11.2.2.8 Resistor Configuration Control 5 Register (RESCTL5)     |       |

| 11.2.2.9 Multiplexing Control 6 Register (MUXCTL6)               |       |

| 11.2.2.10 Resistor Configuration Control 6 Register (RESCTL6)    |       |

| 11.2.2.11 Multiplexing Control 7 Register (MUXCTL7)              |       |

| 11.2.2.12 Resistor Configuration Control 7 Register (RESCTL7)    |       |

| 11.2.2.13 Multiplexing Control 10 Register (MUXCTL10)            |       |

| 11.2.2.14 Resistor Configuration Control 10 Register (RESCTL10)  |       |

| 11.2.2.15 Multiplexing Control 11 Register (MUXCTL11)            |       |

| 11.2.2.16 Resistor Configuration Control 11 Register (RESCTL11)  |       |

| 11.2.2.17 Multiplexing Control 12 Register (MUXCTL12)            | 11-26 |

| 11.2.2.18 Resistor Configuration Control 12 Register (RESCTL12)  |       |

| 11.2.2.19 Resistor Configuration Control 13 Register (RESCTL13)  | 11-29 |

| 11.2.2.20 Multiplexing Control 14 Register (MUXCTL14)            | 11-30 |

| 11.2.2.21 Multiplexing Control 15 Register (MUXCTL15)            | 11-32 |

| 11.2.2.22 Resistor Configuration Control 15 Register (RESCTL15)  | 11-32 |

| 11.2.2.23 Resistor Configuration Control 17 Register (RESCTL17)  | 11-33 |

| 11.2.2.24 Multiplexing Control 19 Register (MUXCTL19)            | 11-34 |

| 11 2 2 25 Resistor Configuration Control 10 Register (RESCTI 10) | 11-36 |

| 11.2.2.26 Multiplexing Control 20 Register (MUXCTL20)           | 11-38 |

|-----------------------------------------------------------------|-------|

| 11.2.2.27 Resistor Configuration Control 20 Register (RESCTL20) | 11-40 |

| 11.2.2.28 Multiplexing Control 21 Register (MUXCTL21)           | 11-42 |

| 11.2.2.29 Resistor Configuration Control 21 Register (RESCTL21) | 11-43 |

| 11.2.2.30 Multiplexing Control 22 Register (MUXCTL22)           |       |

| 11.2.2.31 Resistor Configuration Control 22 Register (RESCTL22) | 11-46 |

| 11.2.2.32 Multiplexing Control 23 Register (MUXCTL23)           |       |

| 11.2.2.33 Resistor Configuration Control 23 Register (RESCTL23) | 11-50 |

| 11.2.2.34 Multiplexing Control 24 Register (MUXCTL24)           | 11-52 |

| 11.2.2.35 Resistor Configuration Control 24 Register (RESCTL24) | 11-53 |

| 11.2.2.36 Multiplexing Control 25 Register (MUXCTL25)           |       |

| Chapter 12 – Real Time Clock                                    |       |

| 12.1 Theory of Operation                                        | 12-1  |

| 12.1.1 Configuring the RTC for Use                              |       |

| 12.2 Register Reference                                         |       |

| •                                                               |       |

| 12.2.1 Memory Map                                               |       |

| · ·                                                             |       |

| 12.2.2.1 Data Register (DR)                                     |       |

| 12.2.2.2 Match Register (MR)                                    |       |

| 12.2.2.3 Load Register (LR)                                     |       |

| 12.2.2.4 Control Register (CR)                                  |       |

| 12.2.2.5 Interrupt Mask Set or Clear Register (IMSC)            |       |

| 12.2.2.6 Raw Interrupt Status Register (RIS)                    |       |

| 12.2.2.7 Masked Interrupt Status Register (MIS)                 |       |

| 12.2.2.8 Interrupt Clear Register (ICR)                         | 12-1  |

| Chapter 13 – Reset, Clock, and Power Controller                 |       |

| 13.1 Theory of Operation                                        |       |

| 13.1.1 System PLL and USB PLL Reset                             |       |

| 13.1.2 Reset Generation                                         |       |

| 13.1.3 Clock Generation                                         |       |

| 13.1.3.1 Enabling Clocks Prior to Programming Registers         |       |

| 13.1.3.2 Peripheral Block Clocks                                |       |

| 13.1.3.3 External Clock Generation (CLKOUT)                     |       |

| 13.1.4 Power Modes                                              |       |

| 13.1.4.1 Active Mode                                            |       |

| 13.1.4.2 Standby Mode                                           | 13-6  |

| 13.1.4.3 Sleep Mode                                             | 13-6  |

| 13.1.4.4 Stop1 Mode                                             | 13-6  |

| 13.1.4.5 Stop2 Mode                                             | 13-7  |

| 13.1.4.6 Power Control in JTAG Mode                             | 13-7  |

| 13.2 Register Reference                                         | 13-8  |

| 13.2.1 Memory Map                                               | 13-8  |

| 13.2.2 Register Descriptions                                    | 13-8  |

| 13.2.2.1 Control Register (CTRL)                                | 13-9  |

| 13.2.2.2 Identification Register (CHIPID)                       | 13-10 |

| 13.2.2.3 Reman Control Register (REMAP)                         | 13-11 |

| 13.2.2.4 Software Reset Register (SOFTRESET)                    | 13-14 |

|-----------------------------------------------------------------|-------|

| 13.2.2.5 Reset Status Register (RSTSTATUS)                      | 13-15 |

| 13.2.2.6 Reset Status Clear Register (RSTSTATUSCLR)             | 13-16 |

| 13.2.2.7 System Clock Prescaler Register (SYSCLKPRE)            | 13-17 |

| 13.2.2.8 CPU Clock Prescaler Register (CPUCLKPRE)               | 13-18 |

| 13.2.2.9 Peripheral Clock Control Register 0 (PCLKCTRL0)        | 13-19 |

| 13.2.2.10 Peripheral Clock Control Register 1 (PCLKCTRL1)       | 13-20 |

| 13.2.2.11 AHB Clock Control Register (AHBCLKCTRL)               | 13-21 |

| 13.2.2.12 Peripheral Clock Select Register 0 (PCLKSEL0)         |       |

| 13.2.2.13 Peripheral Clock Select Register 1 (PCLKSEL1)         |       |

| 13.2.2.14 Silicon Revision Register (SILICONREV)                |       |

| 13.2.2.15 LCD Clock Prescaler Register (LCDPRE)                 |       |

| 13.2.2.16 SSP Clock Prescaler Register (SSPPRE)                 |       |

| 13.2.2.17 ADC Clock Prescaler Register (ADCPRE)                 |       |

| 13.2.2.18 USB Clock Prescaler Register (USBPRE)                 |       |

| 13.2.2.19 External Interrupt Configuration Register (INTCONFIG) |       |

| 13.2.2.20 External Interrupt Clear Register (INTCLR)            |       |

| 13.2.2.21 Core Clock Configuration Register (CORECONFIG)        |       |

| 13.2.2.22 System PLL Control Register (SYSPLLCTL)               |       |

| 13.2.2.23 USB PLL Control Register (USBPLLCTL)                  |       |

| •                                                               |       |

| Chapter 14 – Synchronous Serial Port                            |       |

| 14.1 Theory of Operation                                        |       |

| 14.1.1 Timing Waveforms                                         |       |

| 14.1.2 Motorola SPI Frame Format                                |       |

| 14.1.3 Texas Instruments Frame Format                           |       |

| 14.1.4 National Semiconductor Frame Format                      |       |

| 14.1.5 Clock Generation                                         |       |

| 14.1.6 Interrupts                                               |       |

| 14.1.6.1 Receive Interrupt                                      |       |

| 14.1.6.2 Transmit Interrupt                                     |       |

| 14.1.6.3 Receive Overrun Interrupt                              |       |

| 14.1.6.4 Receive Timeout Interrupt                              |       |

| 14.1.6.5 SSPINTR                                                |       |

| 14.2 Register Reference                                         |       |

| 14.2.1 Memory Map                                               |       |

| 14.2.2 Register Descriptions                                    |       |

| 14.2.2.1 Control Register 0 (CTRL0)                             |       |

| 14.2.2.2 Control Register 1 (CTRL1)                             |       |

| 14.2.2.3 Data Register – Receive/Transmit FIFO Register (DR)    |       |

| 14.2.2.4 Status Register (SR)                                   |       |

| 14.2.2.5 Clock Prescale Register (CPSR)                         |       |

| 14.2.2.6 Interrupt Mask Set and Clear Register (IMSC)           |       |

| 14.2.2.7 Raw Interrupt Status Register (RIS)                    |       |

| 14.2.2.8 Masked Interrupt Status Register (MIS)                 |       |

| 14.2.2.9 Interrupt Clear Register (ICR)                         |       |

| 14.2.2.10 DMA Control Register (DCR)                            | 14-20 |

| Chapter 15 – Timers                                            |      |

|----------------------------------------------------------------|------|

| 15.1 Theory of Operation                                       | 15-2 |

| 15.1.1 Counter Clear Upon Compare Match                        | 15-3 |

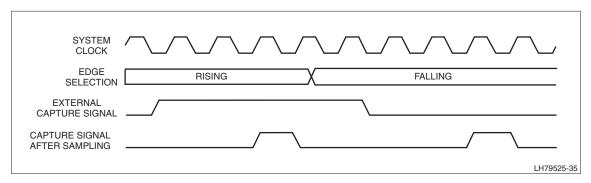

| 15.1.2 Capture Signal Sampling                                 | 15-4 |

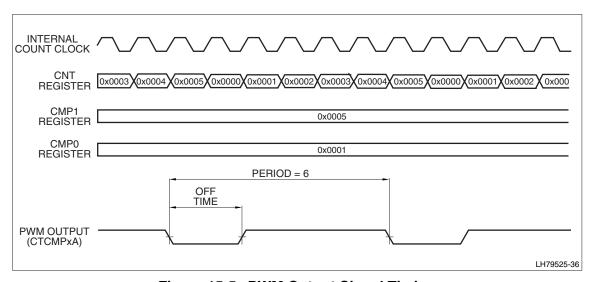

| 15.1.3 PWM Mode                                                | 15-4 |

| 15.1.3.1 Timer Interrupts                                      | 15-5 |

| 15.2 Register Reference                                        | 15-6 |

| 15.2.1 Memory Map                                              |      |

| 15.2.2 Register Descriptions                                   |      |

| 15.2.2.1 Timer 0 Control Register (CTRL0)                      |      |

| 15.2.2.2 Timer 0 Compare/Capture Control Register (CMP_CAP_CTR |      |

| 15.2.2.3 Timer 0 Interrupt Control Register (INTEN0)           | -    |

| 15.2.2.4 Timer 0 Status Register (STATUS0)                     |      |

| 15.2.2.5 Timer 0 Counter Register (CNT0)                       |      |

| 15.2.2.6 Timer 0 Compare Registers (T0CMPn)                    |      |

| 15.2.2.7 Timer 0 Capture Registers (CAPn)                      |      |

| 15.2.2.8 Timer 1 Control Register (CTRL1)                      |      |

| 15.2.2.9 Timer 1 Interrupt Control Register (INTEN1)           |      |

| 15.2.2.10 Timer 1 Status Register (STATUS1)                    |      |

| 15.2.2.11 Timer 1 Counter Register (CNT1)                      |      |

| 15.2.2.12 Timer 1 Compare Registers (T1CMPn)                   |      |

| 15.2.2.13 Timer 1 Capture Registers (T1CAPn)                   |      |

| 15.2.2.14 Timer 2 Control Register (CTRL2)                     |      |

| 15.2.2.15 Timer 2 Interrupt Control Register (INTEN2)          |      |

| 15.2.2.16 Timer 2 Status Register (STATUS2)                    |      |

| 15.2.2.17 Timer 2 Counter Register (CNT2)                      |      |

| 15.2.2.18 Timer 2 Compare Registers (T2CMPn)                   |      |

| 15.2.2.19 Timer 2 Capture Registers (T2CAPn)                   |      |

|                                                                |      |

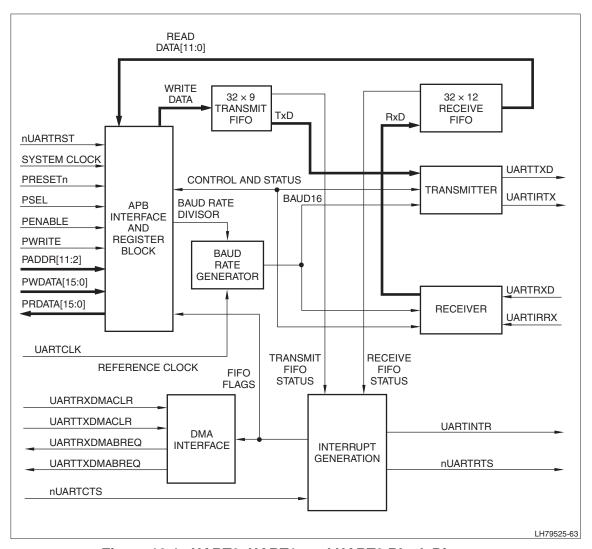

| Chapter 16 – UARTs                                             | 40.0 |

| 16.1 Theory of Operation                                       |      |

| 16.1.1 Transmitting Data                                       |      |

| 16.1.2 Receive Data Frame                                      |      |

| 16.1.3 Nine-bit Mode                                           |      |

| 16.1.4 Status Conditions                                       |      |

| 16.1.5 On-Chip DMA Capabilities                                |      |

| 16.1.6 Programming the SIR                                     |      |

| 16.1.7 Hardware Flow Control                                   |      |

| 16.1.7.1 RTS Flow Control                                      |      |

| 16.1.7.2 CTS Flow Control                                      |      |

| 16.1.8 Programming Control Registers                           |      |

| 16.2 Interrupts                                                |      |

| 16.2.1 UARTINTR                                                |      |

| 16.3 Register Reference                                        |      |

| 16.3.1 Memory Map                                              |      |

| 16.3.2 Register Definitions                                    |      |

| 16.3.2.1 Data Register (UARTDR)                                |      |

| 16.3.2.2 Receive Status/Error Clear Register (UARTRSR/UARTECR) | 16-9 |

| 16.3.2.3 Flag Register (UARTFR)                                   | 16-11       |

|-------------------------------------------------------------------|-------------|

| 16.3.2.4 IrDA Low-Power Counter Register (UARTILPR)               | 16-12       |

| 16.3.2.5 Integer Baud Rate Divisor Register (UARTIBRD)            | 16-13       |

| 16.3.2.6 Fractional Baud Rate Divisor Register (UARTFBRD)         |             |

| 16.3.2.7 Line Control Register (UARTLCR_H)                        |             |

| 16.3.2.8 UART Control Register (UARTCR)                           |             |

| 16.3.2.9 Interrupt FIFO Level Select Register (UARTIFLS)          |             |

| 16.3.2.10 Interrupt Mask Set/Clear Register (UARTIMSC)            |             |

| 16.3.2.11 Raw Interrupt Status Register (UARTRIS)                 |             |

| 16.3.2.12 Masked Interrupt Status Register (UARTMIS)              |             |

| 16.3.2.13 Interrupt Clear Register (UARTICR)                      |             |

| 16.3.2.14 UARTO DMA Control Register (DMACTRL)                    |             |

| Chapter 17 – Universal Serial Bus Device                          |             |

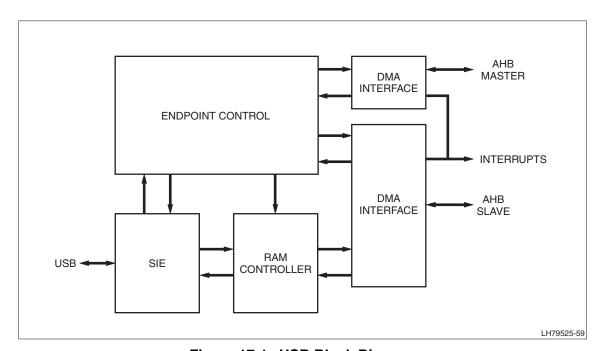

| 17.1 Theory of Operation                                          | 17-1        |

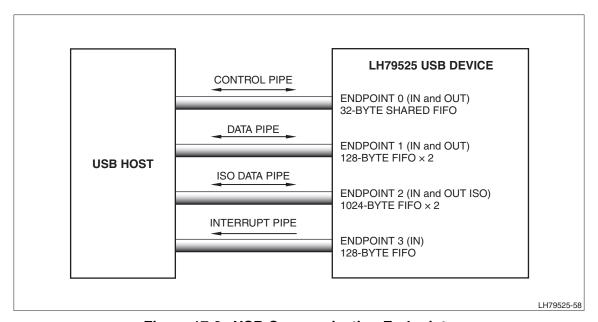

| 17.1.1 Endpoints                                                  |             |

| 17.1.1.1 Isochronous Endpoints                                    |             |

| 17.1.2 FIFOs                                                      |             |

| 17.1.3 Serial Interface Engine (SIE)                              |             |

| 17.1.3.1 OUT_PKT_RDY Interrupt Operation for Endpoint 0           |             |

| 17.1.4 DMA Interface                                              |             |

| 17.1.4.1 DMA Modes                                                |             |

| 17.1.4.2 DMA Bus Cycles                                           |             |

| 17.1.4.3 Bus Errors                                               |             |

| 17.1.5 DMA Operation                                              |             |

| 17.1.5.1 DMA Mode 0: OUT Endpoints                                |             |

| 17.1.5.2 DMA Mode 0: IN Endpoints                                 |             |

| 17.1.5.3 DMA Mode 1: OUT Endpoints                                |             |

| 17.1.5.4 DMA Mode 1: IN Endpoints                                 |             |

| 17.1.6 Remote Wakeup                                              |             |

| 17.2 Register Reference                                           |             |

| 17.2.1 Memory Map                                                 |             |

| 17.2.2 Register Definitions                                       |             |

| 17.2.2.1 Function Address Register (FAR)                          |             |

| 17.2.2.2 Power Management Register (PMR)                          |             |

| 17.2.2.3 Interrupt Register for Endpoint 0, 1, 2, and 3 (IIR)     |             |

| 17.2.2.4 Interrupt Register for OUT Endpoint 1 and 2 (OIR)        |             |

| 17.2.2.5 Interrupt Register for common USB interrupts (UIR)       |             |

| 17.2.2.6 IN Interrupt Enable Register (IIE)                       |             |

| 17.2.2.7 OUT Interrupt Enable Register (OIE)                      |             |

| 17.2.2.8 Interrupt Enable Register (UIE)                          |             |

| 17.2.2.9 Frame Number Registers (FRAMEx)                          |             |

| 17.2.3 Indexed Registers                                          |             |

| 17.2.3.1 Index Register (INDEX)                                   |             |

| 17.2.3.1 Index Register (INDEX)                                   |             |

| 17.2.3.2 IN Maximum Packet Size Register (INMAXP)                 |             |

| 17.2.3.4 Control Status Register 1 for IN EP 1, 2, and 3 (INCSR1) |             |

| 17.2.3.4 Control Status Register 1 for IN EP 1, 2, and 3 (INCSR1) |             |

|                                                                   | 1 / - / : ) |

| 17.2.3.6 OUT Maximum Packet Size Register EP 1 and 2 (OUTMAXP)       | .17-26  |

|----------------------------------------------------------------------|---------|

| 17.2.3.7 Control Status Register 1 for OUT EP1 and EP2 (OUTSCSR1).   |         |

| 17.2.3.8 Control Status Register 2 for OUT EP1 and EP 2 (OUTCSR2)    | . 17-29 |

| 17.2.3.9 Count 0 Register (OUTCOUNT0)                                | . 17-30 |

| 17.2.3.10 Count 1 Register (OUTCOUNT1)                               |         |

| 17.2.3.11 Out Count 2 Register (OUTCOUNT2)                           |         |

| 17.2.3.12 FIFOs for Endpoints 0-3 (FIFOx)                            |         |

| 17.2.3.13 Pending DMA Interrupts Register (INTR)                     |         |

| 17.2.3.14 DMA Channel x Control Register (CNTLx)                     |         |

| 17.2.3.15 DMA Channel x AHB Memory Address Register                  |         |

| 17.2.3.16 DMA Channel x Byte Count Register (COUNTx)                 |         |

|                                                                      |         |

| Chapter 18 – Vectored Interrupt Controller  18.1 Theory of Operation | 10 1    |

| 18.1.1 VIC Interrupt Listing                                         |         |

| · · · · · · · · · · · · · · · · · · ·                                |         |

| 18.1.2 Vectored Interrupts                                           |         |

| 18.1.3 External Interrupts                                           |         |

| 18.1.4 Clearing Interrupts                                           |         |

| 18.1.5 Priority                                                      |         |

| 18.1.6 External Level-Sensitive Interrupts                           |         |

| 18.1.7 Software Guidelines                                           |         |

| 18.2 Register Reference                                              |         |

| 18.2.1 Memory Map                                                    |         |

| 18.2.2 Register Descriptions                                         |         |

| 18.2.2.1 IRQ Status Register (IRQSTATUS)                             |         |

| 18.2.2.2 FIQ Status Register (FIQSTATUS)                             |         |

| 18.2.2.3 Raw Interrupt Status Register (RAWINTR)                     |         |

| 18.2.2.4 Interrupt Select Register (INTSELECT)                       |         |

| 18.2.2.5 Interrupt Enable Register (INTENABLE)                       |         |

| 18.2.2.6 Interrupt Enable Clear Register (INTENCLEAR)                |         |

| 18.2.2.7 Software Interrupt Register (SOFTINT)                       |         |

| 18.2.2.8 Software Interrupt Clear Register (SOFTINTCLEAR)            |         |

| 18.2.2.9 Vector Address Register (VECTADDR)                          |         |

| 18.2.2.10 Default Vector Address Register (DEFVECTADDR)              |         |

| 18.2.2.11 Vector Address Registers (VECTADDRx)                       |         |

| 18.2.2.12 Vector Control Registers (VECTCTRLx)                       |         |

| 18.2.2.13 Interrupt Test Output Register (ITOP)                      | . 18-15 |

| Chapter 19 – Watchdog Timer                                          |         |

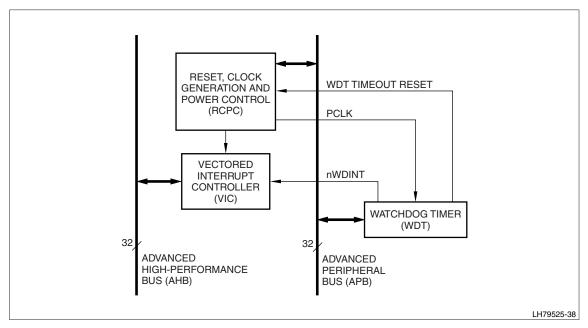

| 19.1 Theory of Operation                                             | 19-1    |

| 19.1.1 WDT Operation Details                                         | 19-3    |

| 19.2 Register Reference                                              | 19-4    |

| 19.2.1 Memory Map                                                    | 19-4    |

| 19.2.2 Register Descriptions                                         | 19-5    |

| 19.2.2.1 Control Register (CTL)                                      |         |

| 19.2.2.2 Counter Reset Register (RST)                                |         |

| 19.2.2.3 Status Register (STATUS)                                    |         |

| 19.2.2.4 Current Watchdog Count Registers (COUNT[3:0])               |         |

|                                                                      |         |

## **List of Figures**

| Preface                                                                           |          |

|-----------------------------------------------------------------------------------|----------|

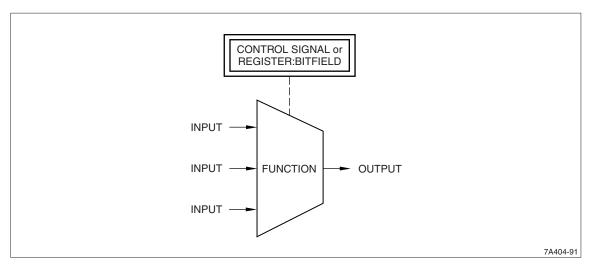

| Figure 1. Multiplexer                                                             | xxxvii   |

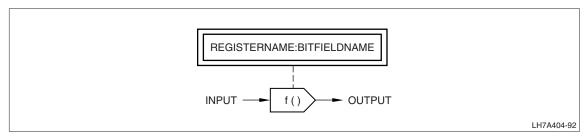

| Figure 2. Register with Bit-Field Named                                           | xxxix    |

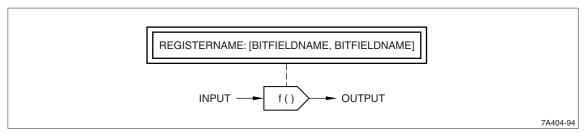

| Figure 3. Register with Multiple Bit-Fields Named                                 |          |

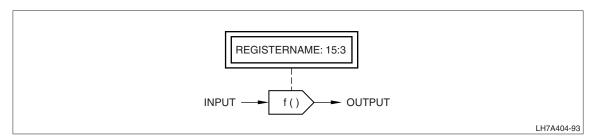

| Figure 4. Register with Bit-Field Numbered                                        | xxxix    |

| Chapter 1 – Overview                                                              |          |

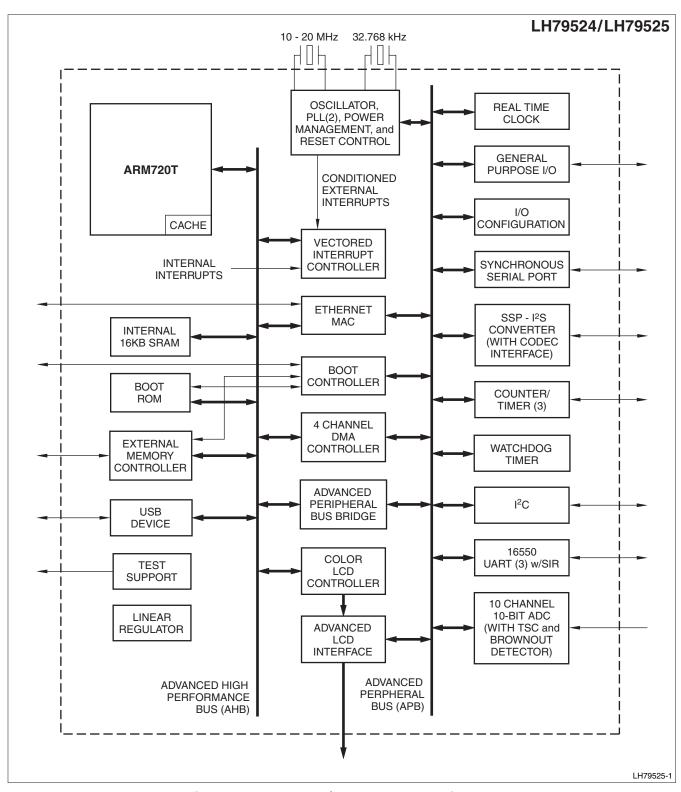

| Figure 1-1. LH79524/LH79525 Block Diagram                                         | 1-2      |

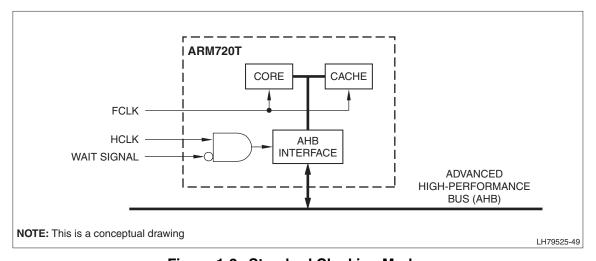

| Figure 1-2. Standard Clocking Modes                                               |          |

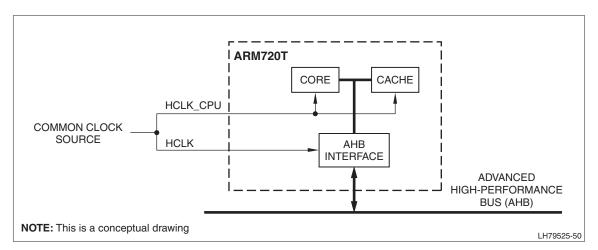

| Figure 1-3. Fastbus Clocking Mode                                                 | 1-7      |

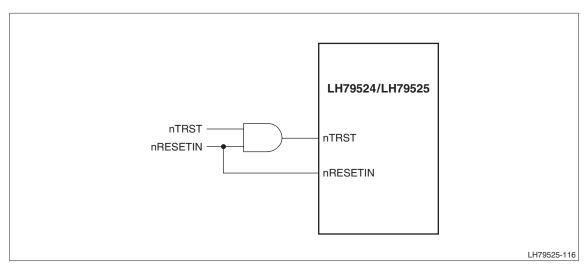

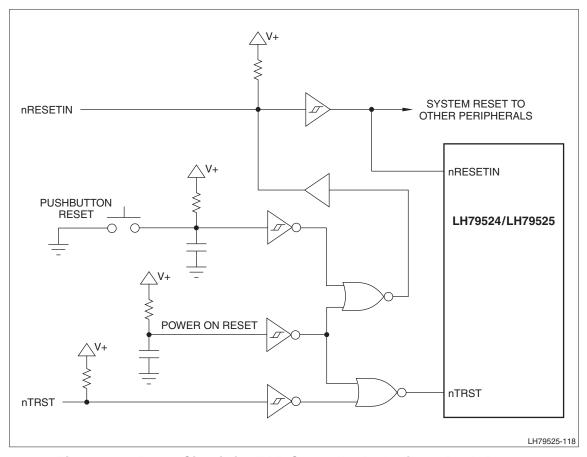

| Figure 1-4. Reset Circuit for TAP Controller                                      | 1-9      |

| Figure 1-5. Reset Circuit for TAP Controller Including a Push Button              | 1-10     |

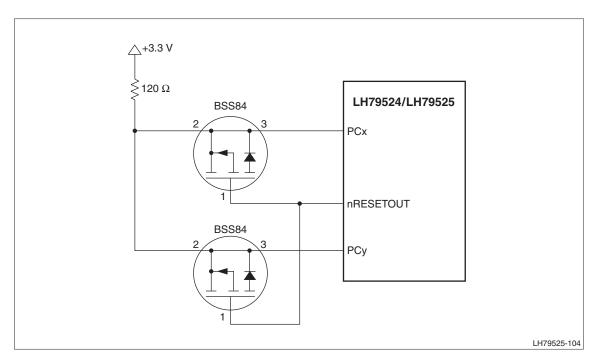

| Figure 1-6. Active Pullup Circuit                                                 | 1-11     |

| Chapter 2 – Analog-to-Digital Converter/Brownout Detector                         |          |

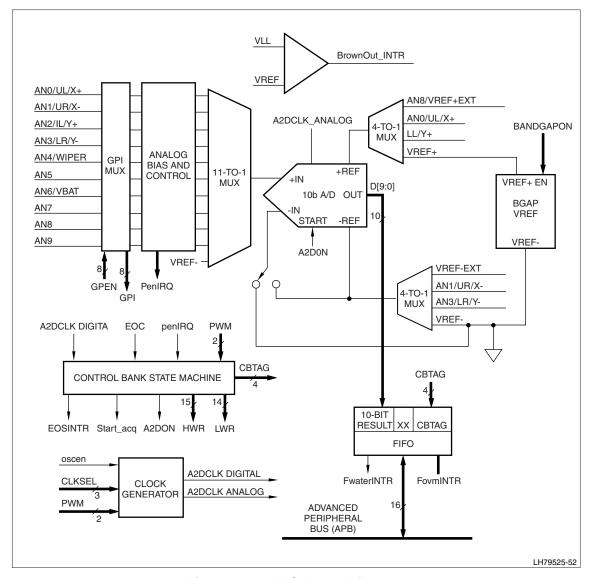

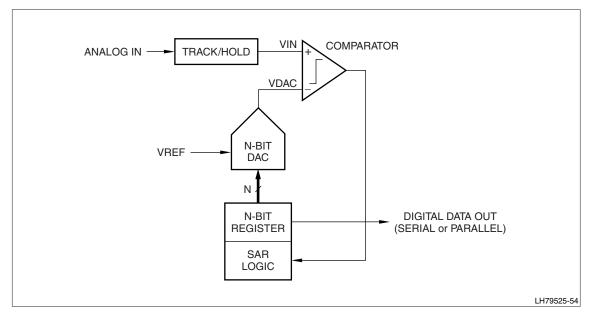

| Figure 2-1. ADC Block Diagram                                                     | 2-2      |

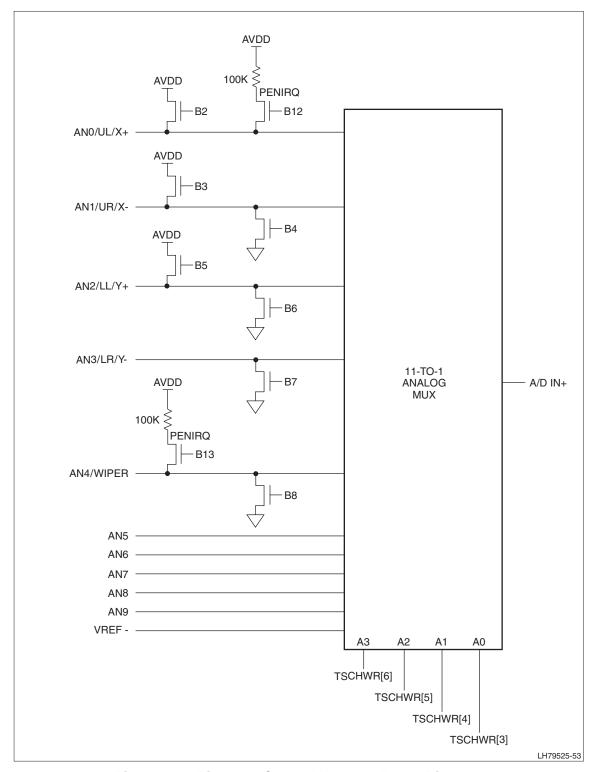

| Figure 2-2. Bias-and-Control Network Block Diagram                                |          |

| Figure 2-3. Simplified N-bit SAR Architecture                                     |          |

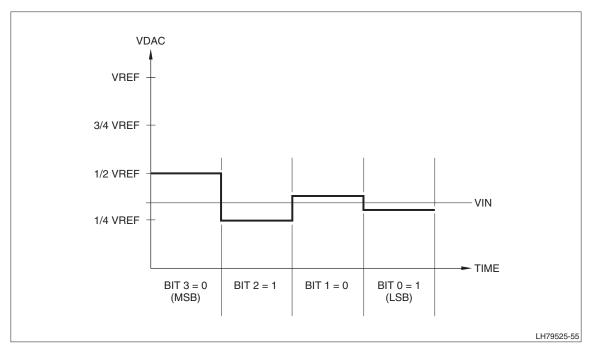

| Figure 2-4. Example of a 4-bit SAR ADC Operation                                  |          |

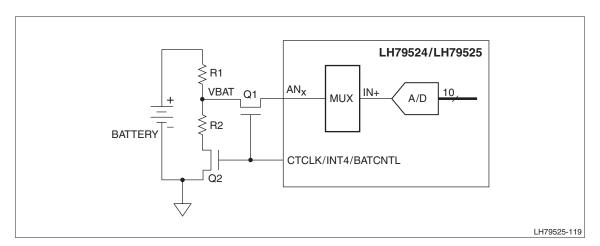

| Figure 2-5. Use of the BATCNTL Pin                                                |          |

| •                                                                                 |          |

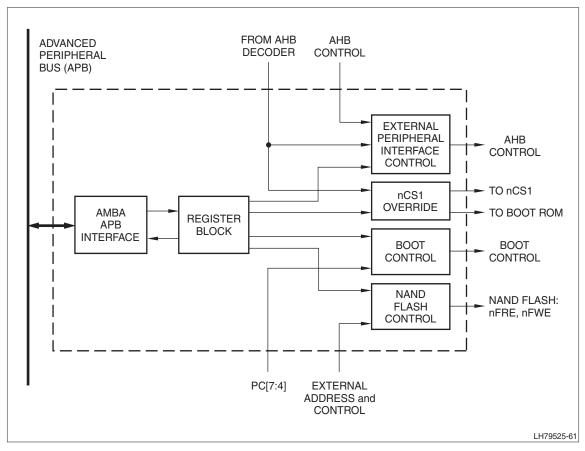

| Chapter 3 – Boot Controller Figure 3-1. Boot Controller Block Diagram             | 2_1      |

| Figure 3-1. Boot Controller Block Diagram                                         |          |

|                                                                                   |          |

| Chapter 4 – Color Liquid Crystal Display Controller                               |          |

| Figure 4-1. LH79524/LH79525 LCD System, Simplified Block Diagram                  |          |

| Figure 4-2. Block Diagram of a Typical Advanced LCD Panel                         |          |

| Figure 4-3. Color LCD Controller Block Diagram                                    |          |

| Figure 4-4. LCD Panel Power Sequencing                                            |          |

| Figure 4-5. ALI Simplified Block DiagramFigure 4-6. STN Horizontal Timing Diagram |          |

| Figure 4-7. STN Vertical Timing Diagram                                           |          |

| Figure 4-8. TFT Horizontal Timing Diagram                                         |          |

| Figure 4-9. TFT Vertical Timing Diagram                                           |          |

| Figure 4-10. AD-TFT, HR-TFT Horizontal Timing Diagram                             |          |

| Figure 4-11. AD-TFT, HR-TFT Vertical Timing Diagram                               |          |

|                                                                                   |          |

| Chapter 5 – Direct Memory Access Controller                                       | <b>-</b> |

| Figure 5-1. Basic DMA Timing                                                      | 5-4      |

| Chapter 6 – Ethernet MAC Controller                                               |          |

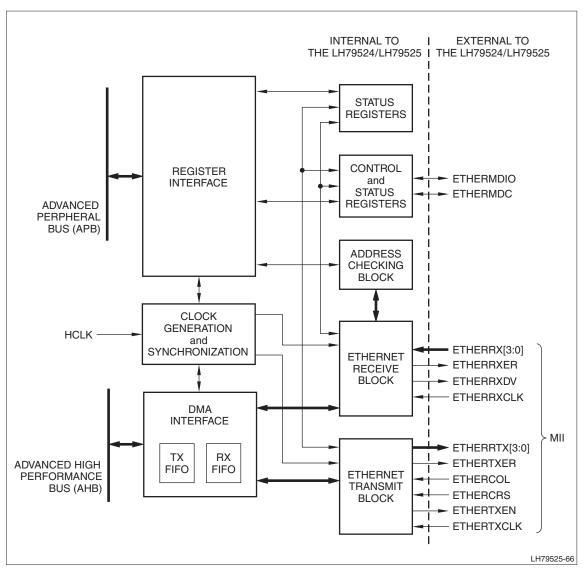

| Figure 6-1. EMAC Block Diagram                                                    |          |

| Figure 6-2. Address Matching                                                      | 6-15     |

| Chapter 7 – External Memory Controller                                      |       |

|-----------------------------------------------------------------------------|-------|

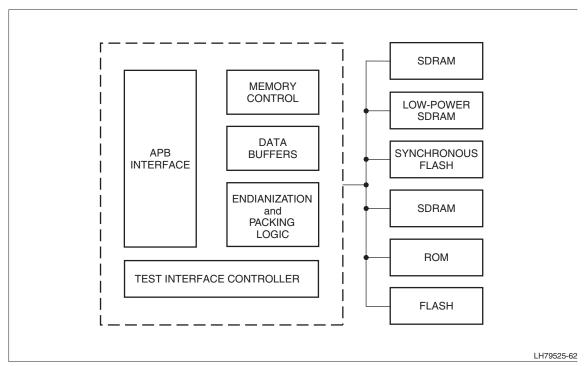

| Figure 7-1. External Memory Controller Block Diagram                        | 7-2   |

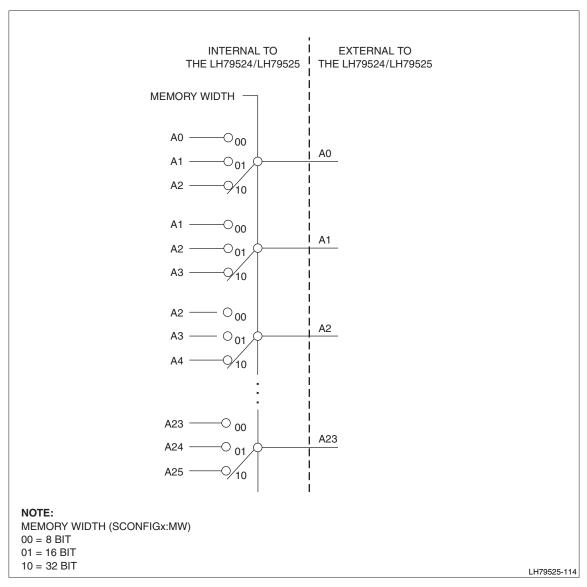

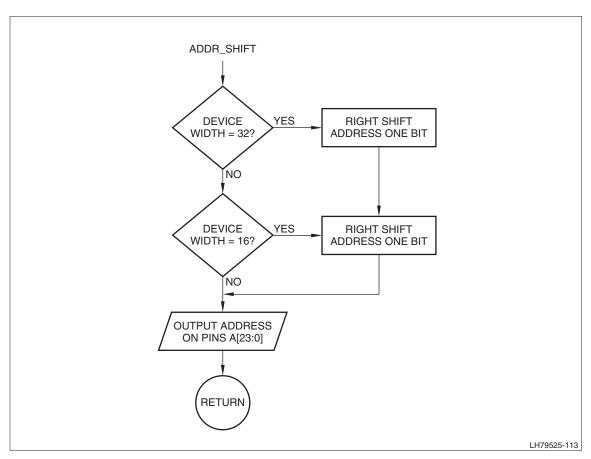

| Figure 7-2. Automatic Address Shifting                                      | 7-4   |

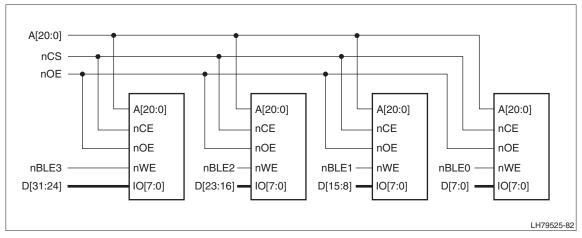

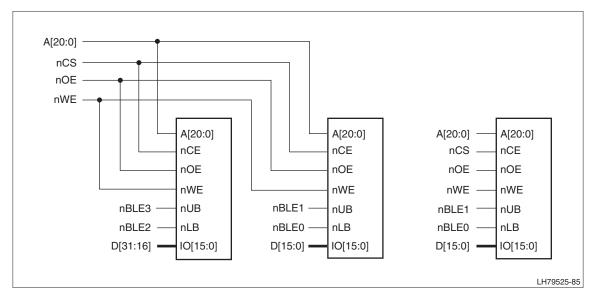

| Figure 7-3. 32-bit Memory Bank Constructed From 8-bit Devices               | 7-6   |

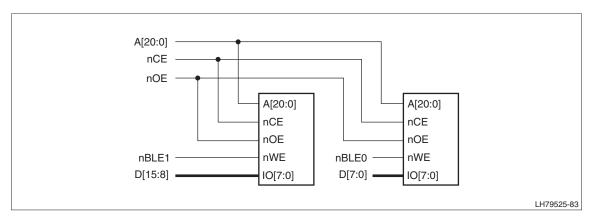

| Figure 7-4. 16-bit Memory Bank Constructed From 8-bit Devices               | 7-6   |

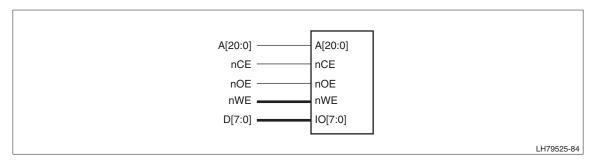

| Figure 7-5. 8-bit Memory Bank                                               | 7-6   |

| Figure 7-6. 32-bit (left) and 16-bit (right) Memory Banks Constructed       |       |

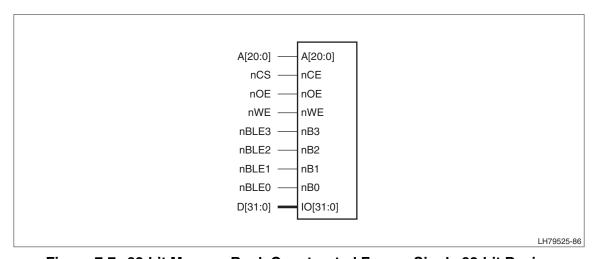

| From 16-bit Devices                                                         |       |

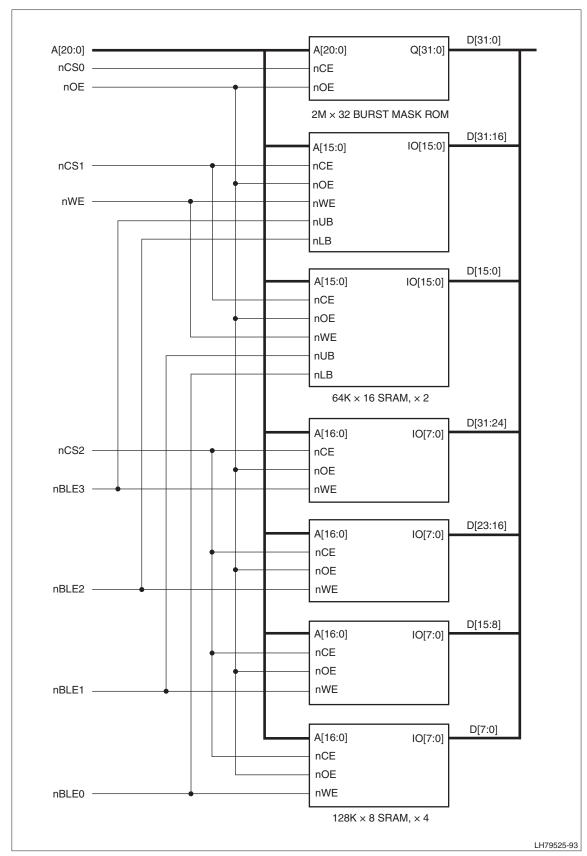

| Figure 7-7. 32-bit Memory Bank Constructed From a Single 32-bit Device      |       |

| Figure 7-8. Typical Memory Connection Diagram                               |       |

| Figure 7-9. Pre-shifting Routine                                            |       |

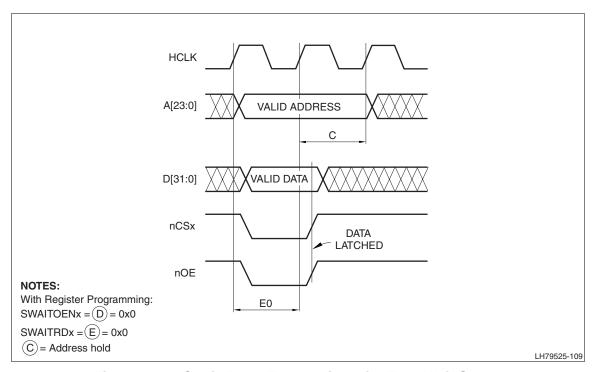

| Figure 7-10. Static Read Transaction with Zero Wait States                  |       |

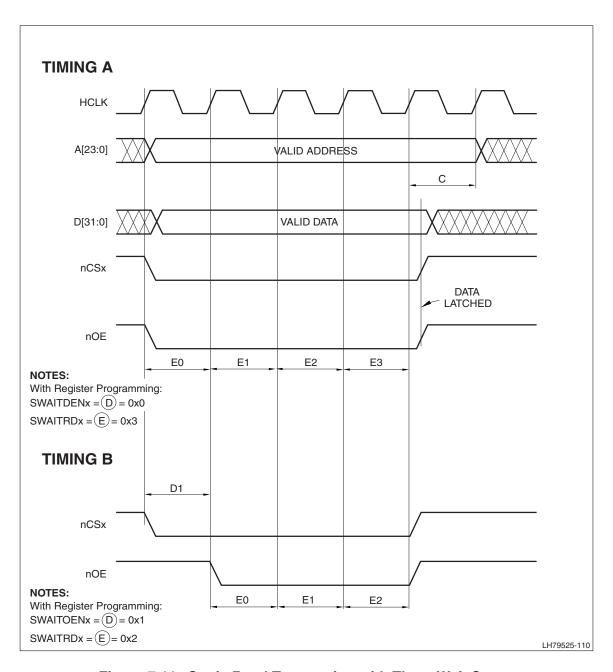

| Figure 7-11. Static Read Transaction with Three Wait States                 |       |

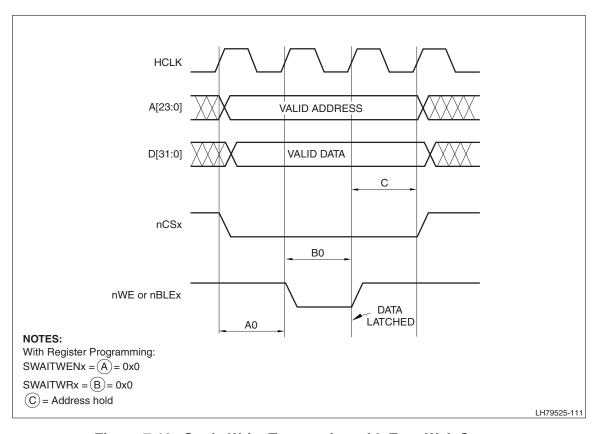

| Figure 7-12. Static Write Transaction with Zero Wait States                 |       |

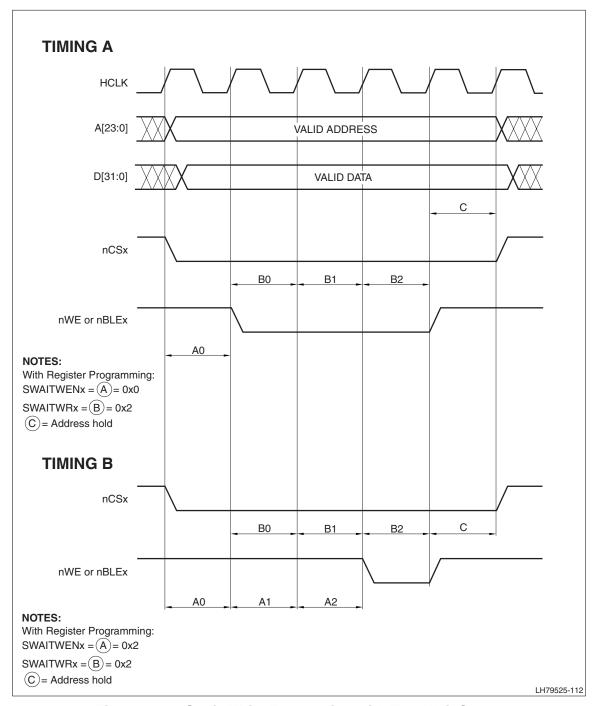

| Figure 7-13. Static Write Transaction with Two Wait States                  |       |

| Figure 7-14. Connection to NAND FlashFigure 7-15. NAND Flash Timing Example |       |

|                                                                             | / - 2 |

| Chapter 9 – I <sup>2</sup> C Module                                         |       |

| Figure 9-1. I <sup>2</sup> C Module Block Diagram                           |       |

| Figure 9-2. I <sup>2</sup> C Bus Protocol                                   | 9-2   |

| Chapter 10 – I <sup>2</sup> S Converter                                     |       |

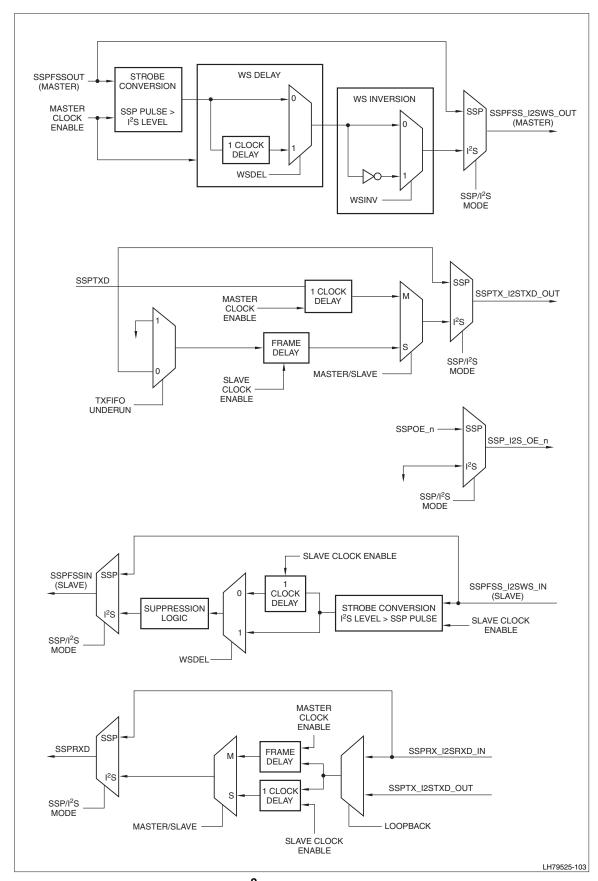

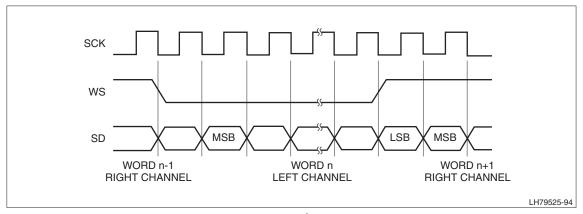

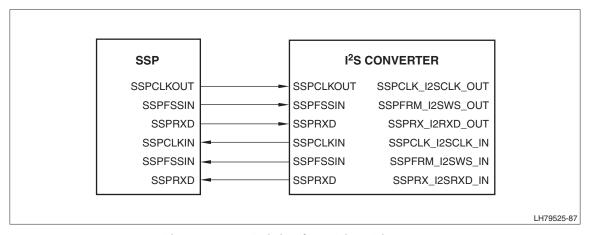

| Figure 10-1. I <sup>2</sup> S Converter Block Diagram                       | 10-2  |

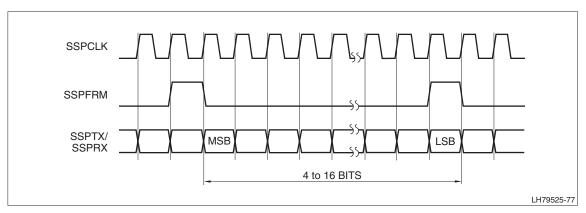

| Figure 10-2. TI SSP Frame Format                                            |       |

| Figure 10-3. I <sup>2</sup> S Format                                        | 10-3  |

| Figure 10-4. Driving/Latching Diagram                                       | 10-4  |

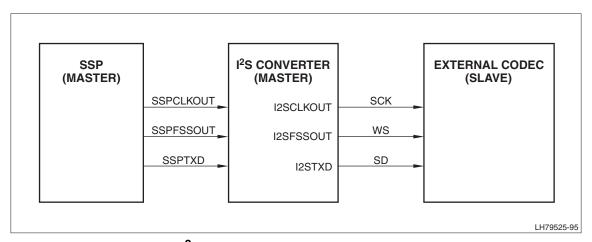

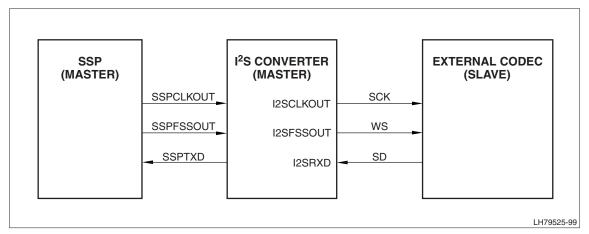

| Figure 10-5. I <sup>2</sup> S Master Mode Transmission Block Diagram        | 10-5  |

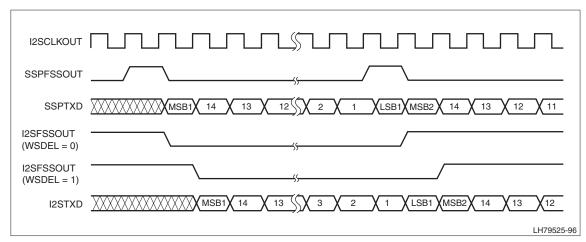

| Figure 10-6. I <sup>2</sup> S Master Mode Transmission Timing Diagram       |       |

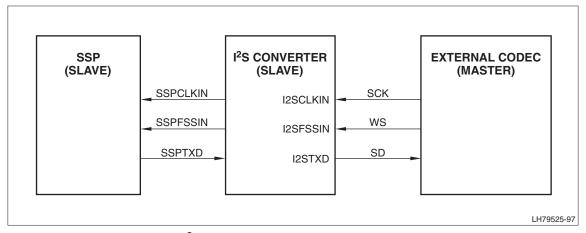

| Figure 10-7. I <sup>2</sup> S Slave Mode Transmission Block Diagram         |       |

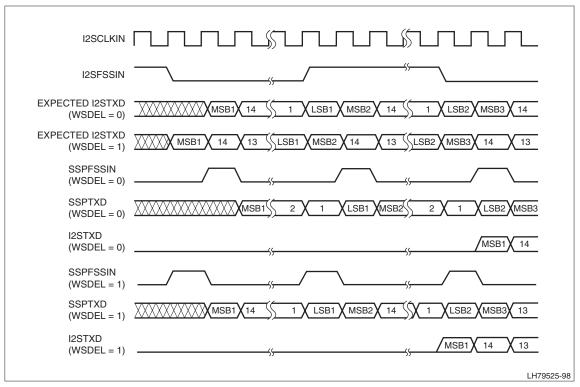

| Figure 10-8. I <sup>2</sup> S Slave Mode Transmission Timing Diagram        |       |

| Figure 10-9. I <sup>2</sup> S Master Mode Reception Block Diagram           |       |

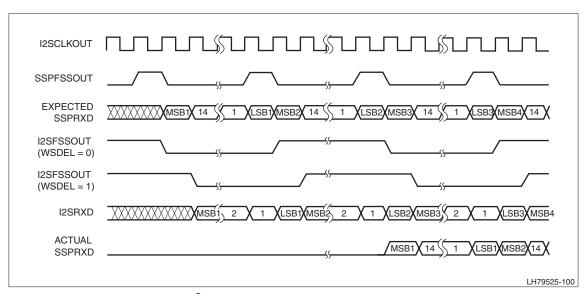

| Figure 10-10. I <sup>2</sup> S Master Mode Reception Timing Diagram         |       |

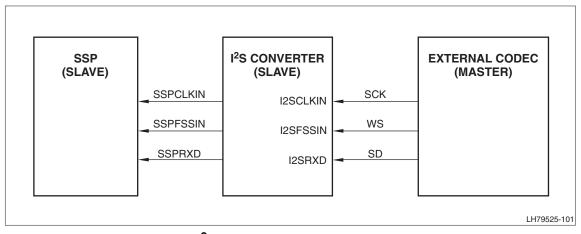

| Figure 10-11. I <sup>2</sup> S Slave Mode Reception Block Diagram           |       |

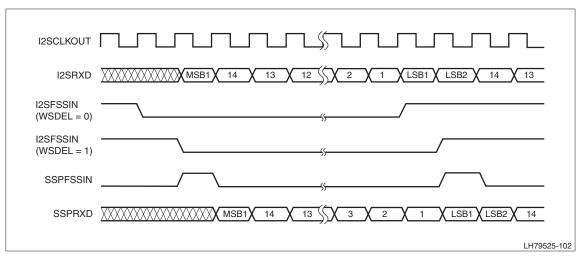

| Figure 10-12. I <sup>2</sup> S Slave Mode Reception Timing Diagram          | 10-9  |

| Chapter 12 – Real Time Clock                                                |       |

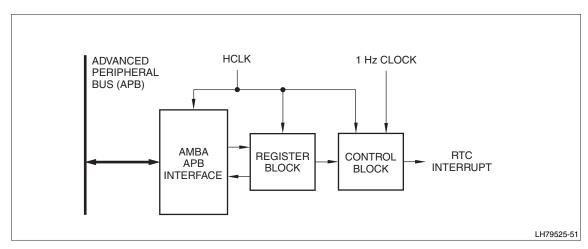

| Figure 12-1. RTC Block Diagram                                              | 12-1  |

| Chapter 13 – Reset, Clock, and Power Controller                             |       |

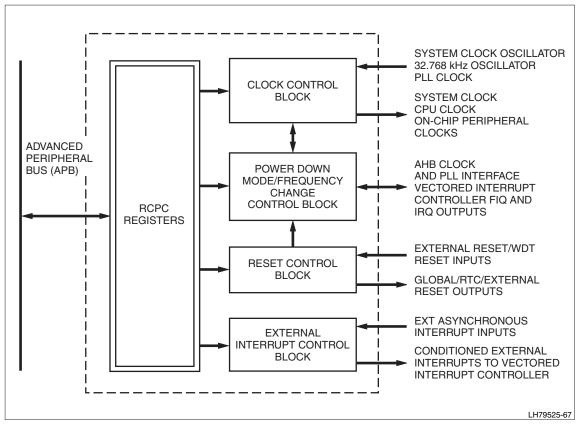

| Figure 13-1. RCPC Block Diagram                                             | 13-2  |

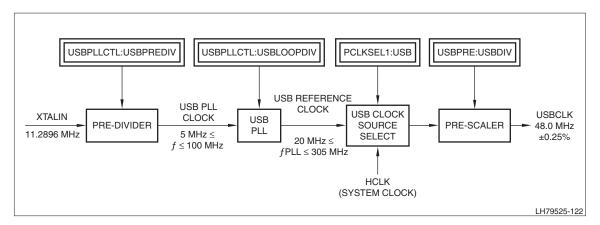

| Figure 13-2. USB Clock Divider Chain                                        |       |

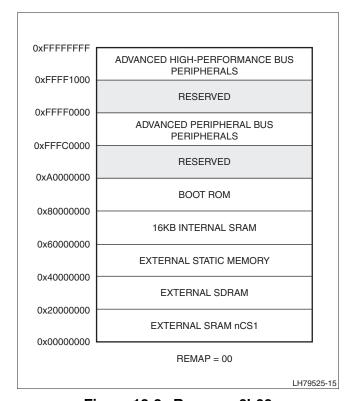

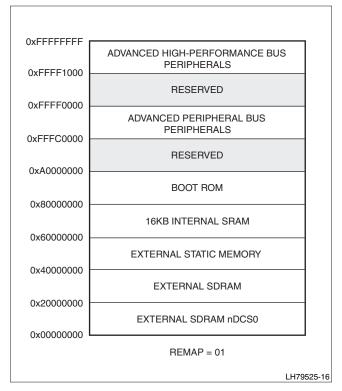

| Figure 13-3. Remap = 0b00                                                   |       |

| Figure 13-4. Remap = 0b01                                                   |       |

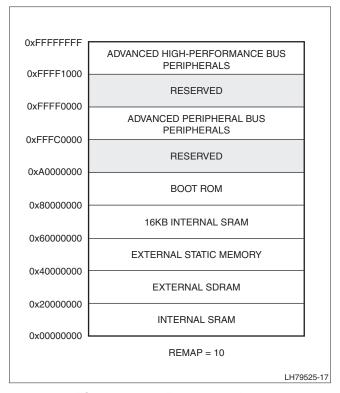

| Figure 13-5. Remap = 0b10                                                   |       |

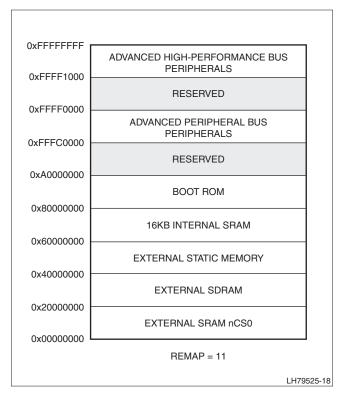

| Figure 13-6. Remap = 0b11                                                   |       |

|                                                                             |       |

| Chapter 14 – Synchronous Serial Port                           |      |

|----------------------------------------------------------------|------|

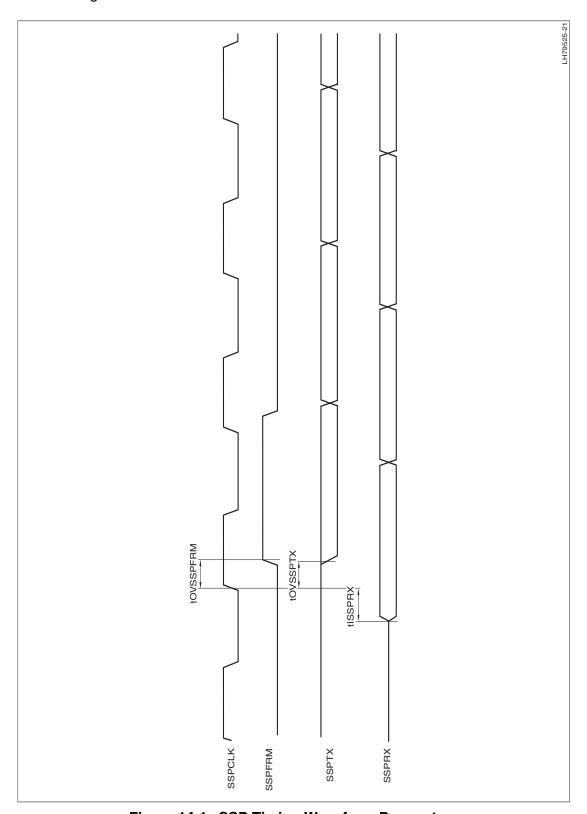

| Figure 14-1. SSP Timing Waveform Parameters                    | 14-3 |

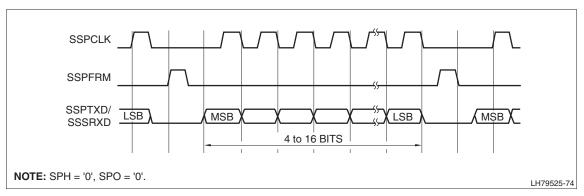

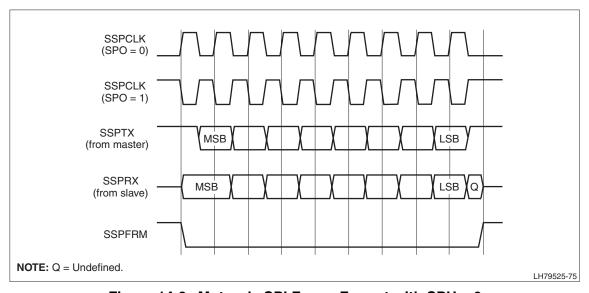

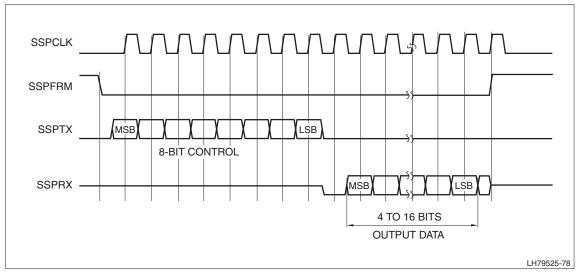

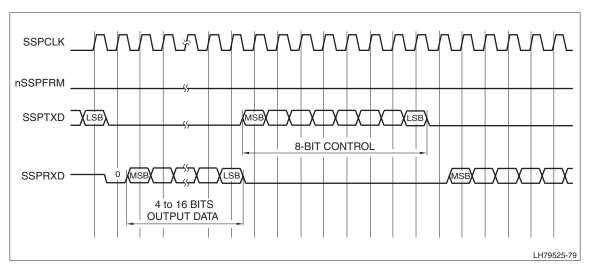

| Figure 14-2. Motorola SPI Frame Format (Continuous Transfer)   | 14-4 |

| Figure 14-3. Motorola SPI Frame Format with SPH = 0            | 14-4 |

| Figure 14-4. Texas Instruments Synchronous Serial Frame Format |      |

| (Single Transfer)                                              | 14-5 |

| Figure 14-5. Texas Instruments Synchronous Serial Frame Format |      |

| (Continuous Transfers)                                         | 14-5 |

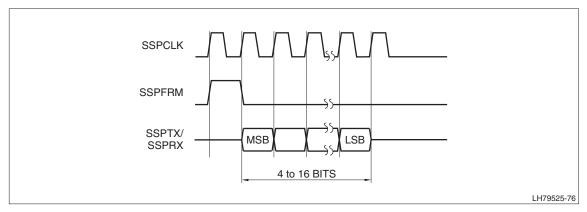

| Figure 14-6. Microwire Frame Format (Single Transfer)          | 14-6 |

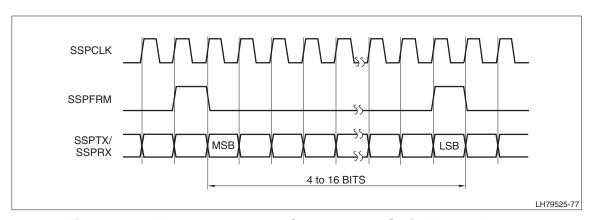

| Figure 14-7. Microwire Frame Format (Continuous Transfers)     | 14-7 |

| Chapter 15 – Timers                                            |      |

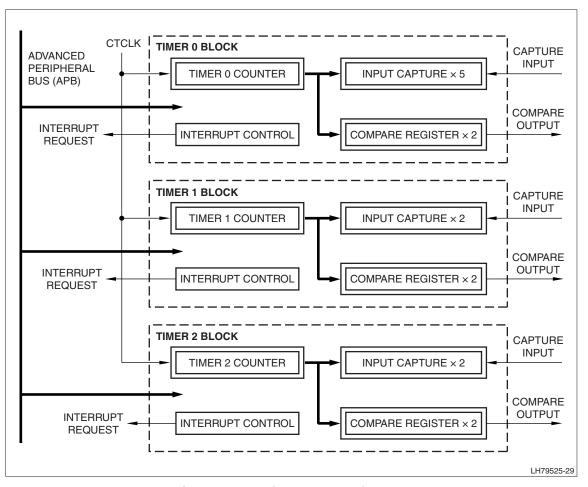

| Figure 15-1. Timer Block Diagram                               | 15-2 |

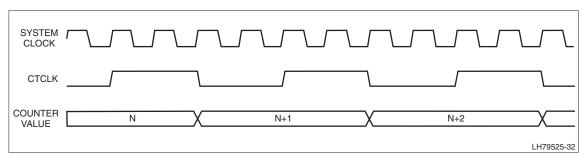

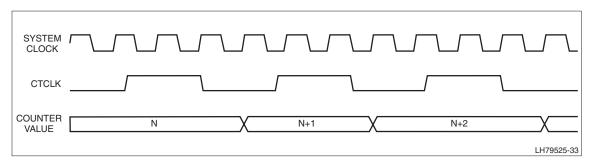

| Figure 15-2. Count Clock Timing (HCLK in Phase with CTCLK)     |      |

| Figure 15-3. Count Clock Timing (HCLK not in Phase with CTCLK) |      |

| Figure 15-4. Capture Signal Synchronization Timing             |      |

| Figure 15-5. PWM Output Signal Timing                          |      |

| Chapter 16 – UARTs                                             |      |

| Figure 16-1. UART0, UART1, and UART2 Block Diagram             | 16-2 |

| Chapter 17 – Universal Serial Bus Device                       |      |

| Figure 17-1. USB Block Diagram                                 | 17-1 |

| Figure 17-2. USB Communication Endpoints                       | 17-2 |

| Chapter 19 – Watchdog Timer                                    |      |

| Figure 19-1. Watchdog Timer Block Diagram                      | 19-2 |

## **List of Tables**

| Preface                                                                                      |        |

|----------------------------------------------------------------------------------------------|--------|

| Table 1. Register Name                                                                       | xxxvii |

| Table 2. Bit Fields                                                                          | xxxvii |

| Chapter 1 – Overview                                                                         |        |

| Table 1-1. LH79524/LH79525 Differences                                                       | 1-1    |

| Table 1-2. Clock Descriptions                                                                |        |

| Table 1-3. Port C Settings For Boot                                                          |        |

| Table 1-4. Default Bus Master Priority                                                       |        |

| Table 1-5. AHB Memory Mapping                                                                |        |

| Table 1-6. External Static Memory Section Mapping                                            |        |

| Table 1-8. Internal SRAM Memory Section Mapping                                              |        |

| Table 1-9. Boot ROM Memory Section Mapping                                                   |        |

| Table 1-7. SDRAM Memory Section Mapping                                                      |        |

| Table 1-7: 3DNAM Memory Section Mapping  Table 1-11. Primary AHB Peripheral Register Mapping |        |

| Table 1-10. AHB Memory Map on Power-up when Boot Configuration = 0bX1XX                      |        |

| Table 1-10. APB Peripheral Register Mapping                                                  |        |

|                                                                                              | . 1-10 |

| Chapter 2 – Analog-to-Digital Converter/Brownout Detector                                    |        |

| Table 2-1. ADC Register Summary                                                              |        |

| Table 2-2. HW Register                                                                       |        |

| Table 2-3. HW Fields                                                                         | . 2-11 |

| Table 2-4. In + Mux Definition                                                               | . 2-12 |

| Table 2-5. LW Register                                                                       | . 2-13 |

| Table 2-6. LW Fields                                                                         | . 2-13 |

| Table 2-7. RR Register                                                                       | . 2-14 |

| Table 2-8. RR Fields                                                                         | . 2-14 |

| Table 2-9. IM Register                                                                       | . 2-15 |

| Table 2-10. IM Fields                                                                        | . 2-15 |

| Table 2-11. PC Register                                                                      | .2-16  |

| Table 2-12. PC Fields                                                                        | .2-16  |

| Table 2-13. Touch Screen Controller Power Modes                                              | . 2-17 |

| Table 2-14. GC Register                                                                      | .2-18  |

| Table 2-15. GC Fields                                                                        | .2-18  |

| Table 2-16. GS Register                                                                      |        |

| Table 2-17. GS Fields                                                                        |        |

| Table 2-18. IS Register                                                                      |        |

| Table 2-19. IS Fields                                                                        |        |

| Table 2-20. FS Register                                                                      |        |

| Table 2-21. FS Fields                                                                        |        |

| Table 2-22. Sample Entries for Control Bank                                                  |        |

| Table 2-23. IHWCTRL Register                                                                 |        |

| Table 2-24. IHWCTRL Fields                                                                   |        |

| Table 2-25 II WCTRL Begister                                                                 | 2-24   |

| Table 2-26. ILWCTRL Fields                                       | 2-24 |

|------------------------------------------------------------------|------|

| Table 2-27. MIS Register                                         | 2-25 |

| Table 2-28. MIS Fields                                           | 2-25 |

| Table 2-29. IC Register                                          | 2-26 |

| Table 2-30. IC Fields                                            | 2-26 |

| Chapter 3 – Boot Controller                                      |      |

| Table 3-1. Boot Configuration for Silicon Version A.0            | 3-3  |

| Table 3-2. Boot Configuration for Silicon Version A.1            |      |

| Table 3-3. Alternate Pin Function During NAND Flash Booting      |      |

| Table 3-4. Boot Parameters for I2C                               |      |

| Table 3-5. Supported Devices                                     |      |

| Table 3-6. UART0 Boot Parameters                                 |      |

| Table 3-7. Boot Controller Register Summary                      |      |

| Table 3-8. PBC Register                                          |      |

| Table 3-9. PBC Fields                                            |      |

| Table 3-10. CS1OV Register                                       |      |

| Table 3-11. CS1OV Fields                                         |      |

| Table 3-12. EPM Register                                         |      |

| Table 3-13. EPM Fields                                           |      |

|                                                                  |      |

| Chapter 4 – Color Liquid Crystal Display Controller              | 4.0  |

| Table 4-1. Pixel Display Arrangement                             |      |

| Table 4-2. Frame Buffer Pixel Storage Format [31:16]             |      |

| Table 4-3. Frame Buffer Pixel Storage Format [15:0]              |      |

| Table 4-4. Palette Data Storage (LH79525 with 12-Bit CLCDC)      |      |

| Table 4-6. Supported TFT, HR-TFT, and AD-TFT LCD Panels          |      |

| Table 4-7. Supported Color STN LCD Panels (LH79524 only)         |      |

| Table 4-8. Supported Mono-STN LCD Panels                         |      |

| Table 4-9. Color STN Intensities From Gray-Scale Modulation      |      |

| Table 4-10. LH79524 LCD Data Multiplexing                        |      |

| Table 4-11. LH79525 LCD Data Multiplexing                        |      |

| Table 4-12. Usable Minimum Values Affecting STN Back Porch Width |      |

| Table 4-13. CLCDC Register Summary                               |      |

| Table 4-14. TIMING0 Register                                     |      |

| Table 4-15. TIMING0 Fields                                       |      |

| Table 4-16. TIMING1 Register                                     |      |

| Table 4-17. TIMING1 Fields                                       |      |

| Table 4-18. TIMING2 Register                                     |      |

| Table 4-19. TIMING2 Fields                                       |      |

| Table 4-20. UPBASE Register                                      |      |

| Table 4-21. UPBASE Fields                                        |      |

| Table 4-22. LPBASE Register                                      |      |