| 1   | Introduction                            |

|-----|-----------------------------------------|

| 2   | ISDN Basic Access System Overview       |

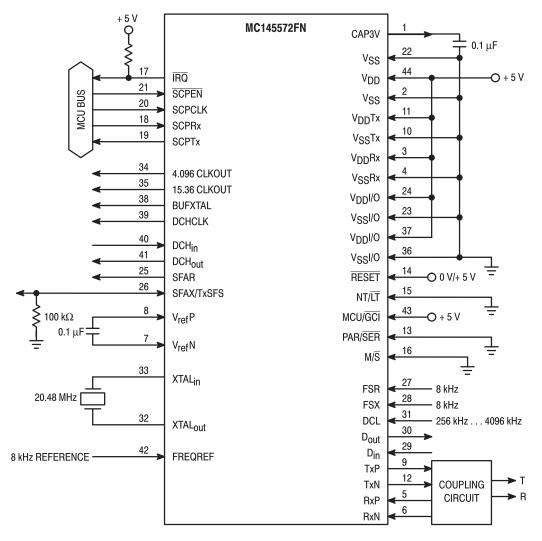

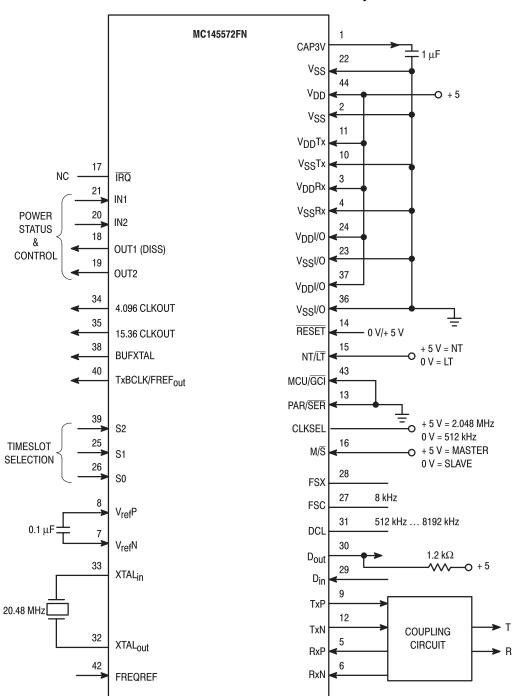

| 3   | Pin Descriptions                        |

| 4   | MCU Mode Register Description Reference |

| 5   | MCU Mode Device Functionality           |

| 6   | MCU Mode Activation and Deactivation    |

| 7   | MCU Mode Maintenance Channel Operation  |

| 8   | GCI Mode Functional Description         |

| 9   | MCU Mode Programming Suggestions        |

| 10  | Electrical Specifications               |

| 11  | Mechanical Data                         |

| A-J | Appendices                              |

# MC145572 ISDN U-Interface Transceiver

All brand and product names appearing in this document are registered trademarks of their respective holders.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

© Motorola, Inc. 1998

## **TABLE OF CONTENTS**

## SECTION 1 INTRODUCTION

| 1.1            | INTRODUCTION                                        | 1–1          |

|----------------|-----------------------------------------------------|--------------|

| 1.2            | SUPPLEMENTAL DOCUMENTATION                          | 1-1          |

| 1.3            | FEATURES                                            | 1–2          |

| 1.4            | REVISIONS                                           | 1–2          |

|                |                                                     |              |

|                | SECTION 2                                           |              |

|                | ISDN BASIC ACCESS SYSTEM OVERVIEW                   |              |

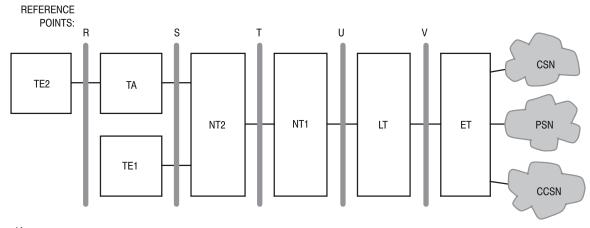

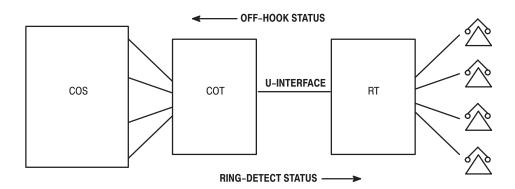

| 2.1            | ISDN REFERENCE MODEL                                | 2–1          |

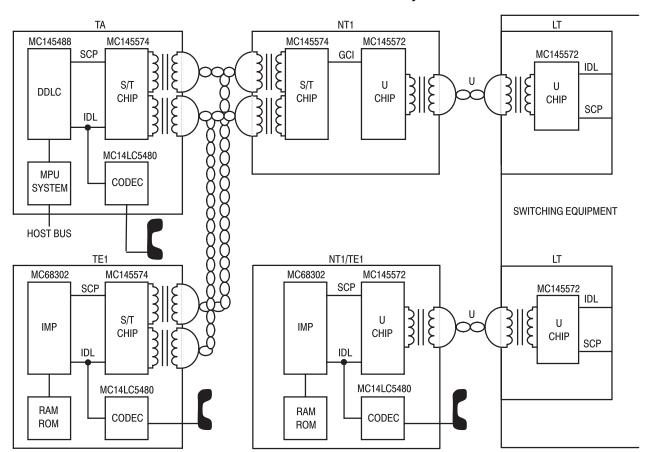

| 2.2            | U-INTERFACE TRANSCEIVER ISDN APPLICATIONS           | 2-1          |

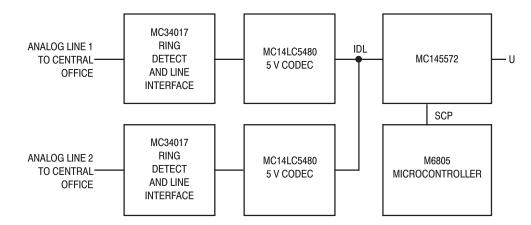

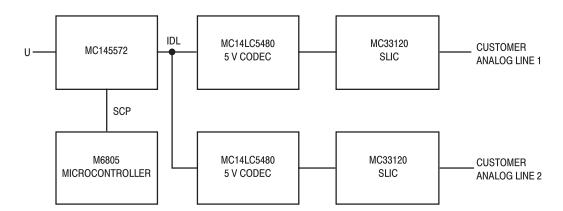

| 2.3            | NON-ISDN U-INTERFACE TRANSCEIVER APPLICATIONS       | 2–3          |

|                | SECTION 3                                           |              |

|                | PIN DESCRIPTIONS                                    |              |

| 3.1            | INTRODUCTION                                        | 3–1          |

| 3.2            | PIN DESCRIPTION QUICK REFERENCE                     | 3–1          |

| _              |                                                     |              |

| 3.3<br>3.3.1   | PIN DESCRIPTIONS                                    | 3–4<br>3–4   |

| 3.3.2          | Mode Selection Pins                                 | 3-4          |

| 3.3.3          | Time Division Multiplex Data Interface Pins         | 3–6          |

| 3.3.4          | Control/Status Interface Pins                       | 3–8          |

| 3.3.5          | 2B1Q Line Interface Pins                            | 3–12         |

| 3.3.6          | Crystal Oscillator and Phase Locked Loop (PLL) Pins | 3–12         |

| 3.3.7          | Crystal Oscillator Description                      | 3–13         |

|                | SECTION 4                                           |              |

|                | MCU MODE REGISTER DESCRIPTION REFERENCE             |              |

| 4.1            | INTRODUCTION                                        | 4–1          |

| 4.2            | REGISTER MAP                                        | 4–3          |

| 4.2.1          | Register Index                                      | 4–3          |

| 4.2.2          | Bit Description Legend                              | 4–5          |

| 4.3            | NIBBLE REGISTERS                                    | 4–5          |

| 4.3.1          | NR0: Reset and Power–Down Register                  | 4–5          |

| 4.3.2          | NR1: Activation Status Register                     | 4–6          |

| 4.3.3          | NR2: Activation Control Register                    | 4–8          |

| 4.3.4          | NR3: Interrupt Status Register                      | 4–9          |

| 4.3.5          | NR4: Interrupt Mask Register                        | 4–9          |

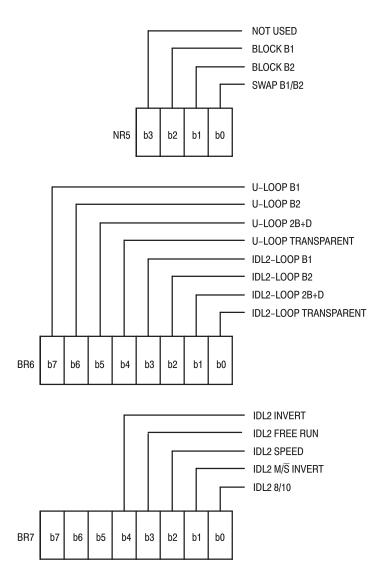

| 4.3.6          | NR5: IDL2 Data Control Register                     | 4–10         |

| 4.3.7          | R6: eoc Data Register                               | 4–10         |

| 4.4            | BYTE REGISTERS                                      | 4–12         |

| 4.4.1<br>4.4.2 | BR0: M4 Transmit Data Register                      | 4–12         |

| 4.4.2<br>4.4.3 | BR1: M4 Receive Data Register                       | 4–12<br>4–13 |

| 4.4.3<br>4.4.4 | BR3: M5/M6 Receive Data Register                    | 4–13         |

| 4.4.5          | BR4: febe Counter                                   | 4–13         |

| 4.4.6          | BR5: nebe Counter                                   | 4–14         |

|                |                                                     |              |

## **TABLE OF CONTENTS (continued)**

| 4.4.7<br>4.4.8<br>4.4.9<br>4.4.10<br>4.4.11<br>4.4.12<br>4.4.13<br>4.4.14<br>4.4.15<br>4.4.16<br>4.4.17<br>4.5<br>4.5.1<br>4.5.2<br>4.5.3<br>4.5.4<br>4.5.5<br>4.5.6<br>4.5.7<br>4.5.8<br>4.5.9<br>4.6.1<br>4.6.2 | BR6: Loopback Control Register BR7: IDL2 Configuration Register BR8: Transmit Framer and Mode Control Register BR9: Maintenance Channel Configuration Register BR10: Overlay Select Register BR11: Activation State Register BR12: Activation State Test Register BR13: Echo Canceller Test Register BR14: Test Register BR15: Revision Number Register BR15: Revision Number Register BR15: Revision Number Register OVERLAY REGISTERS OR0: Dout B1 Timeslot Register OR1: Dout B2 Timeslot Register OR2: Dout D Timeslot Register OR3: Din B1 Timeslot Register OR4: Din B2 Timeslot Register OR5: Din D and GCI Timeslot Register OR6: Timeslot and GCI Control Register OR7: Configuration Register 1 OR8: Configuration Register 2 OR9: Configuration Register 3 D CHANNEL AND DEBUG REGISTERS OR12: D Channel Data Register OR13: Dump/Restore Test Register | 4-15<br>4-17<br>4-20<br>4-21<br>4-24<br>4-25<br>4-26<br>4-27<br>4-28<br>4-29<br>4-30<br>4-30<br>4-31<br>4-31<br>4-31<br>4-31<br>4-31<br>4-31<br>4-35<br>4-35<br>4-35 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                   | SECTION 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                      |

|                                                                                                                                                                                                                   | MCU MODE DEVICE FUNCTIONALITY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                      |

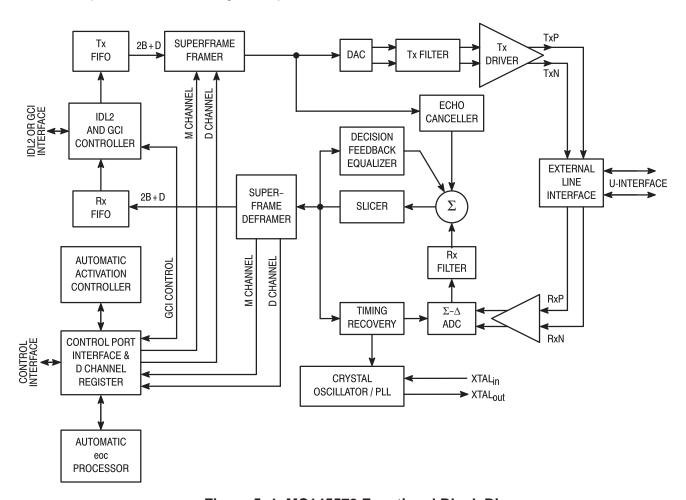

| 5.1                                                                                                                                                                                                               | FUNCTIONAL OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5–1                                                                                                                                                                  |

| 5.2                                                                                                                                                                                                               | MC145472/MC14LC5472 COMPATIBILITY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5–2                                                                                                                                                                  |

| 5.3                                                                                                                                                                                                               | CONTROL INTERFACES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5–4                                                                                                                                                                  |

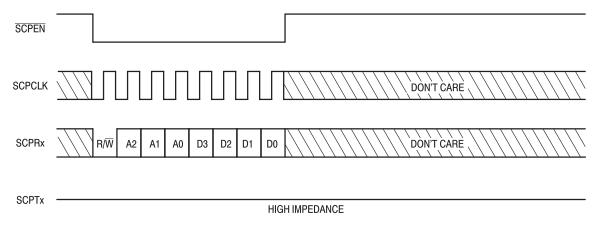

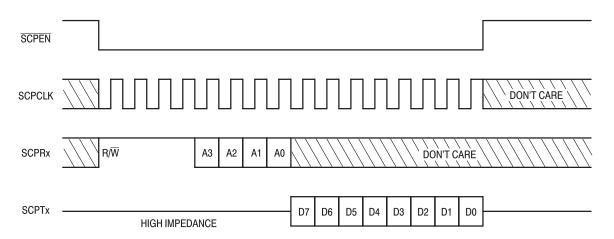

| 5.3.1                                                                                                                                                                                                             | SCP Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5–5                                                                                                                                                                  |

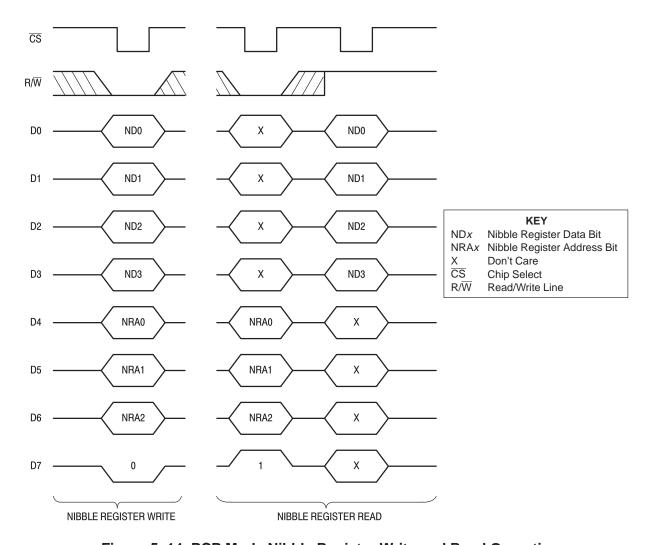

| 5.3.1.1                                                                                                                                                                                                           | Nibble Register Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5–6                                                                                                                                                                  |

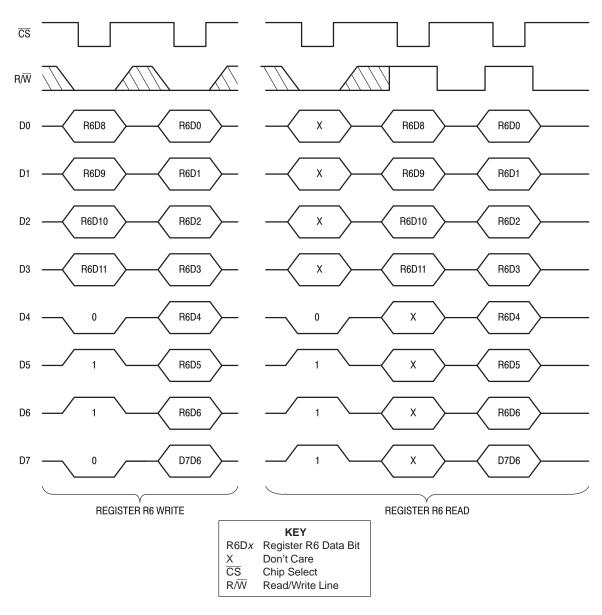

| 5.3.1.2                                                                                                                                                                                                           | Register R6 Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5–7                                                                                                                                                                  |

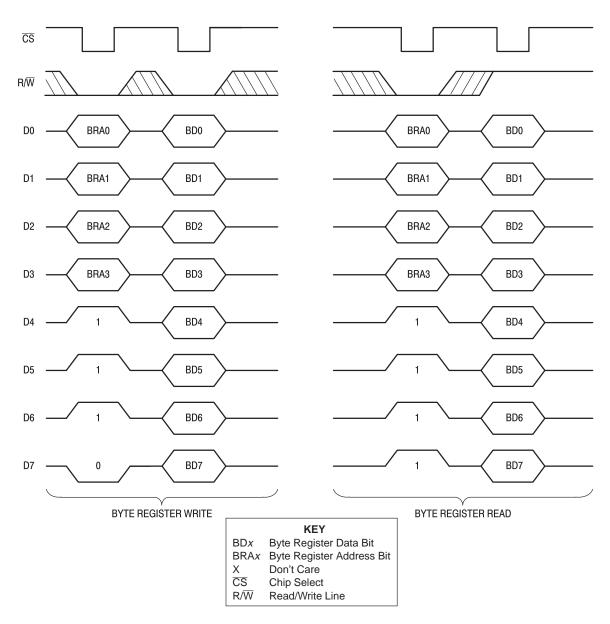

| 5.3.1.3                                                                                                                                                                                                           | Byte Register Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5–9                                                                                                                                                                  |

| 5.3.2<br>5.3.2.1                                                                                                                                                                                                  | PCP Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5–11<br>5–12                                                                                                                                                         |

| 5.3.2.1                                                                                                                                                                                                           | PCP Nibble Register Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5–12                                                                                                                                                                 |

| 5.3.2.3                                                                                                                                                                                                           | PCP Byte Register Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5–14                                                                                                                                                                 |

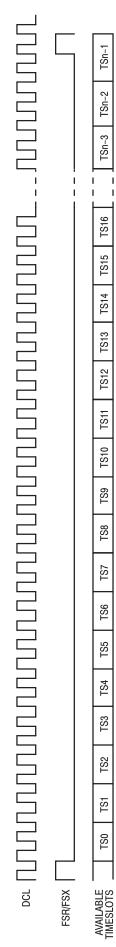

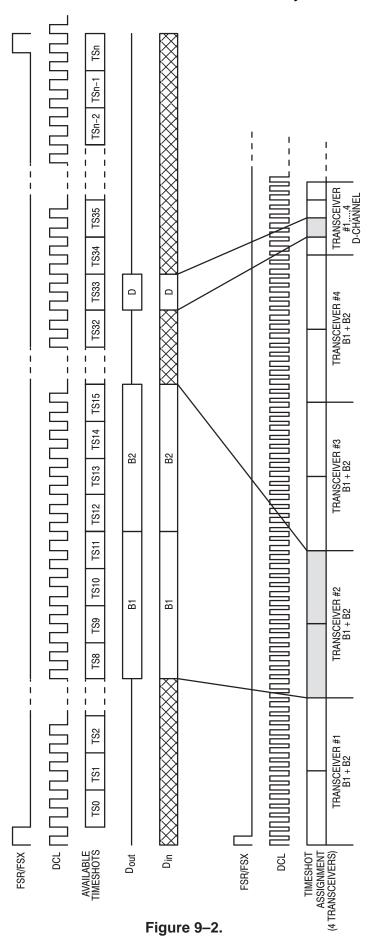

| 5.4                                                                                                                                                                                                               | IDL2 TIME DIVISION BUS INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5–15                                                                                                                                                                 |

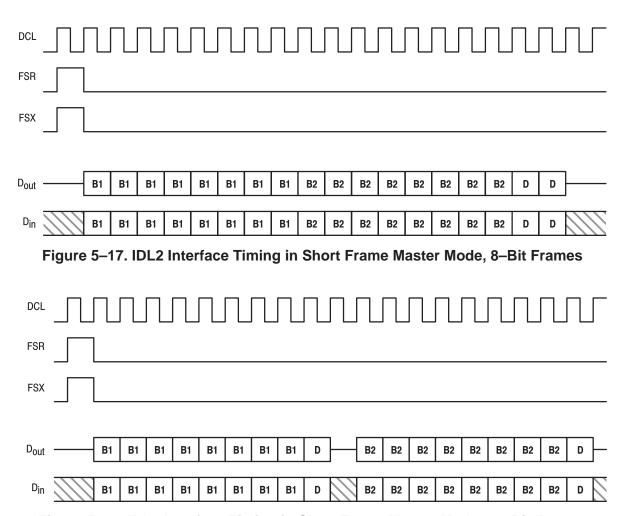

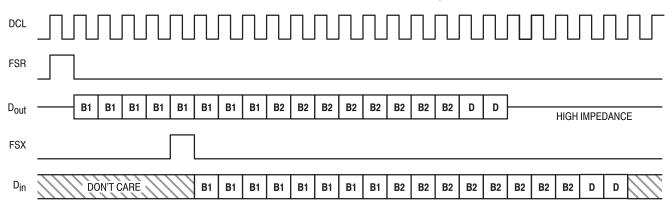

| 5.4.1                                                                                                                                                                                                             | Short Frame Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5–16                                                                                                                                                                 |

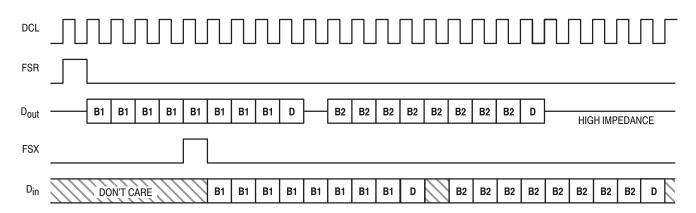

| 5.4.2                                                                                                                                                                                                             | Long Frame Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5–18                                                                                                                                                                 |

| 5.4.3                                                                                                                                                                                                             | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5–19                                                                                                                                                                 |

| 5.4.4                                                                                                                                                                                                             | GCI 2B+D Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                      |

| 5.4.5                                                                                                                                                                                                             | Master and Slave Mode Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5–20                                                                                                                                                                 |

| 5.4.6                                                                                                                                                                                                             | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5–20                                                                                                                                                                 |

| 5.4.7                                                                                                                                                                                                             | Master and Slave Mode Operation  D Channel Port  Timeslot Assigner                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5–20<br>5–22                                                                                                                                                         |

|                                                                                                                                                                                                                   | Master and Slave Mode Operation  D Channel Port  Timeslot Assigner  Timeslot Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5–20<br>5–22<br>5–26                                                                                                                                                 |

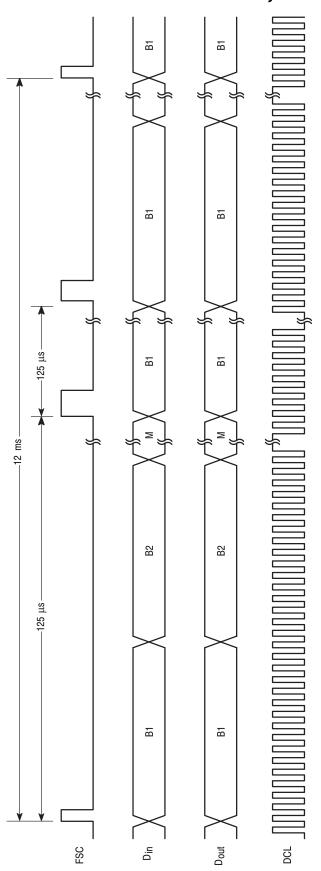

| 5.4.8                                                                                                                                                                                                             | Master and Slave Mode Operation  D Channel Port  Timeslot Assigner  Timeslot Selection  IDL2 2B+D Data Alignment to U-Interface Superframe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5–20<br>5–22<br>5–26<br>5–27                                                                                                                                         |

| 5.4.8<br>5.4.8.1                                                                                                                                                                                                  | Master and Slave Mode Operation D Channel Port Timeslot Assigner Timeslot Selection IDL2 2B+D Data Alignment to U–Interface Superframe IDL2 Short Frame Mode Superframe Alignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5–20<br>5–22<br>5–26<br>5–27<br>5–27                                                                                                                                 |

| 5.4.8<br>5.4.8.1<br>5.4.8.2                                                                                                                                                                                       | Master and Slave Mode Operation D Channel Port Timeslot Assigner Timeslot Selection IDL2 2B+D Data Alignment to U-Interface Superframe IDL2 Short Frame Mode Superframe Alignment IDL2 Long Frame Mode Superframe Alignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5–20<br>5–22<br>5–26<br>5–27<br>5–27<br>5–27                                                                                                                         |

| 5.4.8<br>5.4.8.1<br>5.4.8.2<br>5.4.8.3                                                                                                                                                                            | Master and Slave Mode Operation D Channel Port Timeslot Assigner Timeslot Selection IDL2 2B+D Data Alignment to U-Interface Superframe IDL2 Short Frame Mode Superframe Alignment IDL2 Long Frame Mode Superframe Alignment GCI 2B+D Mode Superframe Alignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5–20<br>5–22<br>5–26<br>5–27<br>5–27<br>5–27<br>5–27                                                                                                                 |

| 5.4.8<br>5.4.8.1<br>5.4.8.2                                                                                                                                                                                       | Master and Slave Mode Operation D Channel Port Timeslot Assigner Timeslot Selection IDL2 2B+D Data Alignment to U-Interface Superframe IDL2 Short Frame Mode Superframe Alignment IDL2 Long Frame Mode Superframe Alignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5–20<br>5–22<br>5–26<br>5–27<br>5–27<br>5–27                                                                                                                         |

## **TABLE OF CONTENTS (continued)**

| 5.6<br>5.6.1<br>5.6.2<br>5.6.3<br>5.6.4<br>5.6.5<br>5.6.6 | U-Interface Loopback IDL2 Interface Loopback Superframe Framer-to-Deframer Loopback Superframe Framer-to-Deframer Loopbacks in Systems Having Multiple MC145572s External Analog Loopback External Analog Loopbacks in Systems Having Multiple MC145572s | 5–30<br>5–31<br>5–32<br>5–33<br>5–34<br>5–35<br>5–37 |

|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

|                                                           | SECTION 6 MCU MODE ACTIVATION AND DEACTIVATION                                                                                                                                                                                                           |                                                      |

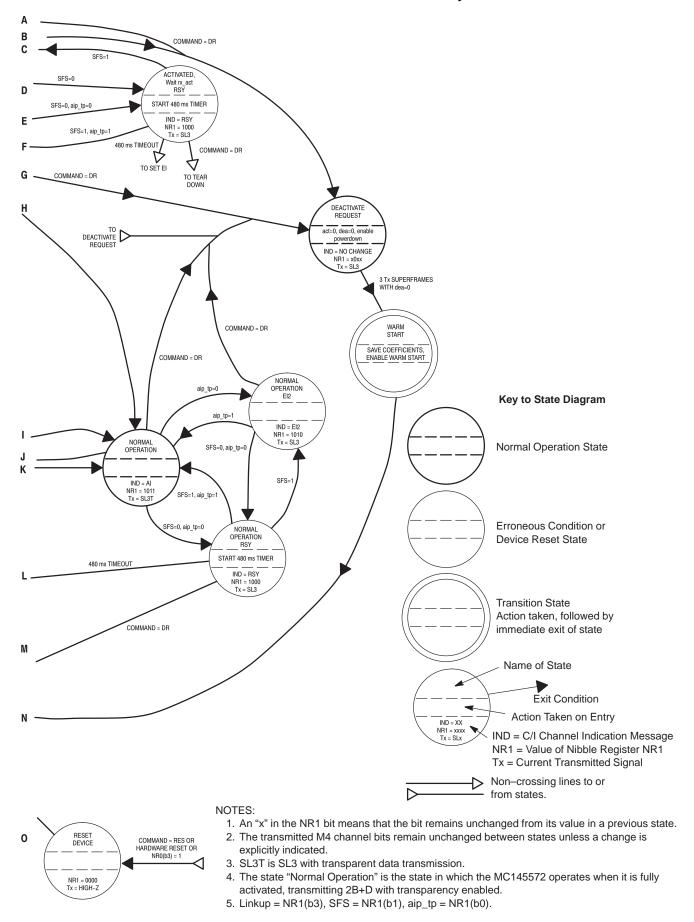

| 6.1                                                       | INTRODUCTION                                                                                                                                                                                                                                             | 6–1                                                  |

| 6.2                                                       | ACTIVATION SIGNALS FOR NT MODE                                                                                                                                                                                                                           | 6–2                                                  |

| 6.3                                                       | ACTIVATION SIGNALS FOR LT MODE                                                                                                                                                                                                                           | 6–3                                                  |

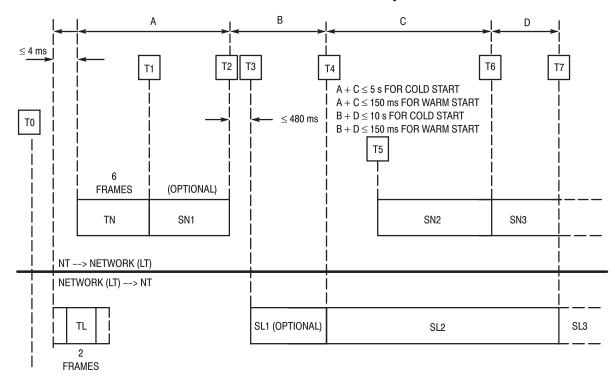

| 6.4                                                       | ACTIVATION INITIATION                                                                                                                                                                                                                                    | 6–3                                                  |

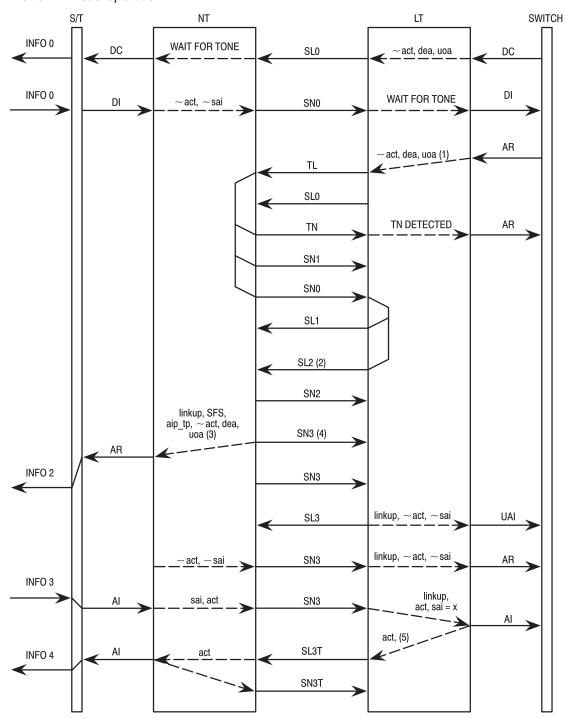

| 6.5                                                       | ACTIVATION OF U-INTERFACE BY NT                                                                                                                                                                                                                          | 6–3                                                  |

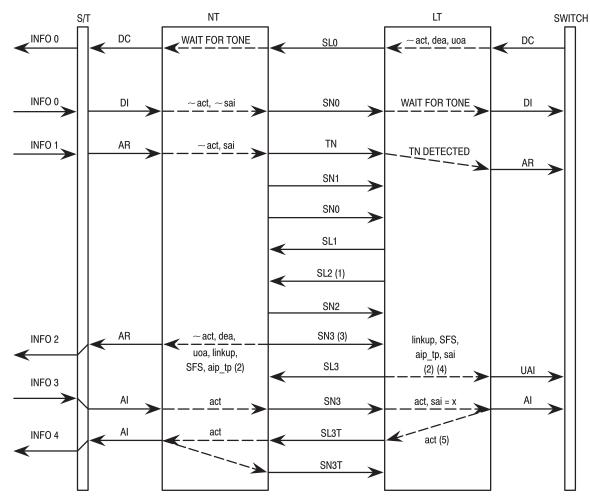

| 6.6                                                       | ACTIVATION OF U-INTERFACE BY LT                                                                                                                                                                                                                          | 6–4                                                  |

| 6.7                                                       | ACTIVATION INDICATION                                                                                                                                                                                                                                    | 6–4                                                  |

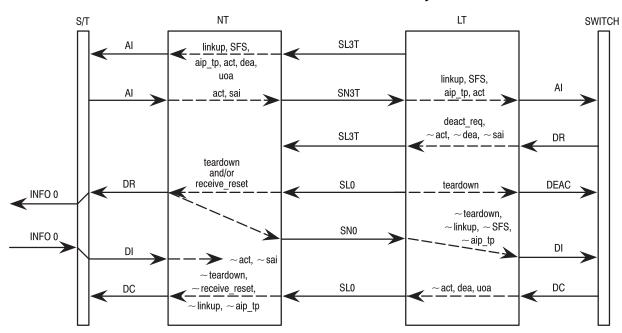

| 6.8                                                       | NT DEACTIVATION PROCEDURES AND WARM START                                                                                                                                                                                                                | 6–5                                                  |

| 6.9                                                       | LT DEACTIVATION PROCEDURES                                                                                                                                                                                                                               | 6–5                                                  |

| 6.10                                                      | INITIAL STATE OF B1 AND B2 CHANNELS                                                                                                                                                                                                                      | 6–5                                                  |

| 6.11<br>6.11.1                                            | ADDITIONAL NOTES                                                                                                                                                                                                                                         | 6–5<br>6–5                                           |

| 6.11.2                                                    | Indication of Transmit States and Repeater Applications                                                                                                                                                                                                  | 6–6                                                  |

|                                                           |                                                                                                                                                                                                                                                          |                                                      |

|                                                           | SECTION 7 MCU MODE MAINTENANCE CHANNEL OPERATION                                                                                                                                                                                                         |                                                      |

|                                                           | WICO WIODE MAIN LENANCE CHANNEL OF ERATION                                                                                                                                                                                                               |                                                      |

| 7.1                                                       | INTRODUCTION                                                                                                                                                                                                                                             | 7–1                                                  |

| 7.2                                                       | EMBEDDED OPERATIONS SUBCHANNEL                                                                                                                                                                                                                           | 7–2                                                  |

| 7.3                                                       | M4 SUBCHANNEL AND DATA TRANSPARENCY                                                                                                                                                                                                                      | 7–2                                                  |

| 7.4                                                       | M5 AND M6 CHANNELS                                                                                                                                                                                                                                       | 7–3                                                  |

| 7.5                                                       | febe AND nebe BITS                                                                                                                                                                                                                                       | 7–3                                                  |

| 7.6                                                       | FORCE CORRUPT crc                                                                                                                                                                                                                                        | 7–4                                                  |

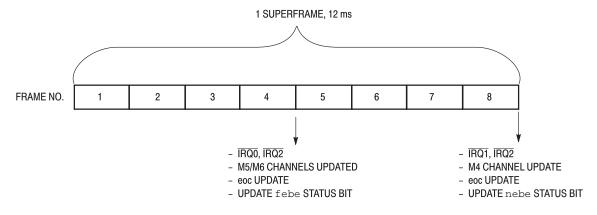

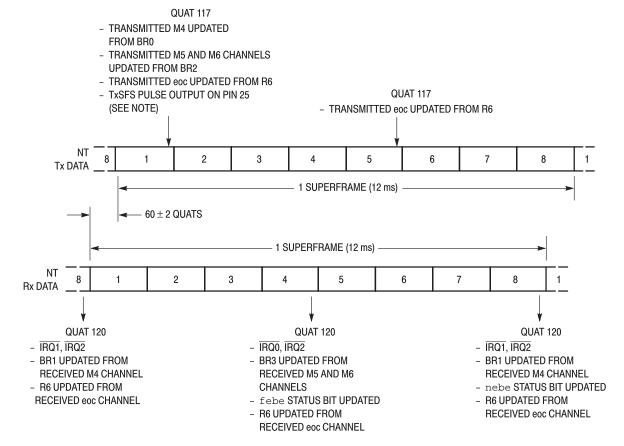

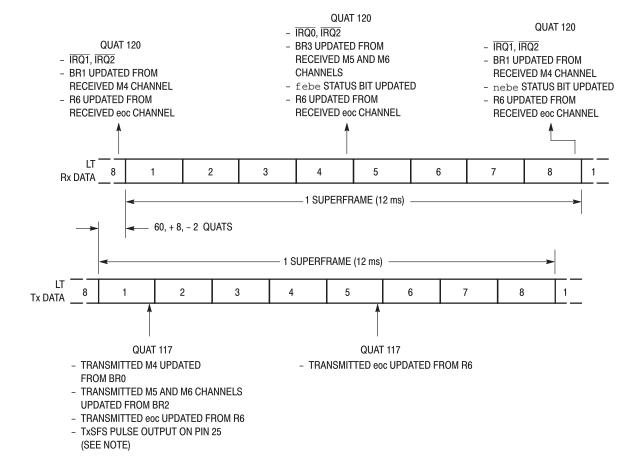

| 7.7                                                       | MAINTENANCE CHANNEL INTERRUPTS AND UPDATES                                                                                                                                                                                                               | 7–7                                                  |

## **TABLE OF CONTENTS (continued)**

## SECTION 8 GCI MODE FUNCTIONAL DESCRIPTION

| 8.1<br>8.2<br>8.3<br>8.3.1<br>8.3.2<br>8.3.2.1<br>8.3.2.2<br>8.3.2.3<br>8.3.3<br>8.4<br>8.5<br>8.6                                                                       | FUNCTIONAL OVERVIEW INTERFACE SIGNALS GCI FRAME STRUCTURE Monitor Channel Operation Monitor Channel Messages and Commands Monitor Channel Commands Monitor Channel Response Messages Monitor Channel Interrupt Indication Messages Command/Indicate Channel Operation GCI ACTIVATION AND DEACTIVATION TIME DIAGRAMS GCI MASTER AND SLAVE MODE OPERATION U-INTERFACE SUPERFRAME ALIGNMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8–10<br>8–11<br>8–12<br>8–19                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

|                                                                                                                                                                          | SECTION 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                        |

|                                                                                                                                                                          | MCU MODE PROGRAMMING SUGGESTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                        |

| 9.1<br>9.2<br>9.2.1<br>9.2.2<br>9.2.3<br>9.3<br>9.4<br>9.5<br>9.6                                                                                                        | INTRODUCTION  ACTIVATION AND INITIALIZATION  NT Automatic eoc Mode Initialization and Activation  NT Non-Automatic eoc Mode Initialization and Activation  LT Mode Initialization and Activation  TIMESLOT ASSIGNER PROGRAMMING EXAMPLE  GCI 2B+D MODE PROGRAMMING EXAMPLE  BLOCK ERROR RATIO CALCULATION USING febe/nebe COUNTERS  D CHANNEL COMMUNICATION VIA THE SERIAL OR PARALLEL CONTROL PORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 9-1<br>9-1<br>9-2<br>9-4<br>9-6<br>9-8<br>9-11<br>9-11 |

|                                                                                                                                                                          | SECTION 10 ELECTRICAL SPECIFICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                        |

| 10.1<br>10.2<br>10.3<br>10.4<br>10.5<br>10.6<br>10.6.1<br>10.6.2<br>10.7<br>10.7.1<br>10.7.2<br>10.7.3<br>10.7.4<br>10.8<br>10.9<br>10.9.1<br>10.9.2<br>10.9.3<br>10.9.4 | ABSOLUTE MAXIMUM RATINGS  RECOMMENDED OPERATING CONDITIONS  POWER CONSUMPTION  PERFORMANCE  DC ELECTRICAL CHARACTERISTICS  2B1Q INTERFACE ELECTRICAL CHARACTERISTICS  Pins TxP and TxN  Pins RxP and RxN  IDL2 TIMING  IDL2 Master Short Frame Sync Timing, 8– and 10–Bit and TSAC Formats  IDL2 Slave Short Frame Sync Timing, 8– and 10–Bit Formats  IDL2 Master Long Frame Sync, 8– and 10–Bit Formats  IDL2 Slave Long Frame Sync, 8– and 10–Bit Formats  IDL2 Slave Long Frame Sync, 8– and 10–Bit Formats  GCI TIMING  D-CHANNEL PORT TIMING  IDL2 (Master or Slave) Short Frame Sync 8–Bit Format, D Channel Port Timing  IDL2 (Master or Slave) Long Frame Sync 8–Bit Format, D Channel Port Timing  IDL2 (Master or Slave) Long Frame Sync 8–Bit Format, D Channel Port Timing  IDL2 (Master or Slave) Long Frame Sync 8–Bit Format, D Channel Port Timing  IDL2 (Master or Slave) Long Frame Sync 8–Bit Format, D Channel Port Timing  IDL2 (Master or Slave) Long Frame Sync 8–Bit Format, D Channel Port Timing  IDL2 (Master or Slave) Long Frame Sync 10–Bit Format, D Channel Port Timing | 10–1                                                   |

## **TABLE OF CONTENTS (continued)**

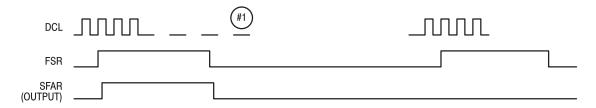

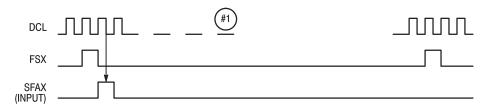

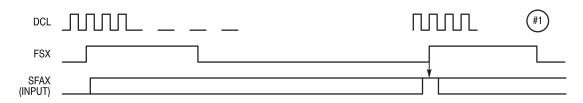

| 10.10              | SUPERFRAME TRANSMIT AND RECEIVE (SFAX/SFAR) TIMING                        |            |

|--------------------|---------------------------------------------------------------------------|------------|

| 10.10.1            | SFAX Input Timing in IDL2 (Master or Slave) Short Frame Mode              |            |

| 10.10.2            | SFAX Input Timing in IDL2 (Master or Slave) Long Frame Mode               |            |

| 10.10.3            | SFAX/SFAR Output Timing in IDL2 (Master or Slave) Short Frame Mode        |            |

| 10.10.4            | SFAX/SFAR Output Timing in IDL2 (Master or Slave) Long Frame Mode         |            |

| 10.11              | PARALLEL CONTROL PORT TIMING                                              |            |

| 10.11.1<br>10.11.2 | Parallel Control Port Write Timing                                        |            |

|                    | Parallel Control Port Read Timing                                         |            |

| 10.12              | SWITCHING CHARACTERISTICS FOR SCP INTERFACE                               |            |

| 10.13              | SWITCHING CHARACTERISTICS FOR SYSCLK AND EYEDATA                          | 10–31      |

| 10.14              | SWITCHING CHARACTERISTICS FOR CRYSTAL INPUT, CLKOUT, BUFXTAL, AND FREQREF | 10–32      |

| 10.15              | SWITCHING CHARACTERISTICS FOR BAUD CLOCKS                                 | 10–33      |

|                    | SECTION 11                                                                |            |

|                    | MECHANICAL DATA                                                           |            |

| 11.1               | PIN ASSIGNMENTS                                                           | 11–1       |

| 11.2               | PACKAGE DIMENSIONS                                                        | 11–3       |

|                    |                                                                           |            |

|                    | APPENDIX A<br>MC145572EVK ISDN U-INTERFACE TRANSCEIVER EVALUATION KIT     |            |

|                    |                                                                           |            |

| A.1                | INTRODUCTION                                                              | A-1        |

| A.2                | FEATURES                                                                  | A-2        |

| A.2.1              | General                                                                   | A-2        |

| A.2.2<br>A.2.3     | HardwareSoftware                                                          | A-2<br>A-3 |

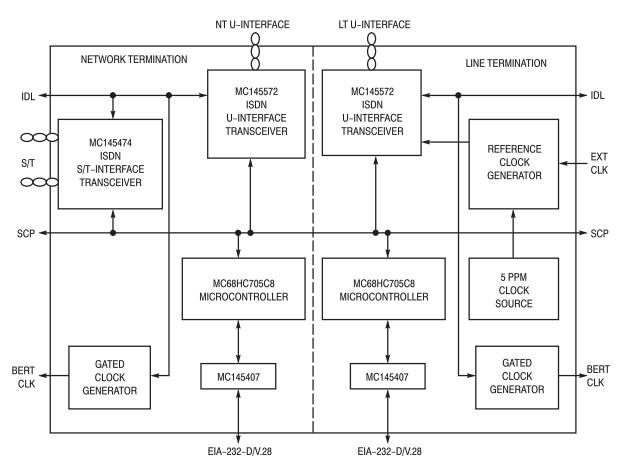

| A.2.3<br>A.3       | BLOCK DIAGRAM                                                             | A-3<br>A-3 |

| A.3                | BLOCK DIAGRAM                                                             | A-3        |

|                    | APPENDIX B                                                                |            |

|                    | COMPONENT SOURCING                                                        |            |

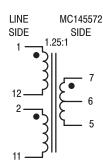

| B.1                | TRANSFORMER SOURCES                                                       | B-1        |

| B.2                | 2B1Q INTERFACE TRANSFORMER SPECIFICATION                                  | B-1        |

| B.3                | MC145572 CRYSTAL SPECIFICATION                                            | B-2        |

| B.3.1              | Pullable Crystal Specification for ISDN and Network Applications          | B-3        |

| B.4                | CRYSTAL SOURCES                                                           | B-3        |

| B.5                | ISDN CALL CONTROL SOURCE CODE SUPPLIERS                                   | B-4        |

## Freescale Semiconductor, Inc. TABLE OF CONTENTS (concluded)

### •

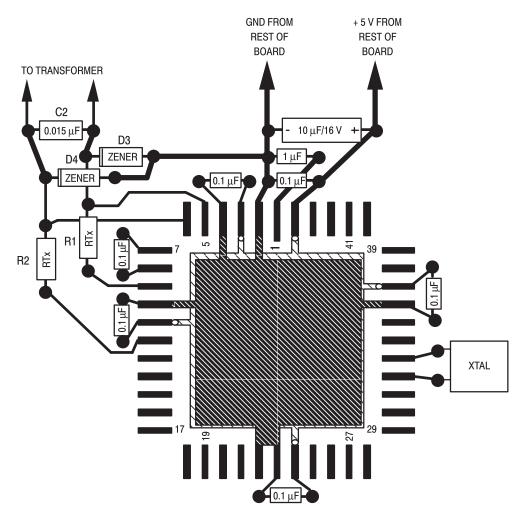

## APPENDIX C PRINTED CIRCUIT BOARD LAYOUT

| C.1        | INTRODUCTION                                        | C-1        |

|------------|-----------------------------------------------------|------------|

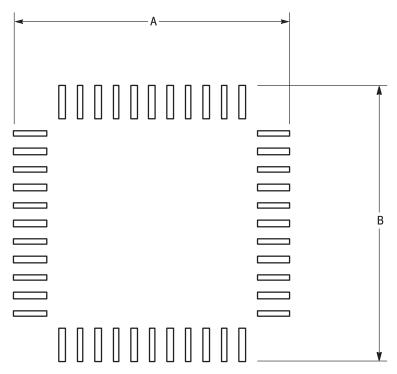

| C.2        | PRINTED CIRCUIT BOARD MOUNTING                      | C-1        |

| C.3        | POWER SUPPLY, GROUND, AND NOISE CONSIDERATIONS      | C-1        |

| C.4        | OSCILLATOR LAYOUT GUIDELINES                        | C-2        |

| C.5        | 2B1Q INTERFACE GUIDELINES                           | C-2        |

| C.6        | PACKAGE FOOTPRINTS FOR PRINTED CIRCUIT BOARDS       | C-4        |

|            | APPENDIX D EYE PATTERN GENERATOR                    |            |

| D.4        | INTRODUCTION                                        | D 4        |

| D.1        | DISCUSSION                                          | D-1<br>D-1 |

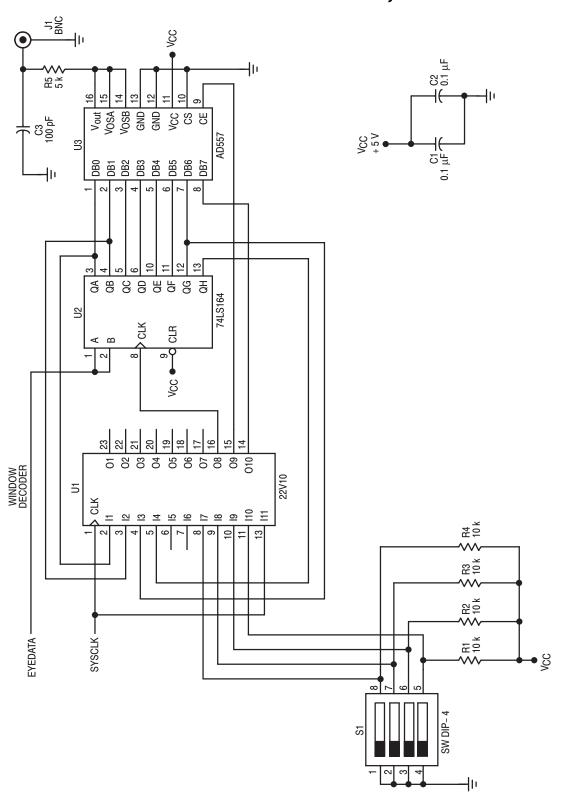

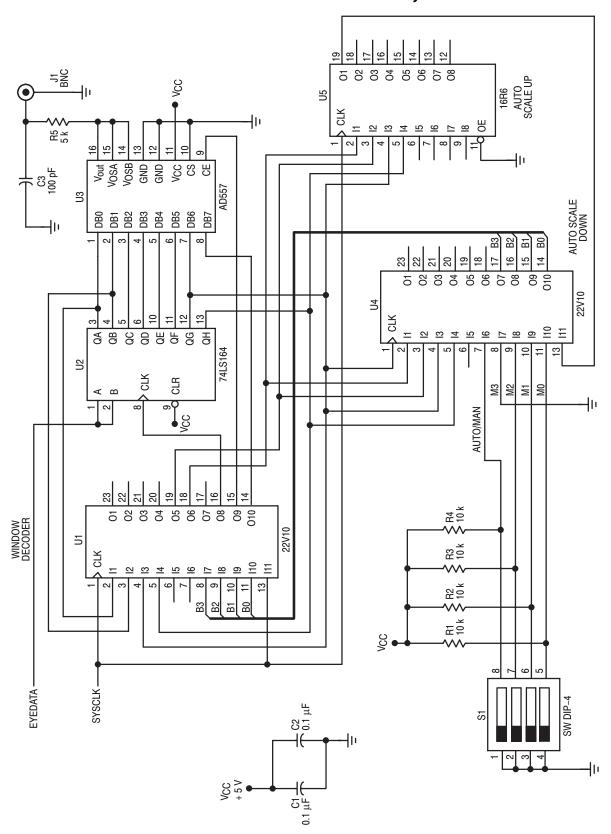

| D.2<br>D.3 | WINDOW DECODER LOGIC EQUATIONS                      | D-1<br>D-5 |

| D.3<br>D.4 | AUTOMATIC SCALE UP COUNTER LOGIC EQUATIONS          | D-5<br>D-6 |

| D.4<br>D.5 | AUTOMATIC SCALE OF COUNTER LOGIC EQUATIONS          | D-6<br>D-7 |

| ט.ט        | AUTOMATIC SCALE DOWN COUNTER LOGIC EQUATIONS        | D-7        |

|            | APPENDIX E                                          |            |

|            | LINE INTERFACE CIRCUIT COMPONENT VALUE CALCULATIONS |            |

| E.1        | INTRODUCTION                                        | E-1        |

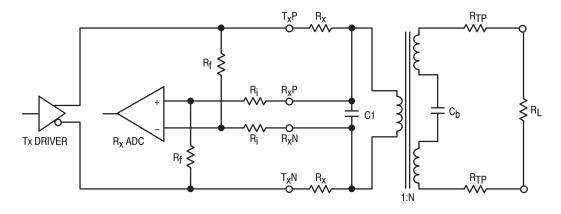

| E.2        | CALCULATION OF TRANSMIT SERIES RESISTORS            | E-1        |

| E.3        | CALCULATION OF TRANSMIT NOISE FILTER CAPACITOR      | E-3        |

| E.4        | 2B1Q LINE INTERFACE                                 | E-4        |

|            | APPENDIX F                                          |            |

|            | APPLICATIONS                                        |            |

| F.1        | INTRODUCTION                                        | F-1        |

|            | ADDENDIV C                                          |            |

|            | APPENDIX G<br>PERFORMANCE                           |            |

| G.1        | INTRODUCTION                                        | G-1        |

|            |                                                     |            |

|            | APPENDIX H TEST AND DEBUG                           |            |

| H.1        | HIGH-IMPEDANCE DIGITAL OUTPUT MODE                  | H–1        |

| H.2        | CONTROL OF TRANSMIT SIGNALS                         | H_1        |

| H.3        | CHARACTERIZATION OF THE PULLABLE CRYSTAL            | H–1        |

| 11.0       | OF MORE THE POLENDEL ON TOTAL                       |            |

|            |                                                     |            |

## APPENDIX I GLOSSARY OF TERMS AND ABBREVIATIONS

#### APPENDIX J STANDARDS BODIES

## **LIST OF FIGURES**

| Figure       | Title                                                            | Page |

|--------------|------------------------------------------------------------------|------|

| Figure 2–1.  | ISDN Reference Model                                             | 2–1  |

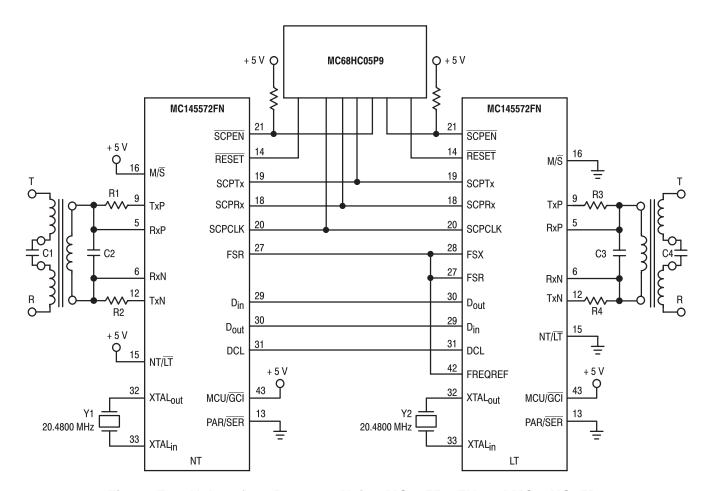

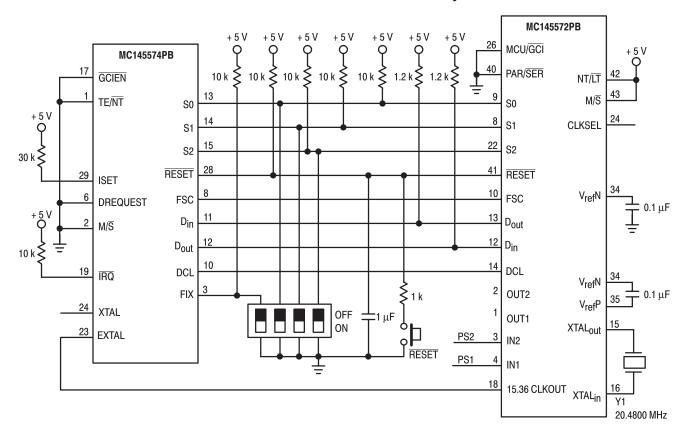

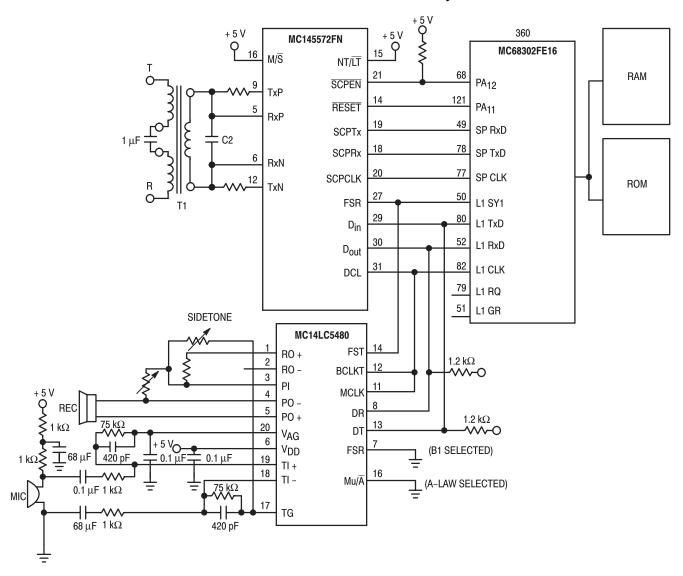

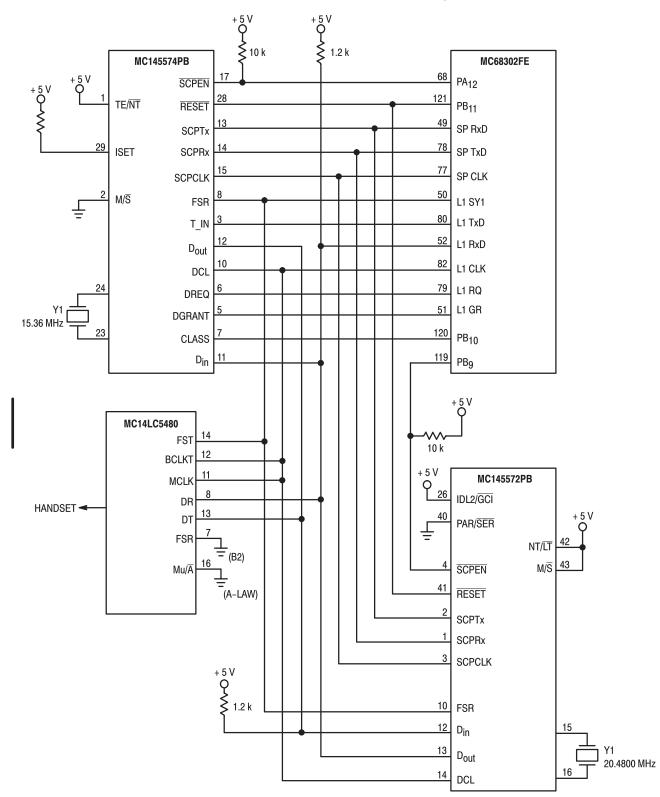

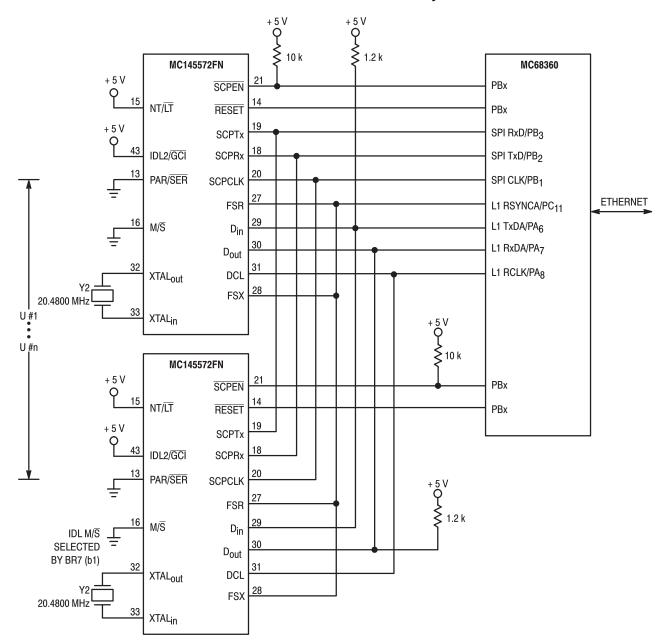

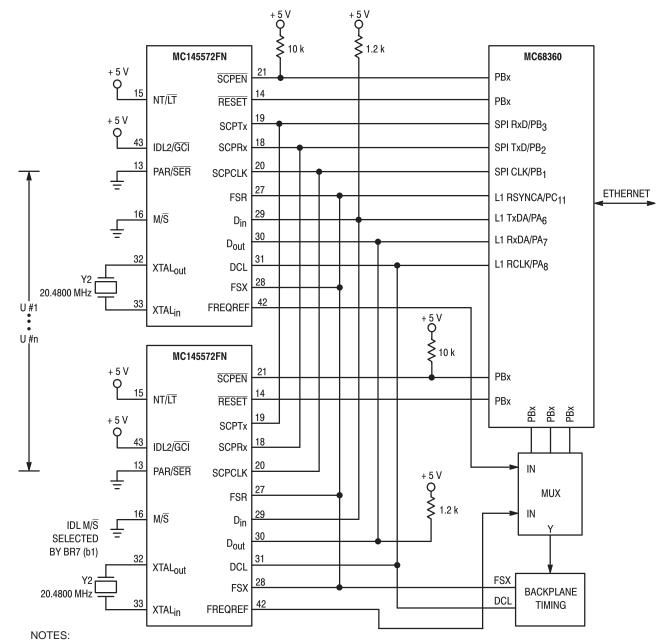

| Figure 2–2.  | MC145572 Typical ISDN Applications                               | 2-2  |

| Figure 2–3.  | Pair Gain Application, Central Office Terminal                   | 2–3  |

| Figure 2–4.  | Pair Gain Application, Remote Terminal                           | 2-3  |

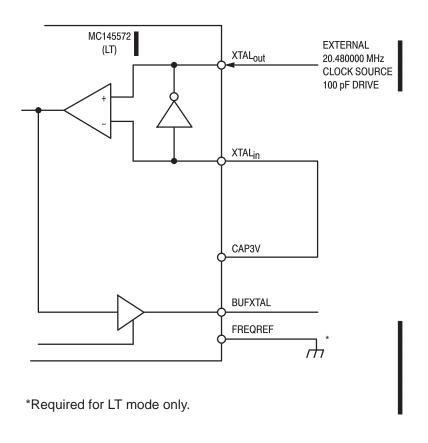

| Figure 3–1.  | Method to Drive MC145572 with External Clock                     | 3–13 |

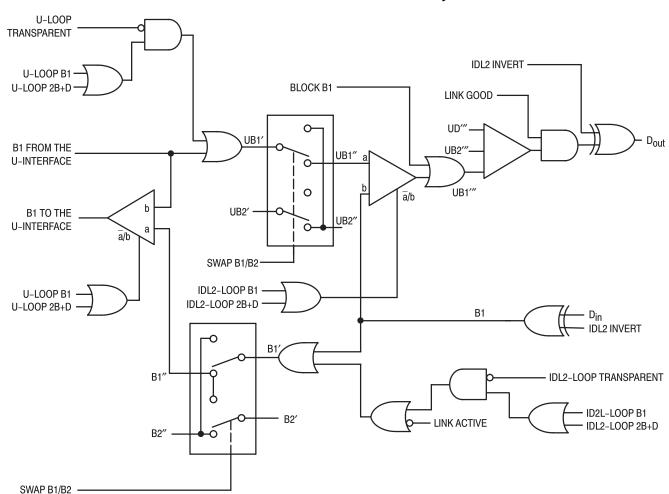

| Figure 4–1.  | IDL2 Interface Loopback Control Bits                             | 4–16 |

| Figure 4–2.  | IDL2 Interface Loopback Logic Diagram                            | 4–17 |

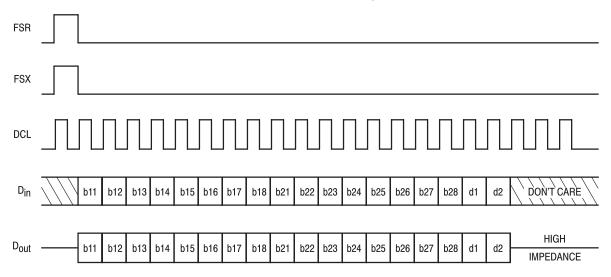

| Figure 4–3.  | IDL2 Interface Timing in 8–Bit Master Mode                       | 4–19 |

| Figure 4–4.  | IDL2 Interface Timing in 10-Bit Master Mode                      | 4–19 |

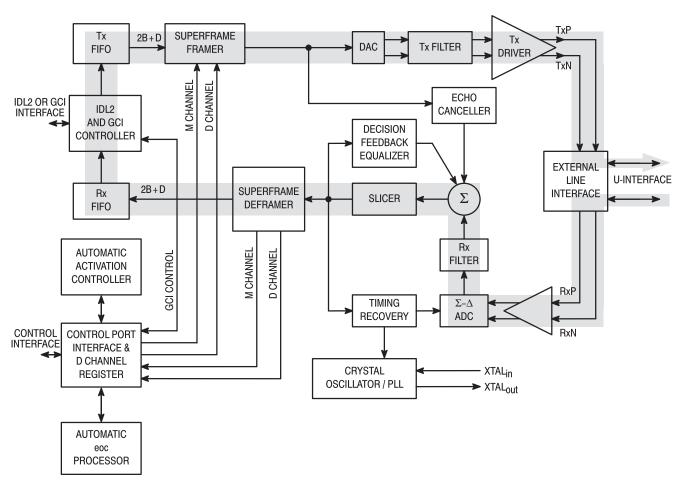

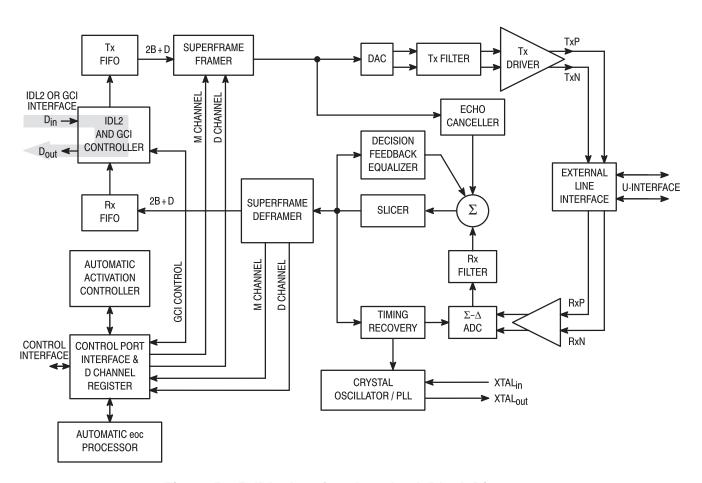

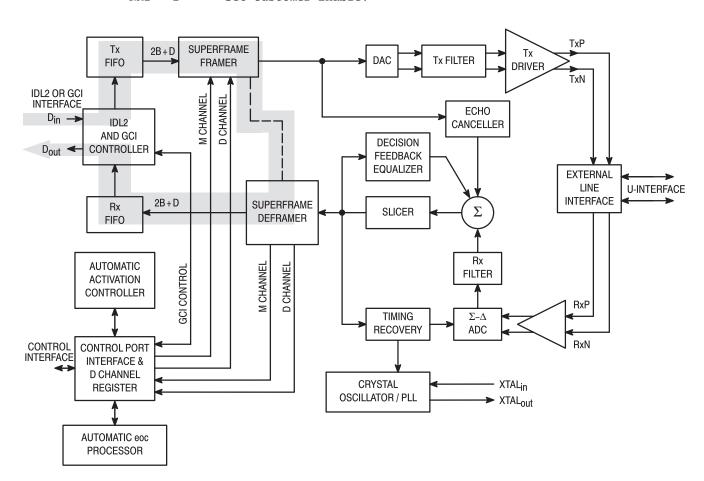

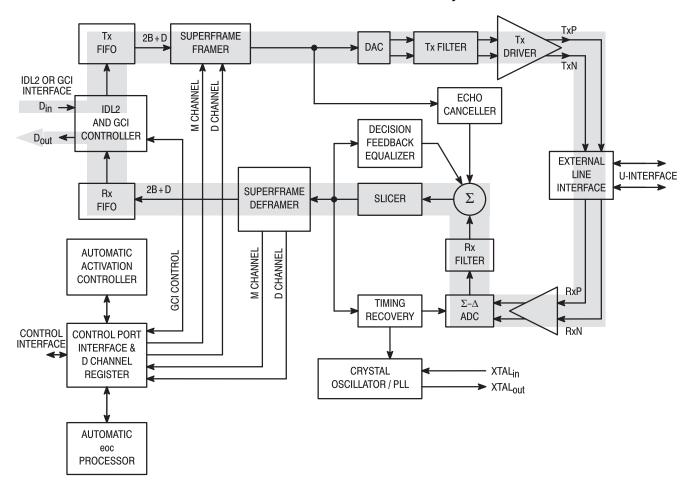

| Figure 5–1.  | MC145572 Functional Block Diagram                                | 5–1  |

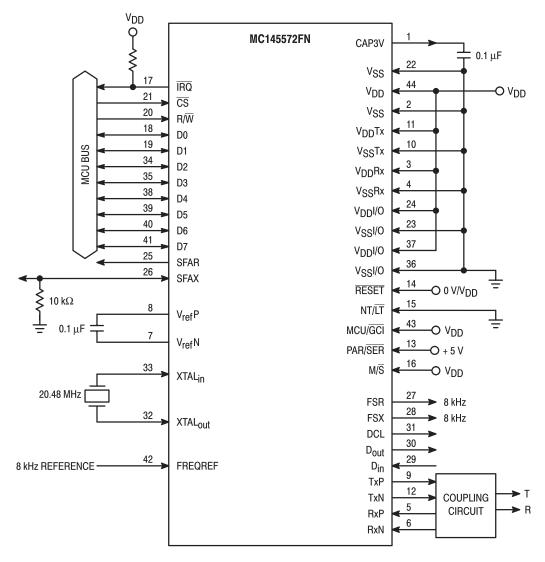

| Figure 5–2.  | MCU Mode with SCP Configuration                                  | 5–5  |

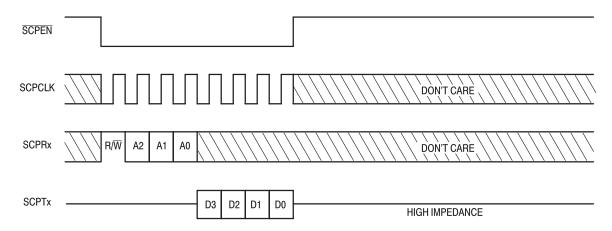

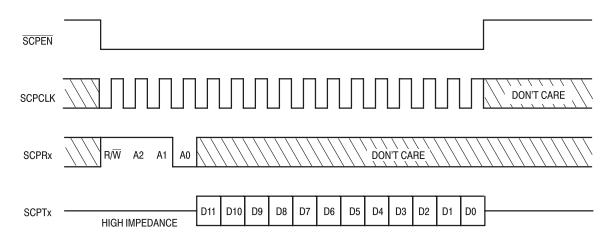

| Figure 5–3.  | SCP Nibble Registers 0 - 5, Write Operation                      | 5–6  |

| Figure 5–4.  | SCP Nibble Registers 0 - 5, Read Operation                       | 5–6  |

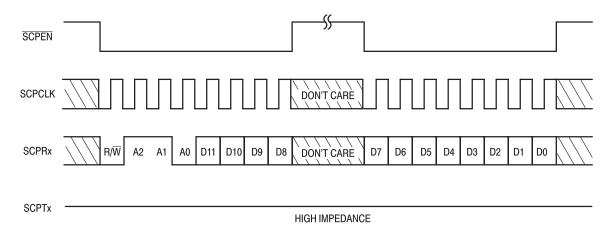

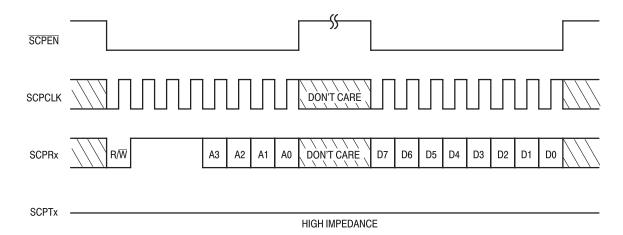

| Figure 5–5.  | SCP eoc Register R6 Write Operation Using Double 8–Bit Transfer  | 5–7  |

| Figure 5–6.  | SCP eoc Register R6 Read Operation Using Double 8–Bit Transfer   | 5–7  |

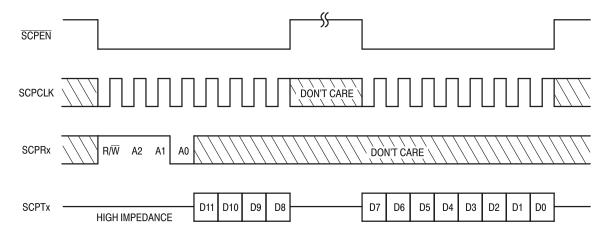

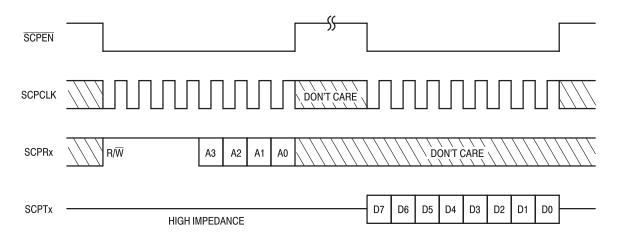

| Figure 5–7.  | SCP eoc Register R6 Write Operation Using Single 16–Bit Transfer | 5–8  |

| Figure 5–8.  | SCP eoc Register R6 Read Operation Using Single 16–Bit Transfer  | 5–8  |

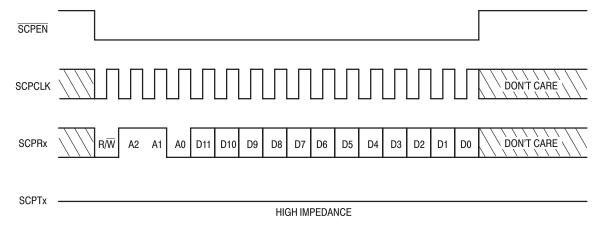

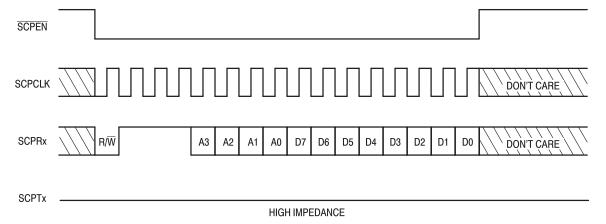

| Figure 5–9.  | SCP Byte Register Write Operation Using Double 8–Bit Transfer    | 5–9  |

| Figure 5–10. | SCP Byte Register Read Operation Using Double 8–Bit Transfer     | 5–9  |

| Figure 5–11. | SCP Byte Register Write Operation Using Single 16–Bit Transfer   | 5–10 |

| Figure 5–12. | SCP Byte Register Read Operation Using Single 16–Bit Transfer    | 5–10 |

| Figure 5–13. | MCU Mode with PCP Configuration                                  | 5–11 |

| Figure 5–14. | PCP Mode Nibble Register Write and Read Operations               | 5–12 |

| Figure 5–15. | PCP Register R6 Write and Read Operations                        | 5–13 |

| Figure 5–16. | PCP Byte Register Write Operation                                | 5–14 |

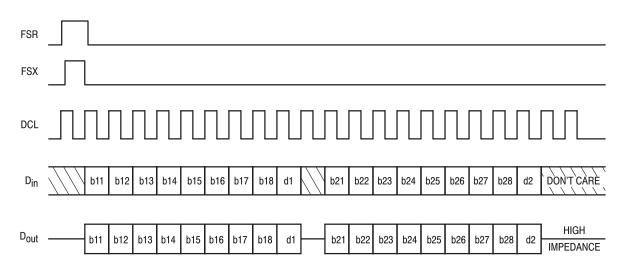

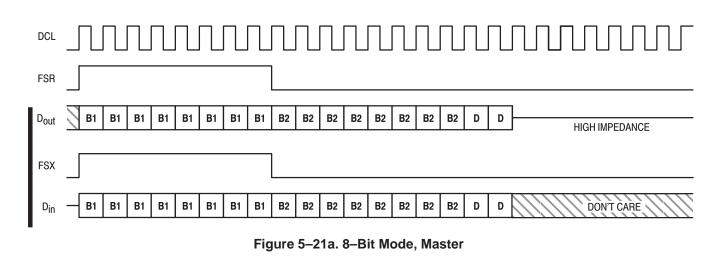

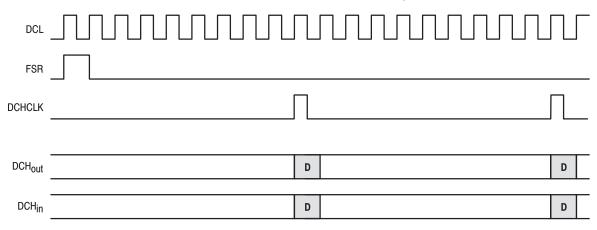

| Figure 5–17. | IDL2 Interface Timing in Short Frame Master Mode, 8–Bit Frames   | 5–16 |

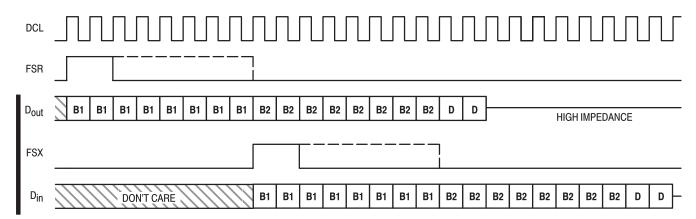

| Figure 5–18. | IDL2 Interface Timing in Short Frame Master Mode, 10–Bit Frames  | 5–16 |

| Figure 5–19. | IDL2 Interface Timing in Short Frame Slave Mode, 8–Bit Frames    | 5–17 |

| Figure 5–20. | IDL2 Interface Timing in Short Frame Slave Mode, 10-Bit Frames   | 5–17 |

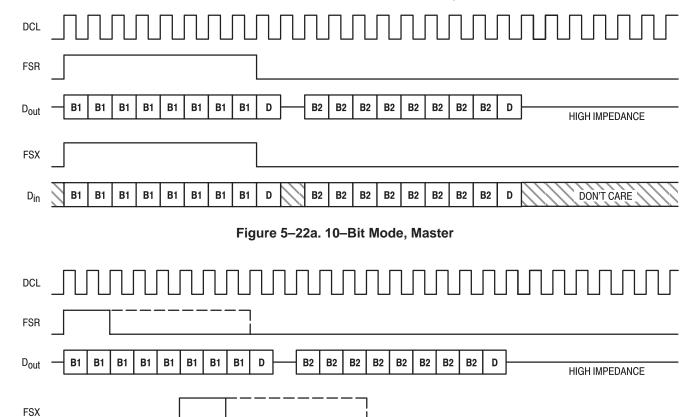

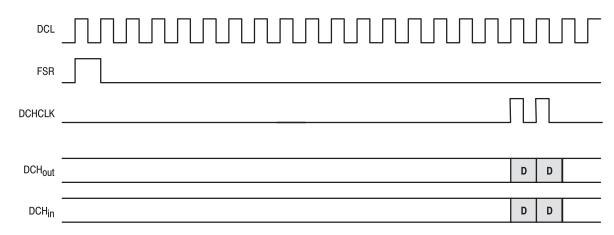

| Figure 5–21. | IDL2 Interface Timing in Long Frame, 8–Bit Frames                | 5–18 |

| Figure 5–22. | IDL2 Interface Timing in Long Frame, 10–Bit Frames               | 5–19 |

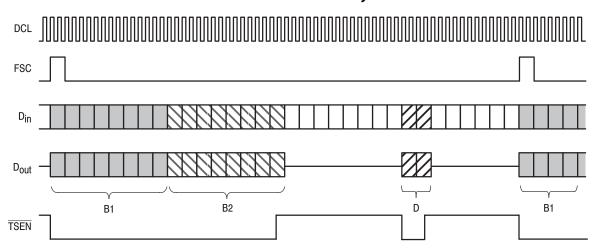

| Figure 5–23. | IDL2 GCI 2B+D Data Formats                                       | 5-20 |

| Figure 5–24. | D Channel Port Timing, IDL2 10-Bit Frames                        | 5–21 |

| Figure 5–25. | D Channel Port Timing, IDL2 8–Bit Frames                         | 5-21 |

| Figure 5–26. | D Channel Port Timing, IDL2 GCI 2B+D Frames                      | 5–21 |

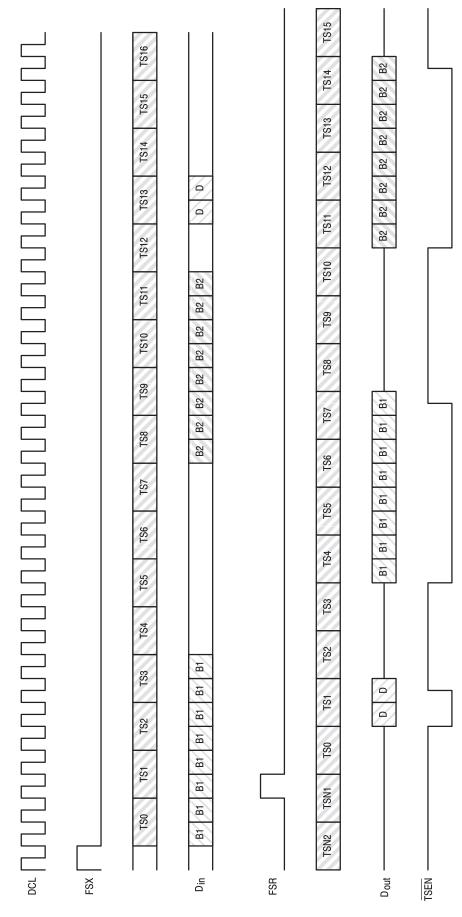

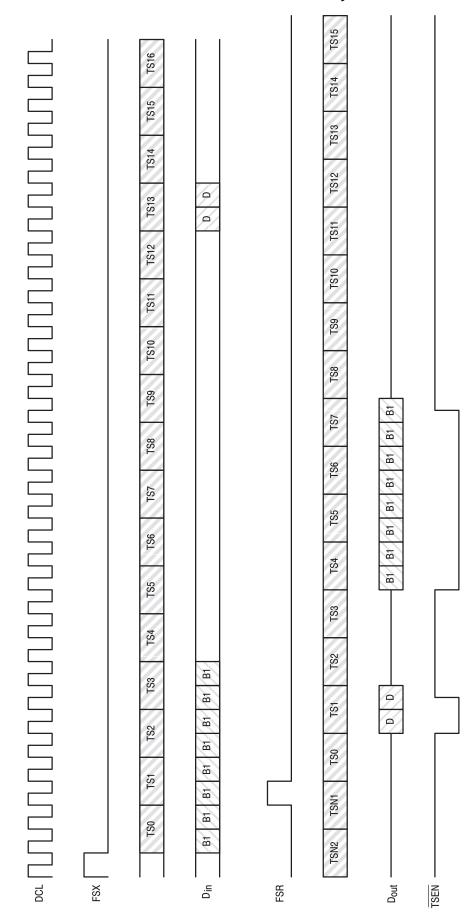

| Figure 5–27. | Timeslot Assigner Data Format Example                            | 5-23 |

| Figure 5–28. | Timeslot Assigner Data Format Example, B2 Channel Not Enabled    | 5–24 |

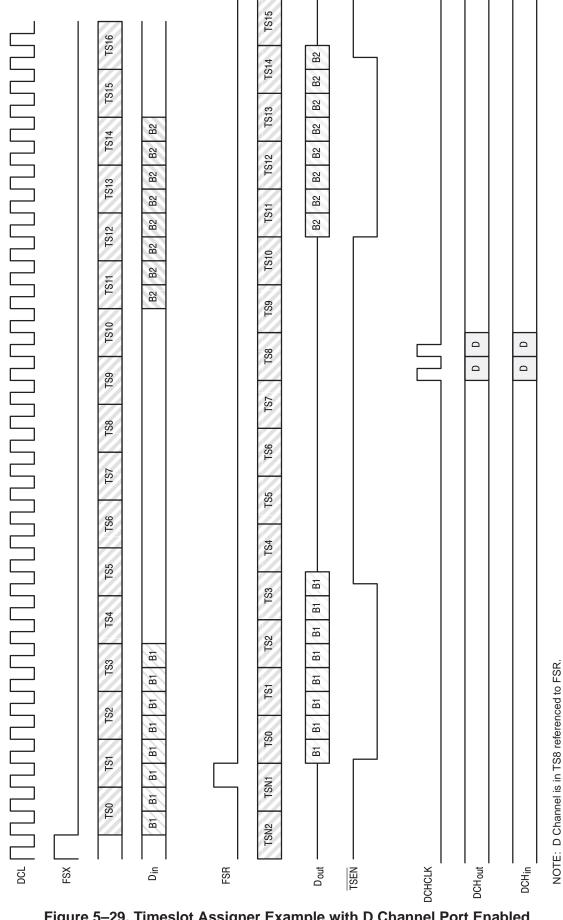

| Figure 5–29. | Timeslot Assigner Example with D Channel Port Enabled            | 5–25 |

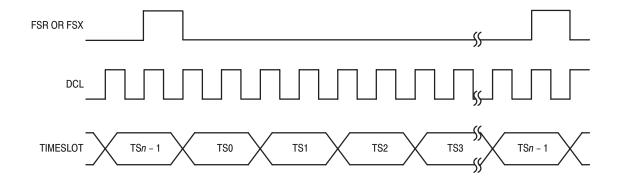

| Figure 5–30. | Timeslot Numbering                                               | 5–26 |

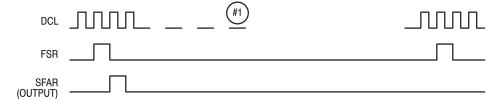

| Figure 5–31. | SFAR Timing                                                      | 5–28 |

| Figure 5–32. | SFAX Timing                                                      | 5–28 |

| Figure 5–33. | IDL2 GCI 2B+D Format Superframe Alignment Signal                 | 5-29 |

| Figure 5–34. | U-Interface Loopback Block Diagram                               | 5-31 |

| Figure 5–35. | IDL2 Interface Loopback Block Diagram                            | 5-32 |

| Figure 5–36. | Superframe Framer-to-Deframer Loopback Block Diagram             | 5–33 |

## **LIST OF FIGURES (Continued)**

| Figure        | Title                                                                                                          | Page  |

|---------------|----------------------------------------------------------------------------------------------------------------|-------|

| Figure 5–37.  | External Analog Loopback Block Diagram                                                                         | 5-36  |

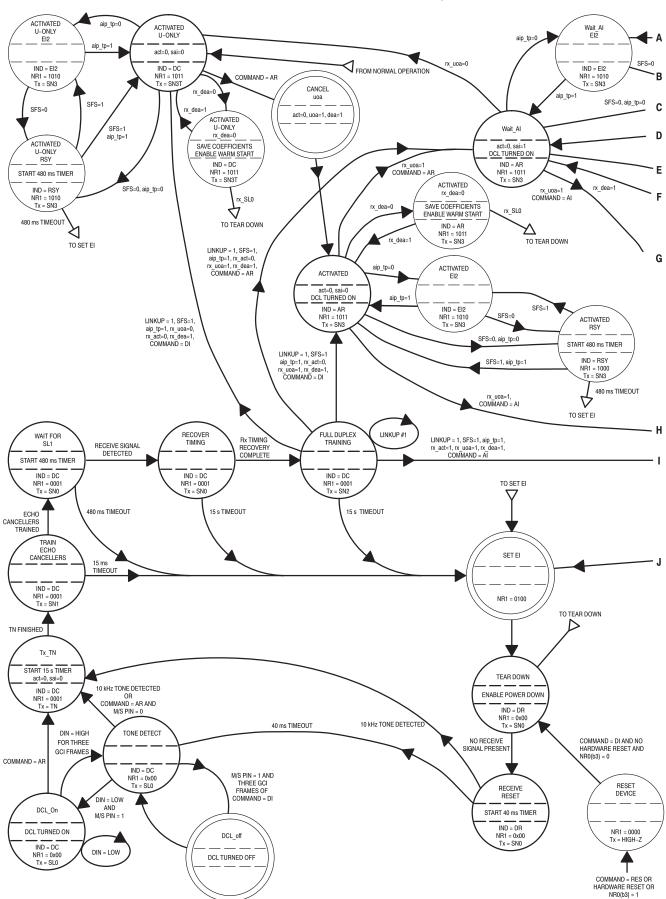

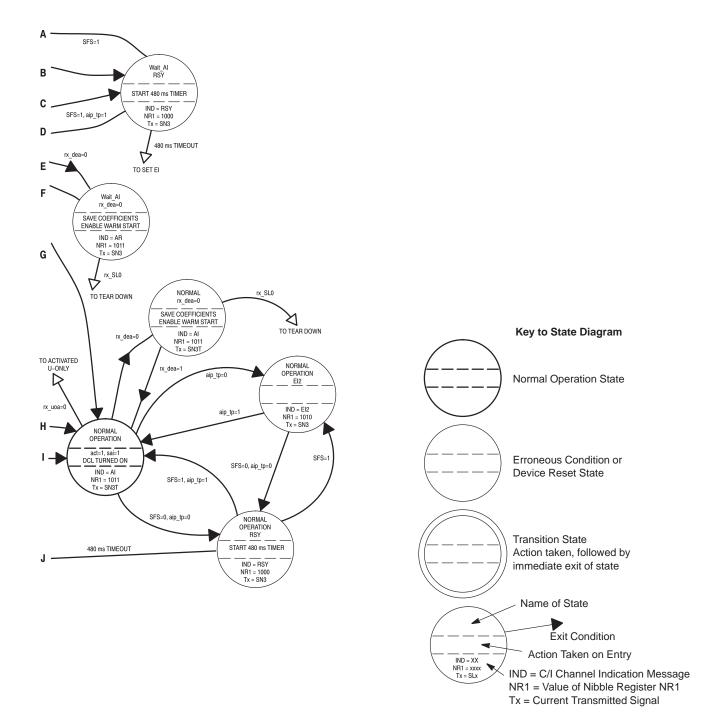

| Figure 6–1.   | ANSI U-Interface Transceiver Activation State Diagram                                                          | 6–2   |

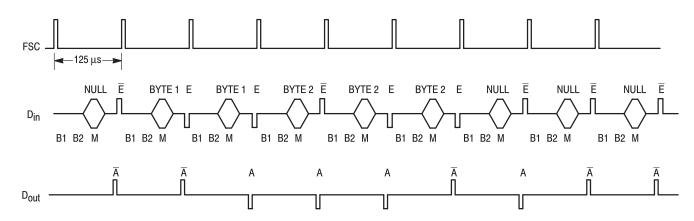

| Figure 7–1.   | Maintenance Channel Interrupt Timing                                                                           | 7–1   |

| Figure 7–2.   | NT Mode Maintenance Channel Updates                                                                            | 7–5   |

| Figure 7–3.   | LT Mode Maintenance Channel Updates                                                                            | 7–6   |

| Figure 8–1.   | MC145572 Configuration for GCI Operation                                                                       | 8–2   |

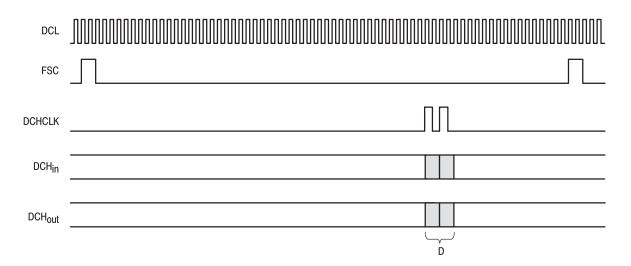

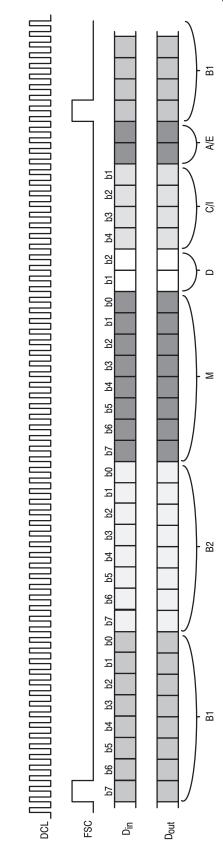

| Figure 8–2.   | Single Channel GCI Format                                                                                      | 8–4   |

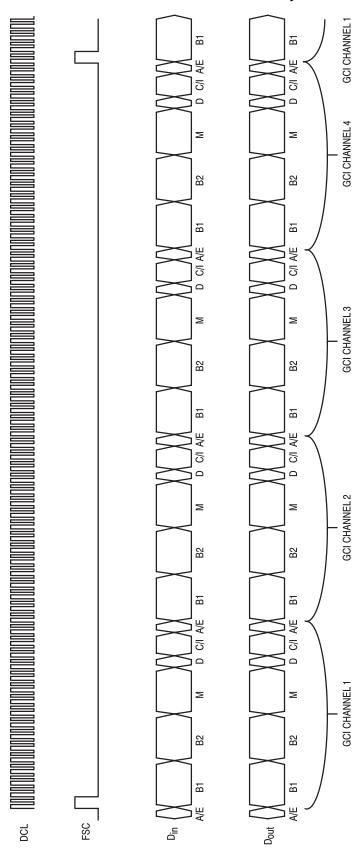

| Figure 8–3.   | Multiplexed GCI Format Example                                                                                 | 8–5   |

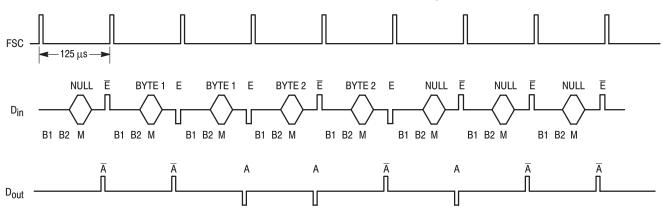

| Figure 8-4.   | Monitor Channel Access Protocol                                                                                | 8–7   |

| Figure 8–5.   | Monitor Channel Protocol with Delay                                                                            | 8–7   |

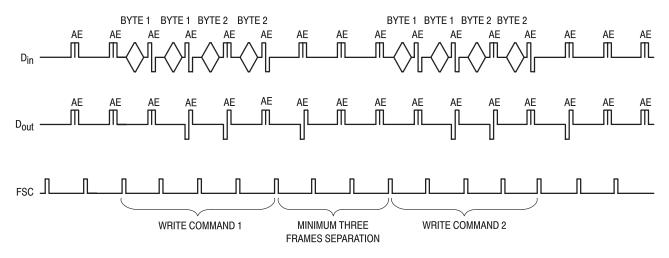

| Figure 8–6.   | Monitor Channel Register Write Sequence                                                                        | 8–7   |

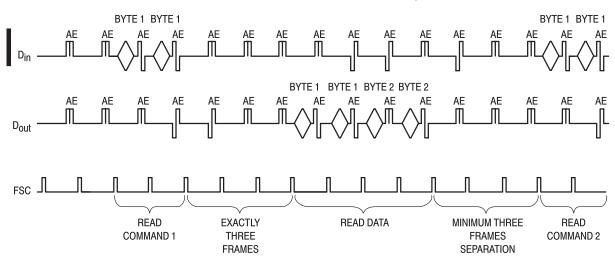

| Figure 8–7.   | Monitor Channel Register Read Sequence                                                                         | 8–8   |

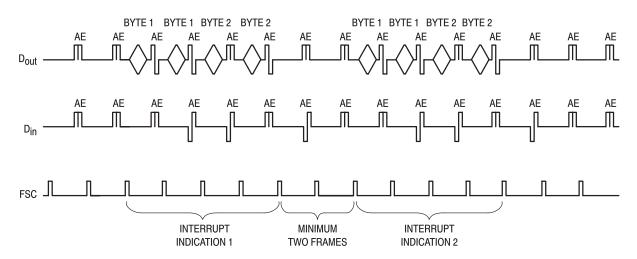

| Figure 8–8.   | Monitor Channel Multiple Interrupt Indications Sequence                                                        | 8–8   |

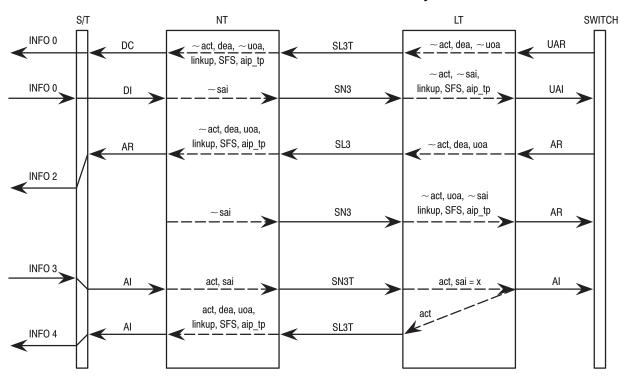

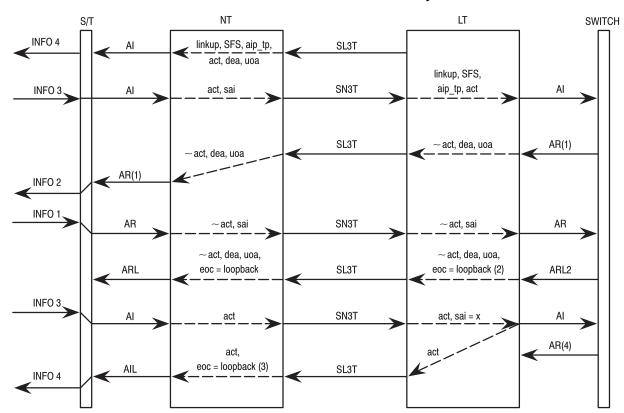

| Figure 8–9.   | Time Diagram for Total Activation Initiated by the Network                                                     | 8–12  |

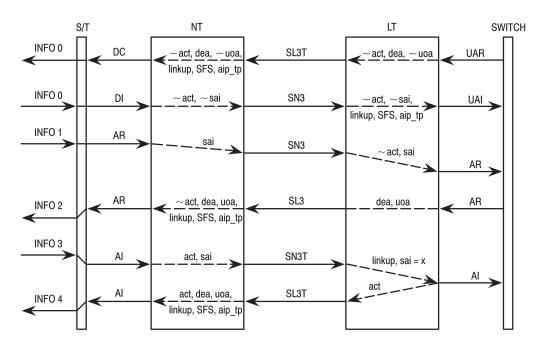

| Figure 8–10.  | Time Diagram for Total Activation Initiated by the Terminal Equipment                                          | 8–13  |

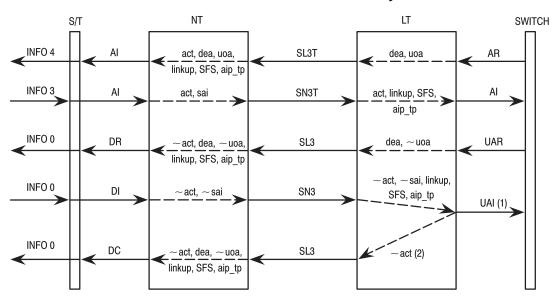

| Figure 8–11.  | Time Diagram for Deactivation (Always Initiated by the Network)                                                | 8–14  |

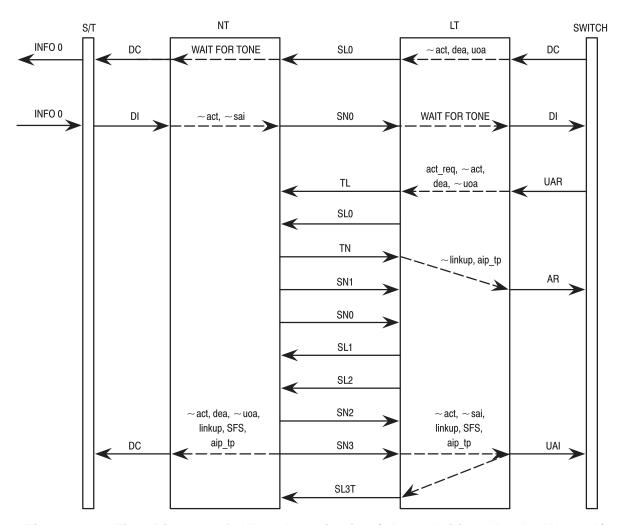

| Figure 8–12.  | Time Diagram of a U–Only Activation (Always Initiated by the Network)                                          | 8–14  |

| Figure 8–13.  | Time Diagram for a Transition from DSL–Only Activation to Total Activation Initiated by the Network            | 8–15  |

| Figure 8–14.  | Time Diagram for a Transition from DSL–Only Activation to Total Activation Initiated by the Terminal Equipment | 8–15  |

| Figure 8–15.  | Time Diagram for a Transition from Total Activation to DSL–Only Activation (Always Initiated by the Network)   | 8–16  |

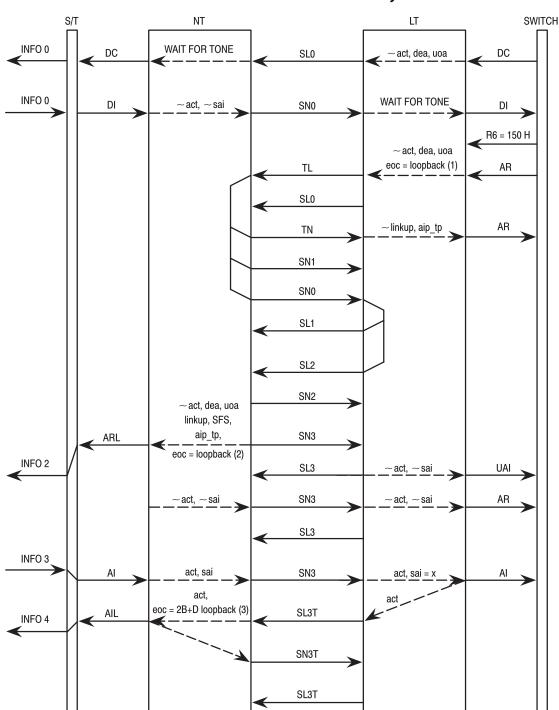

| Figure 8–16.  | Time Diagram for Activation with Loopback 2 (Always Initiated by the Network)                                  | 8–17  |

| Figure 8–17.  | Time Diagram for Execution of Loopback 2 Once Link is Active (Always Initiated by the Network)                 | 8–18  |

| Figure 8–18.  | NT Mode GCI State Diagram                                                                                      | 8–20  |

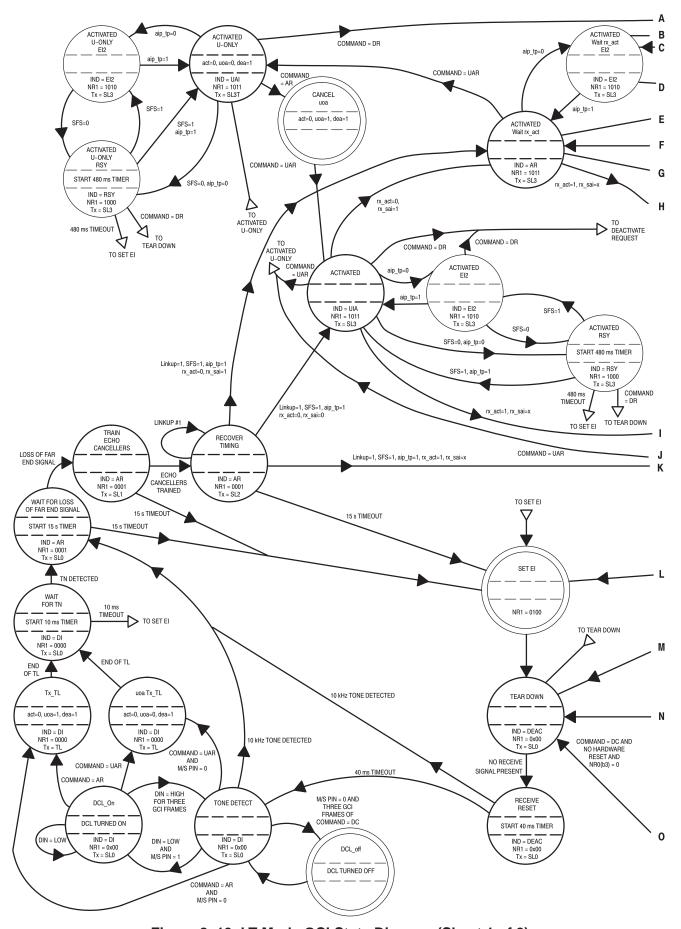

| Figure 8–19.  | LT Mode GCI State Diagram                                                                                      | 8–22  |

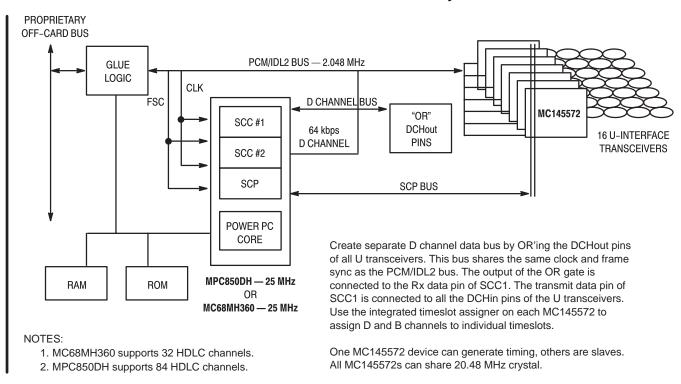

| Figure 9–1.   |                                                                                                                | 9–9   |

| Figure 9–2.   |                                                                                                                | 9–10  |

| Figure 9–3.   | Status Information Flow in a 4:1 Pair–Gain Application                                                         | 9–13  |

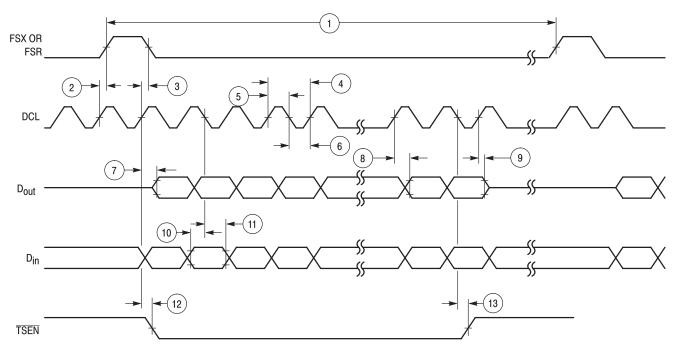

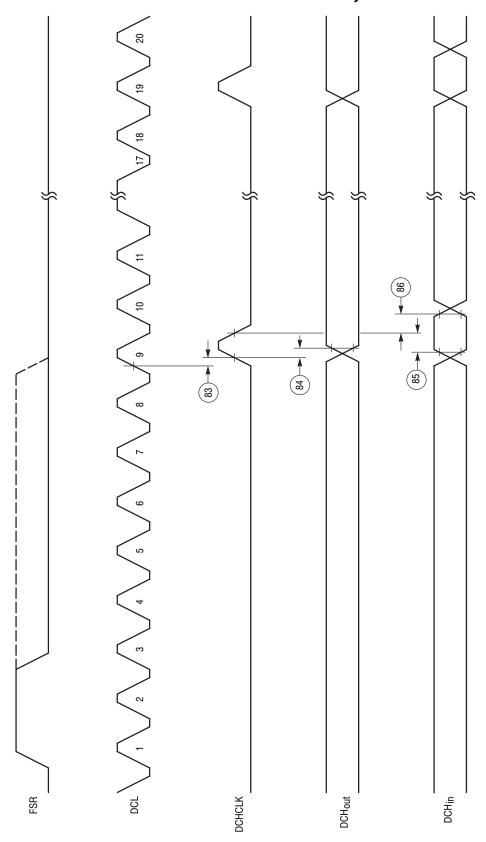

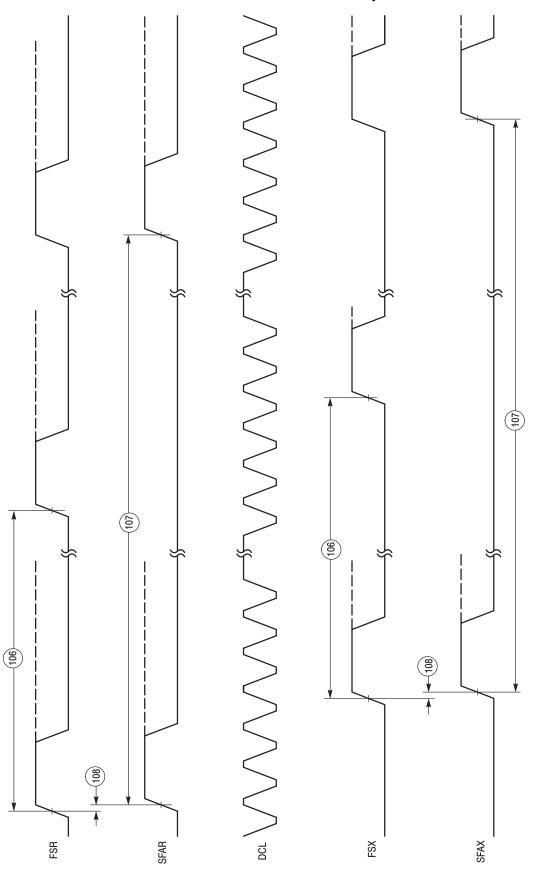

| Figure 10–1.  | IDL Short Frame Sync Master Timing, 8– and 10–Bit Formats and TSAC Formats                                     | 10–4  |

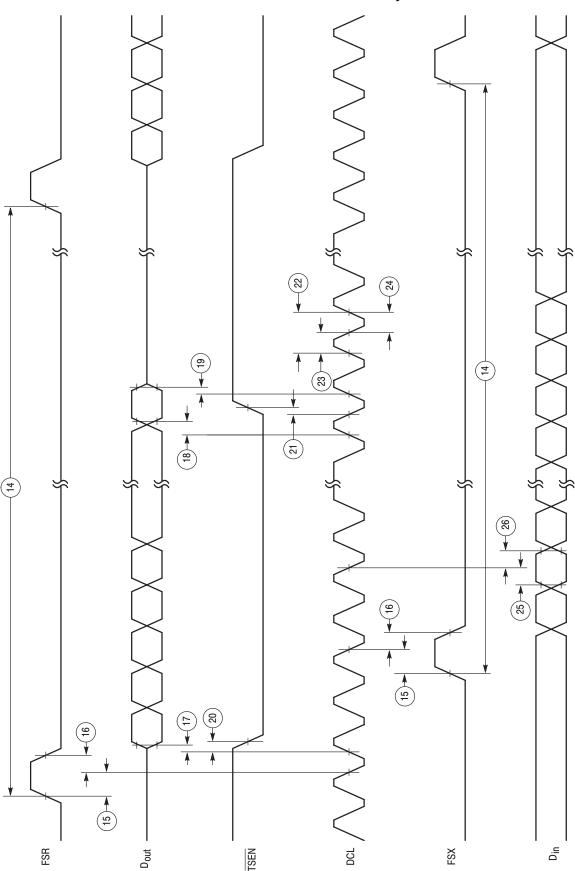

| Figure 10–2.  | IDL Short Frame Sync Slave Timing, 8– and 10–Bit Formats                                                       | 10–6  |

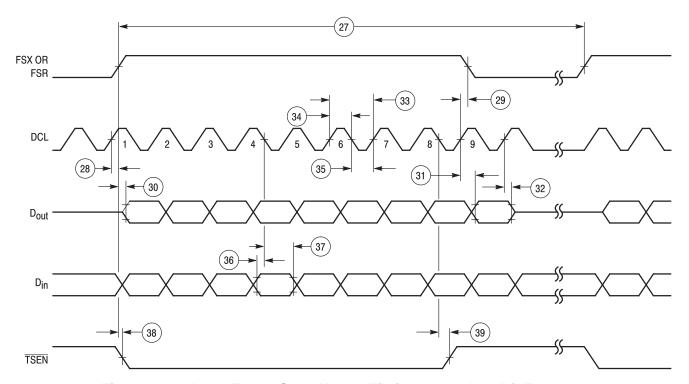

| Figure 10–3.  | Long Frame Sync Master Timing, 8– and 10–Bit Formats                                                           | 10–7  |

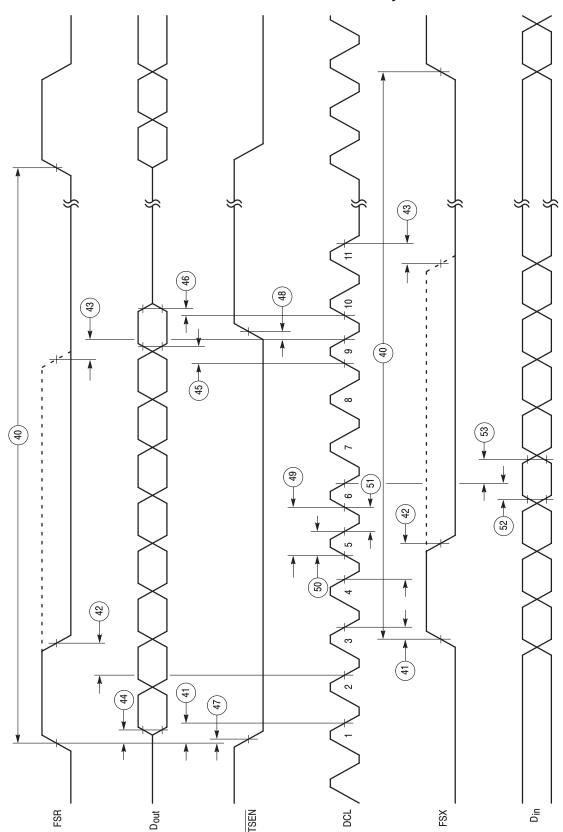

| Figure 10–4.  | Long Frame Sync Slave Timing, 8– and 10–Bit Formats                                                            | 10–9  |

| Figure 10–5.  | GCI Timing                                                                                                     | 10-11 |

| Figure 10-6.  | IDL2 (Master or Slave) Short Frame Sync 8–Bit Format, D Channel Port Timing                                    | 10-13 |

| Figure 10-7.  | IDL2 (Master or Slave) Short Frame Sync 10–Bit Format, D Channel Port Timing                                   | 10–15 |

| Figure 10–8.  | IDL2 (Master or Slave) Long Frame Sync 8–Bit Format, D Channel Port Timing                                     | 10–17 |

| Figure 10–9.  | IDL2 (Master or Slave) Long Frame Sync 10–Bit Format, D Channel Port Timing                                    | 10–19 |

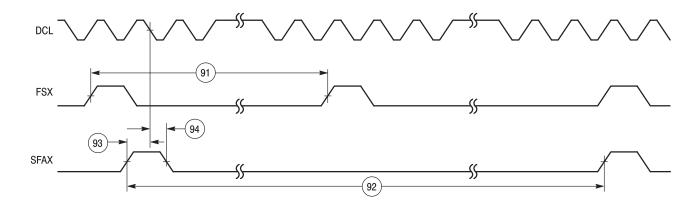

| Figure 10–10. | SFAX Input Timing in IDL2 (Master or Slave) Short Frame Mode                                                   | 10-20 |

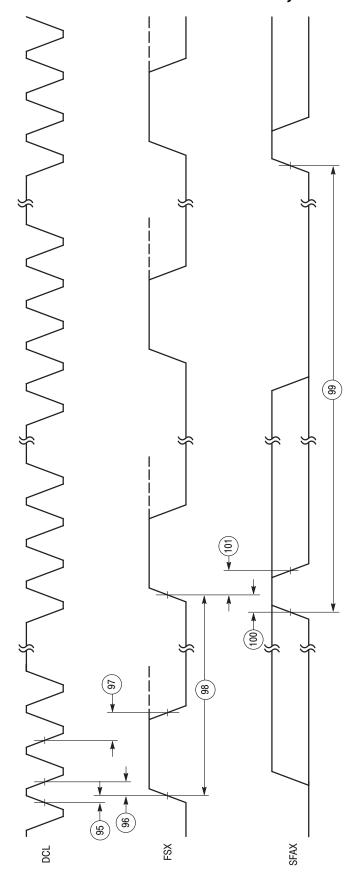

| Figure 10–11. | SFAX Input Timing in IDL2 (Master or Slave) Long Frame Mode                                                    | 10–22 |

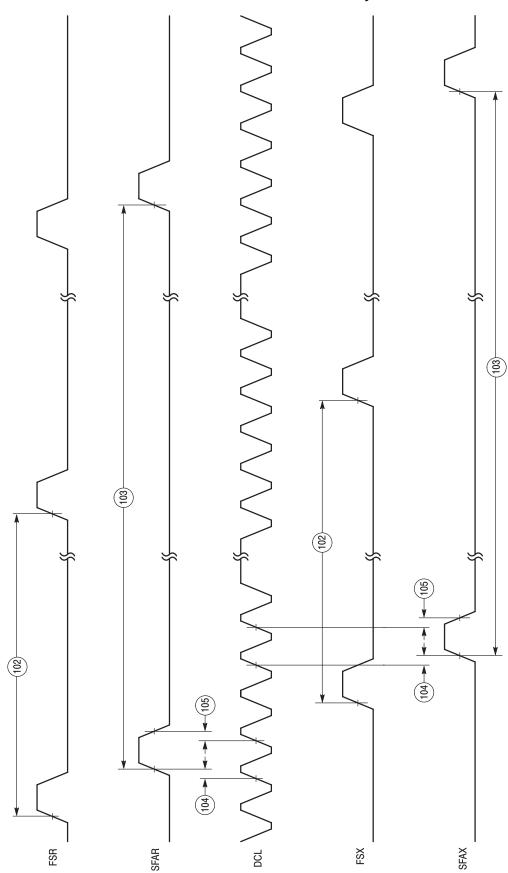

| Figure 10–12. | SFAX/SFAR Output Timing in IDL2 Short Frame Mode (Master or Slave)                                             | 10–24 |

| Figure 10–13. | SFAX/SFAR Output Timing in IDL2 Long Frame Mode (Master or Slave)                                              | 10–26 |

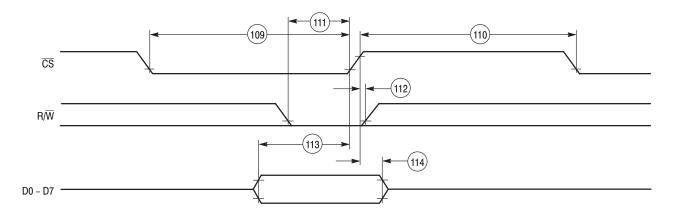

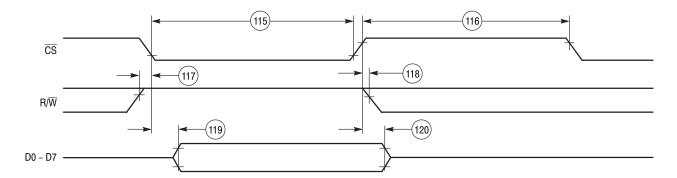

| Figure 10–14. | Parallel Control Port Write Timing                                                                             | 10–27 |

| Figure 10–15. | Parallel Control Port Read Timing                                                                              | 10–28 |

## **LIST OF FIGURES (Concluded)**

| Figure        | Title                                                                     | Page  |

|---------------|---------------------------------------------------------------------------|-------|

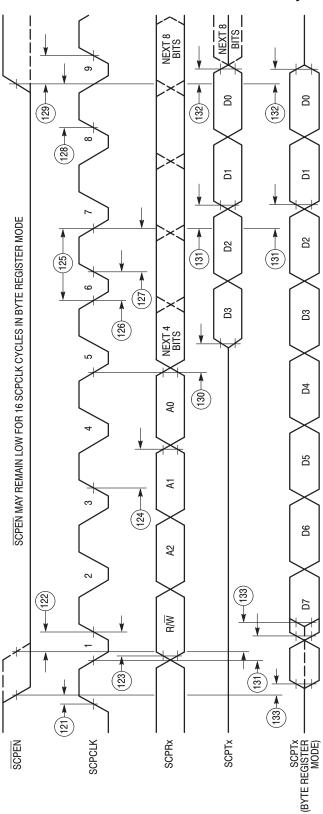

| Figure 10–16. | SCP Interface Timing                                                      | 10–30 |

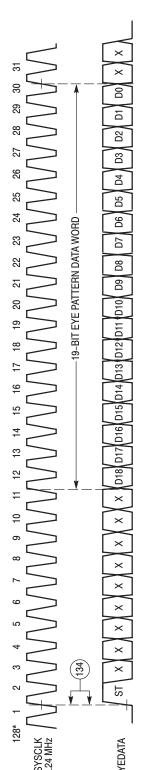

| Figure 10–17. | SYSCLK and EYEDATA Timing                                                 | 10-31 |

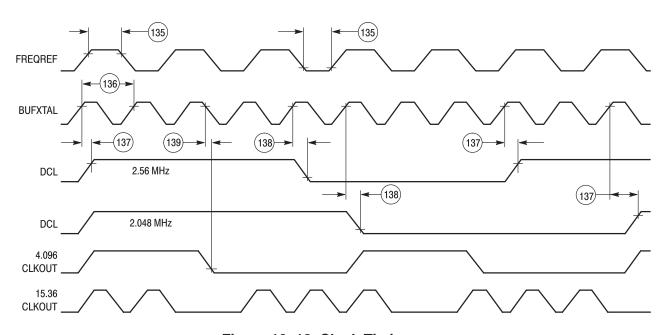

| Figure 10–18. | Clock Timing                                                              | 10-32 |

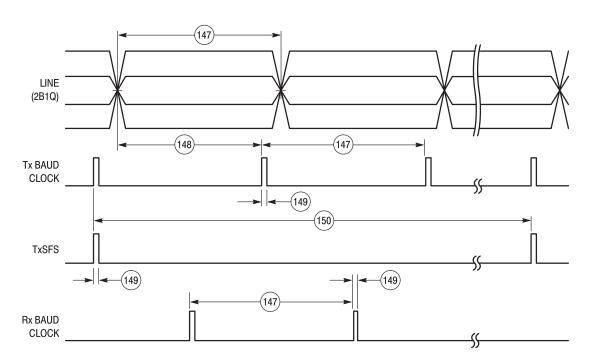

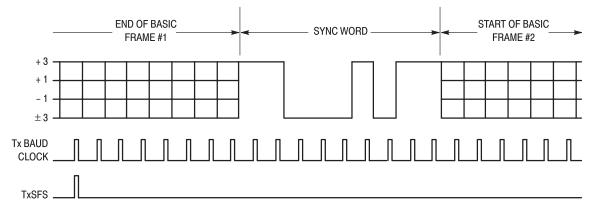

| Figure 10–19. | Baud Clock Timing                                                         | 10-33 |

| Figure 10–20. | Tx Superframe Sync Pulse Alignment                                        | 10-33 |

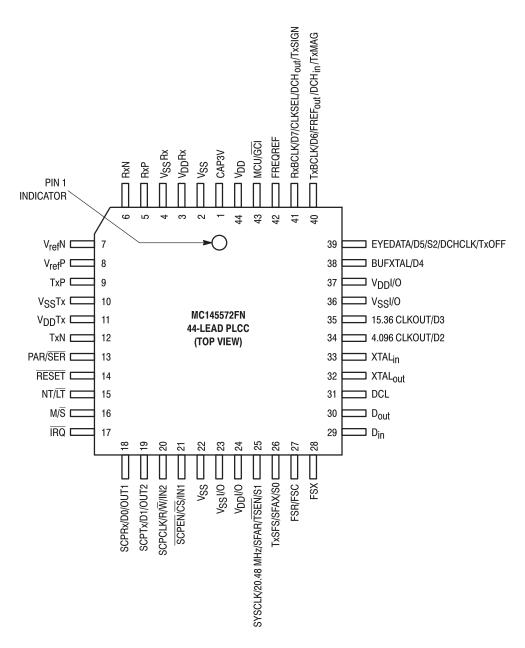

| Figure 11–1.  | MC145572FN Pin Assignment                                                 | 11–1  |

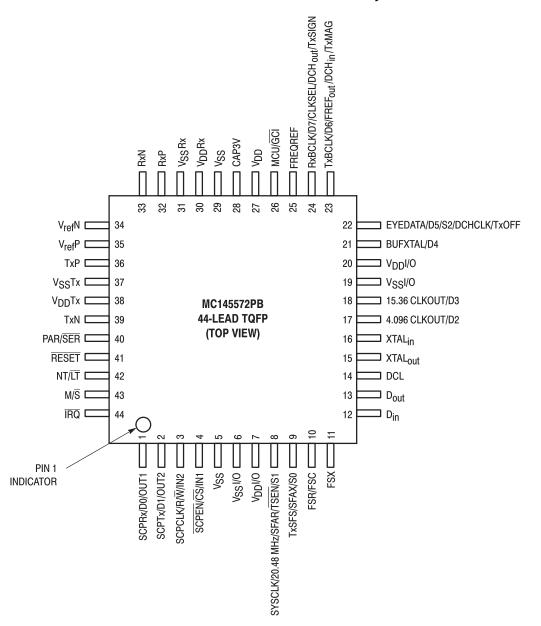

| Figure 11–2.  | MC145572PB Pin Assignment                                                 | 11–2  |

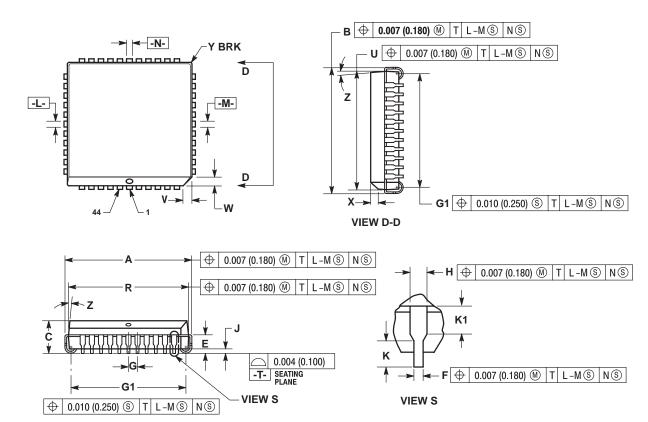

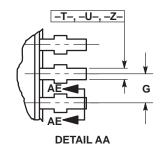

| Figure 11–3.  | MC145572FN Mechanical Outline                                             | 11–3  |

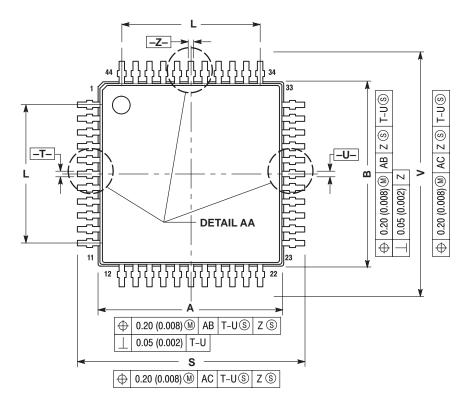

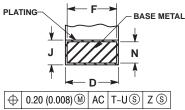

| Figure 11–4.  | MC145572PB Mechanical Outline                                             | 11–4  |

| Figure A-1.   | Motorola Silicon Applications and the MC145572EVK                         | A-2   |

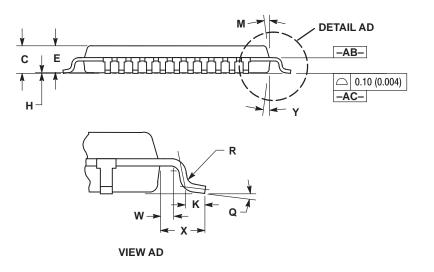

| Figure A–2.   | MC145572EVK Functional Block Diagram                                      | A-3   |

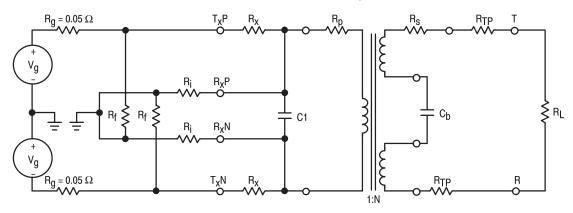

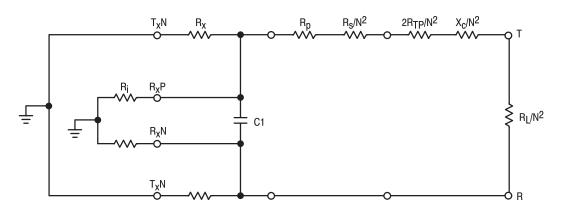

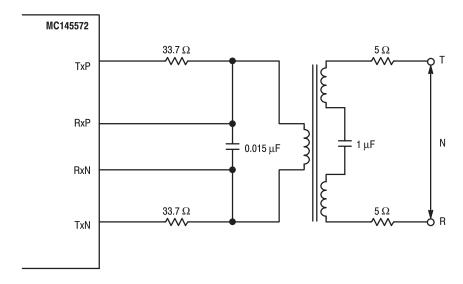

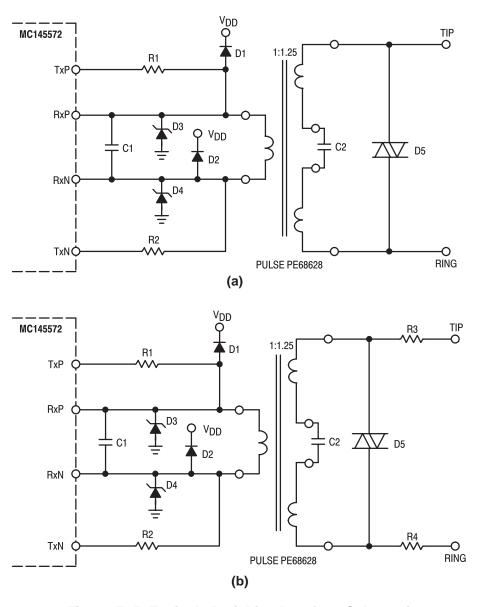

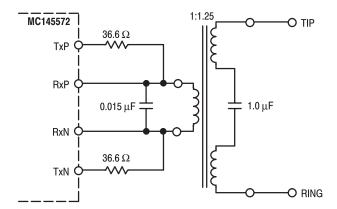

| Figure B-1.   | Schematic Reference for U–Interface Transformer                           | B-2   |

| Figure C-1.   | MC145572 Printed Circuit Board Footprint Dimensions                       | C-3   |

| Figure C–2.   | MC145572 Suggested PCB Layout                                             | C-4   |

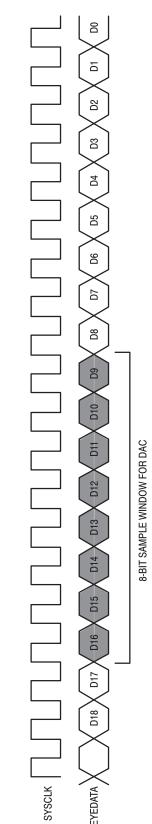

| Figure D-1.   | 8-Bit Sample Window Positioned Over Bits D16:D9                           | D-2   |

| Figure D–2.   | Manual Eye Pattern Decoder                                                | D-3   |