# SECTION 5 SYSTEM INTEGRATION MODULE

This section is an overview of the system integration module (SIM) function. Refer to the *SIM Reference Manual* (SIMRM/AD) for a comprehensive discussion of SIM capabilities. Refer to **D.2 System Integration Module** for information concerning the SIM address map and register structure.

#### 5.1 General

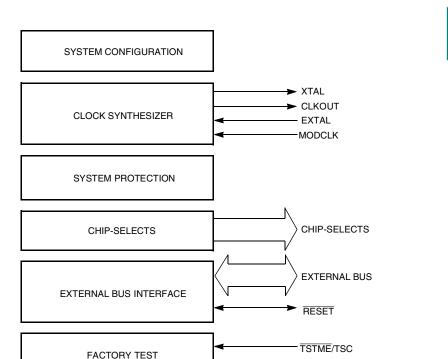

The SIM consists of six functional blocks. **Figure 5-1** shows a block diagram of the SIM.

The system configuration block controls MCU configuration parameters.

The system clock generates clock signals used by the SIM, other IMB modules, and external devices.

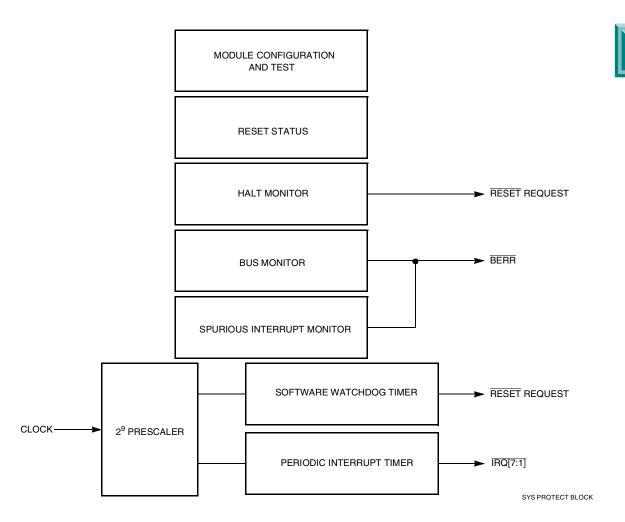

The system protection block provides bus and software watchdog monitors. In addition, it also provides a periodic interrupt timer to support execution of time-critical control routines.

The external bus interface handles the transfer of information between IMB modules and external address space.

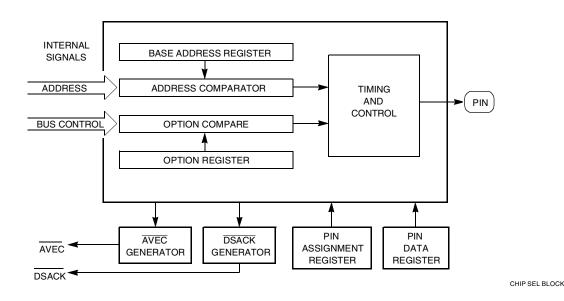

The chip-select block provides 12 chip-select signals. Each chip-select signal has an associated base address register and option register that contain the programmable characteristics of that chip-select.

The system test block incorporates hardware necessary for testing the MCU. It is used to perform factory tests, and its use in normal applications is not supported.

300 S(C)IM BLOCK

FREEZE/QUOT

Figure 5-1 System Integration Module Block Diagram

# 5.2 System Configuration

The SIM configuration register (SIMCR) governs several aspects of system operation. The following paragraphs describe those configuration options controlled by SIMCR.

### 5.2.1 Module Mapping

Control registers for all the modules in the microcontroller are mapped into a 4-Kbyte block. The state of the module mapping bit (MM) in the SIM configuration register (SIMCR) determines where the control register block is located in the system memory map. When MM = 0, register addresses range from \$7FF000 to \$7FFFFF; when MM = 1, register addresses range from \$FFF000 to \$FFFFFF.

### **5.2.2 Interrupt Arbitration**

Each module that can request interrupts has an interrupt arbitration (IARB) field. Arbitration between interrupt requests of the same priority is performed by serial contention between IARB field bit values. Contention must take place whenever an interrupt request is acknowledged, even when there is only a single request pending. For an interrupt to be serviced, the appropriate IARB field must have a non-zero value. If an interrupt request from a module with an IARB field value of %0000 is recognized, the CPU32 processes a spurious interrupt exception.

Because the SIM routes external interrupt requests to the CPU32, the SIM IARB field value is used for arbitration between internal and external interrupts of the same prior-

ity. The reset value of IARB for the SIM is %1111, and the reset IARB value for all other modules is %0000, which prevents SIM interrupts from being discarded during initialization. Refer to **5.8 Interrupts** for a discussion of interrupt arbitration.

### 5.2.3 Show Internal Cycles

A show cycle allows internal bus transfers to be monitored externally. The SHEN field in SIMCR determines what the external bus interface does during internal transfer operations. **Table 5-1** shows whether data is driven externally, and whether external bus arbitration can occur. Refer to **5.6.6.1 Show Cycles** for more information.

**Table 5-1 Show Cycle Enable Bits**

| SHEN[1:0] | Action                                                                                        |

|-----------|-----------------------------------------------------------------------------------------------|

| 00        | Show cycles disabled, external arbitration enabled                                            |

| 01        | Show cycles enabled, external arbitration disabled                                            |

| 10        | Show cycles enabled, external arbitration enabled                                             |

| 11        | Show cycles enabled, external arbitration enabled; internal activity is halted by a bus grant |

### **5.2.4 Register Access**

The CPU32 can operate at one of two privilege levels. Supervisor level is more privileged than user level — all instructions and system resources are available at supervisor level, but access is restricted at user level. Effective use of privilege level can protect system resources from uncontrolled access. The state of the S bit in the CPU status register determines access level, and whether the user or supervisor stack pointer is used for stacking operations. The SUPV bit places SIM global registers in either supervisor or user data space. When SUPV = 0, registers with controlled access are accessible from either the user or supervisor privilege level; when SUPV = 1, registers with controlled access are restricted to supervisor access only.

### 5.2.5 Freeze Operation

The FREEZE signal halts MCU operations during debugging. FREEZE is asserted internally by the CPU32 if a breakpoint occurs while background mode is enabled. When FREEZE is asserted, only the bus monitor, software watchdog, and periodic interrupt timer are affected. The halt monitor and spurious interrupt monitor continue to operate normally. Setting the freeze bus monitor (FRZBM) bit in SIMCR disables the bus monitor when FREEZE is asserted. Setting the freeze software watchdog (FRZSW) bit disables the software watchdog and the periodic interrupt timer when FREEZE is asserted.

### 5.3 System Clock

The system clock in the SIM provides timing signals for the IMB modules and for an external peripheral bus. Because the MCU is a fully static design, register and memory contents are not affected when the clock rate changes. System hardware and software support changes in clock rate during operation.

The system clock signal can be generated from one of two sources. An internal phase-locked loop (PLL) can synthesize the clock from a fast reference, or the clock signal can be directly input from an external frequency source. The fast reference is typically a 4.194 MHz crystal, but may be generated by sources other than a crystal. Keep these sources in mind while reading the rest of this section. Refer to **Table A-4** in the **APPENDIX A ELECTRICAL CHARACTERISTICS** for clock specifications.

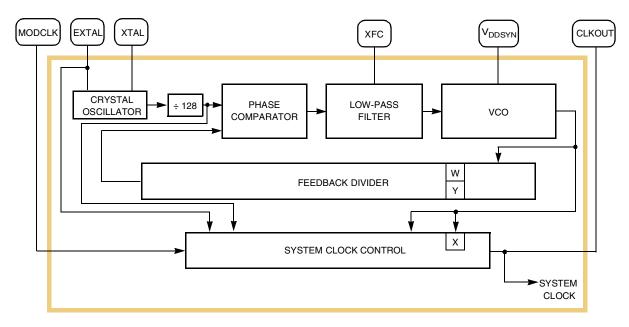

Figure 5-2 is a block diagram of the clock submodule.

16/32 PLL BLOCK 4M

Figure 5-2 System Clock Block Diagram

#### 5.3.1 Clock Sources

The state of the clock mode (MODCLK) pin during reset determines the system clock source. When MODCLK is held high during reset, the clock synthesizer generates a clock signal from an external reference frequency. The clock synthesizer control register (SYNCR) determines operating frequency and mode of operation. When MODCLK is held low during reset, the clock synthesizer is disabled and an external system clock signal must be driven onto the EXTAL pin.

The input clock is referred to as  $f_{ref}$ , and can be either a crystal or an external clock source. The output of the clock system is referred to as  $f_{sys}$ . Ensure that  $f_{ref}$  and  $f_{sys}$  are within normal operating limits.

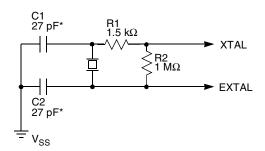

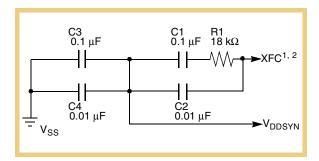

To generate a reference frequency using the crystal oscillator, a reference crystal must be connected between the EXTAL and XTAL pins. Typically, a 4.194 MHz crystal is used, but the frequency may vary between 1 and 6 MHz. **Figure 5-3** shows a typical circuit.

Figure 5-3 System Clock Oscillator Circuit

If a fast reference frequency is provided to the PLL from a source other than a crystal, or an external system clock signal is applied through the EXTAL pin, the XTAL pin must be left floating.

When an external system clock signal is applied (MODCLK = 0 during reset), the PLL is disabled. The duty cycle of this signal is critical, especially at operating frequencies close to maximum. The relationship between clock signal duty cycle and clock signal period is expressed as follows:

Minimum External Clock Period =

Minimum External Clock High/Low Time

50% - Percentage Variation of External Clock Input Dut@

# 5.3.2 Clock Synthesizer Operation

$V_{DDSYN}$  is used to power the clock circuits when the system clock is synthesized from either a crystal or an externally supplied reference frequency. A separate power source increases MCU noise immunity and can be used to run the clock when the MCU is powered down. A quiet power supply must be used as the  $V_{DDSYN}$  source. Adequate external bypass capacitors should be placed as close as possible to the  $V_{DDSYN}$  pin to assure a stable operating frequency. When an external system clock signal is applied and the PLL is disabled,  $V_{DDSYN}$  should be connected to the  $V_{DD}$  supply. Refer to the *SIM Reference Manual* (SIMRM/AD) for more information regarding system clock power supply conditioning.

A voltage controlled oscillator (VCO) in the PLL generates the system clock signal. To maintain a 50% clock duty cycle, the VCO frequency (f<sub>VCO</sub>) is either two or four times the system clock frequency, depending on the state of the X bit in SYNCR. The clock signal is fed back to a divider/counter. The divider controls the frequency of one input to a phase comparator. The other phase comparator input is a reference signal, either from the crystal oscillator or from an external source. The comparator generates a control signal proportional to the difference in phase between the two inputs. This signal is low-pass filtered and used to correct the VCO output frequency.

<sup>\*</sup> RESISTANCE AND CAPACITANCE BASED ON A TEST CIRCUIT CONSTRUCTED WITH A KDS041-18 4.194 MHz CRYSTAL. SPECIFIC COMPONENTS MUST BE BASED ON CRYSTAL TYPE. CONTACT CRYSTAL VENDOR FOR EXACT CIRCUIT.

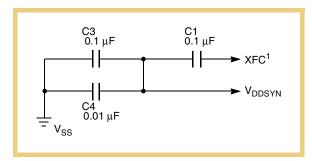

Filter circuit implementation can vary, depending upon the external environment and required clock stability. **Figure 5-4** shows two recommended system clock filter networks. XFC pin leakage must be kept as low as possible to maintain optimum stability and PLL performance.

An external filter network connected to the XFC pin is not required when an external system clock signal is applied and the PLL is disabled (MODCLK = 0 at reset). The XFC pin must be left floating in this case.

NORMAL OPERATING ENVIRONMENT

HIGH-STABILITY OPERATING ENVIRONMENT

- 1. MAINTAIN LOW LEAKAGE ON THE XFC NODE. REFER TO APPENDIX A ELECTRICAL CHARACTERISTICS FOR MORE INFORMATION.

- 2. RECOMMENDED LOOP FILTER FOR REDUCED SENSITIVITY TO LOW FREQUENCY NOISE.

NORMAL/HIGH-STABILITY XFC CONN

Figure 5-4 System Clock Filter Networks

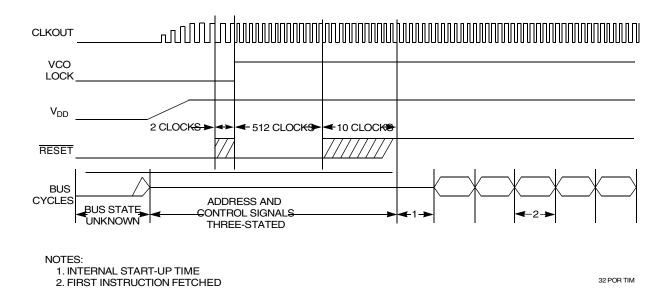

The synthesizer locks when the VCO frequency is equal to f<sub>ref</sub>. Lock time is affected by the filter time constant and by the amount of difference between the two comparator inputs. Whenever a comparator input changes, the synthesizer must relock. Lock status is shown by the SLOCK bit in SYNCR. During power-up, the MCU does not come out of reset until the synthesizer locks. Crystal type, characteristic frequency, and layout of external oscillator circuitry affect lock time.

When the clock synthesizer is used, SYNCR determines the system clock frequency and certain operating parameters. The W and Y[5:0] bits are located in the PLL feedback path, enabling frequency multiplication by a factor of up to 256. When the W or Y values change, VCO frequency changes, and there is a VCO relock delay. The SYNCR X bit controls a divide-by circuit that is not in the synthesizer feedback loop. When X = 0 (reset state), a divide-by-four circuit is enabled, and the system clock frequency is one-fourth the VCO frequency ( $f_{VCO}$ ). When X = 1, a divide-by-two circuit is enabled and system clock frequency is one-half the VCO frequency ( $f_{VCO}$ ). There is no relock delay when clock speed is changed by the X bit.

Clock frequency is determined by SYNCR bit settings as follows:

$$f_{sys} = \frac{f_{ref}}{128} [4(Y+1)(2^{(2W+X)})]$$

5-6

The reset state of SYNCR (\$3F00) results in a power-on  $f_{sys}$  of 8.388 MHz when  $f_{ref}$  is 4.194 MHz.

For the device to operate correctly, the clock frequency selected by the W, X, and Y bits must be within the limits specified for the MCU.

Internal VCO frequency is determined by the following equations:

$$f_{VCO} = 4f_{sys}$$

if  $X = 0$

or

$f_{VCO} = 2f_{sys}$  if  $X = 1$

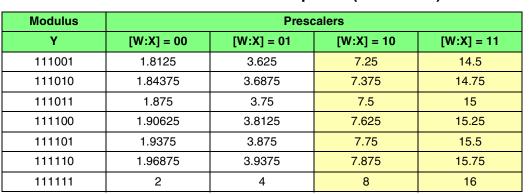

Table 5-2 shows clock control multipliers for all possible combinations of SYNCR bits. To obtain clock frequency, find counter modulus in the leftmost column, then multiply the reference frequency by the value in the appropriate prescaler cell. Shaded cells exceed the maximum system clock frequency at the time of manual publication; however, they may be usable in the future. Refer to APPENDIX A ELECTRICAL CHARACTERISTICS for maximum allowable clock rate.

**Table 5-3** shows clock frequencies available with a 4.194 MHz reference and a maximum specified clock frequency of 20.97 MHz. To obtain clock frequency, find counter modulus in the leftmost column, then refer to appropriate prescaler cell. Shaded cells exceed the maximum system clock frequency at the time of manual publication; however, they may be usable in the future. Refer to **APPENDIX A ELECTRICAL CHARACTERISTICS** for maximum system frequency (f<sub>svs</sub>).

**Table 5-2 Clock Control Multipliers**

| Modulus | Prescalers |            |            |            |

|---------|------------|------------|------------|------------|

| Υ       | [W:X] = 00 | [W:X] = 01 | [W:X] = 10 | [W:X] = 11 |

| 000000  | .03125     | .625       | .125       | .25        |

| 000001  | .0625      | .125       | .25        | .5         |

| 000010  | .09375     | .1875      | .375       | .75        |

| 000011  | .125       | .25        | .5         | 1          |

| 000100  | .15625     | .3125      | .625       | 1.25       |

| 000101  | .1875      | .375       | .75        | 1.5        |

| 000110  | .21875     | .4375      | .875       | 1.75       |

| 000111  | .25        | .5         | 1          | 2          |

| 001000  | .21825     | .5625      | 1.125      | 2.25       |

| 001001  | .3125      | .625       | 1.25       | 2.5        |

| 001010  | .34375     | .6875      | 1.375      | 2.75       |

| 001011  | .375       | .75        | 1.5        | 3          |

| 001100  | .40625     | .8125      | 1.625      | 3.25       |

| 001101  | .4375      | .875       | 1.75       | 3.5        |

| 001110  | .46875     | .9375      | 1.875      | 3.75       |

| 001111  | .5         | 1          | 2          | 4          |

**Table 5-2 Clock Control Multipliers (Continued)**

| Modulus | Prescalers |            |            |            |

|---------|------------|------------|------------|------------|

| Y       | [W:X] = 00 | [W:X] = 01 | [W:X] = 10 | [W:X] = 11 |

| 010000  | .53125     | 1.0625     | 2.125      | 4.25       |

| 010001  | .5625      | 1.125      | 2.25       | 4.5        |

| 010010  | .59375     | 1.1875     | 2.375      | 4.75       |

| 010011  | .625       | 1.25       | 2.5        | 5          |

| 010100  | .65625     | 1.3125     | 2.625      | 5.25       |

| 010101  | .6875      | 1.375      | 2.75       | 5.5        |

| 010110  | .71875     | 1.4375     | 2.875      | 5.75       |

| 010111  | .75        | 1.5        | 3          | 6          |

| 011000  | .78125     | 1.5625     | 3.125      | 6.25       |

| 011001  | .8125      | 1.625      | 3.25       | 6.5        |

| 011010  | .84375     | 1.6875     | 3.375      | 6.75       |

| 011011  | .875       | 1.75       | 3.5        | 7          |

| 011100  | .90625     | 1.8125     | 3.625      | 7.25       |

| 011101  | .9375      | 1.875      | 3.75       | 7.5        |

| 011110  | .96875     | 1.9375     | 3.875      | 7.75       |

| 011111  | 1          | 2          | 4          | 8          |

| 100000  | 1.03125    | 2.0625     | 4.125      | 8.25       |

| 100001  | 1.0625     | 2.125      | 4.25       | 8.5        |

| 100010  | 1.09375    | 2.1875     | 4.375      | 8.75       |

| 100011  | 1.125      | 2.25       | 4.5        | 9          |

| 100100  | 1.15625    | 2.3125     | 4.675      | 9.25       |

| 100101  | 1.1875     | 2.375      | 4.75       | 9.5        |

| 100110  | 1.21875    | 2.4375     | 4.875      | 9.75       |

| 100111  | 1.25       | 2.5        | 5          | 10         |

| 101000  | 1.28125    | 2.5625     | 5.125      | 10.25      |

| 101001  | 1.3125     | 2.625      | 5.25       | 10.5       |

| 101010  | 1.34375    | 2.6875     | 5.375      | 10.75      |

| 101011  | 1.375      | 2.75       | 5.5        | 11         |

| 101100  | 1.40625    | 2.8125     | 5.625      | 11.25      |

| 101101  | 1.4375     | 2.875      | 5.75       | 11.5       |

| 101110  | 1.46875    | 2.9375     | 5.875      | 11.75      |

| 101111  | 1.5        | 3          | 6          | 12         |

| 110000  | 1.53125    | 3.0625     | 6.125      | 12.25      |

| 110001  | 1.5625     | 3.125      | 6.25       | 12.5       |

| 110010  | 1.59375    | 3.1875     | 6.375      | 12.75      |

| 110011  | 1.625      | 3.25       | 6.5        | 13         |

| 110100  | 1.65625    | 3.3125     | 6.625      | 13.25      |

| 110101  | 1.6875     | 3.375      | 6.75       | 13.5       |

| 110110  | 1.71875    | 3.4375     | 6.875      | 13.75      |

| 110111  | 1.75       | 3.5        | 7          | 14         |

| 111000  | 1.78125    | 3.5625     | 7.125      | 14.25      |

**Table 5-2 Clock Control Multipliers (Continued)**

Table 5-3 System Frequencies from 4.194 MHz Reference

| Modulus | Prescaler  |            |            |            |

|---------|------------|------------|------------|------------|

| Υ       | [W:X] = 00 | [W:X] = 01 | [W:X] = 10 | [W:X] = 11 |

| 000000  | 131 kHz    | 262 kHz    | 524 kHz    | 1049 kHz   |

| 000001  | 262        | 524        | 1049       | 2097       |

| 000010  | 393        | 786        | 1573       | 3146       |

| 000011  | 524        | 1049       | 2097       | 4194       |

| 000100  | 655        | 1311       | 2621       | 5243       |

| 000101  | 786        | 1573       | 3146       | 6291       |

| 000110  | 918        | 1835       | 3670       | 7340       |

| 000111  | 1049       | 2097       | 4194       | 8389       |

| 001000  | 1180       | 2359       | 4719       | 9437       |

| 001001  | 1311       | 2621       | 5243       | 10486      |

| 001010  | 1442       | 2884       | 5767       | 11534      |

| 001011  | 1573       | 3146       | 6291       | 12583      |

| 001100  | 1704       | 3408       | 6816       | 13631      |

| 001101  | 1835       | 3670       | 7340       | 14680      |

| 001110  | 1966       | 3932       | 7864       | 15729      |

| 001111  | 2097       | 4194       | 8389       | 16777      |

| 010000  | 2228       | 4456       | 8913       | 17826      |

| 010001  | 2359       | 4719       | 9437       | 18874      |

| 010010  | 2490       | 4981       | 9961       | 19923      |

| 010011  | 2621       | 5243       | 10486      | 20972      |

| 010100  | 2753       | 5505       | 11010      | 22020      |

| 010101  | 2884       | 5767       | 11534      | 23069      |

| 010110  | 3015       | 6029       | 12059      | 24117      |

| 010111  | 3146       | 6291       | 12583      | 25166      |

| 011000  | 3277       | 6554       | 13107      | 26214      |

| 011001  | 3408       | 6816       | 13631      | 27263      |

| 011010  | 3539       | 7078       | 14156      | 28312      |

| 011011  | 3670       | 7340       | 14680      | 29360      |

| 011100  | 3801       | 7602       | 15204      | 30409      |

Table 5-3 System Frequencies from 4.194 MHz Reference (Continued)

| Modulus | Prescaler  |            |            |            |

|---------|------------|------------|------------|------------|

| Υ       | [W:X] = 00 | [W:X] = 01 | [W:X] = 10 | [W:X] = 11 |

| 011101  | 3932       | 7864       | 15729      | 31457      |

| 011110  | 4063       | 8126       | 16253      | 32506      |

| 011111  | 4194       | 8389       | 16777      | 33554      |

| 100000  | 4325 kHz   | 8651 kHz   | 17302 kHz  | 34603 kHz  |

| 100001  | 4456       | 8913       | 17826      | 35652      |

| 100010  | 4588       | 9175       | 18350      | 36700      |

| 100011  | 4719       | 9437       | 18874      | 37749      |

| 100100  | 4850       | 9699       | 19399      | 38797      |

| 100101  | 4981       | 9961       | 19923      | 39846      |

| 100110  | 5112       | 10224      | 20447      | 40894      |

| 100111  | 5243       | 10486      | 20972      | 41943      |

| 101000  | 5374       | 10748      | 21496      | 42992      |

| 101001  | 5505       | 11010      | 22020      | 44040      |

| 101010  | 5636       | 11272      | 22544      | 45089      |

| 101011  | 5767       | 11534      | 23069      | 46137      |

| 101100  | 5898       | 11796      | 23593      | 47186      |

| 101101  | 6029       | 12059      | 24117      | 48234      |

| 101110  | 6160       | 12321      | 24642      | 49283      |

| 101111  | 6291       | 12583      | 25166      | 50332      |

| 110000  | 6423       | 12845      | 25690      | 51380      |

| 110001  | 6554       | 13107      | 26214      | 52428      |

| 110010  | 6685       | 13369      | 26739      | 53477      |

| 110011  | 6816       | 13631      | 27263      | 54526      |

| 110100  | 6947       | 13894      | 27787      | 55575      |

| 110101  | 7078       | 14156      | 28312      | 56623      |

| 110110  | 7209       | 14418      | 28836      | 57672      |

| 110111  | 7340       | 14680      | 29360      | 58720      |

| 111000  | 7471       | 14942      | 2988       | 59769      |

| 111001  | 7602       | 15204      | 30409      | 60817      |

| 111010  | 7733       | 15466      | 30933      | 61866      |

| 111011  | 7864       | 15729      | 31457      | 62915      |

| 111100  | 7995       | 15991      | 31982      | 63963      |

| 111101  | 8126       | 16253      | 32506      | 65011      |

| 111110  | 8258       | 16515      | 33030      | 66060      |

| 111111  | 8389       | 16777      | 33554      | 67109      |

#### 5.3.3 External Bus Clock

The state of the E-clock division bit (EDIV) in SYNCR determines clock rate for the E-clock signal (ECLK) available on pin ADDR23. ECLK is a bus clock for M6800 devices and peripherals. ECLK frequency can be set to system clock frequency divided by eight or system clock frequency divided by sixteen. The clock is enabled by the CS10

field in chip-select pin assignment register 1 (CSPAR1). ECLK operation during low-power stop is described in the following paragraph. Refer to **5.9 Chip-Selects** for more information about the external bus clock.

## 5.3.4 Low-Power Operation

Low-power operation is initiated by the CPU32. To reduce power consumption selectively, the CPU can set the STOP bits in each module configuration register. To minimize overall microcontroller power consumption, the CPU can execute the LPSTOP instruction, which causes the SIM to turn off the system clock.

When individual module STOP bits are set, clock signals inside each module are turned off, but module registers are still accessible.

When the CPU executes LPSTOP, a special CPU space bus cycle writes a copy of the current interrupt mask into the clock control logic. The SIM brings the MCU out of low-power stop mode when one of the following exceptions occur:

- U-bus interface

- RESET

- Trace

- SIM interrupt of higher priority than the stored interrupt mask

Refer to 5.6.4.2 LPSTOP Broadcast Cycle and 4.8.2.1 Low-Power Stop (LPSTOP) for more information.

During low-power stop mode, unless the system clock signal is supplied by an external source and that source is removed, the SIM clock control logic and the SIM clock signal (SIMCLK) continue to operate. The periodic interrupt timer and input logic for the RESET and IRQ pins are clocked by SIMCLK, and can be used to bring the processor out of LPSTOP. Optionally, the SIM can also continue to generate the CLKOUT signal while in low-power stop mode.

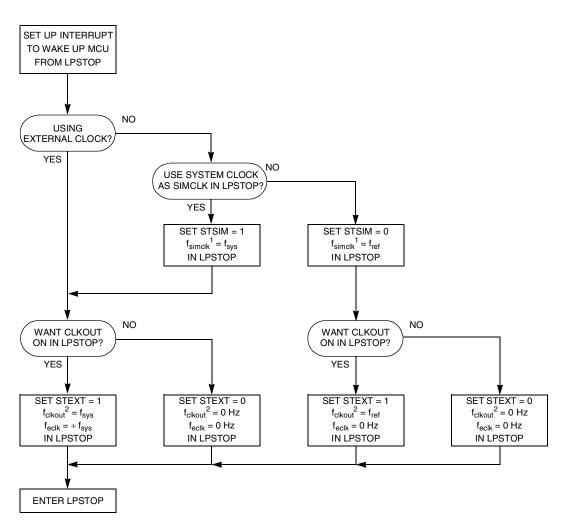

STSIM and STEXT bits in SYNCR determine clock operation during low-power stop mode.

The flowchart shown in **Figure 5-5** summarizes the effects of the STSIM and STEXT bits when the MCU enters normal low power stop mode. Any clock in the off state is held low. If the synthesizer VCO is turned off during low-power stop mode, there is a PLL relock delay after the VCO is turned back on.

NOTES

- 1. THE SIMCLK IS USED BY THE PIT,  $\overline{\text{IRQ}}$ , AND INPUT BLOCKS OF THE SIM.

- 2. CLKOUT CONTROL DURING LPSTOP IS OVERRIDDEN BY THE EXOFF BIT IN SIMCR. IF EXOFF = 1, THE CLKOUT PIN IS ALWAYS IN A HIGH IMPEDANCE STATE AND STEXT HAS NO EFFECT IN LPSTOP. IF EXOFF = 0, CLKOUT IS CONTROLLED BY STEXT IN LPSTOP.

LPSTOPFLOW

Figure 5-5 LPSTOP Flowchart

### 5.4 System Protection

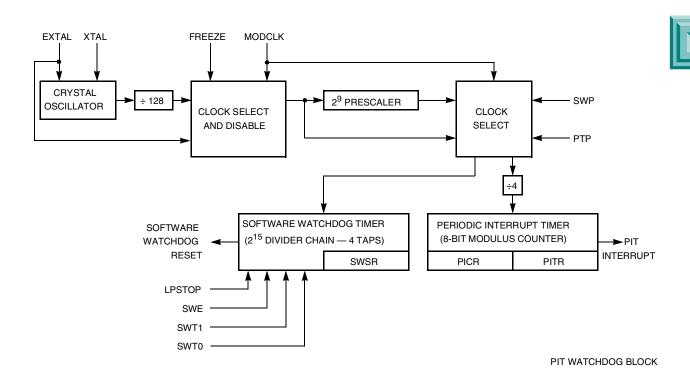

The system protection block preserves reset status, monitors internal activity, and provides periodic interrupt generation. **Figure 5-6** is a block diagram of the submodule.

Figure 5-6 System Protection Block

#### 5.4.1 Reset Status

The reset status register (RSR) latches internal MCU status during reset. Refer to **5.7.10 Reset Status Register** for more information.

#### 5.4.2 Bus Monitor

The internal bus monitor checks data and size acknowledge (DSACK) or autovector (AVEC) signal response times during normal bus cycles. The monitor asserts the internal bus error (BERR) signal when the response time is excessively long.

DSACK and AVEC response times are measured in clock cycles. Maximum allowable response time can be selected by setting the bus monitor timing (BMT[1:0]) field in the system protection control register (SYPCR). **Table 5-4** shows the periods allowed.

**Table 5-4 Bus Monitor Period**

| BMT[1:0] | Bus Monitor Time-Out Period |  |

|----------|-----------------------------|--|

| 00       | 64 system clocks            |  |

| 01       | 32 system clocks            |  |

| 10       | 16 system clocks            |  |

| 11       | 8 system clocks             |  |

MC68336/376 USER'S MANUAL

The monitor does not check DSACK response on the external bus unless the CPU32 initiates a bus cycle. The BME bit in SYPCR enables the internal bus monitor for internal to external bus cycles. If a system contains external bus masters, an external bus monitor must be implemented and the internal-to-external bus monitor option must be disabled.

When monitoring transfers to an 8-bit port, the bus monitor does not reset until both byte accesses of a word transfer are completed. Monitor time-out period must be at least twice the number of clocks that a single byte access requires.

#### 5.4.3 Halt Monitor

The halt monitor responds to an assertion of the HALT signal on the internal bus, caused by a double bus fault. A flag in the reset status register (RSR) indicates that the last reset was caused by the halt monitor. Halt monitor reset can be inhibited by the halt monitor (HME) enable bit in SYPCR. Refer to **5.6.5.2 Double Bus Faults** for more information.

### **5.4.4 Spurious Interrupt Monitor**

During interrupt exception processing, the CPU32 normally acknowledges an interrupt request, recognizes the highest priority source, and then either acquires a vector or responds to a request for autovectoring. The spurious interrupt monitor asserts the internal bus error signal (BERR) if no interrupt arbitration occurs during interrupt exception processing. The assertion of BERR causes the CPU32 to load the spurious interrupt exception vector into the program counter. The spurious interrupt monitor cannot be disabled. Refer to 5.8 Interrupts for more information. For detailed information about interrupt exception processing, refer to 4.9 Exception Processing.

#### 5.4.5 Software Watchdog

The software watchdog is controlled by the software watchdog enable (SWE) bit in SYPCR. When enabled, the watchdog requires that a service sequence be written to the software service register (SWSR) on a periodic basis. If servicing does not take place, the watchdog times out and asserts the RESET signal.

Each time the service sequence is written, the software watchdog timer restarts. The sequence to restart consists of the following steps:

- 1. Write \$55 to SWSR.

- 2. Write \$AA to SWSR.

Both writes must occur before time-out in the order listed. Any number of instructions can be executed between the two writes.

Watchdog clock rate is affected by the software watchdog prescale (SWP) bit and the software watchdog timing (SWT[1:0]) field in SYPCR.

SWP determines system clock prescaling for the watchdog timer and determines that one of two options, either no prescaling or prescaling by a factor of 512, can be

selected. The value of SWP is affected by the state of the MODCLK pin during reset, as shown in **Table 5-5**. System software can change SWP value.

Table 5-5 MODCLK Pin and SWP Bit During Reset

| MODCLK           | SWP       |

|------------------|-----------|

| 0 (PLL disabled) | 1 (÷ 512) |

| 1 (PLL enabled)  | 0 (÷ 1)   |

SWT[1:0] selects the divide ratio used to establish the software watchdog time-out period. The following equation calculates the time-out period for a fast reference frequency.

Time-out Period =

$$\frac{(128)(\text{Divide Ratio Specified by SWP and SWT[1:0]})}{f_{ref}}$$

The following equation calculates the time-out period for an externally input clock frequency.

Time-out Period =

$$\frac{\text{Divide Ratio Specified by SWP and SWT[1:0]}}{f_{ref}}$$

**Table 5-6** shows the divide ratio for each combination of SWP and SWT[1:0] bits. When SWT[1:0] are modified, a watchdog service sequence must be performed before the new time-out period can take effect.

**Table 5-6 Software Watchdog Ratio**

| SWP | SWT[1:0] | Watchdog Time-Out Period           |

|-----|----------|------------------------------------|

| 0   | 00       | 2 <sup>9</sup> ÷ f <sub>sys</sub>  |

| 0   | 01       | 2 <sup>11</sup> ÷ f <sub>sys</sub> |

| 0   | 10       | 2 <sup>13</sup> ÷ f <sub>sys</sub> |

| 0   | 11       | 2 <sup>15</sup> ÷ f <sub>sys</sub> |

| 1   | 00       | 2 <sup>18</sup> ÷ f <sub>sys</sub> |

| 1   | 01       | $2^{20} \div f_{sys}$              |

| 1   | 10       | 2 <sup>22</sup> ÷ f <sub>sys</sub> |

| 1   | 11       | $2^{24} \div f_{sys}$              |

Figure 5-7 is a block diagram of the watchdog timer and the clock control for the periodic interrupt timer.

Figure 5-7 Periodic Interrupt Timer and Software Watchdog Timer

### 5.4.6 Periodic Interrupt Timer

The periodic interrupt timer (PIT) allows the generation of interrupts of specific priority at predetermined intervals. This capability is often used to schedule control system tasks that must be performed within time constraints. The timer consists of a prescaler, a modulus counter, and registers that determine interrupt timing, priority and vector assignment. Refer to **4.9 Exception Processing** for more information.

The periodic interrupt timer modulus counter is clocked by one of two signals. When the PLL is enabled (MODCLK = 1 during reset),  $f_{ref} \div 128$  is used. When the PLL is disabled (MODCLK = 0 during reset),  $f_{ref}$  is used. The value of the periodic timer prescaler (PTP) bit in the periodic interrupt timer register (PITR) determines system clock prescaling for the periodic interrupt timer. One of two options, either no prescaling, or prescaling by a factor of 512, can be selected. The value of PTP is affected by the state of the MODCLK pin during reset, as shown in **Table 5-7**. System software can change PTP value.

Table 5-7 MODCLK Pin and PTP Bit at Reset

| MODCLK           | PTP       |

|------------------|-----------|

| 0 (PLL disabled) | 1 (÷ 512) |

| 1 (PLL enabled)  | 0 (÷ 1)   |

Either clock signal selected by the PTP is divided by four before driving the modulus counter. The modulus counter is initialized by writing a value to the periodic interrupt timer modulus (PITM[7:0]) field in PITR. A zero value turns off the periodic timer. When

the modulus counter value reaches zero, an interrupt is generated. The modulus counter is then reloaded with the value in PITM[7:0] and counting repeats. If a new value is written to PITR, it is loaded into the modulus counter when the current count is completed.

When a fast reference frequency is used, the PIT period can be calculated as follows:

$$PIT \ Period \ = \ \frac{(128)(PITM[7:0])(1 \ if \ PTP = 0, \ 512 \ if \ PTP = 1)(4)}{f_{ref}}$$

When an externally input clock frequency is used, the PIT period can be calculated as follows:

$$PIT \ Period = \frac{(PITM[7:0])(1 \ if \ PTP = 0, 512 \ if \ PTP = 1)(4)}{f_{ref}}$$

### 5.4.7 Interrupt Priority and Vectoring

111

Interrupt priority and vectoring are determined by the values of the periodic interrupt request level (PIRQL[2:0]) and periodic interrupt vector (PIV) fields in the periodic interrupt control register (PICR).

The PIRQL field is compared to the CPU32 interrupt priority mask to determine whether the interrupt is recognized. **Table 5-8** shows PIRQL[2:0] priority values. Because of SIM hardware prioritization, a PIT interrupt is serviced before an external interrupt request of the same priority. The periodic timer continues to run when the interrupt is disabled.

**Priority Level** PIRQL[2:0] Periodic interrupt disabled 000 Interrupt priority level 1 001 010 Interrupt priority level 2 011 Interrupt priority level 3 Interrupt priority level 4 100 Interrupt priority level 5 101 110 Interrupt priority level 6

**Table 5-8 Periodic Interrupt Priority**

The PIV field contains the periodic interrupt vector. The vector is placed on the IMB when an interrupt request is made. The vector number is used to calculate the address of the appropriate exception vector in the exception vector table. The reset value of the PIV field is \$0F, which corresponds to the uninitialized interrupt exception vector.

Interrupt priority level 7

### **5.4.8 Low-Power STOP Mode Operation**

During low-power stop mode, the clock input to the software watchdog timer is disabled and the timer stops. The software watchdog begins to run again on the first rising clock edge after low-power stop mode ends. The watchdog is not reset by low-power stop mode. A service sequence must be performed to reset the timer.

The periodic interrupt timer does not respond to the LPSTOP instruction, but continues to run during LPSTOP. To stop the periodic interrupt timer, PITR must be loaded with a zero value before the LPSTOP instruction is executed. A PIT interrupt, or an external interrupt request, can bring the MCU out of low-power stop mode if it has a higher priority than the interrupt mask value stored in the clock control logic when low-power stop mode is initiated. LPSTOP can be terminated by a reset.

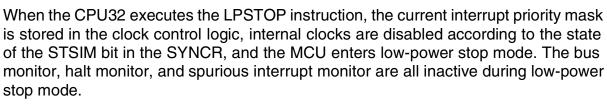

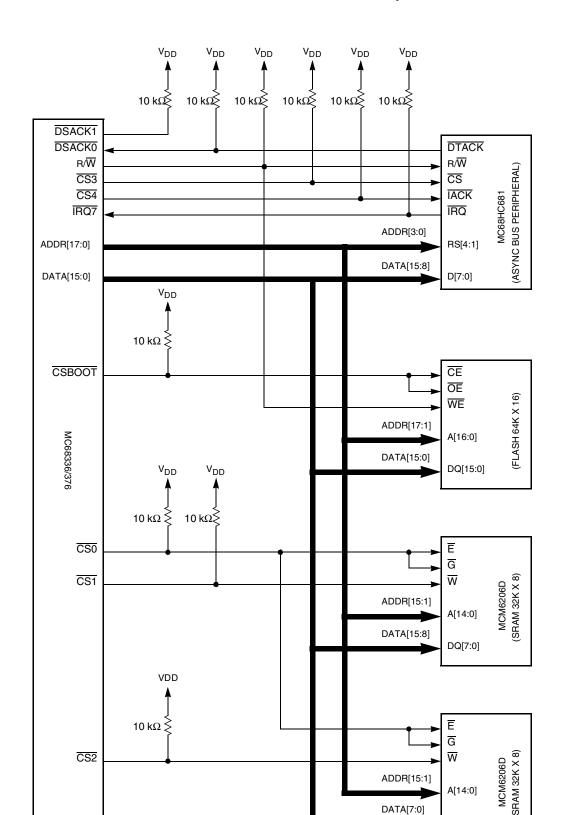

#### 5.5 External Bus Interface

The external bus interface (EBI) transfers information between the internal MCU bus and external devices. **Figure 5-8** shows a basic system with external memory and peripherals.

Figure 5-8 MCU Basic System

MC68336/376 **USER'S MANUAL**

SYSTEM INTEGRATION MODULE For More Information On This Product. Go to: www.freescale.com

DQ[7:0]

68300 SIM/SCIM I

The external bus has 24 address lines and 16 data lines. The EBI provides dynamic sizing between 8-bit and 16-bit data accesses. It supports byte, word, and long-word transfers. Port width is the maximum number of bits accepted or provided during a bus transfer. Widths of eight and sixteen bits are accessed through the use of asynchronous cycles controlled by the size (SIZ1 and SIZ0) and data and size acknowledge (DSACK1 and DSACK0) pins. Multiple bus cycles may be required for dynamically sized transfers.

To add flexibility and minimize the necessity for external logic, MCU chip-select logic can be synchronized with EBI transfers. Refer to **5.9 Chip-Selects** for more information.

### 5.5.1 Bus Control Signals

The address bus provides addressing information to external devices. The data bus transfers 8-bit and 16-bit data between the MCU and external devices. Strobe signals, one for the address bus and another for the data bus, indicate the validity of an address and provide timing information for data.

Control signals indicate the beginning of each bus cycle, the address space it is to take place in, the size of the transfer, and the type of cycle. External devices decode these signals and respond to transfer data and terminate the bus cycle. The EBI operates in an asynchronous mode for any port width.

#### 5.5.1.1 Address Bus

Bus signals ADDR[23:0] define the address of the byte (or the most significant byte) to be transferred during a bus cycle. The MCU places the address on the bus at the beginning of a bus cycle. The address is valid while  $\overline{AS}$  is asserted.

#### 5.5.1.2 Address Strobe

Address strobe  $(\overline{AS})$  is a timing signal that indicates the validity of an address on the address bus and of many control signals. It is asserted one-half clock after the beginning of a bus cycle.

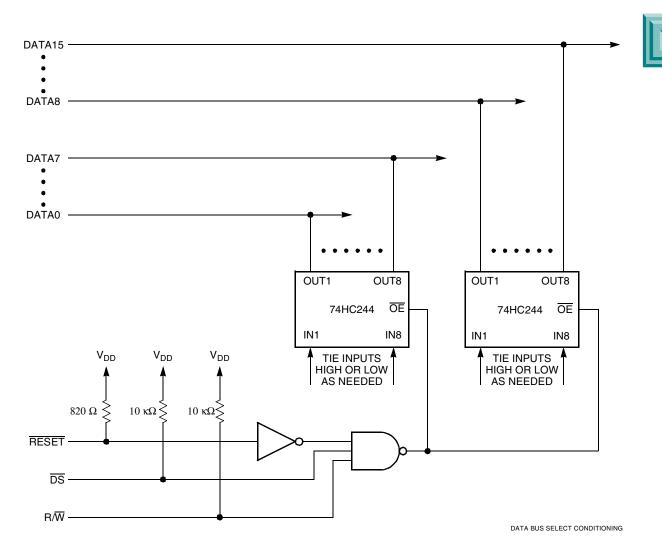

#### 5.5.1.3 Data Bus

Signals DATA[15:0] form a bidirectional, non-multiplexed parallel bus that transfers data to or from the MCU. A read or write operation can transfer eight or sixteen bits of data in one bus cycle. During a read cycle, the data is latched by the MCU on the last falling edge of the clock for that bus cycle. For a write cycle, all 16 bits of the data bus are driven, regardless of the port width or operand size. The MCU places the data on the data bus one-half clock cycle after  $\overline{AS}$  is asserted in a write cycle.

#### 5.5.1.4 Data Strobe

Data strobe  $(\overline{DS})$  is a timing signal. For a read cycle, the MCU asserts  $\overline{DS}$  to signal an external device to place data on the bus.  $\overline{DS}$  is asserted at the same time as  $\overline{AS}$  during a read cycle. For a write cycle,  $\overline{DS}$  signals an external device that data on the bus is

valid. The MCU asserts  $\overline{DS}$  one full clock cycle after the assertion of  $\overline{AS}$  during a write cycle.

### 5.5.1.5 Read/Write Signal

The read/write signal (R/W) determines the direction of the transfer during a bus cycle. This signal changes state, when required, at the beginning of a bus cycle, and is valid while  $\overline{AS}$  is asserted. R/W only transitions when a write cycle is preceded by a read cycle or vice versa. The signal may remain low for two consecutive write cycles.

### 5.5.1.6 Size Signals

Size signals (SIZ[1:0]) indicate the number of bytes remaining to be transferred during an operand cycle. They are valid while the  $\overline{AS}$  is asserted. **Table 5-9** shows SIZ0 and SIZ1 encoding.

**Table 5-9 Size Signal Encoding**

| SIZ1 | SIZ0 | Transfer Size |

|------|------|---------------|

| 0    | 1    | Byte          |

| 1    | 0    | Word          |

| 1    | 1    | Three bytes   |

| 0    | 0    | Long word     |

#### 5.5.1.7 Function Codes

The CPU generates function code signals (FC[2:0]) to indicate the type of activity occurring on the data or address bus. These signals can be considered address extensions that can be externally decoded to determine which of eight external address spaces is accessed during a bus cycle.

Address space 7 is designated CPU space. CPU space is used for control information not normally associated with read or write bus cycles. Function codes are valid while  $\overline{AS}$  is asserted.

Table 5-10 shows address space encoding.

Table 5-10 Address Space Encoding

| FC2 | FC1 | FC0 | Address Space            |

|-----|-----|-----|--------------------------|

| 0   | 0   | 0   | Reserved                 |

| 0   | 0   | 1   | User data space          |

| 0   | 1   | 0   | User program space       |

| 0   | 1   | 1   | Reserved                 |

| 1   | 0   | 0   | Reserved                 |

| 1   | 0   | 1   | Supervisor data space    |

| 1   | 1   | 0   | Supervisor program space |

| 1   | 1   | 1   | CPU space                |

The supervisor bit in the status register determines whether the CPU is operating in supervisor or user mode. Addressing mode and the instruction being executed determine whether a memory access is to program or data space.

### 5.5.1.8 Data and Size Acknowledge Signals

During normal bus transfers, external devices assert the data and size acknowledge signals (DSACK[1:0]) to indicate port width to the MCU. During a read cycle, these signals tell the MCU to terminate the bus cycle and to latch data. During a write cycle, the signals indicate that an external device has successfully stored data and that the cycle can terminate. DSACK[1:0] can also be supplied internally by chip-select logic. Refer to 5.9 Chip-Selects for more information.

### 5.5.1.9 Bus Error Signal

The bus error signal (BERR) is asserted when a bus cycle is not properly terminated by DSACK or AVEC assertion. It can also be asserted in conjunction with DSACK to indicate a bus error condition, provided it meets the appropriate timing requirements. Refer to **5.6.5** Bus Exception Control Cycles for more information.

The internal bus monitor can generate the BERR signal for internal-to-internal and internal-to-external transfers. In systems with an external bus master, the SIM bus monitor must be disabled and external logic must be provided to drive the BERR pin, because the internal BERR monitor has no information about transfers initiated by an external bus master. Refer to **5.6.6** External Bus Arbitration for more information.

# 5.5.1.10 Halt Signal

The halt signal (HALT) can be asserted by an external device for debugging purposes to cause single bus cycle operation or (in combination with BERR) a retry of a bus cycle in error. The HALT signal affects external bus cycles only. As a result, a program not requiring use of the external bus may continue executing, unaffected by the HALT signal.

When the MCU completes a bus cycle with the HALT signal asserted, DATA[15:0] is placed in a high-impedance state and bus control signals are driven inactive; the address, function code, size, and read/write signals remain in the same state. If HALT is still asserted once bus mastership is returned to the MCU, the address, function code, size, and read/write signals are again driven to their previous states. The MCU does not service interrupt requests while it is halted. Refer to **5.6.5 Bus Exception Control Cycles** for more information.

#### 5.5.1.11 Autovector Signal

The autovector signal (AVEC) can be used to terminate external interrupt acknowledge cycles. Assertion of AVEC causes the CPU32 to generate vector numbers to locate an interrupt handler routine. If AVEC is continuously asserted, autovectors are generated for all external interrupt requests. AVEC is ignored during all other bus cycles. Refer to 5.8 Interrupts for more information. AVEC for external interrupt requests can also be supplied internally by chip-select logic. Refer to 5.9 Chip-

**Selects** for more information. The autovector function is disabled when there is an external bus master. Refer to **5.6.6 External Bus Arbitration** for more information.

### 5.5.2 Dynamic Bus Sizing

The MCU dynamically interprets the port size of an addressed device during each bus cycle, allowing operand transfers to or from 8-bit and 16-bit ports.

During an operand transfer cycle, an external device signals its port size and indicates completion of the bus cycle to the MCU through the use of the DSACK inputs, as shown in **Table 5-11**. Chip-select logic can generate data and size acknowledge signals for an external device. Refer to **5.9 Chip-Selects** for more information.

Table 5-11 Effect of DSACK Signals

| DSACK1 | DSACK0 | Result                                         |

|--------|--------|------------------------------------------------|

| 1      | 1      | Insert Wait States in Current Bus Cycle        |

| 1      | 0      | Complete Cycle — Data Bus Port Size is 8 Bits  |

| 0      | 1      | Complete Cycle — Data Bus Port Size is 16 Bits |

| 0      | 0      | Reserved                                       |

If the CPU is executing an instruction that reads a long-word operand from a 16-bit port, the MCU latches the 16 bits of valid data and then runs another bus cycle to obtain the other 16 bits. The operation for an 8-bit port is similar, but requires four read cycles. The addressed device uses the  $\overline{DSACK}$  signals to indicate the port width. For instance, a 16-bit device always returns  $\overline{DSACK}$  for a 16-bit port (regardless of whether the bus cycle is a byte or word operation).

Dynamic bus sizing requires that the portion of the data bus used for a transfer to or from a particular port size be fixed. A 16-bit port must reside on data bus bits [15:0], and an 8-bit port must reside on data bus bits [15:8]. This minimizes the number of bus cycles needed to transfer data and ensures that the MCU transfers valid data.

The MCU always attempts to transfer the maximum amount of data on all bus cycles. For any bus access, it is assumed that the port is 16 bits wide when the bus cycle begins.

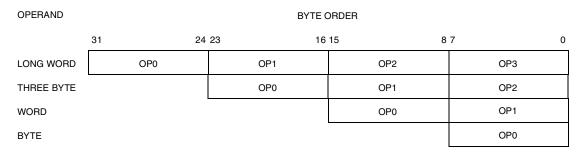

Operand bytes are designated as shown in **Figure 5-9**. OP[0:3] represent the order of access. For instance, OP0 is the most significant byte of a long-word operand, and is accessed first, while OP3, the least significant byte, is accessed last. The two bytes of a word-length operand are OP0 (most significant) and OP1. The single byte of a byte-length operand is OP0.

OPERAND BYTE ORDER

Figure 5-9 Operand Byte Order

### 5.5.3 Operand Alignment

The EBI data multiplexer establishes the necessary connections for different combinations of address and data sizes. The multiplexer takes the two bytes of the 16-bit bus and routes them to their required positions. Positioning of bytes is determined by the size and address outputs. SIZ1 and SIZ0 indicate the number of bytes remaining to be transferred during the current bus cycle. The number of bytes transferred is equal to or less than the size indicated by SIZ1 and SIZ0, depending on port width.

ADDR0 also affects the operation of the data multiplexer. During an operand transfer, ADDR[23:1] indicate the word base address of the portion of the operand to be accessed. ADDR0 indicates the byte offset from the base.

### 5.5.4 Misaligned Operands

The CPU32 uses a basic operand size of 16 bits. An operand is misaligned when it overlaps a word boundary. This is determined by the value of ADDR0. When ADDR0 = 0 (an even address), the address is on a word and byte boundary. When ADDR0 = 1 (an odd address), the address is on a byte boundary only. A byte operand is aligned at any address; a word or long-word operand is misaligned at an odd address. The CPU32 does not support misaligned transfers.

The largest amount of data that can be transferred by a single bus cycle is an aligned word. If the MCU transfers a long-word operand through a 16-bit port, the most significant operand word is transferred on the first bus cycle and the least significant operand word is transferred on a following bus cycle.

### 5.5.5 Operand Transfer Cases

**Table 5-12** is a summary of how operands are aligned for various types of transfers. OPn entries are portions of a requested operand that are read or written during a bus cycle and are defined by SIZ1, SIZ0, and ADDR0 for that bus cycle. The following paragraphs discuss all the allowable transfer cases in detail.

**Table 5-12 Operand Alignment**

| Current<br>Cycle | Transfer Case <sup>1</sup>        | SIZ1 | SIZ0 | ADDR0 | DSACK1 | DSACK0 | DATA<br>[15:8] | DATA<br>[7:0]      | Next<br>Cycle |

|------------------|-----------------------------------|------|------|-------|--------|--------|----------------|--------------------|---------------|

| 1                | Byte to 8-bit port (even)         | 0    | 1    | 0     | 1      | 0      | OP0            | (OP0) <sup>2</sup> | _             |

| 2                | Byte to 8-bit port (odd)          | 0    | 1    | 1     | 1      | 0      | OP0            | (OP0)              | _             |

| 3                | Byte to 16-bit port (even)        | 0    | 1    | 0     | 0      | 1      | OP0            | (OP0)              | _             |

| 4                | Byte to 16-bit port (odd)         | 0    | 1    | 1     | 0      | 1      | (OP0)          | OP0                | _             |

| 5                | Word to 8-bit port                | 1    | 0    | 0     | 1      | 0      | OP0            | (OP1)              | 2             |

| 6                | Word to 16-bit port               | 1    | 0    | 0     | 0      | 1      | OP0            | OP1                | 1             |

| 7                | 3-Byte to 8-bit port <sup>3</sup> | 1    | 1    | 1     | 1      | 0      | OP0            | (OP0)              | 5             |

| 8                | Long word to 8-bit port           | 0    | 0    | 0     | 1      | 0      | OP0            | (OP0)              | 7             |

| 9                | Long word to 16-bit port          | 0    | 0    | 0     | 0      | 1      | OP0            | OP1                | 6             |

#### NOTES:

- 1. All transfers are aligned. The CPU32 does not support misaligned word or long-word transfers.

- 2. Operands in parentheses are ignored by the CPU32 during read cycles.

- 3. Three-Byte transfer cases occur only as a result of a long word to 8-bit port transfer.

### 5.6 Bus Operation

Internal microcontroller modules are typically accessed in two system clock cycles. Regular external bus cycles use handshaking between the MCU and external peripherals to manage transfer size and data. These accesses take three system clock cycles, with no wait states. During regular cycles, wait states can be inserted as needed by bus control logic. Refer to **5.6.2 Regular Bus Cycles** for more information.

Fast termination cycles, which are two-cycle external accesses with no wait states, use chip-select logic to generate handshaking signals internally. Chip-select logic can also be used to insert wait states before internal generation of handshaking signals. Refer to 5.6.3 Fast Termination Cycles and 5.9 Chip-Selects for more information. Bus control signal timing, as well as chip-select signal timing, are specified in APPENDIX A ELECTRICAL CHARACTERISTICS. Refer to the SIM Reference Manual (SIMRM/AD) for more information about each type of bus cycle.

### 5.6.1 Synchronization to CLKOUT

External devices connected to the MCU bus can operate at a clock frequency different from the frequencies of the MCU as long as the external devices satisfy the interface signal timing constraints. Although bus cycles are classified as asynchronous, they are interpreted relative to the MCU system clock output (CLKOUT).

Descriptions are made in terms of individual system clock states, labeled {S0, S1, S2,..., SN}. The designation "state" refers to the logic level of the clock signal and does not correspond to any implemented machine state. A clock cycle consists of two successive states. Refer to **Table A-4** for more information.

Bus cycles terminated by  $\overline{DSACK}$  assertion normally require a minimum of three CLK-OUT cycles. To support systems that use CLKOUT to generate  $\overline{DSACK}$  and other inputs, asynchronous input setup time and asynchronous input hold times are speci-

fied. When these specifications are met, the MCU is guaranteed to recognize the appropriate signal on a specific edge of the CLKOUT signal.

For a read cycle, when assertion of DSACK is recognized on a particular falling edge of the clock, valid data is latched into the MCU on the next falling clock edge, provided that the data meets the data setup time. In this case, the parameter for asynchronous operation can be ignored.

When a system asserts  $\overline{\text{DSACK}}$  for the required window around the falling edge of S2 and obeys the bus protocol by maintaining  $\overline{\text{DSACK}}$  and  $\overline{\text{BERR}}$  or  $\overline{\text{HALT}}$  until and throughout the clock edge that negates  $\overline{\text{AS}}$  (with the appropriate asynchronous input hold time), no wait states are inserted. The bus cycle runs at the maximum speed of three clocks per cycle.

To ensure proper operation in a system synchronized to CLKOUT, when either BERR or BERR and HALT is asserted after DSACK, BERR (or BERR and HALT) assertion must satisfy the appropriate data-in setup and hold times before the falling edge of the clock cycle after DSACK is recognized.

### 5.6.2 Regular Bus Cycles

The following paragraphs contain a discussion of cycles that use external bus control logic. Refer to **5.6.3 Fast Termination Cycles** for information about fast termination cycles.

To initiate a transfer, the MCU asserts an address and the SIZ[1:0] signals. The SIZ signals and ADDR0 are externally decoded to select the active portion of the data bus. Refer to **5.5.2 Dynamic Bus Sizing**. When  $\overline{AS}$ ,  $\overline{DS}$ , and R/W are valid, a peripheral device either places data on the bus (read cycle) or latches data from the bus (write cycle), then asserts a  $\overline{DSACK[1:0]}$  combination that indicates port size.

The DSACK[1:0] signals can be asserted before the data from a peripheral device is valid on a read cycle. To ensure valid data is latched into the MCU, a maximum period between DSACK assertion and DS assertion is specified.

There is no specified maximum for the period between the assertion of AS and DSACK. Although the MCU can transfer data in a minimum of three clock cycles when the cycle is terminated with DSACK, the MCU inserts wait cycles in clock period increments until either DSACK signal goes low.

If bus termination signals remain unasserted, the MCU will continue to insert wait states, and the bus cycle will never end. If no peripheral responds to an access, or if an access is invalid, external logic should assert the BERR or HALT signals to abort the bus cycle (when BERR and HALT are asserted simultaneously, the CPU32 acts as though only BERR is asserted). When enabled, the SIM bus monitor asserts BERR when DSACK response time exceeds a predetermined limit. The bus monitor timeout period is determined by the BMT[1:0] field in SYPCR. The maximum bus monitor timeout period is 64 system clock cycles.

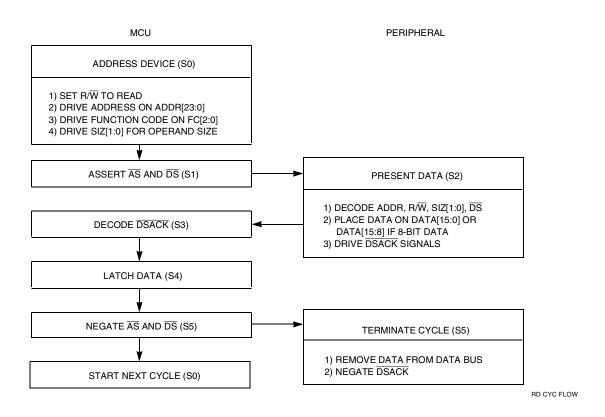

### 5.6.2.1 Read Cycle

During a read cycle, the MCU transfers data from an external memory or peripheral device. If the instruction specifies a long-word or word operation, the MCU attempts to read two bytes at once. For a byte operation, the MCU reads one byte. The portion of the data bus from which each byte is read depends on operand size, peripheral address, and peripheral port size. Figure 5-10 is a flowchart of a word read cycle. Refer to 5.5.2 Dynamic Bus Sizing, 5.5.4 Misaligned Operands, and the SIM Reference Manual (SIMRM/AD) for more information.

Figure 5-10 Word Read Cycle Flowchart

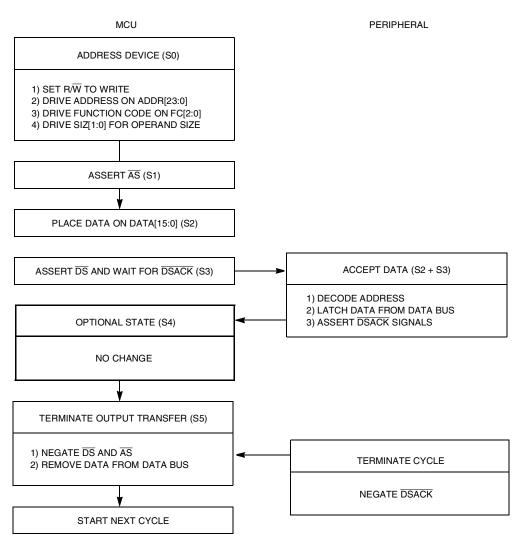

### 5.6.2.2 Write Cycle

During a write cycle, the MCU transfers data to an external memory or peripheral device. If the instruction specifies a long-word or word operation, the MCU attempts to write two bytes at once. For a byte operation, the MCU writes one byte. The portion of the data bus upon which each byte is written depends on operand size, peripheral address, and peripheral port size.

Refer to **5.5.2 Dynamic Bus Sizing** and **5.5.4 Misaligned Operands** for more information. **Figure 5-11** is a flowchart of a write-cycle operation for a word transfer. Refer to the **SIM Reference Manual** (SIMRM/AD) for more information.

WR CYC FLOW

Figure 5-11 Write Cycle Flowchart

# 5.6.3 Fast Termination Cycles

When an external device has a fast access time, the chip-select circuit fast termination option can provide a two-cycle external bus transfer. Because the chip-select circuits are driven from the system clock, the bus cycle termination is inherently synchronized with the system clock.

If multiple chip-selects are to be used to provide control signals to a single device and match conditions occur simultaneously, all MODE, STRB, and associated  $\overline{DSACK}$  fields must be programmed to the same value. This prevents a conflict on the internal bus when the wait states are loaded into the  $\overline{DSACK}$  counter shared by all chip-selects.

5-28

Fast termination cycles use internal handshaking signals generated by the chip-select logic. To initiate a transfer, the MCU asserts an address and the SIZ[1:0] signals. When  $\overline{AS}$ ,  $\overline{DS}$ , and  $R/\overline{W}$  are valid, a peripheral device either places data on the bus (read cycle) or latches data from the bus (write cycle). At the appropriate time, chip-select logic asserts data and size acknowledge signals.

The DSACK option fields in the chip-select option registers determine whether internally generated DSACK or externally generated DSACK is used. The external DSACK lines are always active, regardless of the setting of the DSACK field in the chip-select option registers. Thus, an external DSACK can always terminate a bus cycle. Holding a DSACK line low will cause all external bus cycles to be three-cycle (zero wait states) accesses unless the chip-select option register specifies fast accesses.

For fast termination cycles, the fast termination encoding (%1110) must be used. Refer to **5.9.1 Chip-Select Registers** for information about fast termination setup.

To use fast termination, an external device must be fast enough to have data ready within the specified setup time (for example, by the falling edge of S4). Refer to **Table A-6**, **Figure A-6** and **Figure A-7** for information about fast termination timing.

When fast termination is in use,  $\overline{DS}$  is asserted during read cycles but not during write cycles. The STRB field in the chip-select option register used must be programmed with the address strobe encoding to assert the chip-select signal for a fast termination write.

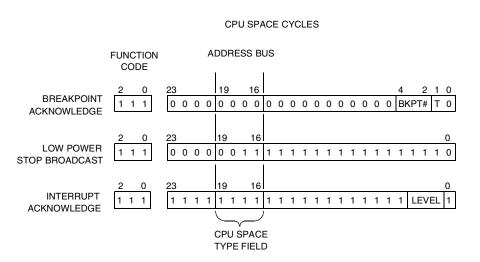

### 5.6.4 CPU Space Cycles

Function code signals FC[2:0] designate which of eight external address spaces is accessed during a bus cycle. Address space 7 is designated CPU space. CPU space is used for control information not normally associated with read or write bus cycles. Function codes are valid only while  $\overline{AS}$  is asserted. Refer to 5.5.1.7 Function Codes for more information on codes and encoding.

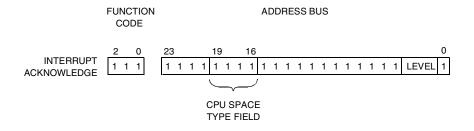

During a CPU space access, ADDR[19:16] are encoded to reflect the type of access being made. Figure 5-12 shows the three encodings used by 68300 family microcontrollers. These encodings represent breakpoint acknowledge (Type \$0) cycles, low power stop broadcast (Type \$3) cycles, and interrupt acknowledge (Type \$F) cycles. Refer to 5.8 Interrupts for information about interrupt acknowledge bus cycles.

CPU SPACE CYC TIM

Figure 5-12 CPU Space Address Encoding

### 5.6.4.1 Breakpoint Acknowledge Cycle

Breakpoints stop program execution at a predefined point during system development. Breakpoints can be used alone or in conjunction with background debug mode. In M68300 microcontrollers, both hardware and software can initiate breakpoints.

The CPU32 BKPT instruction allows the user to insert breakpoints through software. The CPU responds to this instruction by initiating a breakpoint acknowledge read cycle in CPU space. It places the breakpoint acknowledge (%0000) code on ADDR[19:16], the breakpoint number (bits [2:0] of the BKPT opcode) on ADDR[4:2], and %0 (indicating a software breakpoint) on ADDR1.

External breakpoint circuitry decodes the function code and address lines and responds by either asserting BERR or placing an instruction word on the data bus and asserting DSACK. If the bus cycle is terminated by DSACK, the CPU32 reads the instruction on the data bus and inserts the instruction into the pipeline. (For 8-bit ports, this instruction fetch may require two read cycles.)

If the bus cycle is terminated by BERR, the CPU32 then performs illegal instruction exception processing: it acquires the number of the illegal instruction exception vector, computes the vector address from this number, loads the content of the vector address into the PC, and jumps to the exception handler routine at that address.

Assertion of the BKPT input initiates a hardware breakpoint. The CPU32 responds by initiating a breakpoint acknowledge read cycle in CPU space. It places the breakpoint acknowledge code of %0000 on ADDR[19:16], the breakpoint number value of %111 on ADDR[4:2], and ADDR1 is set to %1, indicating a hardware breakpoint.

External breakpoint circuitry decodes the function code and address lines, places an instruction word on the data bus, and asserts BERR. The CPU32 then performs hard-

ware breakpoint exception processing: it acquires the number of the hardware breakpoint exception vector, computes the vector address from this number, loads the content of the vector address into the PC, and jumps to the exception handler routine at that address. If the external device asserts DSACK rather than BERR, the CPU32 ignores the breakpoint and continues processing.

When BKPT assertion is synchronized with an instruction prefetch, processing of the breakpoint exception occurs at the end of that instruction. The prefetched instruction is "tagged" with the breakpoint when it enters the instruction pipeline. The breakpoint exception occurs after the instruction executes. If the pipeline is flushed before the tagged instruction is executed, no breakpoint occurs. When BKPT assertion is synchronized with an operand fetch, exception processing occurs at the end of the instruction during which BKPT is latched.

Refer to the *CPU32 Reference Manual* (CPU32RM/AD) and the *SIM Reference Manual* (SIMRM/AD) for additional information. Breakpoint operation flow for the CPU32 is shown in **Figure 5-13**.

BREAKPOINT OPERATION FLOW PERIPHERAL CPU32 ACKNOWLEDGE BREAKPOINT IF BREAKPOINT INSTRUCTION EXECUTED: 1) SET R/W TO READ 2) SET FUNCTION CODE TO CPU SPACE 3) PLACE CPU SPACE TYPE 0 ON ADDR[19:16] 4) PLACE BREAKPOINT NUMBER ON ADDR[4:2] 5) CLEAR T-BIT (ADDR1) TO ZERO 6) SET SIZE TO WORD 7) ASSERT AS AND DS IF BKPT PIN ASSERTED: 1) SET R/W TO READ 2) SET FUNCTION CODE TO CPU SPACE 3) PLACE CPU SPACE TYPE 0 ON ADDR[19:16] IF BKPT INSTRUCTION EXECUTED: 4) PLACE ALL ONES ON ADDR[4:2] 1) PLACE REPLACEMENT OPCODE ON DATA BUS 5) SET T-BIT (ADDR1) TO ONE 2) ASSERT DSACK 6) SET SIZE TO WORD 7) ASSERT AS AND DS 1) ASSERT BERR TO INITIATE EXCEPTION PROCESSING IF BKPT ASSERTED: IF BREAKPOINT INSTRUCTION EXECUTED AND 1) ASSERT DSACK **DSACK** IS ASSERTED: 1) LATCH DATA 1) ASSERT BERR TO INITIATE EXCEPTION PROCESSING 2) NEGATE AS AND DS 3) GO TO (A) IF BKPT PIN ASSERTED AND DSACK IS ASSERTED: 1) NEGATE  $\overline{\text{AS}}$  AND  $\overline{\text{DS}}$ 2) GO TO (A) IF BERR ASSERTED: 1) NEGATE AS AND DS 2) GO TO (B) (B) IF BKPT INSTRUCTION EXECUTED: 1) NEGATE DSACK or BERR 1) PLACE LATCHED DATA IN INSTRUCTION PIPELINE 2) CONTINUE PROCESSING IF BKPT PIN ASSERTED: 1) CONTINUE PROCESSING IF BKPT INSTRUCTION EXECUTED: 1) INITIATE ILLEGAL INSTRUCTION PROCESSING IF BKPT PIN ASSERTED: 1) INITIATE HARDWARE BREAKPOINT PROCESSING

Figure 5-13 Breakpoint Operation Flowchart

5-32

BREAKPOINT OPERATION FLOW

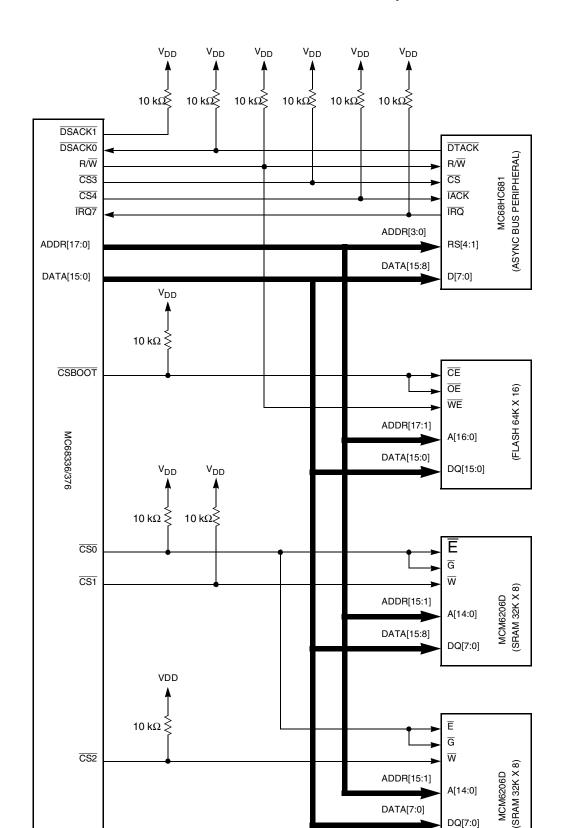

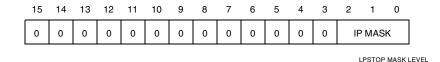

### 5.6.4.2 LPSTOP Broadcast Cycle

Low-power stop mode is initiated by the CPU32. Individual modules can be stopped by setting the STOP bits in each module configuration register, or the SIM can turn off system clocks after execution of the LPSTOP instruction. When the CPU32 executes LPSTOP, an LPSTOP broadcast cycle is generated. The SIM brings the MCU out of low-power stop mode when either an interrupt of higher priority than the stored mask or a reset occurs. Refer to 5.3.4 Low-Power Operation and 4.8.2.1 Low-Power Stop (LPSTOP) for more information.

During an LPSTOP broadcast cycle, the CPU32 performs a CPU space write to address \$3FFFE. This write puts a copy of the interrupt mask value in the clock control logic. The mask is encoded on the data bus as shown in **Figure 5-14**. The LPSTOP CPU space cycle is shown externally (if the bus is available) as an indication to external devices that the MCU is going into low-power stop mode. The SIM provides an internally generated DSACK response to this cycle. The timing of this bus cycle is the same as for a fast termination write cycle. If the bus is not available (arbitrated away), the LPSTOP broadcast cycle is not shown externally.

#### NOTE

BERR during the LPSTOP broadcast cycle is ignored.

Figure 5-14 LPSTOP Interrupt Mask Level

### 5.6.5 Bus Exception Control Cycles

An external device or a chip-select circuit must assert at least one of the DSACK[1:0] signals or the AVEC signal to terminate a bus cycle normally. Bus error processing occurs when bus cycles are not terminated in the expected manner. The SIM bus monitor can be used to generate BERR internally, causing a bus error exception to be taken. Bus cycles can also be terminated by assertion of the external BERR or HALT pins signal, or by assertion of the two signals simultaneously.

Acceptable bus cycle termination sequences are summarized as follows. The case numbers refer to **Table 5-13**, which indicates the results of each type of bus cycle termination.

- Normal Termination

- DSACK is asserted; BERR and HALT remain negated (case 1).

- Halt Termination

- HALT is asserted at the same time or before DSACK, and BERR remains negated (case 2).

- Bus Error Termination

- BERR is asserted in lieu of, at the same time as, or before DSACK (case 3).

or after DSACK (case 4), and HALT remains negated; BERR is negated at the same time or after DSACK.

- Retry Termination

- HALT and BERR are asserted in lieu of, at the same time as, or before DSACK (case 5) or after DSACK (case 6); BERR is negated at the same time or after DSACK; HALT may be negated at the same time or after BERR.

**Table 5-13** shows various combinations of control signal sequences and the resulting bus cycle terminations.

Table 5-13 DSACK, BERR, and HALT Assertion Results

| Case<br>Number | Control Signal        | Asserted on Rising<br>Edge of State     |                                        | Result                                                                            |  |  |

|----------------|-----------------------|-----------------------------------------|----------------------------------------|-----------------------------------------------------------------------------------|--|--|

| Number         |                       | N <sup>1</sup>                          | N + 2                                  |                                                                                   |  |  |

| 1              | DSACK<br>BERR<br>HALT | A <sup>2</sup><br>NA <sup>3</sup><br>NA | S <sup>4</sup><br>NA<br>X <sup>5</sup> | Normal termination.                                                               |  |  |

| 2              | DSACK<br>BERR<br>HALT | A<br>NA<br>A/S                          | S A S                                  | Halt termination: normal cycle terminate and halt. Continue when HALT is negated. |  |  |

| 3              | DSACK<br>BERR<br>HALT | NA/A<br>A<br>NA                         | X<br>S<br>X                            | Bus error termination: terminate and take bus error exception, possibly deferred. |  |  |

| 4              | DSACK<br>BERR<br>HALT | A<br>A<br>NA                            | X<br>S<br>NA                           | Bus error termination: terminate and take bus error exception, possibly deferred. |  |  |

| 5              | DSACK<br>BERR<br>HALT | NA/A<br>A<br>A/S                        | X<br>S<br>S                            | Retry termination: terminate and retry when HALT is negated.                      |  |  |

| 6              | DSACK<br>BERR<br>HALT | A<br>NA<br>NA                           | X<br>A<br>A                            | Retry termination: terminate and retry when HALT is negated.                      |  |  |

#### NOTES:

- 1. N = The number of current even bus state (S2, S4, etc.).

- 2. A = Signal is asserted in this bus state.

- 3. NA = Signal is not asserted in this state.

- 4. X = Don't care.

- 5. S = Signal was asserted in previous state and remains asserted in this state.

To control termination of a bus cycle for a retry or a bus error condition properly, DSACK, BERR, and HALT must be asserted and negated with the rising edge of the MCU clock. This ensures that when two signals are asserted simultaneously, the required setup time and hold time for both of them are met for the same falling edge of the MCU clock. Refer to **APPENDIX A ELECTRICAL CHARACTERISTICS** for timing requirements. External circuitry that provides these signals must be designed with these constraints in mind, or else the internal bus monitor must be used.

$\overline{\text{DSACK}}$ ,  $\overline{\text{BERR}}$ , and  $\overline{\text{HALT}}$  may be negated after  $\overline{\text{AS}}$  is negated.

#### WARNING

If DSACK or BERR remain asserted into S2 of the next bus cycle, that cycle may be terminated prematurely.

#### **5.6.5.1 Bus Errors**

The CPU32 treats bus errors as a type of exception. Bus error exception processing begins when the CPU32 detects assertion of the IMB BERR signal (by the internal bus monitor or an external source) while the HALT signal remains negated.

BERR assertions do not force immediate exception processing. The signal is synchronized with normal bus cycles and is latched into the CPU32 at the end of the bus cycle in which it was asserted. Because bus cycles can overlap instruction boundaries, bus error exception processing may not occur at the end of the instruction in which the bus cycle begins. Timing of BERR detection/acknowledge is dependent upon several factors:

- Which bus cycle of an instruction is terminated by assertion of BERR.

- The number of bus cycles in the instruction during which BERR is asserted.

- The number of bus cycles in the instruction following the instruction in which BERR is asserted.

- Whether BERR is asserted during a program space access or a data space access.

Because of these factors, it is impossible to predict precisely how long after occurrence of a bus error the bus error exception is processed.

#### **CAUTION**

The external bus interface does not latch data when an external bus cycle is terminated by a bus error. When this occurs during an instruction prefetch, the IMB precharge state (bus pulled high, or \$FF) is latched into the CPU32 instruction register, with indeterminate results.

### 5.6.5.2 Double Bus Faults

Exception processing for bus error exceptions follows the standard exception processing sequence. Refer to **4.9 Exception Processing** for more information. However, a special case of bus error, called double bus fault, can abort exception processing.

BERR assertion is not detected until an instruction is complete. The BERR latch is cleared by the first instruction of the BERR exception handler. Double bus fault occurs in three ways:

- 1. When bus error exception processing begins and a second BERR is detected before the first instruction of the exception handler is executed.

- 2. When one or more bus errors occur before the first instruction after a reset exception is executed.

- 3. A bus error occurs while the CPU32 is loading information from a bus error stack frame during a return from exception (RTE) instruction.

Multiple bus errors within a single instruction that can generate multiple bus cycles cause a single bus error exception after the instruction has been executed.

Immediately after assertion of a second BERR, the MCU halts and drives the HALT line low. Only a reset can restart a halted MCU. However, bus arbitration can still occur. Refer to **5.6.6 External Bus Arbitration** for more information. A bus error or address error that occurs after exception processing has been completed (during the execution of the exception handler routine, or later) does not cause a double bus fault. The MCU continues to retry the same bus cycle as long as the external hardware requests it.

### 5.6.5.3 Retry Operation

When an external device asserts BERR and HALT during a bus cycle, the MCU enters the retry sequence. A delayed retry can also occur. The MCU terminates the bus cycle, places the  $\overline{AS}$  and  $\overline{DS}$  signals in their inactive state, and does not begin another bus cycle until the BERR and HALT signals are negated by external logic. After a synchronization delay, the MCU retries the previous cycle using the same address, function codes, data (for a write), and control signals. The  $\overline{BERR}$  signal should be negated before S2 of the read cycle to ensure correct operation of the retried cycle.

If BR, BERR, and HALT are all asserted on the same cycle, the EBI will enter the rerun sequence but first relinquishes the bus to an external master. Once the external master returns the bus and negates BERR and HALT, the EBI runs the previous bus cycle. This feature allows an external device to correct the problem that caused the bus error and then try the bus cycle again.

The MCU retries any read or write cycle of an indivisible read-modify-write operation separately. RMC remains asserted during the entire retry sequence. The MCU will not relinquish the bus while RMC is asserted. Any device that requires the MCU to give up the bus and retry a bus cycle during a read-modify-write cycle must assert BERR and BR only (HALT must remain negated). The bus error handler software should examine the read-modify-write bit in the special status word and take the appropriate action to resolve this type of fault when it occurs. Refer to the *SIM Reference Manual* (SIMRM/AD) for additional information on read-modify-write and retry operations.

### 5.6.5.4 Halt Operation

When HALT is asserted while BERR is not asserted, the MCU halts external bus activity after negation of DSACK. The MCU may complete the current word transfer in progress. For a long-word to byte transfer, this could be after S2 or S4. For a word to byte transfer, activity ceases after S2.

Negating and reasserting HALT according to timing requirements provides single-step (bus cycle to bus cycle) operation. The HALT signal affects external bus cycles only, so that a program that does not use the external bus can continue executing.

During dynamically-sized 8-bit transfers, external bus activity may not stop at the next cycle boundary. Occurrence of a bus error while HALT is asserted causes the CPU32 to initiate a retry sequence.

When the MCU completes a bus cycle while the HALT signal is asserted, the data bus goes into a high-impedance state and the AS and DS signals are driven to their inactive states. Address, function code, size, and read/write signals remain in the same state.

The halt operation has no effect on bus arbitration. However, when external bus arbitration occurs while the MCU is halted, address and control signals go into a high-impedance state. If HALT is still asserted when the MCU regains control of the bus, address, function code, size, and read/write signals revert to the previous driven states. The MCU cannot service interrupt requests while halted.

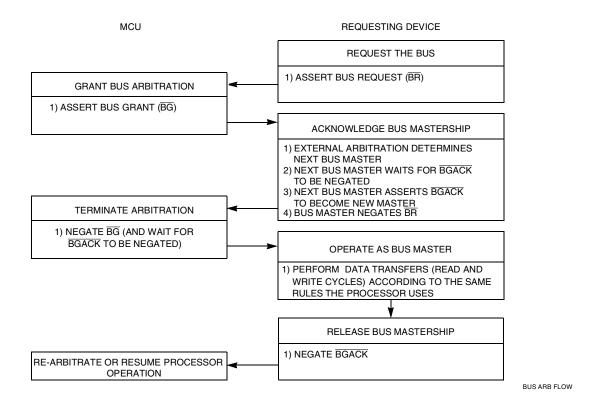

#### 5.6.6 External Bus Arbitration

The MCU bus design provides for a single bus master at any one time. Either the MCU or an external device can be master. Bus arbitration protocols determine when an external device can become bus master. Bus arbitration requests are recognized during normal processing, HALT assertion, and when the CPU32 has halted due to a double bus fault.

The bus controller in the MCU manages bus arbitration signals so that the MCU has the lowest priority. External devices that need to obtain the bus must assert bus arbitration signals in the sequences described in the following paragraphs.

Systems that include several devices that can become bus master require external circuitry to assign priorities to the devices, so that when two or more external devices attempt to become bus master at the same time, the one having the highest priority becomes bus master first. The protocol sequence is:

- 1. An external device asserts the bus request signal (BR);

- 2. The MCU asserts the bus grant signal ( $\overline{BG}$ ) to indicate that the bus is available;

- 3. An external device asserts the bus grant acknowledge (BGACK) signal to indicate that it has assumed bus mastership.

$\overline{BR}$  can be asserted during a bus cycle or between cycles.  $\overline{BG}$  is asserted in response to  $\overline{BR}$ . To guarantee operand coherency,  $\overline{BG}$  is only asserted at the end of operand transfer. Additionally,  $\overline{BG}$  is not asserted until the end of an indivisible read-modify-write operation (when  $\overline{RMC}$  is negated).

If more than one external device can be bus master, required external arbitration must begin when a requesting device receives BG. An external device must assert BGACK when it assumes mastership, and must maintain BGACK assertion as long as it is bus master.