# APPENDIX D REGISTER SUMMARY

This appendix contains address maps, register diagrams, and bit/field definitions for MC68336 and MC68376 microcontrollers. More detailed information about register function is provided in the appropriate sections of the manual.

Except for central processing unit resources, information is presented in the intermodule bus address order shown in **Table D-1**.

| Module                | Size<br>(Bytes) | Base<br>Address |

|-----------------------|-----------------|-----------------|

| SIM                   | 128             | \$YFFA00        |

| SRAM                  | 8               | \$YFFB40        |

| MRM (MC68376 Only)    | 32              | \$YFF820        |

| QADC                  | 512             | \$YFF200        |

| QSM                   | 512             | \$YFFC00        |

| CTM4                  | 256             | \$YFF400        |

| TPU                   | 512             | \$YFFE00        |

| TPURAM                | 64              | \$YFFB00        |

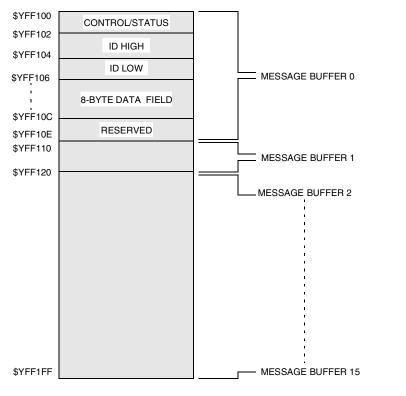

| TouCAN (MC68376 Only) | 384             | \$YFF080        |

# Table D-1 Module Address Map

Control registers for all the modules in the microcontroller are mapped into a 4-Kbyte block. The state of the module mapping (MM) bit in the SIM configuration register (SIMCR) determines where the control register block is located in the system memory map. When MM = 0, register addresses range from \$7FF000 to \$7FFFFF; when MM = 1, register addresses range from \$FFF000 to \$FFFFFF.

In the module memory maps in this appendix, the "Access" column specifies which registers are accessible when the CPU32 is in supervisor mode only and which registers can be assigned to either supervisor or user mode.

# D.1 Central Processor Unit

CPU32 registers are not part of the module address map. **Figure D-1** and **Figure D-2** show a functional representation of CPU32 resources.

# D.1.1 CPU32 Register Model

| 31 | 16 15 | 87 | 0 |          |                         |

|----|-------|----|---|----------|-------------------------|

|    |       |    |   | D0       |                         |

|    |       |    |   | D1       |                         |

|    |       |    |   | D2       |                         |

|    |       |    |   | D3       | DATA REGISTERS          |

|    |       |    |   | D4       |                         |

|    |       |    |   | D5       |                         |

|    |       |    |   | D6       |                         |

|    |       |    |   | D7       |                         |

| 31 | 16 15 |    | 0 |          |                         |

|    |       |    |   | A0       |                         |

|    |       |    |   | A1       |                         |

|    |       |    |   | A2       |                         |

|    |       |    |   | A3       | ADDRESS REGISTERS       |

|    |       |    |   | A4       |                         |

|    |       |    |   | A5       |                         |

|    |       |    |   | A6       |                         |

| 31 | 16 15 |    | 0 |          |                         |

|    |       |    |   | A7 (SSP) | USER STACK POINTER      |

| 31 |       |    | 0 |          |                         |

|    |       |    |   | PC       | PROGRAM COUNTER         |

|    |       | 7  | 0 |          |                         |

|    |       |    |   | CCR      | CONDITION CODE REGISTER |

|    |       |    |   |          | CPU32 USER PROG MODEL   |

Figure D-1 User Programming Model

For More Information On This Product, Go to: www.freescale.com

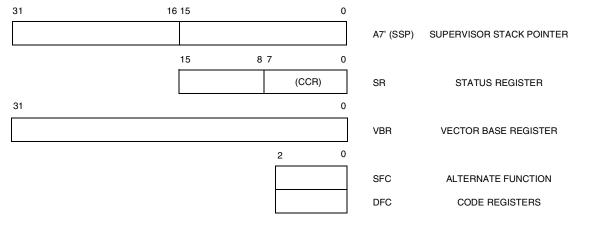

CPU32 SUPV PROG MODEL

#### Figure D-2 Supervisor Programming Model Supplement

#### **D.1.2 Status Register**

#### SR — Status Register

| 15     | 14   | 13 | 12 | 11 | 10 | 9       | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|--------|------|----|----|----|----|---------|---|---|---|---|---|---|---|---|---|

| T[1    | [0:1 | S  | 0  | 0  |    | IP[2:0] |   | 0 | 0 | 0 | Х | Ν | Z | V | С |

| RESET: |      |    |    |    |    |         |   |   |   |   |   |   |   |   |   |

| 0      | 0    | 1  | 0  | 0  | 1  | 1       | 1 | 0 | 0 | 0 | U | U | U | U | U |

The status register (SR) contains condition codes, an interrupt priority mask, and three control bits. The condition codes are contained in the condition code register (CCR), the lower byte of the SR. (The lower and upper bytes of the status register are also referred to as the user and system bytes, respectively.) In user mode, only the CCR is available. In supervisor mode, software can access the full status register.

#### T[1:0] — Trace Enable

This field places the processor in one of two tracing modes or disables tracing. Refer to **Table D-2**.

| T[1:0] | Response                       |

|--------|--------------------------------|

| 00     | No tracing                     |

| 01     | Trace on change of flow        |

| 10     | Trace on instruction execution |

| 11     | Undefined; reserved            |

#### Table D-2 T[1:0] Encoding

#### S — Supervisor/User State

0 = CPU operates at user privilege level

1 = CPU operates at supervisor privilege level

IP[2:0] — Interrupt Priority Mask

MC68336/376 USER'S MANUAL **REGISTER SUMMARY**

Rev. 15 Oct 2000 For More Information On This Product, Go to: www.freescale.com

The priority value in this field (0 to 7) is used to mask interrupts.

#### X — Extend Flag

Used in multiple-precision arithmetic operations. In many instructions, it is set to the same value as the C bit.

N — Negative Flag

Set when the MSB of a result register is set.

Z — Zero Flag

Set when all bits of a result register are zero.

V — Overflow Flag

Set when two's complement overflow occurs as the result of an operation.

C — Carry Flag

Set when a carry or borrow occurs during an arithmetic operation. Also used during shift and rotate instructions to facilitate multiple word operations.

# **D.2 System Integration Module**

Table D-3 shows the SIM address map. The column labeled "Access" indicates the privilege level at which the CPU32 must be operating to access the register. A designation of "S" indicates that supervisor mode is required. A designation of "S/U" indicates that the register can be programmed for either supervisor mode access or unrestricted access.

| Access | Address <sup>1</sup> | 15 8                 | 7 0                               |  |  |  |  |  |

|--------|----------------------|----------------------|-----------------------------------|--|--|--|--|--|

| S      | \$YFFA00             | SIM Module Configur  | ration Register (SIMCR)           |  |  |  |  |  |

| S      | \$YFFA02             | SIM Test Re          | gister (SIMTR)                    |  |  |  |  |  |

| S      | \$YFFA04             | Clock Synthesizer Co | ontrol Register (SYNCR)           |  |  |  |  |  |

| S      | \$YFFA06             | Not Used             | Reset Status Register (RSR)       |  |  |  |  |  |

| S      | \$YFFA08             | SIM Test Regi        | ster E (SIMTRE)                   |  |  |  |  |  |

| S      | \$YFFA0A             | Not                  | Used                              |  |  |  |  |  |

| S      | \$YFFA0C             | Not                  | Used                              |  |  |  |  |  |

| S      | \$YFFA0E             | Not Used             |                                   |  |  |  |  |  |

| S/U    | \$YFFA10             | Not Used             | Port E Data (PORTE0)              |  |  |  |  |  |

| S/U    | \$YFFA12             | Not Used             | Port E Data (PORTE1)              |  |  |  |  |  |

| S/U    | \$YFFA14             | Not Used             | Port E Data Direction (DDRE)      |  |  |  |  |  |

| S      | \$YFFA16             | Not Used             | Port E Pin Assignment (PEPAR)     |  |  |  |  |  |

| S/U    | \$YFFA18             | Not Used             | Port F Data (PORTF0)              |  |  |  |  |  |

| S/U    | \$YFFA1A             | Not Used             | Port F Data (PORTF1)              |  |  |  |  |  |

| S/U    | \$YFFA1C             | Not Used             | Port F Data Direction (DDRF)      |  |  |  |  |  |

| S      | \$YFFA1E             | Not Used             | Port F Pin Assignment (PFPAR)     |  |  |  |  |  |

| S      | \$YFFA20             | Not Used             | System Protection Control (SYPCR) |  |  |  |  |  |

| S      | \$YFFA22             | Periodic Interrupt C | ontrol Register (PICR)            |  |  |  |  |  |

# Table D-3 SIM Address Map

MC68336/376 **USER'S MANUAL**

#### **REGISTER SUMMARY**

MOTOROLA

Rev. 15 Oct 2000 For More Information On This Product. Go to: www.freescale.com

D-4

## Table D-3 SIM Address Map (Continued)

| Access | Address <sup>1</sup> | 15 8                 | 7                               |  |  |  |  |  |  |  |

|--------|----------------------|----------------------|---------------------------------|--|--|--|--|--|--|--|

| S      | \$YFFA24             | Periodic Interrupt T | iming Register (PITR)           |  |  |  |  |  |  |  |

| S      | \$YFFA26             | Not Used             | Software Service (SWSR)         |  |  |  |  |  |  |  |

| S      | \$YFFA28             | Not                  | Used                            |  |  |  |  |  |  |  |

| S      | \$YFFA2A             | Not                  | Used                            |  |  |  |  |  |  |  |

| S      | \$YFFA2C             | Not                  | Used                            |  |  |  |  |  |  |  |

| S      | \$YFFA2E             | Not                  | Used                            |  |  |  |  |  |  |  |

| S      | \$YFFA30             | Test Module Maste    | er Shift A (TSTMSRA)            |  |  |  |  |  |  |  |

| S      | \$YFFA32             | Test Module Maste    | er Shift B (TSTMSRB)            |  |  |  |  |  |  |  |

| S      | \$YFFA34             | Test Module Sh       | Test Module Shift Count (TSTSC) |  |  |  |  |  |  |  |

| S      | \$YFFA36             | Test Module Repeti   | tion Counter (TSTRC)            |  |  |  |  |  |  |  |

| S      | \$YFFA38             | Test Module          | Control (CREG)                  |  |  |  |  |  |  |  |

| S/U    | \$YFFA3A             | Test Module Di       | stributed (DREG)                |  |  |  |  |  |  |  |

|        | \$YFFA3C             | Not                  | Used                            |  |  |  |  |  |  |  |

|        | \$YFFA3E             | Not                  | Used                            |  |  |  |  |  |  |  |

| S/U    | \$YFFA40             | Not Used             | Port C Data (PORTC)             |  |  |  |  |  |  |  |

|        | \$YFFA42             | Not                  | Used                            |  |  |  |  |  |  |  |

| S      | \$YFFA44             | Chip-Select Pin As   | ssignment (CSPAR0)              |  |  |  |  |  |  |  |

| S      | \$YFFA46             | Chip-Select Pin As   | ssignment (CSPAR1)              |  |  |  |  |  |  |  |

| S      | \$YFFA48             | Chip-Select Base     | e Boot (CSBARBT)                |  |  |  |  |  |  |  |

| S      | \$YFFA4A             | Chip-Select Option   | on Boot (CSORBT)                |  |  |  |  |  |  |  |

| S      | \$YFFA4C             | Chip-Select B        | ase 0 (CSBAR0)                  |  |  |  |  |  |  |  |

| S      | \$YFFA4E             | Chip-Select O        | ption 0 (CSOR0)                 |  |  |  |  |  |  |  |

| S      | \$YFFA50             | Chip-Select B        | ase 1 (CSBAR1)                  |  |  |  |  |  |  |  |

| S      | \$YFFA52             | Chip-Select O        | ption 1 (CSOR1)                 |  |  |  |  |  |  |  |

| S      | \$YFFA54             | Chip-Select B        | ase 2 (CSBAR2)                  |  |  |  |  |  |  |  |

| S      | \$YFFA56             | Chip-Select O        | ption 2 (CSOR2)                 |  |  |  |  |  |  |  |

| S      | \$YFFA58             | Chip-Select B        | ase 3 (CSBAR3)                  |  |  |  |  |  |  |  |

| S      | \$YFFA5A             | Chip-Select O        | ption 3 (CSOR3)                 |  |  |  |  |  |  |  |

| S      | \$YFFA5C             | Chip-Select B        | ase 4 (CSBAR4)                  |  |  |  |  |  |  |  |

| S      | \$YFFA5E             | Chip-Select O        | ption 4 (CSOR4)                 |  |  |  |  |  |  |  |

| S      | \$YFFA60             | Chip-Select B        | ase 5 (CSBAR5)                  |  |  |  |  |  |  |  |

| S      | \$YFFA62             | Chip-Select O        | ption 5 (CSOR5)                 |  |  |  |  |  |  |  |

| S      | \$YFFA64             | Chip-Select B        | ase 6 (CSBAR6)                  |  |  |  |  |  |  |  |

| S      | \$YFFA66             | Chip-Select O        | ption 6 (CSOR6)                 |  |  |  |  |  |  |  |

| S      | \$YFFA68             | Chip-Select B        | ase 7 (CSBAR7)                  |  |  |  |  |  |  |  |

| S      | \$YFFA6A             | Chip-Select O        | ption 7 (CSOR7)                 |  |  |  |  |  |  |  |

| S      | \$YFFA6C             | Chip-Select B        | ase 8 (CSBAR8)                  |  |  |  |  |  |  |  |

| S      | \$YFFA6E             | Chip-Select O        | ption 8 (CSOR8)                 |  |  |  |  |  |  |  |

| S      | \$YFFA70             | Chip-Select B        | ase 9 (CSBAR9)                  |  |  |  |  |  |  |  |

| S      | \$YFFA72             | Chip-Select O        | ption 9 (CSOR9)                 |  |  |  |  |  |  |  |

| S      | \$YFFA74             |                      | se 10 (CSBAR10)                 |  |  |  |  |  |  |  |

| S      | \$YFFA76             | •                    | tion 10 (CSOR10)                |  |  |  |  |  |  |  |

MC68336/376 USER'S MANUAL

#### **REGISTER SUMMARY**

MOTOROLA

Rev. 15 Oct 2000 For More Information On This Product, Go to: www.freescale.com D-5

| Access | Address <sup>1</sup> | 15 | 8        | 7 | 0 |  |  |  |  |  |

|--------|----------------------|----|----------|---|---|--|--|--|--|--|

|        | \$YFFA78             |    | Not Used |   |   |  |  |  |  |  |

|        | \$YFFA7A             |    | Not Used |   |   |  |  |  |  |  |

|        | \$YFFA7C             |    | Not Used |   |   |  |  |  |  |  |

|        | \$YFFA7E             |    | Not Used |   |   |  |  |  |  |  |

Table D-3 SIM Address Map (Continued)

\$TFFA00

NOTES:

1. Y = M111, where M is the logic state of the module mapping (MM) bit in the SIMCR.

# **D.2.1 SIM Configuration Register**

## SIMCR — SIM Configuration Register

| 1 |            |           |           |    |                   |    |      |        |      |    |   |   | • |      |        |   |  |

|---|------------|-----------|-----------|----|-------------------|----|------|--------|------|----|---|---|---|------|--------|---|--|

|   | 15         | 14        | 13        | 12 | 11                | 10 | 9    | 8      | 7    | 6  | 5 | 4 | 3 | 2    | 1      | 0 |  |

|   | EX-<br>OFF | FRZS<br>W | FRZB<br>M | 0  | RSVD <sup>1</sup> | 0  | SHEN | N[1:0] | SUPV | MM | 0 | 0 |   | IARE | 8[3:0] |   |  |

|   | RE         | SET:      |           |    |                   |    |      |        |      |    |   |   |   |      |        |   |  |

|   | 0          | 0         | 0         | 0  | DATA11            | 0  | 0    | 0      | 1    | 1  | 0 | 0 | 1 | 1    | 1      | 1 |  |

NOTES:

1. This bit must be left at zero. Pulling DATA11 high during reset ensures this bit remains zero. A one in this bit could allow the MCU to enter an unsupported operating mode.

SIMCR controls system configuration. SIMCR can be read or written at any time, except for the module mapping (MM) bit, which can only be written once.

## EXOFF — External Clock Off

- 0 = The CLKOUT pin is driven during normal operation.

- 1 = The CLKOUT pin is placed in a high-impedance state.

- FRZSW Freeze Software Enable

- 0 = When FREEZE is asserted, the software watchdog and periodic interrupt timer counters continue to run.

- 1 = When FREEZE is asserted, the software watchdog and periodic interrupt timer counters are disabled, preventing interrupts during background debug mode.

### FRZBM — Freeze Bus Monitor Enable

- 0 = When FREEZE is asserted, the bus monitor continues to operate.

- 1 = When FREEZE is asserted, the bus monitor is disabled.

### SHEN[1:0] — Show Cycle Enable

The SHEN field determines how the external bus is driven during internal transfer operations. A show cycle allows internal transfers to be monitored externally.

**Table D-4** shows whether show cycle data is driven externally, and whether external bus arbitration can occur. To prevent bus conflict, external peripherals must not be enabled during show cycles.

## Table D-4 Show Cycle Enable Bits

| SHEN[1:0] | Action                                                                                           |

|-----------|--------------------------------------------------------------------------------------------------|

| 00        | Show cycles disabled, external arbitration enabled                                               |

| 01        | Show cycles enabled, external arbitration disabled                                               |

| 10        | Show cycles enabled, external arbitration enabled                                                |

| 11        | Show cycles enabled, external arbitration enabled;<br>internal activity is halted by a bus grant |

SUPV — Supervisor/Unrestricted Data Space

The SUPV bit places the SIM global registers in either supervisor or user data space.

- 0 = Registers with access controlled by the SUPV bit are accessible in either supervisor or user mode.

- 1 = Registers with access controlled by the SUPV bit are restricted to supervisor access only.

# MM — Module Mapping

- 0 = Internal modules are addressed from \$7FF000 \$7FFFFF.

- 1 = Internal modules are addressed from \$FFF000 \$FFFFFF.

# IARB[3:0] — Interrupt Arbitration ID

Each module that can generate interrupts, including the SIM, has an IARB field. Each IARB field can be assigned a value from \$0 to \$F. During an interrupt acknowledge cycle, IARB permits arbitration among simultaneous interrupts of the same priority level. The reset value of the SIM IARB field is \$F. This prevents SIM interrupts from being discarded during system initialization.

# D.2.2 System Integration Test Register

# **SIMTR** — System Integration Test Register

### \$YFFA02

0

Т

0

1

Used for factory test only.

# **D.2.3 Clock Synthesizer Control Register**

#### **SYNCR** — Clock Synthesizer Control Register SYFFA04 2 15 14 13 12 11 10 9 6 5 3 SLOC RSVD STSI STEX

| W   | Х    | Y[5:0] |   |   |   |   |   | EDIV | 0 | 0 | RSVD <sup>1</sup> | K | 1 | M |  |

|-----|------|--------|---|---|---|---|---|------|---|---|-------------------|---|---|---|--|

| RES | SET: |        |   |   |   |   |   |      |   |   |                   |   |   |   |  |

| 0   | 0    | 1      | 1 | 1 | 1 | 1 | 1 | 0    | 0 | 0 | 0                 | U | 0 | 0 |  |

#### NOTES:

1. Ensure that initialization software does not change the value of these bits. They should always be zero.

SYNCR determines system clock operating frequency and operation during low-power stop mode. Clock frequency is determined by SYNCR bit settings as follows:

$$f_{sys} = \frac{f_{ref}}{128} [4(Y+1)(2^{(2W+X)})]$$

# W — Frequency Control (VCO)

This bit controls a prescaler tap in the synthesizer feedback loop. Setting this bit increases the VCO speed by a factor of four. VCO relock delay is required.

X — Frequency Control (Prescaler)

This bit controls a divide by two prescaler that is not in the synthesizer feedback loop. Setting the bit doubles clock speed without changing the VCO speed. No VCO relock delay is required.

Y[5:0] — Frequency Control (Counter)

The Y field controls the modulus down counter in the synthesizer feedback loop, causing it to divide by a value of Y + 1. VCO relock delay is required.

- EDIV E Clock Divide Rate

- 0 = ECLK frequency is system clock divided by 8.

- 1 = ECLK frequency is system clock divided by 16.

ECLK is an external M6800 bus clock available on ADDR23.

# SLOCK — Synthesizer Lock Flag

- 0 = VCO is enabled, but has not locked.

- 1 = VCO has locked on the desired frequency or VCO is disabled.

The MCU remains in reset until the synthesizer locks, but SLOCK does not indicate synthesizer lock status until after the user writes to SYNCR.

# STSIM — Stop Mode SIM Clock

- 0 = When LPSTOP is executed, the SIM clock is driven from the crystal oscillator and the VCO is turned off to conserve power.

- 1 = When LPSTOP is executed, the SIM clock is driven from the VCO.

- STEXT Stop Mode External Clock

- 0 = When LPSTOP is executed, the CLKOUT signal is held negated to conserve power.

- 1 = When LPSTOP is executed and EXOFF | 1 in SIMCR, the CLKOUT signal is driven from the SIM clock, as determined by the state of the STSIM bit.

# D.2.4 Reset Status Register

| <b>RSR</b> — Reset Status Register <b>\$YFFA</b> |   |     |     |    |     |   |      |     | FA07 |

|--------------------------------------------------|---|-----|-----|----|-----|---|------|-----|------|

| 15                                               | 8 | 7   | 6   | 5  | 4   | 3 | 2    | 1   | 0    |

| NOT USED                                         |   | EXT | POW | SW | HLT | 0 | RSVD | SYS | TST  |

RSR contains a status bit for each reset source in the MCU. RSR is updated when the MCU comes out of reset. A set bit indicates what type of reset occurred. If multiple sources assert reset signals at the same time, more than one bit in RSR may be set. This register can be read at any time; writes have no effect.

| MC68336/376   |  |

|---------------|--|

| USER'S MANUAL |  |

REGISTER SUMMARY Rev. 15 Oct 2000 For More Information On This Product, Go to: www.freescale.com MOTOROLA D-8

EXT — External Reset Reset caused by the RESET pin.

- POW Power-Up Reset Reset caused by the power-up reset circuit.

- SW Software Watchdog Reset Reset caused by the software watchdog circuit.

- HLT Halt Monitor Reset Reset caused by the halt monitor.

- SYS System Reset Reset caused by a RESET instruction.

- TST Test Submodule Reset Reset caused by the test submodule. Used during system test only.

# D.2.5 System Integration Test Register (ECLK)

| SIMTRE — System Integration Test Register (ECLK) | \$YFFA08 |

|--------------------------------------------------|----------|

| Used for factory test only.                      |          |

### D.2.6 Port E Data Register

| <b>PORTE0</b> — Port E0 Data Register<br><b>PORTE1</b> — Port E1 Data Register |   |     |     |     |     |     |     | •   | FA11<br>FA13 |

|--------------------------------------------------------------------------------|---|-----|-----|-----|-----|-----|-----|-----|--------------|

| 15                                                                             | 8 | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0            |

| NOT USED                                                                       |   | PE7 | PE6 | PE5 | PE4 | PE3 | PE2 | PE1 | PE0          |

| RESET:                                                                         |   |     |     |     |     |     |     |     |              |

|                                                                                |   | U   | U   | U   | U   | U   | U   | U   | U            |

| _                                                                              |   |     |     |     |     |     |     |     |              |

PORTE is an internal data latch that can be accessed at two locations. It can be read or written at any time. If a port E I/O pin is configured as an output, the corresponding bit value is driven out on the pin. When a pin is configured as an output, a read of PORTE returns the latched bit value; when a pin is configured as an input, a read returns the pin logic level.

### **D.2.7 Port E Data Direction Register**

| DDRE — Port E Data Direction Regis | ster |      |      |      |      |      |      | \$YFF | A15  |

|------------------------------------|------|------|------|------|------|------|------|-------|------|

| 15                                 | 8    | 7    | 6    | 5    | 4    | 3    | 2    | 1     | 0    |

| NOT USED                           |      | DDE7 | DDE6 | DDE5 | DDE4 | DDE3 | DDE2 | DDE1  | DDE0 |

| RESET:                             |      |      |      |      |      |      |      |       |      |

|                                    |      | 0    | 0    | 0    | 0    | 0    | 0    | 0     | 0    |

Bits in this register control the direction of the port E pin drivers when pins are configured for I/O. Setting a bit configures the corresponding pin as an output; clearing a bit

MC68336/376 USER'S MANUAL REGISTER SUMMARY Rev. 15 Oct 2000 For More Information On This Product, Go to: www.freescale.com

configures the corresponding pin as an input. This register can be read or written at any time.

## D.2.8 Port E Pin Assignment Register

| PEPAR — Port E Pin Assignment |   |           |           |           |           |           |           | \$YFF     | A17       |

|-------------------------------|---|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| 15                            | 8 | 7         | 6         | 5         | 4         | 3         | 2         | 1         | 0         |

| NOT USED                      |   | PEPA<br>7 | PEPA<br>6 | PEPA<br>5 | PEPA<br>4 | PEPA<br>3 | PEPA<br>2 | PEPA<br>1 | PEPA<br>0 |

| RESET:                        |   |           |           |           |           |           |           |           |           |

|                               |   | DATA<br>8 |

Bits in this register determine the function of port E pins. Setting a bit assigns the corresponding pin to a bus control signal; clearing a bit assigns the pin to I/O port E. Refer to **Table D-5**.

| PEPAR Bit | Port E Signal | Bus Control Signal |

|-----------|---------------|--------------------|

| PEPA7     | PE7           | SIZ1               |

| PEPA6     | PE6           | SIZ0               |

| PEPA5     | PE5           | AS                 |

| PEPA4     | PE4           | DS                 |

| PEPA3     | PE3           | RMC                |

| PEPA2     | PE2           | AVEC               |

| PEPA1     | PE1           | DSACK1             |

| PEPA0     | PE0           | DSACK0             |

## Table D-5 Port E Pin Assignments

### **D.2.9 Port F Data Register**

| <b>PORTF0</b> — Port F Data Register 0<br><b>PORTF1</b> — Port F Data Register 1 |   |     |     |     |     |     |     | \$YFF<br>\$YFF |     |

|----------------------------------------------------------------------------------|---|-----|-----|-----|-----|-----|-----|----------------|-----|

| 15                                                                               | 8 | 7   | 6   | 5   | 4   | 3   | 2   | 1              | 0   |

| NOT USED                                                                         |   | PF7 | PF6 | PF5 | PF4 | PF3 | PF2 | PF1            | PF0 |

| RESET:                                                                           |   |     |     |     |     |     |     |                |     |

|                                                                                  |   | U   | U   | U   | U   | U   | U   | U              | U   |

PORTF is an internal data latch that can be accessed at two locations. It can be read or written at any time. If a port F I/O pin is configured as an output, the corresponding bit value is driven out on the pin. When a pin is configured as an output, a read of PORTF returns the latched bit value; when a pin is configured as an input, a read returns the pin logic level.

#### **D.2.10 Port F Data Direction Register**

| DDRF — Port F Data Direction Register |   |      |      |      |      |      | :    | \$YFF | A1D      |

|---------------------------------------|---|------|------|------|------|------|------|-------|----------|

| 15                                    | 8 | 7    | 6    | 5    | 4    | 3    | 2    | 1     | 0        |

| NOT USED                              |   | DDF7 | DDF6 | DDF5 | DDF4 | DDF3 | DDF2 | DDF1  | DDF0     |

| RESET:                                |   |      |      |      |      |      |      |       | <u> </u> |

|                                       |   | 0    | 0    | 0    | 0    | 0    | 0    | 0     | 0        |

Bits in this register control the direction of the port F pin drivers when pins are configured for I/O. Setting a bit configures the corresponding pin as an output; clearing a bit configures the corresponding pin as an input. This register can be read or written at any time.

### D.2.11 Port F Pin Assignment Register

| <b>PFPAR</b> — Port F Pin Assignment Regis | ter |           |           |           |           |           |           | \$YFF     | A1F       |

|--------------------------------------------|-----|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| 15                                         | 8   | 7         | 6         | 5         | 4         | 3         | 2         | 1         | 0         |

| NOT USED                                   |     | PFPA<br>7 | PFPA<br>6 | PFPA<br>5 | PFPA<br>4 | PFPA<br>3 | PFPA<br>2 | PFPA<br>1 | PFPA<br>0 |

| RESET:                                     |     | DATA<br>9 |

Bits in this register determine the function of port F pins. Setting a bit assigns the corresponding pin to a control signal; clearing a bit assigns the pin to port F. Refer to **Table D-6**.

| PFPAR Field | Port F Signal | Alternate Signal |

|-------------|---------------|------------------|

| PFPA7       | PF7           | IRQ7             |

| PFPA6       | PF6           | IRQ6             |

| PFPA5       | PF5           | IRQ5             |

| PFPA4       | PF4           | IRQ4             |

| PFPA3       | PF3           | IRQ3             |

| PFPA2       | PF2           | IRQ2             |

| PFPA1       | PF1           | IRQ1             |

| PFPA0       | PF0           | MODCLK           |

### Table D-6 Port F Pin Assignments

#### **D.2.12 System Protection Control Register**

| SYPCR — System Protection |   |     |             | \$` | YFFA  | 21  |     |     |       |

|---------------------------|---|-----|-------------|-----|-------|-----|-----|-----|-------|

| 15                        | 8 | 7   | 6           | 5   | 4     | 3   | 2   | 1   | 0     |

| NOT USED                  |   | SWE | SWP         | SWT | [1:0] | HME | BME | BM1 | [1:0] |

| RESET:                    |   |     |             |     |       |     |     |     |       |

|                           |   | 1   | MOD-<br>CLK | 0   | 0     | 0   | 0   | 0   | 0     |

SYPCR controls system monitor functions, software watchdog clock prescaling, and bus monitor timing. This register can be written once following power-on or reset.

#### SWE — Software Watchdog Enable

0 = Software watchdog is disabled.

1 = Software watchdog is enabled.

#### SWP — Software Watchdog Prescale

This bit controls the value of the software watchdog prescaler.

0 = Software watchdog clock is not prescaled.

1 = Software watchdog clock is prescaled by 512.

The reset value of SWP is the complement of the state of the MODCLK pin during reset.

### SWT[1:0] — Software Watchdog Timing

This field selects the divide ration used to establish software watchdog timeout period. Refer to **Table D-7**.

| SWP | SWT[1:0] | Watchdog Time-Out Period           |

|-----|----------|------------------------------------|

| 0   | 00       | $2^9 \div f_{sys}$                 |

| 0   | 01       | 2 <sup>11</sup> ÷ f <sub>sys</sub> |

| 0   | 10       | 2 <sup>13</sup> ÷ f <sub>sys</sub> |

| 0   | 11       | 2 <sup>15</sup> ÷ f <sub>sys</sub> |

| 1   | 00       | 2 <sup>18</sup> ÷ f <sub>sys</sub> |

| 1   | 01       | 2 <sup>20</sup> ÷f <sub>sys</sub>  |

| 1   | 10       | 2 <sup>22</sup> ÷ f <sub>sys</sub> |

| 1   | 11       | 2 <sup>24</sup> ÷f <sub>sys</sub>  |

# Table D-7 Software Watchdog Timing Field

HME — Halt Monitor Enable

0 = Halt monitor is disabled.

1 = Halt monitor is enabled.

BME — Bus Monitor External Enable

- 0 = Disable bus monitor for internal to external bus cycle.

- 1 = Enable bus monitor for internal to external bus cycle.

MC68336/376 USER'S MANUAL **REGISTER SUMMARY**

MOTOROLA D-12

Rev. 15 Oct 2000 For More Information On This Product, Go to: www.freescale.com

#### BMT[1:0] — Bus Monitor Timing

This field selects the bus monitor time-out period. Refer to Table D-8.

## Table D-8 Bus Monitor Time-Out Period

| BMT[1:0] | Bus Monitor Time-Out Period |

|----------|-----------------------------|

| 00       | 64 system clocks            |

| 01       | 32 system clocks            |

| 10       | 16 system clocks            |

| 11       | 8 system clocks             |

## **D.2.13 Periodic Interrupt Control Register**

| PICR — Periodic Interrupt Control Register           15         14         13         12         11         10         9         8         7         6         5         4 |      |   |   |   |   |            |   |   |          |   |   |   |   | \$YFF | A22 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---|---|---|---|------------|---|---|----------|---|---|---|---|-------|-----|

|                                                                                                                                                                            |      |   |   |   |   |            |   |   | 6        | 5 | 4 | 3 | 2 | 1     | 0   |

| 0                                                                                                                                                                          | 0    | 0 | 0 | 0 | Р | PIRQL[2:0] |   |   | PIV[7:0] |   |   |   |   |       |     |

| RES                                                                                                                                                                        | SET: |   |   |   |   |            |   |   |          |   |   |   |   |       |     |

| 0 0 0 0 0 0 0                                                                                                                                                              |      |   |   |   |   |            | 0 | 0 | 0        | 0 | 0 | 1 | 1 | 1     | 1   |

PICR sets the interrupt level and vector number for the periodic interrupt timer (PIT). Bits [10:0] can be read or written at any time. Bits [15:11] are unimplemented and always read zero.

## PIRQL[2:0] — Periodic Interrupt Request Level

This field determines the priority of periodic interrupt requests. A value of %000 disables PIT interrupts.

### PIV[7:0] — Periodic Interrupt Vector

This field specifies the periodic interrupt vector number supplied by the SIM when the CPU32 acknowledges an interrupt request.

# **D.2.14 Periodic Interrupt Timer Register**

| PITR — Periodic Interrupt Timer Register       \$YFFA24         15       14       13       12       11       10       9       8       7       6       5       4       3       2       1       0         0       0       0       0       0       0       PTP       PITM[7:0]       PITM[7:0]       PITM[7:0]         RESET:         0       0       0       0       0       PTP       0       0       0       0       0 |    |    |    | <b>A2</b> 4                                                                                                                                |    |    |   |   |   |   |   |   |   |   |   |   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|----|--------------------------------------------------------------------------------------------------------------------------------------------|----|----|---|---|---|---|---|---|---|---|---|---|

|                                                                                                                                                                                                                                                                                                                                                                                                                        | 15 | 14 | 13 | 12                                                                                                                                         | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 15     14     13     12     11     10     9     8     7     6     5     4     3     2     1     0       0     0     0     0     0     0     PTP     PITM[7:0]                                                                                                                                                                                                                                                          |    |    |    |                                                                                                                                            |    |    |   |   |   |   |   |   |   |   |   |   |

| 15       14       13       12       11       10       9       8       7       6       5       4       3       2         0       0       0       0       0       0       PTP       PITM[7:0]         RESET:                                                                                                                                                                                                             |    |    |    |                                                                                                                                            |    |    |   |   |   |   |   |   |   |   |   |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                        | 0  | 0  | 0  | 12     11     10     9     8     7     6     5     4     3     2     1     0       0     0     0     0     PTP     PITM[7:0]     PITM[7:0] |    |    |   |   |   |   |   |   |   |   |   |   |

PITR specifies the prescaling and modulus value for the PIT. This register can be read or written at any time.

PTP — Periodic Timer Prescaler Control

- 0 = Periodic timer clock is not prescaled.

- 1 = Periodic timer clock is prescaled by 512.

# PITM[7:0] — Periodic Interrupt Timing Modulus

This field determines the periodic interrupt rate. Use the following expressions to

| MC68336/376   | REGISTER SUMMARY                                                  |

|---------------|-------------------------------------------------------------------|

| USER'S MANUAL | Rev. 15 Oct 2000                                                  |

|               | For More Information On This Product,<br>Go to: www.freescale.com |

calculate timer period.

When a fast reference frequency is used, the PIT period can be calculated as follows:

PIT Period =

$$\frac{(128)(PITM[7:0])(1 \text{ if } PTP = 0, 512 \text{ if } PTP = 1)(4)}{f_{ref}}$$

When an externally input clock frequency is used, the PIT period can be calculated as follows:

PIT Period =

$$\frac{(PITM[7:0])(1 \text{ if } PTP = 0, 512 \text{ if } PTP = 1)(4)}{f_{ref}}$$

# **D.2.15 Software Watchdog Service Register**

| SWSR — Software Watchdog Service Register <sup>1</sup> \$Y |          |   |   |   |   |   |   |   |   | A27 |

|------------------------------------------------------------|----------|---|---|---|---|---|---|---|---|-----|

|                                                            | 15       | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|                                                            | NOT USED |   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0   |

|                                                            | RESET:   |   |   |   |   |   |   |   |   |     |

|                                                            |          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |   |     |

|                                                            | NOTEO    |   |   |   |   |   |   |   |   |     |

NOTES:

1. Register shown with read value.

To reset the software watchdog:

- 1. Write \$55 to SWSR.

- 2. Write \$AA to SWSR.

Both writes must occur in the order specified before the software watchdog times out, but any number of instructions can occur between the two writes.

# D.2.16 Port C Data Register

| PORTC — Port C Data Register |   |   |     |     |     |     |     | \$YFF | A41 |

|------------------------------|---|---|-----|-----|-----|-----|-----|-------|-----|

| 15                           | 8 | 7 | 6   | 5   | 4   | 3   | 2   | 1     | 0   |

| NOT USED                     |   | 0 | PC6 | PC5 | PC4 | PC3 | PC2 | PC1   | PC0 |

| RESET:                       |   |   |     |     |     |     |     |       |     |

|                              |   | 0 | 1   | 1   | 1   | 1   | 1   | 1     | 1   |

PORTC latches data for chip-select pins configured as discrete outputs.

# **Freescale Semiconductor, Inc.**

| CSP/ | CSPAR0 — Chip-Select Pin Assignment Register 0 \$YFFA44<br>15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0<br>0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                                                                 |  |  |  |                |                            |  |  |  |  |       |       |       |             |  |  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|----------------|----------------------------|--|--|--|--|-------|-------|-------|-------------|--|--|

| 15   |                                                                                                                                                                                                                                                                                                         |  |  |  |                |                            |  |  |  |  |       |       |       |             |  |  |

| 0    | 0 0 CS5PA[1:0] CS4PA[1:0]                                                                                                                                                                                                                                                                               |  |  |  | <b>\</b> [1:0] | CS3PA[1:0] CS2PA[1:0] CS1P |  |  |  |  | [1:0] | CS0PA | [1:0] | CSBTPA[1:0] |  |  |

| RES  | SET:                                                                                                                                                                                                                                                                                                    |  |  |  |                |                            |  |  |  |  |       |       |       |             |  |  |

| 0    | 0         0         CS3PA[1:0]         CS3PA[1:0]         CS3PA[1:0]         CS1PA[1:0]         CS0PA[1:0]         CSBTPA[1:0]           RESET:         0         0         DATA<br>2         1         DATA<br>2         1         DATA<br>1         1         1         1         1         DATA<br>0 |  |  |  |                |                            |  |  |  |  |       |       |       |             |  |  |

The chip-select pin assignment registers configure the chip-select pins for use as discrete I/O, an alternate function, or as an 8-bit or 16-bit chip-select. Each 2-bit field in CSPAR[0:1] (except for CSBTPA[1:0]) has the possible encoding shown inTable D-9.

## Table D-9 Pin Assignment Field Encoding

| CSxPA[1:0] | Description                     |

|------------|---------------------------------|

| 00         | Discrete output <sup>1</sup>    |

| 01         | Alternate function <sup>1</sup> |

| 10         | Chip-select (8-bit port)        |

| 11         | Chip-select (16-bit port)       |

|            |                                 |

NOTES:

**D.2.17 Chip-Select Pin Assignment Registers**

1. Does not apply to the CSBOOT field.

CSPAR0 contains seven 2-bit fields that determine the function of corresponding chipselect pins. Bits [15:14] are not used. These bits always read zero; writes have no effect. CSPAR0 bit 1 always reads one; writes to CSPAR0 bit 1 have no effect. The alternate functions can be enabled by data bus mode selection during reset.

Table D-10 shows CSPAR0 pin assignments.

### **Table D-10 CSPAR0 Pin Assignments**

| CSPAR0 Field | Chip-Select Signal | Alternate Signal | Discrete Output |

|--------------|--------------------|------------------|-----------------|

| CS5PA[1:0]   | CS5                | FC2              | PC2             |

| CS4PA[1:0]   | CS4                | FC1              | PC1             |

| CS3PA[1:0]   | CS3                | FC0              | PC0             |

| CS2PA[1:0]   | CS2                | BGACK            | —               |

| CS1PA[1:0]   | CS1                | BG               | -               |

| CS0PA[1:0]   | CS0                | BR               | —               |

| CSBTPA[1:0]  | CSBOOT             | _                | _               |

| CSP/ | AR1 – | – Chij | p-Sele | ect Pi | n Ass | signme                 | nt Re  | egister                    | 1             |                            |        |                            |       | \$YFF/                     | 446   |   |

|------|-------|--------|--------|--------|-------|------------------------|--------|----------------------------|---------------|----------------------------|--------|----------------------------|-------|----------------------------|-------|---|

| 15   | 14    | 13     | 12     | 11     | 10    | 9                      | 8      | 7                          | 6             | 5                          | 4      | 3                          | 2     | 1                          | 0     |   |

| 0    | 0     | 0      | 0      | 0      | 0     | CS10P                  | A[1:0] | CS9PA                      | <b>\[1:0]</b> | CS8PA                      | A[1:0] | CS7PA                      | [1:0] | CS6PA                      | [1:0] | / |

| RES  | SET:  |        |        |        |       |                        |        | •                          |               |                            |        |                            |       |                            |       |   |

| 0    | 0     | 0      | 0      | 0      | 0     | DATA<br>7 <sup>1</sup> | 1      | DATA<br>[7:6] <sup>1</sup> | 1             | DATA<br>[7:5] <sup>1</sup> | 1      | DATA<br>[7:4] <sup>1</sup> | 1     | DATA<br>[7:3] <sup>1</sup> | 1     |   |

NOTES:

1. Refer to Table D-12 for CSPAR1 reset state information.

CSPAR1 contains five 2-bit fields that determine the functions of corresponding chipselect pins. Bits [15:10] are not used. These bits always read zero; writes have no effect. **Table D-11** shows CSPAR1 pin assignments, including alternate functions that can be enabled by data bus mode selection during reset.

| CSPAR1 Field | Chip-Select Signal | Alternate Signal | Discrete Output |

|--------------|--------------------|------------------|-----------------|

| CS10PA[1:0]  | CS10               | ADDR23           | ECLK            |

| CS9PA[1:0]   | CS9                | ADDR22           | PC6             |

| CS8PA[1:0]   | CS8                | ADDR21           | PC5             |

| CS7PA[1:0]   | CS7                | ADDR20           | PC4             |

| CS6PA[1:0]   | CS6                | ADDR19           | PC3             |

#### Table D-11 CSPAR1 Pin Assignments

The reset state of DATA[7:3] determines whether pins controlled by CSPAR1 are initially configured as high-order address lines or chip-selects. Table D-12 shows the correspondence between DATA[7:3] and the reset configuration of  $\overline{CS[10:6]}$ /ADDR[23:19].

|       | Data B | us Pins at | Reset |       | Chip-Select/Address Bus Pin Function |                |                |                |                |  |  |  |

|-------|--------|------------|-------|-------|--------------------------------------|----------------|----------------|----------------|----------------|--|--|--|

| DATA7 | DATA6  | DATA5      | DATA4 | DATA3 | CS10/<br>ADDR23                      | CS9/<br>ADDR22 | CS8/<br>ADDR21 | CS7/<br>ADDR20 | CS8/<br>ADDR19 |  |  |  |

| 1     | 1      | 1          | 1     | 1     | CS10                                 | CS9            | CS8            | CS7            | CS6            |  |  |  |

| 1     | 1      | 1          | 1     | 0     | CS10                                 | CS9            | CS8            | CS7            | ADDR19         |  |  |  |

| 1     | 1      | 1          | 0     | Х     | CS10                                 | CS9            | CS8            | ADDR20         | ADDR19         |  |  |  |

| 1     | 1      | 0          | Х     | Х     | CS10                                 | CS9            | ADDR21         | ADDR20         | ADDR19         |  |  |  |

| 1     | 0      | Х          | Х     | Х     | CS10                                 | ADDR22         | ADDR21         | ADDR20         | ADDR19         |  |  |  |

| 0     | Х      | Х          | Х     | Х     | ADDR23                               | ADDR22         | ADDR21         | ADDR20         | ADDR19         |  |  |  |

### Table D-12 Reset Pin Function of CS[10:6]

|        | CSB/       | ARBT       | — C        | hip-Se     | elect E    | Base /     | Addre      | ss Re      | giste      | r Boot     | ROM        | 1          |            |            | \$YFF | A48 |

|--------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|-------|-----|

|        | 15         | 14         | 13         | 12         | 11         | 10         | 9          | 8          | 7          | 6          | 5          | 4          | 3          | 2          | 1     | 0   |

|        | ADDR<br>23 | ADDR<br>22 | ADDR<br>21 | ADDR<br>20 | ADDR<br>19 | ADDR<br>18 | ADDR<br>17 | ADDR<br>16 | ADDR<br>15 | ADDR<br>14 | ADDR<br>13 | ADDR<br>12 | ADDR<br>11 | BLKSZ[2:0] |       | 0]  |

| RESET: |            |            |            |            |            |            |            |            |            |            |            |            |            |            |       |     |

|        | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 1          | 1     | 1   |

#### D.2.18 Chip-Select Base Address Register Boot ROM

#### **D.2.19 Chip-Select Base Address Registers**

|        | CSBAR[0:10] — Chip-Select Base Address Registers\$YFFA4C-\$YFFA74 |            |            |            |            |            |            |            |            |            |            |            |            | 474 |          |   |

|--------|-------------------------------------------------------------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|-----|----------|---|

|        | 15                                                                | 14         | 13         | 12         | 11         | 10         | 9          | 8          | 7          | 6          | 5          | 4          | 3          | 2   | 1        | 0 |

|        | ADDR<br>23                                                        | ADDR<br>22 | ADDR<br>21 | ADDR<br>20 | ADDR<br>19 | ADDR<br>18 | ADDR<br>17 | ADDR<br>16 | ADDR<br>15 | ADDR<br>14 | ADDR<br>13 | ADDR<br>12 | ADDR<br>11 | В   | LKSZ[2:0 | ] |

| RESET: |                                                                   |            |            |            |            |            |            |            |            |            |            |            |            |     |          |   |

|        | 0                                                                 | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0   | 0        | 0 |

Each chip-select pin has an associated base address register. A base address is the lowest address in the block of addresses enabled by a chip select. CSBARBT contains the base address for selection of a bootstrap memory device. Bit and field definitions for CSBARBT and CSBAR[0:10] are the same, but reset block sizes differ.

#### ADDR[23:11] — Base Address

This field sets the starting address of a particular chip-select's address space. The address compare logic uses only the most significant bits to match an address within a block. The value of the base address must be an integer multiple of the block size. Base address register diagrams show how base register bits correspond to address lines.

#### BLKSZ[2:0] — Block Size Field

This field determines the size of the block that is enabled by the chip-select.

Table D-13 shows bit encoding for the base address registers block size field.

| BLKSZ[2:0] | Block Size | Address Lines Compared |

|------------|------------|------------------------|

| 000        | 2 Kbytes   | ADDR[23:11]            |

| 001        | 8 Kbytes   | ADDR[23:13]            |

| 010        | 16 Kbytes  | ADDR[23:14]            |

| 011        | 64 Kbytes  | ADDR[23:16]            |

| 100        | 128 Kbytes | ADDR[23:17]            |

| 101        | 256 Kbytes | ADDR[23:18]            |

| 110        | 512 Kbytes | ADDR[23:19]            |

| 111        | 1 Mbyte    | ADDR[23:20]            |

### Table D-13 Block Size Field Bit Encoding

# **Freescale Semiconductor, Inc.**

#### D.2.20 Chip-Select Option Register Boot ROM

| CSO      | <b>CSORBT</b> — Chip-Select Option Register Boot ROM <b>\$YFFA4A</b> |        |     |       |      |   |      |        |   |      |        |   |          |   |      |

|----------|----------------------------------------------------------------------|--------|-----|-------|------|---|------|--------|---|------|--------|---|----------|---|------|

| 15       | 14                                                                   | 13     | 12  | 11    | 10   | 9 | 8    | 7      | 6 | 5    | 4      | 3 | 2        | 1 | 0    |

| MOD<br>E | BYT                                                                  | E[1:0] | R/W | [1:0] | STRB |   | DSAC | K[3:0] |   | SPAC | E[1:0] |   | IPL[2:0] |   | AVEC |

| RESET:   |                                                                      |        |     |       |      |   |      |        |   |      |        |   |          |   |      |

| 0        | 1                                                                    | 1      | 1   | 1     | 0    | 1 | 1    | 0      | 1 | 1    | 1      | 0 | 0        | 0 | 0    |

## **D.2.21 Chip-Select Option Registers**

| CSOF     | CSOR[0:10] — Chip-Select Option Registers \$YFFA4E-YFFA76 |        |     |       |      |   |      |        |   |      |        |   |          |   |      |

|----------|-----------------------------------------------------------|--------|-----|-------|------|---|------|--------|---|------|--------|---|----------|---|------|

| 15       | 14                                                        | 13     | 12  | 11    | 10   | 9 | 8    | 7      | 6 | 5    | 4      | 3 | 2        | 1 | 0    |

| MOD<br>E | BYTE                                                      | E[1:0] | R/W | [1:0] | STRB |   | DSAC | K[3:0] |   | SPAC | E[1:0] |   | IPL[2:0] |   | AVEC |

| RESET:   |                                                           |        |     |       |      |   |      |        |   |      |        |   |          |   |      |

| 0        | 0                                                         | 0      | 0   | 0     | 0    | 0 | 0    | 0      | 0 | 0    | 0      | 0 | 0        | 0 | 0    |

CSORBT and CSOR[0:10] contain parameters that support bootstrap operations from peripheral memory devices. Bit and field definitions for CSORBT and CSOR[0:10] are the same.

## MODE — Asynchronous/Synchronous Mode

- 0 = Asynchronous mode selected.

- 1 = Synchronous mode selected.

In asynchronous mode, chip-select assertion is synchronized with  $\overline{AS}$  and  $\overline{DS}$ .

In synchronous mode, the DSACK field is not used because a bus cycle is only performed as a synchronous operation. When a match condition occurs on a chip-select programmed for synchronous operation, the chip-select signals the EBI that an Eclock cycle is pending. Refer to 5.3 System Clock for more information on ECLK.

### BYTE[1:0] — Upper/Lower Byte Option

This field is used only when the chip-select 16-bit port option is selected in the pin assignment register. Table D-14 shows upper/lower byte options.

| BYTE[1:0] | Description |

|-----------|-------------|

| 00        | Disable     |

| 01        | Lower byte  |

| 10        | Upper byte  |

| 11        | Both bytes  |

# Table D-14 BYTE Field Bit Encoding

# R/W[1:0]— Read/Write

This field causes a chip-select to be asserted only for a read, only for a write, or for both read and write. Table D-15 shows the options.

Table D-15 Read/Write Field Bit Encoding

| R/W[1:0] | Description |

|----------|-------------|

| 00       | Disable     |

| 01       | Read only   |

| 10       | Write only  |

| 11       | Read/Write  |

# STRB — Address Strobe/Data Strobe

This bit controls the timing for assertion of a chip-select in asynchronous mode. Selecting address strobe causes the chip-select to be asserted synchronized with address strobe. Selecting data strobe causes the chip-select to be asserted synchronized with data strobe.

0 = Address strobe

1 = Data strobe

# DSACK[3:0] — Data Strobe Acknowledge

This field specifies the source of  $\overline{\text{DSACK}}$  in asynchronous mode. It also allows the user to adjust bus timing with internal  $\overline{\text{DSACK}}$  generation by controlling the number of wait states that are inserted to optimize bus speed in a particular application. Table D-16 shows the  $\overline{\text{DSACK}[3:0]}$  field encoding. The fast termination encoding (%1110) effectively corresponds to -1 wait states.

# Table D-16 DSACK Field Encoding

| DSACK[3:0] | Clock Cycles Required<br>Per Access | Wait States Inserted<br>Per Access |

|------------|-------------------------------------|------------------------------------|

| 0000       | 3                                   | 0                                  |

| 0001       | 4                                   | 1                                  |

| 0010       | 5                                   | 2                                  |

| 0011       | 6                                   | 3                                  |

| 0100       | 7                                   | 4                                  |

| 0101       | 8                                   | 5                                  |

| 0110       | 9                                   | 6                                  |

| 0111       | 10                                  | 7                                  |

| 1000       | 11                                  | 8                                  |

| 1001       | 12                                  | 9                                  |

| 1010       | 13                                  | 10                                 |

| 1011       | 14                                  | 11                                 |

| 1100       | 15                                  | 12                                 |

| 1101       | 16                                  | 13                                 |

| 1110       | 2                                   | Fast Termination                   |

| 1111       | —                                   | External DSACK                     |

SPACE[1:0] — Address Space Select

Use this option field to select an address space for the chip-select logic. The CPU32 normally operates in supervisor or user space, but interrupt acknowledge cycles must take place in CPU space. **Table D-17** shows address space bit encodings.

MC68336/376 USER'S MANUAL

#### **REGISTER SUMMARY**

MOTOROLA D-19

Rev. 15 Oct 2000 For More Information On This Product, Go to: www.freescale.com

**Table D-17 Address Space Bit Encodings**

| SPACE[1:0] | Address Space         |

|------------|-----------------------|

| 00         | CPU Space             |

| 01         | User Space            |

| 10         | Supervisor Space      |

| 11         | Supervisor/User Space |

# IPL[2:0] — Interrupt Priority Level

When SPACE[1:0] is set for CPU space (%00), chip-select logic can be used for interrupt acknowledge. During an interrupt acknowledge cycle, the priority level on address lines ADDR[3:1] is compared to the value in IPL[2:0]. If the values are the same, a chip-select can be asserted, provided other option register conditions are met. **Table D-18** shows IPL[2:0] field encoding.

## Table D-18 Interrupt Priority Level Field Encoding

| IPL[2:0] | Interrupt Priority Level |

|----------|--------------------------|

| 000      | Any Level                |

| 001      | 1                        |

| 010      | 2                        |

| 011      | 3                        |

| 100      | 4                        |

| 101      | 5                        |

| 110      | 6                        |

| 111      | 7                        |

This field only affects the response of chip-selects and does not affect interrupt recognition by the CPU32.

### AVEC — Autovector Enable

This field selects one of two methods of acquiring an interrupt vector during an interrupt acknowledge cycle. It is not usually used with a chip-select pin.

0 = External interrupt vector enabled

1 = Autovector enabled

If the chip select is configured to trigger on an interrupt acknowledge cycle (SPACE[1:0] = %00) and the AVEC field is set to one, the chip-select automatically generates AVEC in response to the interrupt acknowledge cycle. Otherwise, the vector must be supplied by the requesting device.

# **D.2.22 Master Shift Registers**

TSTMSRA — Master Shift Register A

Used for factory test only.

# TSTMSRB — Master Shift Register B

Used for factory test only.

MC68336/376 USER'S MANUAL REGISTER SUMMARY Rev. 15 Oct 2000 For More Information On This Product, Go to: www.freescale.com \$YFFA30

\$YFFA32

MOTOROLA D-20

| D.2.23 Test Module Shift Count Register                                      |          |  |

|------------------------------------------------------------------------------|----------|--|

| <b>TSTSC</b> — Test Module Shift Count<br>Used for factory test only.        | \$YFFA34 |  |

| D.2.24 Test Module Repetition Count Register                                 |          |  |

| <b>TSTRC</b> — Test Module Repetition Count<br>Used for factory test only.   | \$YFFA36 |  |

| D.2.25 Test Submodule Control Register                                       |          |  |

| <b>CREG</b> — Test Submodule Control Register<br>Used for factory test only. | \$YFFA38 |  |

| D.2.26 Distributed Register                                                  |          |  |

| DREG — Distributed Register                                                  | \$YFFA3A |  |

Used for factory test only.

# **D.3 Standby RAM Module**

Table D-19 shows the SRAM address map. SRAM control registers are accessible at the supervisor privilege level only.

### Table D-19 SRAM Address Map

| Address <sup>1</sup> | 15 0                                          |

|----------------------|-----------------------------------------------|

| \$YFFB40             | RAM Module Configuration Register (RAMMCR)    |

| \$YFFB42             | RAM Test Register (RAMTST)                    |

| \$YFFB44             | RAM Array Base Address Register High (RAMBAH) |

| \$YFFB46             | RAM Array Base Address Register Low (RAMBAL)  |

|                      | ·                                             |

NOTES:

1. Y = M111, where M is the logic state of the module mapping (MM) bit in the SIMCR.

# **D.3.1 RAM Module Configuration Register**

| RAMMCR — RAM Module | Configuration | Register |

|---------------------|---------------|----------|

|---------------------|---------------|----------|

| STOP   | 0 | 0 | 0 | RLCK | 0 | RASI | P[1:0] | NOT USED |   |   |   |   |   |   |   |

|--------|---|---|---|------|---|------|--------|----------|---|---|---|---|---|---|---|

| RESET: |   |   |   |      |   |      |        |          |   |   |   |   |   |   |   |

| 1      | 0 | 0 | 0 | 0    | 0 | 1    | 1      | 0        | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

STOP — Low-Power Stop Mode Enable

0 = SRAM operates normally.

1 = SRAM enters low-power stop mode.

MC68336/376 **USER'S MANUAL**

15

#### **REGISTER SUMMARY** Rev. 15 Oct 2000 For More Information On This Product. Go to: www.freescale.com

MOTOROLA D-21

0

This bit controls whether SRAM operates normally or enters low-power stop mode. In low-power stop mode, the array retains its contents, but cannot be read or written.

### RLCK — RAM Base Address Lock

0 = SRAM base address registers can be written.

1 = SRAM base address registers are locked.

RLCK defaults to zero on reset; it can be written once to one

#### RASP[1:0] — RAM Array Space

The RASP field limits access to the SRAM array to one of four CPU32 address spaces. Refer to **Table D-20**.

## Table D-20 RASP Encoding

| RASP[1:0] | Space                         |

|-----------|-------------------------------|

| 00        | Unrestricted program and data |

| 01        | Unrestricted program          |

| 10        | Supervisor program and data   |

| 11        | Supervisor program            |

## **D.3.2 RAM Test Register**

### RAMTST — RAM Test Register

Used for factory test only.

# D.3.3 Array Base Address Register High

### RAMBAH — Array Base Address Register High

#### 15 8 7 6 5 4 3 2 1 0 ADDR ADDR ADDR ADDR ADDR ADDR ADDR ADDR NOT USED 22 20 18 23 21 19 17 16 RESET: 0 0 0 0 0 0 0 0

### D.3.4 Array Base Address Register Low

| RAMBAL — Array Base Address Register Low |            |            |            |    |    |   |   |   |   |   |   |   | \$YFFB46 |   |   |

|------------------------------------------|------------|------------|------------|----|----|---|---|---|---|---|---|---|----------|---|---|

| 15                                       | 14         | 13         | 12         | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2        | 1 | 0 |

| ADDR<br>15                               | ADDR<br>14 | ADDR<br>13 | ADDR<br>12 | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0        | 0 | 0 |

| RESET:                                   |            |            |            |    |    |   |   |   |   |   |   |   |          |   |   |

| 0                                        | 0          | 0          | 0          | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0        | 0 | 0 |

RAMBAH and RAMBAL specify the SRAM array base address in the system memory map. They can only be written while the SRAM is in low-power stop mode (STOP = 1, the default out of reset) and the base address lock is disabled (RLCK = 0, the default out of reset). This prevents accidental remapping of the array.

\$YFFB42

\$YFFB44

#### **D.4 Masked ROM Module**

The MRM is used only in the MC68376. **Table D-21** shows the MRM address map. MRM control registers are accessible in supervisor mode only.

The reset states shown for the MRM registers are for the generic (blank ROM) versions of the device. Several MRM register bit fields can be user-specified on a custommasked ROM device. Contact a Motorola sales representative for information on ordering a custom ROM device.

| Address  | 15                                               | 0 |

|----------|--------------------------------------------------|---|

| \$YFF820 | Masked ROM Module Configuration Register (MRMCR) |   |

| \$YFF822 | Not Implemented                                  |   |

| \$YFF824 | ROM Array Base Address High Register (ROMBAH)    |   |

| \$YFF826 | ROM Array Base Address Low Register (ROMBAL)     |   |

| \$YFF828 | Signature High Register (SIGHI)                  |   |

| \$YFF82A | Signature Low Register (SIGLO)                   |   |

| \$YFF82C | Not Implemented                                  |   |

| \$YFF82E | Not Implemented                                  |   |

| \$YFF830 | ROM Bootstrap Word 0 (ROMBS0)                    |   |

| \$YFF832 | ROM Bootstrap Word 1 (ROMBS1)                    |   |

| \$YFF834 | ROM Bootstrap Word 2 (ROMBS2)                    |   |

| \$YFF836 | ROM Bootstrap Word 3 (ROMBS3)                    |   |

| \$YFF838 | Not Implemented                                  |   |

| \$YFF83A | Not Implemented                                  |   |

| \$YFF83C | Not Implemented                                  |   |

| \$YFF83E | Not Implemented                                  |   |

#### Table D-21 MRM Address Map

### D.4.1 Masked ROM Module Configuration Register

| MRMO                | MRMCR — Masked ROM Module Configuration Register |    |      |      |      |      |        |     |        |   |   |   |   | \$YFF820 |   |  |  |

|---------------------|--------------------------------------------------|----|------|------|------|------|--------|-----|--------|---|---|---|---|----------|---|--|--|

| 15                  | 14                                               | 13 | 12   | 11   | 10   | 9    | 8      | 7   | 6      | 5 | 4 | 3 | 2 | 1        | 0 |  |  |

| STOP                | 0                                                | 0  | BOOT | LOCK | EMUL | ASPO | C[1:0] | WAI | Г[1:0] | 0 | 0 | 0 | 0 | 0        | 0 |  |  |

| RES                 | ET:                                              |    | -    |      |      |      |        |     |        |   |   |   |   |          |   |  |  |

| D <u>AT</u> A<br>14 | 0                                                | 0  | 1    | 0    | 0    | 1    | 1      | 1   | 1      | 0 | 0 | 0 | 0 | 0        | 0 |  |  |

STOP — Low-Power Stop Mode Enable

The reset state of the STOP bit is the complement of DATA14 state during reset. The ROM array base address cannot be changed unless the STOP bit is set.

- 0 = ROM array operates normally.

- 1 = ROM array operates in low-power stop mode.

REGISTER SUMMARY Rev. 15 Oct 2000 For More Information On This Product, Go to: www.freescale.com

## NOTE

Unless DATA14 is pulled down during reset, the MRM will be enabled. On generic MC68376 devices (blank ROM), the MRM is enabled at address \$FF0000 (which is outside of the 1 Mbyte address range of CSBOOT. On these devices, the MRM should be disabled (since it is blank) by setting the STOP bit during system initialization.

# BOOT — Boot ROM Control

Reset state of  $\overline{\text{BOOT}}$  is specified at mask time. Bootstrap operation is overridden if STOP = 1 at reset. This is a read-only bit.

- 0 = ROM responds to bootstrap word locations during reset vector fetch.

- 1 = ROM does not respond to bootstrap word locations during reset vector fetch.

### LOCK — Lock Registers

The reset state of LOCK is specified at mask time. If the reset state of the LOCK is zero, it can be set once after reset to allow protection of the registers after initialization. Once the LOCK bit is set, it cannot be cleared again until after a reset. LOCK protects the ASPC and WAIT fields, as well as the ROMBAL and ROMBAH registers. ASPC, ROMBAL and ROMBAH are also protected by the STOP bit.

0 = Write lock disabled. Protected registers and fields can be written.

1 = Write lock enabled. Protected registers and fields cannot be written.

## EMUL — Emulation Mode Control

0 = Normal ROM operation

The MC68376 does not support emulation mode, therefore, this bit reads zero. Writes have no effect.

# ASPC[1:0] — ROM Array Space

ASPC can be written only if LOCK = 0 and STOP = 1. ASPC1 places the ROM array in either supervisor or unrestricted space. ASPC0 determines if the array resides in program space only or with program and data space. The reset state of ASPC[1:0] is specified at mask time. Table D-22 shows ASPC[1:0] encoding.

| ASPC[1:0] | State Specified               |

|-----------|-------------------------------|

| 00        | Unrestricted program and data |

| 01        | Unrestricted program          |

| 10        | Supervisor program and data   |

| 11        | Supervisor program            |

# Table D-22 ROM Array Space Field

WAIT[1:0] — Wait States

WAIT[1:0] specifies the number of wait states inserted by the MRM during ROM array accesses. The reset state of WAIT[1:0] is specified at mask time. WAIT[1:0] can be written only if LOCK = 0 and STOP = 1. Table D-23 shows WAIT[1:0] encoding.

MC68336/376 USER'S MANUAL REGISTER SUMMARY Rev. 15 Oct 2000 For More Information On This Product, Go to: www.freescale.com MOTOROLA D-24

#### Table D-23 Wait States Field

| WAIT[1:0] | Cycles per Transfer |

|-----------|---------------------|

| 00        | 3                   |

| 01        | 4                   |

| 10        | 5                   |

| 11        | 2                   |

## D.4.2 ROM Array Base Address Register High

|   | <b>ROMBAH</b> — ROM Array Base Address Register High |      |    |    |    |    |   |   |            |            |            |            |            | <b>\$YFF824</b> |            |            |

|---|------------------------------------------------------|------|----|----|----|----|---|---|------------|------------|------------|------------|------------|-----------------|------------|------------|

|   | 15                                                   | 14   | 13 | 12 | 11 | 10 | 9 | 8 | 7          | 6          | 5          | 4          | 3          | 2               | 1          | 0          |

|   | 0                                                    | 0    | 0  | 0  | 0  | 0  | 0 | 0 | ADDR<br>23 | ADDR<br>22 | ADDR<br>21 | ADDR<br>20 | ADDR<br>19 | ADDR<br>18      | ADDR<br>17 | ADDR<br>16 |

| - | RES                                                  | SET: |    |    |    |    |   |   |            |            |            |            |            |                 |            |            |

|   |                                                      |      |    |    |    |    |   |   | 1          | 1          | 1          | 1          | 1          | 1               | 1          | 1          |

### D.4.3 ROM Array Base Address Register Low

| <b>ROMBAL</b> — ROM Array Base Address Register Low \$YFF826 |            |            |    |    |    |   |   |   |   |   |   |   |   | <sup>:</sup> 826 |   |

|--------------------------------------------------------------|------------|------------|----|----|----|---|---|---|---|---|---|---|---|------------------|---|

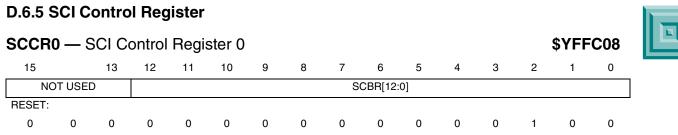

| 15                                                           | 14         | 13         | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1                | 0 |