Order this document by MC92501UM/A

Advance Information

# MC92501

# ATM Cell Processor User's Manual

Preliminary

For More Information On This Product, Go to: www.freescale.com

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and the officers are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

Preliminary

For More Information On This Product, Go to: www.freescale.com

#### Section 1 Introduction

| 1.1 | ATM Networks                         | 1-1 |

|-----|--------------------------------------|-----|

| 1.2 | MC92501 ATM Cell Processing Device   | 1-3 |

|     | 1.2.1 ATM Network Line Card          | 1-3 |

|     | 1.2.2 ATM Network Access Multiplexer | 1-4 |

| 1.3 | MC92501 Features                     | 1-4 |

|     | 1.3.1 Ingress                        | 1-6 |

|     | 1.3.2 Egress                         | 1-7 |

| 1.4 | The MC92500 Versus the MC92501       | 1-8 |

| 1.5 | Notation Conventions                 | 1-8 |

#### Section 2 Functional Description

| 2.1 | Introd | uction                             | 2-1 |

|-----|--------|------------------------------------|-----|

| 2.2 | Syster | n Functional Description           | 2-1 |

| 2.3 | MC92   | 501 Functional Description         | 2-3 |

|     |        | Ingress Cell Flow                  |     |

|     | 2.3.2  | Egress Cell Flow                   |     |

|     | 2.3.3  | Other Functions                    |     |

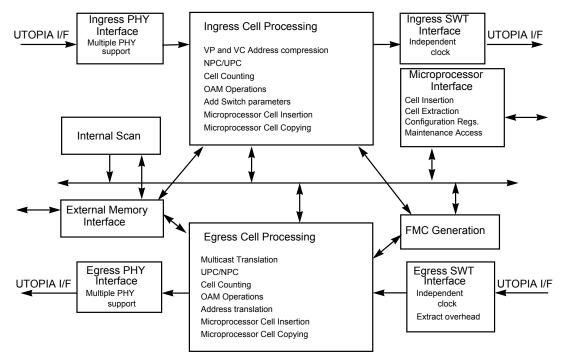

| 2.4 | MC92   | 501 Block Diagram                  | 2-5 |

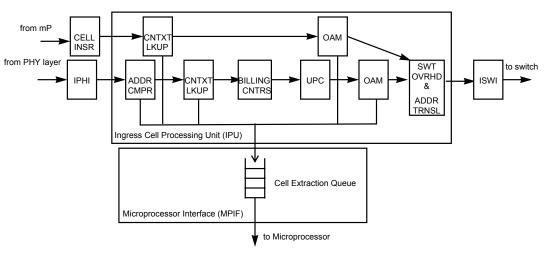

|     | 2.4.1  | Ingress PHY Interface (IPHI)       |     |

|     | 2.4.2  | Ingress Cell Processing Unit (IPU) |     |

|     | 2.4.3  | Ingress Switch Interface (ISWI)    |     |

|     | 2.4.4  | Egress Switch Interface (ESWI)     |     |

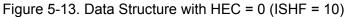

|     | 2.4.5  | Egress Cell Processing Unit (EPU)  |     |

|     | 2.4.6  | Egress PHY Interface (EPHI)        |     |

|     | 2.4.7  | External Memory Interface (EMIF)   |     |

|     | 2.4.8  | Microprocessor Interface (MPIF)    | 2-7 |

|     | 2.4.9  | Internal Scan (ISCAN)              |     |

|     | 2.4.10 | FMC Generation                     | 2-7 |

|     |        |                                    |     |

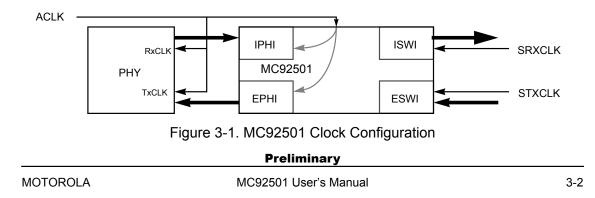

#### Section 3 System Operation

| MC92501 Modes of Operation    | 3-1 |

|-------------------------------|-----|

|                               |     |

| 3.1.2 Operate Mode            | 3-1 |

| 3.1.3 Reset                   | 3-2 |

| Data Path Clock Configuration | 3-2 |

| External Memory Maintenance   | 3-3 |

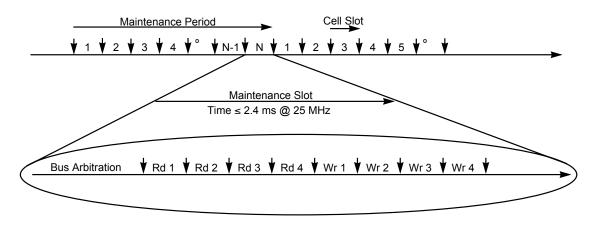

| 3.3.1 Maintenance Slots       | 3-3 |

|                               |     |

|     | 3.3.2 | Maintenance Slot Parameters       | 3-4  |

|-----|-------|-----------------------------------|------|

|     | 3.3.3 | Maintenance Slot Structure        | 3-5  |

|     | 3.3.4 | Indirect Memory Access            | 3-6  |

|     |       | 3.3.4.1 Write Access              | 3-6  |

|     |       | 3.3.4.2 Read Access               | 3-6  |

| 3.4 |       | nsertion And Extraction           |      |

|     | 3.4.1 | Cell Insertion                    | 3-8  |

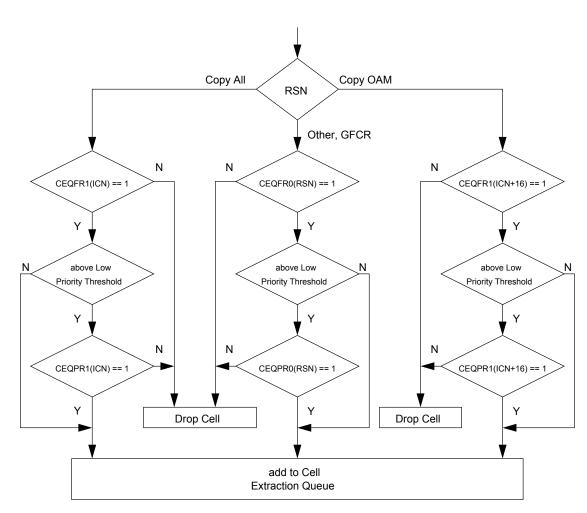

|     | 3.4.2 | Cell Extraction                   | 3-10 |

|     |       | 3.4.2.1 Cell Extraction Queue     | 3-10 |

|     |       | 3.4.2.2 Cell Extraction Registers | 3-12 |

|     |       |                                   |      |

#### Section 4 MC92501 External Interfaces

| 4.1 |        | duction                                        |      |

|-----|--------|------------------------------------------------|------|

| 4.2 | PHY    | Interface                                      |      |

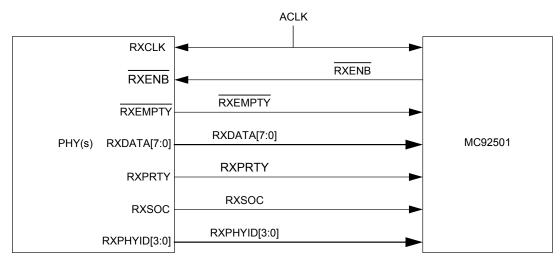

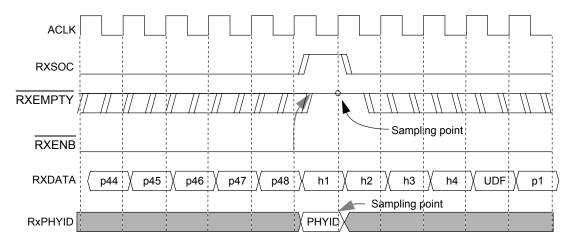

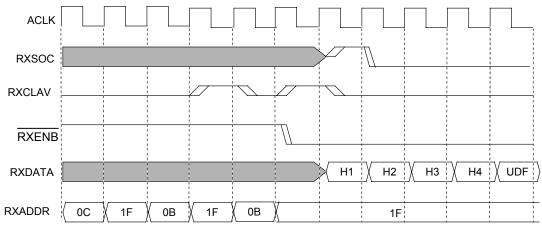

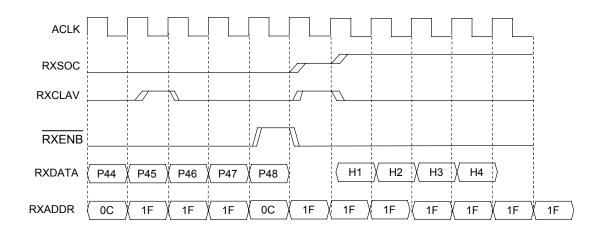

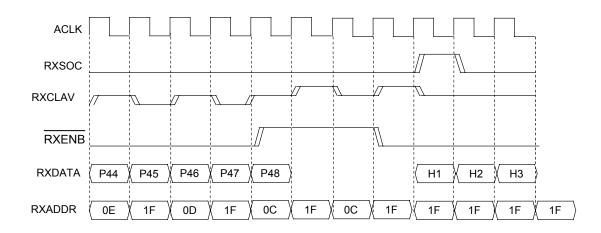

|     | 4.2.1  | UTOPIA Level 1 Receive PHY Interface (Ingress) | 4-1  |

|     |        | 4.2.1.1 Octet-Based Receive Interface          | 4-3  |

|     |        | 4.2.1.2 Cell-Based Receive Interface           | 4-5  |

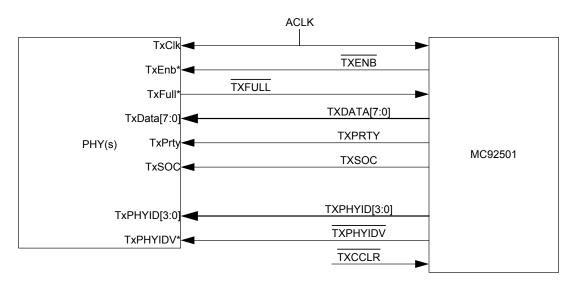

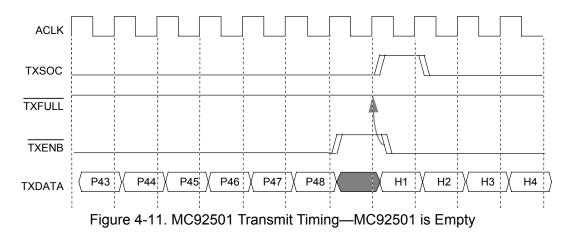

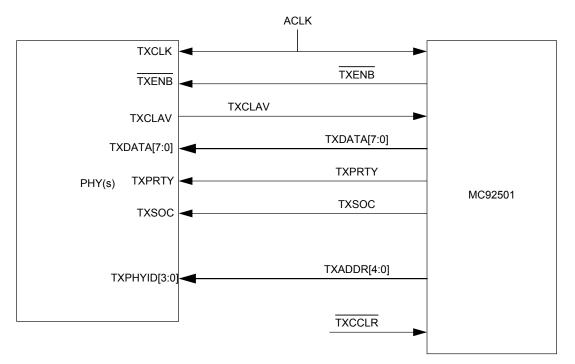

|     | 4.2.2  | UTOPIA Level 1 Transmit PHY Interface (Egress) | 4-6  |

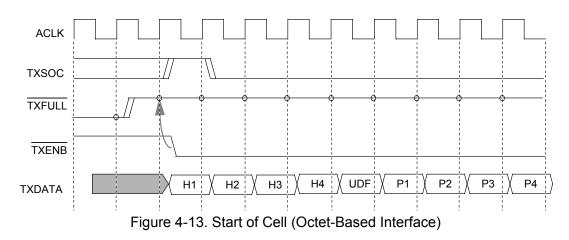

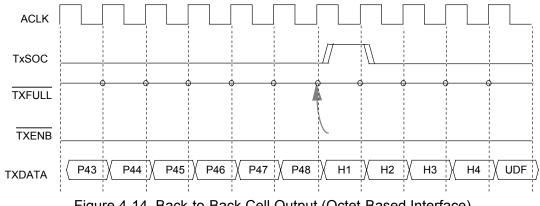

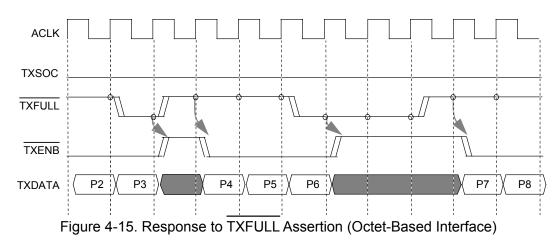

|     |        | 4.2.2.1 Octet-Based Transmit Interface         | 4-9  |

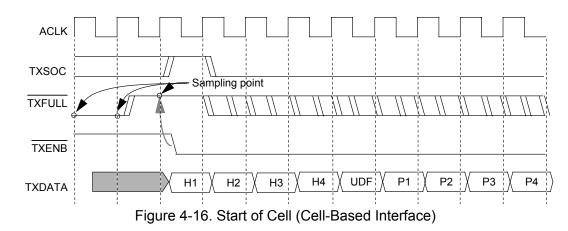

|     |        | 4.2.2.2 Cell-Based Transmit Interface          | 4-10 |

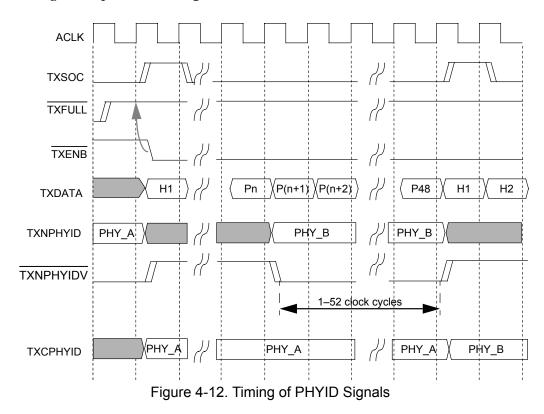

|     |        | 4.2.2.3 Clearing a Transmitted Cell            | 4-11 |

|     | 4.2.3  | UTOPIA Level 2 Receive PHY Interface (Ingress) |      |

|     | 4.2.4  | UTOPIA Level 2 Transmit PHY Interface (Egress) | 4-15 |

| 4.3 | Switc  | h Interface                                    |      |

|     | 4.3.1  | Receive Interface (Ingress)                    | 4-17 |

|     | 4.3.2  | Transmit Interface (Egress)                    | 4-20 |

| 4.4 | Extern | nal Memory Interface                           | 4-22 |

|     | 4.4.1  | EM Bank Select Signals                         | 4-23 |

|     | 4.4.2  | EM Interface Timing For Normal Access          | 4-26 |

|     |        | 4.4.2.1 Normal Read Cycle                      | 4-26 |

|     |        | 4.4.2.2 Normal Write Cycle                     | 4-26 |

|     | 4.4.3  | EM Interface Timing for Maintenance Access     |      |

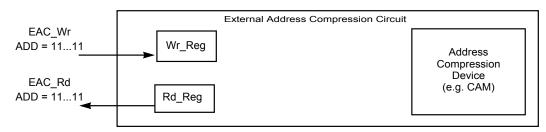

|     | 4.4.4  | External Address Compression Device Access     | 4-29 |

| 4.5 | Micro  | processor Interface                            | 4-30 |

|     | 4.5.1  |                                                |      |

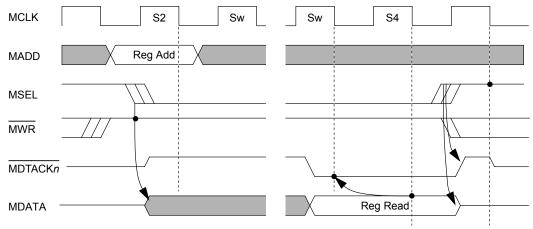

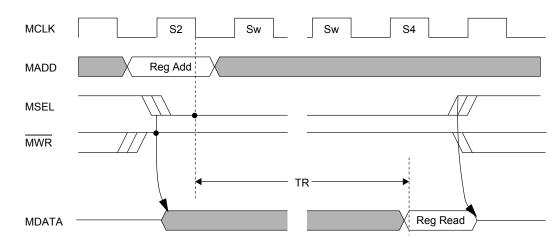

|     |        | 4.5.1.1 Processor Read Operations              | 4-31 |

|     |        | 4.5.1.1.1 General Register Read                | 4-31 |

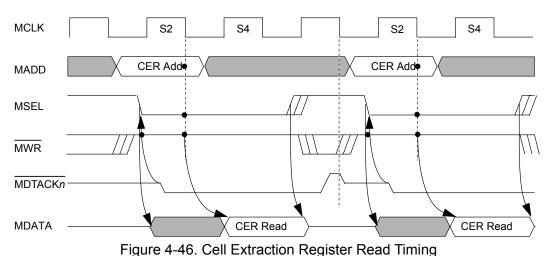

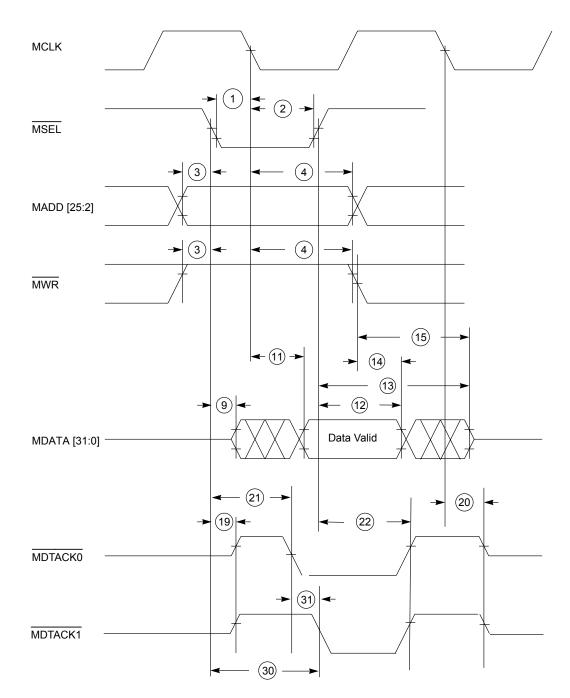

|     |        | 4.5.1.1.2 Cell Extraction Register Read        | 4-32 |

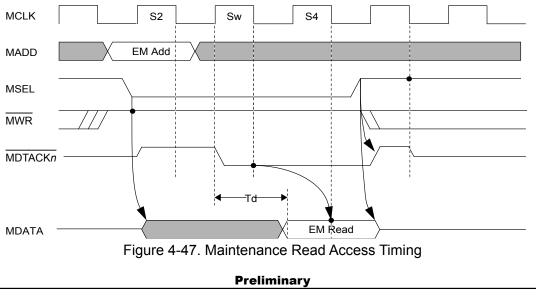

|     |        | 4.5.1.1.3 Maintenance Read Access              | 4-33 |

|     |        | 4.5.1.2 Processor Write Operations             | 4-34 |

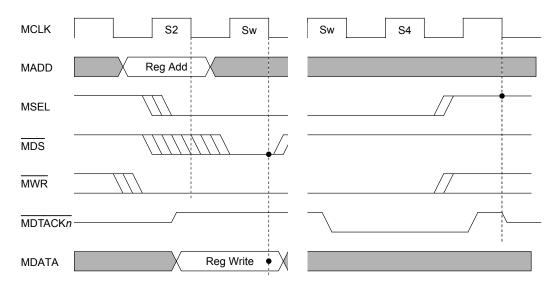

|     |        | 4.5.1.2.1 General Register Write               |      |

|     |        | 4.5.1.2.2 Cell Insertion Register Write        | 4-35 |

|     |        | 4.5.1.2.3 Maintenance Write Access             | 4-37 |

MC92501 User's Manual

| 4.5.2 | DMA Device Support                            | 4-38 |

|-------|-----------------------------------------------|------|

|       | 4.5.2.1 Cell Extraction with DMA Support      |      |

|       | 4.5.2.2 Cell Insertion with DMA Support       |      |

|       | 4.5.2.3 Maintenance Accesses with DMA Support |      |

|       |                                               |      |

#### Section 5 MC92501 Data Path Operation

| 5.1 |                | luction                                               |        |

|-----|----------------|-------------------------------------------------------|--------|

| 5.2 | 0              | ss Data Path Operation                                |        |

|     | 5.2.1          | Interface to Physical Layer – Cell Assembly           |        |

|     | 5.2.2          | Address Compression                                   |        |

|     |                | 5.2.2.1 Address Compression Options                   |        |

|     |                | 5.2.2.2 Table Lookup                                  |        |

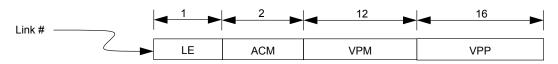

|     |                | 5.2.2.2.1 Link Table                                  |        |

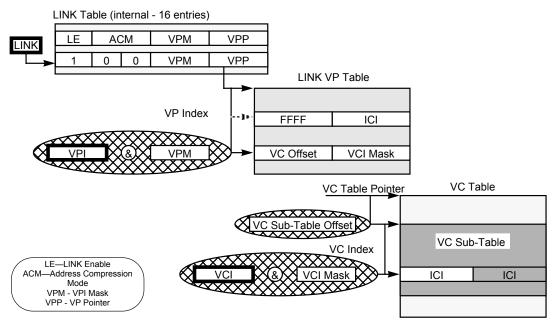

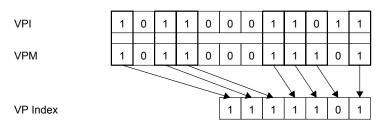

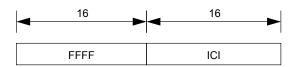

|     |                | 5.2.2.2 VP Table                                      |        |

|     |                | 5.2.2.3 VC Table                                      |        |

|     |                | 5.2.2.4 VC Lookup Disable.                            |        |

|     |                | 5.2.2.3 External Address Compression                  |        |

|     |                | 5.2.2.3.1 External Address Compression with VP Lookup |        |

|     | <b>- - - -</b> | 5.2.2.3.2 VP Lookup Disable                           |        |

|     | 5.2.3          | Ingress Context Table Lookup                          |        |

|     | 5.2.4          | Cell Counting                                         |        |

|     | 5.2.5          | UPC/NPC                                               |        |

|     | 5.2.6          | Ingress Cell Insertion                                |        |

|     | 5.2.7          | Ingress Copy/Remove/OAM Processing                    |        |

|     | 5.2.8          | Switch Overhead Information                           |        |

|     | 5.2.9          | Transfer to Switch                                    |        |

| 5.3 |                | s Data Path Operation                                 |        |

|     | 5.3.1          | Transfer from Switch                                  |        |

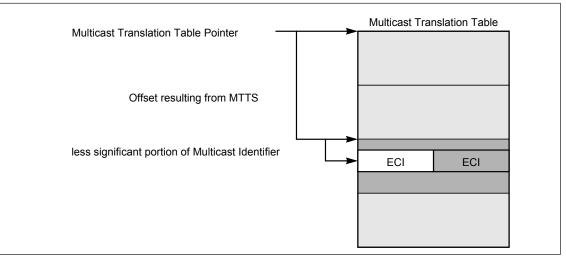

|     | 5.3.2          | Multicast Identifier Translation                      |        |

|     | 5.3.3          | Egress Cell Insertion                                 |        |

|     | 5.3.4          | Egress Context Table Lookup                           |        |

|     | 5.3.5          | UPC/NPC                                               |        |

|     | 5.3.6          | Egress Copy/Remove/OAM Processing                     | . 5-26 |

|     | 5.3.7          | Address Translation                                   |        |

|     | 5.3.8          | Cell Counting                                         |        |

|     | 5.3.9          | Transmission to the Physical Layer                    | . 5-27 |

# Section 6

MC92501 Protocol Processing Support

| 6.1 | Overview        | 6-1 |

|-----|-----------------|-----|

| 6.2 | UPC/NPC Support | 6-2 |

|     |        |                                                       | _             |

|-----|--------|-------------------------------------------------------|---------------|

|     | 6.2.1  | Cell Based UPC 6-                                     |               |

|     | 6.2.2  | Packet Based UPC 6-                                   | -3            |

|     | 6.2.3  | Cell-based UPC 6-                                     | -3            |

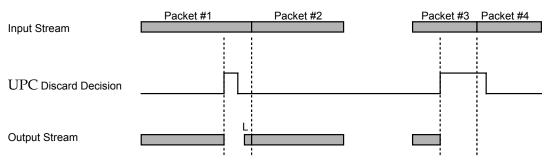

|     | 6.2.4  | Partial Packet Discard (PPD) 6-                       | -3            |

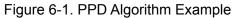

|     | 6.2.5  | Early Packet Discard (EPD) 6-                         |               |

|     | 6.2.6  | Limited Early Packet Discard (Limited EPD) 6-         |               |

| 6.3 |        | [Support                                              |               |

| 0.0 | 6.3.1  | Conventions                                           |               |

|     | 6.3.2  | ATM Layer OAM Definitions                             |               |

|     | 0.5.2  | 6.3.2.1 Virtual Path (F4) Flow Mechanism              |               |

|     |        |                                                       |               |

|     |        | 6.3.2.2 Virtual Channel (F5) Flow Mechanism           |               |

|     |        | 6.3.2.3 OAM Types and Function Types                  |               |

|     | 6.3.3  | Internal Scan                                         |               |

|     | 6.3.4  | General OAM                                           |               |

|     |        | 6.3.4.1 Illegal OAM Cells 6-1                         |               |

|     |        | 6.3.4.2 Other OAM Cells                               |               |

|     | 6.3.5  | Fault Management    6-1                               | 1             |

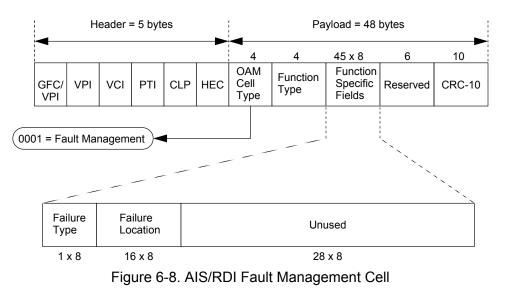

|     |        | 6.3.5.1 Alarm Surveillance 6-1                        | 1             |

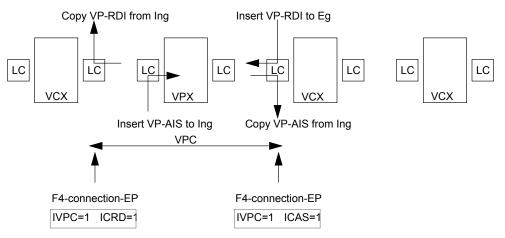

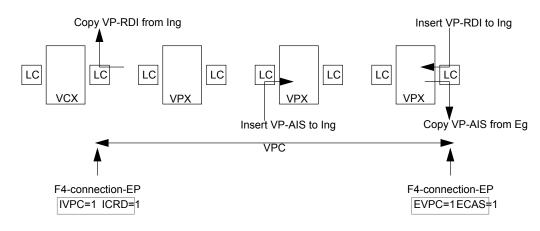

|     |        | 6.3.5.1.1 VP/VC AIS 6-1                               | 2             |

|     |        | 6.3.5.1.2 VP/VC RDI 6-1                               | 3             |

|     |        | 6.3.5.1.3 Continuity Check 6-1                        |               |

|     |        | 6.3.5.2 Failure Localization and Testing              |               |

|     |        | 6.3.5.3 VPC/VCC Loopback Cells                        |               |

|     | 6.3.6  | Performance Management 6-2                            |               |

|     | 6.3.7  | Performance Monitoring                                |               |

|     | 6.3.8  | Activation/Deactivation OAM Cells                     |               |

| 6.4 |        | Support                                               |               |

| 0.1 | 6.4.1  | RM Cell Definition                                    |               |

|     | 6.4.2  | RM Cell Fields                                        |               |

|     | 6.4.3  |                                                       |               |

|     | 0.4.5  | Cell Marking (CI, NI, PTI)                            |               |

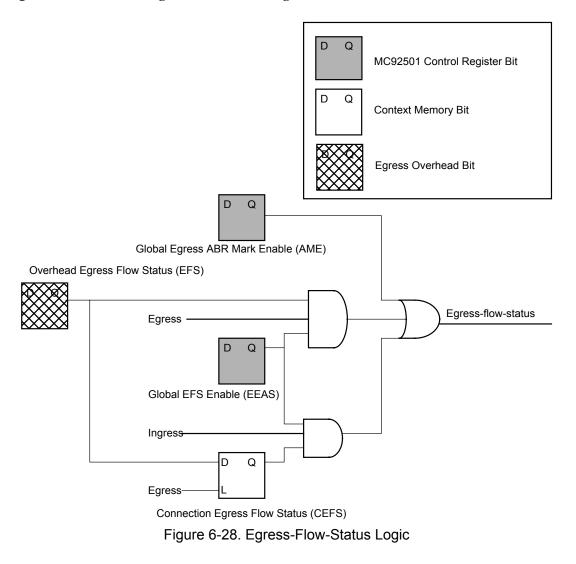

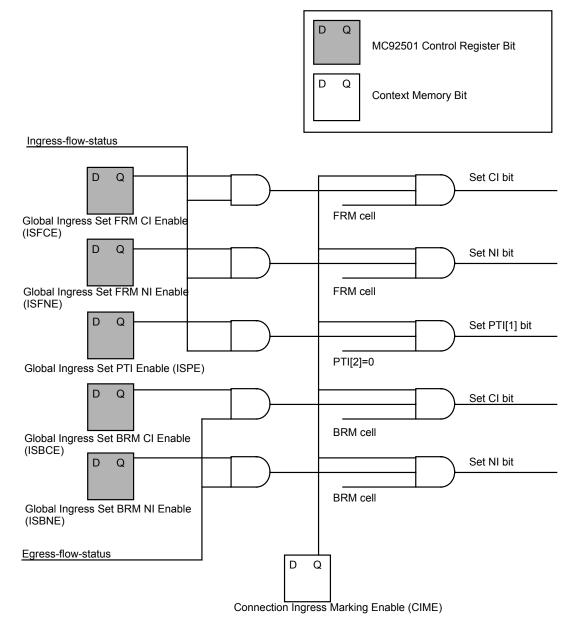

|     |        | 6.4.3.1 Sources for Ingress Flow Status               |               |

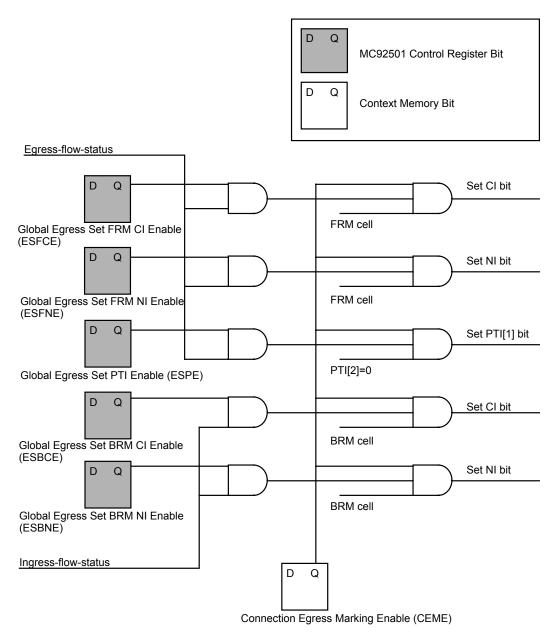

|     |        | 6.4.3.2 Sources for Egress Flow Status                |               |

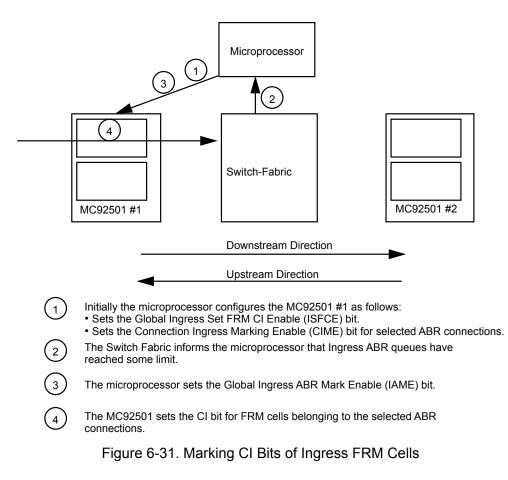

|     |        | 6.4.3.3 MC92501 Ingress Direction Actions             |               |

|     |        | 6.4.3.4 MC92501 Egress Direction Actions              |               |

|     |        | 6.4.3.5 Cell Marking Examples 6-3                     | 38            |

|     | 6.4.4  | Ingress Switch Parameters Hooks 6-4                   |               |

|     | 6.4.5  | Egress Reset EFCI                                     | 1             |

| 6.5 | CLP 7  | Fransparency Support    6-4                           | 12            |

| 6.6 | Select | tive Discard Support 6-4                              | 13            |

| 6.7 | Multi  | ple PHY Support                                       | 13            |

|     | 6.7.1  |                                                       |               |

|     | 6.7.2  | Cell Counters                                         |               |

|     | 6.7.3  | Address Compression                                   |               |

|     | 6.7.4  | Address Translation                                   |               |

|     | 6.7.5  | Cell Extraction Queue                                 |               |

|     | 6.7.6  | Multicast Translation                                 |               |

|     | 0.7.0  | 1/10/10/2011 11/10/10/10/10/10/10/10/10/10/10/10/10/1 | $\mathcal{O}$ |

MOTOROLA

-6

Section 7 MC92501 Programming Model

| 7.1<br>7.2 | Introduction          |                                                                  |       |  |  |

|------------|-----------------------|------------------------------------------------------------------|-------|--|--|

|            | Registers Description |                                                                  |       |  |  |

|            | 7.2.1                 | 1                                                                |       |  |  |

|            |                       | 7.2.1.1 Cell Insertion Address Space                             |       |  |  |

|            |                       | 7.2.1.2 CIR Alternate Address Space                              |       |  |  |

|            | 7.2.2                 | Cell Extraction Registers (CER0-CER15)                           |       |  |  |

|            |                       | 7.2.2.1 Cell Extraction Address Space                            | . 7-4 |  |  |

|            | 7.2.3                 | General Register List                                            |       |  |  |

|            | 7.2.4                 | Status Reporting Registers                                       | . 7-7 |  |  |

|            |                       | 7.2.4.1 Interrupt Register (IR)                                  | . 7-7 |  |  |

|            |                       | 7.2.4.2 Interrupt Mask Register (IMR)                            | 7-10  |  |  |

|            |                       | 7.2.4.3 Last Cell Processing Time Register (LCPTR)               |       |  |  |

|            |                       | 7.2.4.4 ATMC CFB Revision Register (ARR)                         | 7-11  |  |  |

|            |                       | 7.2.4.5 MC92501 Revision Register (RR)                           |       |  |  |

|            | 7.2.5                 | Control Registers                                                | 7-12  |  |  |

|            |                       | 7.2.5.1 Microprocessor Control Register (MPCTLR)                 | 7-12  |  |  |

|            |                       | 7.2.5.2 Maintenance Control Register (MACTLR)                    | 7-13  |  |  |

|            |                       | 7.2.5.3 Cell Extraction Queue Filtering Register 0 (CEQFR0)      |       |  |  |

|            |                       | 7.2.5.4 Cell Extraction Queue Filtering Register 1 (CEQFR1)      |       |  |  |

|            |                       | 7.2.5.5 Cell Extraction Queue Priority Register 0 (CEQPR0)       |       |  |  |

|            |                       | 7.2.5.6 Cell Extraction Queue Priority Register 1 (CEQPR1)       | 7-15  |  |  |

|            |                       | 7.2.5.7 Ingress Insertion Leaky Bucket Register (IILB)           | 7-16  |  |  |

|            |                       | 7.2.5.8 Ingress Insertion Bucket Fill Register (IIBF)            | 7-16  |  |  |

|            |                       | 7.2.5.9 Egress Insertion Leaky Bucket Register (EILB)            |       |  |  |

|            |                       | 7.2.5.10 Egress Insertion Bucket Fill Register (EIBF)            | 7-17  |  |  |

|            |                       | 7.2.5.11 Internal Scan Control Register (ISCR)                   |       |  |  |

|            |                       | 7.2.5.12 Ingress Link Registers (ILNK0-ILNK15)                   | 7-18  |  |  |

|            |                       | 7.2.5.13 Egress Link Enable Register (ELER)                      | 7-19  |  |  |

|            |                       | 7.2.5.14 Ingress Billing Counters Table Pointer Register (IBCTP) |       |  |  |

|            |                       | 7.2.5.15 Egress Billing Counters Table Pointer Register (EBCTP)  | 7-20  |  |  |

|            |                       | 7.2.5.16 Policing Counters Table Pointer Register (PCTP)         | 7-20  |  |  |

|            |                       | 7.2.5.17 Cell Time Register (CLTM)                               |       |  |  |

|            |                       | 7.2.5.18 Ingress Processing Control Register (IPLR)              | 7-21  |  |  |

|            |                       | 7.2.5.19 Egress Processing Control Register (EPLR)               |       |  |  |

|            |                       | 7.2.5.20 Indirect External Memory Access Address Register (IAAR) | 7-22  |  |  |

|            |                       | 7.2.5.21 Indirect External Memory Access Data Register (IADR)    | 7-22  |  |  |

|            | 7.2.6                 | Configuration Registers                                          | 7-22  |  |  |

|            |                       | 7.2.6.1 Microprocessor Configuration Register (MPCONR)           | 7-23  |  |  |

|            |                       | 7.2.6.2 Maintenance Configuration Register (MACONR)              | 7-25  |  |  |

|            |                       | 7.2.6.3 Ingress PHY Configuration Register (IPHCR)               |       |  |  |

|            |                       | 7.2.6.4 Egress PHY Configuration Register (EPHCR)                |       |  |  |

|            |                       | 7.2.6.5 Ingress Switch Interface Configuration Register (ISWCR)  | 7-28  |  |  |

|       | 7.2.6.6 Egress Switch Interface Configuration Register (ESWCR)                       |      |

|-------|--------------------------------------------------------------------------------------|------|

|       | 7.2.6.7 Egress Switch Overhead Information Register (ESOIR0)                         |      |

|       | 7.2.6.8 Egress Switch Overhead Information Register 1 (ESOIR1)                       |      |

|       | 7.2.6.9 UNI Register (UNIR)                                                          | 7-36 |

|       | 7.2.6.9 UNI Register (UNIR)7.2.6.10 Ingress Processing Configuration Register (IPCR) | 7-36 |

|       | 7.2.6.11 Egress Processing Configuration Register (EPCR)                             | 7-39 |

|       | 7.2.6.12 Egress Multicast Configuration Register (EMCR)                              | 7-41 |

|       | 7.2.6.13 ATMC CFB Configuration Register (ACR)                                       | 7-41 |

|       | 7.2.6.14 General Configuration Register (GCR)                                        | 7-44 |

|       | 7.2.6.15 Context Parameters Table Pointer Register (CPTP)                            | 7-44 |

|       | 7.2.6.16 OAM Table Pointer Register (OTP)                                            | 7-45 |

|       | 7.2.6.17 Dump Vector Table Pointer Register (DVTP)                                   | 7-45 |

|       | 7.2.6.18 VC Table Pointer Register (VCTP)                                            | 7-45 |

|       | 7.2.6.19 Multicast Translation Table Pointer Register (MTTP)                         | 7-45 |

|       | 7.2.6.20 Flags Table Pointer Register (FTP)                                          |      |

|       | 7.2.6.21 Egress Link Counters Table Pointer Register (ELCTP)                         | 7-46 |

|       | 7.2.6.22 Ingress Link Counters Table Pointer Register (ILCTP)                        | 7-46 |

|       | 7.2.6.23 Context Parameters Extension Table Pointer Register (CPETP)                 | 7-46 |

|       | 7.2.6.24 Node ID Register 0 (ND0)                                                    | 7-47 |

|       | 7.2.6.25 Node ID Register 1 (ND1)                                                    | 7-47 |

|       | 7.2.6.26 Node ID Register 2 (ND2)                                                    | 7-47 |

|       | 7.2.6.27 Node ID Register 3 (ND3)                                                    | 7-47 |

|       | 7.2.6.28 Ingress VCI Copy Register (IVCR)                                            | 7-48 |

|       | 7.2.6.29 Egress VCI Copy Register (EVCR)                                             | 7-48 |

|       | 7.2.6.30 Ingress VCI Remove Register (IVRR)                                          |      |

|       | 7.2.6.31 Egress VCI Remove Register (EVRR)                                           |      |

|       | 7.2.6.32 Performance Monitoring Exclusion Register (PMER)                            |      |

|       | 7.2.6.33 External Memory Timing Configuration Register (EMTCR)                       |      |

|       | 7.2.6.34 External Memory Interface Configuration Register (EMICR) .                  |      |

|       | 7.2.6.35 RM Overlay Register (RMOR)                                                  |      |

|       | 7.2.6.36 CLP Transparency Overlay Register (CTOR)                                    | 7-54 |

|       | 7.2.6.37 Egress Overhead Manipulation Register (EGOMR)                               |      |

| 7.2.7 | Pseudo-Registers                                                                     | 7-56 |

|       | 7.2.7.1 Software Reset Register (SRR)                                                |      |

|       | 7.2.7.2 Start SCAN Register (SSR)                                                    |      |

|       | 7.2.7.3 Enter Operate Mode Register (EOMR)                                           |      |

| 7.2.8 | External Address Compression Device Access                                           |      |

| 7.2.9 | Maintenance Access                                                                   |      |

|       | nal Memory Description                                                               |      |

| 7.3.1 | Memory Partitioning                                                                  |      |

| 7.3.2 | Memory Allocation                                                                    |      |

| 7.3.3 | Context Parameters Table                                                             |      |

|       | 7.3.3.1 Egress Translation Address                                                   |      |

|       | 7.3.3.2 Ingress Translation Address                                                  |      |

|       | 7.3.3.3 Switch Parameters                                                            |      |

|       | 7.3.3.4 Common Parameters                                                            | 7-66 |

MC92501 User's Manual

MOTOROLA

7.3

|     |        | 7.3.3.5 Egress Parameters                                           |

|-----|--------|---------------------------------------------------------------------|

|     |        | 7.3.3.6 Ingress Parameters                                          |

|     | 7.3.4  | Ingress Billing Counters Table                                      |

|     | 7.3.5  | Egress Billing Counters Table                                       |

|     | 7.3.6  | Policing Counters Table                                             |

|     | 7.3.7  | Flags Table         7-78                                            |

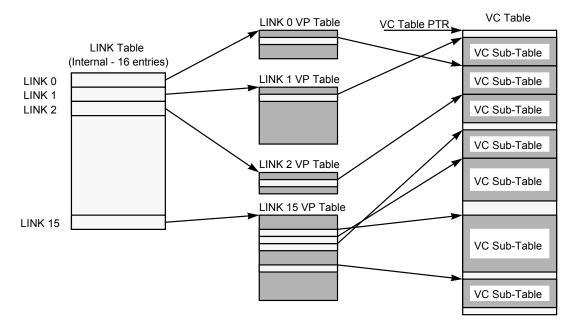

|     | 7.3.8  | VP Table                                                            |

|     |        | 7.3.8.1 VP Table Record without VC Table Lookup                     |

|     |        | 7.3.8.2 VP Table Record with VC Table Lookup                        |

|     | 7.3.9  | VC Table                                                            |

|     |        | Multicast Translation Table                                         |

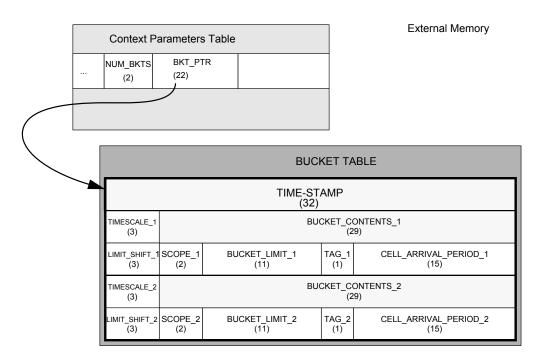

|     | 7.3.11 | Buckets Record                                                      |

|     |        | 7.3.11.1 Bucket Entries for One Connection                          |

|     |        | 7.3.11.2 Bucket Information                                         |

|     |        | OAM Table                                                           |

|     |        | Dump Vector Table7-86                                               |

|     |        | Ingress Link Counters Table                                         |

|     |        | Egress Link Counters Table                                          |

|     |        | Context Parameters Extension Table                                  |

| 7.4 |        | Otructures                                                          |

|     | 7.4.1  | Inserted Cell                                                       |

|     |        | 7.4.1.1 Cell Descriptor                                             |

|     |        | 7.4.1.2 Connection Descriptor                                       |

|     |        | 7.4.1.3 ATM Cell Header                                             |

|     |        | 7.4.1.4 Inserted OAM Fields Template                                |

|     | 7.4.2  | Extracted Cell                                                      |

|     |        | 7.4.2.1 Cell Indication                                             |

|     |        | 7.4.2.1.1 User/OAM Cell Indication                                  |

|     |        | 7.4.2.1.2 Egress Multicast Translation Failure Cell Indication 7-98 |

|     |        | 7.4.2.1.3 Error Cell Indication                                     |

|     |        | 7.4.2.1.4 Short Report Indication                                   |

|     |        | 7.4.2.1.5 OAM Fields Template Indication                            |

|     |        | 7.4.2.2 Connection Indication                                       |

|     |        | 7.4.2.3 Time-Stamp                                                  |

|     |        | 7.4.2.4 ATM Cell Header                                             |

|     |        | 7.4.2.5 Extracted OAM Fields Template                               |

|     | 7.4.3  | External Address Compression                                        |

|     | 7.4.4  | General Fields                                                      |

|     |        | 7.4.4.1 Cell Name                                                   |

|     |        | 7.4.4.2 Reason                                                      |

#### Section 8 Test Operation

| 8.1 JTAG Overview |

|-------------------|

|-------------------|

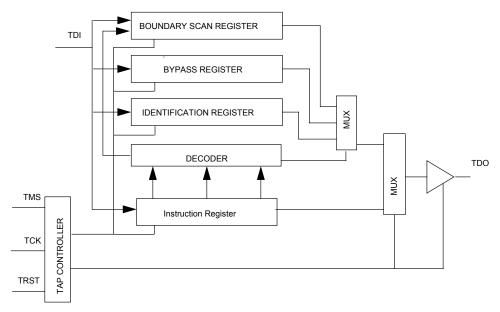

| 8.1.1 | Functional Blocks                      | . 8-2 |

|-------|----------------------------------------|-------|

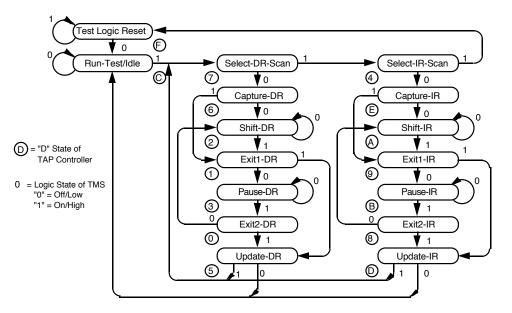

|       | 8.1.1.1 TAP Controller                 | . 8-3 |

|       | 8.1.1.2 Instruction Register           | . 8-3 |

|       | 8.1.1.3 Device Identification Register | . 8-3 |

|       | 8.1.1.4 Bypass Register                | . 8-4 |

|       | 8.1.1.5 Boundary Scan Register         | . 8-4 |

| 8.1.2 | JTAG Instruction Support               | . 8-4 |

| 8.1.3 | Boundary Scan Register Path            | . 8-6 |

#### Section 9

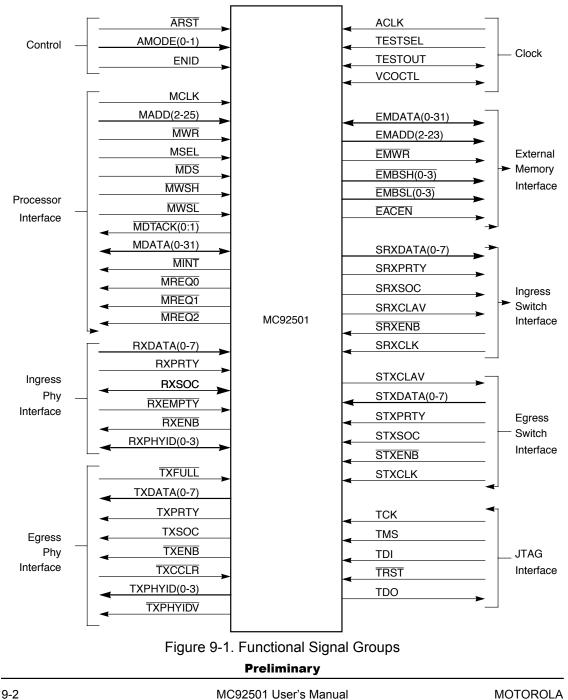

| 9.1 | Introd | luction                           |

|-----|--------|-----------------------------------|

| 9.2 | Signal | Description                       |

|     | 9.2.1  | Ingress PHY Signals               |

|     | 9.2.2  | Egress PHY Signals                |

|     | 9.2.3  | Ingress Switch Interface Signals  |

|     | 9.2.4  | Egress Switch Interface Signals   |

|     | 9.2.5  | External Memory Signals           |

|     | 9.2.6  | Control Signals                   |

|     | 9.2.7  | Microprocessor Signals (MP)       |

|     | 9.2.8  | PLL Signals                       |

|     | 9.2.9  | Test Signals                      |

| 9.3 | Electr | ical and Physical Characteristics |

|     | 9.3.1  | Absolute Maximum Ratings          |

|     | 9.3.2  | Recommended Operating Conditions  |

|     | 9.3.3  | DC Electrical Characteristics     |

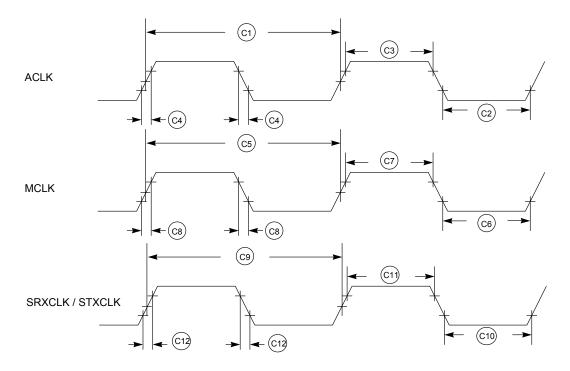

|     | 9.3.4  | Clocks                            |

|     | 9.3.5  | Microprocessor Interface Timing   |

|     | 9.3.6  | PHY Interface Timing              |

|     | 9.3.7  | Switch Interface Timing           |

|     | 9.3.8  | External Memory Interface Timing  |

|     |        | 9.3.8.1 Write Cycle Timing        |

|     |        | 9.3.8.2 Read Cycle Timing         |

| 9.4 | Order  | ing Information                   |

| 9.5 | Mecha  | anical Data                       |

|     | 9.5.1  | Pin Assignments                   |

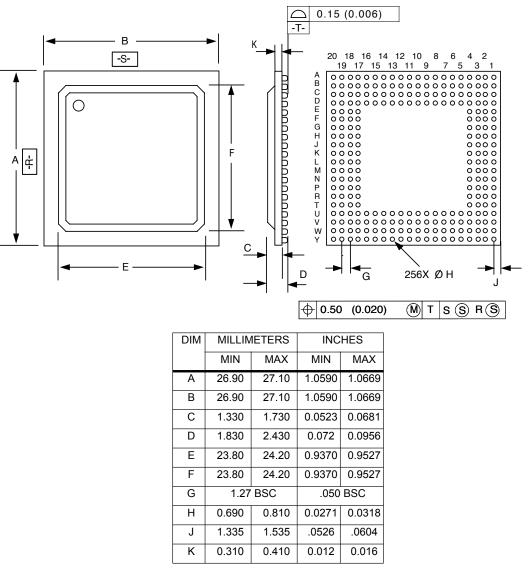

|     | 9.5.2  | Package Dimensions                |

#### Appendix A UPC/NPC Design

| A.1 | Time-Stamped Leaky Time Bucket | A-1 |

|-----|--------------------------------|-----|

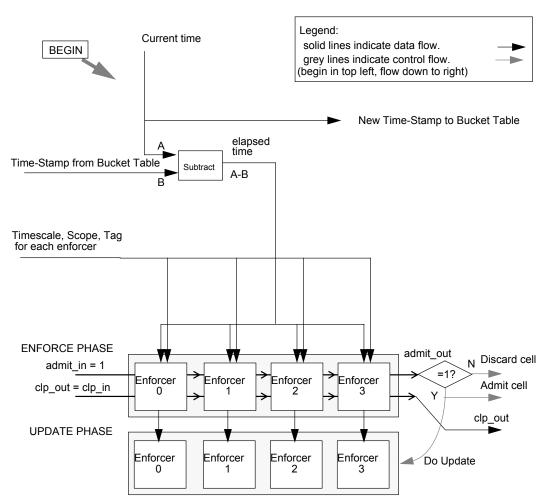

| A.2 | Multi-Enforcer UPC/NPC         | A-2 |

-10

**Freescale Semiconductor, Inc.**

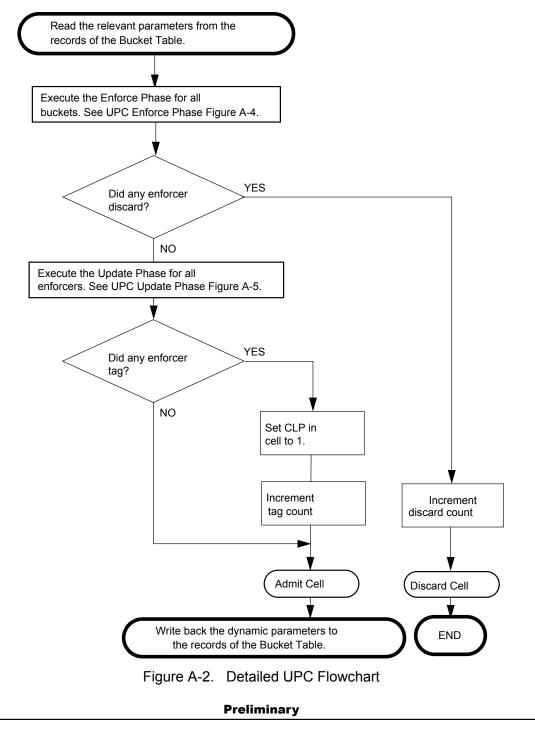

| Α3  | Data Structure                         | A-3  |

|-----|----------------------------------------|------|

|     | Detailed Flowchart                     |      |

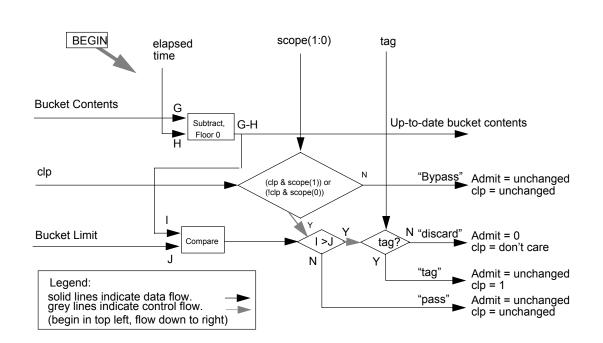

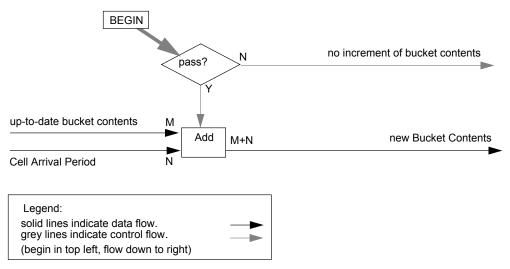

|     | Control/Data Flowcharts                |      |

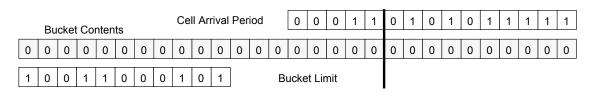

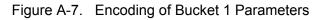

| A.6 | Bucket Parameter Encoding              | A-7  |

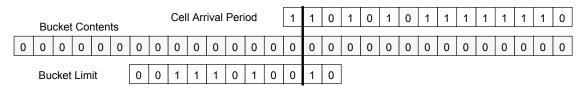

| A   | .6.1 Cell Arrival Computation Example  | A-8  |

| A   | .6.2 Bucket Limit Encoding             | A-9  |

| A.7 | UPC Parameter Calculations             | A-9  |

| A   | .7.1 Example A                         | A-9  |

|     | .7.2 Example B                         |      |

| A.8 | Bellcore Cell Relay Service Parameters | A-11 |

#### Appendix B

Maintenance Slot Calculations

| B.1 | Maintenance Slot Equations B-    | ·1 |

|-----|----------------------------------|----|

| B.2 | Maintenance Time Slot Example B- | ·2 |

|     | Maintenance Slot Parameters B-   |    |

## Appendix C

**External Memory Calculations**

| C.1 | External Memory Allocation Program  | C-1  |

|-----|-------------------------------------|------|

| C.2 | External Memory Allocation Examples | C-7  |

| C.  | .2.1 16K Connections – 2 MB RAM     | C-7  |

| C.  | .2.2 8K Connections – 512 KB RAM    | C-8  |

| C.  | .2.3 4K Connections – 256 KB RAM    | C-9  |

| C.  | .2.4 64K Connections – 16 MB of RAM | C-10 |

## Appendix D

Tutorial

| D.1 VC Bundling                                   | D-1 |

|---------------------------------------------------|-----|

| D.1.1 VP-VC Boundary                              |     |

| D.1.1.1 Bundling VCs into a VP                    | D-1 |

| D.1.1.2 Separating a VP into VCs                  | D-2 |

| D.1.2 F4-Level OAM Processing at a VP/VC Boundary | D-3 |

| D.1.2.1 Continuity Check                          |     |

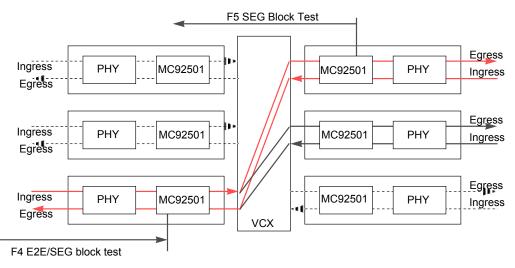

| D.1.2.2 OAM Block Test                            |     |

| D.1.3 F5-Level OAM Processing at a VP/VC Boundary | D-3 |

| D.1.4 Reserved VCI Values                         | D-4 |

|                                                   |     |

#### Appendix E

#### MC92501 Applications

| E.1 | Int            | troduction                         | <br>E-1 |

|-----|----------------|------------------------------------|---------|

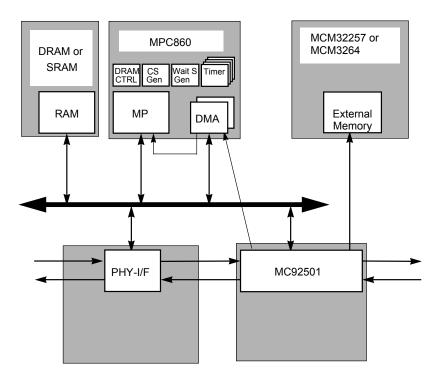

| E.2 | Sta            | andard Line Card Architecture      | <br>E-1 |

|     | E. <b>2</b> .1 | MC92501                            | <br>E-2 |

|     | E.2.2          | РНҮ                                | <br>E-2 |

|     | E.2.3          | Microprocessor                     | <br>E-2 |

|     | E.2.4          | External Memory                    | <br>E-2 |

|     | E.2.5          | Microprocessor RAM                 | <br>E-2 |

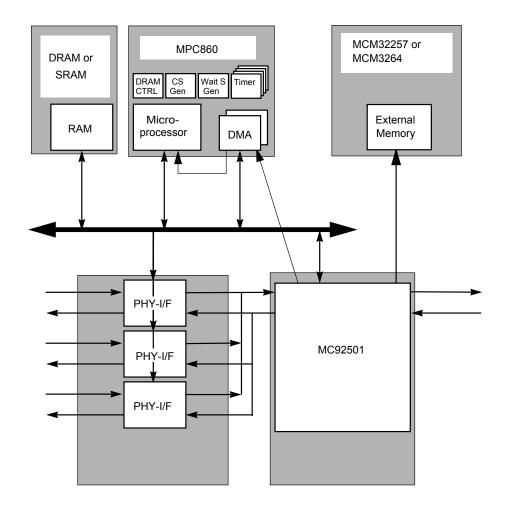

|     |                | ultiple PHY Line Card Architecture |         |

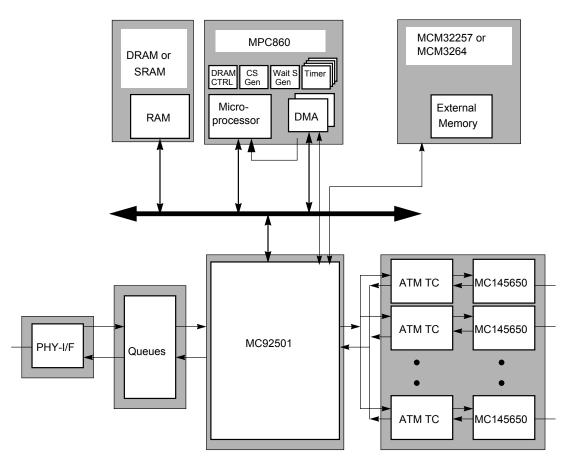

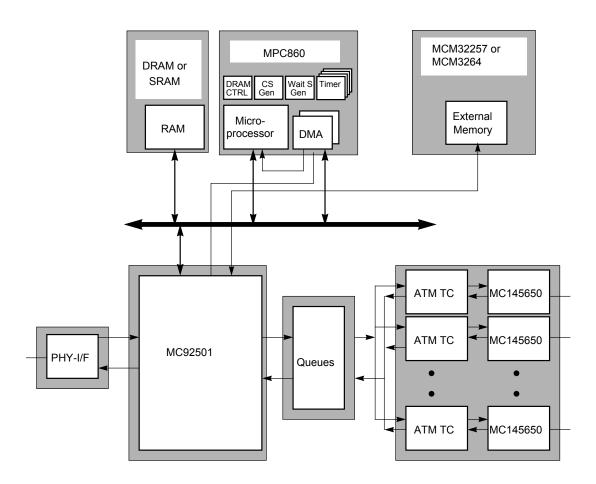

| E.4 | DS             | SLAM Access Network Architectures  | <br>E-4 |

Appendix F BSDL Code

Appendix G References

# **List of Figures**

| 1-1                    | Typical ATM Notycerk Structure 1.2                                           |

|------------------------|------------------------------------------------------------------------------|

| 1-1<br>1-2             | Typical ATM Network Structure1-2Typical ATM Line Card Application1-3         |

| 1-2<br>1-3             | MC92501 Network Access Multiplexer Design Examples                           |

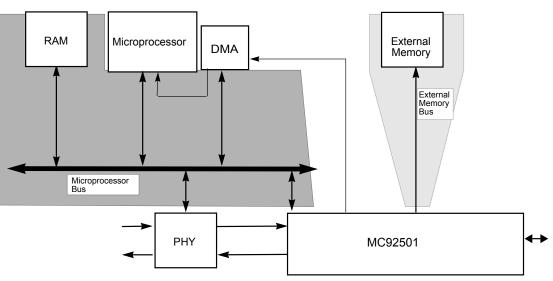

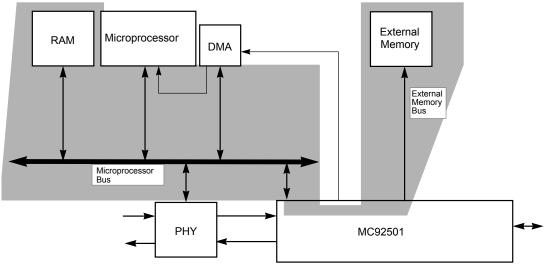

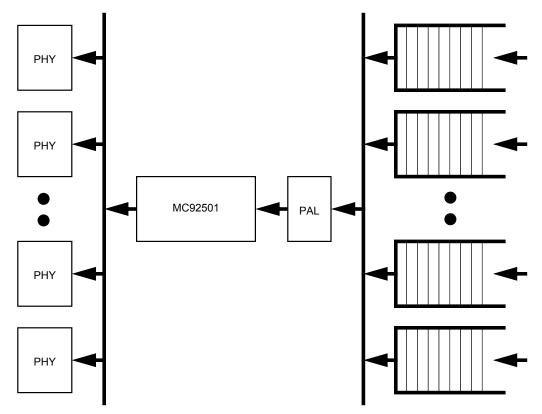

| 1-5<br>2-1             | ATMC Schematic Interface                                                     |

| 2-1<br>2-2             | ATMC System During Cell Processing                                           |

| 2-2<br>2-3             | ATMC System During Cent Hocessing                                            |

| 2-3<br>2-4             | MC92501 Block Diagram                                                        |

| 2- <del>4</del><br>3-1 | MC92501 Diock Diagram                                                        |

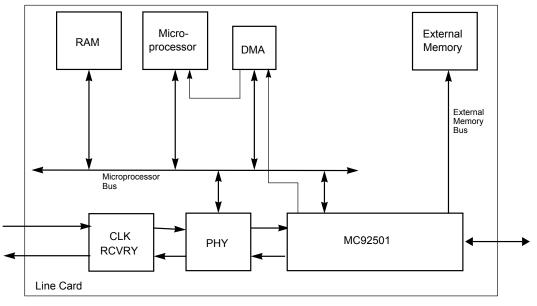

| 3-1<br>3-2             | ATM Line Card Architecture with DMA Device                                   |

| 3-3                    | Example of Maintenance Slot Usage                                            |

| 3-4                    | Inserted Cell Structure (Motorola-style byte order)                          |

| 3- <del>1</del><br>3-5 | Inserted Cell Structure (Intel-style byte order)                             |

| 3-6                    | Cell Extraction Queue Filtering                                              |

| 3-7                    | Cell Extraction Queue                                                        |

| 3-8                    | Extracted Cell Structure (Motorola-style byte order)                         |

| 3-9                    | Extracted Cell Structure (Intel-style byte order)                            |

| 4 <b>-</b> 1           | MC92501 Receive PHY Interface                                                |

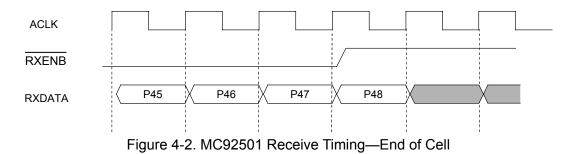

| 4-2                    | MC92501 Receive Timing – End of Cell                                         |

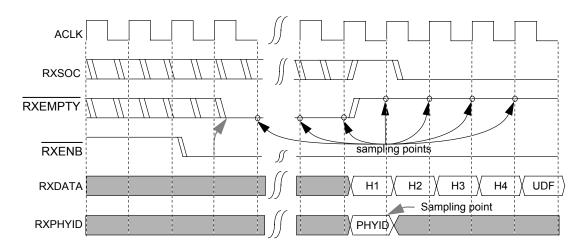

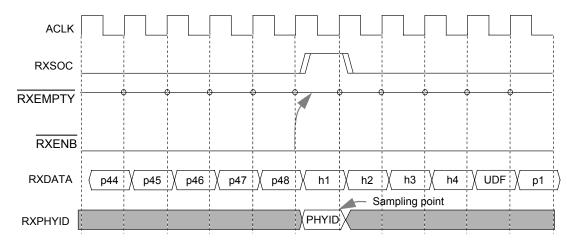

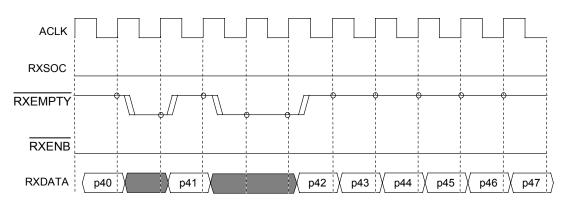

| 4-3                    | Start of Cell – MC92501 Empty (Octet-Based Interface)                        |

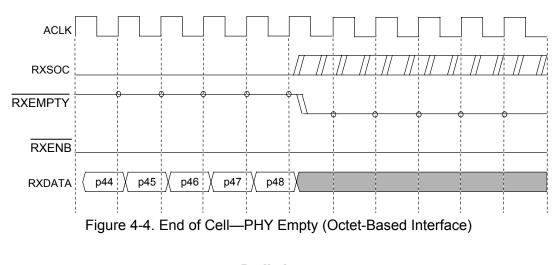

| 4-4                    | End of Cell – PHY Empty (Octet-Based Interface)                              |

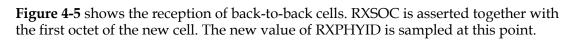

| 4-5                    | Back-to-Back Cell Input (Octet-Based Interface)                              |

| 4-6                    | Response to RXEMPTY Assertion (Octet-Based Interface)                        |

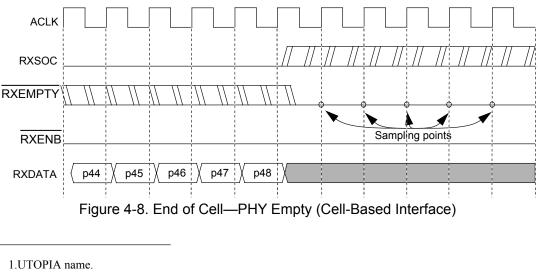

| 4-7                    | Start of Cell – MC92501 Empty (Cell-Based Interface)                         |

| 4-8                    | End of Cell – PHY Empty (Cell-Based Interface)                               |

| 4-9                    | Back to Back Cell Input (Cell-Based Interface)                               |

| 4-10                   | MC92501 Transmit PHY Interface                                               |

| 4-11                   | MC92501 Transmit Timing – MC92501 is Empty                                   |

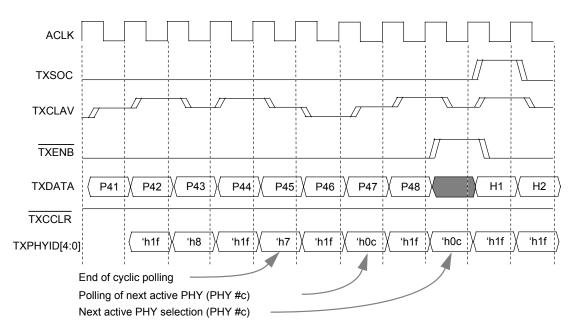

| 4-12                   | Timing of PHYID Signals                                                      |

| 4-13                   | Start of Cell (Octet-Based Interface)                                        |

| 4-14                   | Back-to-Back Cell Output (Octet-Based Interface)                             |

| 4-15                   | Response to TXFULL Assertion (Octet-Based Interface)                         |

| 4-16                   | Start of Cell (Cell-Based Interface)                                         |

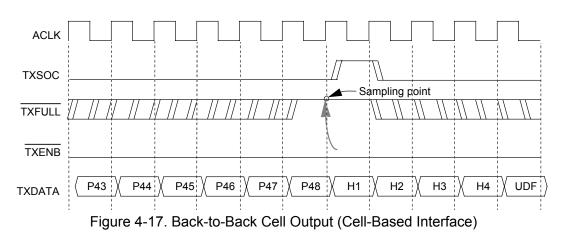

| 4-17                   | Back-to-Back Cell Output (Cell-Based Interface)                              |

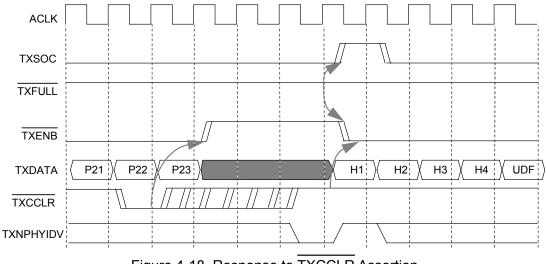

| 4-18                   | Response to TXCCLR Assertion                                                 |

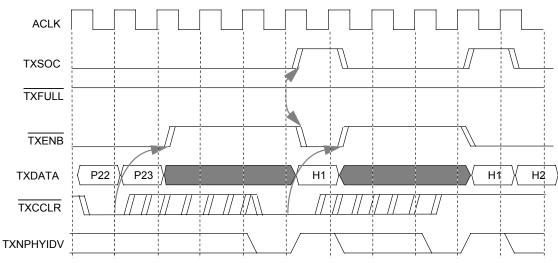

| 4-19                   | Consecutive Cell Discards                                                    |

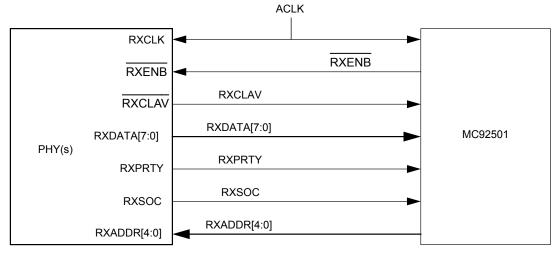

| 4-20                   | MC92501 Receive PHY Interface                                                |

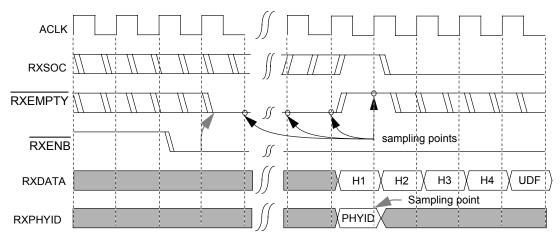

| 4-21                   | Poll PHYs, Select PHY, and Start Reading a Cell 4-13                         |

| 4-22                   | The MC92501 Polls the PHYs While Transferring a Cell and Starts Transferring |

|                        | Data from the Selected Cell 4-14                                             |

| 4-23                   | The MC92501 Reads Cells from the Same PHY 4-14                               |

|                        |                                                                              |

Preliminary

MOTOROLA

MC92501 User's Manual

List of Figures

| 4.04         |                                                                   | 4 4 5 |

|--------------|-------------------------------------------------------------------|-------|

| 4-24         | MC92501 Transmit PHY Interface                                    |       |

| 4-25         | ATMC CFB Transmit Timing – End of Cell Output and PHY Switching . |       |

| 4-26         | ATMC CFB End of Cell Output and PHY Switching                     |       |

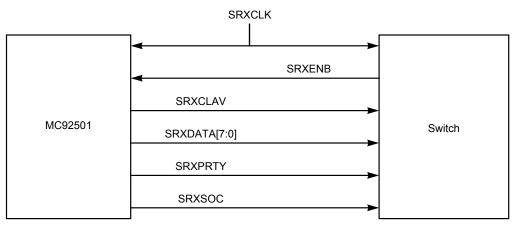

| 4-27         | MC92501 Switch Receive Interface                                  |       |

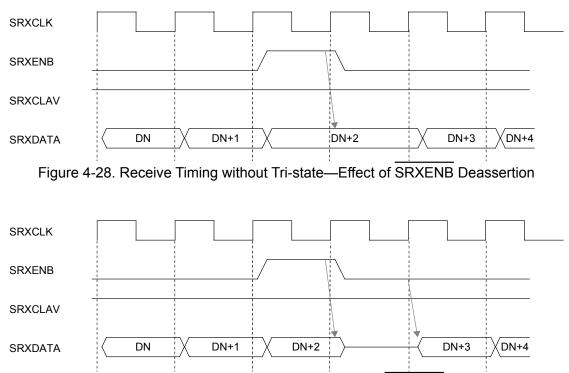

| 4-28         | Receive Timing without Tri-state – Effect of SRXENB Deassertion   |       |

| 4-29         | Receive Timing with Tri-state – Effect of SRXENB Deassertion      | 4-18  |

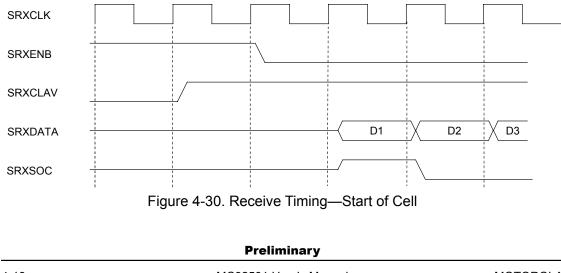

| 4-30         | Receive Timing – Start of Cell                                    | 4-18  |

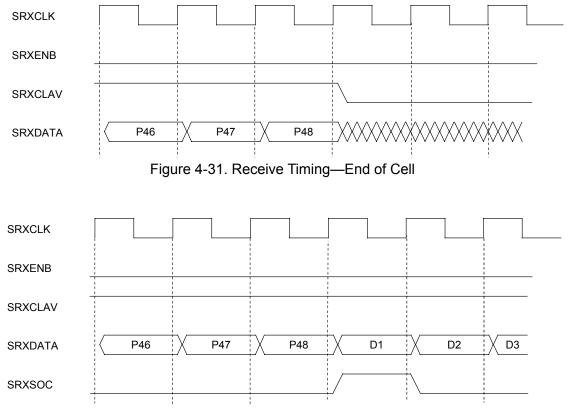

| 4-31         | Receive Timing – End of Cell                                      | 4-19  |

| 4-32         | Receive Timing – Back-to-Back Cell Transfers                      | 4-19  |

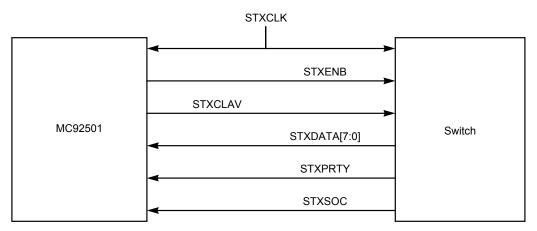

| 4-33         | MC92501 Switch Transmit Interface                                 | 4-20  |

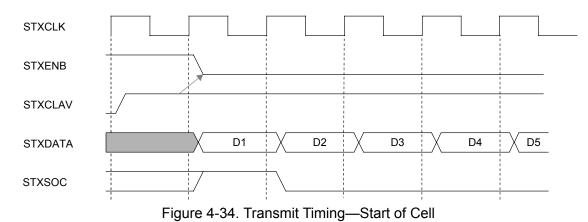

| 4-34         | Transmit Timing – Start of Cell                                   | 4-20  |

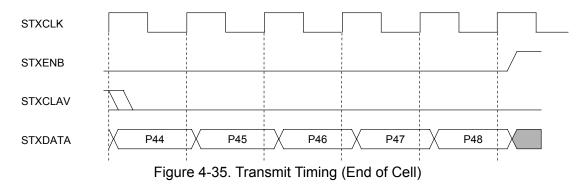

| 4-35         | Transmit Timing (End of Cell)                                     |       |

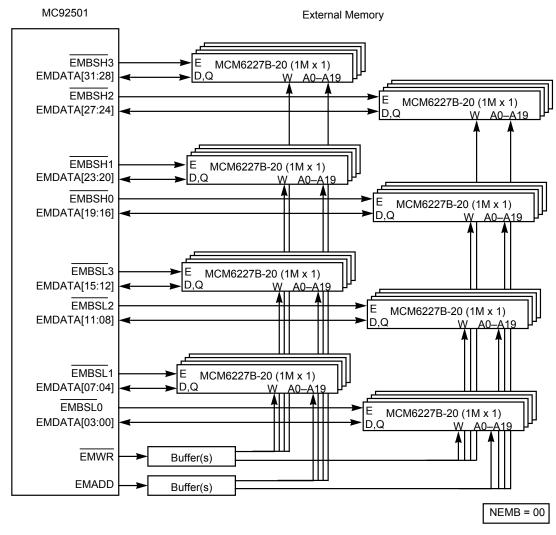

| 4-36         | External Memory Configuration Providing 4 MB in 1 Bank            |       |

| 4-37         | EM Configuration Providing 4 MB Using 4 Banks                     |       |

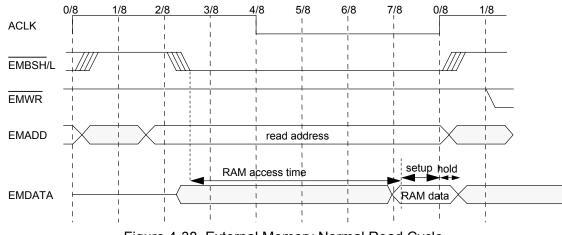

| 4-38         | External Memory Normal Read Cycle                                 | 4-26  |

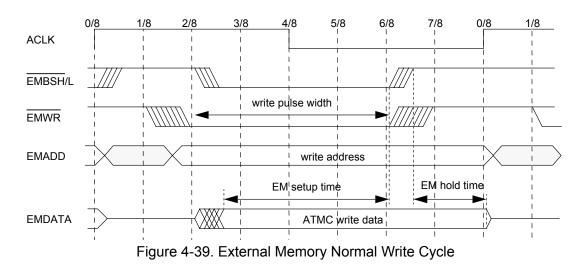

| 4-39         | External Memory Normal Write Cycle                                | 4-27  |

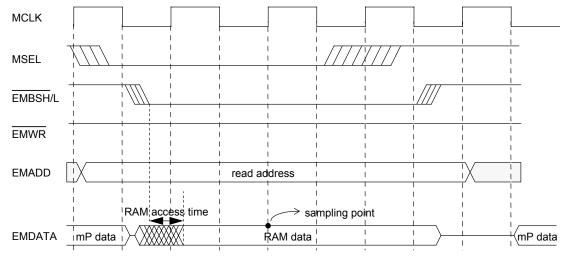

| 4-40         | External Memory Maintenance Read Access                           |       |

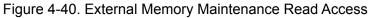

| 4-41         | External Memory Maintenance Write Access                          |       |

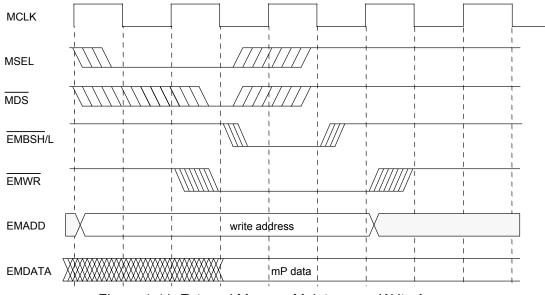

| 4-42         | External Memory Maintenance Read/Clear Access                     |       |

| 4-43         | Example Implementation of External Address Compression            |       |

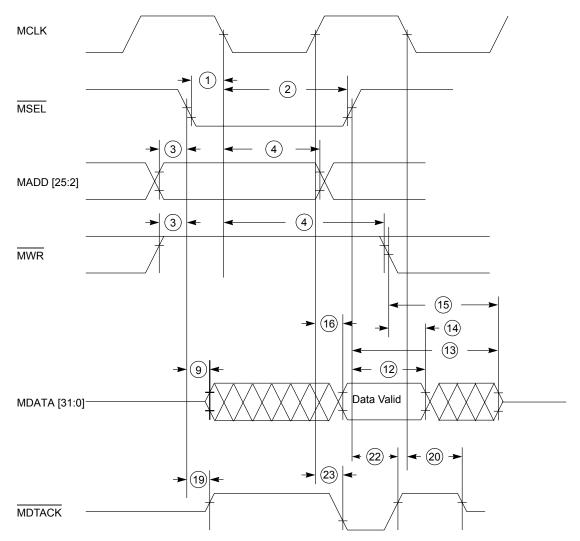

| 4-44         | MC92501 Register Read Timing with DTACK                           |       |

| 4-45         | MC92501 Register Read Timing without DTACK                        |       |

| 4-46         | Cell Extraction Register Read Timing                              |       |

| 4-47         | Maintenance Read Access Timing                                    |       |

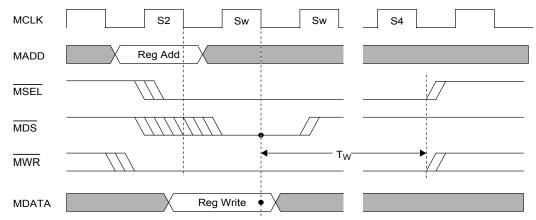

| 4-48         | MC92501 Register Write Timing with DTACK                          | 4-34  |

| 4-49         | MC92501 Register Write Timing without DTACK                       |       |

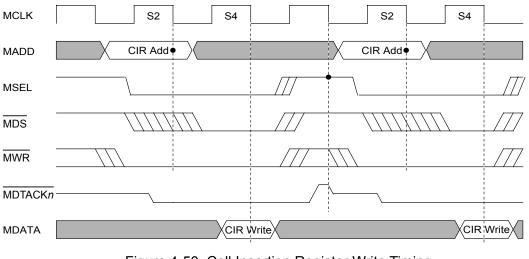

| 4-50         | Cell Insertion Register Write Timing                              |       |

| 4-50<br>4-51 | Cell Insertion Register Write Timing with Delayed Data Strobe     | 1-36  |

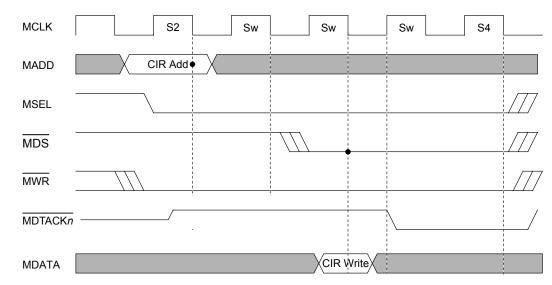

| 4-52         | Maintenance Write Access Timing                                   | 4-37  |

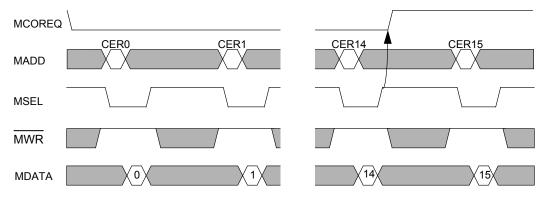

| 4-53         | DMA Device Support on Cell Extraction Register                    |       |

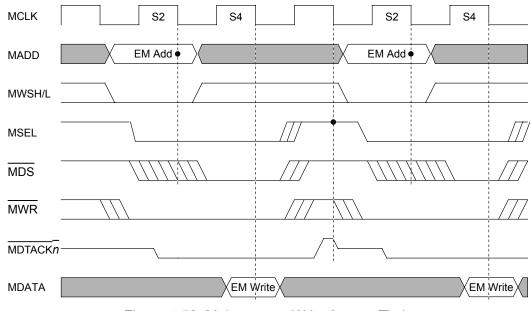

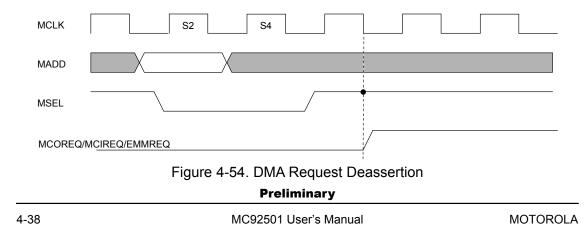

| 4-54         | DMA Device Support on Cen Extraction Register                     |       |

| 4-54<br>4-55 | DMA Device Support on Cell Insertion Register                     |       |

| 4-33<br>5-1  | Ingress Data Path                                                 |       |

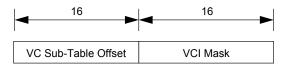

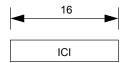

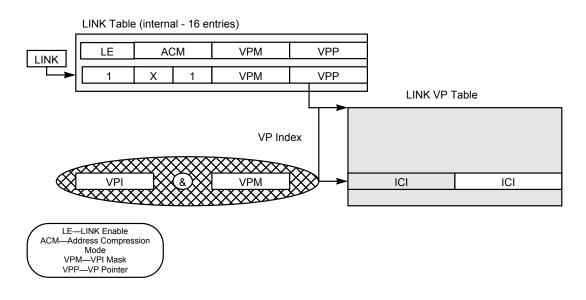

| 5-1<br>5-2   | Address Compression Tables                                        |       |

| 5-2<br>5-3   | Link Table Logical Structure                                      |       |

| 5-3<br>5-4   |                                                                   |       |

| 5-4<br>5-5   | Full Table Lookup Scheme                                          |       |

|              | VP Index Derivation                                               |       |

| 5-6          | VP Table Record Logical Structure for VP Switching                |       |

| 5-7          | VP Table Record Logical Structure as Pointer to VC Table          |       |

| 5-8          | VC Table Record Logical Structure                                 |       |

| 5-9          | Address Compression with VC Lookup Disable                        |       |

| 5-10         | External Address Compression Events                               |       |

| 5-11         | External Address Compression Response Logical Structure           |       |

| 5-12         | Data Structure with No HEC Octet (ISHF=00)                        |       |

| 5-13         | Data Structure with HEC = 0 (ISHF = 10)                           |       |

| 5-14         | Data Structure with HEC Octet from Switch Parameters 2            | 5-16  |

xiv

| 5-15         | Data Structure with HEC Octet from Switch Parameters 1        |      |

|--------------|---------------------------------------------------------------|------|

| 5-16         | Data Structure with HEC Octet from Switch Parameters 0        |      |

| 5-17         | Egress Data Path                                              |      |

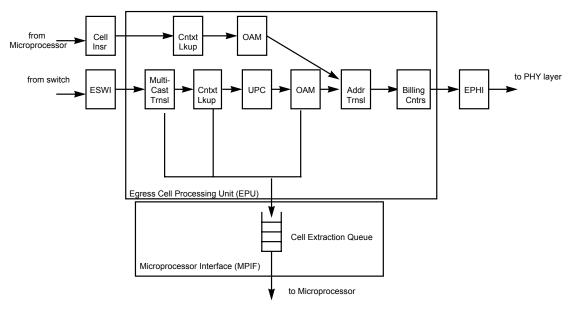

| 5-18         | ECI Extraction from Switch Cell Data Structure                | 5-20 |

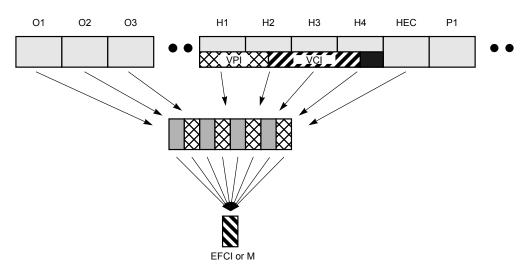

| 5-19         | EFCI and M Extraction from Switch Cell Data Structure         | 5-21 |

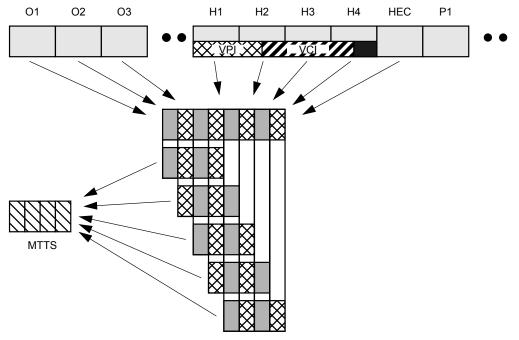

| 5-20         | MTTS Extraction from Switch Cell Data Structure               | 5-21 |

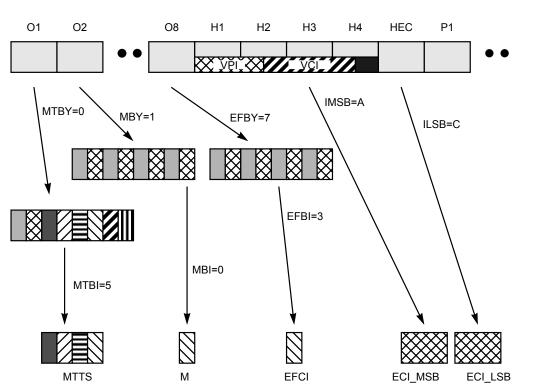

| 5-21         | Overhead Extraction Example                                   | 5-22 |

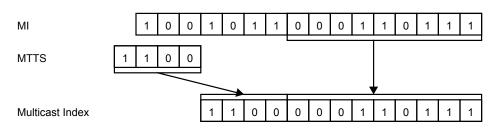

| 5-22         | Sectionized Multicast Derivation Example                      |      |

| 5-23         | Multicast Translation                                         |      |

| 6-1          | PPD Algorithm Example                                         |      |

| 6-2          | EPD Algorithm Example                                         |      |

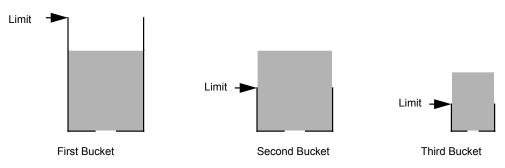

| 6-3          | Three Bucket Example                                          |      |

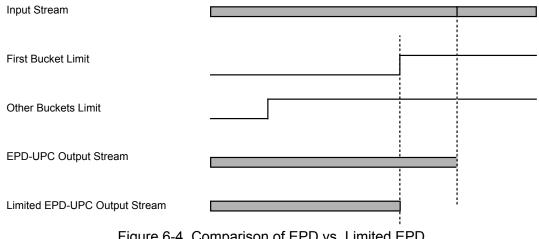

| 6-4          | Comparison of EPD vs. Limited EPD                             |      |

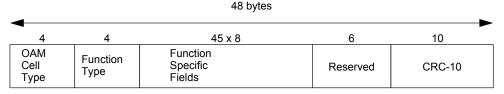

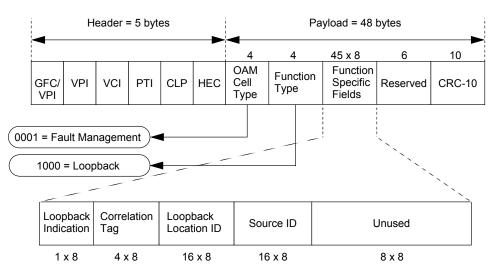

| 6-5          | OAM Cell Payload Structure                                    | 6-8  |

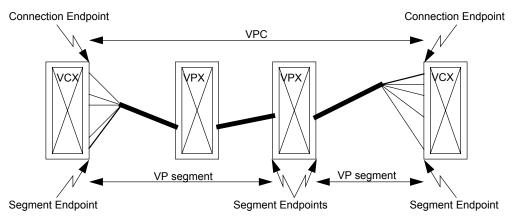

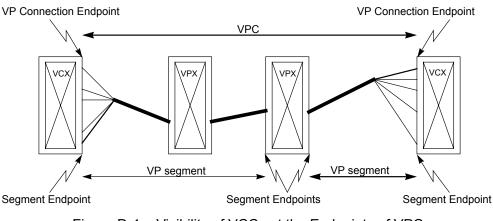

| 6-6          | Visibility of VCCs at the Endpoints of VPCs                   |      |

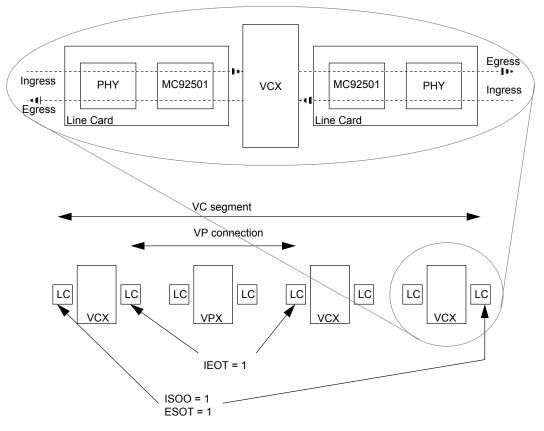

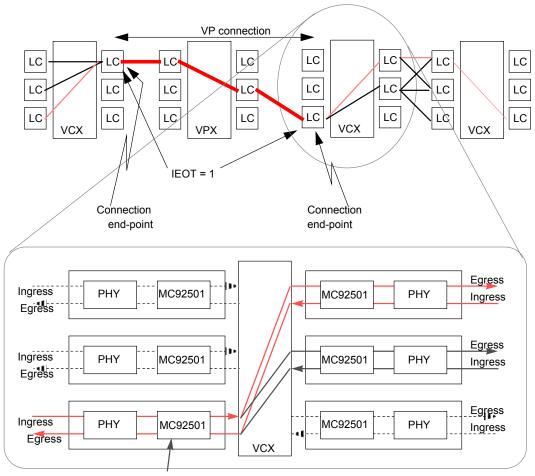

| 6-7          | Example of VP Connection / VC Segment                         |      |

| 6-8          | AIS/RDI Fault Management Cell                                 |      |

|              |                                                               |      |

| 6-9          | F4 AIS/RDI Flows for a VPC Internal to the Network            |      |

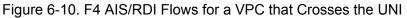

| 6-10         | F4 AIS/RDI Flows for a VPC that Crosses the UNI               |      |

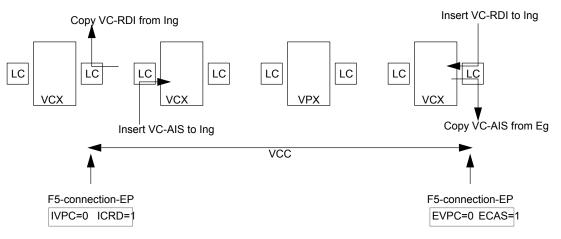

| 6-11         | F5 AIS/RDI Flows                                              | 6-15 |

| 6-12         | CC Fault Management Cell                                      | 6-16 |

| 6-13         | OAM Loopback Cell                                             | 6-18 |

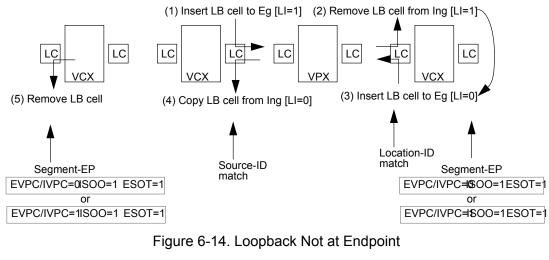

| 6-14         | Loopback Not at Endpoint                                      | 6-19 |

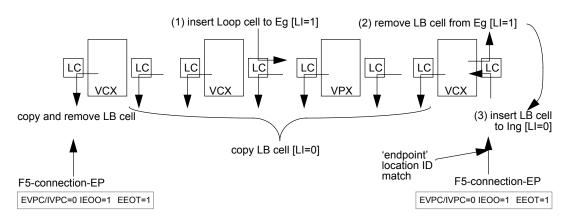

| 6-15         | Loopback at Endpoint of VCC                                   |      |

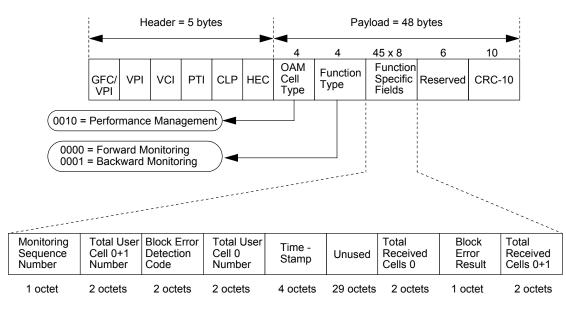

| 6-16         | Performance Management Cell                                   |      |

| 6-17         | Performance Management Block Test on a VPC Segment            |      |

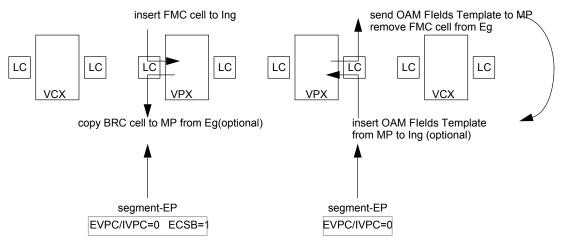

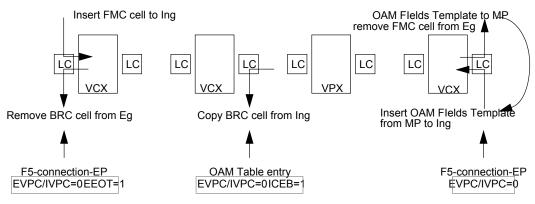

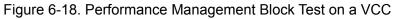

| 6-18         | Performance Management Block Test on a VCC                    | 6-25 |

| 6-19         | F4 PM Block Test on a VPC Internal to the Network             | 6-26 |

| 6-20         | F4 PM Block Test on a VPC that Crosses the UNI                | 6-26 |

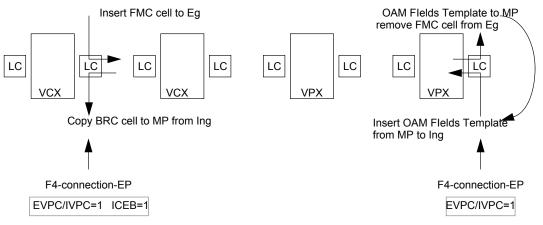

| 6-21         | F4 OAM Flow for a VPC Internal to the Network                 | 6-27 |

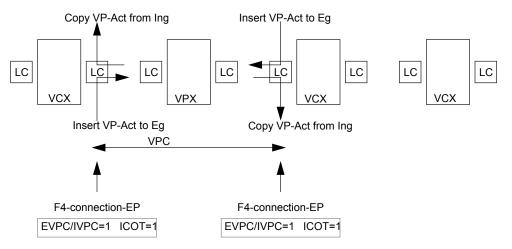

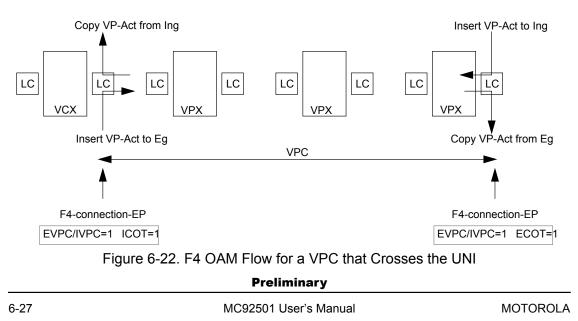

| 6-22         | F4 OAM Flow for a VPC that Crosses the UNI                    | 6-27 |

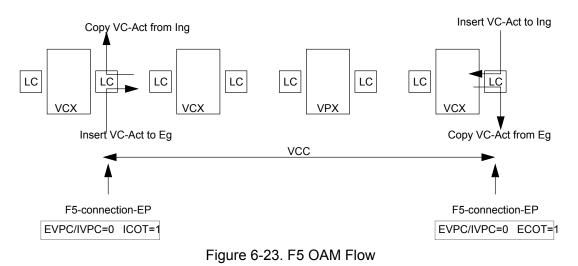

| 6-23         | F5 OAM Flow                                                   |      |

| 6-24         | RM Cell Fields                                                |      |

| 6-25         | MC92501 to Switch Connections                                 |      |

| 6-26         | MC92501 Marking Scheme                                        |      |

| 6-27         | Ingress-Flow-Status Logic                                     |      |

| 6-28         | Egress-Flow-Status Logic                                      |      |

| 6-29         | Ingress Direction Actions                                     |      |

| 6-30         | Egress Direction Actions                                      |      |

| 6-31         | Marking CI Bits of Ingress FRM Cells                          |      |

| 6-32         | Marking a BRM Cell NI Field                                   |      |

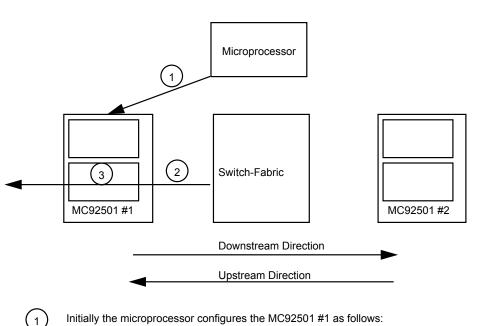

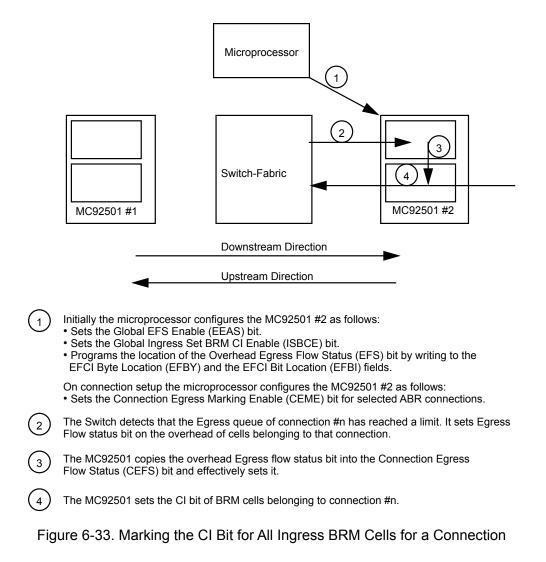

| 6-33         | Marking the CI Bit for All Ingress BRM Cells for a Connection |      |

| 6-33<br>6-34 |                                                               |      |

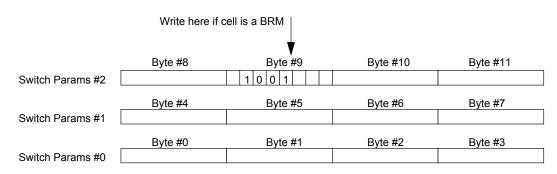

|              | Ingress Switch Parameter Example                              |      |

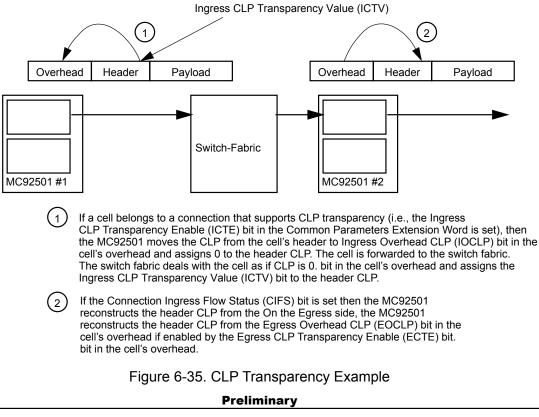

| 6-35         | CLP Transparency Example                                      |      |

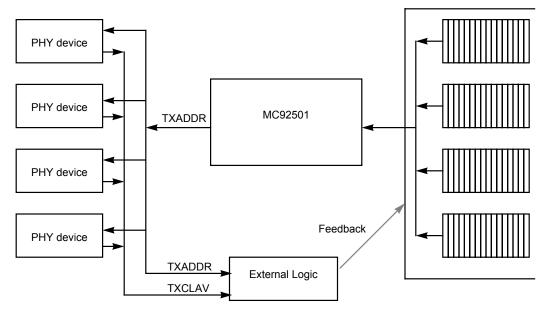

| 6-36         | Multiple PHY Configuration on the Egress Side of the Switch   |      |

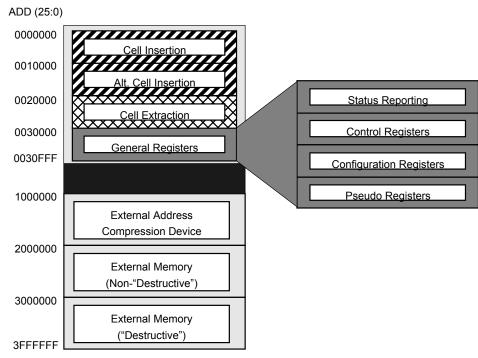

| 7-1          | Memory Map                                                    | 7-2  |

#### Preliminary

| MOTOR | OLA |

|-------|-----|

|-------|-----|

MC92501 User's Manual

xv

List of Figures

| 7-2  | Cell Insertion Register Addresses                              | 7-3  |

|------|----------------------------------------------------------------|------|

| 7-3  | Cell Extraction Register Addresses                             |      |

| 7-4  | Interrupt Register (IR) Fields                                 |      |

| 7-5  | Interrupt Mask Register (IMR) Fields                           | 7-10 |

| 7-6  | Last Cell Processing Time Register (LCPTR) Fields              |      |

| 7-7  | ATMC CFB Revision Register (ARR) Fields                        |      |

| 7-8  | Revision Register (RR) Fields                                  |      |

| 7-9  | Maintenance Control Register (MACTLR)                          | 7-13 |

| 7-10 | Cell Extraction Queue Filtering Register 0 (CEQFR0) Fields     | 7-14 |

| 7-11 | Cell Extraction Queue Filtering Register 1 (CEQFR1) Fields     |      |

| 7-12 | Cell Extraction Queue Priority Register 0 (CEQPR0) Fields      |      |

| 7-13 | Cell Extraction Queue Priority Register 1 (CEQPR1) Fields      |      |

| 7-14 | Ingress Insertion Leaky Bucket Register (IILB) Fields          |      |

| 7-15 | Ingress Insertion Bucket Fill Register (IIBF) Fields           |      |

| 7-16 | Egress Insertion Leaky Bucket Register (EILB) Fields           |      |

| 7-17 | Egress Insertion Bucket Fill Register (EIBF) Fields            |      |

| 7-18 | Internal Scan Register (ISCR) Fields                           | 7-17 |

| 7-19 | Ingress Link Register (ILNKn) Fields                           | 7-18 |

| 7-20 | Egress Link Enable Register (ELER) Fields                      | 7-19 |

| 7-21 | Ingress Billing Counters Table Pointer (IBCTP) Fields          |      |

| 7-22 | Egress Billing Counters Table Pointer (EBCTP) Fields           |      |

| 7-23 | Policing Counters Table Pointer (PCTP) Fields                  |      |

| 7-24 | Cell Time Register (CLTM) Fields                               |      |

| 7-25 | Ingress Processing Control Register (IPLR) Fields              |      |

| 7-26 | Egress Processing Control Register (EPLR) Fields               |      |

| 7-27 | Indirect External Memory Access Address Register (IAAR) Fields |      |

| 7-28 | Microprocessor Configuration Register (MPCONR) Fields          |      |

| 7-29 | Maintenance Configuration Register (MACONR) Fields             |      |

| 7-30 | Ingress PHY Configuration Register (IPHCR) Fields              |      |

| 7-31 | Egress PHY Configuration Register (EPHCR) Fields               |      |

| 7-32 | Ingress Switch Interface Configuration Register (ISWCR)        |      |

| 7-33 | Egress Switch Interface Configuration Register (ESWCR) Fields  |      |

| 7-34 | Egress Switch Overhead Information Register (ESOIR0) Fields    |      |

| 7-35 | Egress Switch Overhead Information Register 1 (ESOIR1) Fields  |      |

| 7-36 | UNI Register (UNIR) Fields                                     |      |

| 7-37 | Ingress Processing Configuration Register (IPCR)               |      |

| 7-38 | Egress Processing Configuration Register (EPCR) Fields         |      |

| 7-39 | Egress Multicast Configuration Register (EMCR) Fields          |      |

| 7-40 | ATMC CFB Configuration Register (ACR) Fields                   |      |

| 7-41 | General Configuration Register (GCR) Fields                    |      |

| 7-42 | Context Parameters Table Pointer (CPTP) Fields                 |      |

| 7-43 | OAM Table Pointer (OTP) Register Fields                        |      |

| 7-44 | Dump Vector Table Pointer (DVTP) Register Fields               |      |

| 7-45 | VC Table Pointer (VCTP) Register Fields                        |      |

| 7-46 | Multicast Translation Table Pointer (MTTP) Register Fields     |      |

| 7-47 | Flags Table Pointer (FTP) Register Fields                      |      |

xvi

| 7 40          |                                                                                                                                           |        |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 7-48          | Egress Link Counters Table Pointer (ELCTP) Register Fields                                                                                |        |

| 7-49          | Ingress Link Counters Table Pointer (ILCTP) Register Fields                                                                               |        |

| 7-50          | Context Parameters Extension Table Pointer (CPETP) Register Fields                                                                        |        |

| 7-51          | Node ID Register 0 (ND0) Fields                                                                                                           |        |

| 7-52          | Node ID Register 1 (ND1) Fields                                                                                                           |        |

| 7-53          | Node ID Register 2 (ND2) Fields                                                                                                           |        |

| 7-54          | Node ID Register 3 (ND3) Fields                                                                                                           |        |

| 7-55          | Ingress VCI Copy Register (IVCR) Fields                                                                                                   |        |

| 7-56          | Egress VCI Copy Register (EVCR) Fields                                                                                                    |        |

| 7-57          | Ingress VCI Remove Register (IVRR) Fields                                                                                                 |        |

| 7-58          | Egress VCI Remove Register (EVRR) Fields                                                                                                  |        |

| 7-59          | Performance Monitoring Exclusive Register (PMER) Fields                                                                                   | . 7-50 |

| 7-60          | External Memory Timing Configuration Register (EMTCR) Fields                                                                              | . 7-50 |

| 7 <b>-</b> 61 | External Memory Interface Configuration Register (EMICR) Fields                                                                           | . 7-52 |

| 7-62          | RM Overlay Register (RMOR) Fields                                                                                                         | . 7-53 |

| 7-63          | CLP Transparency Overlay Register (CTOR) Fields                                                                                           |        |

| 7-64          | Egress Overhead Manipulation Register (EGOMR) Fields                                                                                      |        |

| 7-65          | External Memory Partitioning                                                                                                              |        |

| 7-66          | Context Parameters Table Record (Full Configuration)                                                                                      | . 7-64 |

| 7-67          | Context Parameters Table Record (ATC=01, SPC=01)                                                                                          |        |

| 7-68          | Egress Translation Address Long Word                                                                                                      |        |

| 7-69          | Ingress Address Translation Long Word                                                                                                     |        |

| 7-70          | Common Parameters Long Word Fields (PMAC = 0)                                                                                             |        |

| 7-71          | Common Parameters Long Word Fields (PMAC = 1)                                                                                             |        |

| 7-72          | Egress Parameters Long Word Fields                                                                                                        | 7-68   |

| 7-73          | Ingress Parameters Long Word Fields                                                                                                       |        |

| 7-74          | Ingress Counters (Full Configuration – IBCC = 001)                                                                                        |        |

| 7-75          | Ingress Counters (Single OAM Configuration – IBCC = $011$ )                                                                               |        |

| 7-76          | Ingress Counters (Single OAM Configuration – $IBCC = 010$ )                                                                               |        |

| 7-77          | Ingress Counters (No CLP Distinction Configuration – IBCC = $100$ )                                                                       |        |

| 7-78          | Ingress Counters (No OAM Distinction Configuration – IBCC = $100$ )                                                                       |        |

| 7-79          | Ingress Counters (No O/NV Distinction Configuration $-$ IDCC $=$ 101)<br>Ingress Counters (Single Counter Configuration $-$ IBCC $=$ 110) |        |

| 7-80          | Egress Counters (Shigh Counter Configuration – IDCC – 110)                                                                                |        |

| 7-81          | Egress Counters (Full Configuration – EBCC = 001)                                                                                         |        |

| 7-82          | Egress Counters (Single OAM Configuration – EBCC = 011)                                                                                   |        |

| 7-82<br>7-83  | Egress Counters (Single OAW Configuration – EBCC – 010)<br>Egress Counters (No CLP Distinction Configuration – EBCC = 100)                | 7 75   |

|               |                                                                                                                                           |        |

| 7-84<br>7-85  | Egress Counters (No OAM Distinction Configuration – EBCC = $101$ )                                                                        |        |

| 7-85          | Egress Counters (Single Counter Configuration – EBCC = $110$ )                                                                            |        |

| 7-86          | Policing Counters (Full Configuration $-PCC = 001$ )                                                                                      |        |

| 7-87          | Policing Counters (Full Configuration – PCC = 010)                                                                                        |        |

| 7-88          | Policing Counters (No CLP Distinction Configuration – PCC = $011$ )                                                                       |        |

| 7-89          | Policing Counters (Only Tag Counter Configuration – PCC = 100)                                                                            |        |

| 7-90          | Policing Counters (Only Discard Counter Configuration – PCC=101)                                                                          |        |

| 7-91          | Flags Table Fields                                                                                                                        |        |

| 7-92          | Arrangement of 16-bit Records in External Memory                                                                                          |        |

| 7-93          | VP Table Structure                                                                                                                        | . 7-80 |

#### Preliminary

```

MOTOROLA

```

MC92501 User's Manual

xvii

List of Figures

| 7-94           | VD Table Decord Fields with VC Switching                             | 7 90   |

|----------------|----------------------------------------------------------------------|--------|

| 7-94<br>7-95   | VP Table Record Fields with VC Switching                             |        |

|                | VP Table Record Fields with VP Switching                             |        |

| 7-96           | VC Record Structure                                                  |        |

| 7-97           | Multicast Translation Table Record Structure                         |        |

| 7-98           | Bucket Entries                                                       |        |

| 7-99           | Bucket Information Word 1, 3, 5, and 7 Fields                        |        |

| 7-100          | Bucket Information Word 2, 4, 6, and 8 Fields                        |        |

| 7-101          | OAM Table Record                                                     |        |

| 7-102          | Control Bit Fields                                                   |        |

| 7-103          | Dump Vector Table Egress Long Word Fields                            |        |

| 7-104          | Dump Vector Table Ingress Long Word Fields                           |        |

| 7-105          | Ingress Link Counters                                                |        |

| 7-106          | Ingress Link Counters                                                |        |

| 7-107          | Parameter Extension Word Fields (PMAC = 1 and UPCF = 0)              |        |

| 7-108          | Parameter Extension Word Fields (PMAC = 1 and UPCF = 1)              | . 7-88 |

| 7-109          | Parameter Extension Word Fields (PMAC = 0 and UPCF = 0)              | . 7-88 |

| 7-110          | Parameter Extension Word Fields (PMAC = 0 and UPCF = 1)              | . 7-89 |

| 7-111          | Inserted Cell Structure                                              | . 7-91 |

| 7-112          | Cell Descriptor Format I                                             | . 7-91 |

| 7-113          | Cell Descriptor Format II                                            | . 7-92 |

| 7-114          | Cell Descriptor Format III                                           | . 7-92 |

| 7-115          | Cell Descriptor Format IV                                            |        |

| 7-116          | Cell Descriptor Format V                                             |        |

| 7-117          | Connection Descriptor Structure                                      |        |

| 7-118          | Inserted Cell ATM Cell Header Fields (UNI)                           |        |

| 7-119          | Inserted Cell ATM Cell Header Fields (NNI)                           |        |

| 7-120          | Inserted BRC Fields Template                                         |        |

| 7-121          | Extracted Cell Structure                                             |        |

| 7-122          | User/OAM Cell Indication Fields                                      |        |

| 7-123          | Egress Multicast Translation Failure Cell Indication Fields          |        |

| 7-124          | Erro Cell Indication Fields                                          |        |

| 7-125          | Short Report Indication Fields                                       |        |

| 7-126          | OAM Fields Template Fields                                           |        |

| 7-127          | Connection Indication Fields                                         |        |

| 7-128          | Egress Multicast Translation Failure Connection Overhead Information |        |

| 7-129          | Extracted Cell ATM Cell Header (UNI)                                 |        |

| 7-12)          | Extracted Cell ATM Cell Header (NNI)                                 |        |

| 7-130<br>7-131 | Extracted BRC Fields Template                                        |        |

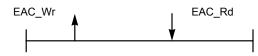

| 7-131<br>7-132 | Received Cell Address Structure                                      |        |

| 7-132          |                                                                      |        |

| 7-133<br>8-1   | User Response to EAC Structure                                       |        |

|                | JTAG Logic Block Diagram                                             |        |

| 8-2            | TAP Controller State Diagram                                         |        |

| 9-1            | Functional Signal Groups                                             |        |

| 9-2            | Clock Timing Diagrams                                                |        |

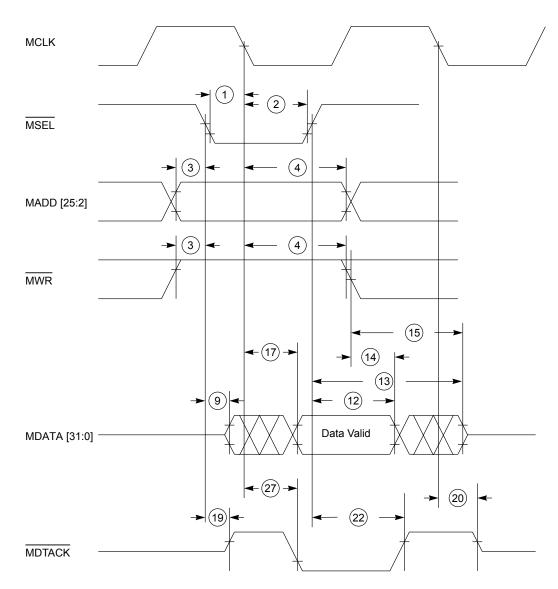

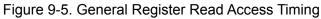

| 9-3            | Cell Extraction Register Read Access Timing                          |        |

| 9-4            | Maintenance Read Access Timing                                       | . 9-17 |

#### Preliminary

xviii

MC92501 User's Manual

List of Figures

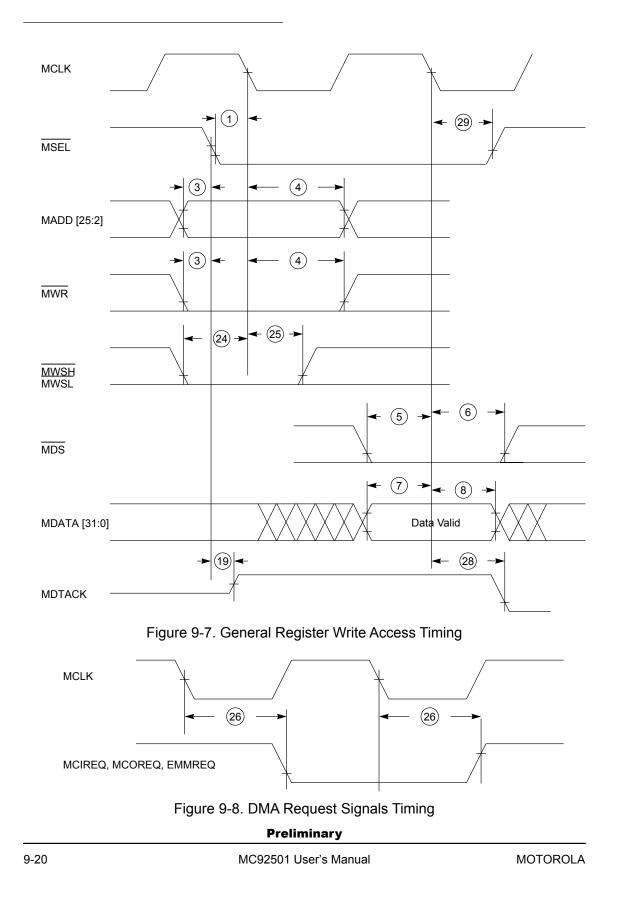

| 9-5 General Register Read Access Timing                                    |               |

|----------------------------------------------------------------------------|---------------|

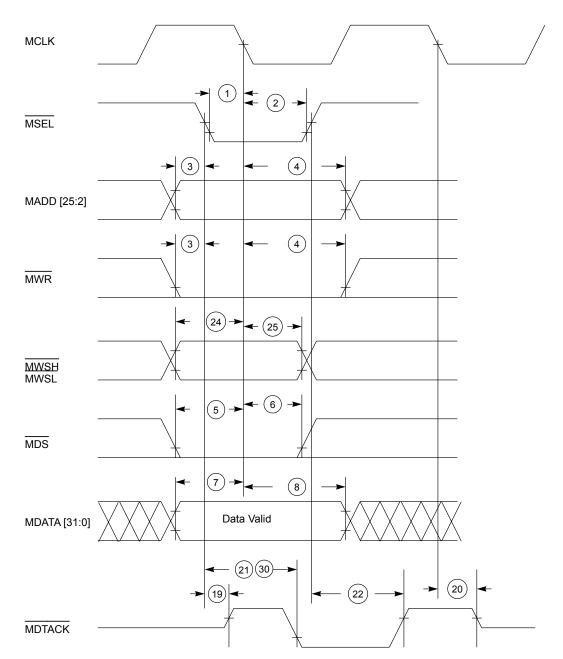

| 9-6 Cell Insertion Register Write Access/Maintenance Write Access Timing . |               |

| 9-7 General Register Write Access Timing                                   | 9-20          |

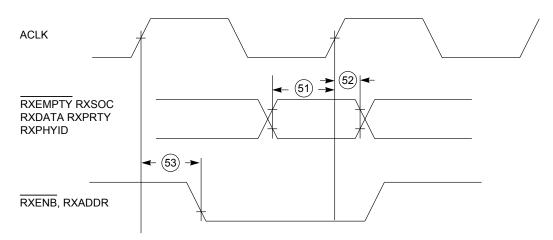

| 9-8 DMA Request Signals Timing                                             | 9-20          |

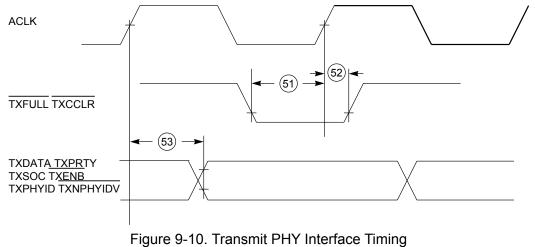

| 9-9 Receive PHY Interface Timing                                           | 9-21          |

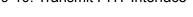

| 9-10 Transmit PHY Interface Timing                                         | 9-21          |

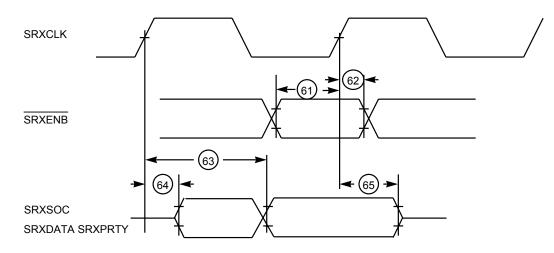

| 9-11 Ingress Switch Interface Timing                                       | 9-22          |

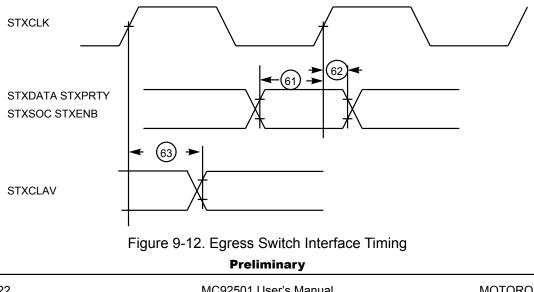

| 9-12 Egress Switch Interface Timing                                        |               |

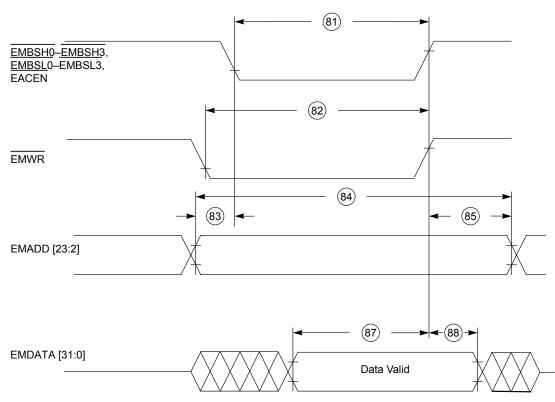

| 9-13 External Memory Write Access Timing                                   |               |

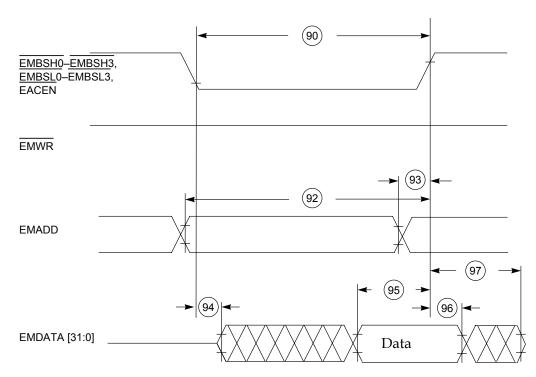

| 9-14 External Memory Read Access Timing                                    |               |

| 9-15 256-pin OMPAC Pin Diagram                                             |               |

| 9-16 256-pin OMPAC PBGA (Preliminary Drawing)                              |               |

| A-1 UPC Data Structures                                                    |               |

| A-2 Detailed UPC Flowchart                                                 | . A-4         |

| A-3 UPC Control and Data Flowchart                                         |               |

| A-4 UPC Enforce Phase                                                      | . A-6         |

| A-5 UPC Update Phase                                                       | . A-7         |

| A-6 Encoding of Bucket Parameters for 64 Kbps Circuit Emulation            |               |

| A-7 Encoding of Bucket 1 Parameters                                        |               |

| A-8 Encoding of Bucket 2 Parameters                                        |               |

| D-1 Visibility of VCCs at the Endpoints of VPCs                            |               |

| D-2 VP/VC Boundary Point                                                   |               |

| D-3 F4- and F5-Level Block Tests at the Same Switch                        | .D <b>-</b> 4 |

| E-1 Motorola's ATM Line Card Architecture                                  | . E-1         |

| E-2 Motorola's ATM Line Card Architecture for Multiple PHY Devices         | . E-3         |

| E-3 Motorola's DSLAM Solution (Ingress Upstream/Égress Downstream)         |               |

| E-4 Motorola's DSLAM Solution (Ingress Downstream/Egress Upstream)         |               |

List of Figures

Preliminary MC92501 User's Manual

# Freescale Semiconductor, Inc.

# **List of Tables**

| 3-1  | Indirect Access fields                                                 |

|------|------------------------------------------------------------------------|

| 4-1  | EM Address Bits Used for Bank Select (2 Banks)                         |

| 4-2  | EM Address Bits Used for Bank Select (4 Banks)                         |

| 4-3  | Active EM Banks Selected by the MSBs of the Active Address             |

| 5-1  | Pre-assigned Header Values at the UNI                                  |

| 5-2  | Pre-assigned Header Values at the NNI                                  |

| 5-3  | Address Compression Options                                            |

| 5-4  | VP Table Address Calculations (VC Lookup Enabled)                      |

| 5-5  | VC Table Address Calculations                                          |

| 5-6  | VP Table Address Calculations (VC Lookup Enabled)                      |

| 5-7  | Number of MI Bits Used for Sectioned Multicast Translation Table 5-24  |

| 6-1  | Pre-assigned Header Values at the UNI                                  |

| 6-2  | Pre-assigned Header Values at the NNI                                  |

| 6-3  | OAM Types Explicitly Identified by the MC92501                         |

| 6-4  | General OAM Bits                                                       |

| 6-5  | AIS Bits                                                               |

| 6-6  | RDI Bits                                                               |

| 6-7  | Continuity Check Bits                                                  |

| 6-8  | Processing of OAM Loopback Cells                                       |

| 6-9  | Performance Monitoring Bits                                            |

| 6-10 | OAM Table Fields                                                       |

| 7-1  | General Register List                                                  |

| 7-2  | Values of ATMC CFB Revision Fields                                     |

| 7-3  | Values of MC92501 Revision Fields                                      |

| 7-4  | Microprocessor Control Register (MPCTLR) Fields                        |

| 7-5  | Parity Checking at Ingress PHY Interface                               |

| 7-6  | Cell Generation at Egress PHY Interface                                |

| 7-7  | Destination Link Number                                                |

| 7-8  | Parity Checking at Egress Switch Interface                             |

| 7-9  | External Memory Timing Parameters                                      |

| 7-10 | Address Space for Accesses that use the External Memory Interface 7-56 |

| 7-11 | Number of Long Words per Connection in Each Table                      |

| 7-12 | VP Table Size (per link)                                               |

| 7-13 | VC Sub-Table Size (per VPI)                                            |

| 7-14 | Multicast Translation Table Size (per link)                            |

| 7-15 | Addressing External Memory Records                                     |

| 7-16 | Cell Name Coding                                                       |

| 7-17 | Reason Coding         7-105                                            |

| 8-1  | Device Identification Register ID Codes                                |

| 8-2  | Instruction Decoding                                                   |

```

MOTOROLA

```

MC92501 User's Manual

xxi

List of Tables

| 8-3  | Boundary Scan Bit Definition                                | 8-6  |

|------|-------------------------------------------------------------|------|

| 9-1  | Host Interface Fields                                       |      |

| 9-2  | Absolute Maximum Ratings                                    |      |

| 9-3  | Recommended Operating Conditions to Guarantee Functionality |      |

| 9-4  | DC Electrical Characteristics                               |      |

| 9-5  | Clock Timing                                                |      |

| 9-6  | Microprocessor Interface Timings                            |      |

| 9-7  | PHY Interface Timings                                       |      |

| 9-8  | Switch Interface Timing                                     |      |

| 9-9  | Write Cycle Timing                                          |      |

| 9-10 | Read Cycle Timing                                           |      |

| 9-11 | Power Pin Assignment                                        |      |

| 9-12 | MC92501 Functional Pin Assignment                           |      |

| A-1  | Enforcer SCOPE Field                                        | A-6  |

| A-2  | Cell Arrival Period and Bucket Contents Encoding            | A-8  |

| A-3  | Bucket Limit Encoding                                       | A-9  |

| A-4  | Bucket Parameters for CBR Connections                       |      |

| A-5  | Bucket Parameters for VBR Connections                       | A-12 |

| B-1  | Maintenance Slot Parameters                                 | B-3  |

Preliminary MC92501 User's Manual

# 1

# Introduction

#### 1.1 ATM Networks

#### The increa

sing demand for broadband data transmission has led to the development of international protocols issued by the American National Standards Institute (ANSI), International Telecommunications Union-Telecommunications (ITU-T), and the European Telecommunication Standards Institute (ETSI). These standards and the recommendations issued by the ATM Forum, Bellcore, UTOPIA, and others are provided to ensure consistent, reliable, and uninterrupted data transmission worldwide.

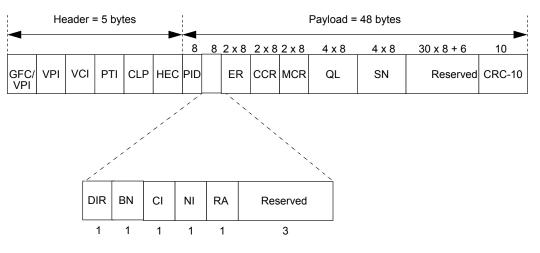

The basic unit of transfer defined by these protocols is called a cell. Each cell is composed of 53 bytes that includes a 5-byte header and 48 bytes of data. The header portion of the cell includes several sections of identifying information used by the cell processor to route and transmit the cell, including the type of data being transmitted and the origin and destination. As with many other means of electronic transfer, the cells of information must be combined with other cells (for efficiency of transfer) and transmitted over a long distance. During transfer, the cells are evaluated and, if required, separated from the transmission stream and rerouted, similar to commuters who share transportation routes during parts of their journeys and then transfer to alternate routes to complete their journeys.

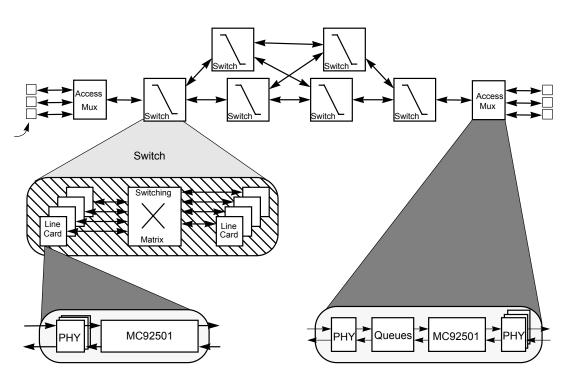

Actual data transmission is performed asynchronously because the distance over which the transfer occurs prevent the use of the same clock signal at both ends and even within the transfer network. Therefore, the transfer method has been defined as the Asynchronous Transfer Mode (ATM). Each network consists of user end stations that transmit and receive the 53-byte data cells using virtual connections. The virtual connections are implemented through physical links and switching elements that interconnect them. The specific combination of physical links that implements a virtual connection is chosen when the connection is established. For a given physical link, each connection is assigned a unique connection identifier. The connection identifier is placed in the header of each cell by the transmitting equipment and is used by the receiving equipment to route the cell to the next physical link on the connection path. All cells belonging to a specific virtual connection follow the identical path from the transmitting end station through the switching elements to the receiving end station. **Figure 1-1** shows a typical ATM network.

Preliminary

MOTOROLA

MC92501 User's Manual

1-1

Figure 1-1. Typical ATM Network Structure