## Freescale Semiconductor

User Guide

# **S12XE IPLL Calculator**

# Suitable to use with the S12XE, XF, XS, and S12P, HY, HA families

by: Michael Galda Freescale Roznov CSC (TIC Team)

## 1 Introduction

The S12XE (S12XF, S12XS, S12P, S12HY) family of MCU's include an internal phase-locked loop (IPLL) frequency multiplier with an internal filter as a part of the S12XECRG (or S12CPMU) module. The purpose of the PLL is to generate an internal timebase from the external resonator signal or from the internal-reference clock (S12P and S12HY only). The IPLL allows the internal timebase (usually called the bus clock) to be generated at higher or lower frequency than the oscillator signal. The usage of a low-frequency resonator facilitates lower power consumption in low-power modes (pseudo stop mode). The usage of a cheaper low-frequency resonator with PLL to increase the internal MCU bus clock instead of usage of high-frequency external (canned) oscillator, may reduce the final costs of design. The PLL adds more flexibility in order to generate a wide range of internal MCU bus clock frequencies from the fixed external resonator frequency. The user can easily switch between the bus frequencies, depending on application performance or power consumption requirements.

#### Contents

| 1 | Introduction                          |

|---|---------------------------------------|

| 2 | IPLL Register Setting Description     |

|   | 2.1 PLL Setting Equations             |

| 3 | The IPLL Calculator Application       |

|   | 3.1 Data Entry 5                      |

| 4 | PLL Software Initialization Examples7 |

|   | 4.1 S12XE PLL Init Examples           |

|   | 4.2 S12P PLL Init Examples 9          |

| 5 | References                            |

|   | 6 Glossary                            |

#### **IPLL Register Setting Description**

The IPLL allows to set an appropriate internal MCU bus clock, in order to achieve correct timing for the internal MCU modules (like SCI, timer modules, and so on), even if the external resonator frequency is not suitable for proper timing. The IPLL (unlike the PLL module on S12(X)) doesn't require any external filter components.

#### NOTE

Sections referring to S12P are generally valid also for the S12HY family, due to module compatibility.

## 2 IPLL Register Setting Description

The SYNR, REFDV, and POSTDIV registers are responsible for the PLL frequency settings.

The following rules, equations, and frequency limitations are considered by the IPLL calculator utility to achieve maximum stability and shortest PLL locking time.

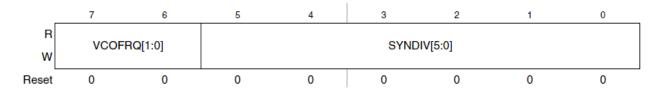

Figure 1. The S12XE(XS) SYNR / S12P CPMUSYNR Register

The VCOFRQ[1:0] bits are used to configure the VCO gain for optimal stability and lock time. For correct IPLL operation, the VCOFRQ[1:0] bits have to be selected according to the actual target VCOCLK frequency, as shown in the following table:

| VCOCLK Frequency Ranges  | VCOFRQ[1:0] |

|--------------------------|-------------|

| 32 MHz <= fvco <= 48 MHz | 00          |

| 48 MHz < fvco <= 80 MHz  | 01          |

| Reserved                 | 10          |

| 80 MHz < fvco <=120 MHz  | 11          |

Table 1. VCO Frequency Selection

Setting the VCOFRQ[1:0] bits wrongly can result in a non-functional IPLL (no locking and/or insufficient stability).

#### **IPLL Register Setting Description**

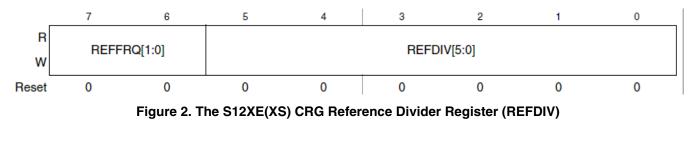

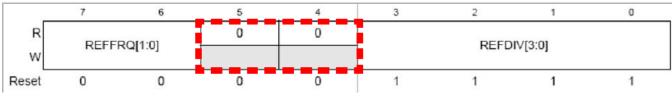

Figure 3. The S12P CPMU Reference Divider Register (CPMUREFDIV)

The REFFRQ[1:0] bits are used to configure the internal IPLL filter for optimal stability and lock time. For correct IPLL operation, the REFFRQ[1:0] bits have to be selected according to actual REFCLK frequency as shown in the following table:

#### **Table 2. Reference Clock Frequency Selection**

REFFRQ[1:0]

**REFCLK Frequency Ranges**

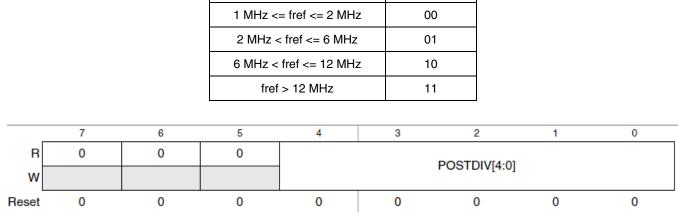

Figure 4. The S12XE(XS ) CRG / S12P CPMU Postdiv Register

NOTE

If POSTDIV = \$00, the  $f_{PLL}$  is identical to  $f_{VCO}$  (divide by one).

#### 2.1 PLL Setting Equations

#### 2.1.1 Equations Valid for S12XE

$$f_{VCO} = 2 \times f_{OSC} \times \frac{(SYNDIV+1)}{(REFDIV+1)}$$

Eqn. 1

$$f_{REF} = \frac{f_{OSC}}{(REFDIV+1)}$$

Ean. 2

$$f_{PLL} = \frac{f_{VCO}}{(2 \times POSTDIV)}$$

Eqn. 3

#### **IPLL Register Setting Description**

If PLL is selected (PLLSEL = 1):

$$f_{BUS} = \frac{f_{PLL}}{2}$$

Ean. 4

#### 2.1.2 Formulas Valid for S12P (S12HY)

If PLL is locked (LOCK = 1), then:

$$f_{PLL(CRG)} = \frac{f_{VCO}}{(1 + POSTDIV)}$$

Ean. 5

If PLL is not locked (LOCK = 0), then:

$$f_{PLL(CPMU)} = \frac{f_{VCO}}{4}$$

Eqn. 6

If the external oscillator is enabled (OSCE = 1) — PLL engaged external mode (PEE), then:

$$f_{REF} = \frac{f_{OSC}}{(REFDIV+1)}$$

Eqn. 7

If the external oscillator is disabled (OSCE = 0) — PLL Engaged Internal Mode (PEI), then:

$$f_{REF} = f_{IRC1M} = 1.000 MHz$$

Eqn. 8

If PLL is selected (PLLSEL = 1), then:

$$f_{BUS} = \frac{f_{PLL}}{2}$$

Eqn. 9

#### Table 3. Frequency Limitations for S12XE, XS, S12P, and S12HY

|                         | S12) | (E(XF) | S1   | 2XS  | S12P (S12HY) |      | _   | NOTE                   |

|-------------------------|------|--------|------|------|--------------|------|-----|------------------------|

| frequency               | min. | max.   | min. | max. | min.         | max. | -   |                        |

| f <sub>OSC (LCP)</sub>  | 4    | 16     | 4    | 16   | 4            | 16   | MHz | loop-controlled pierce |

| f <sub>OSC (FSP)</sub>  | 2    | 40     | 2    | 40   | -            | Ι    | MHz | full-swing pierce      |

| f <sub>OSC (ext.)</sub> | 2    | 50     | 2    | 50   | -            | _    | MHz | external square clock  |

| f <sub>BUS</sub>        | 0.5  | 50     | 0.5  | 40   | 0.5          | 32   | MHz |                        |

| f <sub>REF</sub>        | 1    | 40     | 1    | 40   | 1            | 40   | MHz |                        |

| f <sub>VCO</sub>        | 32   | 120    | 32   | 120  | 32           | 64   | MHz |                        |

NOTE: f<sub>OSC</sub> is limited to 4–16 MHz in LCP mode, 2–40 MHz in FSP mode, and 2–50 MHz for external clk. S12XE IPLL Calculator, Rev. 1

#### NOTE

The following rules help to achieve optimum stability and shortest lock time possible:

- Use the lowest possible  $f_{VCO} / f_{REF}$  ratio (SYNDIV value).

- Use the highest possible REFCLK frequency  $f_{REF}$ .

## **3** The IPLL Calculator Application

The S12XE IPLL filter calculator application has been written in free Borland Turbo C++ Explorer IDE, available at <u>http://www.turboexplorer.com/cpp</u>.

Calculator is run by executing the file S12XE\_IPLL\_Calc.exe on a PC, running a Windows<sup>TM</sup> XP OS. The application window shown in Figure 5 is presented.

| S12XE iPLL Calculator ver. 1.03               |         |             |         |          |

|-----------------------------------------------|---------|-------------|---------|----------|

| Select Frequency                              |         | Register s  | ettings |          |

| Oscillator 4,0000                             | MHz     | SYNR        | 0x03    | hex      |

| 🔽 Integer osc. only                           |         |             |         |          |

| Add New Osc                                   |         | REFDV       | 0x40    | hex      |

|                                               |         | DOCTOR      | 0.00    | <b>h</b> |

| Bus Freq. 16,00000                            | MHZ     | POSTDIV     | UXUU    | hex      |

| Select MCU Family                             | Statist | ics         |         |          |

| S12XE (XF, XS)                                |         | VCO Freq.   | 32,00   | MHz      |

| C 512P (512HY)                                |         |             |         |          |

| PRESSOR                                       | REF     | FCLK Freq.  | 4,00    | MHz      |

| 24                                            | Max     | < Lock time |         | 115      |

| 1                                             | maz     | CLOCK CITIE | 214,00  | us       |

| S12XE                                         |         | FDIV        | 0x03    | hex      |

|                                               |         |             |         |          |

|                                               |         |             |         |          |

| S12XE (XF, XS, P, HY) iPLL calculator ? About |         |             |         |          |

Figure 5. The S12XE IPLL Calculator

## 3.1 Data Entry

The following data is required in order to calculate the correct register values.

The IPLL Calculator Application

## 3.1.1 The MCU Family

Since there are some differences between S12XE, XS, S12P, and S12HY register settings and frequency limitations (See Section 2.1, "PLL Setting Equations"), the user has to select the appropriate MCU family by the radio button.

## 3.1.2 Oscillator Frequency

The oscillator frequency in units of MHz is picked from the Oscillator listbox. A PC mouse or keyboard input can be used. The basic set of the most often manufactured resonator frequencies in range 2–50 MHz are stored in the internal database. Only the integer frequency values are available in the list by default. Uncheck the checkbox window to show the complete list of all manufactured and user-defined frequencies from the internal database. The user can add a new oscillator frequency by clicking the Add New Osc button. The user-defined oscillator frequency will be stored in the myosc.cfg file in the application directory. The newly-added oscillator frequency will appear at the end of the Oscillator list after restarting the calculator application. Depending on the selected MCU family, only the valid and suitable oscillator frequencies are shown in the Oscillator listbox window. See Table 3 for more details.

#### NOTE

If the S12P (S12HY) MCU family is selected and 1.000 MHz internal reference clock (IRC) is picked,  $f_{REF}$  is fixed to  $f_{IRC1M}$ .

$$f_{REF} = f_{IRC1M} = 1.000 MHz$$

Fap. 10

#### 3.1.3 Bus Frequency

The required MCU-bus frequency is selected from the Bus Freq listbox window.

Depending on the selected MCU family, only the bus frequencies from the allowed bus ranges are shown in the Oscillator listbox window. See Table 3 for more details.

#### 3.1.4 Output Results

If any bus frequency is picked, the correct register settings are calculated by the application, allowed  $f_{VCO}$  and  $f_{REF}$  ranges are considered by the application. The SYNR, REFDV, and POSTDIV register values are displayed in hexadecimal format in the appropriate boxes.

The VCO frequency, reference frequency, and maximum PLL lock time are calculated and displayed in the Statistic window.

The FDIV (FCLKDIV) register value is important for proper internal flash state-machine timing, in case the internal flash or emulated EEPROM is used by the embedded application. Correct FDIV is chosen from the appropriate lookup table, depending either on the selected oscillator frequency (S12XE, XF, XS), or the internal bus frequency (S12P, S12HY). Correct flash clock frequency range is checked.

NP

PLL Software Initialization Examples

The PLL locking time is defined as follows:

Eqn. 11

$$t_{lock}[\mu s] = 150 + \frac{256}{f_{REF}[MHz]}$$

## 4 PLL Software Initialization Examples

## 4.1 S12XE PLL Init Examples

## 4.1.1 Basic S12XE PLL Init

```

//-----

// **** S12XE PLL init example ****

//-----

void PLL init(unsigned char synr, unsigned char refdv, unsigned char postdiv)

{

PLLCTL = 0B00000001; // CME=0, PLLON=0, FM1=0, FM2=0, FSTWKP=0, PRE=0, PCE=0, SCME=1

CLKSEL = 0B00000011; // PLLSEL=0,PSTP=0,PLLWAI=0,RTIWAI=1,COPWAI=1

SYNR = synr; // Set the multiplier register

REFDV = refdv; // Set the divider register

POSTDIV = postdiv; // Set the post divider register

PLLCTL PLLON = 1; // Enable the Phase Lock Loop

while (!CRGFLG LOCK); // Wait till the PLL VCO is within tolerance

CLKSEL_PLLSEL = 1; // Select clock source from PLLCLK

//ECLKCTL NECLK=0;

// Enable the BusClk output at ECLK pin

}

//-----

```

**PLL Software Initialization Examples**

## 4.1.2 S12XE PLL Init with Timeout and Status Checking

```

//-----

// **** S12XE PLL_init example with status checking and timeout ****

// return 0 - OK

11

1 - Error - PLL not locked

//-----

unsigned char PLL init (unsigned char synr, unsigned char refdv, unsigned char postdiv)

{

unsigned int timeout=0xffff; // aux. var. to make small SW delay

PLLCTL = 0B00000001; // CME=0, PLLON=0, FM1=0, FM2=0, FSTWKP=0, PRE=0, PCE=0, SCME=1

CLKSEL = 0B00000011; // PLLSEL=0, PSTP=0, PLLWAI=0, RTIWAI=1, COPWAI=1

SYNR = synr; // Set the multiplier register

REFDV = refdv;

// Set the divider register

POSTDIV = postdiv; // Set the post divider register

PLLCTL PLLON = 1; // Enable the Phase Lock Loop

// Wait till the PLL VCO is within tolerance

while((!CRGFLG LOCK)&&( timeout-- != 0));

// PLL didn't lock for some reason

if(timeout == 0)

// return error

return(1);

CRGFLG = 0 \times 10;

// Ensure clearing of LOCKIF flag

CRGINT_LOCKIE = 1; // Enable PLL lock interrupt - to know if it loses clock

CLKSEL_PLLSEL = 1; // Select clock source from PLLCLK

if(CLKSEL_PLLSEL != 1) // will only be set if the PLL was still locked

return(1);

// return error if loss of lock

// else return OK

return(0);

}

11-

_____

//------

// PLL LOCK_ISR

// Triggered when PLL lock status changed (locked / unlocked)

//------

#pragma CODE_SEG NON_BANKED

interrupt 28 void PLL LOCK ISR(void)

{

// Clear LOCKIF flag

CRGFLG = 0 \times 10;

if(CRGFLG_LOCK == 0)

{

//do something here

}

else

{

//do something here

#pragma CODE_SEG DEFAULT

//_____

```

### 4.2 S12P PLL Init Examples

#### 4.2.1 S12P PLL Init in PEI Mode

#### 4.2.2 S12P Basic Init in PEE Mode

```

//-----

_____

// **** S12P PLL init in PEE mode ****

// - PLL Engaged, External Reference Clock used

//------

void PLL init PEE (unsigned char synr, unsigned char refdv, unsigned char postdiv)

{

// Set the multiplier register

CPMUSYNR = synr;

CPMUREFDIV = refdv; // Set the ref. divider register

CPMUPOSTDIV = postdiv;// Set the post divider register

//if(OSCE = 0) then fref = fIRC1M

//if(OSCE = 1) then fref = fosc / (REFDIV + 1)

CPMUOSC OSCE = 1; //enable external oscillator OSCE

//Wait for the UPOSC bit to be set, indicating the oscillator start up

while(CPMUFLG UPOSC == 0);

while (!CPMUFLG LOCK); // Wait till the PLL VCO is within tolerance (PLL locked)

//now the PLL has been locked and fpll = fvco / (POSTDIV + 1)

//ECLKCTL NECLK=0; // Enable the BusClk output at ECLK pin

}

//-----

```

**PLL Software Initialization Examples**

#### 4.2.3 S12P Init in PEE Mode with Timeout & Status Checking

```

//-----

// **** S12P PLL init in PEE mode with status checking and timeout ****

// - PLL Engaged, External Reference Clock used

// return 0 - OK

1 - Error - PLL not locked, oscillator start up error

11

//-----

unsigned char PLL init PEE(unsigned char synr, unsigned char refdv, unsigned char postdiv)

{

unsigned int timeout=0xffff; // aux. var. to make small SW delay

unsigned char i; // aux. var.

CPMUSYNR = synr;

// Set the multiplier register

CPMUREFDIV = refdv; // Set the ref. divider register

CPMUPOSTDIV = postdiv; // Set the post divider register

//if external oscillator is disabled (OSCE = 0) then fref = fIRC1M

//if external oscillator is enabled (OSCE = 1) then fref = fosc / (REFDIV + 1)

CPMUOSC OSCE = 1; //enable external oscillator OSCE

//Wait for the UPOSC bit to be set, indicating the oscillator start up

while((!CPMUFLG UPOSC) && (timeout-- != 0)) {

for(i=0;i<20;i++) {asm nop;}</pre>

}// total timeout delay > ~ 100ms

if(timeout == 0)

return(1);

// Oscillator doesn't started properly, return error

// Wait till the PLL VCO is within tolerance

timeout=0xffff;

while((!CPMUFLG LOCK)&&( timeout-- != 0));

if(timeout == 0) // PLL didn't lock for some reason

// return error

return(1);

CPMUFLG = 0 \times 10;

// Ensure clearing of LOCKIF flag

CPMUINT_LOCKIE = 1; // Enable PLL lock interrupt - to know if it loses clock

CPMUCLKS_PLLSEL = 1; // Select clock source from PLLCLK

if(CPMUCLKS_PLLSEL != 1) // will only be set if the PLL was still locked

return(1);

// return error if loss of lock

return(0);

// else return OK

//now the PLL has been locked and fpll = fvco / (POSTDIV + 1)

//ECLKCTL NECLK=0; // Enable the BusClk output at ECLK pin

}

//------

```

#### PLL Software Initialization Examples

## NP

#### 4.2.3.1 PLL Lock Interrupt Service Routine

```

//-----

_____

// PLL LOCK ISR

// Triggered when PLL lock status changed (locked / unlocked)

//-----

#pragma CODE SEG NON BANKED

interrupt 28 void PLL LOCK ISR(void)

CPMUFLG = 0 \times 10;

// Clear LOCKIF flag

if(CPMUFLG LOCK == 0)

{

//do something here

}

else

{

//do something here

}

}

#pragma CODE SEG DEFAULT

_____

//-----

```

#### 4.2.4 S12P Init in PBE Mode

First of all, we have to set a valid PEE mode, and then we can switch to PBE mode.

To enter the PBE mode from PEI (PEE) mode take the following steps:

- 1. Make sure the PLL configuration is valid: Program the reference divider (REFDIV[3:0] bits) to divide down the oscillator frequency if necessary.

- 2. Enable the external oscillator (OSCE bit).

- 3. Wait for the oscillator to start up (UPOSC = 1).

- 4. Select the oscillator clock as bus clock (PLLSEL = 0).

```

//-----

_____

// **** S12P CLK init in PBE mode ****

// - PLL Bypassed, External Oscillator Clock signal used

//-----

void CLK init PBE (unsigned char synr, unsigned char refdv, unsigned char postdiv)

{

//CPMUSYNR = synr;

// Set the multiplier register - optional

//CPMUREFDIV = refdv; // Set the ref. divider register - optional

//CPMUPOSTDIV = postdiv;// Set the post divider register - optional

//if (OSCE = 0) then fref = fIRC1M

//if (OSCE = 1) then fref = fosc / (REFDIV + 1)

CPMUOSC OSCE = 1; //enable external oscillator OSCE

//Wait for the UPOSC bit to set, indicating the oscillator start up

while(CPMUFLG UPOSC == 0);

//Set the PLLSEL to 0. System clock derived from OSC now. (fbus = fosc/2)

CPMUCLKS PLLSEL = 0;

//ECLKCTL NECLK=0;

// Enable the BusClk output at ECLK pin

_____

```

References

## 4.2.5 Important Notes for S12P PLL Init

Writing into the CPMUSYNR or CPMUREFDIV will unlock the PLL.While PLL is unlocked,  $f_{pll} = f_{vco}/4$  to protect the system from high-core clock frequencies during the PLL stabilization time. If PLL is locked, then  $f_{pll} = f_{vco} / (POSTDIV + 1)$ .

Since the adaptive spike filter uses the VCOCLK (from PLL) to continuously qualify the external oscillator clock, losing the PLL lock status (LOCK = 0) means losing the oscillator status information as well (UPOSC = 0).

The impact of losing the oscillator status in PBE mode is as follows:

- The MSCAN module, which can be configured to run on the oscillator clock, may need to be reconfigured.

- The PLLSEL is set automatically and the bus clock is switched back to the PLL clock.

- Application software needs to be prepared to deal with the impact of losing the oscillator status at any time.

If external oscillator is disabled (OSCE = 0), then  $f_{ref} = f_{IRC1M}$ .

If external oscillator is enabled (OSCE = 1), then  $f_{ref} = f_{osc} / (REFDIV + 1)$ .

## 5 References

- MC9S12XEP100 Reference Manual, MC9S12XEP100RMV1.pdf

- MC9S12XS256 Reference Manual, MC9S12XS256RMV1.pdf

- MC9S12P Reference Manual, MC9S12P128.pdf

- Comparsion of the S12XS CRG Module with S12P CPMU Module, AN3622.pdf

## 6 Glossary

| Term                | Definition                                                                                                           |

|---------------------|----------------------------------------------------------------------------------------------------------------------|

| Resonator           | Common term used for the external ceramic resonator, quartz crystal, or active oscillator clock (canned oscillator). |

| Oscillator          | External or internal reference clock source, used by MCU.                                                            |

| External oscillator | external clock reference source                                                                                      |

| fosc                | frequency of oscillator                                                                                              |

| f <sub>BUS</sub>    | frequency of internal MCU bus clock                                                                                  |

| f <sub>VCO</sub>    | frequency of PLL voltage-controlled oscillator                                                                       |

| f <sub>REF</sub>    | PLL reference frequency                                                                                              |

| PEI                 | PLL engaged — Internal 1 MHz reference clock is used by PLL to derive MCU bus clock (S12P, S12HY only).              |

| PEE                 | PLL engaged — External reference clock is used by PLL to derive MCU bus clock (S12P, S12HY only).                    |

| PBE                 | PLL bypassed — External reference clock is directly used for MCU timing.                                             |

#### How to Reach Us:

Home Page: www.freescale.com

#### Web Support:

http://www.freescale.com/support

#### USA/Europe or Locations Not Listed:

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 +1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

For Literature Requests Only: Freescale Semiconductor Literature Distribution Center 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com

Document Number: Rev. 1 08/2009 Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics as their non-RoHS-compliant and/or non-Pb-free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2009. All rights reserved.