# **UM10113**

User manual for the PNX2015 family

Rev. 01 - 6 May 2005

User manual

#### Document information

| Info     | Content                                                                                                                     |

|----------|-----------------------------------------------------------------------------------------------------------------------------|

| Keywords | TV810 platform, PNX8550, ATV, ATSC, Jaguar, HD subsystem, AVIP1, AVIP2, Columbus, TV microcontroller.                       |

| Abstract | This user manual provides a functional overview of PNX2015, together with detailed descriptions of major functional blocks. |

# **Philips Semiconductors**

**Revision history**

| Rev | Date     | Description    |

|-----|----------|----------------|

| 01  | 20050506 | Objective data |

# **Contact information**

For additional information, please visit: http://www.semiconductors.philips.com

For sales office addresses, please send an email to: sales.addresses@www.semiconductors.philips.com

# 1. Introduction

The Functional Overview section of this User Manual contains three IC level overviews:

- Interfaces

IC interfaces and configuration of AVIP 1 and 2 in the PNX2015

- Top level, structure

IC wide signal and power requirement

Subsystems

Summary of IP block functions

The main body of the manual describes the IP blocks that the PNX2015 contains:

• AVIP

Dlink audio video input interface IP block. This section is applicable to both AVIP 1 and AVIP 2

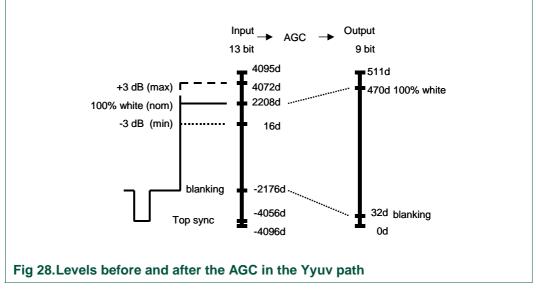

Columbus

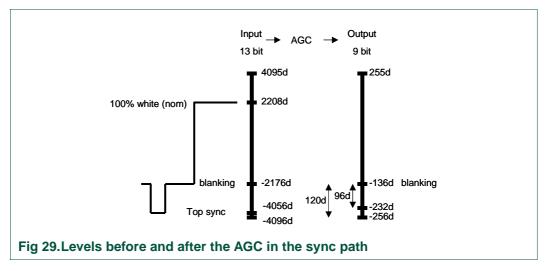

3D comb filter and spatial/temporal noise reduction block description

• HD subsystem

This module subdivides to further IP block descriptions

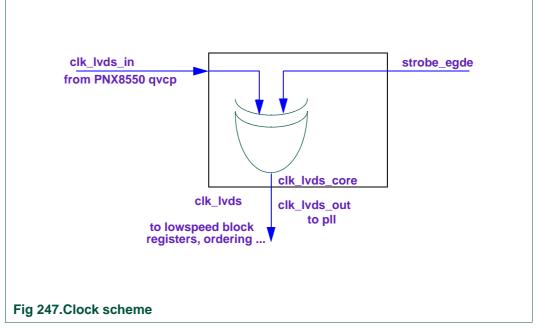

• LVDS transmitter

30 bit input (from PNX8550 QVCP) IP block description

• TV microcontroller

Standby micro (containing an 80C51 CPU core) description

The end sections include Limitations, Glossary and Contents.

#### This user manual provides:

This User Manual contains a description of the PNX2015 components and its internal IP blocks. The Internal IP bock descriptions contain register listings and show how the IP blocks perform their function. There are IC inter connectivity descriptions to the PNX8550 and Video coprocessor. There are explanations of the video audio and programming interfaces.

#### This user manual does not provide:

Since the PNX2015 is a component within a system this document is not a Use Case based programming guide. The register descriptions do not contain recommended programming values. The PNX2015 has a memory bases architecture which provides for flexible configuration to meet Use Case requirements. There are therefore no configuration descriptions for the PNX2015.

# 2. Functional overview

### 2.1 Introduction

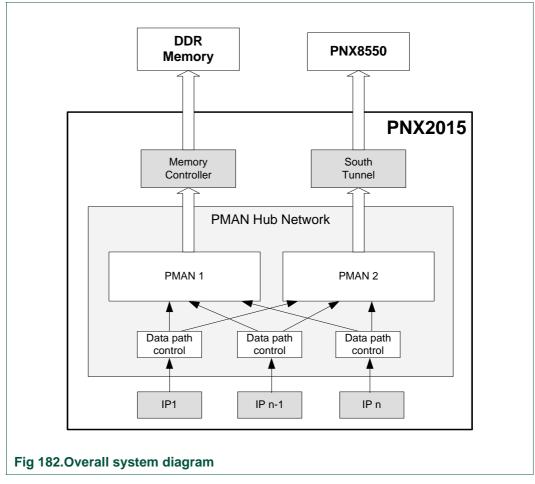

The PNX2015 is a prime component for the mid-to high-end market segment of the ATSC, DVB and Flat Panel markets. Through the addition of various hardware and software components, systems can meet high-end requirements of connectivity and picture performance.

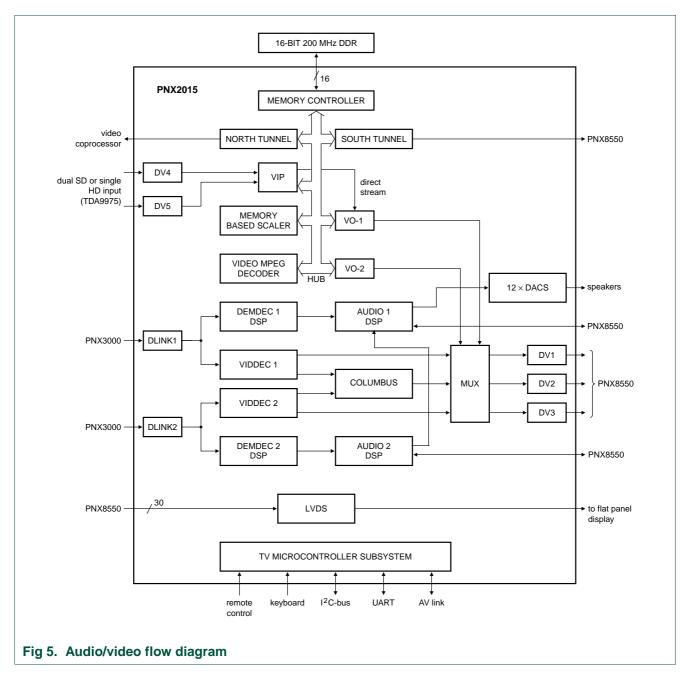

The PNX2015 accompanies the PNX8550 and provides the following functionality, in addition to that provided by PNX8550:

- Dual analog audio/video decoding.

- Full audio processing.

- Analog video improvement, e.g. 3D comb filter, noise reduction and noise measurement (Columbus).

- Second channel HD decode with memory based scaler.

- Interface to additional external video improvement IC's.

- RGB via standard LVDS interface for LCD panels.

- Embedded TV microcontroller.

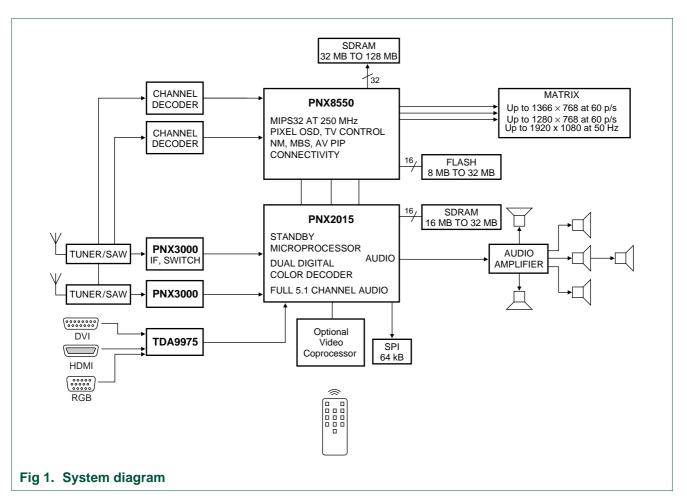

An example system diagram is shown in Figure 1

In terms of functional blocks the PNX2015 can be described as follows:

- Audio Video Input Processor 1 (AVIP1).

- Audio Video Input Processor 2 (AVIP2).

- 3D comb filter with spatial and temporal noise reduction (Columbus).

- High Definition MPEG decoder (HD Subsystem).

- Standby microcontroller for low-power control.

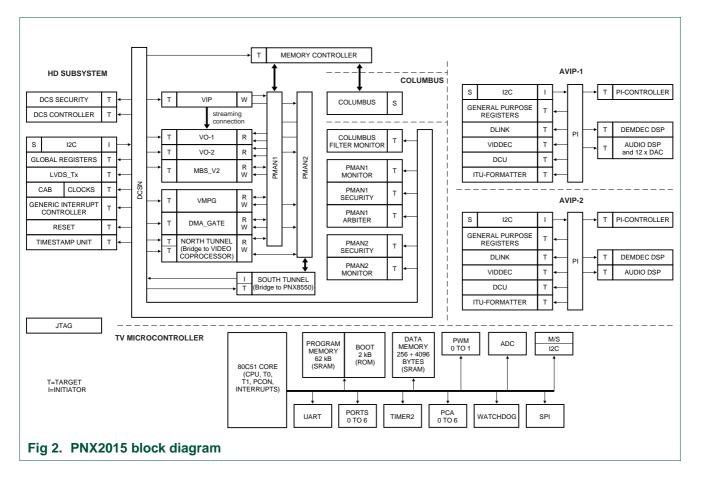

The PNX2015 block diagram is shown in Figure 2.

UM10113

**UM10113**

PNX2015 User Manual

### **Philips Semiconductors**

### 2.2 Feature summary

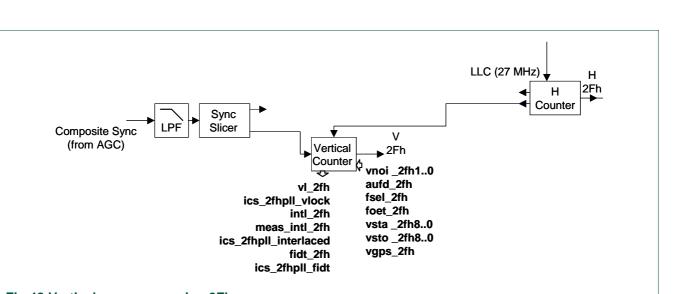

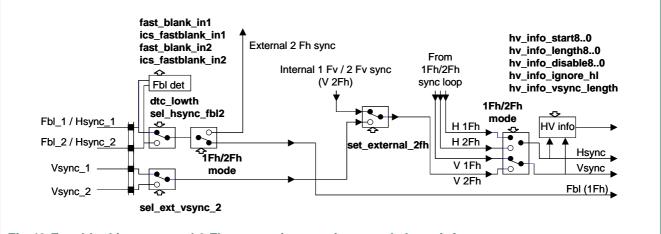

- Detection of PAL, NTSC or SECAM analog sources and 1<sub>fH</sub> and 2<sub>fH</sub> component video input sources. (1<sub>fH</sub> = 13.3 MHz, 2<sub>fH</sub> = 27 MHz).

- Support for 1<sub>fH</sub> and 2<sub>fH</sub> video sources; progressive and interlaced.

- 3D comb filters for PAL/NTSC standards.

- Spatial and temporal noise reduction for PAL, NTSC and SECAM analog sources.

- Decoding for global VBI Standards (WST, WSS, VPS, CC, VITC and Gemstar<sup>™</sup>).

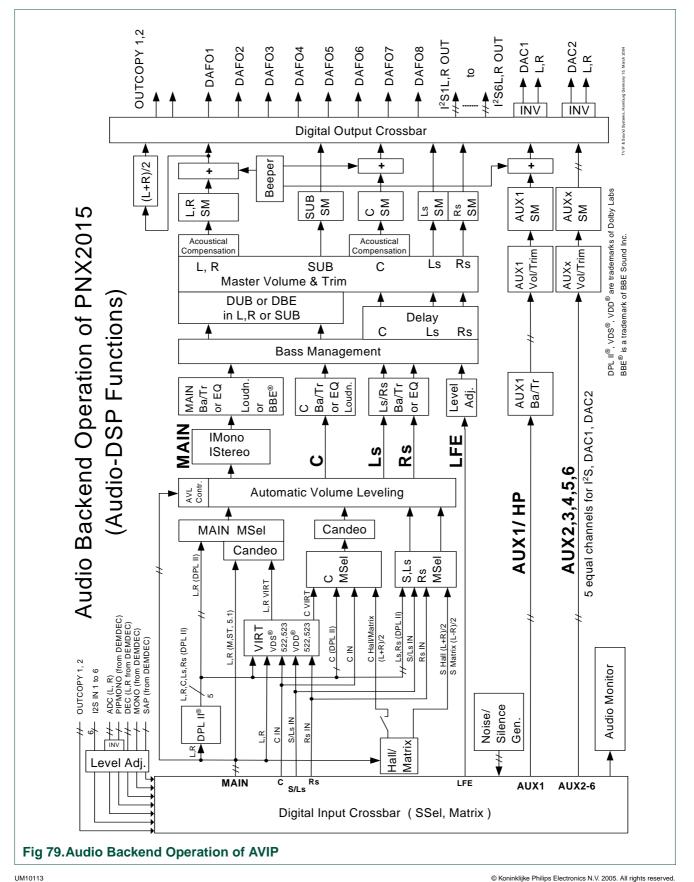

- Global multi-standard audio demodulation and decoding (FM, AM, NICAM, BTSC, A2).

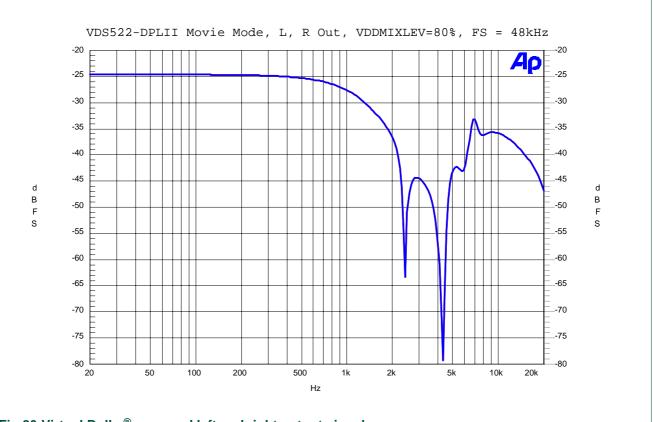

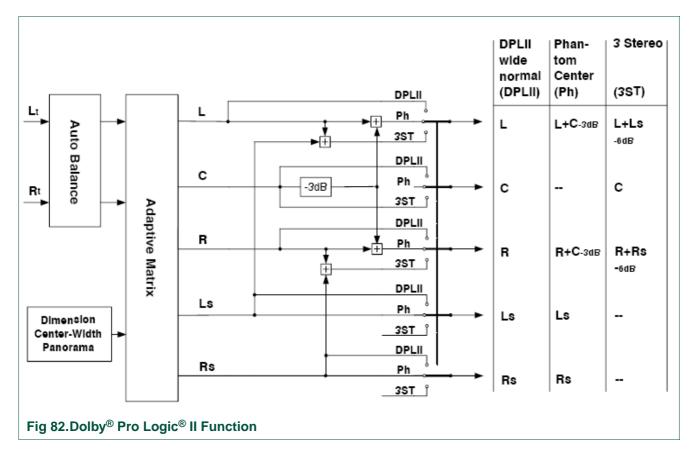

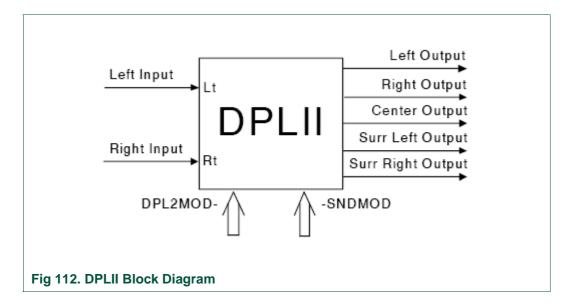

- Dolby<sup>®</sup> ProLogic<sup>®</sup> II multi-channel audio decoding and post-processing.

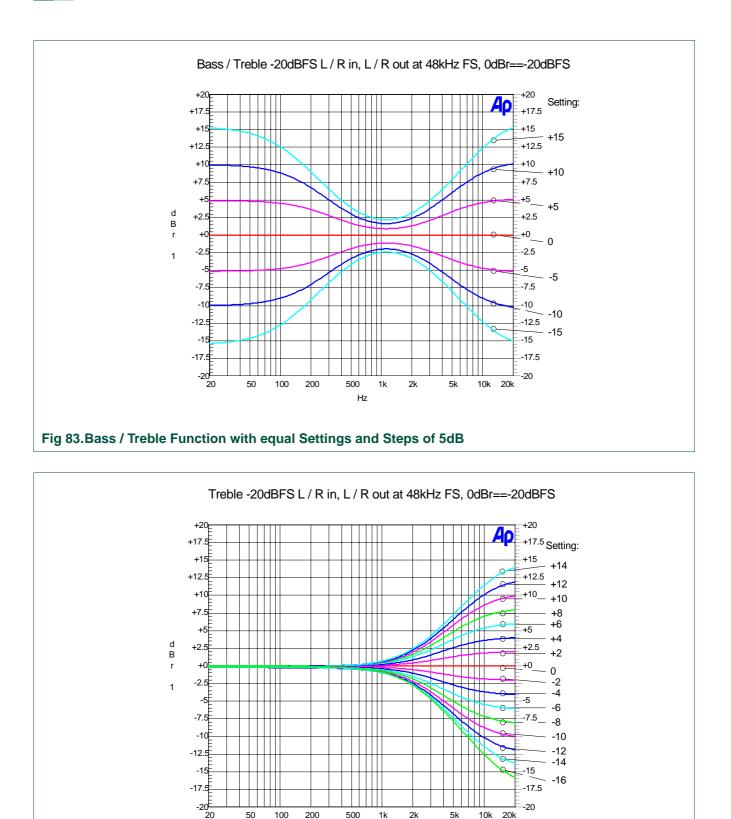

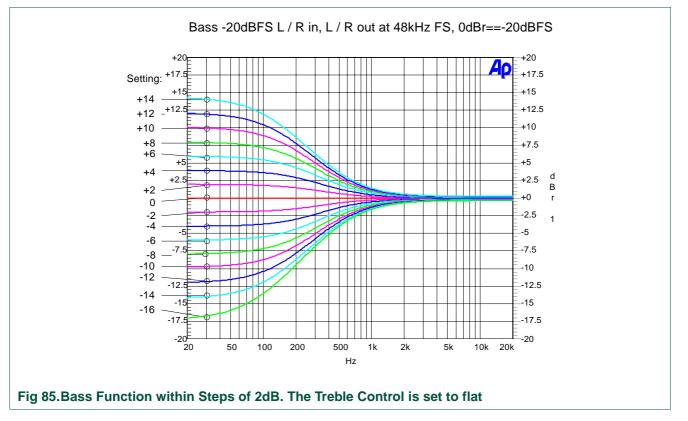

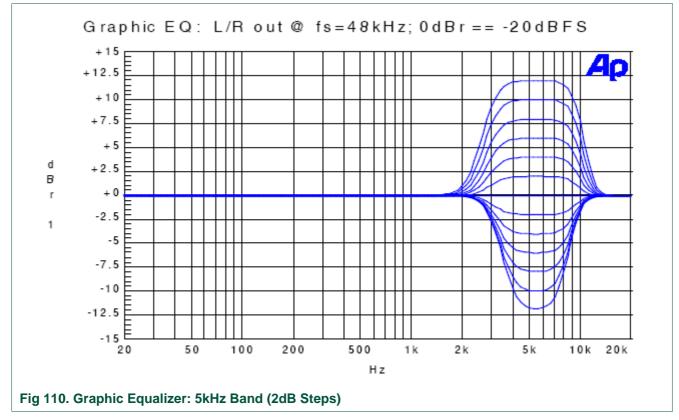

- Advanced, fully programmable audio post-processing functions (VDS, VDD, bass management and graphic equalizer).

- RGB via standard LVDS interface for National<sup>™</sup> (18/24-bit) and THine<sup>™</sup> (18/24/30-bit).

- High and Standard Definition digital video input interface.

- Hardware decoding of two SD streams (MPEG2 MP@ML) or one HD (MPEG2 MP@HL).

- Embedded TV Microcontroller for TV control and system power management.

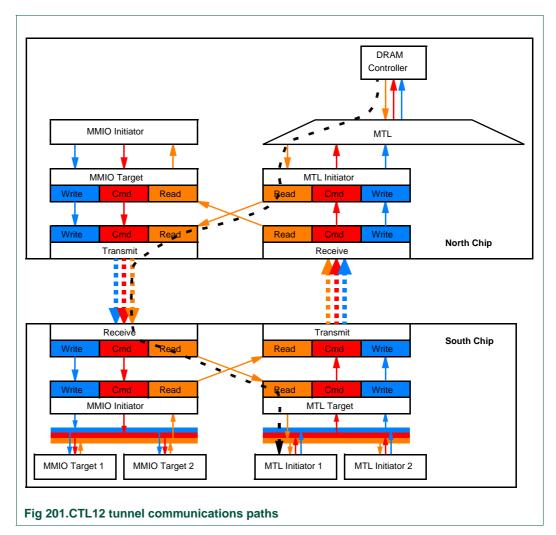

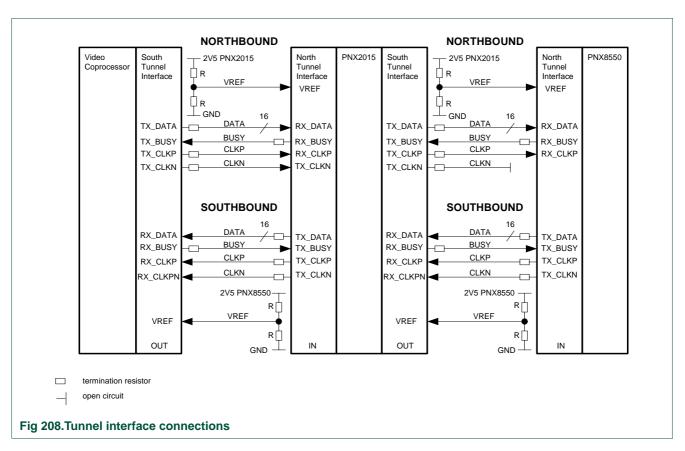

- Two independent tunnel interfaces for PNX8550 and video coprocessor.

UM10113

PNX2015 User Manual

- Memory interface for DDR/GDDR SDRAM and SPI™ for external flash. •

- Three digital video outputs 8/10-bit YUV 4:2:2. •

Three versions of the PNX2015 are available, the features are shown in Table 1.

#### Table 1: PNX2015 versions

| Type number    | Features |        |      |      |      |

|----------------|----------|--------|------|------|------|

|                | 3D NTSC  | 3D PAL | DPL2 | BBE™ | dbx™ |

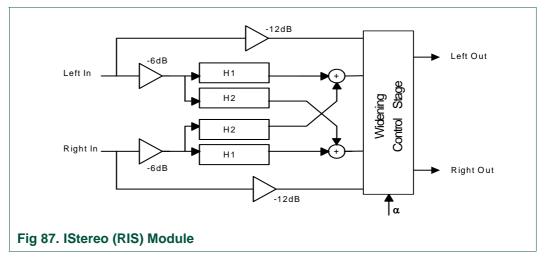

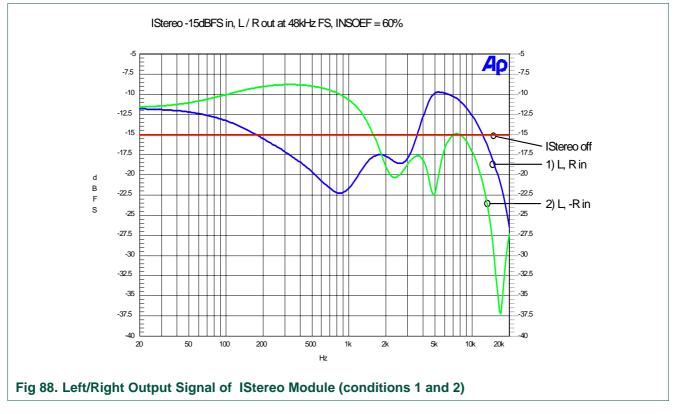

| PNX2015E/M1C02 |          | 3      | 3    |      |      |

| PNX2015E/M1C03 | 3        |        | 3    |      | 3    |

### 2.3 Interfaces

#### 2.3.1 Video

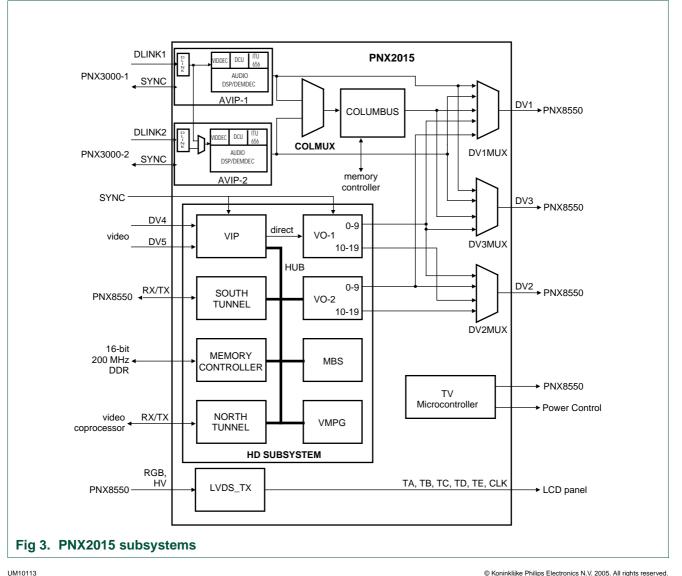

Figure 3 shows the main video interfaces of PNX2015, and how the video signals are connected between subsystems.

7 of 795

Table 3:

Select

1 Default

0

3

Table 2 to Table 4 show the outputs available on the three Digital Video output ports. Each DV port can independently select the required (8/10-bit YUV) output source. There is no link between the DV outputs.

The DV1 and DV2 ports can be used in combination to output a 16/20-bit semi-planar signal. In this mode DV1 outputs the Y (lower 10-bits) component, and DV2 the UV (upper 10-bits) component.

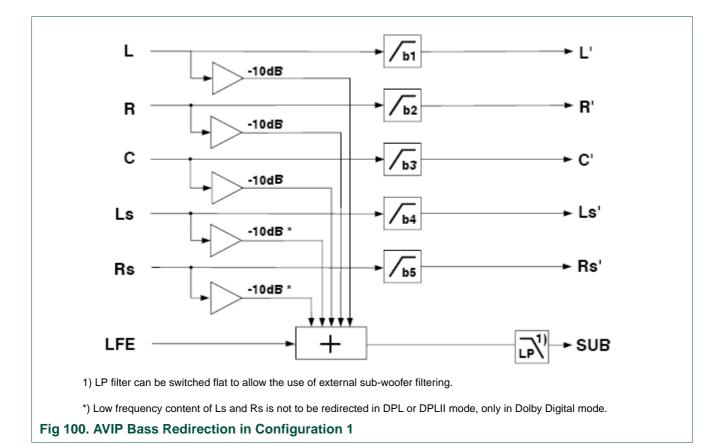

| Table 2:  | Output port DV1 - signal combinations        |

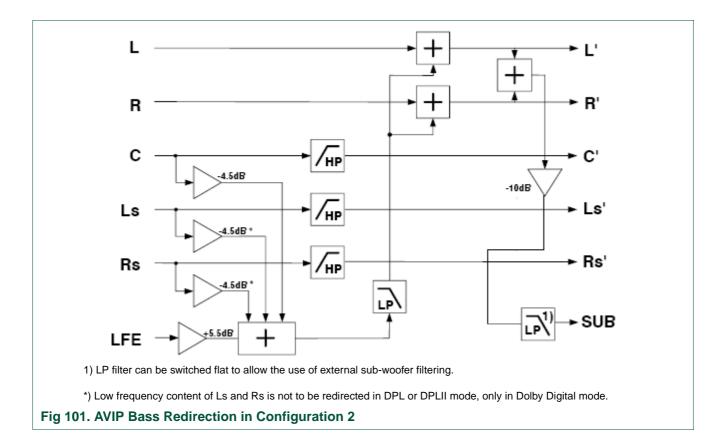

|-----------|----------------------------------------------|

| Select    | DV1                                          |

| 0 Default | AVIP1                                        |

| 1         | AVIP2                                        |

| 2         | Columbus                                     |

| 3         | VO-1 (lower) 656 mode = YUV; semi-planar = Y |

| 4         | VO-2 (lower) 656 mode = YUV; semi-planar = Y |

#### Table 0. **~** . C DV/A ......

| 2 | VO-1 (upper) 656 mode = N/A; semi-planar = UV     |

|---|---------------------------------------------------|

| 2 | VO-1 (upper) 000 mode – $WA$ , semi-planal – $OV$ |

DV2

**Output port DV2 - signal combinations**

VO-1 656 mode = YUV; semi-planar = N/A

VO-2 656 mode = YUV; semi-planar = N/A

VO-2 (upper) 656 mode = N/A; semi-planar = UV

#### Table 4: **Output port DV3 - signal combinations**

| Select    | DV3                                    |

|-----------|----------------------------------------|

| 0         | AVIP1                                  |

| 1 Default | AVIP2                                  |

| 2         | Columbus                               |

| 3         | VO-1 656 mode = YUV; semi-planar = N/A |

|           |                                        |

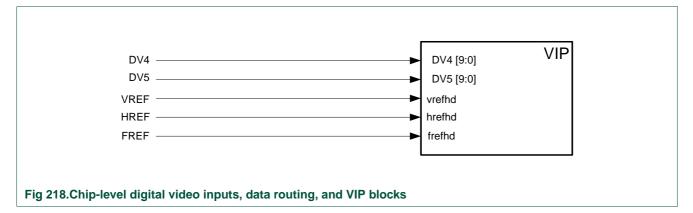

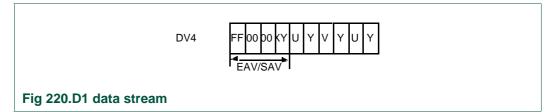

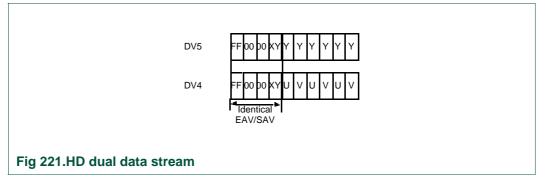

The DV Input ports can be used as a standard 656 interface 8/10-bit with DV4 only, or as a 16/20-bit semi-planar mode with the addition of DV5. One clock is provided for DV4 and DV5, so they may not be used independently.

#### DV input port signal combinations (DV4, DV5) Table 5:

| Input port | 656 mode | Semi-planar mode |

|------------|----------|------------------|

| DV4        | YUV      | Y                |

| DV5        | -        | UV               |

The use of video data bus bits on DV1 to DV5, and their connections for the SD and HD capture modes are shown in Table 7 and Table 6. DV1, DV2 and DV3 are outputs, DV4 and DV5 are inputs.

In all modes, the MSB of the data words is always placed on pin [9], i.e. in any 8-bit mode the valid data occupies the upper 8 most significant bit positions of the 10-bit input.

#### 2.3.1.1 Multi-mode video output

#### Table 6: Multi-mode video output connections (DV1, DV2, DV3)

| Signal         | Port | 656 mode  |           | Semi-planar |          |

|----------------|------|-----------|-----------|-------------|----------|

|                |      | 10-bit    | 8-bit     | 20-bit      | 16-bit   |

| DV1_DATA [9:2] | DV1  | YUV [9:0] | YUV [7:0] | Y [9:0]     | Y [9:2]  |

| DV1_DATA [1:0] |      |           | not used  | _           | not used |

| DV2_DATA [9:2] | DV2  | YUV [9:0] | YUV [7:0] | UV [9:0]    | UV [9:2] |

| DV2_DATA [1:0] |      |           | not used  | _           | not used |

| DV3_DATA [9:2] | DV3  | YUV [9:0] | YUV [7:0] | not used    | not used |

| DV3_DATA [1:0] | _    |           | not used  | _           |          |

#### 2.3.1.2 Multi-mode video input

#### Table 7: Multi-mode video input connections (DV4, DV5)

| Signal         | Port | 656 mode  |           | Semi-planar |          |

|----------------|------|-----------|-----------|-------------|----------|

|                |      | 10-bit    | 8-bit     | 20-bit      | 16-bit   |

| DV4_DATA [9:2] | DV4  | YUV [9:0] | YUV [7:0] | Y [9:0]     | Y [9:2]  |

| DV4_DATA [1:0] | _    |           | not used  |             | not used |

| DV5_DATA [9:2] | DV5  | not used  | YUV [7:0] | UV [9:0]    | UV [9:2] |

| DV5_DATA [1:0] |      |           | not used  |             | not used |

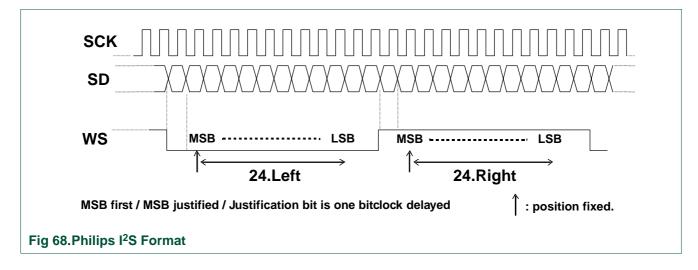

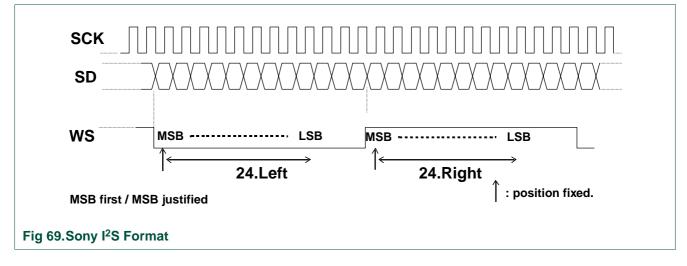

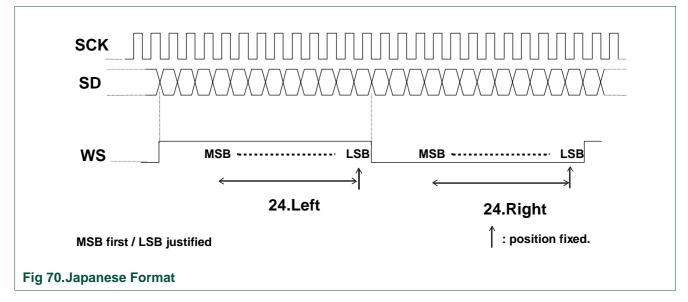

#### 2.3.2 Audio

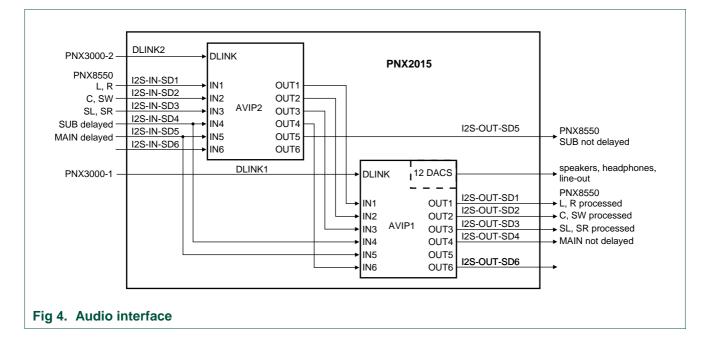

The audio interfaces allow for up to six I<sup>2</sup>S[9] digital inputs, and six I<sup>2</sup>S digital outputs. All I<sup>2</sup>S interfaces share a common clock system and Word Select signal. The I<sup>2</sup>S clock system can be configured as Master or Slave.

Figure 4 shows the interconnections between the two AVIP instances and the connections to the I<sup>2</sup>S device pins. The legend shows the suggested signal content when used with PNX8550, although the assignment of signals to the I<sup>2</sup>S channels and DAC outputs is fully flexible. Audio DACs are only present on AVIP1, otherwise the two AVIP audio sections are identical.

In single MPIF AvPip mode the suggested routing of the sub channel is to I2S\_OUT\_SD4.

#### 2.3.3 Audio/video flow

#### 2.3.4 Control

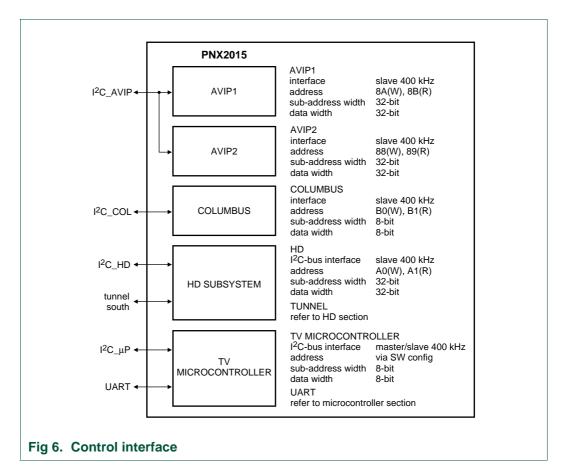

The AVIP and Columbus subsystems are controlled via I<sup>2</sup>C interfaces as shown in Figure 6.

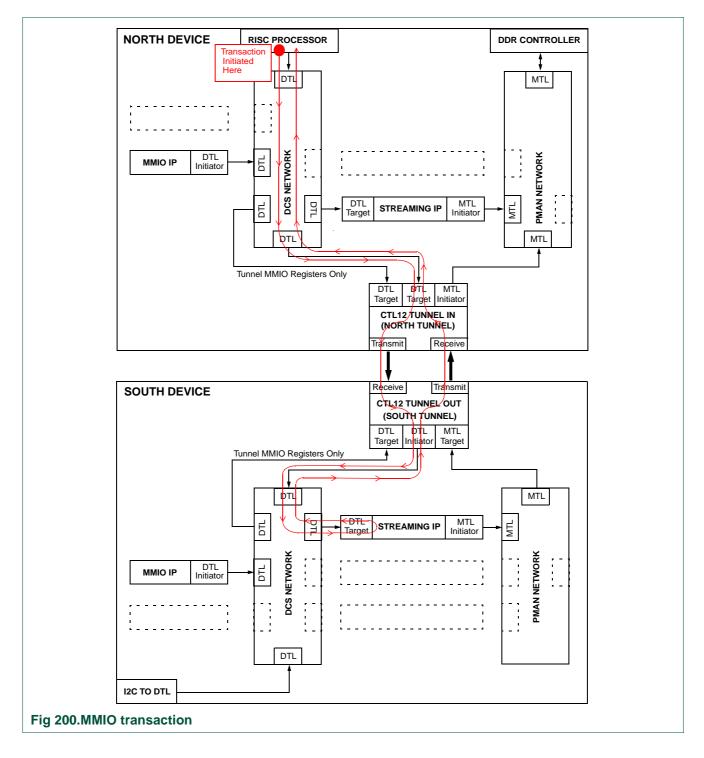

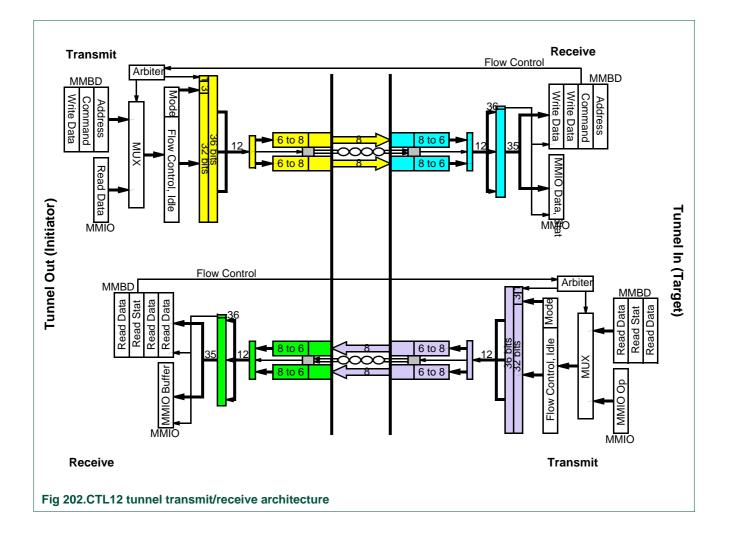

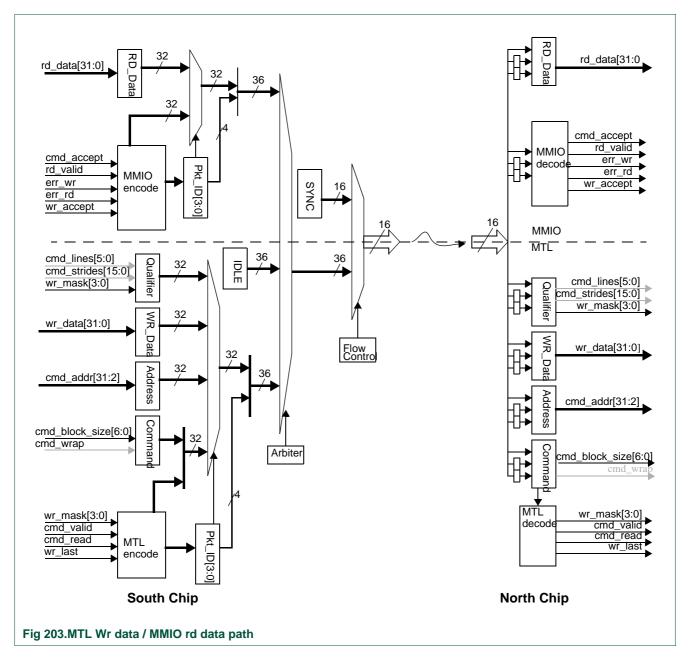

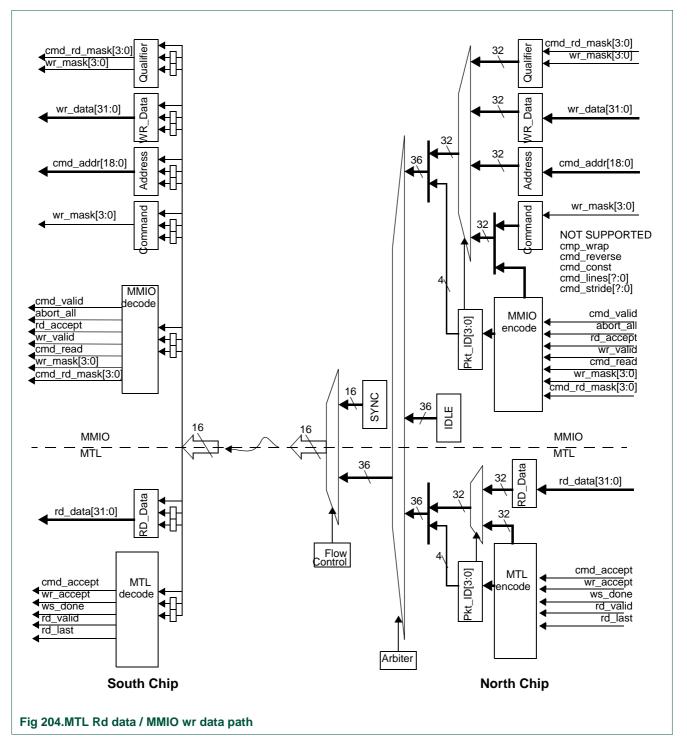

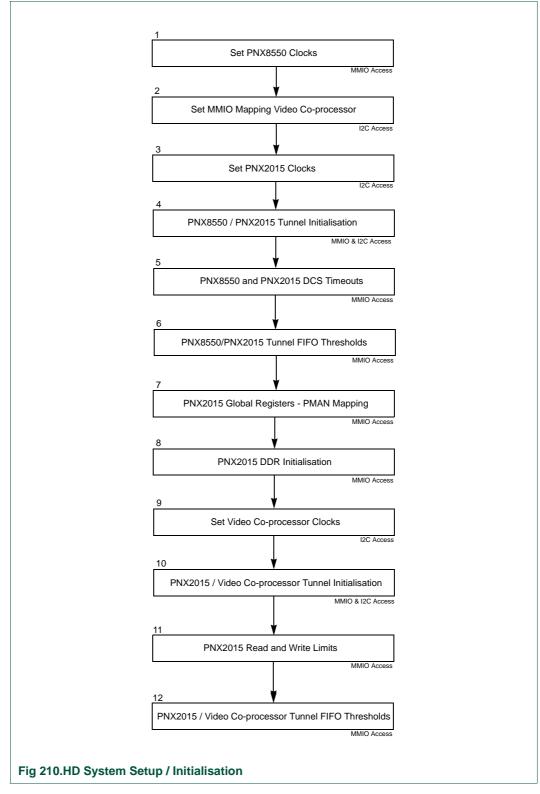

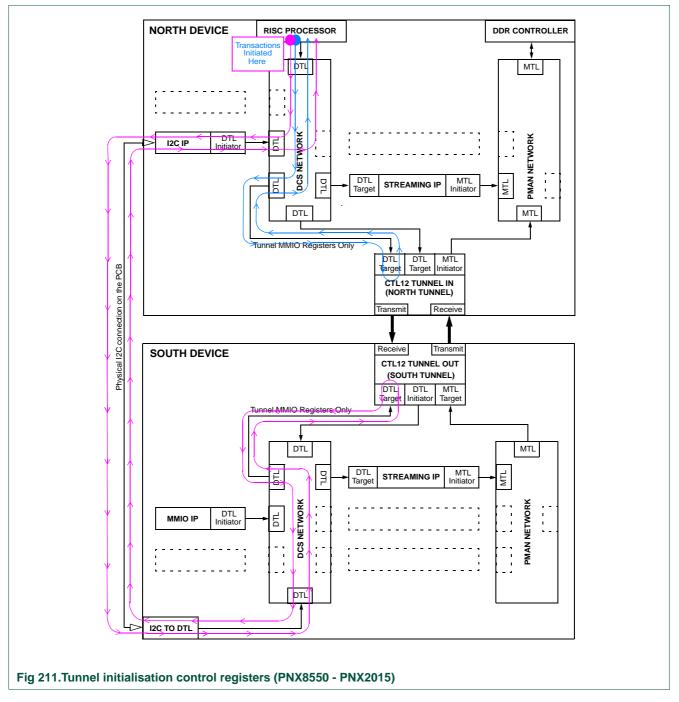

The main method of control for the HD subsystem is via MMIO commands across the south tunnel interface, once the tunnel is initialized using the  $l^2C$ .

The TV Microcontroller has a master/slave I<sup>2</sup>C interface, which is mainly used by the TV Microcontroller to control the devices in the system.

The I<sup>2</sup>C module implements a master/slave I<sup>2</sup>C interface with integrated shift register timing generation and slave address recognition. It is compliant to the I<sup>2</sup>C specification Ref. 1. The I<sup>2</sup>C standard mode (100 KHz SCL) and fast mode (400 KHz SCL) are supported. Extended 10-bit addressing is not supported.

| Table | 8: | Control i | nterface |

|-------|----|-----------|----------|

|-------|----|-----------|----------|

| Block              | Sub-address   | Sub-address width | Data width |

|--------------------|---------------|-------------------|------------|

| AVIP1              | 8A(W), 8B(R)  | 32-bit            | 32-bit     |

| AVIP2              | 88(W), 89(R)  | 32-bit            | 32-bit     |

| Columbus           | B0(W), B1(R)  | 8-bit             | 8-bit      |

| HD subsystem       | A0(W), A1(R)  | 32-bit            | 32-bit     |

| TV Microcontroller | via SW config | 8-bit             | 8-bit      |

#### 2.3.5 Test (JTAG)

A JTAG interface is used for both IC testing via a TAP controller and boundary scan. A single boundary scan chain is provided for the whole of the PNX2015. Pads that are not included in the boundary scan chain are:

- Power supplies.

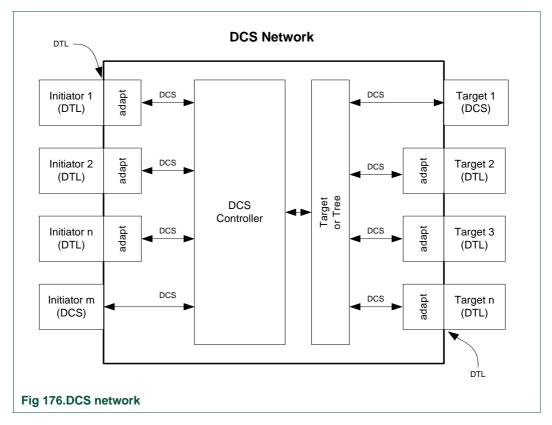

- Analog input and output.

- DDR/GDDR SDRAM Interface.

- LVDS interface.

The Boundary Scan Description Language (BSDL) file detailing the TAP Controller ID and Instructions is available on request from Philips Semiconductors.

#### 2.4 Top level structure

The following paragraphs describe the top-level structure of the PNX2015 with respect to clocking, reset, interrupts and power supplies. Details of the subsystem implementation can be found in <u>Section 2.5</u>.

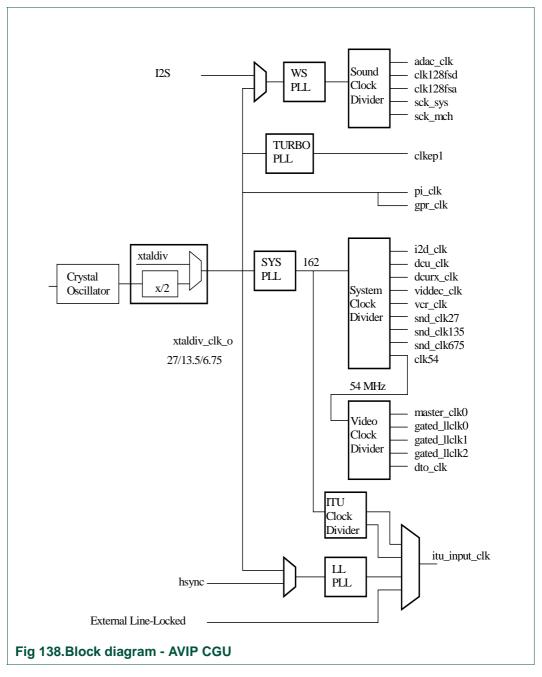

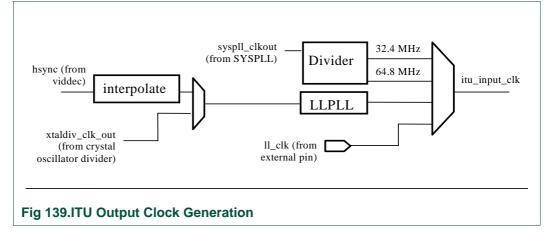

#### 2.4.1 Clocking

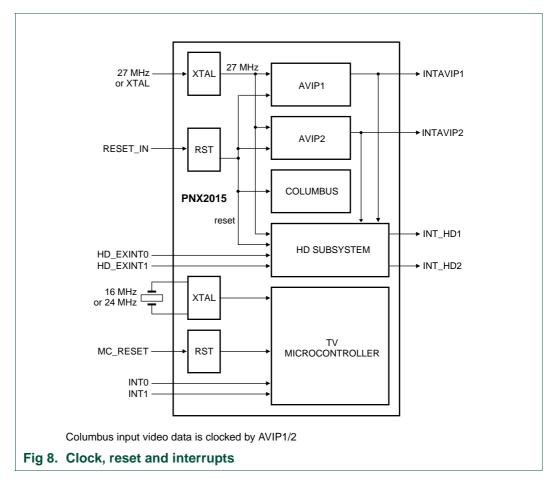

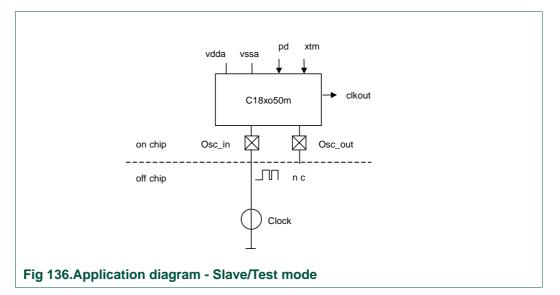

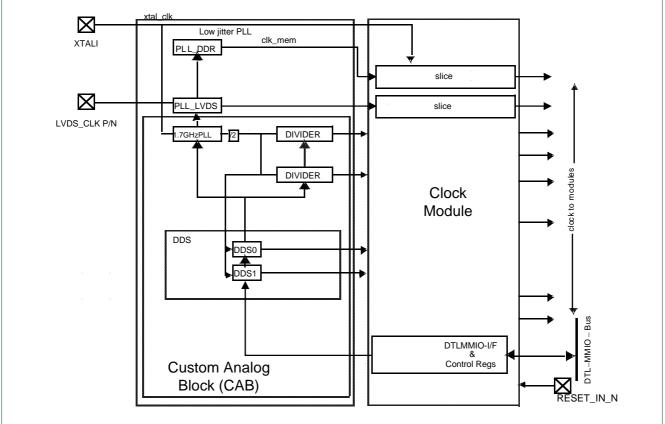

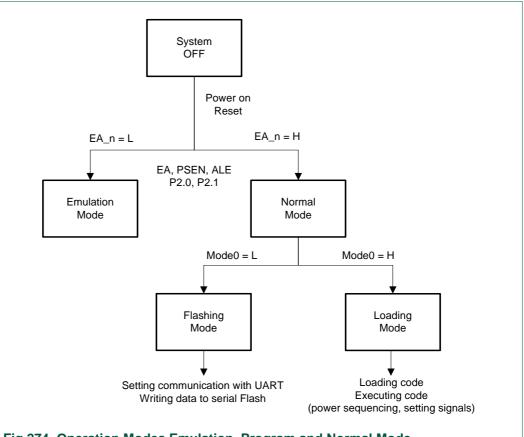

The PNX2015 requires two clock sources, one for the TV Microcontroller subsystem and one for the remaining subsystems. These may be from a clock generator source, or from a crystal. See Figure 8.

The TV Microcontroller supports either 16 MHz or 24 MHz external crystal.

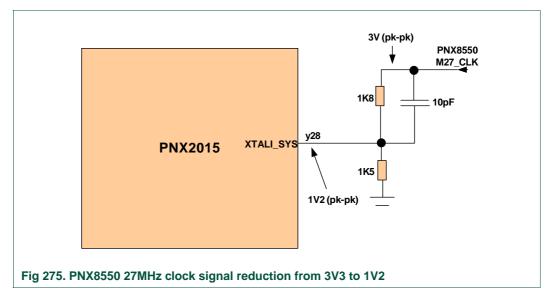

The HD, AVIP1 and AVIP2 require a clock of 27 MHz. Columbus receives a clock from either AVIP1 or AVIP2, depending on the selected input source. To ensure synchronization of video streams processed across the PNX8550 and PNX2015 devices, the 27 MHz is be supplied from PNX8550.

See *PNX2015* Limitations <u>Section 8.1</u> for voltage divider network.

Remark: An external crystal may be used for testing purposes only.

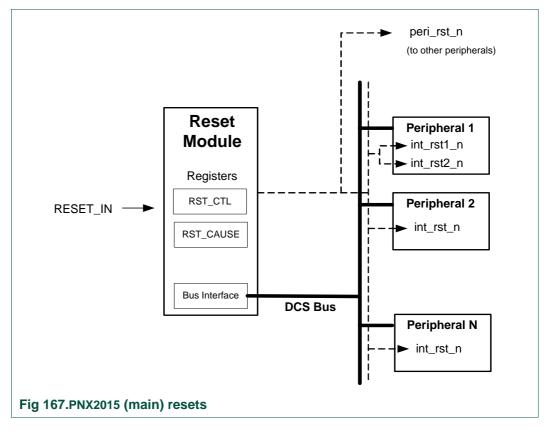

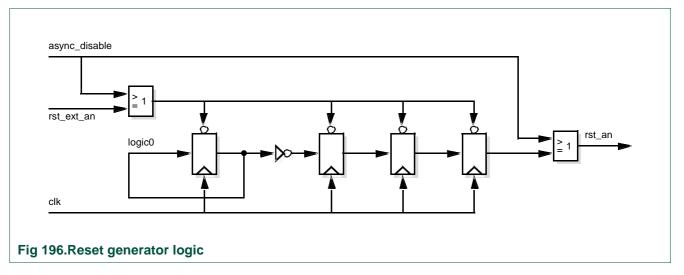

#### 2.4.2 Reset

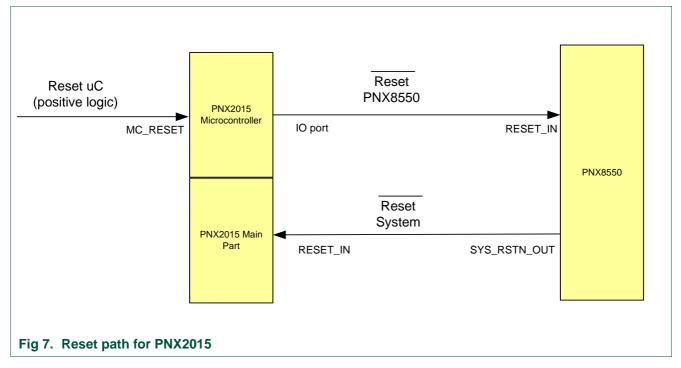

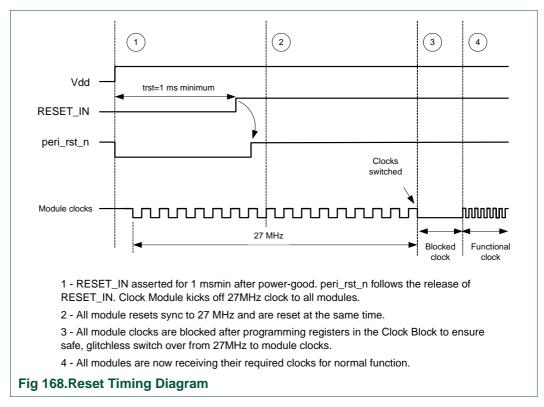

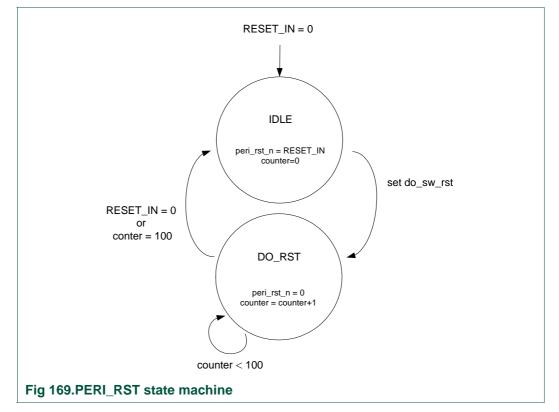

The PNX2015 has two external reset signals, one for the TV Microcontroller subsystem, and one for the remaining subsystems. This is shown in <u>Figure 7</u> and <u>Figure 8</u>. The TV Microcontroller reset is active high and held high for at least 30 clock cycles after the crystal frequency has become stable.

The reset for AVIP1 and AVIP2, Columbus and the HD subsystem is derived from a single input. The signal is active low and held low for at least 30 clock cycles after the 27 MHz clock is applied. The reset signal is extended within the subsystems for up to 1.2 ms to allow for all blocks to initialize correctly. After the 1.2 ms period communication with the subsystems can commence.

PNX2015 User Manual

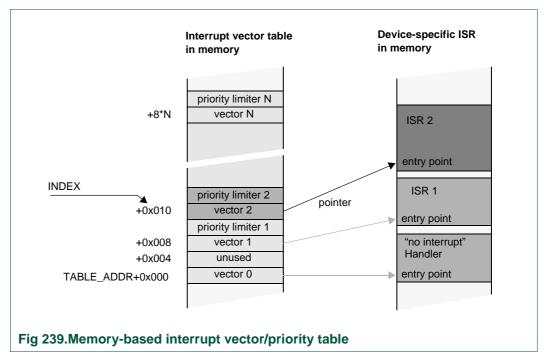

### 2.4.3 Interrupts

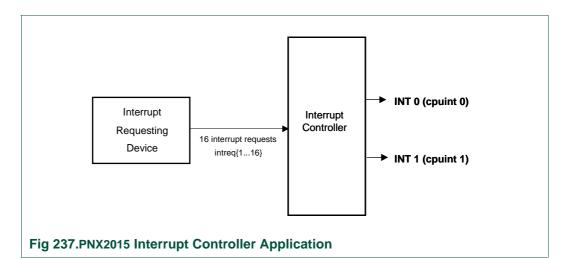

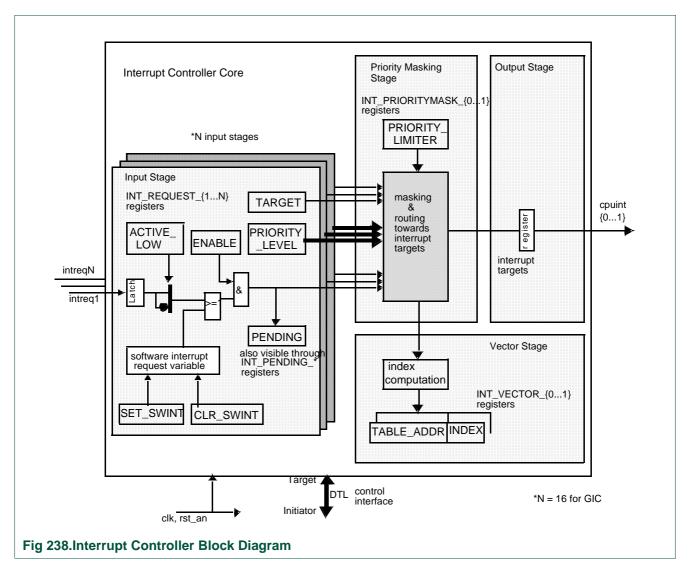

The PNX2015 has an interrupt structure based on the individual subsystems. The details of all interrupt sources and control can be found in the subsystem descriptions.

The PNX2015 provides:

- Four interrupt outputs, one each from AVIP1 and AVIP2 and two from the HD

- Four interrupt inputs, two for the TV Microcontroller and two for the HD

# UM10113

PNX2015 User Manual

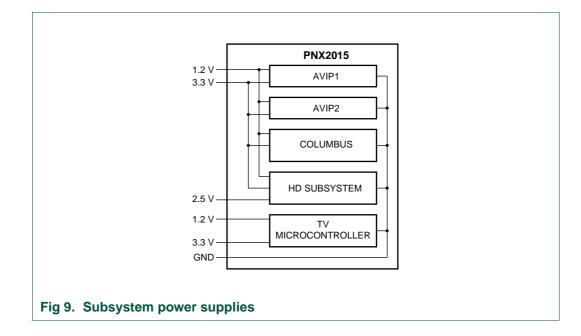

#### 2.4.4 Power supplies

The PNX2015 requires the following:

- 1.2 V for core logic

- 2.5 V for DDR-SDRAM and tunnel interfaces

- 3.3 V for periphery (excluding DDR and Tunnel)

and for the TV Microcontroller:

- 1.2 V for MC core

- 3.3 V for MC periphery

PNX2015 User Manual

### 2.5 Subsystems

The following paragraphs describe in more detail the functions of the various subsystems.

The processor referred to by the term CPU has different meanings depending on where it occurs in this User Manual:

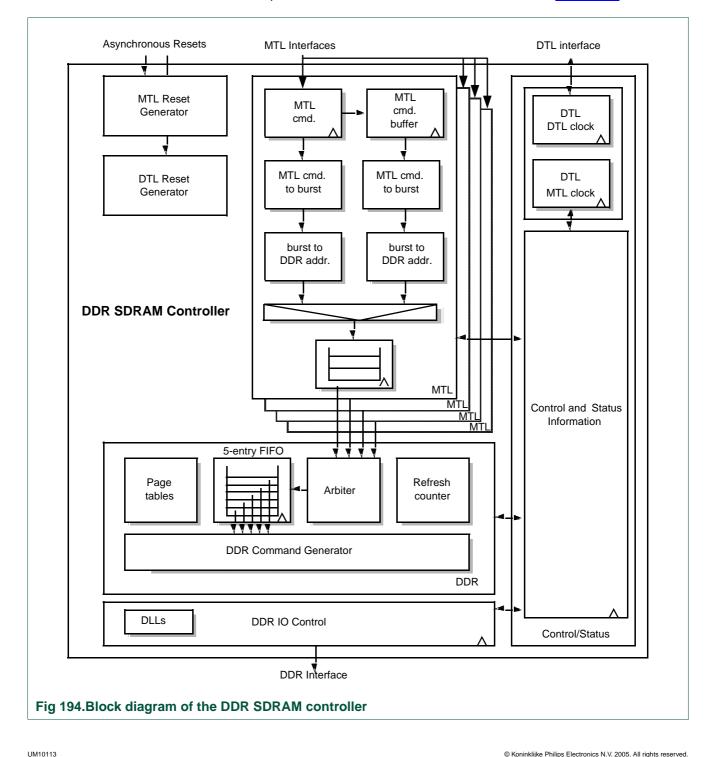

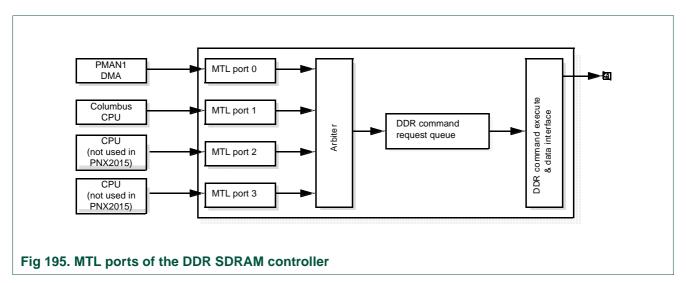

- In the DDR SDRAM section of the HD subsystem, CPU refers to a low latency MTL port of DDR SDRAM controller.

- In the TV microcontroller section CPU refers to the PNX2015 TV micro core processor.

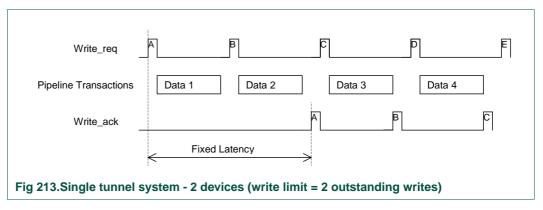

- In the remainder of the document, CPU refers to a processor in the PNX8550 (MIPS or Trimedia).

### 2.5.1 AVIP1 and AVIP2

Each AVIP performs input decoding of single stream analog audio and single stream analog video signals. In addition, AVIP1 provides processing and presentation of all audio output streams in the system.

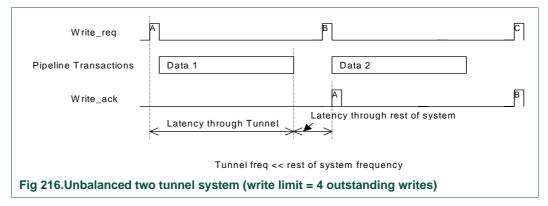

The AVIPs support the following features:

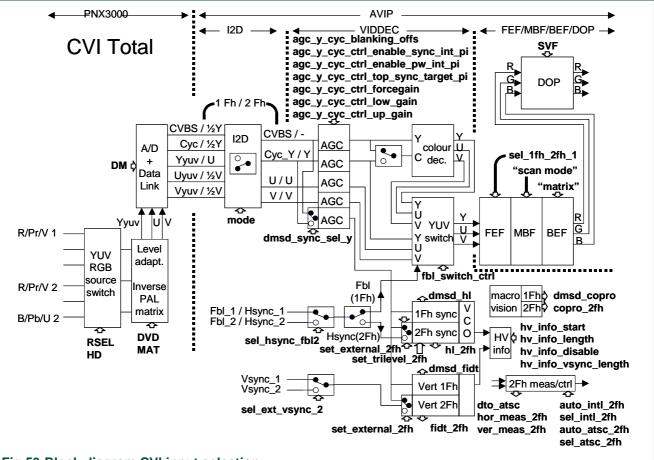

- Detection of PAL, NTSC or SECAM, and various 1f<sub>H</sub> and 2f<sub>H</sub> component video input sources.

- Full support for 1f<sub>H</sub> and 2f<sub>H</sub> video sources; progressive and interlaced.

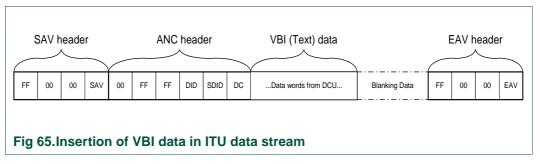

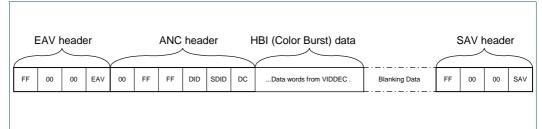

- Decoding for global VBI Standards (WST, WSS, VPS, CC, VITC).

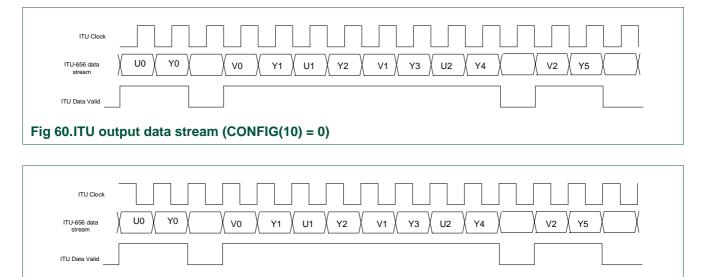

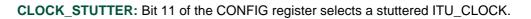

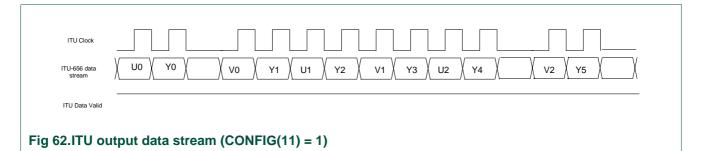

- ITU-656 output interface.

- Global multi-standard audio demodulation and decoding.

- Dolby<sup>®</sup> Pro Logic<sup>®</sup> II multi-channel audio decoding and post-processing.

- Advanced fully programmable audio post-processing functions, including psychoacoustic spatial algorithms for optimal loudspeaker matching.

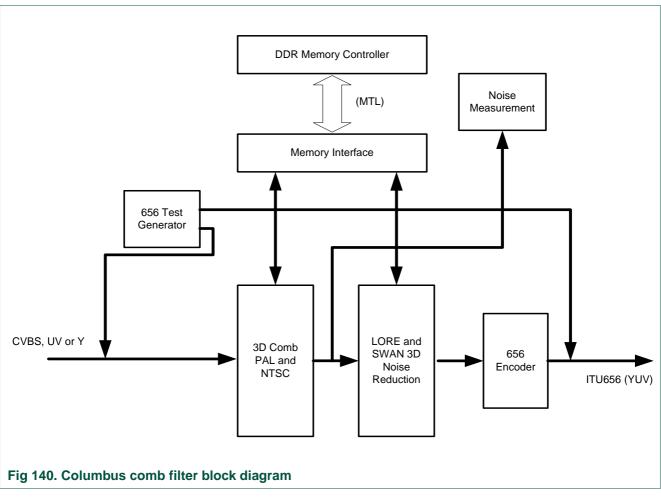

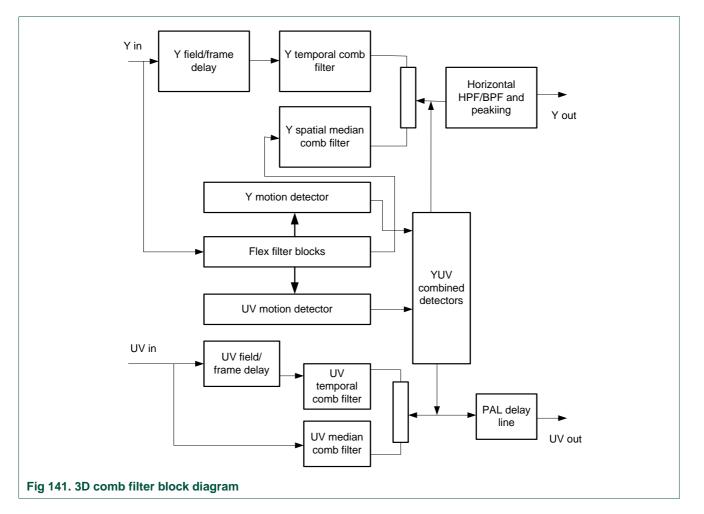

#### 2.5.2 Columbus

This block provides the following picture improvement functions:

- Enhanced 2D comb for PAL and NTSC.

- 3D field comb for PAL and NTSC.

- 3D frame comb for PAL and NTSC.

- Spatial noise reduction for all component video standards.

- Temporal noise reduction for all component video standards.

The comb filter is controlled via a separate I<sup>2</sup>C interface on the PNX2015, this is to ensure registers containing measurement are accessed at appropriate times. The measurement information is also available as ancillary data within the video stream (ITU-656).

For certain features of the comb filter access to external memory is required. The PNX2015 has a unified memory that both comb filter and HD subsystem's share concurrently.

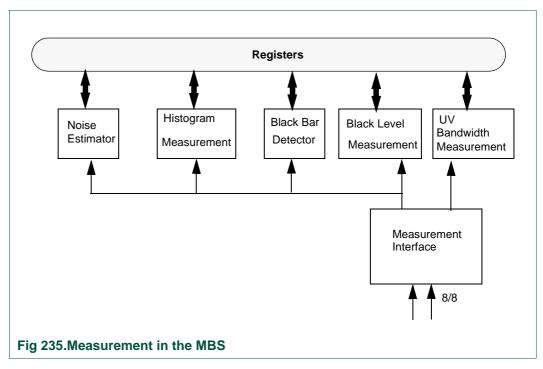

A functional block diagram is shown in Figure 140.

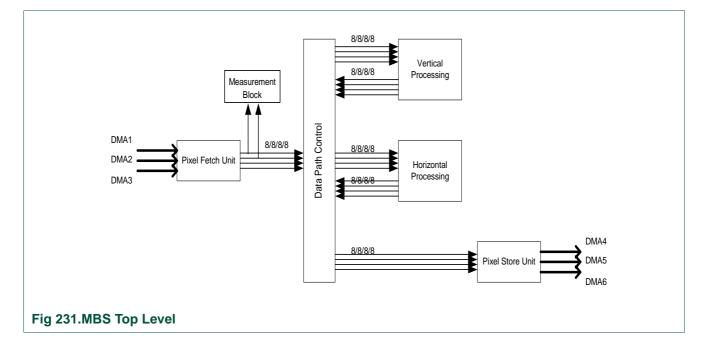

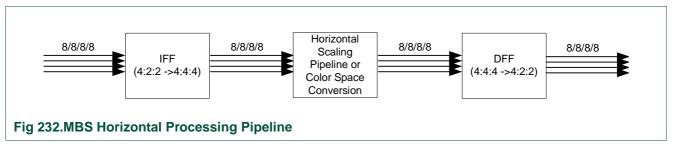

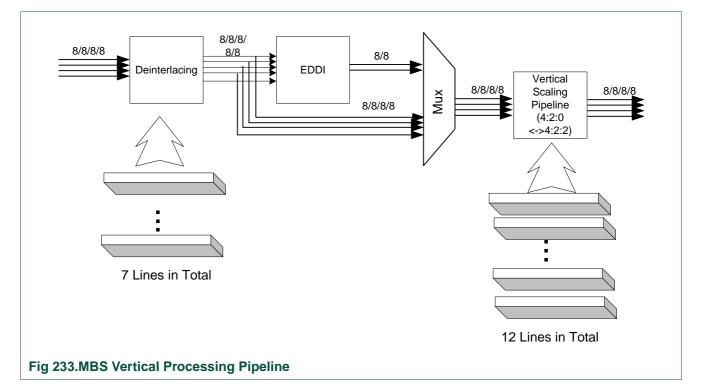

#### 2.5.3 HD subsystem (High Definition)

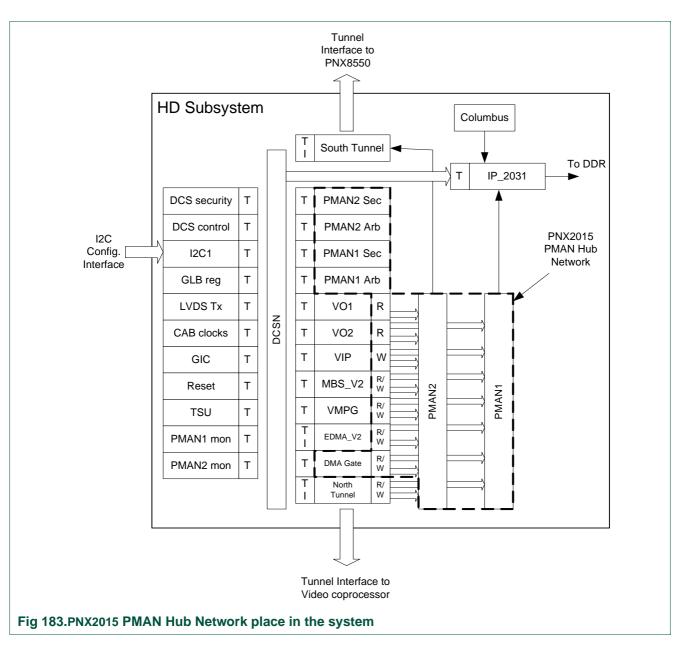

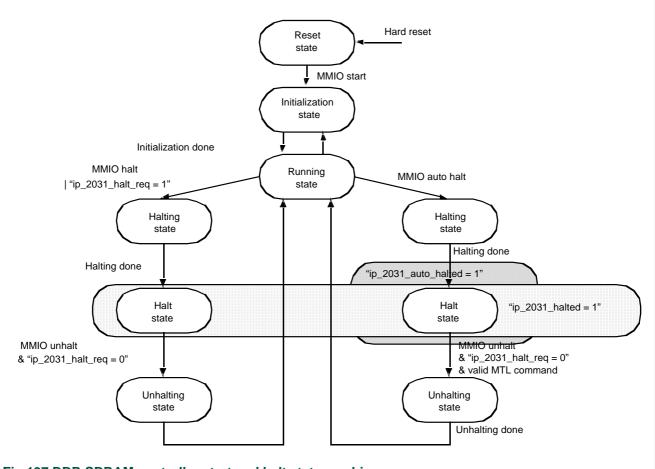

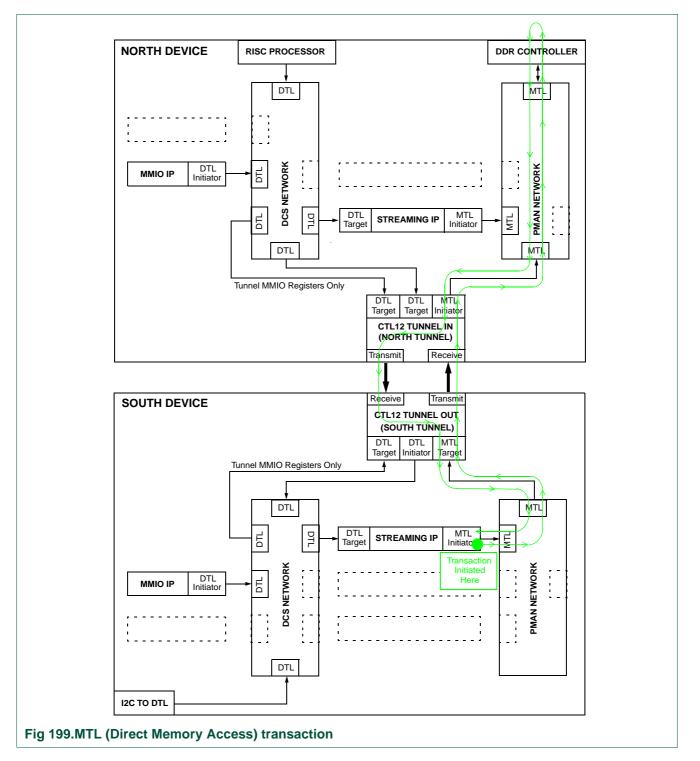

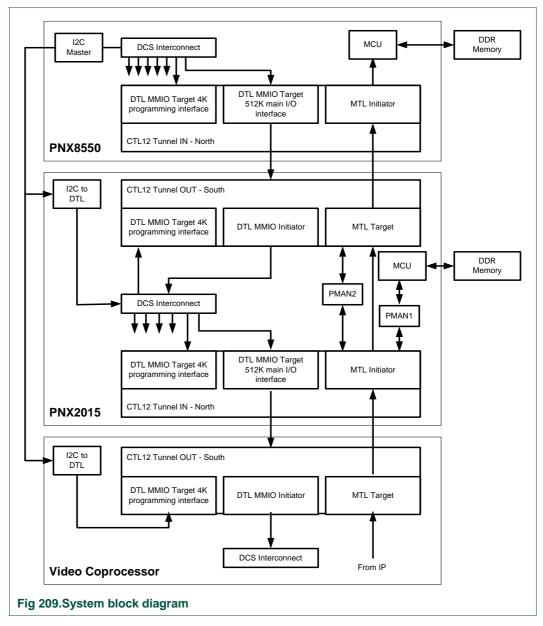

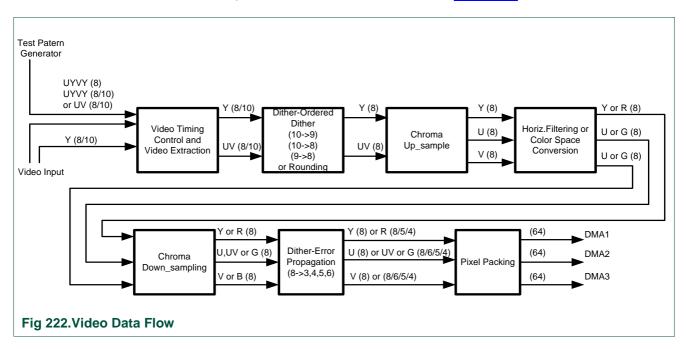

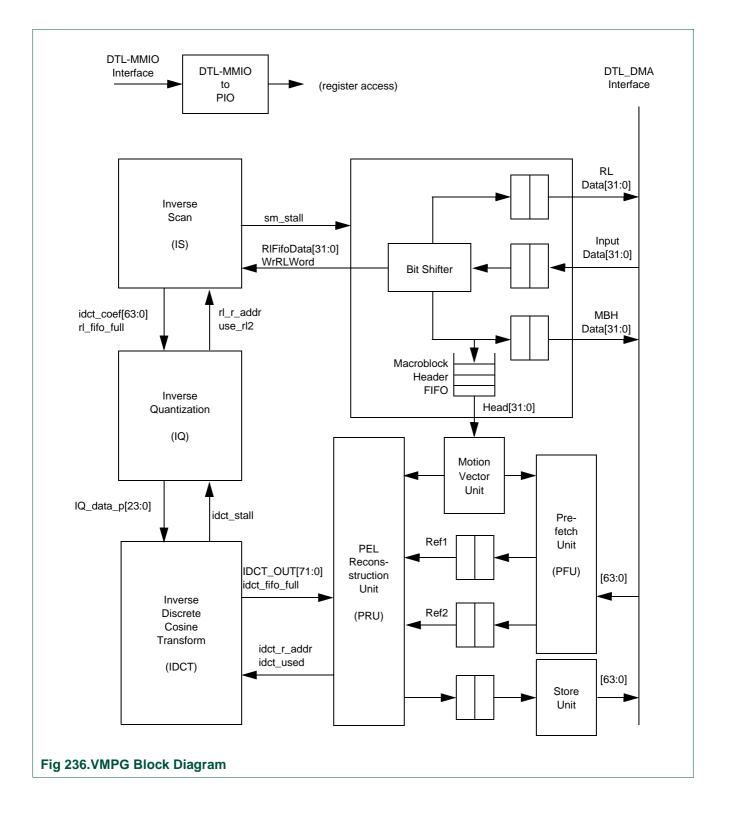

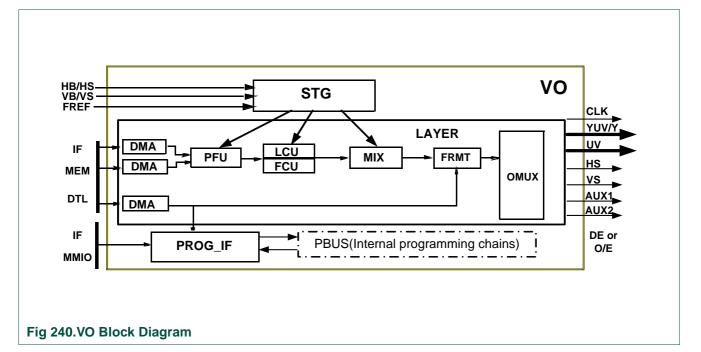

The HD subsystem performs MPEG video decoding for up to MP@HL streams. It interfaces with PNX8550 and video coprocessor via tunnel interfaces (high bandwidth, low pin count interface), HD/SD video using DV4 and DV5 inputs and PNX8550 using DV1, DV2 and DV3 outputs.

The HD subsystem can also perform horizontal and vertical scaling of video images, and perform a range of video measurements on a stream.

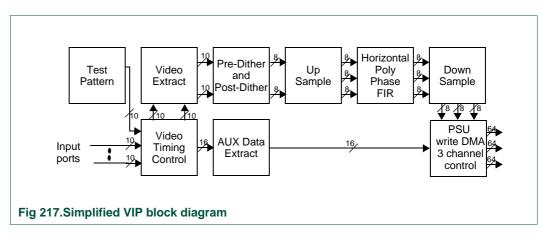

A functional block diagram of the HD subsystem is shown in Figure 164.

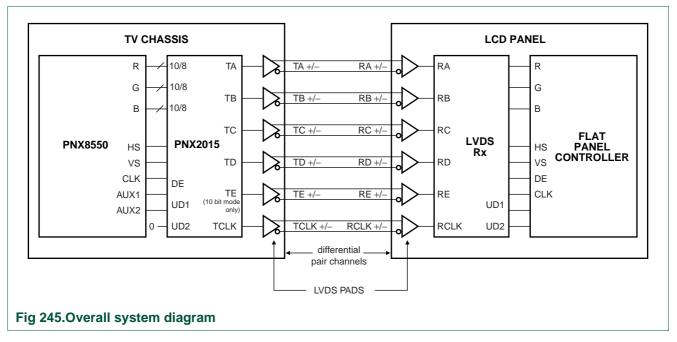

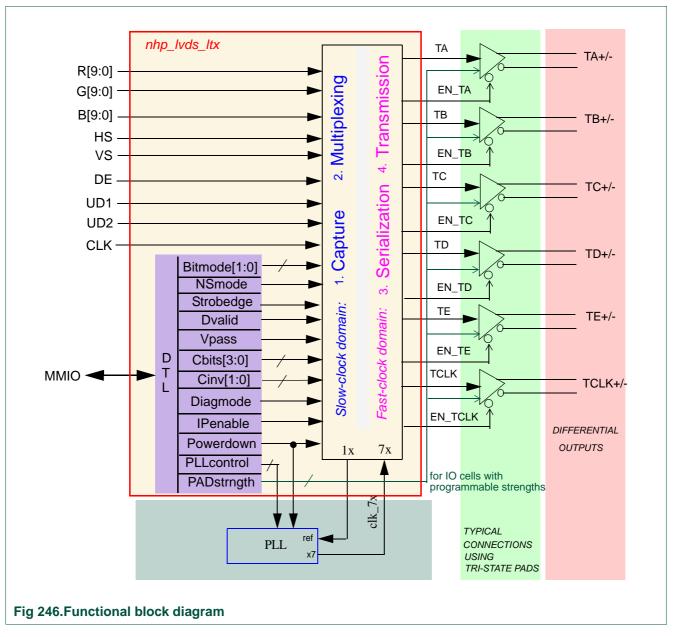

#### 2.5.4 LVDS transmission interface

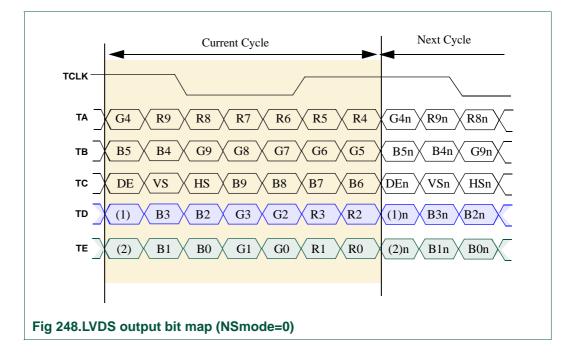

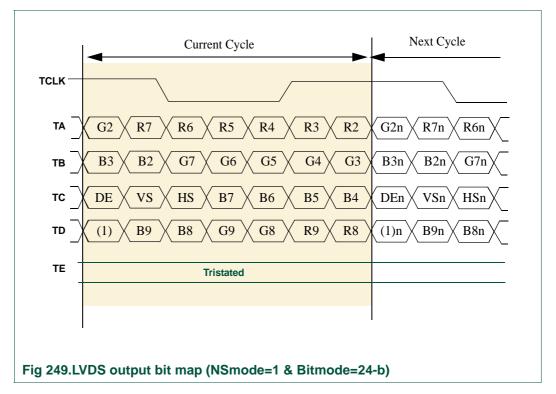

The LVDS transmission interface connects to compatible LCD and flat panel displays. The block uses the LVDS technology as per the TIA/EIA standard. The protocol for video output encoding is selectable and can be THine<sup>™</sup> or National<sup>™</sup> semiconductors format.

The following features are supported in the LVDS transmitter IP:

• Single-link transmission of RGB video pixel data.

Up to 30 bits of RGB pixel data, synchronization signals (HS and VS), data valid indication signal (DE), and up to two user-defined control bits (UD1 and UD2) sampled at the input using a 13.5 MHz to 86 MHz input clock.

- Transmission of two user defined control bits with four selectable values for each bit.

- Either 30, 24 or 18 bpp (i.e. 10, 8 or 6 bits-per-component) selectable video data transmission formats.

- Selectable polarity for the data valid (DE) input signal programmable high or low level to designate (qualify) active video data.

- Support for selectable output transmission formats:

National<sup>™</sup> semiconductor and THine<sup>™</sup> formats for 18, 24 and 30 bits per pixel.

- Optional substitution of invalid pixel data by zero (RGB) values.

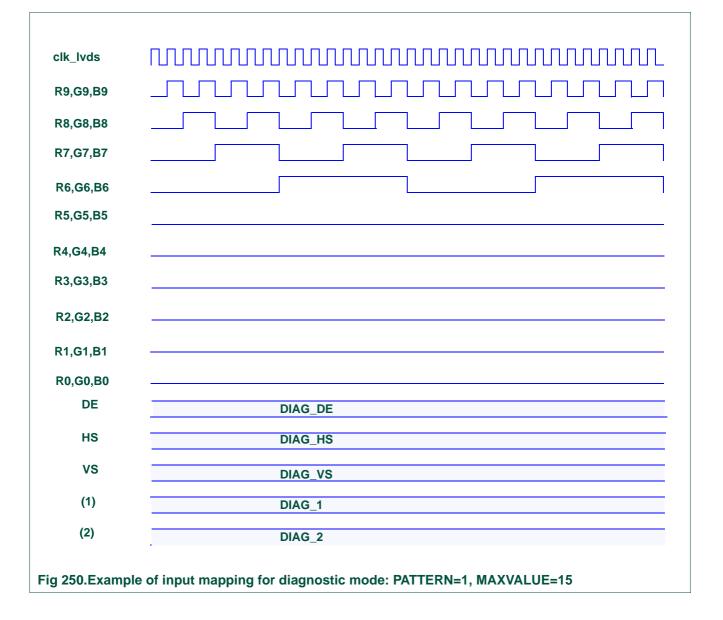

- Selectable diagnostic modes (stress test and pattern test).

- Selectable clock strobe positive or negative edge of the clock for input data sampling.

An example of a system set-up is shown in Figure 245.

#### 2.5.5 TV Microcontroller

The TV Microcontroller is the system power controller and supports the following functions:

- System power management; control and detection of power supplies.

- User interfacing via keyboard or remote control.

- Communication with external sources via AV\_LINK <u>Ref. 4</u>.

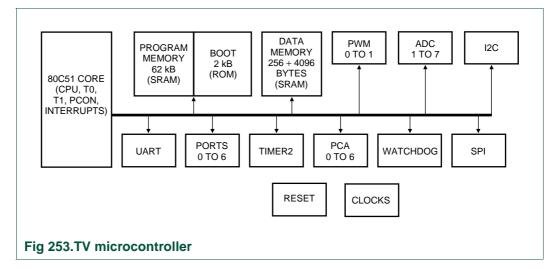

The TV Microcontroller subsystem consists of an 80C51 core, together with extended memory and peripherals required for TV systems.

The TV Microcontroller is isolated from the other (Main) subsystems within the PNX2015, having its own power domain with 1.2 V and 3.3 V supplies, together with separate clocking and reset. This allows the TV Microcontroller to be active while all other subsystems are inactive, by either clock being disabled, or powered down, or by being held indefinitely in reset as shown in Table 9.

| Table 9:         Power supply connections for standby and other subsystem power saving | modes |

|----------------------------------------------------------------------------------------|-------|

|----------------------------------------------------------------------------------------|-------|

| Signal/Supply description | Signal/Supply Pin<br>name | Power down<br>(Standby) | Clk disabled<br>(27MHz) | Indefinite Reset | Main PNX2015<br>Operational |

|---------------------------|---------------------------|-------------------------|-------------------------|------------------|-----------------------------|

| 3.3V Main                 | VDDD3.3V                  | Not powered             | Powered                 | Powered          | Powered                     |

| 2.5V Main                 | VDDD2.5V                  | Not powered             | Powered                 | Powered          | Powered                     |

| 1.2V Main                 | VDDD1.2V                  | Not powered             | Powered                 | Powered          | Powered                     |

| 27 MHz CLK                | XTALI                     | Disabled                | Disabled                | Enabled          | Enabled                     |

| Reset Main (active low)   | RESET_IN                  | Low                     | Low                     | Low              | High                        |

| 3.3V Micro                | VDDD(MCIO)                | Powered                 | Powered                 | Powered          | Powered                     |

| 1V2 Micro                 | VDDD(MC_CORE)             | Powered                 | Powered                 | Powered          | Powered                     |

| Reset Micro (active high) | MC_Reset                  | Low                     | Low                     | Low              | Low                         |

The above table is the only legal reference to Power Down modes. This table supersedes all other imported IP references to Power Down modes that may be embedded within the User Manual. Any references outside of this table should be considered illegal. The Standby and Power Down modes embedded in IP blocks should not be used.

A functional block diagram is shown in Figure 253.

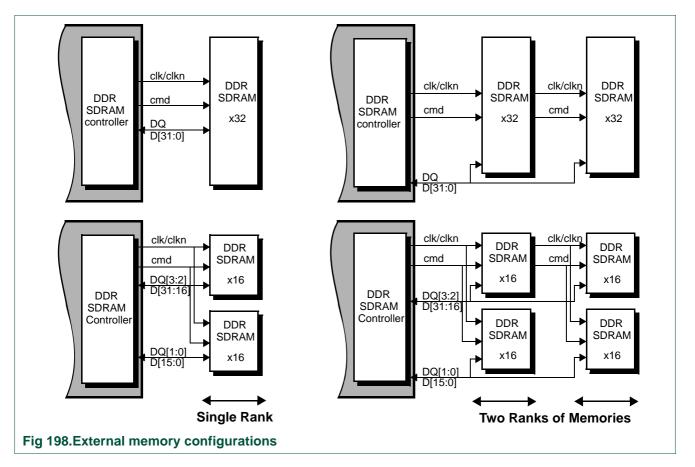

#### 2.6 External memory requirements

The PNX2015 requires two external memories:

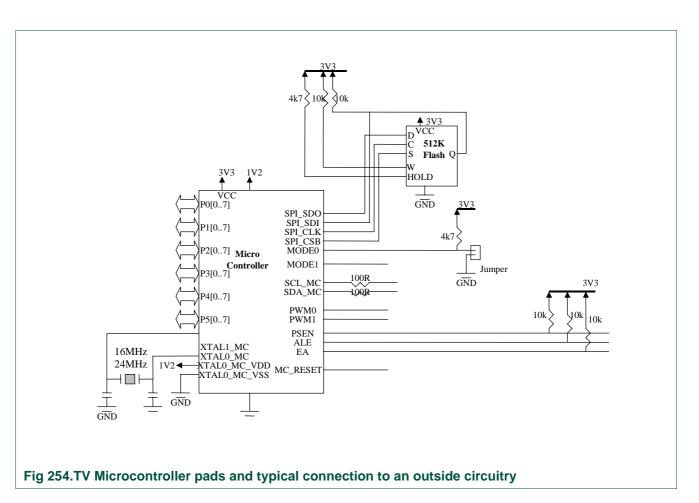

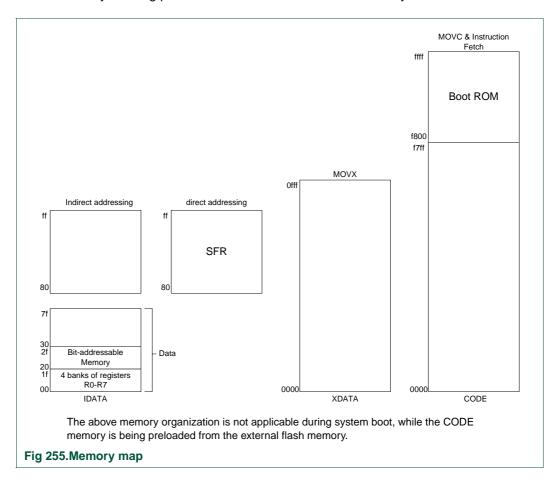

- 512 k bit (64 × 8) SPI Flash connected to the TV Microcontroller via the Motorola SPI<sup>™</sup> interface. This enables the Microcontroller to download code during the initial boot sequence. The SPI is a master only, and cannot be used in slave mode. (See Section 7.14.3).

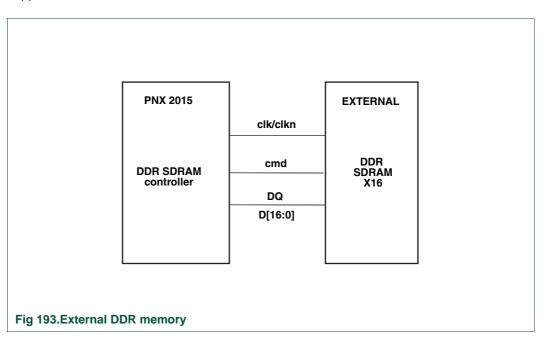

- 64 Mbits, 128 Mbits or 256 Mbits (8 MB, 16 MB or 32 MB) DDR<sup>1</sup> SDRAM connected to the DDR memory controller interface. See memory controller <u>Section 5.1.14</u>.

## 2.7 Power management

The PNX2015 has two separate power domains for the device. The first is for the TV Microcontroller subsystem the second is for the remaining AVIP, Columbus and HD subsystems. There are various modes with associated levels of power dissipation for the PNX2015. The following lists the modes in increasing level of power consumption.

#### Mode 1

Power is applied to the TV Microcontroller only. The TV Microcontroller is running from the 16 (or 24) MHz XTAL. All TV Microcontroller functions are available.

#### Mode 2

27 MHz clock is applied to the system and all subsystems are active.

#### 2.7.1 Power supply sequencing

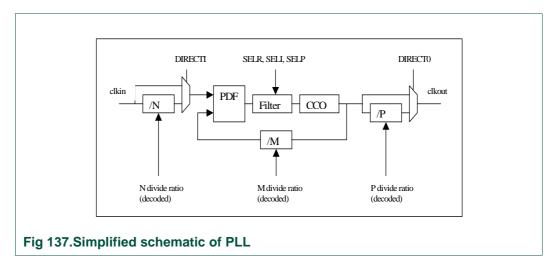

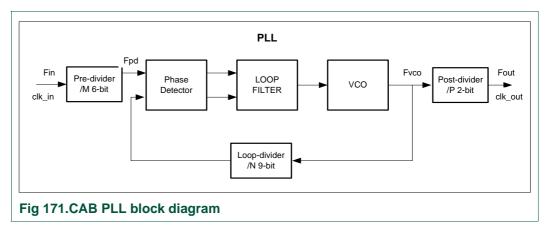

On power-up, the clock module will output all clocks to modules, defaulting to the 27 MHz xtal\_clk clock. Reset of all modules and the boot-up sequence executed by the Boot block will run on the 27 MHz clock. During boot up the boot block will program all PLLs with their operating frequencies. After the 300 us PLL settling time, the boot block will set the exit\_reset registers for these clocks and the clock module will switch these bus clocks from 27 MHz xtal\_clk to their individual frequencies.

#### **Power ON sequence**

- 1. Apply power to  $V_{DDD1.2V}$ .

- 2. Allow  $V_{DDD1.2V}$  to stabilize (approx.100 ms).

- 3. Apply power to  $V_{DDD2.5V}$ .

- 4. Apply power to  $V_{DDD3.3V}$ .

When the power supply to the TV Microcontroller is applied first, the same ordering of power supply sequence is used; firstly for the TV Microcontroller and subsequently the remainder of the PNX2015.

#### **Power OFF sequence**

- 1. Power may be removed simultaneously from  $V_{DDD3.3V}$ ,  $V_{DDD2.5V}$  and  $V_{DDD1.2V}$ .

- 2. Otherwise, remove  $V_{DDD3.3V}$  followed by  $V_{DDD2.5V}$  and  $V_{DDD1.2V}$ .

<sup>1.</sup> For frequencies equal to or below 200Mhz use DDR, for frequencies above 200MHz GDDR should be used.

**Remark:** If supply sequencing is used and other parts of the system are powered ahead of the PNX2015, it is important to ensure that the 3.3 V supply to the PNX2015 is cleanly applied. i.e. no back-feeding of 3.3 V supply from other devices (or higher voltage rails that are powered first). This can occur with pull-ups or termination resistors to a system 5 V supply (e.g.  $I^2C$ ) or to an inappropriate 3.3 V rails.

#### 2.7.2 Low-power modes

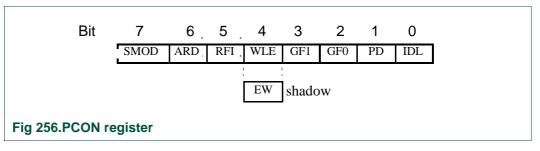

The TV Microcontroller has two power-saving modes: Idle and Power-down, which are controlled by the PCON SFR. AVIP blocks are put into a low-power standby mode by disabling all PLLs. See <u>Section 3.10.9.2</u>.

# 3. AVIP1 and AVIP2

## 3.1 Introduction

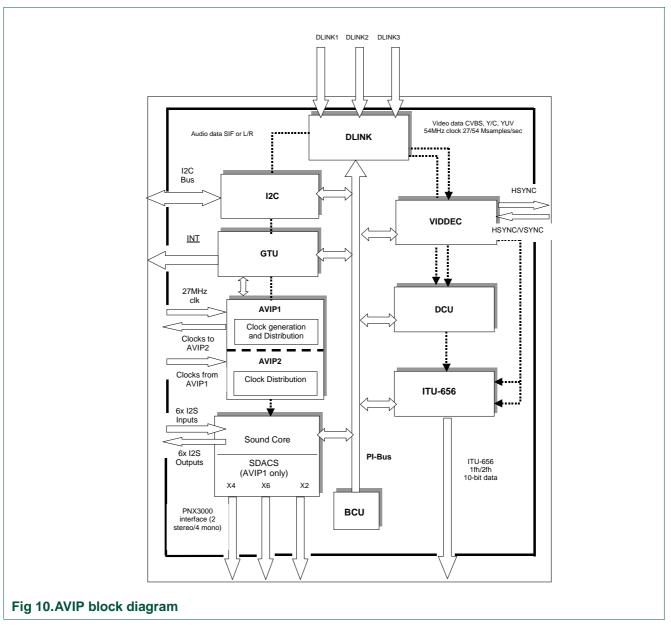

Figure 10 shows a diagram of the AVIP block.

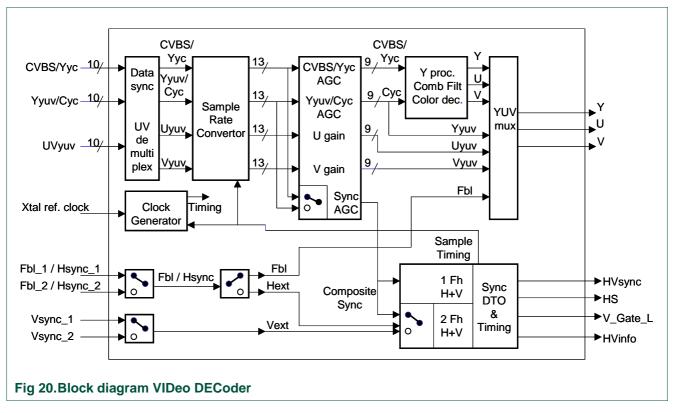

Each AVIP provides the following functionality:

- Detection of PAL, NTSC or SECAM, and various 1f<sub>H</sub> and 2f<sub>H</sub> component video input sources.

- Full support for  $1f_H$  and  $2f_H$  video sources; progressive and interlaced.

- Decoding for global VBI Standards (WST, WSS, VPS, CC, VITC).

- ITU-656 output interface.

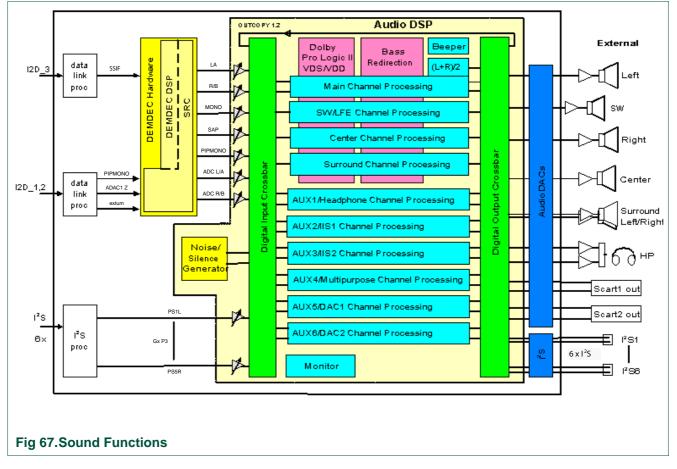

- Global multi-standard audio demodulation and decoding.

- Dolby<sup>®</sup> Pro Logic<sup>®</sup> II multi-channel audio decoding and post-processing.

- Advanced fully programmable audio post-processing functions, including psychoacoustic spatial algorithms for optimal loudspeaker matching.

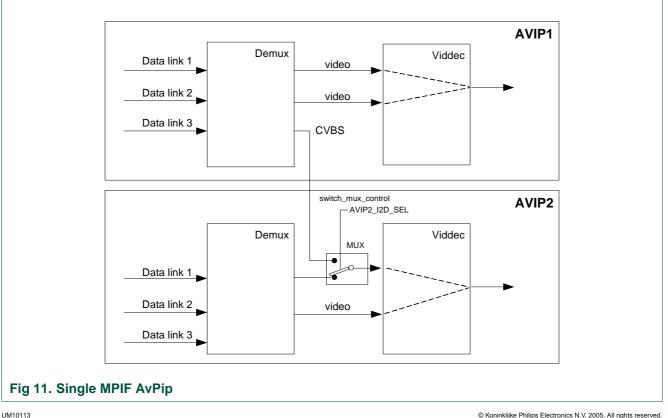

### 3.2 Dual AVIP configuration in PNX2015

The AVIP1 sub system has the following differences compared to the standalone PNX2000.

- Fixed I<sup>2</sup>C Address. Refer to <u>Table 12</u>

- Restricted I<sup>2</sup>S input and Output capability. Refer to <u>Section 2.3.2</u>.

- Provides clocking sources for AVIP2

The AVIP2 sub system has the following differences compared to the standalone PNX2000.

- Fixed I<sup>2</sup>C Address. Refer to <u>Table 12</u>

- Restricted I<sup>2</sup>S input and Output capability. Refer to <u>Section 2.3.2</u>

- No dedicated PLL/Clock source, slaved from AVIP1

- No dedicated DACs, shared with AVIP1

AVIP modules are IP blocks.

To utilize a single MPIF AvPip mode, the AVIP2 incorporates a video mux controlled by register bit AVIP2\_I2D\_SEL.

## 3.3 Functional specification

#### 3.3.1 Overview of functional partitioning

Table 10 shows the major functions mapped to hardware blocks (Figure 10).

| Table 10: Major functions |                  |                                                               |  |  |  |

|---------------------------|------------------|---------------------------------------------------------------|--|--|--|

| Function                  | Block            | Description                                                   |  |  |  |

| High speed data-link      | DLINK            | Receives data in 3 streams from PNX3000                       |  |  |  |

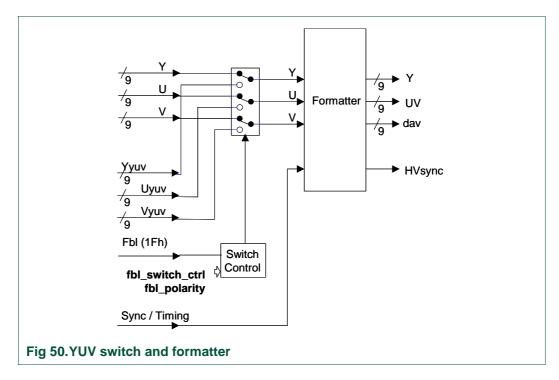

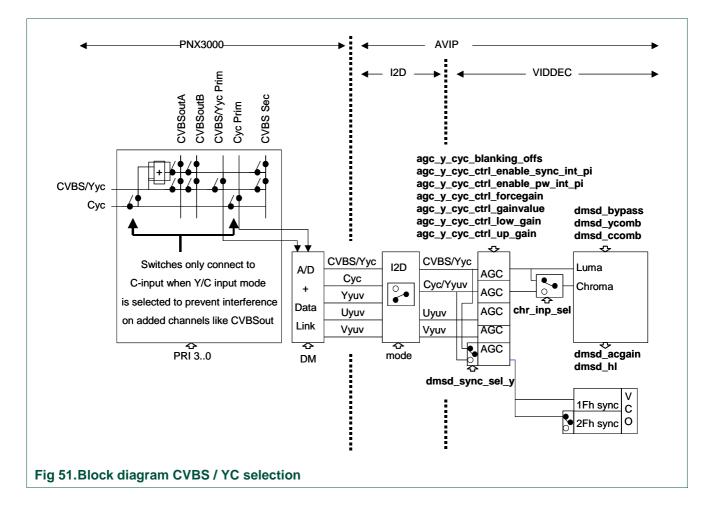

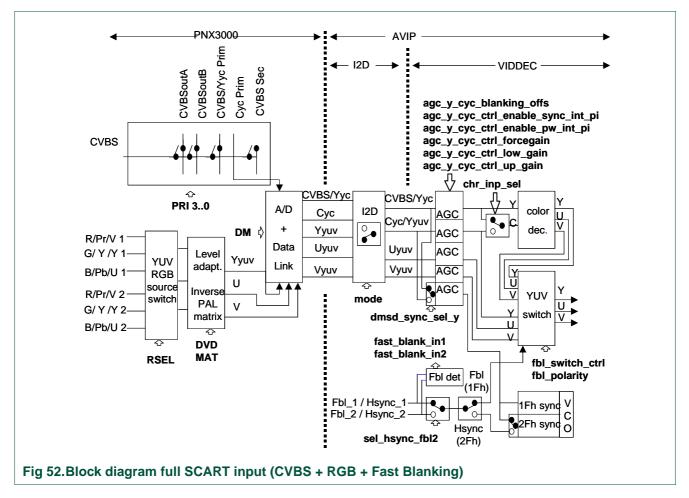

| Video decoder processor   | VIDDEC           | Decodes and processes CVBS, YUV or Y/C in YUV stream          |  |  |  |

| Serial interface          | l <sup>2</sup> C | To access all the internal registers                          |  |  |  |

| Global Task Unit          | GTU              | Generates all the internal clocks, Reset and Power management |  |  |  |

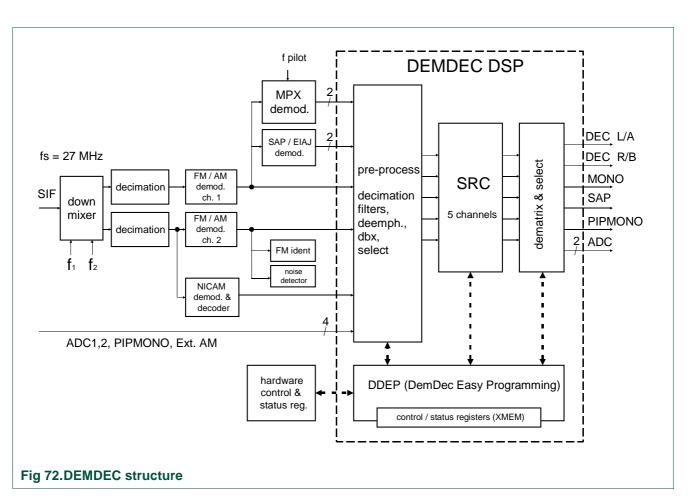

| TV sound decoder          | DEMDEC DSP       | Demodulation, decoding of terrestrial TV audio standards      |  |  |  |

| Audio processor           | AUDIO DSP        | Processing analogue and digital audio sources                 |  |  |  |

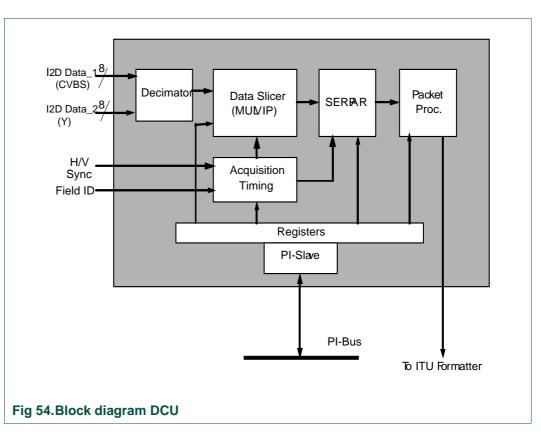

| Data Capture Unit         | DCU              | Acquires VBI data (Teletext, CC, VPS) and formats in a stream |  |  |  |

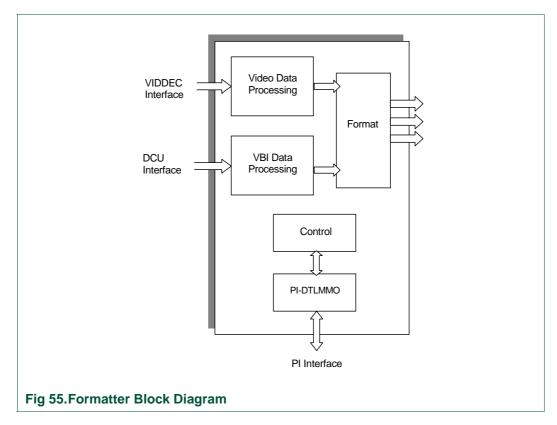

| Formatter unit            | ITU-656          | Formats YUV, VBI data and CVBS data in ITU-656                |  |  |  |

| Bus Control Unit          | BCU              | Bus arbitration among all the internal blocks                 |  |  |  |

#### 3.3.2 AVIP interfaces

#### Table 11: Interfaces

| Interface        | Description                                                                                                                                                                                                                                                                                                                          |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I <sup>2</sup> C | Each AVIP is controlled using I <sup>2</sup> C. It performs like an I <sup>2</sup> C to PI bridge, i.e. translates I <sup>2</sup> C-slave received commands to PI master commands.                                                                                                                                                   |

| DLINK            | Receives data in three streams from PNX3000.                                                                                                                                                                                                                                                                                         |

| l <sup>2</sup> S | Serial digital audio interface (6 stereo inputs and 6 stereo outputs) for connection to other devices that support the I <sup>2</sup> S standard. Are used to receive decoded sound from a multi-channel digital audio decoder, provide additional ADCs and DACs, or loop audio signals through an external processor or delay line. |

| ITU656           | Mainly intended to transfer output data streams externally to the PNX8550, but may also be read by other ITU 656 input devices that implement data valid signalling.                                                                                                                                                                 |

| DACS             | Digital-analogue converters used to generate analogue outputs from Sound Core                                                                                                                                                                                                                                                        |

#### 3.3.3 AVIP features

#### 3.3.3.1 Video features

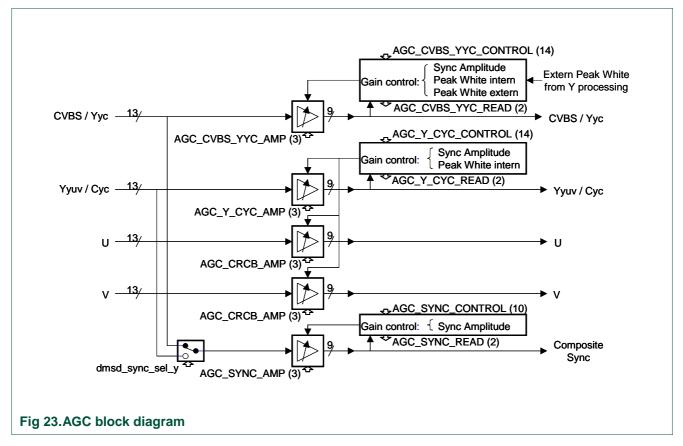

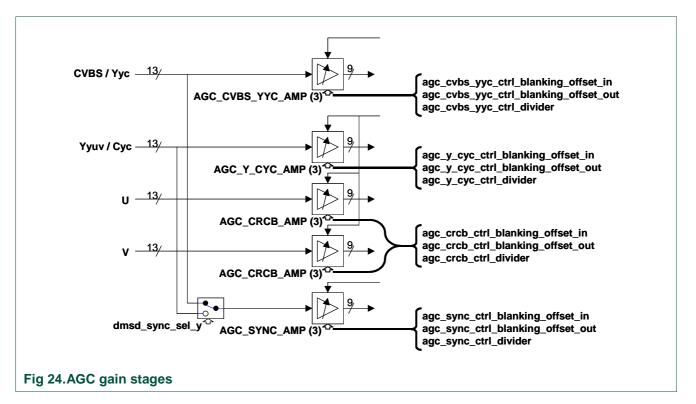

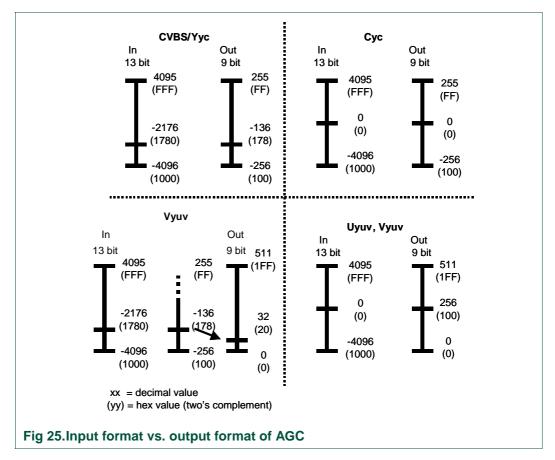

- Automatic Gain Control (AGC) to correct amplitude errors at input source.

- Synchronisation identification (used for channel search).

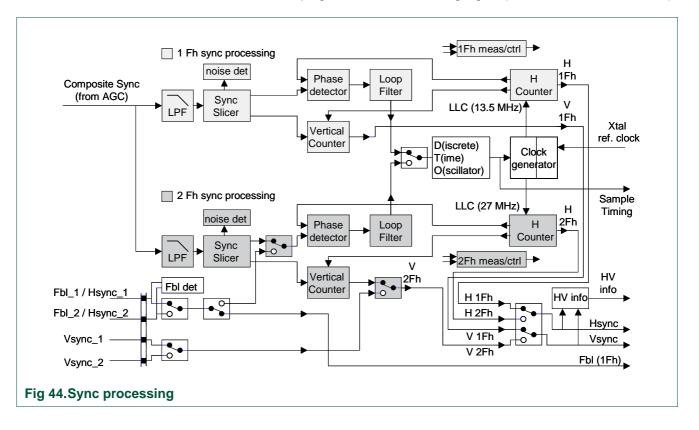

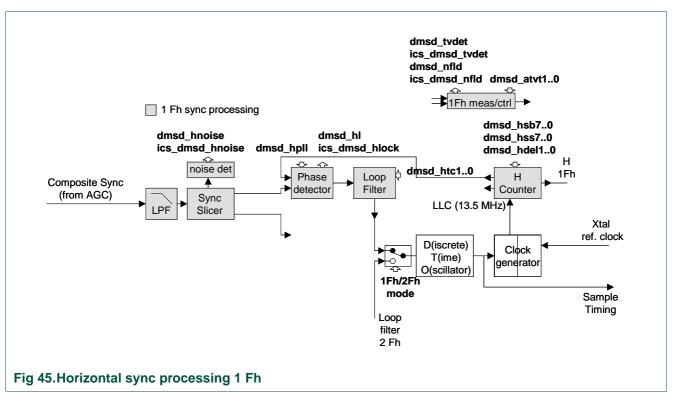

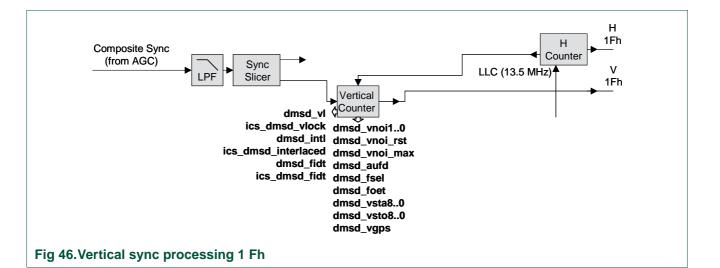

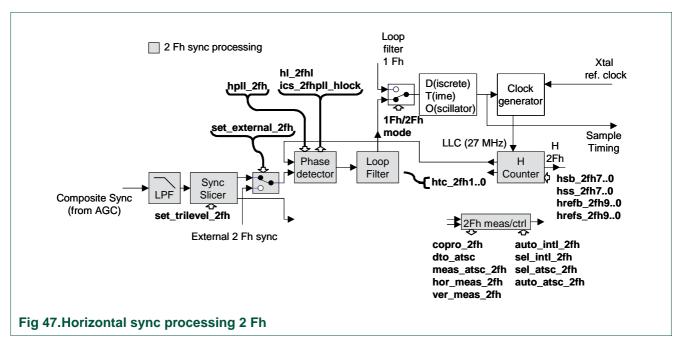

- Sync processing for 1FH and 2FH video input source.

- Standard detection of PAL, NTSC or SECAM and various 1FH/2FH component video input sources.

#### 1FH video

• Color decoding (ITU-601) for PAL, NTSC or SECAM input sources.

- 2D comb filter.

- Supports component video sources with sync on CVBS or green.

- Fastblank insertion of RGB signals onto CVBS input.

#### 2FH video

- Supports various progressive and interlaced component video sources.

- Synchronisation of video sources with sync on Y or external H/V inputs.

#### VBI data capture

- Decodes 525 line standards WST, WSS, VPS, CC, VITC.

- Decodes 625 line standards WST, WSS, CC, VITC.

#### ITU656 output interface

- Video and VBI formatted into an ITU-style output data stream, compliant to ITU-656/1364 REF [10] (exception being the use of a data valid signal).

- Interfaces to PNX8550 IC.

- Supports CVBS/C mode to interface to external picture improvement devices.

#### 3.3.3.2 Audio features

#### Demodulator and decoder

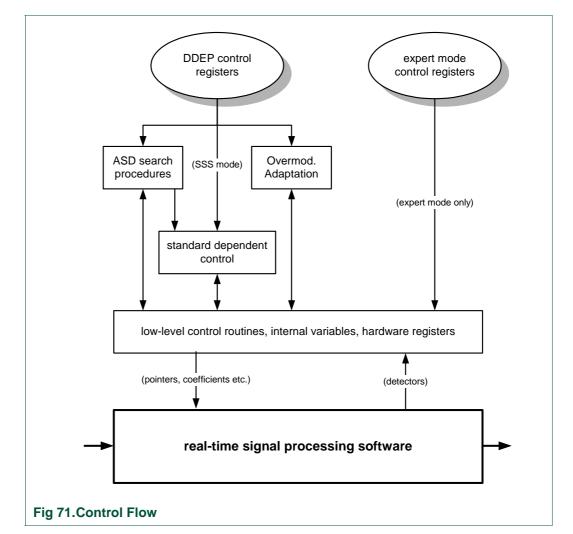

- Demodulator and Decoder Easy Programming (DDEP)

- Auto standard detection (ASD)

- Static Standard Selection (SSS)

- DQPSK demodulation for different standards, simultaneously with 1-channel FM demodulation

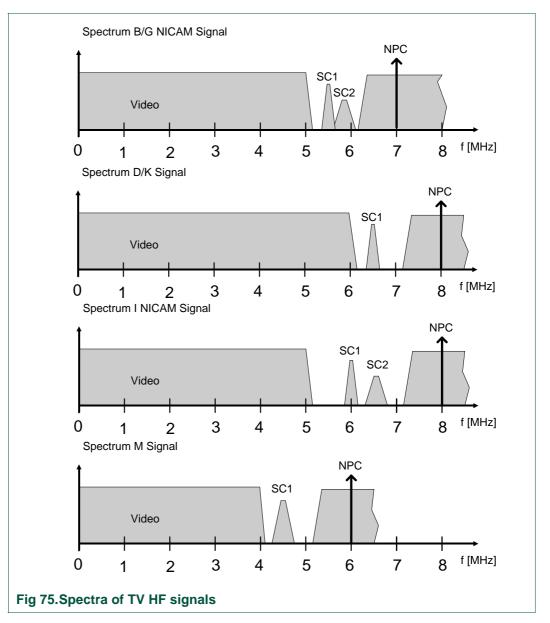

- NICAM decoding (B/G, I, D/K and L standard)

- Two-carrier multistandard FM demodulation (B/G, D/K and M standard)

- Decoding for three analogue multi-channel systems (A2, A2+ and A2\*) and satellite sound

- Adaptive de-emphasis for satellite FM

- Optional AM demodulation for system L, simultaneously with NICAM

- Identification A2 systems (B/G, D/K and M standard) with different identification time constants

- FM pilot carrier present detector

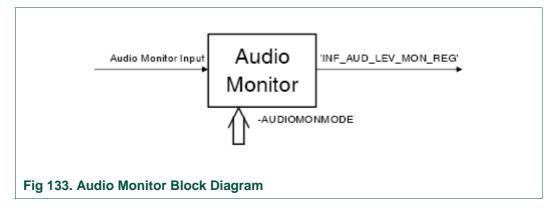

- Monitor selection for FM/AM DC values and signals, with peak and quasi peak detection option

- BTSC MPX decoder

- SAP decoder

- dbx noise reduction

- Japan (EIAJ) decoder

- FM radio decoder

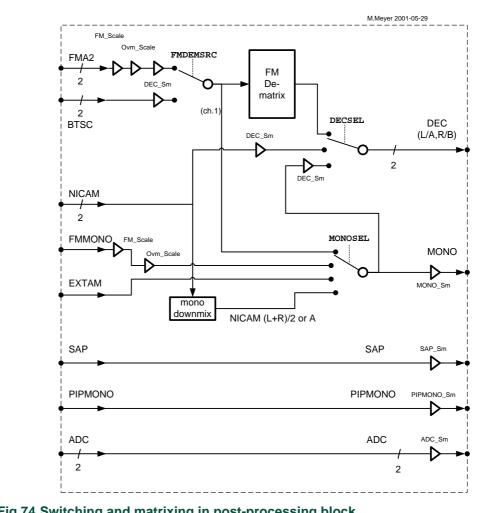

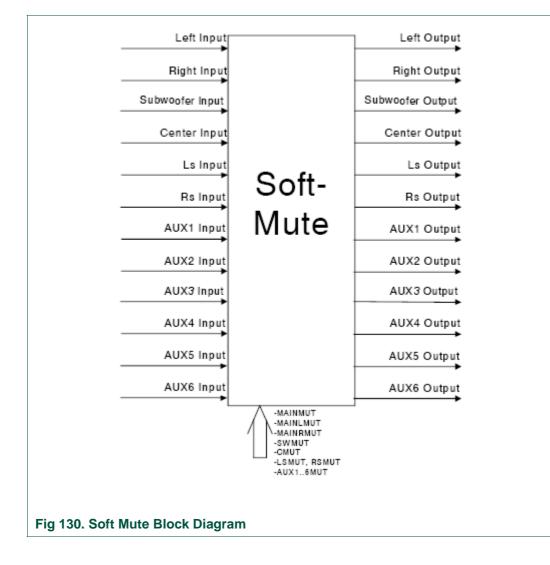

- Soft-mute for DEMDEC outputs DEC, MONO and SAP

- · FM overmodulation adaptation option to avoid clipping and distortion

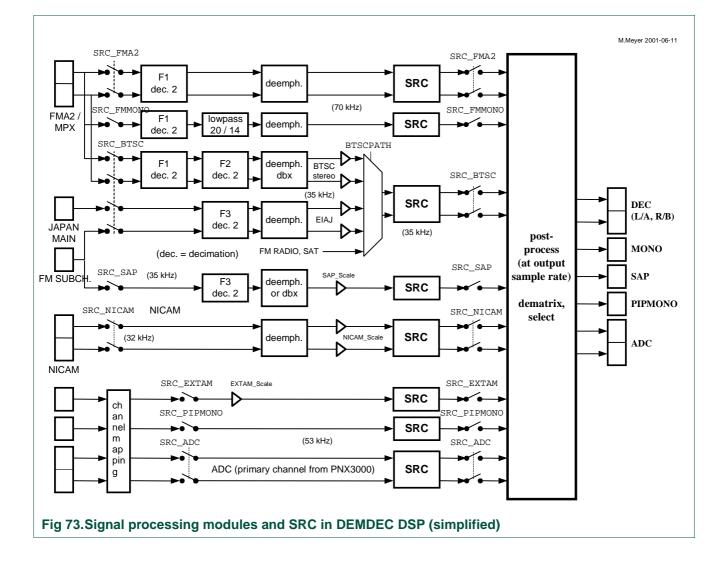

- Sample rate conversion (SRC) for up to three demodulated terrestrial audio signals. It is possible to process SCART signals together with demodulated terrestrial signals.

#### Audio multi-channel decoder

- Dolby® Pro Logic® II Surround (DPL2); Trademark of Dolby Laboratories Licensing Corporation.

- Six channel processing for Main Left and Main Right, Subwoofer, Center, Surround Left and Surround Right.

#### Volume and tone control

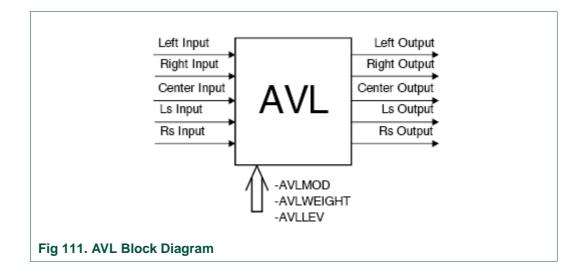

- Automatic Volume Level (AVL) control

- Smooth volume control

- Master volume control and Balance

- Soft-mute

- Loudness

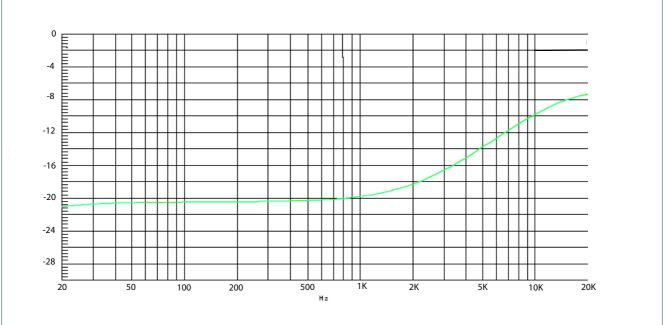

- Bass, Treble

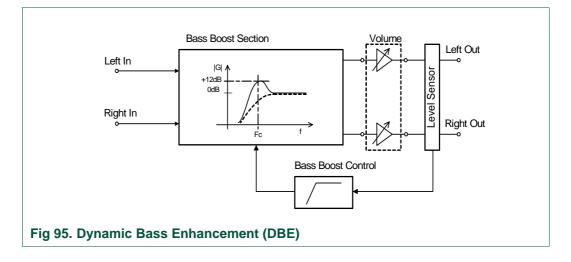

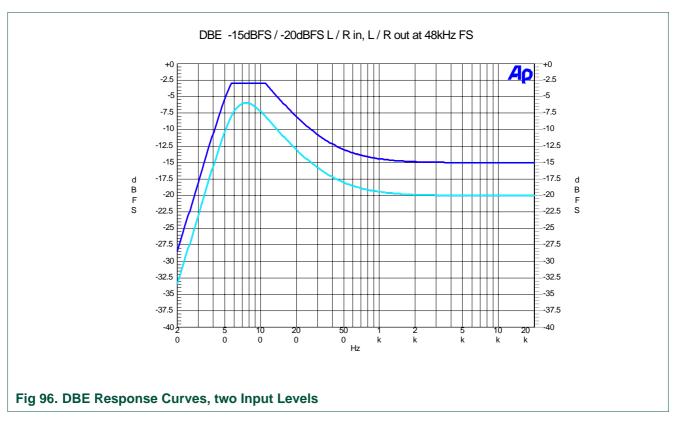

- Dynamic Bass Enhancement (DBE)

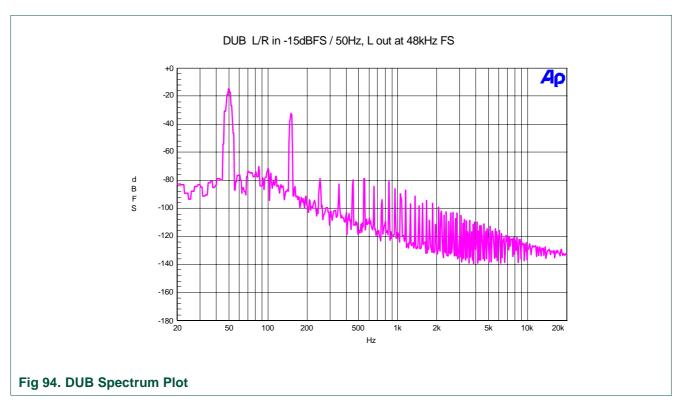

- Dynamic Ultra Bass (DUBII)

- Non processed subwoofer

- 5 band equalizer

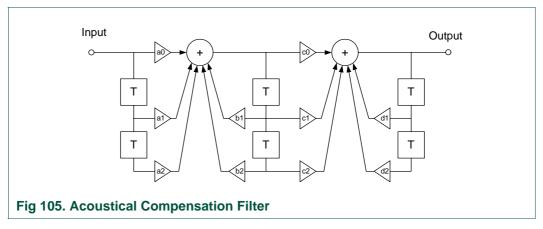

- Acoustical compensation

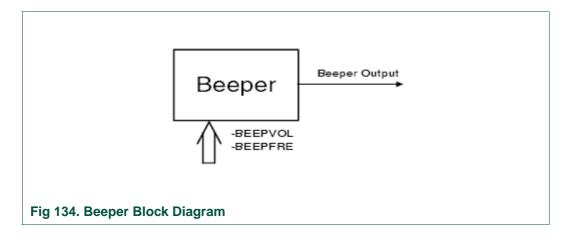

- Programmable beeper

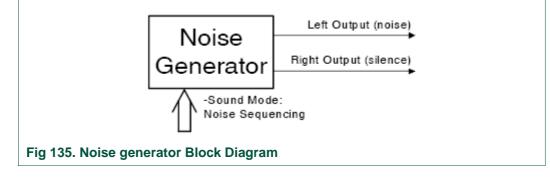

- Noise generator for loudspeaker level trimming

#### **Reflection and delay**

- Dolby® Pro Logic® Delay

- Pseudo hall/matrix function

#### Psychoacoustic spatial algorithms, downmix and split

- Incredible Mono

- Incredible Stereo

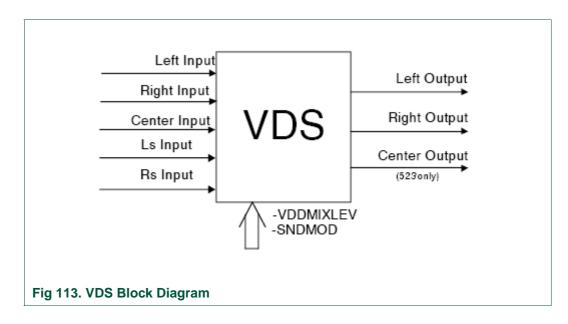

- Virtual Dolby® Surround (VDS 522,523)

- Virtual Dolby® Digital (VDD 522,523)

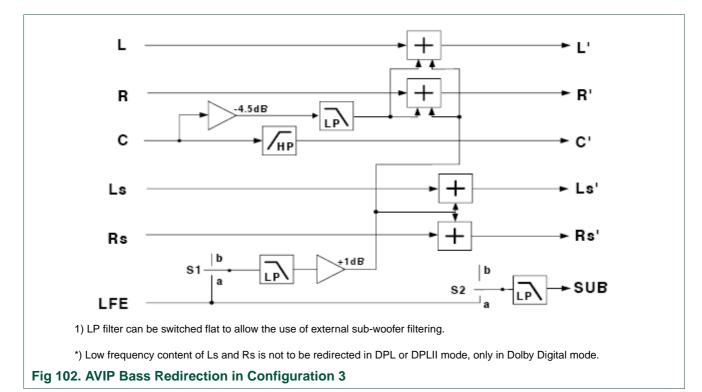

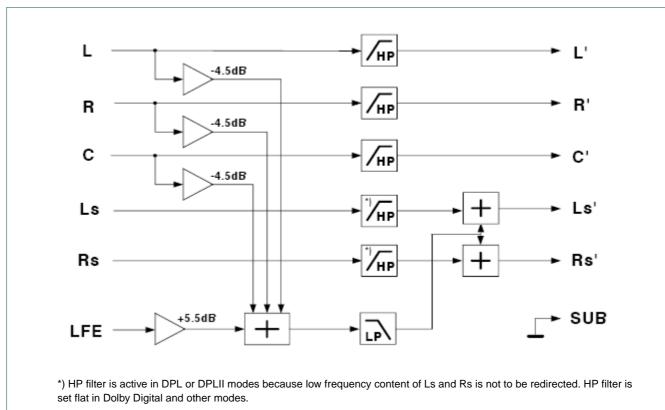

- Bass Redirection according to Dolby specifications

#### Interfaces and switching

- Digital audio input interface (stereo I<sup>2</sup>S input interface)

- Digital audio output interface (stereo I<sup>2</sup>S output interface)

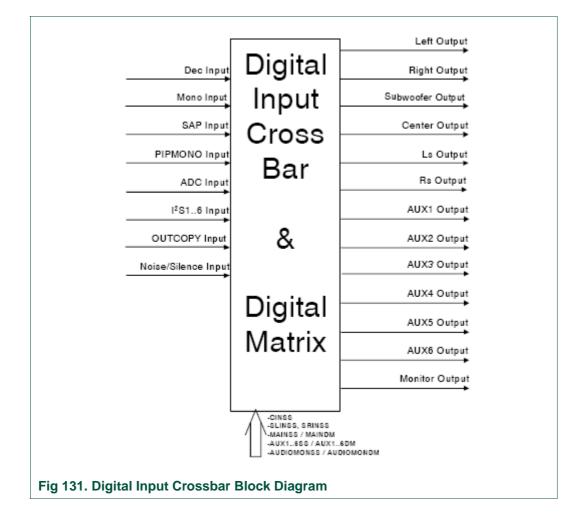

- Digital crossbar switch for all digital signal sources and destinations

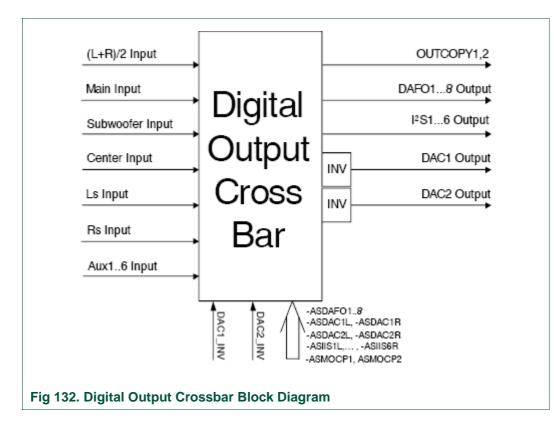

- Output crossbar for exchange of channel processing functionality

- Audio monitor for level detection

- 8 audio DACs for six channel loudspeaker outputs and stereo headphones output

- 4 audio DACs for stereo SCART output and stereo LINE output.

- Serial data link interface for interfacing with the analogue multi-purpose interface IC PNX3000.

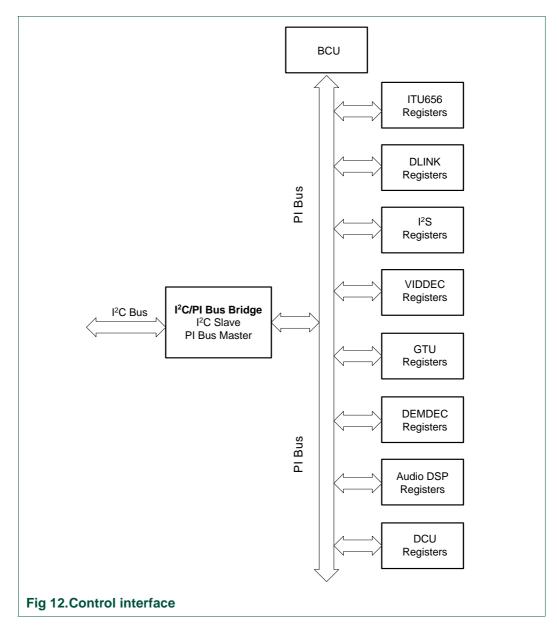

# 3.4 Control interface

#### 3.4.1 AVIP control interface

The AVIP blocks are controlled via an I<sup>2</sup>C interface. Internally, an I<sup>2</sup>C-to-PI Bus bridge converts I<sup>2</sup>C accesses into read and write transactions on the internal PI. This PI provides access to the control and status registers for all the modules in the AVIP design. The operation of the internal PI bus is controlled by the BCU block.

UM10113

25 of 795

# UM10113

PNX2015 User Manual

#### 3.4.2 I<sup>2</sup>C interface

### 3.4.2.1 I<sup>2</sup>C features

The I<sup>2</sup>C module has the following features:

- 7-bit I<sup>2</sup>C slave address.

- LSB of I<sup>2</sup>C address selectable from external pin, to allow two AVIP blocks to coexist on a shared I<sup>2</sup>C.

- PI Bus data width 32 bits.

- PI bus address width 32 bits.

- I<sup>2</sup>C data transmitted in big endian format (MSB transmitted first).

- Up to 400 kHz I<sup>2</sup>C speed.

#### 3.4.2.2 AVIP I<sup>2</sup>C address

#### Table 12: AVIP I<sup>2</sup>C address

| Block | Sub-address  | Sub-address width | Data width |

|-------|--------------|-------------------|------------|

| AVIP1 | 8A(W), 8B(R) | 32-bit            | 32-bit     |

| AVIP2 | 88(W), 89(R) | 32-bit            | 32-bit     |

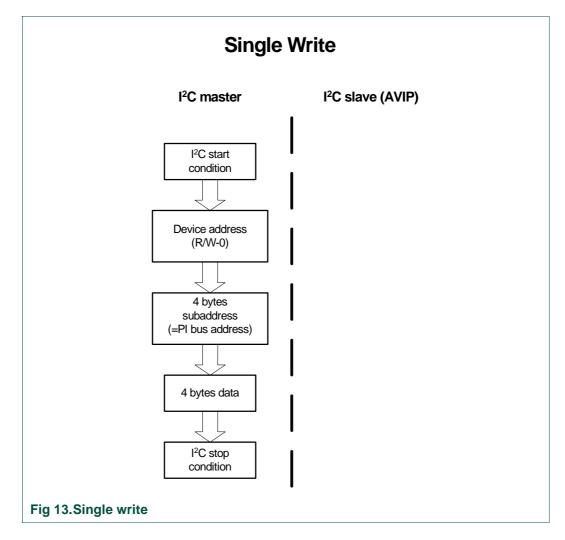

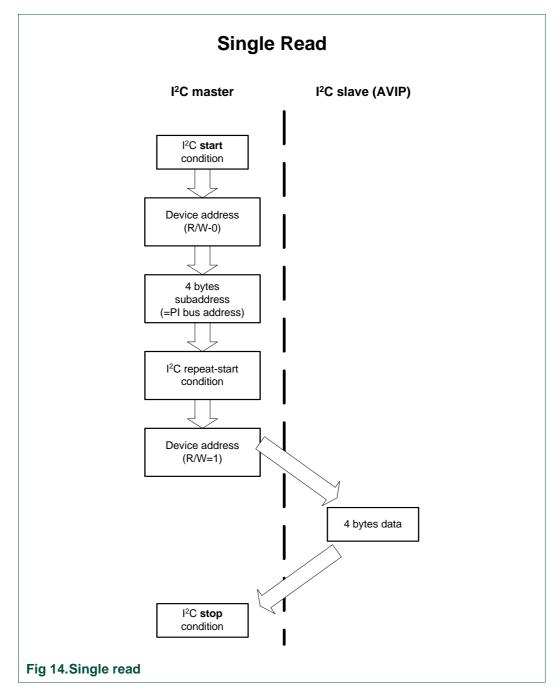

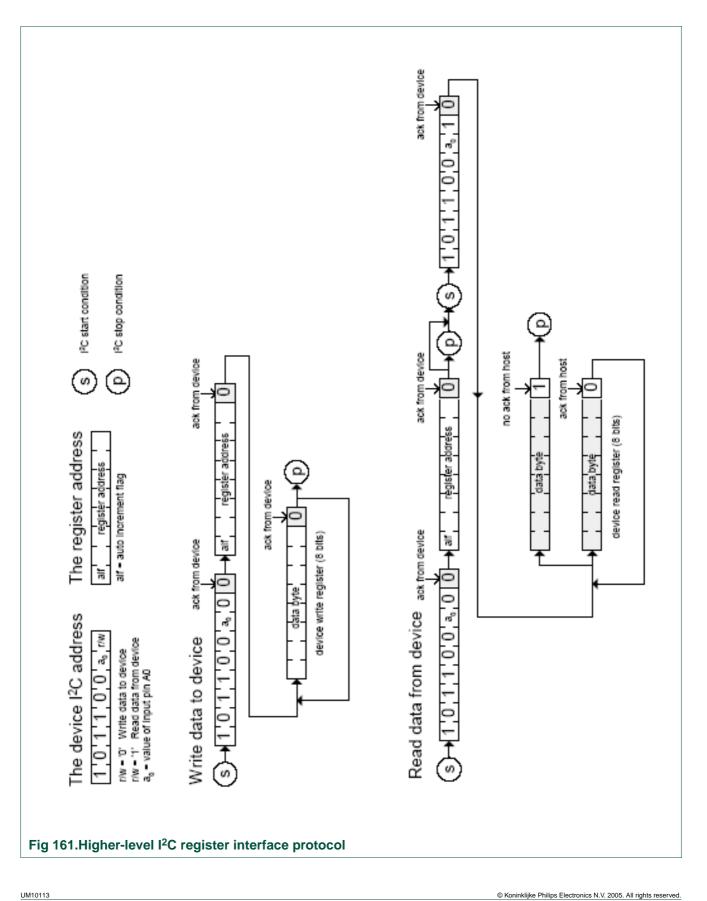

#### 3.4.2.3 I<sup>2</sup>C register access protocol

The following diagrams illustrate the procedure used to access register locations over the  $\ensuremath{I^2C}$  .

PNX2015 User Manual

#### 3.4.2.4 I<sup>2</sup>C interface block

The I<sup>2</sup>C interface module contains no software-accessible status or configuration registers.

If the internal PI locks up, the I<sup>2</sup>C interface will lock the external I<sup>2</sup>C bus by holding the SCL signal low. The only way to break the lock-up is to reset the entire AVIP block. In order to avoid this condition, the BCU timeout register must be configured by software early in the AVIP initialization process.

The AVIP I<sup>2</sup>C module will not respond to a 'general call' on the I<sup>2</sup>C, i.e. when a slave address of 0000000 is sent by a master. In case of any illegal address, transmission of the data that follows is not acknowledged, and the transmission is aborted.

The I<sup>2</sup>C slave devices are capable of operating at a maximum speed of 400 kbits/s in accordance with the I<sup>2</sup>C fast-mode specification.

#### 3.4.3 BCU module

#### 3.4.3.1 BCU features

The BCU module performs the following functions:

- Address space mapping and slave selection

- Bus error notification and logging

- Bus timeout monitoring, with software programmable timeout threshold

- Interrupt generation on bus error and timeout

#### 3.4.3.2 Registers

The BCU contains eight software accessible registers which are listed in the following table. Note that the base address of the BCU is 0x07fe8000.

The "reset" values given in the tables in the following subsections correspond to the state of a variable after PI reset.

| Table 13: | BCO register sum | BCO register summary     |  |  |  |  |

|-----------|------------------|--------------------------|--|--|--|--|

| Address   | Name             | Description              |  |  |  |  |

| 0x0       | INT_STATUS       | BCU interrupt status     |  |  |  |  |

| 0x4       | INT_SET          | BCU interrupt set        |  |  |  |  |

| 0x8       | INT_CLEAR        | BCU interrupt clear      |  |  |  |  |

| 0xC       | FAULT_STATUS     | Bus fault status         |  |  |  |  |

| 0x10      | FAULT_ADDRESS    | Bus fault address        |  |  |  |  |

| 0x14      | INT_ENABLE       | BCU interrupt enable     |  |  |  |  |

| 0x18      | TOUT             | Time-out control         |  |  |  |  |

| 0x1C      | SNOOP            | Memory coherency control |  |  |  |  |

|           |                  |                          |  |  |  |  |

## Table 13: BCU register summary

#### Table 14: PI\_1003\_BCU registers

| Bit     | Symbol                  | Access | Reset value    | Description                                                                                                                                             |  |  |

|---------|-------------------------|--------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Offset  | Offset 0x0 - INT_STATUS |        |                |                                                                                                                                                         |  |  |

| 31:2    | RSD[31:2]               | R      | 0x0000000      | Reserved                                                                                                                                                |  |  |

| 1       | BCU_TO_STATUS           | R      | 0x0            | Time-out status: '0' = no time-out error has occurred.<br>'1' = time-out error has occurred                                                             |  |  |

| 0       | BCU_BE_STATUS           | R      | 0x0            | Bus error status: '0' = no bus error has occurred. Fault logging enabled if BCU_TO=0 and BCU_BE=0; '1' = bus error has occurred, Fault logging stopped. |  |  |

| Offset  | : 0x4 - INT_SET         |        |                |                                                                                                                                                         |  |  |

| 31:2    | RSD[31:2]               | R      | 0xXXXXXXX<br>X | Reserved                                                                                                                                                |  |  |

| UM10113 |                         |        |                | © Koninklijke Philips Electronics N.V. 2005. All rights reserved.                                                                                       |  |  |

29 of 795

PNX2015 User Manual

| Bit       | Symbol                     | Access |                | Description                                                                                                                                                                                             |

|-----------|----------------------------|--------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1         | BCU_TO_SET                 | W      | 0xX            | Write '1' to set Time-Out interrupt; '0' has no effect                                                                                                                                                  |

| 0         | BCU_BE_SET                 | W      | 0xX            | Write '1' to set Bus-Error interrupt; '0' has no effect                                                                                                                                                 |

| Offset    | t 0x8 - INT_CLEAR          |        |                |                                                                                                                                                                                                         |

| 31:2      | RSD[31:2]                  | R      | 0xXXXXXXX<br>X | Reserved                                                                                                                                                                                                |

| 1         | BCU_TO_CLEAR               | W      | 0xX            | Write '1' to clear Time-Out interrupt; '0' has no effect                                                                                                                                                |

| 0         | BCU_BE_CLEAR               | W      | 0xX            | Write '1' to clear Bus-Error interrupt; '0' has no effect                                                                                                                                               |

| Offset    | t 0xC - FAULT_STATUS       |        |                |                                                                                                                                                                                                         |

| 31:1<br>5 | RSD[31:15]                 | R      | 0xXXXXX        | Reserved                                                                                                                                                                                                |

| 14:7      | BCU_MASTER[7:0]            | R      | 0xXX           | Bus master of failed bus operation: 1 = Bus master 0;<br>2 = Bus master 1; 3 = Bus master 2; 4 = Bus master<br>3; &H10 = Bus master 4; &H20 = Bus master 5; &H40<br>= Bus master 6; &H80 = Bus master 7 |

| 6         | BCU_LOCK                   | R      | 0xX            | Lock status of failed bus operation: '0' = LOCK was 0;<br>'1' = LOCK was 1                                                                                                                              |

| 5         | BCU_READ                   | R      | 0xX            | Data direction of failed bus operation: 0 = write operation; 1 = read operation                                                                                                                         |

| 4:0       | BCU_OPC[4:0]               | R      | 0xXX           | Opcode of failed operation                                                                                                                                                                              |

| Offset    | t 0x10 - FAULT_ADDRESS     |        |                |                                                                                                                                                                                                         |

| 31:2      | BCU_ADDR[29:0]             | R      | 0xXXXXXXX<br>X | Address of failed bus operation                                                                                                                                                                         |

| 1:0       | RSD[1:0]                   | R      | 0x0            | Reserved. Returns '0' on read.                                                                                                                                                                          |

| Offset    | t 0x14 - INT_ENABLE        |        |                |                                                                                                                                                                                                         |

| 31:1      | RSD[31:1]                  | R      | 0x0000000      | Reserved                                                                                                                                                                                                |

| 0         | BCU_INT_EN                 | R/W    | 0x0            | '0' = disable BCU interrupt request; '1' = enable<br>interrupt request - an interrupt is generated when<br>BCU_TO and/or BCU_BE flag is set                                                             |

| Offset    | t 0x18 - TOUT              |        |                |                                                                                                                                                                                                         |

| 31:0      | BCU_TO_THRESHOL<br>D[31:0] | R/W    | 0x00000000     | Time-out threshold: '0' = never time-out; '1' = time-out after 1st data cycle in bus operation; , $\ddot{A}$ ¶; 255 = time-out after 256th data cycle in bus operation                                  |

| Offset    | t 0x1C - SNOOP             |        |                |                                                                                                                                                                                                         |

| 31:1<br>0 | RSD[31:10]                 | R      | 0x000000       | Reserved                                                                                                                                                                                                |

| 9:2       | BCU_SNOOP_MASTE<br>RS[7:0] | R/W    | 0x00           | Snoop on masters: Bit 0 corresponds to master 0,<br>,Ķ, bit 7 corresponds to master 7; '1' on each bit to<br>enable snooping                                                                            |

| 1         | BCU_SNOOP_WRITE            | R/W    | 0x0            | Snoop on write: '0' = disable snoop on write; '1' = enable snoop on write                                                                                                                               |

| 0         | BCU_SNOOP_READ             | R/W    | 0x0            | Snoop on read: '0' = disable snoop on read; '1' = enable snoop on read                                                                                                                                  |

# Table 14: PI\_1003\_BCU registers ... continued

UM10113 User manual

# 3.5 DLINK (also known as I<sup>2</sup>D)

#### 3.5.1 Introduction

This section provides an overview of DLINK functions and guidance in its use. The DLINK allows the transmission of data from PNX3000 (MPIF) to AVIP1 and AVIP2.

The communication between one datalink transmitter and one datalink receiver consists of two signals, a data signal and a strobe signal. The strobe signal contains the data, bit-sync and word-sync information. For optimal EMC performance both data and strobe are low voltage differential signals. The voltage swing on the wires is about 300mV.

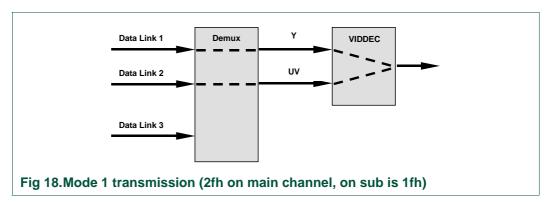

In the PNX3000 the video and audio data to be transmitted is multiplexed in an output register of 42 bits. The content of that 42-bit register is serial transmitted on one of the three datalinks. In the AVIPs the serial data is demultiplexed into parallel streams. With a software selection in the PNX3000 you can choose which data you want to set in the output register for the datalink and in the AVIPs you have to make a selection which data from the datalink you want to use. The data on the datalink is divided in several groups of signals (video, audio and strobe\_signals). It is important that the transmitter and receiver are in the same transmitting mode.

#### 3.5.2 Functional capabilities of the links

The DLINK has the following characteristics.

- The datalink runs at 297 MHz / 594 Mbs.

- The driver rise/fall time is around 200 pS.

- The datalink uses differential signals.

The receiver has an internal termination resistor of 100  $\Omega$  differential connected.

- The differential threshold is 50 mV.

- The signalling voltages are between 200 500 mV.

- The datalink traces, both pairs should be of equal length and internally terminated with 100  $\Omega$  (The PCB-lines also characteristic).

- The max length of the datalink tracks is 20 cm (equal length), normal advice is 5 cm maximum

- The maximum capacitance on the line is approximately 15 pF.

#### 3.5.3 Transmitter

In the PNX3000 the data coming from the A/D converters (digital video and audio) is multiplexed and put in data words. Each data word on the data links consists of 44 bits (4 video samples of 10 bits each, 2 audio samples of 2 bits and 2 word-sync bits). The word clock is 13.5 MHz. The data rate on each of the three data links is 44 bits/cycle\*13.5\*106 Cycle/s = 594 Mbit/s. For detailed transmission information see Table 16.

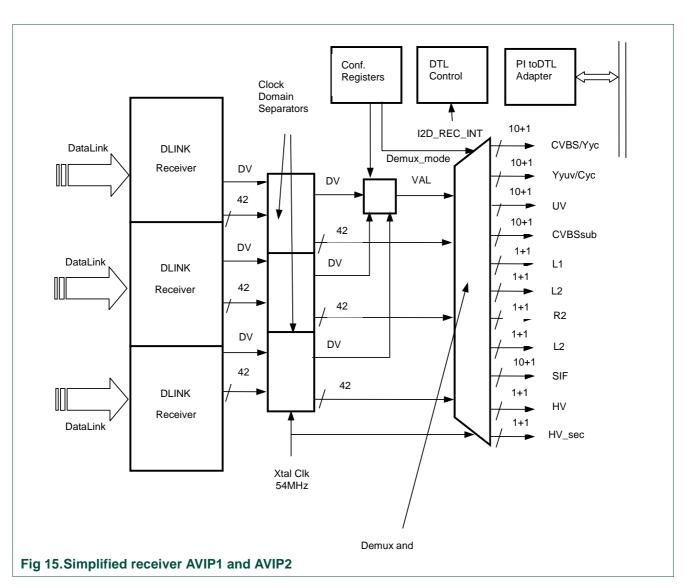

#### 3.5.4 Receiver

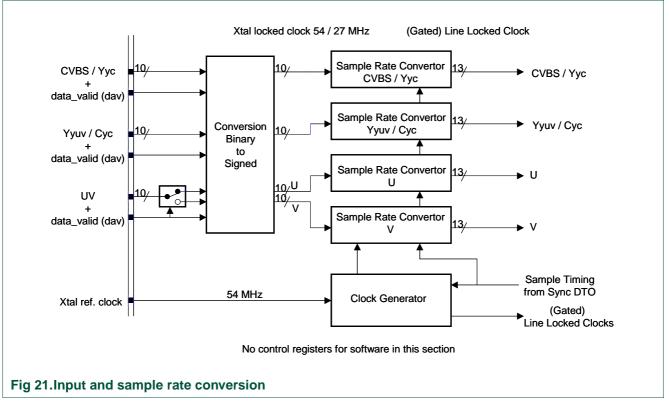

The DLINK receiver module consists of three datalink receivers, and three Data Strobe receivers. The data receiver regenerates the serial data bit-streams, and converts them to parallel words of 42 bits (picture 4x10 bits and 2 bits of audio). When the data is ready for

output a valid Word Sync pulse is generated in the DLINK receiver module. The Word Sync pulses are used by the clock domain separator to take over the 42 bits wide data from the DLINK receivers to the AVIP clock domain.

The clock domain separator module converts the data from the transmitter clock (13.5 or 27 MHz) domain (PNX3000) to the AVIP clock (13.5 / 54 MHz) domain. There is a clock domain separator necessary because the signals in the PNX3000 are processed via different paths and then multiplexed on a serial data line with a Data Strobe (and Word Sync). This leads to a static but unknown phase difference between the AVIP and PNX3000 clock. In addition, the duration of the serial data differs according the link length and group of data on the link and the different processing in the PNX3000. That is why a clock domain separator is necessary.

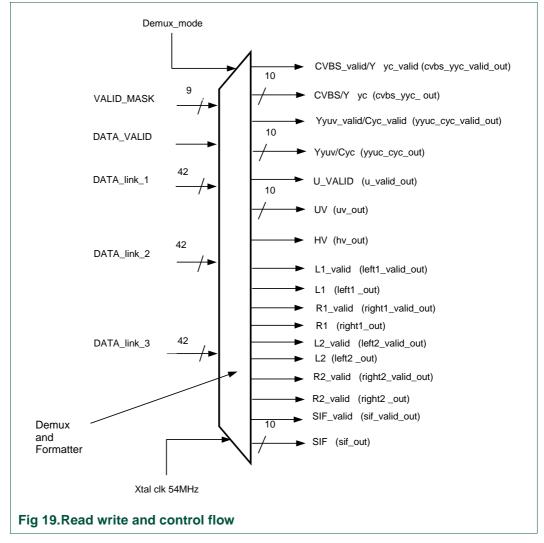

The data from the clock domain separator module is passed to the de-multiplexer module. This module formats the data into several audio and video streams (parallel data) together with accompanying VALid pulses derived from the clock domain separator (ready for takeover) to the Viddec and Demdec modules.

When the expected Word Sync pulse is not detected in the DLINK receiver, the clock domain separator still generates a DV pulse. The previous data is still on the parallel output lines of the DLINK receiver. When the Word Sync pulse is not detected, the counter counts the missing DataValids. This internal counting continues until it reaches the DV\_MISS\_MAX value. When the limit of DV\_MISS\_MAX is reached, an interrupt DVx\_MISS\_STAT is generated and a synchronisation action will follow. When the limit is reached the internal counter is frozen.

When the max value of DV\_MISS\_MAX is not reached and a Word Sync pulse arrives in the receiver window, the counter DV\_MISS\_MAX is reset.

When there is a situation in which the expected Word Sync pulse is detected in the DLINK receiver, but not within the data valid window (receiver window) of the clock domain separator, the pulse is Out Of Window (OOW). The clock domain separator generates a Data Valid (DV) pulse on the time that the clock domain separator expects to receive a Word Sync pulse from the receiver. The data can still be valid if the pulse comes to early, but if the pulse comes to late, the previous data can be on the output when the clock domain separator takes the data over. When the Word Sync pulse is out of his window detected, it generates an Out Of Window (OOW) pulse (referring to I2D\_REC\_SYNC\_LOST). This Out Of Window pulse increments the counter (it counts the OOW pulses), the counter value itself cannot be read. This counting continues till it reaches the OOW\_MAX value (register I2D\_REC\_SYNC\_LOST). When the limit of OOW\_MAX is reached, an interrupt SYNCx\_LOST\_STAT is generated, ref to I2D\_INT\_STATUS for more details, and a synchronisation action will follow. When the max value of OOW\_MAX is reset.

At the end of the receiver is a de-multiplexer, the de-multiplexer reformats the data into several audio and video streams (parallel data) to the Viddec and Demdec. The functional block diagram of the receiver is shown in Figure 15.

#### 3.5.4.1 Transmitter / receiver transmission modes

The data from the PNX3000 can be sent in two modes (0,1) to the receiver in the AVIP. <u>Table 15</u> describes the data that can be extracted from the datalink. The transmitter in the PNX3000 has to be set by the external I<sup>2</sup>C communication link. The microprocessor in the AVIP transmits the mode settings and other multiplexer settings by the I<sup>2</sup>C to the PNX3000. The receiver in the AVIP has to be configured in the same mode by the PI bus in the AVIP. <u>Table 15</u> describes the dataflow and possible modes on each link. The software for the receiver runs in the MIPS processor in the AVIP. The software takes care of the boot sequences, interrupts and the use of the data on the datalink.

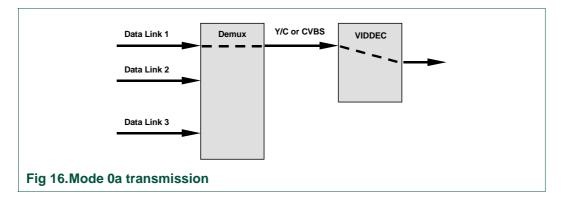

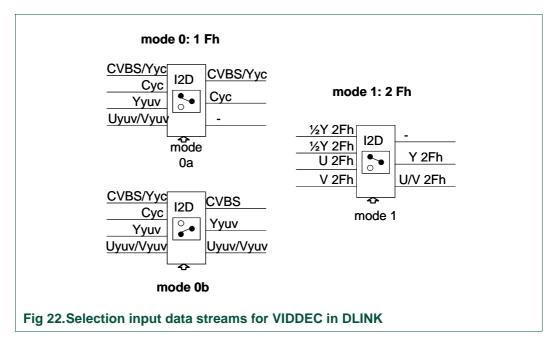

When the transmitter is in mode 0 (all three transmitters are in mode 0), the receiver has the possibility to extract data in mode 0a en 0b (for all three links together). This is possible due to the group of 42 bits send together, see <u>Table 16</u>.

When Viddec uses Y and C from mode 0 datalink 1, it can't use YUV from datalink 2 (no sync available, they use the same bus in the demultiplexer output). If the Viddec use YUV from datalink 2 (input from RGB in PNX3000) it use the CVBS datalink 1 for sync.

UM10113

**UM10113**

PNX2015 User Manual

# UM10113

#### PNX2015 User Manual

|                       |                   | Bits  |    |         |              |         |            |

|-----------------------|-------------------|-------|----|---------|--------------|---------|------------|

| Mode<br>setting       | Mode reg<br>value | 41    | 40 | 39:30   | 29:20        | 19:10   | 9:0        |

| Datalink <sup>•</sup> | 1                 |       |    |         |              |         |            |

| mode 0a               | 0x0               | R1    | L1 | Cn+1    | CVBS or Yn+1 | Cn      | CVBS or Yn |

| mode 0b               | 0x1               | R1    | L1 | -       | CVBS or Yn+1 | -       | CVBS or Yn |

| mode 1                | 0x2               | R1    | L1 | Yyuvn+3 | Yyuvn+2      | Yyuvn+1 | Yyuvn      |

| Datalink              | 2                 |       |    |         |              |         |            |

| mode 0a               | 0x0               | R2    | L2 | -       | -            | -       | -          |

| mode 0b               | 0x1               | R2    | L2 | Vn      | Yyuvn+1      | Un      | Yyuvn      |

| mode 1                | 0x2               | R2    | L2 | Vn+2    | Un+2         | Vn      | Un         |

| Datalink 3            |                   |       |    |         |              |         |            |

| mode 0a               | 0x0               | HVsec | ΗV | SIFn+1  | CVBSsecn+1   | SIFn    | CVBSsecn   |

| mode 0b               | 0x1               | HVsec | ΗV | SIFn+1  | CVBSsecn+1   | SIFn    | CVBSsecn   |

| mode 1                | 0x2               | HVsec | ΗV | SIFn+1  | CVBSsecn+1   | SIFn    | CVBSsecn   |

A CVBS or Y signal may be connected to the inputs of the PNX3000. The type of signal on Datalink 1, in Mode 0 (a or b) is not known, but the preferred is shown **bold underlined**.

If from datalink 1 (mode 0b) the CVBS is used, via fast insertion the Viddec can use the YUV (1fH-mode) signals from datalink2 if the signal contains a sync signal.

The following figures show the use modes (video) in the receiver at the output of the multiplexer.

UM10113 User manual

PNX2015 User Manual

The control software has to set the correct settings in the PNX3000 and AVIP.

#### 3.5.4.2 Data rate and timing output signals

The output rate of the data from the datalink receiver is shown in Table 16.

The HV\_PRIM and HV\_SEC are for the horizontal and vertical sync for the primary and secondary channel (timing pulses in IF part). These are clamping signals, which are coming from the VIDDEC. The frequency of the signals is dependent of the selected mode. These signals are not needed for DLINK.

| Pin name     | Sample rate (Msamples/s) |     |

|--------------|--------------------------|-----|

|              | 1FH                      | 2FH |

| CVBS_YYC_OUT | 27                       | -   |

| YYUV_CYC_OUT | 27                       | 54  |

| UV_OUT       | 27                       | 54  |

| CVBS_SEC_OUT | 27                       | -   |

| LEFT1_OUT    | 6.75                     |     |

| RIGHT1_OUT   | 6.75                     |     |

| LEFT2_OUT    | 6.75                     |     |

| RIGHT2_OUT   | 6.75                     |     |

| HV_OUT       | 54                       |     |

| HV_SEC_OUT   | 54                       |     |

| SIF_OUT      | 27                       |     |

#### Table 16: Data rate output signals

All data is generated on the negative edge of the 54 MHz clock.

### 3.5.5 Configuration registers.

The DLINK configuration registers are used to control the DLINK receiver module. For description of the de-multiplexer outputs see Figure 19.

UM10113

35 of 795

UM10113

PNX2015 User Manual

The DLINK configuration register block contains the control registers which are used to configure the DLINK receiver block, address decoder and two state machines. One to synchronize the write request and the register write enable, and the other one to synchronize the read request and read enable.

#### 3.5.5.1 DLINK register map

This section provides information on the DLINK configuration. Each of the registers within the receiver block is described separately below. The base address for the DLINK is set to 0x07FF8000 (32 bits), the last 3 digits (12 bits) are for the DLINK control register.

|         | Deliver register summary |                                                                                                 |  |

|---------|--------------------------|-------------------------------------------------------------------------------------------------|--|

| Address | Name                     | Description                                                                                     |  |

| 0x0     | RX_CTRL                  | Settings for analogue receiver                                                                  |  |

| 0x4     | RX_STATUS                | Status of analogue receiver                                                                     |  |

| 0x10    | I2D_DTM_M_STAB           | Number of flip flops for synchronization of the read and write access to DLINK config register. |  |

Table 17: DLINK register summary

# PNX2015 User Manual

| Address | Name           | Description                                                                                                                          |

|---------|----------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 0x14    | I2D_MTD_M_STAB | DLINK number of flip flops for synchronization of the read and write access from DLINK config register to the DTL target Controller. |

| 0x18    | REC_DEMUX_MODE | Demux settings                                                                                                                       |

| 0x1C    | REC_SYNC_LOST  | Sync lost timer before generating an interrupt                                                                                       |

| 0x20    | PRBS_STAT      | Pseudo Random Bit Sequence checksum status                                                                                           |

| 0x24    | PRBS_CTRL      | Pseudo Random Bit Sequence checksum settings                                                                                         |

| 0xFE0   | I2D_INT_STATUS | Status of (possible) DVP interrupt requests                                                                                          |

| 0xFE4   | I2D_INT_ENABLE | Enable the DVP interrupt for request to the system irq controller                                                                    |

| 0xFE8   | I2D_INT_CLEAR  | Clear a DVP interrupts                                                                                                               |

| 0xFEC   | I2D_INT_SET    | Set a DVP interrupt                                                                                                                  |

| 0xFFC   | I2D_MOD_ID     | Block information                                                                                                                    |

| -       |                |                                                                                                                                      |

## Table 18: DLINK registers

| Bit     | Symbol                | Access | Reset value    | Description                                                                                                                                                                                                                            |

|---------|-----------------------|--------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Offset  | 0x0 - RX_CTRL         |        |                |                                                                                                                                                                                                                                        |

| 31:1    | RSD[31:1]             | R/W    | 0x0000000<br>0 | reserved                                                                                                                                                                                                                               |

| 0       | RX_APPL_PD            | R/W    | 0x1            | Power down for analog receiver in application mode<br>'0' : The analog receiver is active (normal mode) '1'<br>The analog receiver is in power down mode (For<br>ADOC sleep/coma modes)                                                |

| Offset  | 0x4 - RX_STATUS       |        |                |                                                                                                                                                                                                                                        |

| 31:28   | RSD[31:28]            | R      | 0x0            | reserved                                                                                                                                                                                                                               |

| 27:16   | RX_DC_MON[11:0]       | R      | 0xXXX          | Internal DC testmode monitor point                                                                                                                                                                                                     |

| 15:2    | RSD[15:2]             | R      | 0x0000         | reserved                                                                                                                                                                                                                               |

| 1       | PD_STAT_STIMGEN       | R      | 0x1            | Power down monitor of internal testmode '1' :<br>internal tester is powered down '0' : internal tester is<br>active                                                                                                                    |

| 0       | PD_STAT_RX            | R      | 0x1            | Power down monitor of analog receivers '1' :<br>analogue receiver is powered down '0' : analog<br>receiver is active                                                                                                                   |

| Offset  | 0x10 - I2D_DTM_M_STAB |        |                |                                                                                                                                                                                                                                        |

| 31:2    | RSD[31:2]             | R/W    | 0x0000000<br>0 | reserved                                                                                                                                                                                                                               |

| 1:0     | DTL_I2D_CTRL[1:0]     | R/W    | 0x0            | Number of flip flops used for synchronization during validation. Located between DTL target Ctrl to I2D '00' Have two metastability registers. '01' Have one register, bypass the other one. '1x' Bypass both metastability registers. |

| Offset  | 0x14 - I2D_MTD_M_STAB |        |                |                                                                                                                                                                                                                                        |

| 31:2    | RSD[31:2]             | R/W    | 0x0000000<br>0 | reserved                                                                                                                                                                                                                               |

| JM10113 |                       |        |                | © Koninklijke Philips Electronics N.V. 2005. All rights reserv                                                                                                                                                                         |

PNX2015 User Manual

| Offset 0 | I2D_DTL_CTRL[1:0]             | R/W | 0x0       | Number of flip flops used for synchronization during                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------|-------------------------------|-----|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |                               |     |           | validation. Located between I2D to DTL ctrl '00'<br>Have two metastability registers. '01' Have one<br>register, bypass the other one. '1x' Bypass both<br>metastability registers.                                                                                                                                                                                                                                                                     |

|          | x18 - REC_DEMUX_MODE          |     |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 31:18    | RSD[31:18]                    | R/W | 0x0000    | reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 17       | I2D_SOFT_RESET                | W   | 0x0       | Softreset of the clock domain separator                                                                                                                                                                                                                                                                                                                                                                                                                 |

|          | i2d_rx_data_valid_m<br>ASK    | R/W | 0x1       | Mask the overall data valid flag inside the I2D (dv from the Clock Domain Separator). Advised not to use. '1' Enable '0' Hide                                                                                                                                                                                                                                                                                                                           |

| 15:12    | RSD[15:12]                    | R/W | 0x0       | reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|          | I2D_DEMUX_VALID_MA<br>SK[8:0] | R/W | 0x1FF     | Mask data valid of the several I2D outputs. Each bit:<br>'0' to hide the valid signal. [11] SIF [10] Right 2 [9]<br>Left 2 [8] Right 1 [7] Left 1 [6] CVBS sec [5] U [4] Y<br>[3] CVBS                                                                                                                                                                                                                                                                  |

| 2:0      | DEMUX_MODE[2:0]               | R/W | 0x1       | Select the I2D content format to output mode '000'<br>mode 0a '001' mode 0b '010' mode 1 '100' mode 2<br>'110' mode 3                                                                                                                                                                                                                                                                                                                                   |

| Offset 0 | x1C - REC_SYNC_LOST           |     |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 31:16    | DV_MISS_MAX[15:0]             | R/W | 0x03E8    | Number of consecutive valid pulses missing before<br>generating an dv error interrupt '0' disables detection<br>and/or resets the counter To ensure proper counting<br>during lowering this value, first write a value of 0 into<br>the max value, before lowering this marker.<br>Otherwise the hold counter marker might be shifted<br>over the counter what will result in a 16 bits<br>overcount (afterwards it will continue at 0).                |

| 15:0     | OOW_MAX[15:0]                 | R/W | 0x03E8    | Number of consecutive valid pulses out of the catching window before generating an 'out of sync' (sync lost) interrupt '0' disables detection and/or resets the counter To ensure proper counting during lowering this value, first write a value of 0 into the max value, before lowering this marker. Otherwise the hold counter marker might be shifted over the counter what will result in a 16 bits overcount (afterwards it will continue at 0). |

| Offset 0 | x20 - PRBS_STAT               |     |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 31:7     | RSD[31:7]                     | R   | 0x0000000 | reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 6        | DV_UNDET                      | R   | 0x1       | Global data valid undetected '1' DV undetected yet '0' DV has been detected                                                                                                                                                                                                                                                                                                                                                                             |

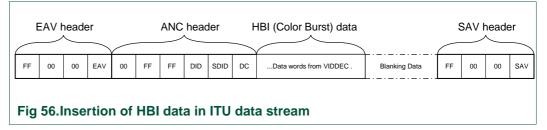

| 5        | DV3_UNDET                     | R   | 0x1       | Data valid of datalink 3 undetected '1' DV<br>undetected yet '0' DV has been detected                                                                                                                                                                                                                                                                                                                                                                   |