# UM10362 LPC314x User manual Rev. 1 — 7 December 2012

**User manual**

#### **Document information**

| Info     | Content                     |

|----------|-----------------------------|

| Keywords | LPC3141, LPC3143, ARM9, USB |

| Abstract | LPC3141/43 User manual      |

LPC314x User manual

#### **Revision history**

| Rev | Date     | Description      |

|-----|----------|------------------|

| 1   | 20121207 | Initial version. |

## **Contact information**

For more information, please visit: <a href="http://www.nxp.com">http://www.nxp.com</a>

For sales office addresses, please send an email to: <a href="mailto:salesaddresses@nxp.com">salesaddresses@nxp.com</a>

# **UM10362**

# **Chapter 1: LPC314x Introductory information**

Rev. 1 — 7 December 2012

**User manual**

#### 1. Introduction

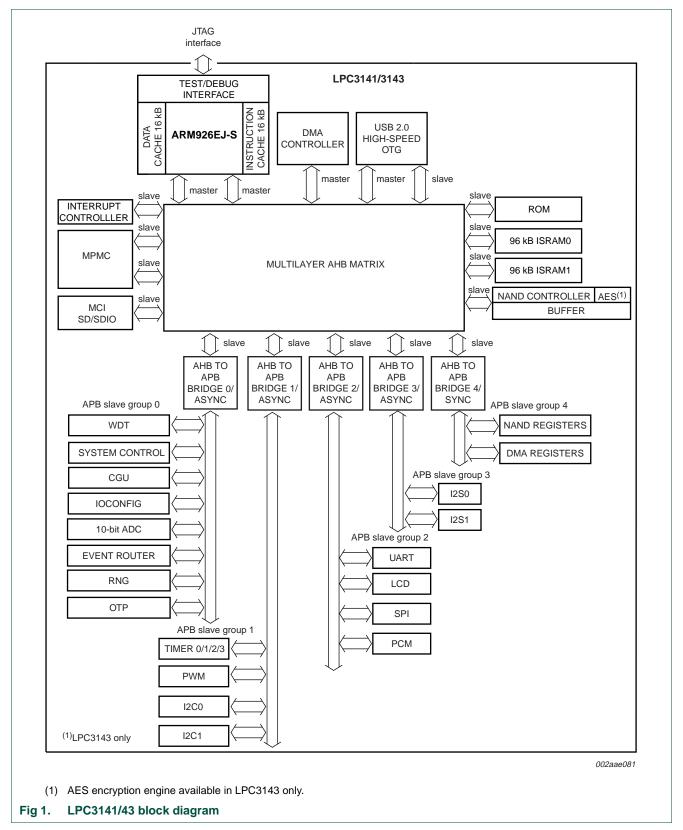

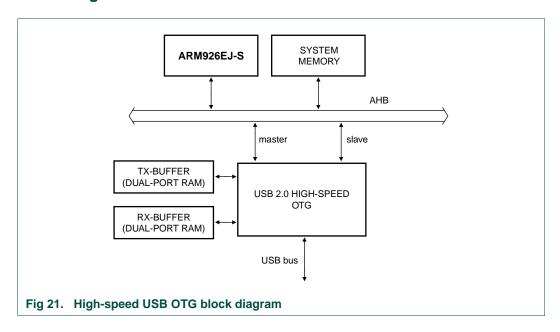

The NXP LPC314x combine a 270 MHz ARM926EJ-S CPU core, High-speed USB 2.0 OTG, 192 KB SRAM, NAND flash controller, flexible external bus interface, three channel 10-bit A/D, and a myriad of serial and parallel interfaces in a single chip targeted at consumer, industrial, medical, and communication markets. To optimize system power consumption, the LPC314x have multiple power domains and a very flexible Clock Generation Unit (CGU) that provides dynamic clock gating and scaling.

#### 2. Features

- CPU platform

- 270 MHz, 32-bit ARM926EJ-S

- 16 kB D-cache and 16 kB I-cache

- Memory Management Unit (MMU)

- Internal memory

- 192 kB embedded SRAM

- External memory interface

- NAND flash controller with 8-bit ECC and AES decryption support (LPC3143 only)

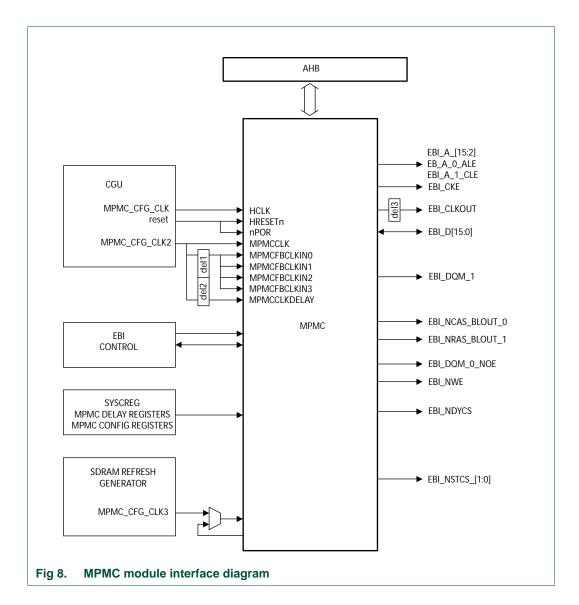

- 8/16-bit Multi-Port Memory Controller (MPMC): SDRAM and SRAM

- Security

- AES decryption engine (LPC3143 only)

- Secure one-time programmable memory for AES key storage and customer use

- 128 bit unique id per device for DRM schemes

- Communication and connectivity

- High-speed USB 2.0 (OTG, Host, Device) with on-chip PHY

- Two I<sup>2</sup>S interfaces

- Integrated master/slave SPI

- Two master/slave I<sup>2</sup>C-bus interfaces

- Fast UART

- Memory Card Interface (MCI): MMC/SD/SDIO/CE-ATA

- Four-channel 10-bit ADC

- Integrated 4/8/16-bit 6800/8080 compatible LCD interface

- · System functions

- Dynamic clock gating and scaling

- Multiple power domains

- Selectable boot-up: SPI flash, NAND flash, SD/MMC cards, UART, or USB

#### Chapter 1: LPC314x Introductory information

- On the LPC3143 only: secure booting using an AES decryption engine from SPI flash, NAND flash, SD/MMC cards, UART, or USB.

- DMA controller

- Four 32-bit timers

- Watchdog timer

- PWM module

- Random Number Generator (RNG)

- 97 General Purpose I/O (GPIO) pins, plus GPI4 which is input only.

- Flexible and versatile interrupt structure

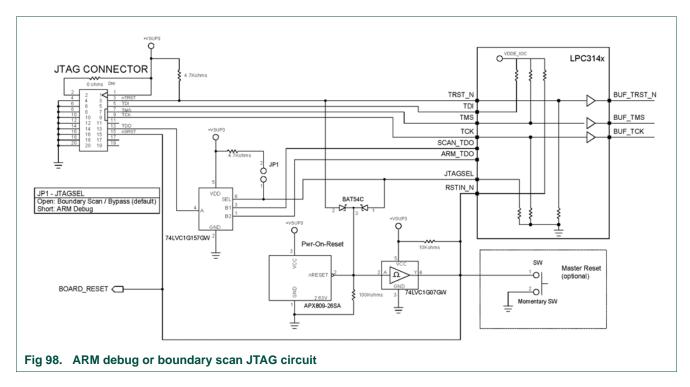

- JTAG interface with boundary scan and ARM debug access

- · Operating voltage and temperature

- Core voltage: 1.2 V

- I/O voltages: 1.8 V, 3.3 V

- Temperature: -40 °C to +85 °C

- TFBGA180 package: 12 × 12 mm<sup>2</sup>, 0.8 mm pitch

# 3. Ordering information

Table 1. Ordering information

|               | •        |                                                                                                 |          |

|---------------|----------|-------------------------------------------------------------------------------------------------|----------|

| Type number   | Package  |                                                                                                 |          |

|               | Name     | Description                                                                                     | Version  |

| LPC3141FET180 | TFBGA180 | Plastic thin fine pitch ball grid array package, 180 balls, body 12 $\times$ 12 $\times$ 0.8 mm | SOT570-3 |

| LPC3143FET180 | TFBGA180 | Plastic thin fine pitch ball grid array package, 180 balls, body 12 $\times$ 12 $\times$ 0.8 mm | SOT570-3 |

Table 2. Ordering options for LPC3141/43

| Type number   | core/bus<br>frequency | Total<br>SRAM | Security<br>engine<br>AES | High-speed<br>USB   | 10-bit<br>ADC<br>channels | I <sup>2</sup> S/<br>I <sup>2</sup> C | MCI<br>SDHC/<br>SDIO/<br>CE-ATA | Temperature range |

|---------------|-----------------------|---------------|---------------------------|---------------------|---------------------------|---------------------------------------|---------------------------------|-------------------|

| LPC3141FET180 | 270/<br>90 MHz        | 192 kB        | no                        | Device/<br>Host/OTG | 4                         | 2 each                                | yes                             | –40 °C to +85 °C  |

| LPC3143FEt180 | 270/<br>90 MHz        | 192 kB        | yes                       | Device/<br>Host/OTG | 4                         | 2 each                                | yes                             | –40 °C to +85 °C  |

#### **Chapter 1: LPC314x Introductory information**

# 4. Block diagram (LPC3141/43)

UM10362 © NXP B.V. 2012. All rights reserved

#### Chapter 1: LPC314x Introductory information

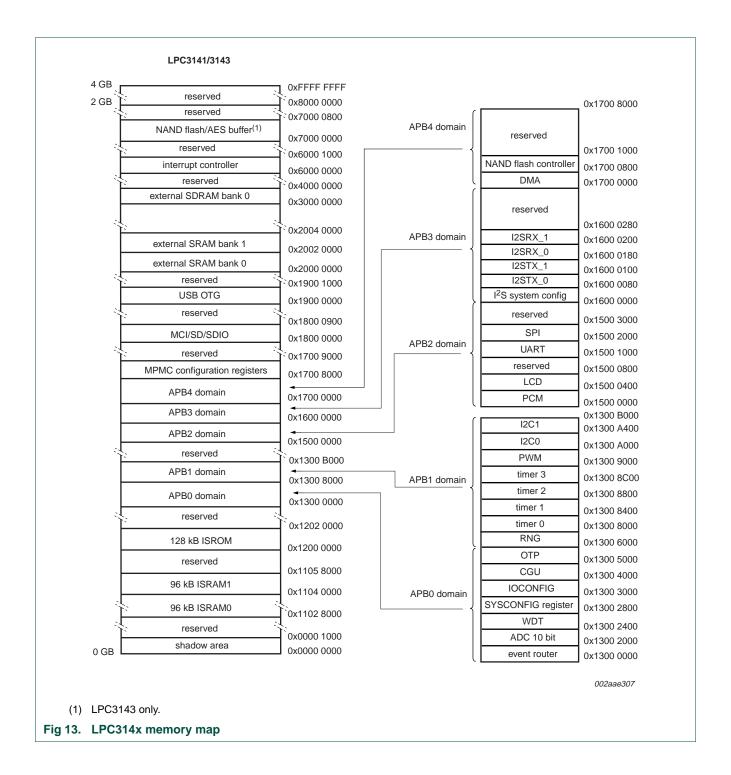

#### 5. Architectural overview

#### 5.1 ARM926EJ-S

The processor embedded in the LPC314x is the ARM926EJ-S. It is a member of the ARM9 family of general-purpose microprocessors. The ARM926EJ-S is intended for multi-tasking applications where full memory management, high performance, and low power are important.

The CPU has the following features:

- ARM926EJ-S processor core which uses a five-stage pipeline consisting of fetch, decode, execute, memory, and write stages. The processor supports both the 32-bit ARM and 16-bit Thumb instruction sets, which allows a trade off between high performance and high code density. The ARM926EJ-S also executes an extended ARMv5TE instruction set which includes support for Java byte code execution.

- Contains an AMBA BIU for both data accesses and instruction fetches.

- Memory Management Unit (MMU).

- 16 kB instruction and 16 kB data separate cache memories with an 8 word line length. The caches are organized using Harvard architecture.

- Little Endian is supported.

- The ARM926EJ-S processor supports the ARM debug architecture and includes logic to assist in both hardware and software debugging.

- Supports dynamic clock gating for power reduction.

- The processor core clock can be set equal to the AHB bus clock or to an integer number times the AHB bus clock. The processor can be switched dynamically between these settings.

- ARM stall support.

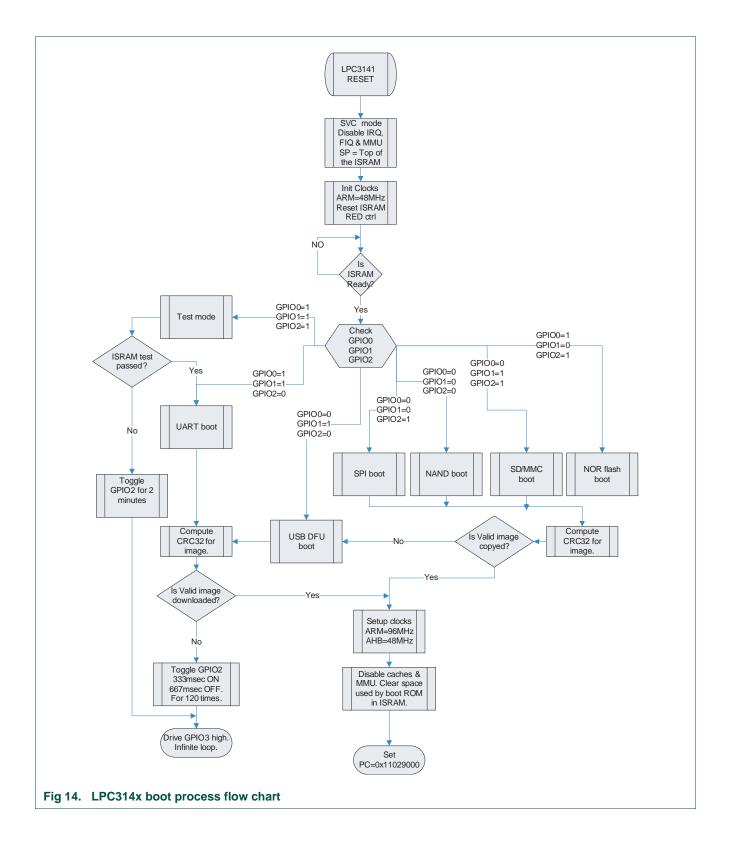

#### 5.2 Internal ROM Memory

The internal ROM memory is used to store the boot code of the LPC314x. After a reset, the ARM processor will start its code execution from this memory.

The LPC314x ROM memory has the following features:

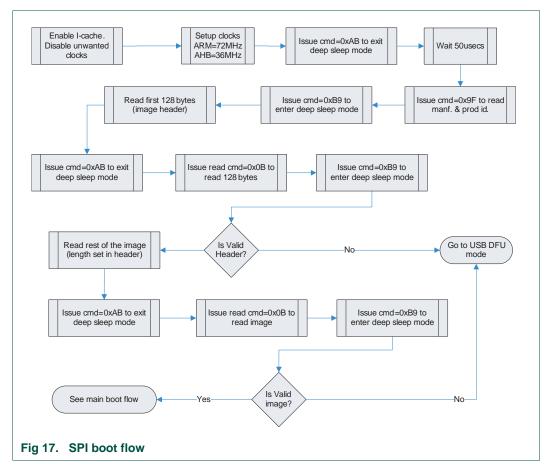

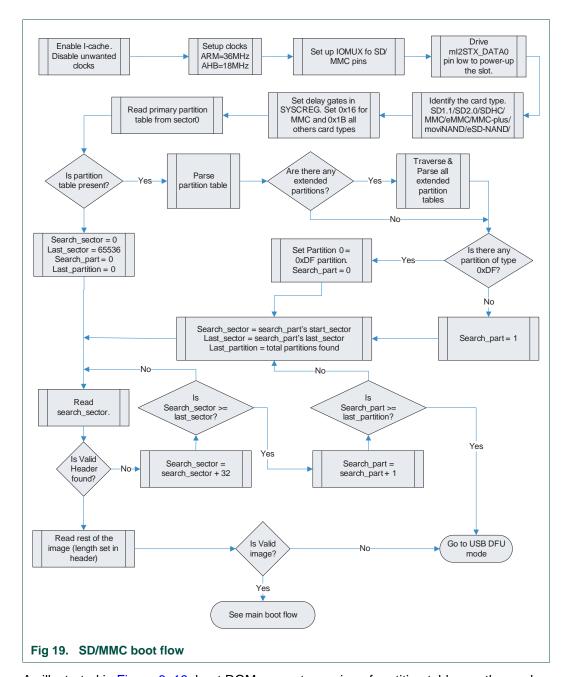

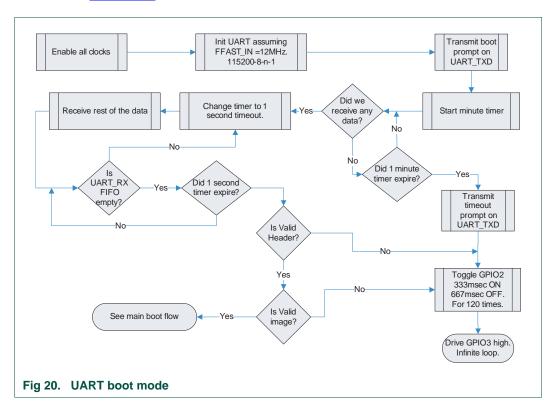

- Supports booting from SPI flash, NAND flash, SD/SDHC/MMC cards, UART, and USB (DFU class) interfaces.

- Supports option to perform CRC32 checking on the boot image.

- Supports booting from managed NAND devices such as moviNAND, iNAND, eMMC-NAND and eSD-NAND using SD/MMC boot mode.

- Contains pre-defined MMU table (16 kB) for simple systems.

#### **Chapter 1: LPC314x Introductory information**

#### 5.3 Internal RAM memory

The ISRAM (Internal Static Memory Controller) module is used as controller between the AHB bus and the internal RAM memory. The internal RAM memory can be used as working memory for the ARM processor and as temporary storage to execute the code that is loaded by boot ROM from external devices such as SPI-flash, NAND flash, and SD/MMC cards.

This module has the following features:

- Capacity of 192 kB

- Implemented as two independent 96 kB memory banks

# **UM10362**

# Chapter 2: LPC314x NAND flash controller

Rev. 1 — 7 December 2012

**User manual**

# 1. How to read this chapter

The AES block is available on the LPC3143 only. See <u>Table 2–3</u> for clocks and registers that are specific to the AES block and are therefore not available in LPC3141.

Table 3. Part specific clocks and registers

| Clock signal or register                                                      | Description                                                                           | LPC3141 | LPC3143 |

|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---------|---------|

| NANDFLASH_AES_CLK                                                             | NAND flash AES clock                                                                  | no      | yes     |

| NandAESKey1-4                                                                 | Words 1 to 4 of 128-bit AES key                                                       | no      | yes     |

| NandAESIV1-4                                                                  | Words 1 to 4 of 128-bit initial AES value                                             | no      | yes     |

| NandAESState                                                                  | Register to display AES state                                                         | no      | yes     |

| Interrupt registers:<br>NandIRQStatus1,<br>NandIRQMask1,<br>NandIRQStatusRaw1 | AES related interrupt status, mask, and raw status bits INT0/1S, INT0/1M, and INT0/1R | no      | yes     |

| NandConfig                                                                    | AO bit: turns AES on/off                                                              | no      | yes     |

| AES_FROM_AHB                                                                  | Enable AES engine access from AHB                                                     | no      | yes     |

#### 2. Introduction

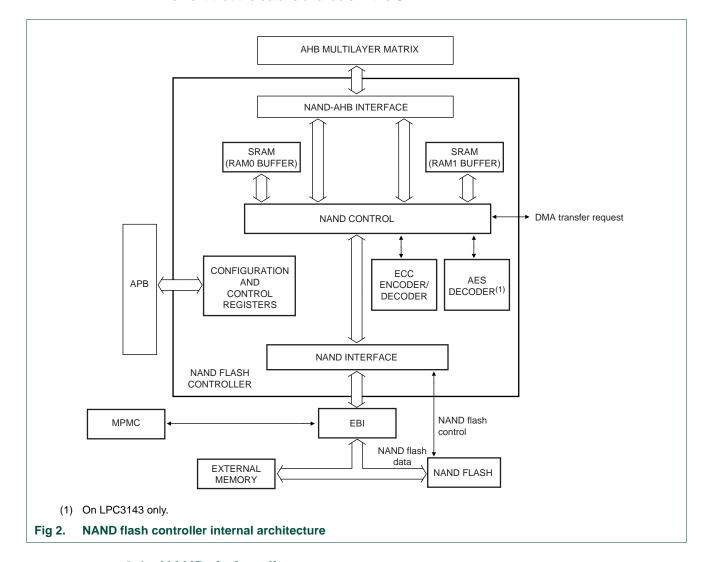

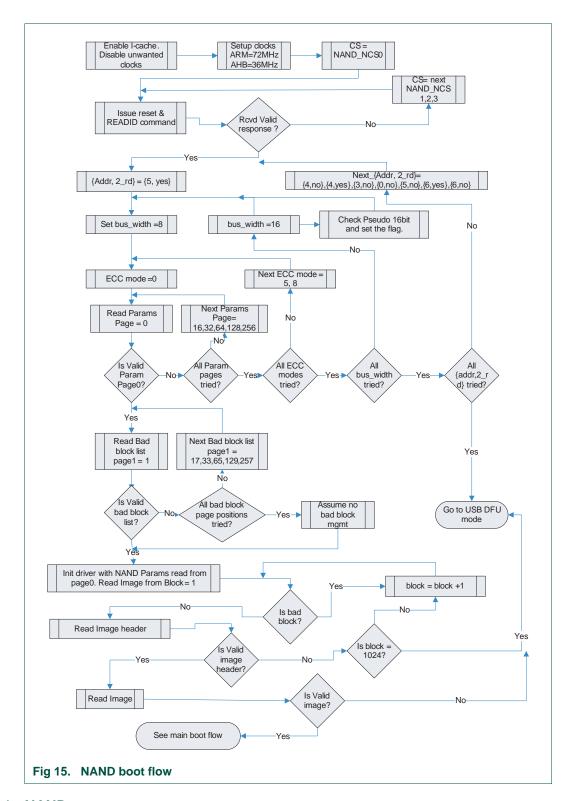

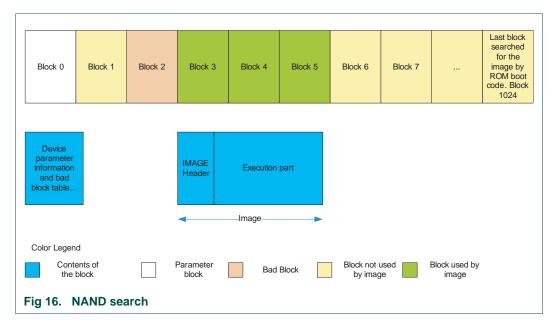

The NAND flash controller is used to transfer data between the LPC314x and external NAND flash devices.

#### 2.1 Features

- AHB/APB interface

- AHB slave interface.

- AHB interface supports 0,1 and 2 wait states.

- 2 SRAMs of 132 words, 32 bits per word used in a double buffering accessible via the AHB bus. RAM0 at 0x7000 0000 and RAM1 at 0x7000 0400.

- Programming by CPU via APB interface using zero wait states.

- Little and big endian support.

- Automatic flow control with the DMA controller, using ext\_en/ext\_ack signals.

- NAND flash support

- Dedicated interface to NAND flash devices.

- Hardware controlled read and write data transfers.

- Software controlled command and address transfers to support a wide range of NAND flash devices.

- GPIO mode.

- Software control mode where the ARM is directly master of the NAND flash device.

- Support for 8 bit and 16 bit NAND flash devices.

#### Chapter 2: LPC314x NAND flash controller

- Support for 528 byte, 2K and 4K page NAND flash devices.

- Programmable NAND timing parameters.

- Support for up to 4 NAND flash device dies in parallel with dedicated chip select and ready/busy pin per device.

- Programmable default state of output signals.

- Erased page detection.

- EBI compatible.

#### Error correction

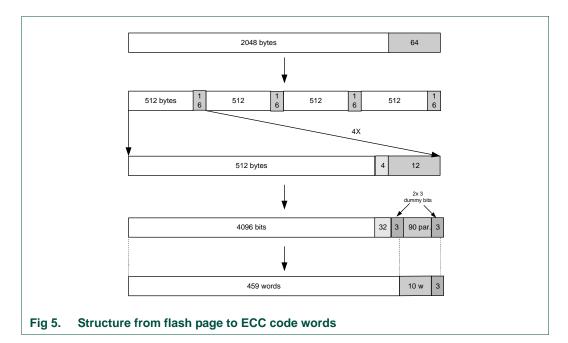

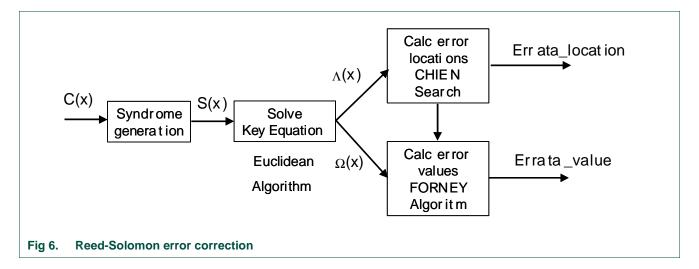

- Two Reed-Solomon error correction codes, one offering 5 symbol error correction and the other 8 symbol error correction capability. 5 symbol correcting code is of length 469, dimension 459, and minimum distance 11 over GF(2<sup>9</sup>). 8 symbol correcting code has length 475, dimension 459 and minimum distance 17 over GF(2<sup>9</sup>).

- Two parity generators.

- Wear leveling and other extra information can be integrated into protected data.

**Remark:** The wear-leveling algorithm ensures that data is stored in different flash pages across the flash media. This not only extends its lifetime, but also ensures reliable operation.

- Interrupts generated after completion of error correction task with 3 interrupt registers.

- Error correction statistics distributed to ARM using interrupt scheme.

- Error correction can be turned on and off.

- AES decryption

- AES-128: 128-bit key, 128-bit data.

- CBC mode over blocks of 512 bytes.

- Initial vector and key can be programmed over APB.

- Each block of 512 bytes uses same initial value.

- AES can be turned on and off.

# 3. General description

#### 3.1 Clock signals

The CGU provides different clocks to the NAND flash controller, see Table 2-4.

Table 4. NAND flash controller clock overview[1]

| Clock name       | Clock<br>acronym | I/O | Source/<br>Destination | Description                  |

|------------------|------------------|-----|------------------------|------------------------------|

| NANDFLASH_S0_CLK | ahb_clk          | I   | CGU                    | AHB port clock of the module |

| NANDFLASH_PCLK   | PCLK             | I   | CGU                    | APB port clock of the module |

<u>UM10362</u> <u>© NXP B.V. 2012. All rights reserved.</u>

#### Chapter 2: LPC314x NAND flash controller

| Clock name         | Clock<br>acronym | I/O | Source/<br>Destination | Description                                                                                                                                           |

|--------------------|------------------|-----|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| NANDFLASH_NAND_CLK | nand_clk         | I   | CGU                    | Main clock for the module                                                                                                                             |

| NANDFLASH_ECC_CLK  | ecc_clk          | I   | CGU                    | Main clock for ECC part in the module. This clock should be programmed to run synchronously at half the NANDFLASH_NAND_CLK in CGU block.              |

| NANDFLASH_AES_CLK  | aes_clk          | I   | CGU                    | Main clock for AES part in the module. This clock should be programmed to run synchronously at the same speed as the NANDFLASH_NAND_CLK in CGU block. |

Table 4. NAND flash controller clock overview ... continued

#### 3.2 Reset signals

The CGU provides the following resets to the NAND flash controller (see Section 13–5.2.2).

- AHB0\_RESERT: Low-active, synchronous reset. Resets the logic in the ahb\_clk domain.

- APB4\_RESETN: Low-active, synchronous reset. Resets the logic in the PCLK domain.

- 3. NANDFLASH\_CTRL\_NAND\_RESET\_N: High-active, synchronous reset. Resets the logic in the main NAND flash controller nand clk domain.

- 4. NANDFLASH\_CTRL\_ECC\_RESET\_N: High-active, synchronous reset. Resets the logic in the ecc\_clk domain.

- 5. NANDFLASH\_CTRL\_AES\_RESET\_N: High-active, synchronous reset. Resets the logic in the aes\_clk domain.

#### 3.3 Interrupt requests

The NAND flash controller generates one interrupt request towards the CPU. The interrupt sources are controlled by two sets of registers: NandlRQStatus1, NandlRQMask1, NandlRQStatusRaw1 and NandlRQStatus2, NandlRQMask2, NandlRQStatusRaw2. See <a href="Table 2-7">Table 2-7</a> to <a href="Table 2-9">Table 2-9</a> and <a href="Table 2-23">Table 2-23</a> to <a href="Table 2-25">Table 2-25</a> for a description of interrupt sources.

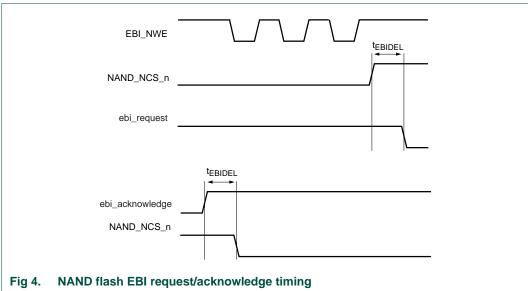

#### 3.4 DMA transfers

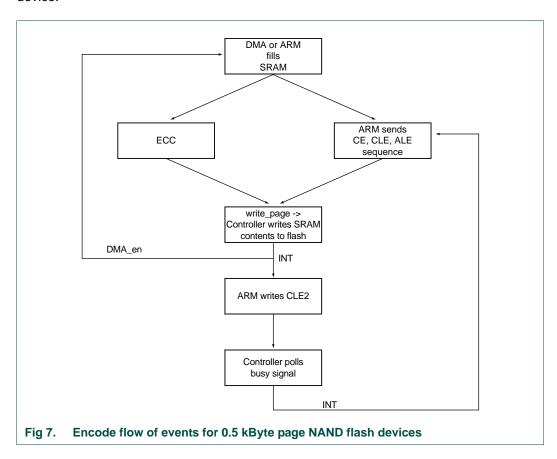

The NAND flash controller has DMA support by means of external enabling. The transfer size is 128 words. DMA auto-flow control is supported only by DMA channel 4.

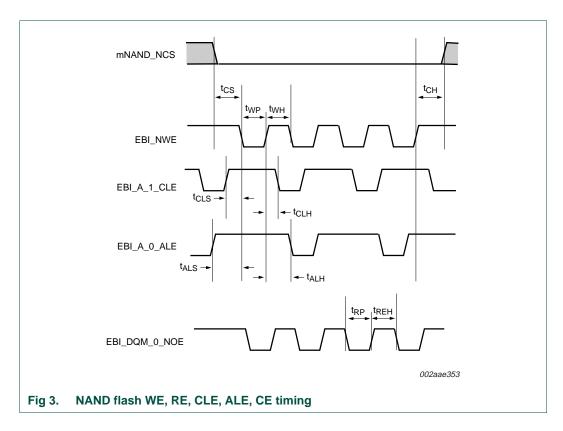

#### 3.5 External pin connections

<u>Table 2–5</u> gives an overview of the external connections to and from the NAND flash controller.

UM10362 © NXP B.V. 2012. All rights reserved

<sup>[1]</sup> See <u>Table 2–3</u> for clocks that are part specific and not implemented on all LPC314x parts.

#### Chapter 2: LPC314x NAND flash controller

Table 5. NAND flash controller external pin overview

| Pin name      | Interface | Acronym | Type<br>(Func.) |       | Description                         |

|---------------|-----------|---------|-----------------|-------|-------------------------------------|

| EBI_D_[15:0]  | EBI       | -       | I               | -     | 16 bits data from NAND flash device |

| EBI_D_[15:0]  | EBI       | -       | 0               | all 0 | 16 bits data to NAND flash device   |

| NAND_NCS_0    |           | CS1_n   | 0               | 1     | Low-active Chip Enable 0            |

| NAND_NCS_1    |           | CS2_n   | 0               | 1     | Low-active Chip Enable 1            |

| NAND_NCS_2    |           | CS3_n   | 0               | 1     | Low-active Chip Enable 2            |

| NAND_NCS_3    |           | CS4_n   | 0               | 1     | Low-active Chip Enable 3            |

| EBI_NWE       | EBI       | WE_n    | 0               | 1     | Low-active Write Enable             |

| EBI_DQM_0_NOE | EBI       | RE_n    | 0               | 1     | Low-active Read Enable              |

| EBI_A_0_ALE   | EBI       | ALE     | 0               | 0     | High-active Address Latch<br>Enable |

| EBI_A_1_CLE   | EBI       | CLE     | 0               | 0     | High-active Command Latch Enable    |

| mNAND_RYBN0   |           | RnB0    | I               | -     | Ready not Busy 0                    |

| mNAND_RYBN1   |           | RnB1    | I               | -     | Ready not Busy 1                    |

| mNAND_RYBN2   |           | RnB2    | I               | -     | Ready not Busy 2                    |

| mNAND_RYBN3   |           | RnB3    | I               | -     | Ready not Busy 3                    |

# 4. Register overview

<u>Table 2–6</u> indicates which registers reside in the NAND flash controller. The NAND RAM buffers are also accessible at locations RAM0: 0x7000 0000 and RAM1: 0x7000 0400.

Table 6. Register overview: NAND flash controller (register base address: 0x1700 0800)[1]

| Name              | Access | Offset | Description                                                    |

|-------------------|--------|--------|----------------------------------------------------------------|

| NandIRQStatus1    | R/W    | 0x00   | Status register of first 32 bits interrupt register            |

| NandlRQMask1      | R/W    | 0x04   | Mask register for first 32 bits interrupt register             |

| NandIRQStatusRaw1 | R/W    | 0x08   | Unmasked status register of first 32 bits interrupt register   |

| NandConfig        | R/W    | 0x0C   | NAND flash controller configuration register                   |

| NandIOConfig      | R/W    | 0x10   | Register which holds the default value settings for IO signals |

| NandTiming1       | R/W    | 0x14   | First NAND flash controller timing register                    |

| NandTiming2       | R/W    | 0x18   | Second NAND flash controller timing register                   |

| NandSetCmd        | R/W    | 0x20   | Register to send specific command towards NAND flash device.   |

| NandSetAddr       | R/W    | 0x24   | Register to send specific address towards NAND flash device    |

| NandWriteData     | R/W    | 0x28   | Register to send specific data towards NAND flash device       |

| NandSetCE         | R/W    | 0x2C   | Register to set all CE signals and WP_n signal                 |

| NandReadData      | R      | 0x30   | Register to check read data from NAND flash device             |

#### Chapter 2: LPC314x NAND flash controller

Table 6. Register overview: NAND flash controller (register base address: 0x1700 0800)[1]

| Name              | Access | Offset | Description                                                   |

|-------------------|--------|--------|---------------------------------------------------------------|

| NandCheckSTS      | R      | 0x34   | Check status of 8 predefined interrupts                       |

| NandControlFlow   | W      | 0x38   | Register which holds command to read and write pages          |

| NandGPIO1         | R/W    | 0x40   | Register to program IO pins, which can be used as GPIO        |

| NandGPIO2         | R      | 0x44   | Register to program IO pins, which can be used as GPIO        |

| NandIRQStatus2    | R/W    | 0x48   | Status register of second 32 bits interrupt register          |

| NandIRQMask2      | R/W    | 0x4C   | Mask register for second 32 bits interrupt register           |

| NandIRQStatusRaw2 | R/W    | 0x50   | Unmasked status register of second 32 bits interrupt register |

| NandAESKey1       | W      | 0x54   | First word of 128-bit AES key                                 |

| NandAESKey2       | W      | 0x58   | Second word of 128-bit AES key                                |

| NandAESKey3       | W      | 0x5C   | Third word of 128-bit AES key                                 |

| NandAESKey4       | W      | 0x60   | Fourth word of 128-bit AES key                                |

| NandAESIV1        | W      | 0x64   | First word of 128-bit initial AES value                       |

| NandAESIV2        | W      | 0x68   | Second word of 128-bit initial AES value                      |

| NandAESIV3        | W      | 0x6C   | Third word of 128-bit initial AES value                       |

| NandAESIV4        | W      | 0x70   | Fourth word of 128-bit initial AES value                      |

| NandAESState      | R/W    | 0x74   | Register to display AES state                                 |

| NandECCErrStatus  | R      | 0x78   | ECC error status register in 8-symbol ECC mode                |

| AES_FROM_AHB      | R/W    | 0x7C   | Enable AES engine from AHB                                    |

|                   |        |        |                                                               |

<sup>[1]</sup> See Table 2–3 for registers that are part specific and not implemented on all LPC314x parts.

# 5. Register description

#### 5.1 NandIRQStatus1

In this register the status of the different interrupt sources can be checked. All interrupts can be masked by the corresponding bit in the NandlRQMask register. A bit which has been set can only be cleared by writing a '1' to this bit in this register. Table 2–7 gives a description of this register.

Table 7. NandIRQStatus1 register description (NandIRQStatus1, address 0x1700 0800)

| Bit | Symbol | Access | Reset value | Description                                                                                                             |

|-----|--------|--------|-------------|-------------------------------------------------------------------------------------------------------------------------|

| 31  | INT31S | R/W    | 0x0         | mNAND_RYBN3 positive edge. Asserted after a positive edge of the mNAND_RYBN3 signal.                                    |

| 30  | INT30S | R/W    | 0x0         | mNAND_RYBN2 positive edge. Asserted after a positive edge of the mNAND_RYBN2 signal.                                    |

| 29  | INT29S | R/W    | 0x0         | mNAND_RYBN1 positive edge. Asserted after a positive edge of the mNAND_RYBN1 signal.                                    |

| 28  | INT28S | R/W    | 0x0         | mNAND_RYBN0 positive edge. Asserted after a positive edge of the mNAND_RYBN0 signal.                                    |

| 27  | INT27S | R/W    | 0x0         | RAM 1 erased. Whenever an erased page is read from flash (all 0xFF) this bit is asserted together with read page1 done. |

UM10362 © NXP B.V. 2012. All rights reserved.

#### Chapter 2: LPC314x NAND flash controller

Table 7. NandIRQStatus1 register description (NandIRQStatus1, address 0x1700 0800)

| Bit | Symbol | Access | Reset value | Description                                                                                                                                                                                                                                    |

|-----|--------|--------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 26  | INT26S | R/W    | 0x0         | RAM 0 erased. Whenever an erased page is read from flash (all 0xFF) this bit is asserted together with read page0 done.                                                                                                                        |

| 25  | INT25S | R/W    | 0x0         | Write page 1 done. Asserted when SRAM1 contents has been written to the flash.                                                                                                                                                                 |

| 24  | INT24S | R/W    | 0x0         | Write page 0 done. Asserted when SRAM0 contents has been written to the flash.                                                                                                                                                                 |

| 23  | INT23S | R/W    | 0x0         | Read page 1 done. Asserted when SRAM1 contents has been read from flash and stored in SRAM1 (not error corrected yet).                                                                                                                         |

| 22  | INT22S | R/W    | 0x0         | Read page 0 done. Asserted when SRAM0 contents has been read from flash and stored in SRAM0 (not error corrected yet).                                                                                                                         |

| 21  | INT21S | R/W    | 0x0         | RAM 0 decoded. Asserted when the contents of SRAM0 has been decoded. Each time bit21 or bit19 are activated, one other bit will be activated too from the group Bit17-4 that indicates how many errors were detected in the current code word. |

| 20  | INT20S | R/W    | 0x0         | RAM 0 encoded. Asserted when the contents of SRAM0 has been encoded.                                                                                                                                                                           |

| 19  | INT19S | R/W    | 0x0         | RAM 1 decoded. Asserted when the contents of SRAM1 has been decoded. Each time bit21 or bit19 are activated, one other bit will be activated too from the group Bit17-4 that indicates how many errors were detected in the current code word. |

| 18  | INT18S | R/W    | 0x0         | RAM 1 encoded. Asserted when the contents of SRAM1 has been encoded.                                                                                                                                                                           |

| 17  | INT17S | R/W    | 0x0         | RAM 0 decoded with 0 errors                                                                                                                                                                                                                    |

| 16  | INT16S | R/W    | 0x0         | In 5bit ECC mode, this interrupt bit is set when a codeword with one error is detected.                                                                                                                                                        |

|     |        |        |             | In 8bit ECC mode, this interrupt bit is set when a codeword with at least one correctable error is detected. The number of errors can then be extracted from the NandEccErrStatus(0x78) register.                                              |

| 15  | INT15S | R/W    | 0x0         | RAM 0 decoded with 2 error                                                                                                                                                                                                                     |

| 14  | INT14S | R/W    | 0x0         | RAM 0 decoded with 3 error                                                                                                                                                                                                                     |

| 13  | INT13S | R/W    | 0x0         | RAM 0 decoded with 4 error                                                                                                                                                                                                                     |

| 12  | INT12S | R/W    | 0x0         | RAM 0 decoded with 5 error                                                                                                                                                                                                                     |

| 11  | INT11S | R/W    | 0x0         | RAM 0 uncorrectable                                                                                                                                                                                                                            |

| 10  | INT10S | R/W    | 0x0         | RAM 1 decoded with 0 errors                                                                                                                                                                                                                    |

| 9   | INT9S  | R/W    | 0x0         | In 5bit ECC mode, this interrupt bit is set when a codeword with one error is detected.                                                                                                                                                        |

|     |        |        |             | In 8bit ECC mode, this interrupt bit is set when a codeword with at least one correctable error is detected. The number of errors can then be extracted from the NandEccErrStatus(0x78) register.                                              |

| 8   | INT8S  | R/W    | 0x0         | RAM 1 decoded with 2 error                                                                                                                                                                                                                     |

| 7   | INT7S  | R/W    | 0x0         | RAM 1 decoded with 3 error                                                                                                                                                                                                                     |

| 6   | INT6S  | R/W    | 0x0         | RAM 1 decoded with 4 error                                                                                                                                                                                                                     |

| 5   | INT5S  | R/W    | 0x0         | RAM 1 decoded with 5 error                                                                                                                                                                                                                     |

| 4   | INT4S  | R/W    | 0x0         | RAM 1 uncorrectable                                                                                                                                                                                                                            |

#### Chapter 2: LPC314x NAND flash controller

14 of 577

Table 7. NandIRQStatus1 register description (NandIRQStatus1, address 0x1700 0800)

| Bit | Symbol | Access | Reset value | Description                                                               |

|-----|--------|--------|-------------|---------------------------------------------------------------------------|

| 3:2 | -      | -      | -           | Reserved                                                                  |

| 1   | INT1S  | R/W    | 0x0         | RAM 1 AES done. Asserted when the contents of SRAM1 has been AES decoded. |

| 0   | INT0S  | R/W    | 0x0         | RAM 0 AES done. Asserted when the contents of SRAM0 has been AES decoded. |

#### 5.2 NandIRQMask1

Each bit in this register field masks the corresponding interrupt bit in the NandIRQStatus register. Table 2–7 gives a description of this register.

Table 8. NandlRQMask1 register description (NandlRQMask1, address 0x1700 0804)

| 30         INT30M         R/W         0x1         mNAND_RYBN2 positive edge m.           29         INT29M         R/W         0x1         mNAND_RYBN1 positive edge m.           28         INT28M         R/W         0x1         mNAND_RYBN0 positive edge m.           27         INT27M         R/W         0x1         RAM 1 erased mask           26         INT26M         R/W         0x1         RAM 0 erased mask           25         INT25M         R/W         0x1         Write page 1 done mask           24         INT24M         R/W         0x1         Read page 1 done mask           23         INT23M         R/W         0x1         Read page 0 done mask           22         INT22M         R/W         0x1         Read page 0 done mask           21         INT21M         R/W         0x1         RAM 0 decoded mask           20         INT20M         R/W         0x1         RAM 0 encoded mask           19         INT19M         R/W         0x1         RAM 1 decoded mask           18         INT19M         R/W         0x1         RAM 0 decoded with 0 errors mask           17         INT15M         R/W         0x1         RAM 0 decoded with 2 error mask                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |        |        |             | <u> </u>                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------|--------|-------------|----------------------------------|

| 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Bit | Symbol | Access | Reset Value | Description                      |

| 29         INT29M         R/W         0x1         mNAND_RYBN1 positive edge may           28         INT28M         R/W         0x1         mNAND_RYBN0 positive edge may           27         INT27M         R/W         0x1         RAM 1 erased mask           26         INT26M         R/W         0x1         RAM 0 erased mask           25         INT25M         R/W         0x1         Write page 1 done mask           24         INT24M         R/W         0x1         Read page 1 done mask           23         INT23M         R/W         0x1         Read page 0 done mask           22         INT22M         R/W         0x1         Read page 0 done mask           21         INT21M         R/W         0x1         Read page 0 done mask           22         INT22M         R/W         0x1         RAM 0 decoded mask           20         INT20M         R/W         0x1         RAM 0 encoded mask           19         INT19M         R/W         0x1         RAM 1 decoded mask           18         INT19M         R/W         0x1         RAM 0 decoded with 0 errors mask           17         INT19M         R/W         0x1         RAM 0 decoded with 3 error mask <tr< td=""><td>31</td><td>INT31M</td><td>R/W</td><td>0x1</td><td>mNAND_RYBN3 positive edge mask</td></tr<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 31  | INT31M | R/W    | 0x1         | mNAND_RYBN3 positive edge mask   |

| 28         INT28M         R/W         0x1         mNAND_RYBN0 positive edge mask           27         INT27M         R/W         0x1         RAM 1 erased mask           26         INT26M         R/W         0x1         RAM 0 erased mask           25         INT25M         R/W         0x1         Write page 1 done mask           24         INT24M         R/W         0x1         Read page 1 done mask           23         INT23M         R/W         0x1         Read page 0 done mask           22         INT22M         R/W         0x1         RAM 0 decoded mask           21         INT21M         R/W         0x1         RAM 0 encoded mask           20         INT20M         R/W         0x1         RAM 1 decoded mask           19         INT19M         R/W         0x1         RAM 1 decoded mask           18         INT19M         R/W         0x1         RAM 1 decoded with 0 errors mask           17         INT17M         R/W         0x1         RAM 0 decoded with 1 error mask           15         INT15M         R/W         0x1         RAM 0 decoded with 2 error mask           14         INT14M         R/W         0x1         RAM 0 decoded with 3 error mask <td>30</td> <td>INT30M</td> <td>R/W</td> <td>0x1</td> <td>mNAND_RYBN2 positive edge mask</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 30  | INT30M | R/W    | 0x1         | mNAND_RYBN2 positive edge mask   |

| 27         INT27M         R/W         0x1         RAM 1 erased mask           26         INT26M         R/W         0x1         RAM 0 erased mask           25         INT25M         R/W         0x1         Write page 1 done mask           24         INT24M         R/W         0x1         Write page 0 done mask           23         INT23M         R/W         0x1         Read page 1 done mask           22         INT22M         R/W         0x1         Read page 0 done mask           21         INT21M         R/W         0x1         RAM 0 decoded mask           20         INT20M         R/W         0x1         RAM 0 encoded mask           19         INT19M         R/W         0x1         RAM 1 decoded mask           17         INT19M         R/W         0x1         RAM 1 decoded with 0 errors mask           18         INT19M         R/W         0x1         RAM 0 decoded with 1 error mask           15         INT15M         R/W         0x1         RAM 0 decoded with 2 error mask           14         INT14M         R/W         0x1         RAM 0 decoded with 3 error mask           12         INT13M         R/W         0x1         RAM 0 decoded with 5 error mask                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 29  | INT29M | R/W    | 0x1         | mNAND_RYBN1 positive edge mask   |

| 26         INT26M         R/W         0x1         RAM 0 erased mask           25         INT25M         R/W         0x1         Write page 1 done mask           24         INT24M         R/W         0x1         Write page 0 done mask           23         INT23M         R/W         0x1         Read page 1 done mask           22         INT22M         R/W         0x1         Read page 0 done mask           21         INT21M         R/W         0x1         RAM 0 decoded mask           20         INT20M         R/W         0x1         RAM 0 encoded mask           19         INT19M         R/W         0x1         RAM 1 decoded mask           18         INT18M         R/W         0x1         RAM 1 decoded with 0 errors mask           16         INT16M         R/W         0x1         RAM 0 decoded with 1 error mask           15         INT15M         R/W         0x1         RAM 0 decoded with 2 error mask           14         INT14M         R/W         0x1         RAM 0 decoded with 3 error mask           12         INT13M         R/W         0x1         RAM 0 decoded with 5 error mask           11         INT11M         R/W         0x1         RAM 0 decoded with 5 erro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 28  | INT28M | R/W    | 0x1         | mNAND_RYBN0 positive edge mask   |

| 25         INT25M         R/W         0x1         Write page 1 done mask           24         INT24M         R/W         0x1         Write page 0 done mask           23         INT23M         R/W         0x1         Read page 1 done mask           22         INT22M         R/W         0x1         Read page 0 done mask           21         INT21M         R/W         0x1         RAM 0 decoded mask           20         INT20M         R/W         0x1         RAM 0 encoded mask           19         INT19M         R/W         0x1         RAM 1 decoded mask           18         INT18M         R/W         0x1         RAM 1 encoded mask           17         INT17M         R/W         0x1         RAM 0 decoded with 0 errors mask           16         INT16M         R/W         0x1         RAM 0 decoded with 2 error mask           15         INT15M         R/W         0x1         RAM 0 decoded with 3 error mask           13         INT13M         R/W         0x1         RAM 0 decoded with 4 error mask           12         INT12M         R/W         0x1         RAM 0 decoded with 5 error mask           10         INT10M         R/W         0x1         RAM 0 decoded with 6 err                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 27  | INT27M | R/W    | 0x1         | RAM 1 erased mask                |

| INT24M   R/W   Ox1   Write page 0 done mask                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 26  | INT26M | R/W    | 0x1         | RAM 0 erased mask                |

| 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 25  | INT25M | R/W    | 0x1         | Write page 1 done mask           |

| 22 INT22M R/W 0x1 Read page 0 done mask 21 INT21M R/W 0x1 RAM 0 decoded mask 20 INT20M R/W 0x1 RAM 0 encoded mask 19 INT19M R/W 0x1 RAM 1 decoded mask 18 INT18M R/W 0x1 RAM 1 encoded mask 17 INT17M R/W 0x1 RAM 0 decoded with 0 errors mask 18 INT16M R/W 0x1 RAM 0 decoded with 1 error mask 19 INT15M R/W 0x1 RAM 0 decoded with 2 error mask 10 INT16M R/W 0x1 RAM 0 decoded with 2 error mask 11 INT15M R/W 0x1 RAM 0 decoded with 3 error mask 12 INT13M R/W 0x1 RAM 0 decoded with 4 error mask 13 INT13M R/W 0x1 RAM 0 decoded with 5 error mask 14 INT11M R/W 0x1 RAM 0 decoded with 5 error mask 15 INT15M R/W 0x1 RAM 0 decoded with 6 errors mask 16 INT10M R/W 0x1 RAM 1 decoded with 1 error mask 17 INT10M R/W 0x1 RAM 1 decoded with 1 error mask 18 INT8M R/W 0x1 RAM 1 decoded with 2 error mask 19 INT9M R/W 0x1 RAM 1 decoded with 2 error mask 10 INT9M R/W 0x1 RAM 1 decoded with 2 error mask 11 INT9M R/W 0x1 RAM 1 decoded with 3 error mask 12 INT9M R/W 0x1 RAM 1 decoded with 3 error mask 13 INT8M R/W 0x1 RAM 1 decoded with 3 error mask 14 INT9M R/W 0x1 RAM 1 decoded with 3 error mask 15 INT5M R/W 0x1 RAM 1 decoded with 4 error mask 16 INT6M R/W 0x1 RAM 1 decoded with 5 error mask 17 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 18 INT6M R/W 0x1 RAM 1 decoded with 5 error mask 19 INT6M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 24  | INT24M | R/W    | 0x1         | Write page 0 done mask           |

| INT21M R/W 0x1 RAM 0 decoded mask  INT20M R/W 0x1 RAM 0 encoded mask  INT19M R/W 0x1 RAM 1 decoded mask  INT19M R/W 0x1 RAM 1 decoded mask  INT18M R/W 0x1 RAM 1 encoded mask  INT17M R/W 0x1 RAM 0 decoded with 0 errors mask  INT16M R/W 0x1 RAM 0 decoded with 1 error mask  INT15M R/W 0x1 RAM 0 decoded with 2 error mask  INT15M R/W 0x1 RAM 0 decoded with 3 error mask  INT14M R/W 0x1 RAM 0 decoded with 4 error mask  INT13M R/W 0x1 RAM 0 decoded with 5 error mask  INT13M R/W 0x1 RAM 0 decoded with 5 error mask  INT11M R/W 0x1 RAM 0 decoded with 5 error mask  INT11M R/W 0x1 RAM 0 decoded with 5 error mask  INT11M R/W 0x1 RAM 1 decoded with 0 errors mask  INT10M R/W 0x1 RAM 1 decoded with 1 error mask  INT9M R/W 0x1 RAM 1 decoded with 2 error mask  INT9M R/W 0x1 RAM 1 decoded with 3 error mask  INT5M R/W 0x1 RAM 1 decoded with 3 error mask  INT5M R/W 0x1 RAM 1 decoded with 3 error mask  RAM 1 decoded with 4 error mask  INT5M R/W 0x1 RAM 1 decoded with 4 error mask  RAM 1 decoded with 5 error mask                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 23  | INT23M | R/W    | 0x1         | Read page 1 done mask            |

| INT20M R/W 0x1 RAM 0 encoded mask  INT19M R/W 0x1 RAM 1 decoded mask  INT18M R/W 0x1 RAM 1 encoded mask  INT17M R/W 0x1 RAM 0 decoded with 0 errors mask  INT16M R/W 0x1 RAM 0 decoded with 1 error mask  INT15M R/W 0x1 RAM 0 decoded with 2 error mask  INT15M R/W 0x1 RAM 0 decoded with 3 error mask  INT14M R/W 0x1 RAM 0 decoded with 3 error mask  INT13M R/W 0x1 RAM 0 decoded with 4 error mask  INT13M R/W 0x1 RAM 0 decoded with 5 error mask  INT12M R/W 0x1 RAM 0 decoded with 5 error mask  INT11M R/W 0x1 RAM 0 decoded with 5 error mask  INT11M R/W 0x1 RAM 0 uncorrectable mask  INT11M R/W 0x1 RAM 1 decoded with 0 errors mask  INT19M R/W 0x1 RAM 1 decoded with 1 error mask  INT19M R/W 0x1 RAM 1 decoded with 2 error mask  INT19M R/W 0x1 RAM 1 decoded with 3 error mask  INT19M R/W 0x1 RAM 1 decoded with 3 error mask  INT19M R/W 0x1 RAM 1 decoded with 3 error mask  INT19M R/W 0x1 RAM 1 decoded with 3 error mask  INT19M R/W 0x1 RAM 1 decoded with 4 error mask  INT19M R/W 0x1 RAM 1 decoded with 5 error mask  INT19M R/W 0x1 RAM 1 decoded with 5 error mask  INT19M R/W 0x1 RAM 1 decoded with 5 error mask  INT19M R/W 0x1 RAM 1 decoded with 5 error mask  INT19M R/W 0x1 RAM 1 decoded with 5 error mask                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 22  | INT22M | R/W    | 0x1         | Read page 0 done mask            |

| 19 INT19M R/W 0x1 RAM 1 decoded mask 18 INT18M R/W 0x1 RAM 1 encoded mask 17 INT17M R/W 0x1 RAM 0 decoded with 0 errors mask 16 INT16M R/W 0x1 RAM 0 decoded with 1 error mask 15 INT15M R/W 0x1 RAM 0 decoded with 2 error mask 14 INT14M R/W 0x1 RAM 0 decoded with 3 error mask 13 INT13M R/W 0x1 RAM 0 decoded with 4 error mask 14 INT12M R/W 0x1 RAM 0 decoded with 5 error mask 17 INT12M R/W 0x1 RAM 0 decoded with 5 error mask 18 INT19M R/W 0x1 RAM 0 decoded with 5 error mask 19 INT10M R/W 0x1 RAM 1 decoded with 0 errors mask 10 INT10M R/W 0x1 RAM 1 decoded with 1 error mask 10 INT9M R/W 0x1 RAM 1 decoded with 2 error mask 11 INT8M R/W 0x1 RAM 1 decoded with 2 error mask 12 INT8M R/W 0x1 RAM 1 decoded with 3 error mask 19 INT8M R/W 0x1 RAM 1 decoded with 3 error mask 10 INT6M R/W 0x1 RAM 1 decoded with 4 error mask 10 INT6M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT6M R/W 0x1 RAM 1 decoded with 5 error mask                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 21  | INT21M | R/W    | 0x1         | RAM 0 decoded mask               |

| 18INT18MR/W0x1RAM 1 encoded mask17INT17MR/W0x1RAM 0 decoded with 0 errors mask16INT16MR/W0x1RAM 0 decoded with 1 error mask15INT15MR/W0x1RAM 0 decoded with 2 error mask14INT14MR/W0x1RAM 0 decoded with 3 error mask13INT13MR/W0x1RAM 0 decoded with 4 error mask12INT12MR/W0x1RAM 0 decoded with 5 error mask11INT11MR/W0x1RAM 0 uncorrectable mask10INT10MR/W0x1RAM 1 decoded with 0 errors mask9INT9MR/W0x1RAM 1 decoded with 1 error mask8INT8MR/W0x1RAM 1 decoded with 2 error mask7INT7MR/W0x1RAM 1 decoded with 3 error mask6INT6MR/W0x1RAM 1 decoded with 4 error mask5INT5MR/W0x1RAM 1 decoded with 5 error mask                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 20  | INT20M | R/W    | 0x1         | RAM 0 encoded mask               |

| 17 INT17M R/W 0x1 RAM 0 decoded with 0 errors mask 16 INT16M R/W 0x1 RAM 0 decoded with 1 error mask 15 INT15M R/W 0x1 RAM 0 decoded with 2 error mask 14 INT14M R/W 0x1 RAM 0 decoded with 3 error mask 13 INT13M R/W 0x1 RAM 0 decoded with 4 error mask 12 INT12M R/W 0x1 RAM 0 decoded with 5 error mask 11 INT11M R/W 0x1 RAM 0 uncorrectable mask 10 INT10M R/W 0x1 RAM 1 decoded with 0 errors mask 10 INT9M R/W 0x1 RAM 1 decoded with 1 error mask 10 INT9M R/W 0x1 RAM 1 decoded with 2 error mask 10 INT9M R/W 0x1 RAM 1 decoded with 2 error mask 10 INT9M R/W 0x1 RAM 1 decoded with 3 error mask 10 INT9M R/W 0x1 RAM 1 decoded with 3 error mask 10 INT9M R/W 0x1 RAM 1 decoded with 3 error mask 10 INT6M R/W 0x1 RAM 1 decoded with 3 error mask 10 INT6M R/W 0x1 RAM 1 decoded with 4 error mask 10 INT6M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT6M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT6M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded wit | 19  | INT19M | R/W    | 0x1         | RAM 1 decoded mask               |

| 16 INT16M R/W 0x1 RAM 0 decoded with 1 error mask 15 INT15M R/W 0x1 RAM 0 decoded with 2 error mask 14 INT14M R/W 0x1 RAM 0 decoded with 3 error mask 13 INT13M R/W 0x1 RAM 0 decoded with 4 error mask 12 INT12M R/W 0x1 RAM 0 decoded with 5 error mask 11 INT11M R/W 0x1 RAM 0 uncorrectable mask 10 INT10M R/W 0x1 RAM 1 decoded with 0 errors mask 10 INT9M R/W 0x1 RAM 1 decoded with 1 error mask 10 INT9M R/W 0x1 RAM 1 decoded with 2 error mask 11 RAM 1 decoded with 2 error mask 11 RAM 1 decoded with 2 error mask 11 RAM 1 decoded with 3 error mask 11 RAM 1 decoded with 4 error mask 11 RAM 1 decoded with 4 error mask 11 RAM 1 decoded with 5 error mask 12 RAM 1 decoded with 5 error mask 13 RAM 1 decoded with 5 error mask 14 RAM 1 decoded with 5 error mask 15 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 15 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 15 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 15 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 15 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 15 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 15 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 15 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 15 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 15 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 15 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 15 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 15 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 15 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 15 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 15 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 15 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 15 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 15 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 15 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 15 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 15 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 15 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 15 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 15 INT5M | 18  | INT18M | R/W    | 0x1         | RAM 1 encoded mask               |

| 15 INT15M R/W 0x1 RAM 0 decoded with 2 error mask 14 INT14M R/W 0x1 RAM 0 decoded with 3 error mask 13 INT13M R/W 0x1 RAM 0 decoded with 4 error mask 12 INT12M R/W 0x1 RAM 0 decoded with 5 error mask 11 INT11M R/W 0x1 RAM 0 uncorrectable mask 10 INT10M R/W 0x1 RAM 1 decoded with 0 errors mask 10 INT9M R/W 0x1 RAM 1 decoded with 1 error mask 18 INT8M R/W 0x1 RAM 1 decoded with 2 error mask 19 INT9M R/W 0x1 RAM 1 decoded with 2 error mask 19 INT9M R/W 0x1 RAM 1 decoded with 3 error mask 19 INT9M R/W 0x1 RAM 1 decoded with 3 error mask 19 INT9M R/W 0x1 RAM 1 decoded with 3 error mask 19 INT9M R/W 0x1 RAM 1 decoded with 3 error mask 19 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 19 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 19 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 19 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 19 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 19 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 19 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 19 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 19 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 19 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 19 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 19 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 19 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 19 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 19 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 19 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 19 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 19 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 19 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 19 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 19 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 19 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 19 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 19 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 19 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 19 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 19 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 19 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 19 INT5M R/W 0x1 RAM 1 decoded with 5 | 17  | INT17M | R/W    | 0x1         | RAM 0 decoded with 0 errors mask |

| 14 INT14M R/W 0x1 RAM 0 decoded with 3 error mask 13 INT13M R/W 0x1 RAM 0 decoded with 4 error mask 12 INT12M R/W 0x1 RAM 0 decoded with 5 error mask 11 INT11M R/W 0x1 RAM 0 uncorrectable mask 10 INT10M R/W 0x1 RAM 1 decoded with 0 errors mask 10 INT9M R/W 0x1 RAM 1 decoded with 1 error mask 10 INT9M R/W 0x1 RAM 1 decoded with 1 error mask 10 INT9M R/W 0x1 RAM 1 decoded with 2 error mask 10 INT8M R/W 0x1 RAM 1 decoded with 3 error mask 10 INT6M R/W 0x1 RAM 1 decoded with 3 error mask 10 INT6M R/W 0x1 RAM 1 decoded with 4 error mask 10 INT6M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5 error mask 10 INT5M R/W 0x1 RAM 1 decoded with 5  | 16  | INT16M | R/W    | 0x1         | RAM 0 decoded with 1 error mask  |

| 13 INT13M R/W 0x1 RAM 0 decoded with 4 error mask 12 INT12M R/W 0x1 RAM 0 decoded with 5 error mask 11 INT11M R/W 0x1 RAM 0 uncorrectable mask 10 INT10M R/W 0x1 RAM 1 decoded with 0 errors mask 9 INT9M R/W 0x1 RAM 1 decoded with 1 error mask 8 INT8M R/W 0x1 RAM 1 decoded with 2 error mask 7 INT7M R/W 0x1 RAM 1 decoded with 3 error mask 6 INT6M R/W 0x1 RAM 1 decoded with 4 error mask 5 INT5M R/W 0x1 RAM 1 decoded with 5 error mask                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 15  | INT15M | R/W    | 0x1         | RAM 0 decoded with 2 error mask  |

| 12 INT12M R/W 0x1 RAM 0 decoded with 5 error mask 11 INT11M R/W 0x1 RAM 0 uncorrectable mask 10 INT10M R/W 0x1 RAM 1 decoded with 0 errors mask 9 INT9M R/W 0x1 RAM 1 decoded with 1 error mask 8 INT8M R/W 0x1 RAM 1 decoded with 2 error mask 7 INT7M R/W 0x1 RAM 1 decoded with 3 error mask 6 INT6M R/W 0x1 RAM 1 decoded with 4 error mask 5 INT5M R/W 0x1 RAM 1 decoded with 5 error mask                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 14  | INT14M | R/W    | 0x1         | RAM 0 decoded with 3 error mask  |

| 11 INT11M R/W 0x1 RAM 0 uncorrectable mask 10 INT10M R/W 0x1 RAM 1 decoded with 0 errors mask 9 INT9M R/W 0x1 RAM 1 decoded with 1 error mask 8 INT8M R/W 0x1 RAM 1 decoded with 2 error mask 7 INT7M R/W 0x1 RAM 1 decoded with 3 error mask 6 INT6M R/W 0x1 RAM 1 decoded with 4 error mask 5 INT5M R/W 0x1 RAM 1 decoded with 5 error mask                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 13  | INT13M | R/W    | 0x1         | RAM 0 decoded with 4 error mask  |